# POUL EDITION Electronics Handbook

1

Fraidoon Mazda

00000

86666

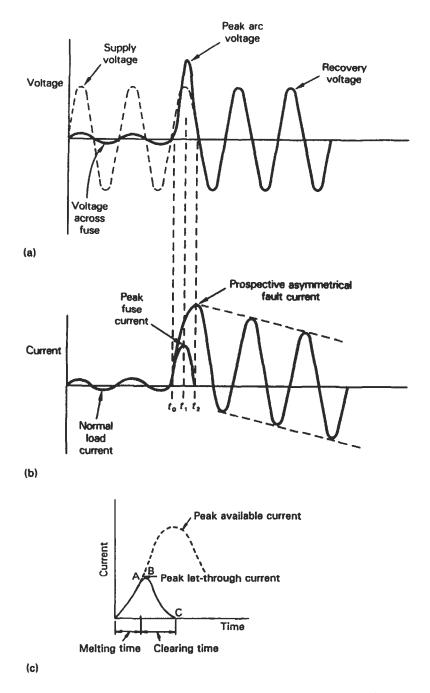

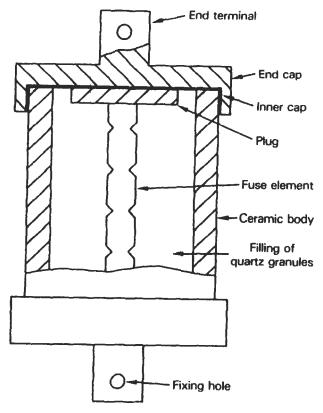

# **Power Electronics Handbook**

Third edition

Fraidoon Mazda

OXFORD AMSTERDAM BOSTON LONDON NEW YORK PARIS SAN DIEGO SAN FRANCISCO SINGAPORE SYDNEY TOKYO Newnes An imprint of Elsevier Science Linacre House, Jordan Hill, Oxford OX2 8DP 200 Wheeler Road, Burlington MA 01803

First published 1990 Second edition 1993 Third edition 1997 Transferred to digital printing 2003

Copyright © 1990, 1993, 1997 Fraidoon Mazda. All rights reserved

The right of Fraidoon Mazda to be identified as the author of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988

No part of this publication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1T 4LP. Applications for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publisher

#### British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

Library of Congress Cataloguing in Publication Data A catalogue record for this book is available from the Library of Congress

ISBN 0 7506 2926 6

For information on all Newnes publications visit our website at www.newnespress.com

Printed and bound in Great Britain by Antony Rowe Ltd, Eastbourne

## Contents

| Preface                                        | vii |

|------------------------------------------------|-----|

| Part 1 Components                              | 1   |

| 1 Power semiconductor devices                  | 3   |

| 2 Thermal design                               | 61  |

| 3 Power semiconductor control components       | 74  |

| 4 Electromagnetic compatibility                | 99  |

| 5 Power semiconductor protection               | 121 |

| Part 2 Circuits                                | 135 |

| 6 Power semiconductor circuits – a résumé      | 137 |

| 7 Static switches                              | 147 |

| 8 A.C. line control                            | 157 |

| 9 Phase-controlled rectification and inversion | 178 |

| 10 Direct a.c. frequency converters            | 221 |

| 11 Forced commutation techniques               | 242 |

| 12 D.C. to d.c. converters                     | 261 |

| 13 D.C. link frequency changers                | 284 |

| Part 3 Applications                            | 353 |

| 14 Power semiconductor circuit applications    | 355 |

| Appendix 1 List of symbols                     | 417 |

| Appendix 2 Glossary of terms                   | 423 |

| Index                                          | 429 |

i.

### Preface

There have been many developments in the field of power electronics since the publication of the second edition, almost five years ago. Devices have become bigger and better – bigger silicon die, and current and voltage ratings. However, semiconductor devices have also become smaller and better, integrated circuit devices, that is. And the marriage of low power integrated circuit tecnology and high power semiconductors has resulted in benefit to both fields.

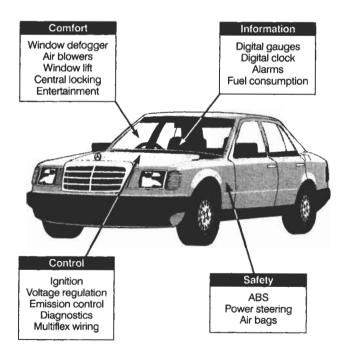

The third edition of the *Power Electronics Handbook* reflects these changes. Although the basic design chapters have been largely unchanged, those on power and control components have been updated with the addition of sections on power devices such as the IGBT, and on the integration of low and high power devices, such as in smart power components The section on EMC has also been updated to include recent standards. A new section on the application of power components within automobiles has been added, since the use of power devices in this area has increased considerably.

The first chapter describes the processes used in the manufacture of power semiconductors and the construction and characteristics of the power semiconductors currently available. Chapters 2 to 5 cover devices which are used in conjunction with power semiconductors. Chapter 2 introduces the methods and components for removing heat generated within the power semiconductor, a vital requirement for effective operation. Chapter 3 describes low power devices, including those classified as smart power, which are used to control the operation of power semiconductors. Chapter 4 introduces the techniques and components necessary to minimise radio frequency interference generated by power electronic circuits; with the tightening of European and world regulations, this is clearly an important consideration. Chapter 5 describes components and circuits used to protect power components from malfunction, such as caused by overcurrent and overvoltage.

Chapters 6 to 13 provide detailed information on the arrangements and design of the various types of power semiconductor circuits. Because there are a large number of different types of such circuits, this whole field is first surveyed in Chapter 6, to give the student a unified picture.

Chapter 7 describes the most basic type of power circuit, that used for simple static switching. This is taken further in Chapter 8 to controlling the value of the a.c. line voltage. Chapter 9 extends the voltage control concept viii Preface

to include rectification, so taht the a.c. is controlled to give a variable d.c. voltage.

Although similar in concept to a.c. line control and rectification, the next chapter describes a completely different application, the use of power electronics to vary the frequency of an a.c. supply without first going through d.c. These are also referred to as cycloconverters.

Chapters 11, 12 and 13 are related, since in these the power semiconductors switches operate from a d.c. supply and need to be forced commutated. Chapter 11 classifies the various commutation systems which are popularly used, and Chapters 12 and 13 describe two prime application areas, those of voltage control and of frequency changing.

Finally Chapter 14 describes some of the most common applications of power semiconductor components and circuits, introduced in earlier chapters of the book. This includes power supplies, electrical machine control, heating and lighting, and automobile control applications.

I started my career as a power electronic engineer at just about the time that the first thyristors were becoming commercially available. From then on I have continued to learn daily, as new developments have been made and new material published. I am grateful to the many authors who have enriched the technical press with their writings and so made this possible. To them, and to the many other power electronic engineers, who have worked to extend our knowledge in this valuable area, this book is gratefully dedicated.

> Fraidoon Mazda Bishop's Stortford September 1997

Part 1

## Components

#### **1.1 Introduction**

#### 1.1.1 Historical development

The field of power electronics is not new. The post- and pre-war periods, from about 1930 to 1950, saw extensive application of power electronics, based primarily on the mercury arc rectifier and the gas-filled tube.

It was in December 1939 that William Shockley first noted the principle of a semiconductor which could be used for controlling electrical power. However, it was not until 23 December 1947, the official date for the invention of the transistor, that a simple point contact transistor was demonstrated by William Shockley, John Bardeen and Walter Brattain, to the executives of Bell Laboratories. It was at this point that semiconductor electronic technology was born.

Two other dates are important when tracking the development of power semiconductors. The integrated circuit was invented by Jack Kelby of Texas Instruments in 1958. Integrated circuits, especially microprocessors, are now used extensively to control power semiconductor devices. Finally, the thyristor, the workhorse of the power semiconductor field, was announced by General Electric in 1957. It was originally called the silicon-controlled rectifier (SCR), to differentiate it from the common silicon rectifier, and it was some time later that the name was changed to thyristor.

#### 1.1.2 Applications

Power semiconductors are used in wide-ranging applications. The following gives only a representative sample.

- (i) Industrial applications consist primarily of two areas, motor control and power supplies. The motors which are controlled vary from the very large, as used in steel mills, to the relatively smaller ones, such as in machine tools. Power supplies too come in many shapes and sizes, such as for battery charging, induction heating, electroplating and welding.

- (ii) Consumer applications cover many different areas in the home, such as audio amplifiers; heat controls; light dimmers; motor control for food mixers and hand power tools; and security systems.

- 4 Power semiconductor devices

- (iii) Transportation applications, the largest being motor drives for areas such as electric vehicles, locomotives, and fork-lift trucks. Equally important are non-motor drive applications, such as traffic signal control, vehicle electronic ignition and vehicle voltage regulation.

- (iv) Aerospace and defence applications include VLF transmitters; power supplies for space and aircraft; and switching using solid state relays and contactors.

#### 1.1.3 Power semiconductor operation

This chapter describes the construction and characteristics of several types of power semiconductor devices. These can generally be operated in different modes, due either to their construction or the application in which they are used. Four operating modes are considered in this chapter:

- (i) One way of differentiating devices is whether they are capable of being controlled, regarding their turn-on point. The power rectifier cannot be so controlled, since it will conduct as soon as the voltage at its anode is more positive than that at its cathode. All other power devices described in this chapter, such as the transistor, thyristor, gate turn-off switch and triac, can be turned on (and sometimes off) by a control signal on an auxiliary input.

- (ii) Some power devices can also be operated in a linear or a switching mode. The transistor is the only component described here which is capable of linear operation, so it is the obvious choice for this application. Losses, caused by the product of current through the device and voltage drop across it, are much higher when in the linear mode. Switching devices can handle greater power, since their dissipation is lower. Their power gain is also generally higher, so that they need less drive current to control their operation.

- (iii) The third operating mode is the type of signal required to control the power semiconductor devices. Generally, this consists of an electrical signal, although in a large class of devices optical energy is used.

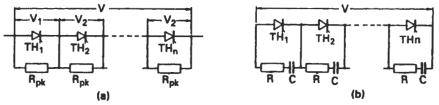

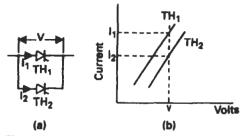

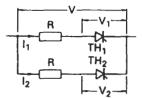

- (iv) Finally, the voltage and current capability of power devices can be considerably increased by operating several of them in series or in parallel mode, so that the total voltage and current are shared across several devices.

#### **1.1.4 Device characteristics**

Many of the power semiconductor devices described here have special characteristics. There are, however, also many similarities, such as:

- (i) The voltage drop across the device when it is carrying current.

- (ii) The capability of the device to handle current. Both the steady state current and the peak or overload current-carrying ability are important, since overload capabilities often determine the need for protection.

- (iii) The capability of the device to block voltage, both in the direction reverse to that in which it normally conducts, and in the conduction direction, when it has not yet been turned on.

- (iv) The maximum rate of rise of current which the device can withstand, without being destroyed due to localised heating, and the maximum rate of rise of voltage in the forward direction which it can withstand, without turning on prematurely.

- (v) The switching speed of the device, which influences its switching losses and the maximum frequency at which it can be operated.

- (vi) The rate at which a conducting device can recover its blocking capability. This again influences its maximum operating frequency.

- (vii) The maximum power dissipation which the device can withstand. This characteristic is often linked to the maximum junction temperature at which the device can operate and its thermal transfer characteristic, that is, its ability to transfer heat to a heatsink.

- (viii) The power gain of the device, which is the ratio of the controlled power to the power needed in the control terminal. The higher this gain, the lower the power dissipation in the control electronics of the power semiconductor.

#### **1.2 Fabrication process**

The manufacturing processes for power semiconductors closely resemble those used for other semiconductor devices. These consist of the following, which are described further in this section:

- (i) Preparation of a wafer of very pure silicon, which forms the base to support the power semiconductor.

- (ii) Oxide growth over selected areas of the semiconductor surface, to protect the layers below it from contamination and to form a mask for subsequent processing steps.

- (iii) Growth of an epitaxial layer onto the silicon wafer, which forms a controlled layer into which the various parts of the semiconductor device can be formed.

- (iv) Photolithography, used to control the areas where the p and n components are formed.

- (v) Diffusion, which is the most common method used to form the p and n components of the semiconductor device.

- (vi) Ion implantation, which is able to produce p and n areas to a high precision.

- (vii) Metal formation, which is used to interconnect the various p and n parts of the semiconductor devices together, and to provide a base for connection of the silicon to the package of the device.

#### **1.2.1 Crystal preparation**

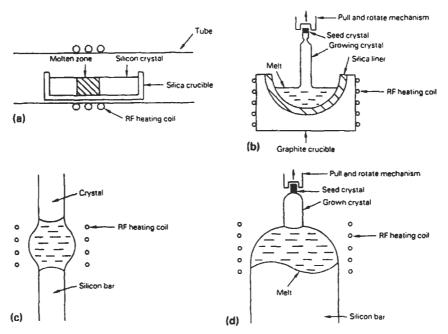

In order to obtain high-quality semiconductor components it is important to start with a semiconductor material which has a very low level of defects in its crystal structure. Several techniques exist for growing bulk semiconductor crystals, some of these being illustrated in Figure 1.1.

In the zone-levelling method a crucible, made from silica, holds the impure silicon, and it is slowly moved along a quartz tube, containing an inert gas. Zoned heating coils are placed along the length of the tube,

Figure 1.1 Semiconductor bulk crystal purification and growth systems: (a) zone-levelling; (b) Czochralski growing; (c) floating zone-refining; (d) pedestal pulling

which cause an area in the silicon to melt. This molten area is moved down the silicon, to one end of the crystal, as the silica crucible moves along the tube. Impurities in the silicon are carried by the molten area to the end region, so that after several passes this end can be cut off, leaving a relatively pure section of silicon behind.

Although the zone-levelling method is simple and cheap to operate, it gives a relatively high level of residual impurities and poor crystal structure, since the silicon cools in contact with the silica crucible. The Czochralski growth method overcomes these problems by avoiding contact between the crystal and its crucible. In this system a tiny seed of silicon crystal is lowered into a bath of molten silicon, contained in a graphite crucible. The seed is rotated and slowly withdrawn from the molten bath. This causes the silicon from the melt to settle on the seed crystal and to cool, resulting in the formation of a bar of pure silicon.

The floating zone-refining method uses an r.f. heating coil, which is slowly moved along the length of a silicon bar. This results in a molten layer of silicon moving along the bar, carrying impurities with it, which can eventually be cut off from the end of the silicon bar. The method is therefore similar to the zone-levelling technique of Figure 1.1(a), except that the risk of contamination is considerably reduced, since the silicon is not in contact with a crucible.

The pedestal-pulling technique is similar in principle to the Czochralski method except that the melt is formed in the surface of the impure silicon bar itself, so that risk of contamination from the use of a crucible is once again avoided. Since in both the floating-zone and pedestal-pulling methods the molten silicon is held in place by surface tension, the size of the melt, and therefore of the silicon bars (and wafers) produced by these methods, cannot be very large. These techniques are used for making relatively low-power components.

During preparation of pure silicon, impurities of p or n type can be added to the melt, to give the final silicon ingots the required resistivity. The ingots are then cut into slices, using a diamond-impregnated saw. The saw cuts are made along the <111> or <100> planes of the crystal. These cuts usually damage the crystal lattice near the silicon surface, resulting in poor resistivity and minority carrier lifetime. The damaged area, which is about 20  $\mu$ m deep, is removed by etching in a mixture of hydrofluoric and nitric acids, and the surface is then polished to give a strain-free, highly flat region.

#### 1.2.2 Oxide growth

Silicon oxide, also called silica or  $SiO_2$ , may be grown and removed several times from the surface of the silicon slice during manufacture of the semiconductor device. The oxide layer is used for diffusion masking, for sealing and passivating the silicon surface, and for insulating the metal interconnections from the silicon. Although the oxide layer may be deposited onto the slice, as done for the epitaxy layer described in the next section, it is more usual to grow it using dry or wet oxygen or steam.

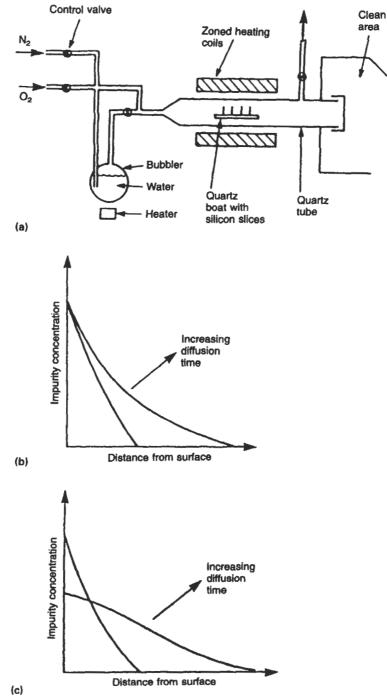

Figure 1.2(a) shows a typical arrangement of the apparatus used for oxidation (and diffusion). The silicon slices are stacked upright in a quartz boat and inserted into a quartz tube. The tube is heated to between 1000°C and 1200°C by zoned heaters, so that the boat is located in an area having a uniform temperature along a length of the tube. Nitrogen, dry oxygen, wet oxygen (which is oxygen bubbled into water at 95°C) or steam can be passed over the slices to grow the oxide layer. A thickness of about 1  $\mu$ m takes about 4 h to grow and consumes between 0.4  $\mu$ m and 0.5  $\mu$ m of the silicon. The colour of the silicon surface changes with the thickness of the oxide layer, due to the shift in the wavelength of the reflected light. This effect is used as an indication of the layer thickness.

#### 1.2.3 Epitaxy growth

Epitaxy means growing a single-crystal silicon structure on the original slice, such that the new structure is essentially a molecular extension of the original silicon. Epitaxy layers can be closely controlled regarding size and resistivity, to about  $\pm 10\%$ . This compares favourably with the  $\pm 30\%$  resistivity control obtained when pulling from the silicon melt.

Epitaxy apparatus is similar to the oxide growth arrangement shown in Figure 1.2(a). However, r.f. heating coils are normally used and the silicon slices are placed in a graphite boat, which may be coated with quartz to prevent the graphite contaminating the silicon. The bubbler usually contains silicon tetrachloride (SiCl<sub>4</sub>) to which may be added a controlled amount of an impurity, such as PCl<sub>3</sub>. Hydrogen gas is bubbled through this mixture before entering the quartz epitaxy tube.

8 Power semiconductor devices

Figure 1.2 Semiconductor diffusion: (a) open-tube arrangement; (b) impurity concentration using error function; (c) Gaussian impurity concentration

Initially the slices are heated to about  $1200^{\circ}$ C and pure hydrogen and hydrochloric acid vapour are passed over them to etch away any oxide or impurities which may exist on the surface of the silicon. HCl vapour is then turned off and hydrogen bubbled through the SiCl<sub>4</sub>, the vapour passing over the silicon slices. When this reaches the hot silicon it dissociates and silicon atoms are deposited on the slice, where they rapidly establish themselves as part of the original crystal structure. It is essential to saturate the tube with SiCl<sub>4</sub> vapour, to ensure a uniform layer thickness over the whole slice.

The epitaxy layer may be doped with p- or n-type impurities by introducing these, in the required concentration, into the vapour stream.

#### 1.2.4 Photolithography

The main use of photolithography, in the manufacture of semiconductor components, is to selectively remove areas of oxide or metal from the surface of the silicon slice (Levenson, 1995; Jeong *et al.*, 1994). To do this the surface is first covered with a thin uniform layer of liquid photoresist. This is best obtained by holding the silicon slice in a vacuum chuck and placing a fixed amount of photoresist onto its centre. The slice is then rotated at very high speeds, to distribute the resist, the excess flying off due to centrifugal forces. The amount left on the slice is clearly a function of the oxide properties and the viscosity of the resist. The slice is then heated for a few minutes in an oven to harden the resist.

The mask, containing the pattern of the area which is to be selectively removed, is then placed in contact with the surface. This may consist of a glass or chrome mask, or, more commonly, a projection of the image onto the surface of the silicon. Once in place, the surface is exposed to ultraviolet light. If negative resist material is used the exposed areas become hardened by the light. The slice is now covered with developer, which dissolves the unexposed resist areas. The slice is then placed in a bath of etchant, such as hydrofluoric acid, which dissolves the exposed areas of the surface, but not the silicon. For applications which require most of the covering surface material to be removed it is more convenient to use a positive resist material, such that the areas exposed to ultraviolet light are dissolved in the developer.

The alternative to the use of photolithography is ion beam lithography in which an ion source is used to form the required pattern directly onto a silicon dice. This system is currently economic only when dense circuits, with very fine lines, are required (Finkelstein and Mondelli, 1995).

#### 1.2.5 Diffusion

In epitaxy a large area is doped by a closely controlled amount of impurity. Diffusion, on the other hand, enables selective areas to be doped. These areas represent those which are not covered by an oxide layer, so that the photolithographic stage is normally followed by diffusion.

The diffusion furnace resembles the arrangement shown in Figure 1.2. The bubbler contains the impurity and nitrogen is passed through it, on its

way to the boat containing the silicon slices. The furnace temperature is kept close to the melting point of silicon, i.e. 1200°C, and at this value the silicon atoms are highly mobile. Impurity atoms readily move through the silicon lattice by substitution, going from a region of high concentration to one of lower density.

Diffusion can be carried out by one of two techniques, as shown in Figure 1.2. In the error function or one-step process the concentration of impurities is kept fixed throughout the diffusion period, giving the curves shown. In Gaussian or two-step diffusion a fixed amount of impurity is present, so that as this moves deeper into the silicon bulk the surface concentration decreases. This gives a flatter dopant distribution of higher resistivity. Generally, diffusion takes place in a slightly oxidising atmosphere. This results in the formation of a glassy layer of impurity on the silicon surface, as well as a slight penetration into the silicon bulk.

The silicon slice can be removed to a second furnace and heated in an inert atmosphere, when the dopants diffuse out of the glassy layer to give an error function distribution. The glassy layer now not only forms a diffusion source but also protects the silicon surface from evaporation, and acts as a getter for impurities from the silicon bulk. For Gaussian diffusion the glassy layer is etched off using hydrofluoric acid, prior to the slice being heated in an inert atmosphere. The critical dopants just below the surface now diffuse into the silicon bulk.

Apart from the open-tube arrangement, shown in Figure 1.2(a), it is possible to diffuse slices by putting them in a sealed quartz container with doped silicon powder and then heating the combination in a quartz furnace. The advantage of this method is that many slices can be diffused simultaneously, giving a larger throughput. However, the quartz container must be broken to remove the slices after diffusion, so the process can prove expensive.

The most commonly used p- and n-type impurities are boron and phosphorus respectively. Both reach maximum solubility at about 1200°C and have a high diffusion constant. Arsenic, on the other hand, is an n-type impurity, which diffuses very slowly. It is used for making the buried layer in transistors, since this must not diffuse appreciably during subsequent high-temperature processes.

Gold is often introduced as an impurity into semiconductor devices. This is a lifetime killer and enables fast-switching components to be built. The gold atom is much smaller than a silicon atom. This means that it does not move through the silicon lattice by substitution, as other impurities do, but very rapidly in between the silicon atoms, that is, intrinsically.

#### 1.2.6 Ion implantation

Ion implantation is a technique for precisely determining the concentration and location of impurities within a silicon slice (Singer, 1995b). In this process selected ions of the required impurity are accelerated into the slice of silicon, where they plough their way through the crystal structure to the required depth. Because of this the material is distorted after ion implantation and it usually needs to go through an annealing stage, in which the atoms are allowd to drift into their places within the lattice.

Figure 1.3 Principal parts of an ion-implantation equipment

There are several basic requirements which must be met in any implantation system:

- (i) The impurity concentration must be uniform over a given slice, and the process must be accurately reproducible over repeated slices.

- (ii) The system must have a high throughput.

- (iii) The purity of the dopant must be accurately controlled. Most ion sources produce a range of dopants in addition to the one required. The impurities must be completely removed from the ion stream before it reaches the silicon slice.

- (iv) The energy imparted to the ions by the accelerating voltage must be high, to enable them to penetrate the maximum distance likely to be required.

Figure 1.3 shows a simplified arrangement of an ion-implantation system. The ion source produces an abundance of the required dopant. The source output should remain constant over a long time, to allow reproducible devices to be made without the need for constant adjustment. A focusing system, which is usually electrostatic, is used to focus the ion beam onto the silicon slice. The ion accelerator gives the ions the necessary penetration energy by applying a high voltage across the ions. A mass analyser is used in conjunction with the focusing system to separate out the impurities from the ion beam.

The beam scanner scans the ion beam over the silicon surface, resulting in uniform dopant concentration. In addition, the silicon slices can be moved past the beam for more uniformity. The doping concentration is monitored by measuring the current in the ion detector. This is quite easily done since each ion carries one positive charge unit. The dose imparted to the silicon, measured in ions/cm<sup>2</sup>, is equal to the product of the current and the exposure time, divided by the wafer area. The wafer chamber holds the silicon samples. It must be quickly accessible and large enough to hold a useful batch at each operation.

#### 1.2.7 Metal formation

Metal is deposited onto the surface of the semiconductor slice using one of two main methods. In the first system the semiconductor is held face down in the top half of a bell jar, operating in vacuum. The material to be deposited is located at the bottom of the jar and heated until it vaporises and settles as a thin layer onto the semiconductor surface.

The second deposition technique is called sputtering. A bell jar is again used, but now it is filled with an inert gas, such as argon. The semiconductor, again face down in the top half of the jar, is connected to the positive terminal of a high-voltage source and the material to be deposited is placed at the bottom of the jar and connected to the negative terminal. Under the effect of this voltage the argon is ionised and positive ions bombard the cathode, causing it to sputter and emit material, which settles on the semiconductor surface, i.e. the anode.

An alternative technique for metal deposition, which can also be used to deposit other films such as polysilicon and silicon dioxide, is known as chemical vapour deposition (Singer, 1995a). It is primarily used to produce devices of very small geometry, as in integrated circuits.

#### **1.3 Power rectifier principles**

#### **1.3.1 Physics of rectification**

It is not intended in this brief introduction to delve into atomic physics. Instead some of the basic concepts of semiconductors are introduced.

The structure of an atom is well known. It consists of a central nucleus and revolving electrons in various orbits. The positive charge on the nucleus is balanced by negative electronic charge. The atom is said to be stable if its outer shell is full, the electrons for the first four shells, working outwards from the nucleus, being 2, 8, 18, 8 or 32. The number of electrons in the outermost shell determines its group number. Silicon has 2, 8, 4 electrons, and is in group IV, and although unstable on its own, a crystal of silicon forms stable covalent bonds between atoms. Each shares its four electrons with neighbouring atoms and so has eight orbital electrons. However, if energy is given to the material, say in the form of heat, an electron can break away from its valency bond and cause conduction in the material. This is called intrinsic conduction.

If an impurity of group V (donor) or group III (acceptor) is added to silicon then there will be an abundance or shortage of electrons respectively, causing increased conduction at a given temperature. This is called extrinsic conduction. A shortage of electrons results in a p-type doping, where holes are the majority carriers and electrons the minority ones, whereas extra electrons results in an *n*-type material, in which the carrier function is reversed.

Holes and electrons are constantly being created in a semiconductor. They disappear due to recombination, a process which can be increased by the presence of specially created trapping centres in the crystal. These hold a carrier until an opposite polarity charge arrives for recombination.

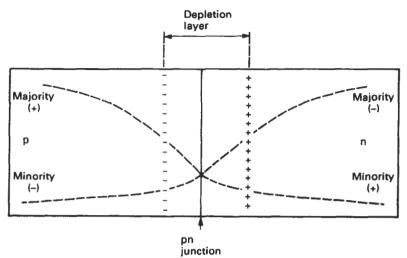

A power rectifier is a two-layer device, similar in principle to a diode, consisting of a p and an n layer formed within the same semiconductor material. Figure 1.4 shows a simplified arrangement of the two layers. The p layer has an abundance of holes (holes are the majority carrier) and the n layer has electrons as the majority carriers. Electrons and holes form the minority carriers in the p and n layers, respectively, as shown in Figure 1.4.

As the junction between the layers is approached, the concentration of p and n decreases to match that in the other layer. Therefore there is a

Figure 1.4 Formation of a depletion layer in a p-n junction

gradient in the material, which results in the diffusion of holes and electrons across the junction. These cause recombination to occur in the opposite layer, so that a negative charge barrier is formed in the p layer, close to the junction, and a positive barrier is formed in the n layer, as shown in Figure 1.4. These result in a potential barrier which hinders further diffusions. Because of this barrier only a few holes and electrons, with high kinetic energy, can cross or remain in the junction region. This region therefore has only a few majority carriers and it is known as the depletion region.

Since the depletion layer has only a few charge carriers it is in effect an insulator. The device therefore resembles a capacitor in having two conducting regions separated by an insulator. The width of the layer, and hence the capacitance, is proportional to the applied reverse voltage across the p-n junction. The capacitive effect influences the switching performance of the rectifier, as will be seen in the next section.

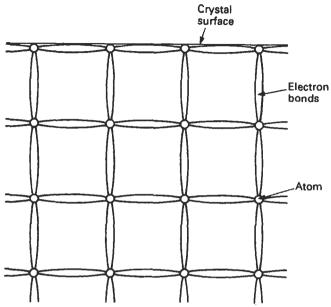

The surface of the semiconductor, even if it is completely pure, forms a break in the overall regularity of the crystal structure. This is shown in Figure 1.5. In the whole lattice each silicon atom is bound to its neighbouring atom by two electron bonds, so that each atom is connected to four other atoms. On the surface layer, however, the atom is bound to three other atoms only, so that two holes are unfilled, resulting in a pure semiconductor having a positive surface charge. In practice these surface atoms attract impurity electrons from the atmosphere, so that the surface of a semiconductor is intrinsically impure, resulting in problems in the surface region. It is therefore important, in any semiconductor, to thoroughly clean its surface and then to protect junctions by stabilisers such as oxides and nitrides

The voltage induced in the depletion region is determined by the intrinsic carrier concentration, which for silicon is  $1.4 \times 10^{10}$  per cubic centimetre. This gives a junction voltage of about 560 mV.

Figure 1.5 A crystal lattice showing the surface effect

#### 1.3.2 Forward and reverse bias

Connecting a battery across the junction in the forward direction, that is, with its positive terminal connected to the p layer, will decrease the depletion region, acting with the potential barrier, and cause a current to flow as given by

$$I_{\rm F} = I_{\rm R} \left[ \exp\left(q V_{\rm j} / k T\right) - 1 \right] \tag{1.1}$$

where  $V_j$  is the voltage across the junction,  $I_R$  is the reverse junction current, q is the electron charge, T the absolute temperature, and k is Boltzmann's constant.

When the voltage across the p-n junction is reversed, the battery potential helps that of the internal depletion barrier, so that only a small minority current can flow. This leakage current is due to three causes:

- (i) Surface contamination, which can be reduced by cleaning the surface; by coating it with protective material such as glasses or silicon resins; or by designing the device such that surface fields are lower than internal fields. This includes bevelling and the use of surface plates, as described in section 1.3.3.

- (ii) Diffusion of minority carriers from the neutral areas into the depletion region. This is low for diodes operating below about 100°C, but is more significant for power devices whose junctions frequently operate above this temperature. If the width of the p and n regions of a reverse-biased diode are  $W_p$  and  $W_n$ , as measured from the edge of the depletion layer;  $\overline{n_p}$  and  $\overline{n_n}$  are equilibrium concentrations of

minority carriers in the p and n regions, respectively; then the reverse current density for diffusion-limited operation is given by equation (1.2), assuming that the p and n regions are short compared to the minority carrier diffusion length. In this equation  $D_p$  and  $D_n$  are the hole and electron diffusion constants, respectively.

$$I_{\rm ld} = \frac{q \, D_{\rm n} \, \overline{n}_{\rm p}}{W_{\rm n}} + \frac{q \, D_{\rm p} \, \overline{n}_{\rm n}}{W_{\rm n}} \tag{1.2}$$

(iii) Charge generation within the depletion layer. This is generally the cause of most of the leakage current, and its value is given by equation (1.3), where  $I_{ig}$  is the space charge generated leakage current in A per square centimetre; q is the charge on an electron;  $n_e$  is the intrinsic electron concentration;  $W_d$  is the width of the depletion layer; and  $\tau_s$  is the space charge generation lifetime.

$$I_{\rm lg} \approx \frac{q n_{\rm e} W_{\rm d}}{2 \tau_{\rm s}} \tag{1.3}$$

The current therefore varies directly as the volume of the depletion layer and inversely as the space charge generation lifetime. High-voltage junctions have wide depletion layers, so it is important to have long lifetimes during processing. The charge generation is proportional to  $n_e$  so it doubles for approximately every 11°C rise in temperature.

#### **1.3.3 Modified structures**

J

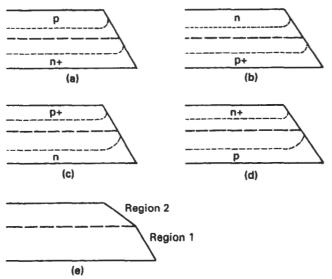

In order to reduce the surface currents, and improve the breakdown characteristics of rectifiers, several techniques can be used. Figure 1.6 shows a method in which the surface, at which the junction between the p and n materials is formed, is bevelled. Both positive and negative bevelling can be used. In positive bevel the part of the crystal which is reduced in volume has a lower concentration of impurities. For negative bevel the converse is true, that is, the part of the crystal which is reduced in volume has the higher concentration of impurities.

Figure 1.6 shows the effect of bevelling on the depletion layer as it approaches the surface. As seen, the layer is wider at the surface than at the centre for positive bevel, giving a lower surface field and therefore leading to less leakage current and a higher breakdown voltage. Since bevelling reduces the metal contact area it is sometimes necessary to use double bevelling, which achieves the same effect on breakdown voltage, but with less shallow bevel angles, and therefore leaves a greater amount of surface contact metal area.

In a p-n structure, as the applied reverse field is increased, a point is reached when mobile carriers attain thermal drift velocities, which for silicon are  $10^7$  cm/s for electrons and  $6.5 \times 10^6$  cm/s for holes. As the field is further increased beyond this point the velocities of the carriers exceed their thermal drift velocities, and they become 'hot' carriers. These collide with atoms and give enough energy to electrons in valence bands to cause them to move to the conduction band, resulting in hole-electron pair generation. Each new pair is involved in ionisation of further hole-elec-

Figure 1.6 Bevelling the semiconductor edge: (a) and (b) positive bevel; (c) and (d) negative bevel; (e) double bevel

tron pairs. When this process attains infinite rate, avalanche breakdown occurs.

If  $\alpha_p$  and  $\alpha_n$  are the ionisation coefficients for holes and electrons, then breakdown occurs when equation (1.4) is satisfied. For the case of  $\alpha_p$ approximately equal to  $\alpha_n$ , and both equal to an average value of  $\alpha_a$ , this equation simplifies to equation (1.5).

$$\int_{0}^{W_{\rm bd}} \alpha_{\rm p} \exp\left[\int_{0}^{y} (\alpha_{\rm n} - \alpha_{\rm p}) \,\mathrm{d}y\right] \mathrm{d}x = 1 \tag{1.4}$$

$$\int_{0}^{W_{\rm bd}} \alpha_{\rm a} \, \mathrm{d}x = 1 \tag{1.5}$$

The breakdown voltage of an  $n^+-p$  junction can also be improved by making the p region almost intrinsic. The  $p^+$  area is used to give a good ohmic contact for connecting leads. This results in an  $n^+-i-p^+$  structure, which has good breakdown characteristics.

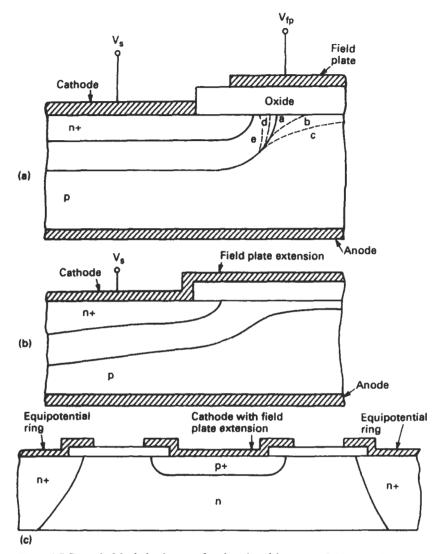

Many power devices are made by forming diffused junctions. These junctions tend to be cylindrical in shape at the edges, which causes a distortion of the space charge lines in this region, resulting in breakdown voltages lower than that for abrupt junctions. The voltage characteristic can be improved by the use of a field plate, as shown in Figure 1.7(a). With no voltage applied to this plate the depletion layer is cylindrical, as in curve a. Applying an increasing positive voltage causes the p region to become successively less p type, that is, more resistive, resulting in the curves b and

Power rectifier principles 17

Figure 1.7 Control of depletion layer surface junction: (a) separate field plates; (b) cathode extension plate; (c) addition of equipotential ring

c. This gives improved breakdown voltage performance. Conversely, a negative voltage on the field plate causes the layer to change to curves d and e, reducing the breakdown voltage.

Figure 1.7(b) shows a practical arrangement of the field plate, which does not need a separate field supply. The strength of the field under the field plate is controlled by the thickness of the oxide, and it distorts the depletion layer as before. It is also usual to surround the field plate with an equipotential ring, as shown in Figure 1.7(c). This prevents the slow drifting breakdown, which field plate structures are prone to exhibit.

#### **1.4 Power rectifier operation**

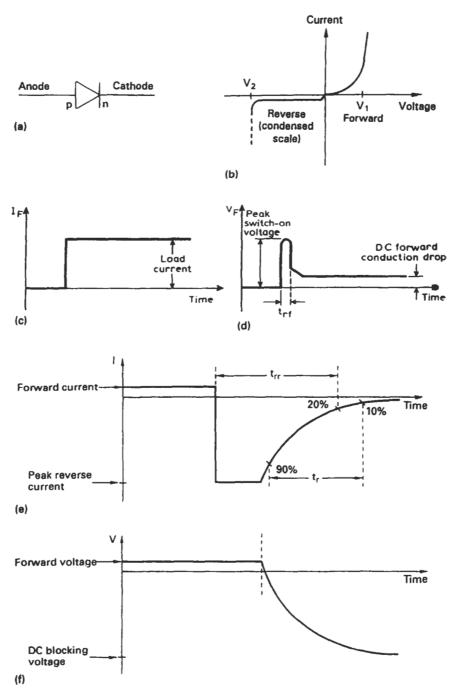

#### 1.4.1 The diode curve

The symbol for a diode is shown in Figure 1.8(a) and its d.c. characteristic in Figure 1.8(b). When the voltage across the diode is increased in the forward direction the current through the device rises rapidly, once the internal potential barrier, caused by the depletion layer, has been overcome. This curve is temperature sensitive and data sheets normally give a typical and a maximum curve, usually at a junction temperature of  $125^{\circ}$ C.

In the reverse direction the diode blocks and a much lower current flows, equal to the leakage current of the diode. This current increases slowly with applied voltage, until at a high enough reverse voltage, called the avalanche voltage of the device, it breaks down due to avalanche conduction, as described in section 1.3.3. The current through the device now increases very rapidly and since the voltage across the diode is still equal to its breakdown value  $(V_2)$ , which can be several thousand times the value of the forward voltage  $(V_1)$ , the diode will dissipate a large amount of power, and could be destroyed.

The reverse characteristic curve of the diode is affected much more by temperature than its forward curve. The leakage current increases with temperature, resulting in a lower breakdown voltage.

#### **1.4.2 Rectifier ratings**

Data sheets normally specify semiconductor devices by two sets of parameters, ratings and characteristics. The ratings define the maximum values at which the component can be operated without being damaged, and the characteristics indicate its performance under specified conditions.

The following are some of the ratings of a diode:

- (i) The maximum reverse voltage. This is usually specified in three ways. The first is the peak working voltage, which defines the normal operating voltage of the device at which it could work indefinitely without any damage. The second is the peak repetitive voltage. This is higher than the peak working voltage, but the diode is capable of withstanding this voltage for a limited period only, this period being specified in the data sheets. The third reverse voltage rating is the peak non-repetitive voltage. This is the voltage which is permitted to occur only infrequently during the life of the device, since it causes the highest power dissipation, and therefore strain, to the silicon die.

- (ii) The maximum current rating. This is also specified in three ways, which correspond to the three voltage parameters. For all these three ratings the assumption is made that the junction temperature of the device does not exceed its rated value. The first is the peak working current, which is the maximum current that the rectifier can carry, provided its junction temperature rating is not exceeded. The second is the peak repetitive current, which is the current the rectifier can carry for short periods. The third is the peak non-repetitive current, which the rectifier can carry for a short time and only infrequently

Figure 1.8 Diode characteristics: (a) diode symbol; (b) static characteristic; (c) turn-on characteristic – current curve; (d) turn-on characteristic – voltage curve; (e) turn-off characteristic – current curve; (f) turn-off characteristic – voltage curve

during its lifetime. This third current is usually used to blow protection fuses associated with the rectifier. The working current of a rectifier may be specified as a direct current or as an average value.

- (iii) The peak power dissipation which the device can withstand. Power dissipation is linked to the device junction temperature and its cooling characteristics.

- (iv) The maximum junction temperature at which the rectifier can be operated. Also specified is the maximum storage temperature of the device, and this is given as the highest and lowest temperatures, since the semiconductor can also be damaged by prolonged exposure to sub-zero temperatures.

#### **1.4.3 Rectifier characteristics**

The characteristics of a semiconductor component can often be divided into static and dynamic. The following are some of the static characteristics:

- (i) Forward voltage drop. This varies with forward current, as shown in Figure 1.8(b), so it is normally specified at a given current or by a graph. The average forward voltage drop is usually specified as an average over a full cycle, at a stated frequency, average forward current and case temperature.

- (ii) Reverse leakage current. This is specified at a defined reverse voltage and temperature, or as an average value over one cycle at a given temperature.

- (iii) The forward power dissipation. This is the product of the forward voltage drop and current and is given as a curve.

- (iv) The reverse power dissipation. This is equal to the reverse leakage current times the reverse voltage, at a defined point in the device curve.

- (v) The junction to case thermal resistance. This characteristic, specified in units of degrees Centigrade per watt, indicates the difference in temperature between junction and case, when the rectifier is dissipating power. It is required for designing rectifier cooling systems, as described in Chapter 2.

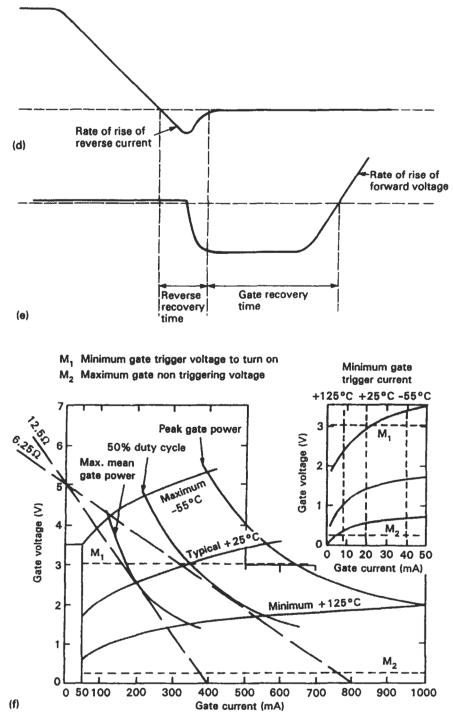

The dynamic characteristics of a rectifier relate to its switching periods, both on and off. When a rectifier is switched into conduction a finite time is required for the minority carriers to flow across the junction and to prime it to carry the full load current. This can result in an initial peak voltage across the device, as seen in Figure 1.8(d). The load current rises rapidly, being limited by the circuit inductances, but the rectifier is in its fully-on mode after a delay time of  $t_{rf}$ . This time is very short, but it does represent a period of large power dissipation, which for very high-frequency operation can start to become important. Data sheets normally specify this forward delay time

When a diode is switched from the forward-conducting to the reverse-biased mode two changes occur. First, the minority charge is swept away as reverse current, in the external supply. This current can be large, often being limited only by the external circuit impedances. It could be

<sup>20</sup> Power semiconductor devices

described as the surge current through the device junction capacitance, although this is not strictly true. In addition to this external current flow, holes and electrons disappear in the vicinity of the reverse-biased region, due to recombination. The current decays to zero, as the reverse voltage-blocking capability of the diode increases, as shown in Figures 1.8(e) and 1.8(f).

The reverse recovery time of the rectifier is several orders of magnitude greater than its forward turn-on time, so the power dissipation during switch-off is much greater. Clearly the reverse recovery time  $t_{rr}$  must be kept as short as possible, in order to limit the device dissipation. However, the decay of current, over time  $t_r$ , must not be too abrupt as this will give rise to large voltage spikes in any associated inductive circuits. The ratio of  $t_r/t_{rr}$  should be as large as possible and devices which have a relatively high value of this ratio are said to be 'soft'.

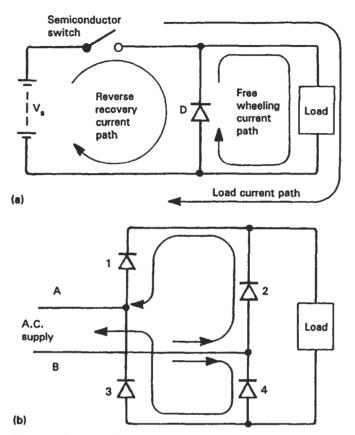

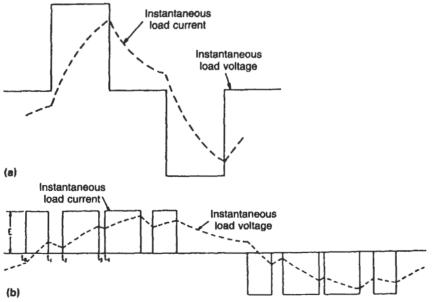

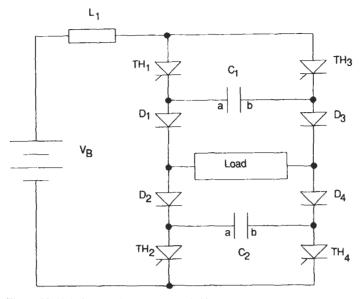

In circuit applications the reverse recovery current, which for power devices can be high due to the larger silicon area involved, is often overlooked, with disastrous effects. For instance, consider the chopper circuit shown is Figure 1.9(a). The semiconductor switch is opened and closed at a relatively high frequency and varying duty cycle, in order to control the magnitude of the mean load voltage and current. Suppose the load is inductive. This requires a diode D, often called a free-wheeling diode, to be connected across it, to prevent excessive surges in the switch when it opens.

Ignoring the reverse recovery current in the diode, the system would operate as follows. With the switch closed D is non-conducting and load current is supplied via the d.c. source  $V_s$ . When the switch opens the load current free-wheels in D and, provided the loss in this path is not large, the current will be substantially unchanged when the switch is again closed. If the reverse recovery current through D is not ignored then, with the load current free-wheeling through it, the operation is basically as before. However, when the semiconductor switch closes this current transfers to the supply. In addition there is now a reverse recovery path as shown, and since this is of a very low impedance, a surge of current can pass, which could destroy the switch.

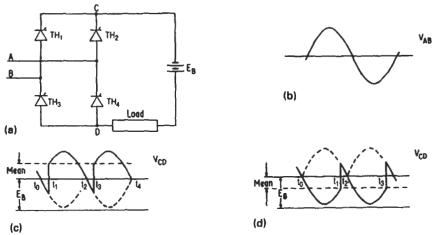

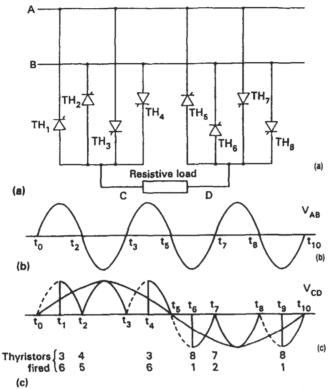

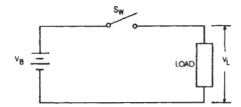

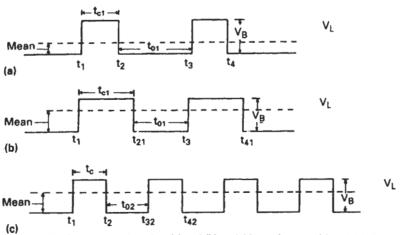

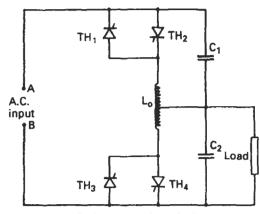

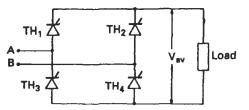

Chopper circuits are not exclusively prone to reverse current effects. Figure 1.9(b) shows a commonly used bridge rectifier circuit. Suppose line A is positive to B so that load current is supplied via rectifiers 1 and 4. When the voltage reverses and line B becomes positive, the current in rectifiers 1 and 4 will decay to zero, whilst that in 3 and 2 will increase to support the load. As soon as 1 and 4 turn off a reverse current path exists through them, as illustrated. This provides a short circuit across the supply lines, which could destroy rectifiers 2 and 3. In all such applications great care must be taken to ensure that there is sufficient line impedance, which would limit this short-circuit current until the reverse-biased device recovers its full blocking capability.

Several design techniques exist to enhance power rectifier characteristics. A  $p^+-p-n-n^+$  (or  $n^+-n-p-p^+$ ) structure can be used in which the base consists of high-resistivity n- (or p-) type material, chosen to withstand the required reverse voltage. One face has a p (or n) diffusion made into it and the opposite face has an  $n^+$  (or  $p^+$ ) diffusion layer. Due to

Figure 1.9 Examples of circuit reverse recovery current: (a) chopper circuit; (b) bridge rectifier circuit

Figure 1.10 An epitaxial diode construction

the high resistivity of the base material a good reverse characteristic is obtained, and the  $n^+$  and  $p^+$  layers cause a large rate of carrier injection into the high resistivity region, giving good forward characteristics.

Fast commutating rectifiers are often obtained using a double-diffused construction. In this the starting material is high-resistivity n type, which is chosen to withstand the required reverse voltage. Into this material  $n^+$  and  $p^+$  diffusions are made, on opposite sides, for the cathode and anode connections.

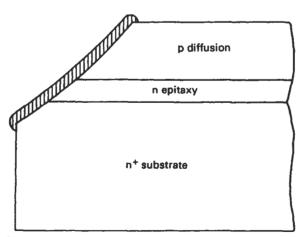

Even faster rectifiers are obtained using an epitaxial construction, as shown in Figure 1.10. The base material is now  $n^+$ . Into this is grown an *n* epitaxy layer of high resistivity, which is designed to provide the required reverse voltage blocking capability. A  $p^+$  diffusion or ion implantation is then made, to form the anode layer. This technique is capable of providing devices in which the reverse recovery time  $t_{rr}$  is less than 100 ns for a component having a rating of over 1000 V.

#### **1.5 Bipolar transistors**

#### 1.5.1 Principle of operation

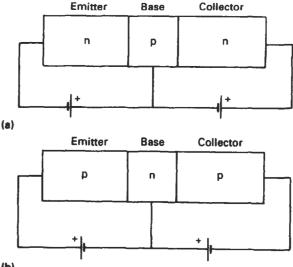

The bipolar transistor is a three-layer device, which can be made up of p-n-p or n-p-n layers, as shown in Figures 1.11(a) and 1.11(b). The base region is narrow and lightly doped, unlike the emitter and collector layers, which are heavily doped and comparatively wide. With the biasing arrangements shown the emitter-base region is forward biased so that majority carriers flow across this junction. These carriers are electrons in the case of the n-p-n transistor and holes for p-n-p.

(b)

**Figure 1.11** Bipolar transistor characteristic: (a) biasing arrangement, n-p-n transistor; (b) biasing arrangement, p-n-p transistor;

Since the base is lightly doped only a few holes (for n-p-n) or electrons (for p-n-p) are available to cross into the emitter. The collector-base region is reverse biased resulting in a small minority carrier flow, which is holes from collector to base and electrons from base to collector, for an n-p-n transistor, and vice versa for a p-n-p transistor.

The collector bias is much greater than that of the base, and since the base region is narrow, the majority carriers which cross the emitter-base region are diffused across the base and into the edge of the collector depletion layer. These carriers then reach the collector, resulting in collector current flow. A small amount of the majority carriers, crossing from the emitter to the base, combine within the base and this, along with the small number of minority carriers crossing from the base to the emitter, results in a low value of base current.

Transistors can be operated in common base, common emitter or common collector modes. Common emitter is the most popular configuration, common collector being used in emitter follower applications. For common emitter the base current  $I_B$  is the input and the collector current  $I_C$  is the output. The ratio between these two  $(I_C/I_B)$  is called the common emitter forward current transfer ratio  $h_{FE}$ . In the transistor a low base-emitter voltage and small base current change results in a large collector current across the high reverse-biased collector-base region. There is therefore power gain within the transistor.

Leakage current is caused within the reverse-biased collector-base junction due to minority carriers. For common emitter this current is multiplied by the gain of the device and flows in the emitter, when the base is open circuit. This leakage current is further increased with temperature.

#### **1.5.2 Characteristics**

The main ratings of a power transistor are related to current and voltage. Since the transistor has three terminals, base, collector and emitter, the ratings are associated with each terminal. The maximum collector current is described as the maximum continuous current and the peak current. Since the peak current is only of the order of twice as large as the maximum continuous value, the transistor does not have a high surge rating. The maximum current is usually limited by the gain of the device and by the bonding wires.

There are also several voltage ratings for a transistor, depending on which junction is being considered and the state of the third terminal. For example  $V_{\rm CBO}$  is the breakdown voltage between the collector and base junctions with the emitter open circuit;  $V_{\rm CES}$  is the breakdown voltage between the collector and emitter with the base short-circuited to the emitter;  $V_{\rm CEO}$  is the collector emitter breakdown voltage with the base open circuit.

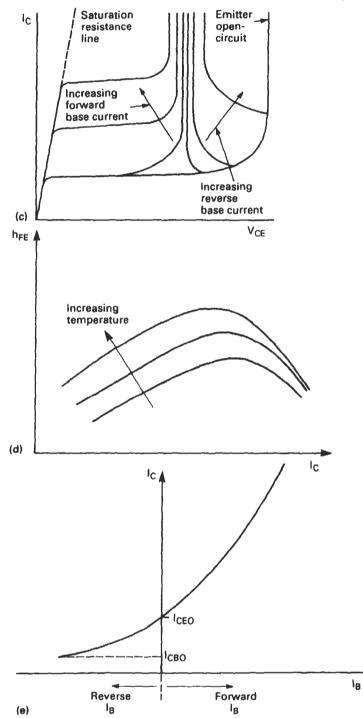

The output characteristic of a bipolar transistor is shown in Figure 1.11(c). For very low values of collector-emitter voltage the collector does not gather up electrons which pass through the base region. This process becomes more efficient as  $V_{CE}$  increases, giving a rapid rise in collector current. After the knee of the curve has passed, most of the carriers

Figure 1.11 continued (c) static characteristic; (d) gain-collector current characteristic; (e) transfer characteristic

generated at the base-emitter junction are gathered up by the collector, so that increasing  $V_{CE}$  does not appreciably affect  $I_C$ . This is known as the saturation region of the characteristic. The larger the value of base current, the higher the collector current at which saturation occurs. Therefore a bipolar transistor is essentially a current-operated device. At very large values of  $V_{CE}$  the carriers attain sufficient energy to cause avalanche breakdown.

There are two gains which are important in bipolar transistors, the large signal or d.c. gain  $(h_{\rm FE})$  and the small signal or a.c. gain  $(h_{\rm fe})$ , given by equations (1.6) and (1.7).

$$h_{\rm FE} = \frac{l_{\rm c}}{I_{\rm B}} \tag{1.6}$$

$$h_{\rm fe} = \frac{\Delta I_{\rm c}}{\Delta I_{\rm B}} \bigg|_{I_{\rm c}}$$

(1.7)

For switching applications the d.c. gain is the most important, and is given by the ratio of the d.c. values of the collector and base currents. It falls off slowly at low values of collector current, as shown in Figure 1.11(d), and also increases slightly with  $V_{\rm CE}$ , which accounts for the slope in the output characteristic of the transistor. The d.c. current gain falls off rapidly at high values of collector current, as the saturation resistance line is approached. The gain also increases with temperature.

For linear applications, and for low-frequency and audio amplifiers, the a.c. gain is of more relevance. It is the ratio of the change in collector current for a small change in the base current, and its value is determined by the magnitude of the steady state collector current.

The bipolar transistor is said to be in saturation when increasing base current gives no further increase in collector current. The voltage drop across the external terminals of the device is now known as the saturation voltage. Data sheets usually give the collector to emitter saturation voltage  $(V_{CE(SAT)})$  and the base to emitter voltage  $(V_{BE(SAT)})$ , and specify the conditions, such as collector current, base current and temperature, under which they were measured. At saturation both collector-emitter and base-emitter junctions are forward biased and the junction voltages oppose. The net junction voltage appearing across the collector-emitter forms one part of the saturation voltage, the drop in the saturation resistance  $(R_{CE})$  forming the other. Data sheets sometimes specify the value of  $R_{CE}$  instead of  $V_{CE(SAT)}$ .

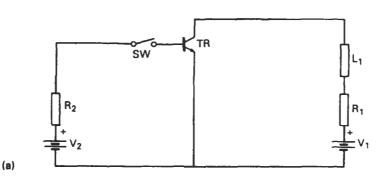

Transistor sustaining voltage is defined as the minimum collector-emitter breakdown voltage. It can be specified with the base open circuit, short circuit, or biased in the forward or reverse directions. For example,  $V_{CEO(SUS)}$  is the minimum collector-emitter voltage with the base open circuit. As the voltage across the transistor increases it reaches the sustaining value, at which point the voltage across the device remains relatively constant, over a wide current range. Figures 1.12(a) and 1.12(b) show the measurement of  $V_{CEO(SUS)}$ . Switch S<sub>w</sub> is initially closed, and then opened once the current has reached a steady state value. The current starts to decay and the inductor L<sub>1</sub> causes the voltage to rise. At a voltage

(1.10)

level, given by the collector-emitter sustaining voltage, the junction breaks down, and the voltage across the transistor remains relatively constant, until the energy in the inductor has been dissipated.

Figure 1.11(e) shows the transfer characteristic of a bipolar transistor. With no base current the collector current equals the leakage value, given by  $I_{CEO}$ . This leakage current decreases as the transistor is driven by negative base current until it reaches a minimum value given by  $I_{CBO}$ , known as the collector-base leakage current with no emitter current. It is related to the collector-emitter leakage by equation (1.8).

$$I_{\rm CEO} = I_{\rm CBO} \left( 1 + h_{\rm FE} \right) \tag{1.8}$$

Power transistors are often used in switching applications, and Figure 1.12(c) shows a test circuit to measure switching parameters, with the waveforms being given in Figures 1.12(d), 1.12(e) and 1.12(f). For a sharp rise in the base current there is a delay in the start of the collector current, due to the time taken to charge emitter and collector depletion capacitances to new values. Once conduction has commenced, the rise time  $(t_r)$  is determined by the junction capacitances and the transit time of the charge carriers in the base region. Removing the base current initially does not cause any decay in collector current. The storage time, shown in Figure 1.12(f), is the time needed for the excess charge in the collector and base regions to recombine, to the extent needed for the transistor to come out of saturation. The rate of charge decay is determined by the minority carrier lifetime in the collector and base regions, the reverse base current  $(I_{BR})$  and the amount of turn-on base drive  $(I_B)$ . Once the current has started to decrease, the rate of decay, which determines the fall time  $(t_f)$ , is determined by the collector junction capacitance and decreases as negative base current is increased. The overall turn-on  $(t_{ON})$  and turn-off  $(t_{OFF})$ times of the transistor are given by equations (1.9) and (1.10). The losses in a transistor during switching can be considerable since during the transition stages the voltage and current of the device are high.

$$t_{\rm ON} = t_{\rm d} + t_{\rm r} \tag{1.9}$$

$t_{\text{OFF}} = t_s + t_f$

Figure 1.12 Bipolar transistor test circuits and waveforms: (a) test circuit to measure  $V_{CEO(SUS)}$ ;

Figure 1.12 continued (b) waveforms for circuit (a); (c) test circuit to measure switching parameters; (d) base voltage waveform for circuit (c); (e) base current waveform for circuit (c); (f) collector current waveform for circuit (c)

Usually the working range of a transistor is limited by the maximum voltage and current. However, when working into inductive loads the device can be destroyed, even when below the maximum limits, giving second breakdown. This is due to hot spots caused by current concentration, resulting in local thermal runaway. Current concentrations occur due to causes such as unstable lateral temperature distribution, base region potential drops, uneven base widths, and uneven mounting of the silicon chip onto the heat sink.

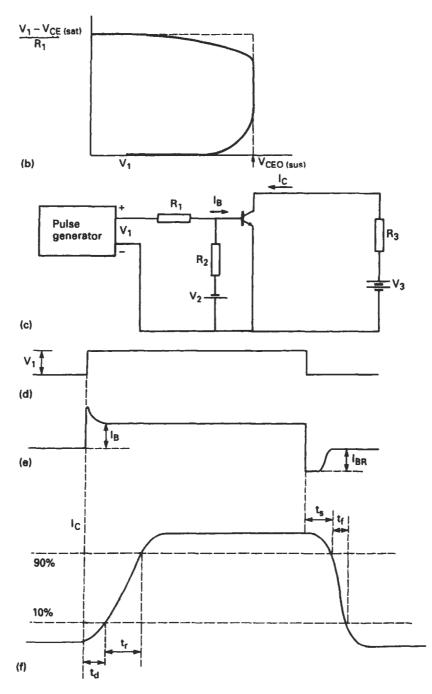

Figure 1.13(a) shows the second breakdown characteristic of a bipolar power transistor. For a given base current the collector current  $(I_C)$  will increase as the collector-emitter voltage  $(V_{CE})$  increases. After a point A on the characteristic the device will go into saturation and the current will remain substantially constant until point B, when avalanche breakdown, or first breakdown, occurs. This causes a rapid rise in current until point C

Figure 1.13 Power bipolar transistor characteristic: (a) second breakdown characteristic; (b) safe operating area

when a second breakdown effect develops. This results in rapid local heating of the silicon die, the collector-emitter voltage collapses, and the current escalates, destroying the transistor. There is a series of curves for different base currents and these give rise to individual second breakdown points, which all lie on a locus, as shown. As the duty cycle of the transistor decreases it runs cooler so that it can work on a wider second breakdown locus.

Power transistors must be operated in a mode such that second breakdown is avoided. This is done using the safe operating area (SOA) curves, of the type shown in Figure 1.13(b). Although these curves are for a device rated at a peak current of  $I_M$  and a voltage of  $V_M$ , the transistor cannot be run at this current and voltage simultaneously. For low values of  $V_{CE}$  the current can increase to  $I_M$ , where it is limited by the current-carrying capability of the bonding wire and the metallisation tracks used on the silicon. As  $V_{CE}$  increases so also does the power dissipation, so that eventually  $I_C$  will need to be decreased. For large values of  $V_{CE}$  the value of  $I_C$  is reduced still further in order to prevent the occurrence of second breakdown effects. The SOA of the transistor increases as the duty cycle reduces, since both the dissipation and second breakdown effects are now lower.

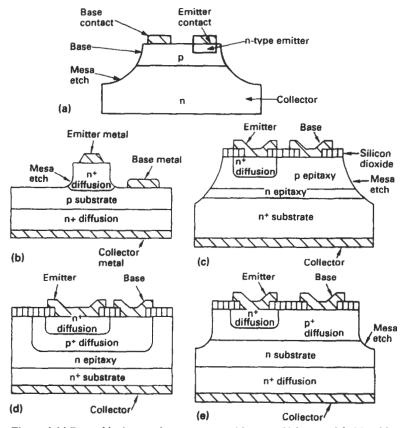

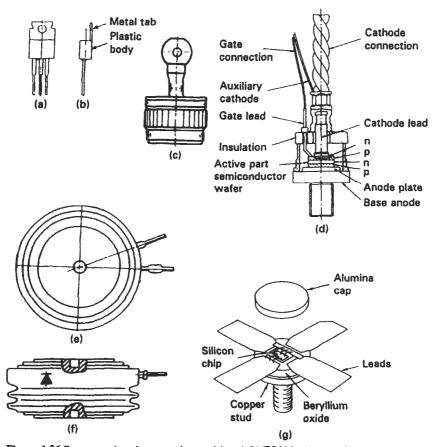

# **1.5.3 Construction**

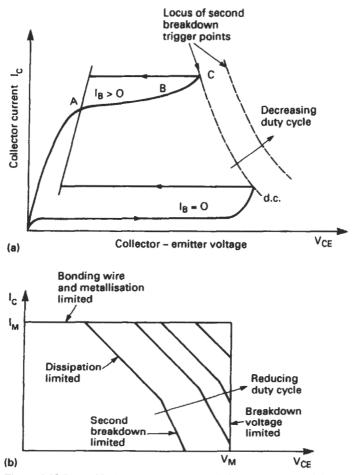

Several different construction techniques are used for power transistors, each giving some advantage, such as high voltage ratings or speed of operation. Figure 1.14 shows a few of these.

In the mesa structure the junction area is reduced by a mesa etch, so that junction capacitances are decreased. This technique also allows the edges of the transistor, mainly the collector-base junction, to be defined and passivated, which prevents contamination, so avoiding high electric fields.

The hometaxial structure is easy to produce so that it is cheap and rugged. It has good overall voltage ratings but suffers from relatively long switching times.

The epi-base transistor generally has a relatively low voltage rating, but this can be increased by adding high-resistivity collector epitaxy. This causes the collector voltage to be shared by the base and collector epitaxy layers, but the voltage rating is still less than for hometaxial. The process uses shallow emitter diffusions and a narrow-base epitaxy, so it has higher speed and current-handling capability than a hometaxial transistor for the same emitter area.

The planar epitaxial arrangement has all its junctions protected during fabrication by an oxide layer, so it is capable of being designed for very low leakage current. The diffusion process also enables very narrow base widths to be built, thus giving higher speeds and lower saturation voltage drops than hometaxial or epi-base transistors. The disadvantage of the planar epitaxial device is that it is not very resistant to the effects of second breakdown.

The triple-diffused transistor is better than planar on second breakdown, but it is still not very resistant to this. Speed and saturation voltage drops are similar to planar epitaxial, but the construction is more expensive and

Figure 1.14 Power bipolar transistor structures: (a) mesa; (b) hometaxial; (c) epi-base; (d) planar epitaxial; (e) triple diffused

has a higher leakage current. The process is also difficult to control, so that a wide distribution in parameters is obtained between batches.

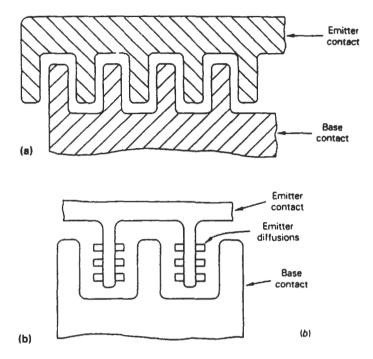

In bipolar transistors operating at high frequencies the current is forced out towards the edges, so the ratio of emitter periphery to area is large. Two techniques are used to overcome this, as illustrated in Figure 1.15. In the interdigitated structure the base and emitter are interleaved and formed on the silicon die. Diffusions for both these are under the metal contact area shown. In the overlay device the emitter metal contact is formed over the base rather than adjacent to it. Emitter diffusions are segmented and spread out from the emitter metal contact, whereas the base diffusion lies below and along the length of the base metal contact.

# **1.6 Unipolar transistors**

## 1.6.1 Principles of operation

Unipolar transistors, unlike bipolar, have a conduction mode which is dependent on only one type of carrier, which may be holes or electrons.

Figure 1.15 High-frequency transistor geometries: (a) interdigitated; (b) overlay

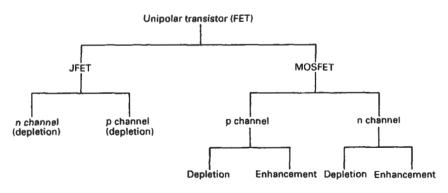

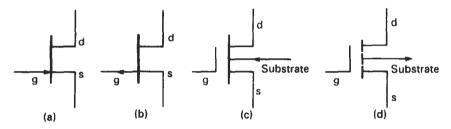

Unipolar transistors are also known as field effect transistors (FET) and they are capable of several different operation modes, as illustrated in Figure 1.16. The junction field effect transistor (JFET) can have a p or an nchannel, but it can only operate in depletion mode, as explained later. The metal oxide semiconductor field effect transistor (MOSFET) can also be por n channel, and both these may be designed to operate in enhancement or depletion mode.

Figure 1.16 Unipolar transistor variations

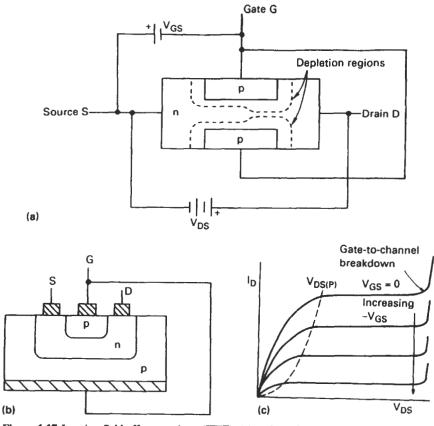

The operation of a JFET can be illustrated by use of the schematic of Figure 1.17(a), a practical arrangement of the device being shown in Figure 1.17(b). The source and drain are formed in the same *n*-type material, hence this is called an *n*-channel device and electrons are the carriers. The gate is made as a *p* diffusion in the *n* material. With this arrangement p-n junctions are formed which, with the biasing arrangement shown, result in depletion regions, which extend deep into the *n* material since it is lightly doped. The gate-source and the gate-drain junctions are reverse biased and current flows between source and drain in the absence of any gate-source voltage. The device is therefore known as depletion mode.

Figure 1.17(c) shows the drain voltage and current curves for a depletion-mode device and it is seen that, with the gate-source voltage held constant, the drain current increases as the drain-source voltage increases. However increasing the drain-source voltage causes the depletion region to extend further, until the two regions in Figure 1.17(a) meet, resulting in the pinch-off state. The pinch-off voltage is shown on Figure 1.17(c) as  $V_{\text{DS}(\text{P})}$ . Increasing the drain-source voltage beyond the pinch-off value

Figure 1.17 Junction field effect transistor (JFET): (a) *n*-channel representation; (b) *n*-channel practical representation; (c) static characteristic

does not cause any significant increase in drain current, but the point along the channel at which the depletion regions meet moves nearer to the source. The drain current is maintained by the electrons being swept through the depletion layer, similar to the process in the base of a bipolar transistor. Eventually the breakdown region is reached at high values of voltage. Making the gate-source voltage negative lowers the value of drain-source voltage at which pinch-off occurs.

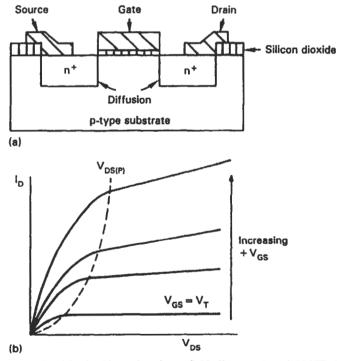

Figure 1.18(a) shows the construction of a MOSFET. The source and drain diffusions are separated by the gate region so no current flows in the absence of a gate voltage. This device is therefore called enhancement mode. For a depletion mode MOSFET a narrow *n* channel would be formed under the gate such that current flowed when there was no gate voltage. Figure 1.18(b) shows the characteristic for an enhancement-mode transistor. As the gate-source voltage is increased a point is reached, called the threshold voltage  $(V_T)$ , when an inversion layer (the doped semiconductor reverses its polarity) is formed under the gate connecting the source to the drain and resulting in current flow. The value of this threshold voltage is determined by the impurity concentration in the semiconductor, the amount of charge in the gate oxide, the type of metal used for the gate, and temperature. As temperature increases, the threshold voltage decreases.

Figure 1.18 Metal oxide semiconductor field effect transistor (MOSFET): (a) construction of an *n*-channel device; (b) static characteristic of an *n*-channel enhancement-mode device

Increasing drain-source voltage causes a rise in the drain current. However, the resulting increase in the voltage drop causes a reduction in the channel conductivity. This reduction has the same effect as a constriction in the inversion layer, resulting in a knee in the curves of Figure 1.18(b). When the drain-source and gate-source voltages are equal the voltage between the gate and drain ends of the channel is zero and this is the pinch-off condition ( $V_{DS(P)}$ ). Further increase in the drain-source voltage causes the drain depletion layer to increase and the end of the channel to move towards the source. The drain current is kept substantially constant by the electrons being swept through the depletion layer.

Figure 1.19 shows some of the symbols possible for unipolar transistors. The arrows point from the p to the n regions. The depletion-mode device shows a solid line between source and drain, since current flows in the absence of any gate voltage, and the MOSFET symbol indicates the oxide layer between gate and source-drain.

Figure 1.19 Unipolar transistor symbols: (a) JFET n channel; (b) JFET p channel; (c) MOSFET n channel depletion mode; (d) MOSFET p channel enhancement mode

## 1.6.2 Characteristics and construction

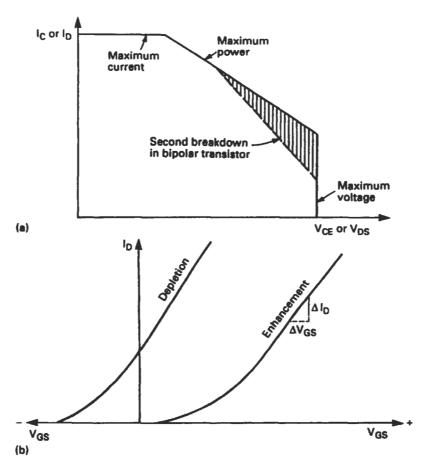

Unipolar transistors are majority carrier bulk semiconductors and are free from minority carrier storage times, so they are inherently faster than bipolar devices. They are also voltage controlled so that their gain is much higher. As the temperature in a unipolar transistor increases, the majority carriers decrease, since the bulk resistivity increases, so there is no thermal runaway effect. Several devices can therefore be connected in parallel to increase the current rating, without any sharing components. The biggest advantage in using unipolar transistors in place of bipolar for power applications is that they do not suffer from second breakdown effects. Therefore the safe operating area curve can be extended, as shown by the shaded area of Figure 1.20(a).

The transfer characteristics of both enhancement- and depletion-mode transistors are shown in Figure 1.20(b). The slope of this curve, given by equation (1.11), is known as the transconductance or mutual conductance, and determines the amplification factor.

$$g_{\rm m} = \frac{\Delta I_{\rm D}}{\Delta V_{\rm GS}} \bigg|_{V_{\rm DS}} \tag{1.11}$$

Figure 1.20 Unipolar transistor characteristics: (a) safe operating area and comparison with a bipolar transistor; (b) transfer characteristic

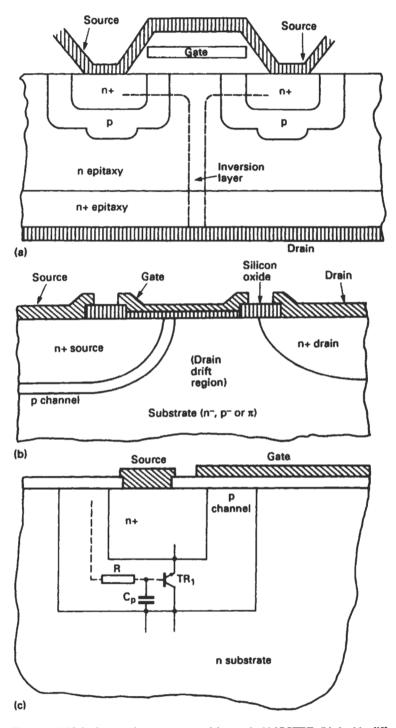

MOSFETs are used in preference to JFETs for power applications. The breakdown voltage of this structure, shown in Figure 1.18(a), is largely determined by the thickness of the oxide between the gate and drain, which can be quite thin. Vertical structures, as shown in Figure 1.21(a), are used for power devices. The gate voltage creates a horizontal channel between the two source regions, which results in an inversion layer down to the drain. The figure shows a polysilicon gate arrangement. Once inversion occurs, the device behaves as a non-linear resistor and not as an n-p-n transistor. This arrangement gives high breakdown voltages, but the capacitance between drain and gate is relatively large, so it is not very good for high-frequency use. The figure of merit of a transistor is given by equation (1.12), where  $C_{in}$  is the input capacitance.

Figure of merit =

$$\frac{g_{\rm m}}{2\pi C_{\rm in}}$$

(1.12)

The on-resistance  $(r_{DS(ON)})$  of the device is given by equation (1.13), where  $R_{ch}$  is the resistance of the channel beneath the gate;  $R_{ex}$  is the resistance of the substrate, solder connections, leads and package; and  $R_{bk}$ is the resistance between the two *p* layers and the drain, through the body of the vertical transistor.

$$r_{\rm DS(ON)} = R_{\rm bk} + R_{\rm ch} + R_{\rm ex} \tag{1.13}$$

The channel and external resistances are constant but the bulk resistance increases with the breakdown voltage of the device. Therefore the on-resistance will also increase as the breakdown voltage capability of the transistor increases. To avoid this, large chips are constructed using many identical parallel cells, which give a low on-resistance and a high breakdown voltage.

The shorter the gate channel in a unipolar device, the higher the transconductance and the lower the parasitic capacitance. The maximum frequency of operation  $(f_{max})$  is given by equation (1.14), where  $W_c$  is the length of the channel in micrometres and  $V_c$  is the carrier velocity in cm/s.

$$f_{\max} = \frac{V_c}{2\pi W_c} \tag{1.14}$$

Figure 1.21(b) shows a short-channel arrangement which is formed by p and n diffusions, hence it is often called a double-diffused (DMOS) transistor. As the drain-source voltage is increased the depletion layer spreads into the drain drift region since it is lightly doped. Since the drain drift region is increased the breakdown voltage is higher, but the drain-source resistance also increases. This can be reduced by using several parallel cells on the semiconductor die.

Figure 1.21(c) shows part of the short-channel transistor of Figure 1.21(b), with an illustration of the parasitic components. The action of the parasitic transistor is usually avoided by a metal contact which bridges the source and the body, i.e. the base and the emitter of the parasitic transistor. Therefore theoretically this transistor should be off, but since the ohmic p layer puts a resistance into the base of this transistor it is possible to turn it on, for example via the parasitic capacitance ( $C_p$ ) which can destroy the device. The parasitic capacitance is formed by the p base and the n drift region. The parasitic diode is useful when switching inductive loads.

The V-groove MOSFET or VMOS device, is shown in Figure 1.21(e). Its operation is identical to the DMOS structure except that it is a vertical structure, and there are now two parallel paths down to the drain. The metal gate shown in the figure is also usually replaced by a silicon gate.

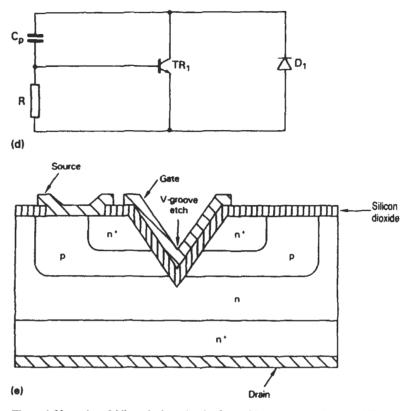

# 1.7 The IGBT

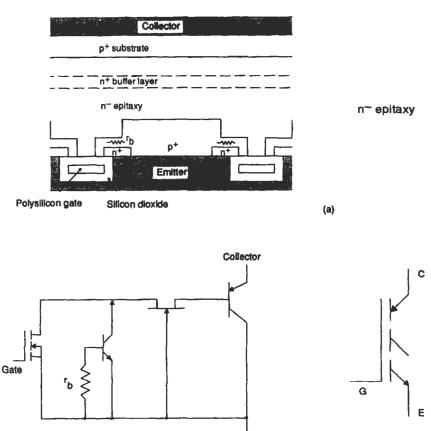

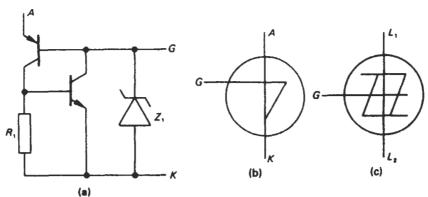

The insulated gate bipolar transistor (IGBT) is a hybrid device which aims to combine the benefits of power MOSFETs, such as low input current drive and wide safe operating area, with the advantages of bipolar transistors, such as low saturation voltage (IR, 1992; Goodenough, 1994; Bush, 1996). Figure 1.22 shows the basic construction of this device, with its equivalent circuit and symbol.

Figure 1.21 Unipolar transistor structures: (a) a vertical MOSFET; (b) double-diffused MOS (DMOS); (c) part of semiconductor structure showing parasitic components;

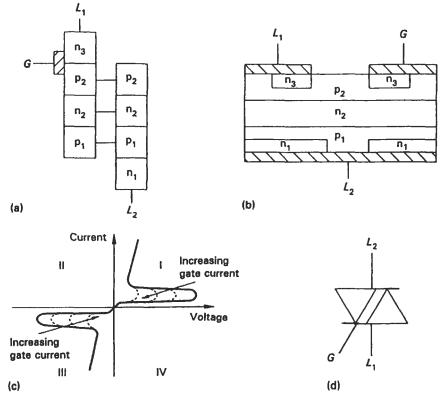

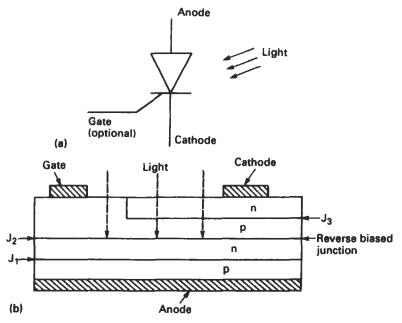

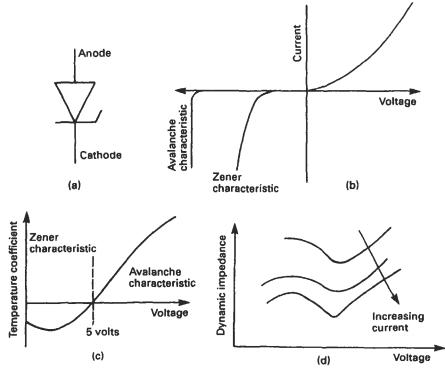

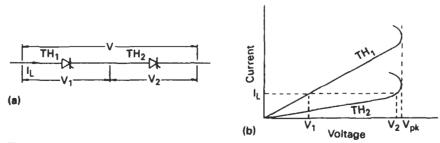

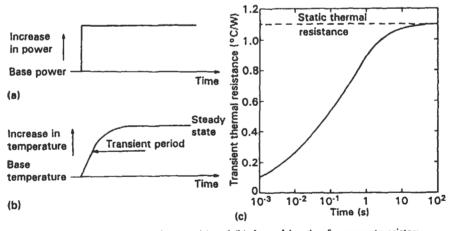

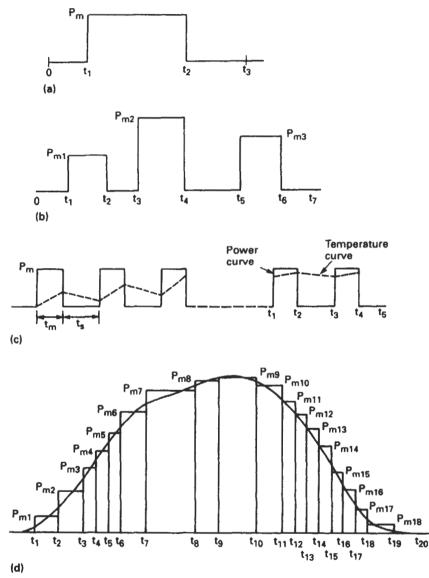

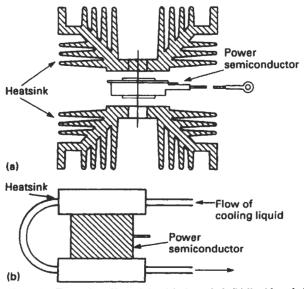

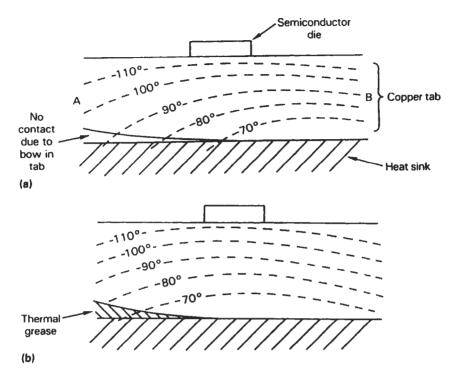

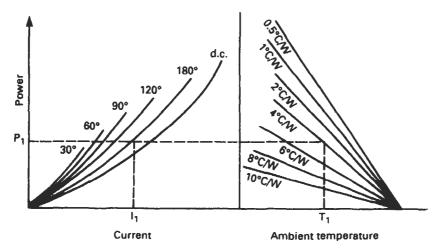

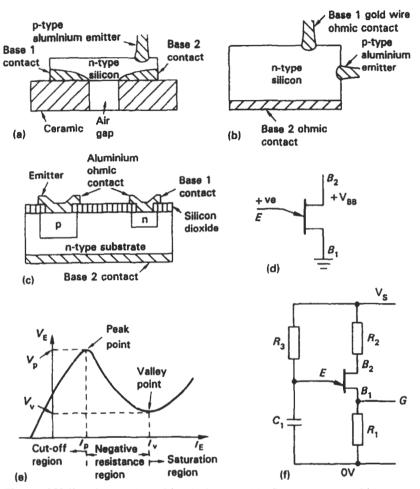

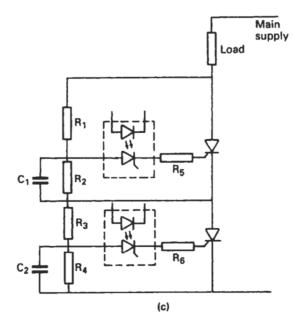

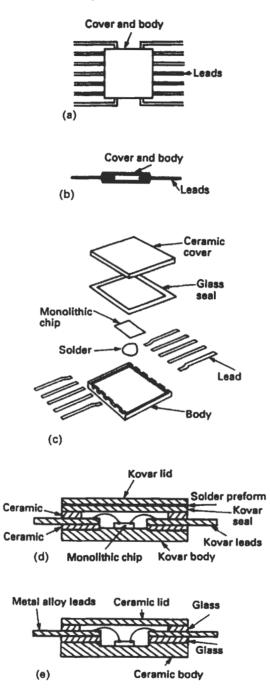

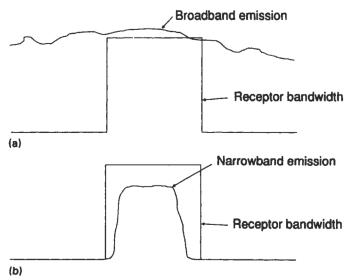

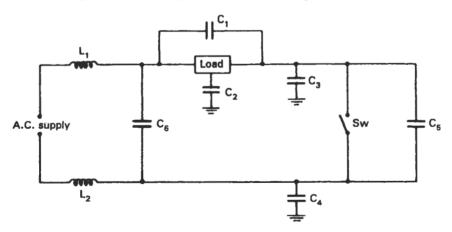

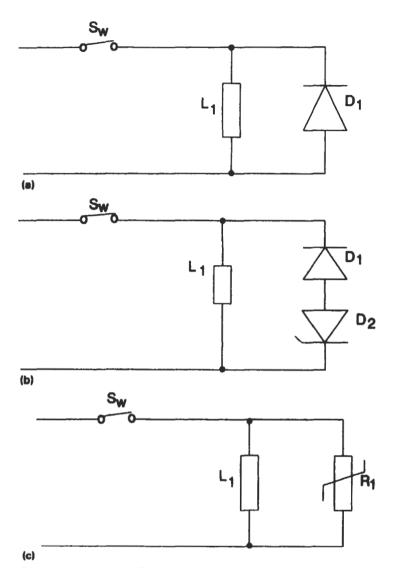

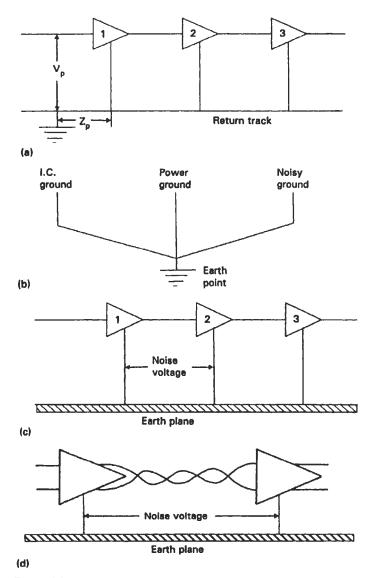

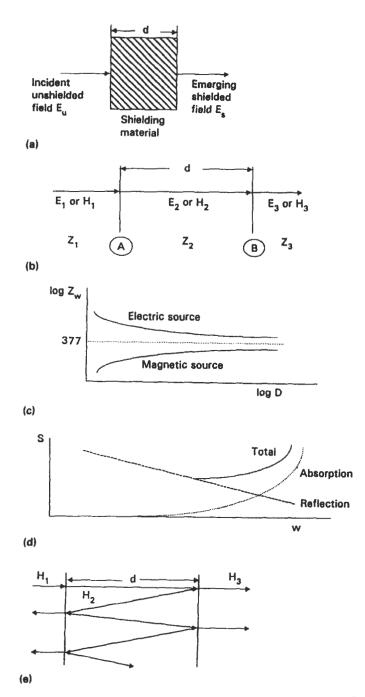

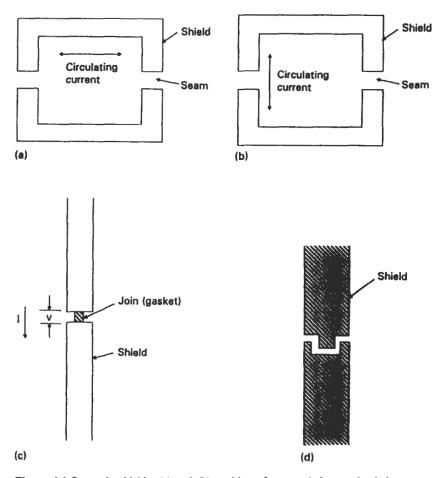

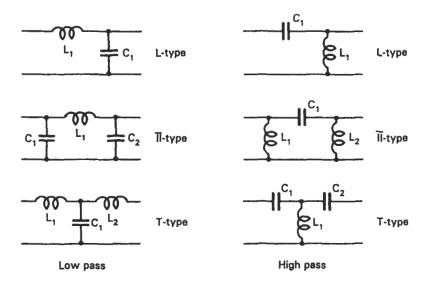

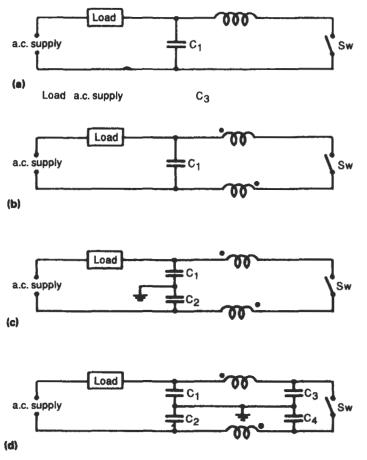

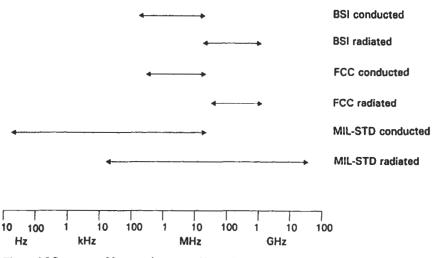

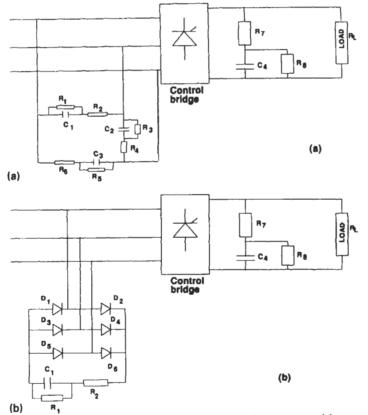

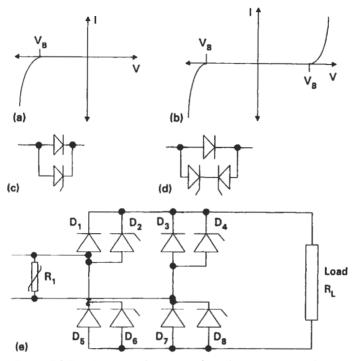

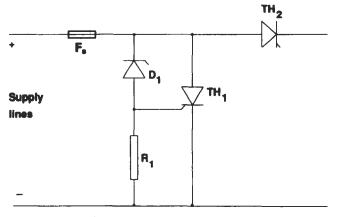

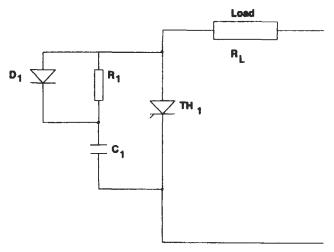

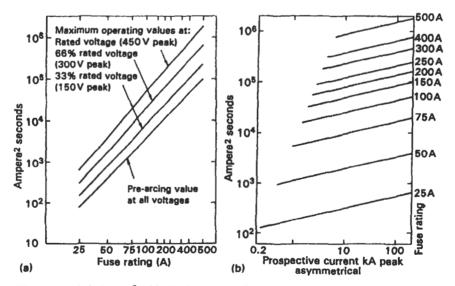

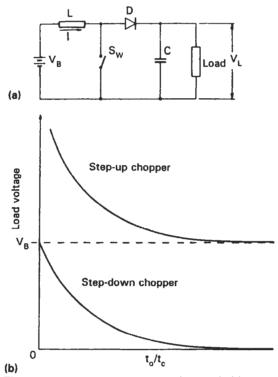

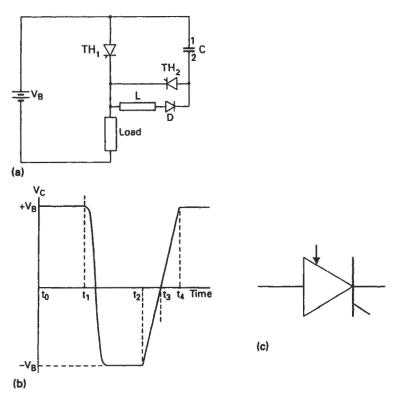

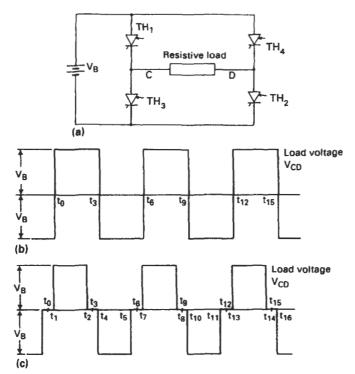

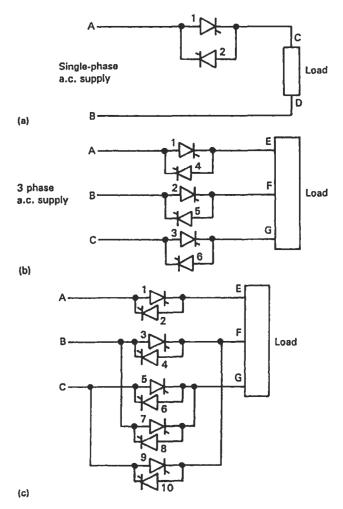

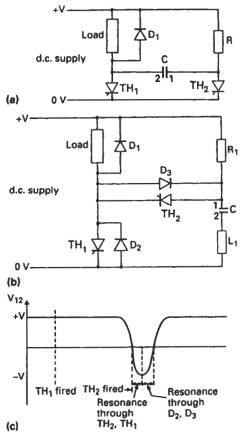

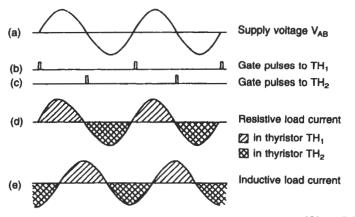

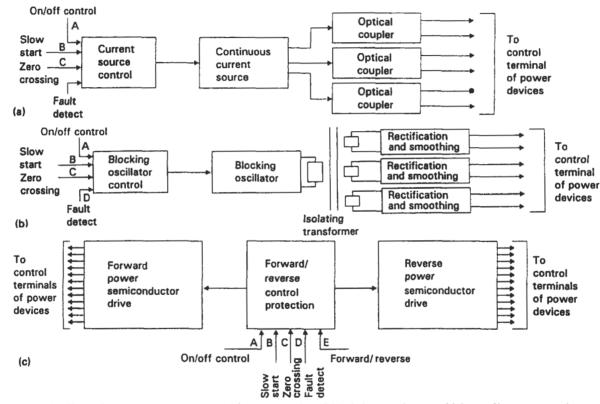

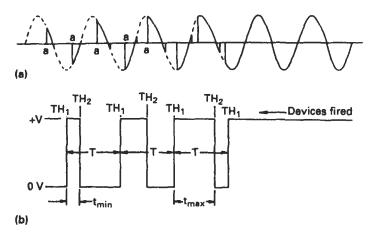

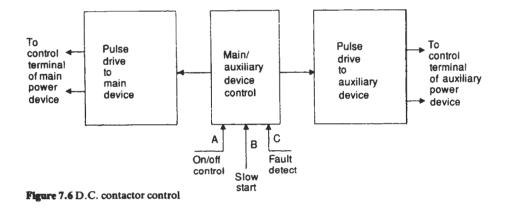

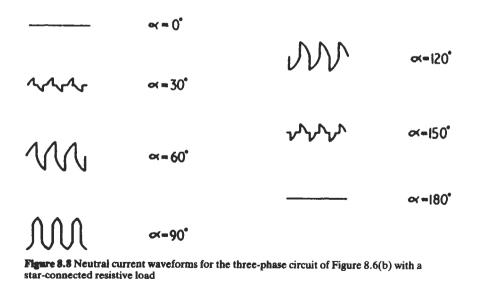

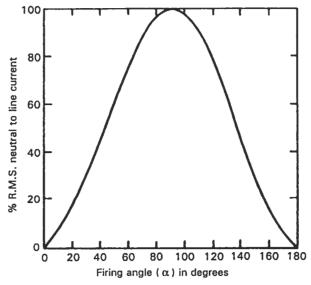

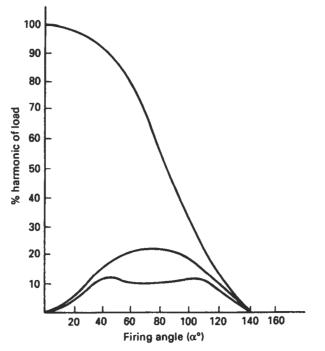

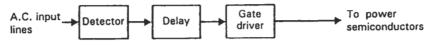

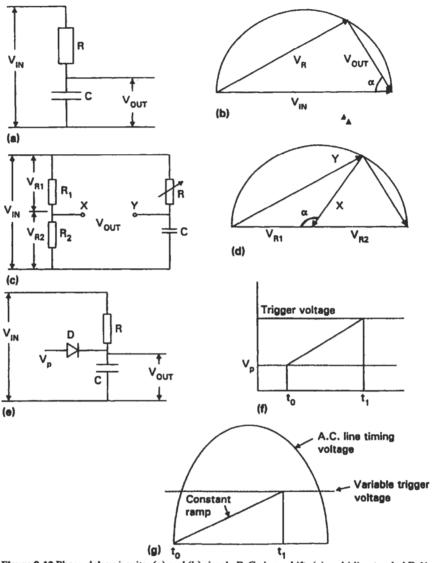

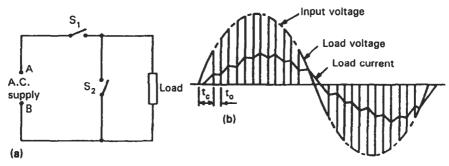

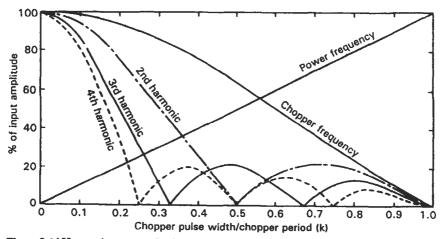

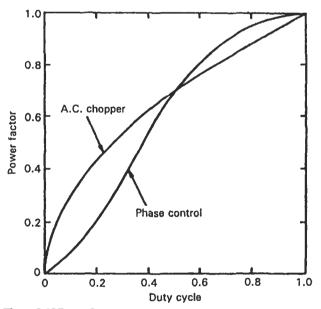

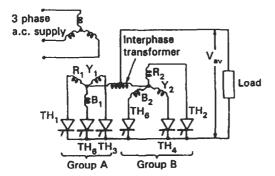

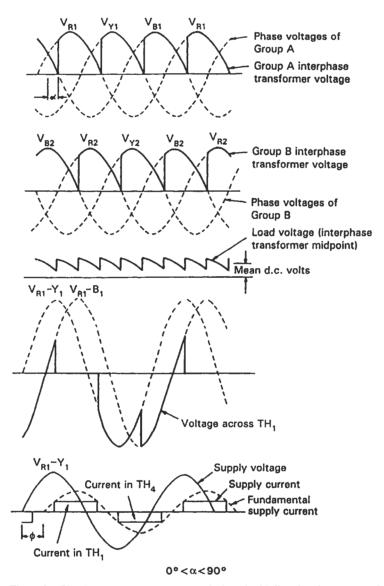

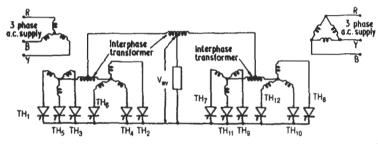

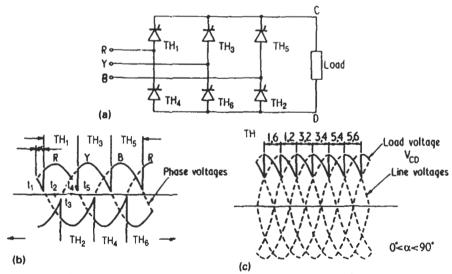

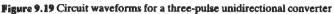

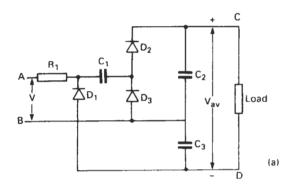

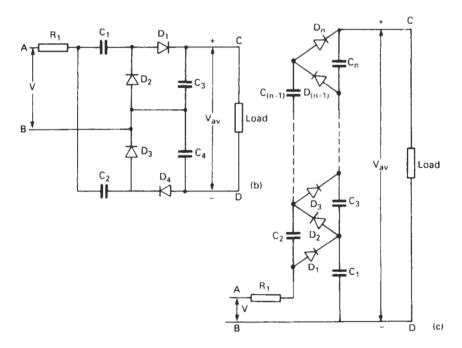

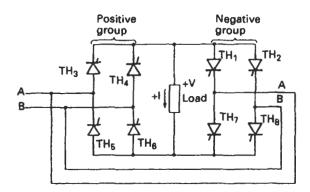

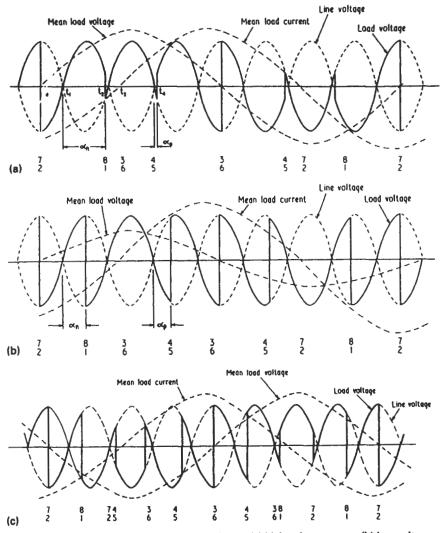

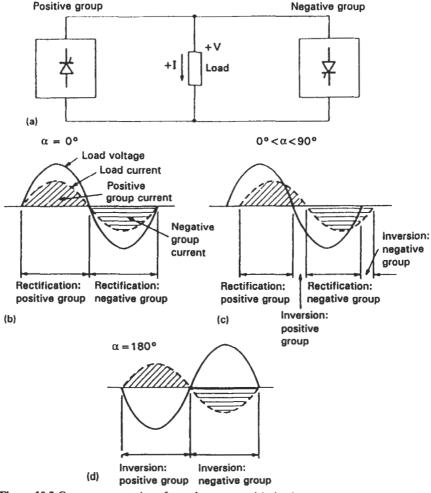

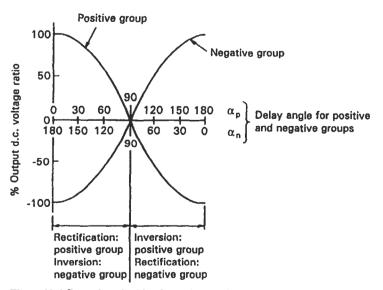

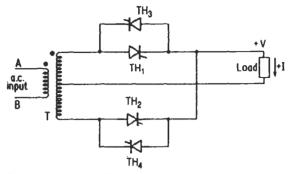

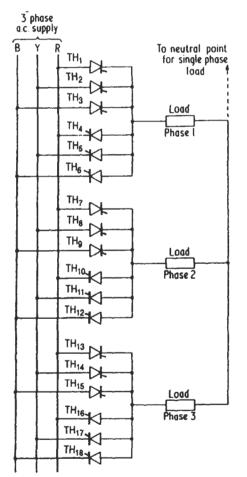

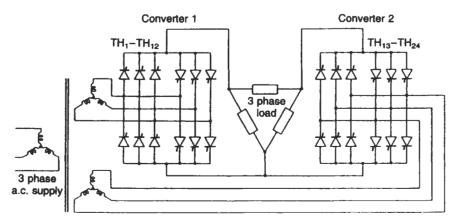

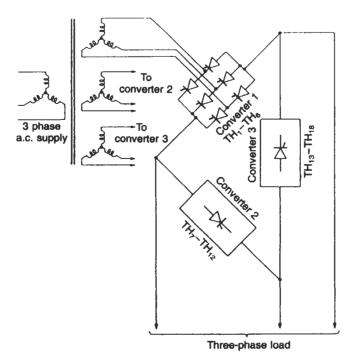

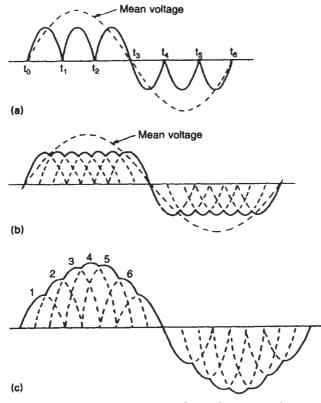

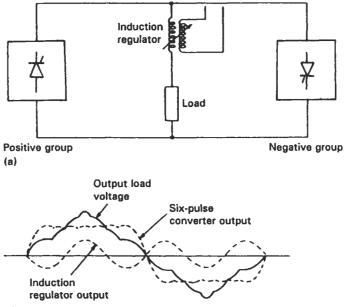

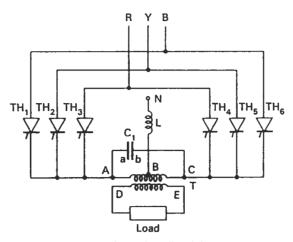

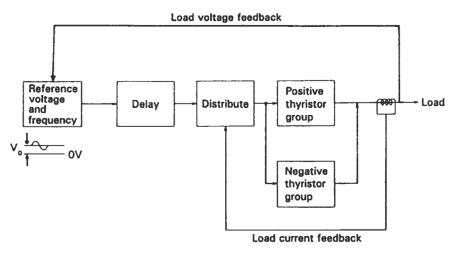

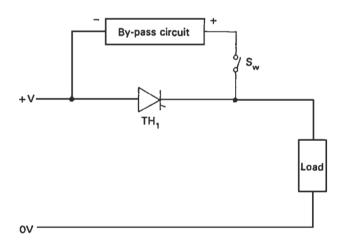

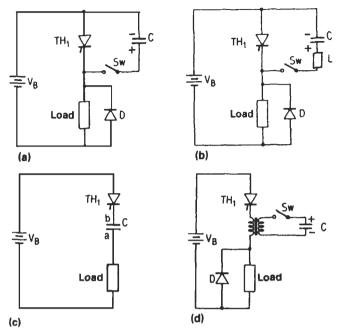

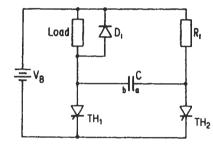

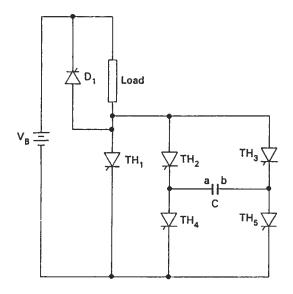

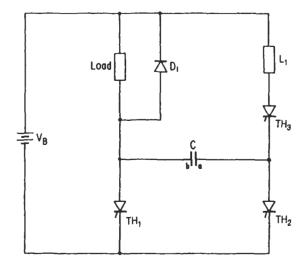

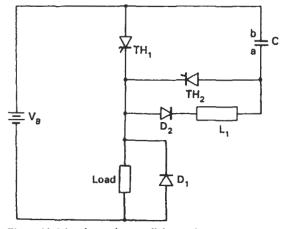

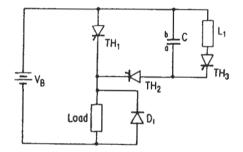

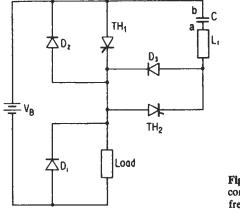

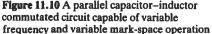

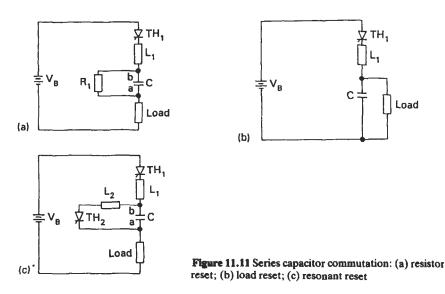

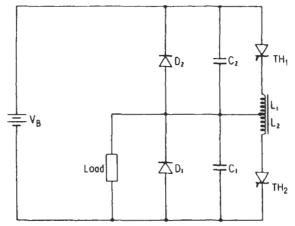

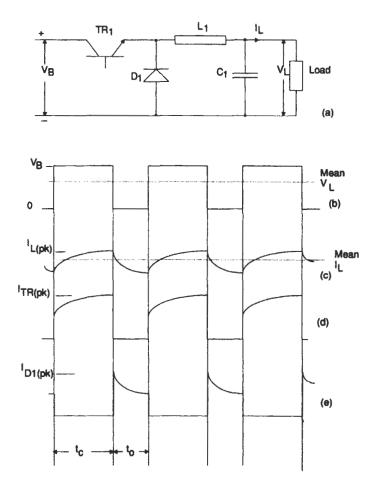

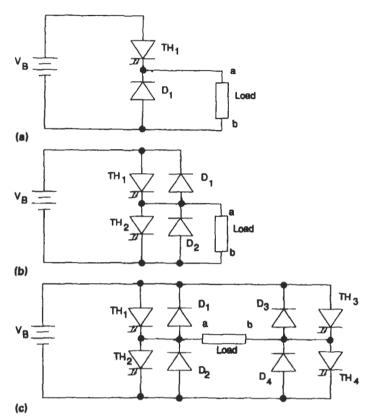

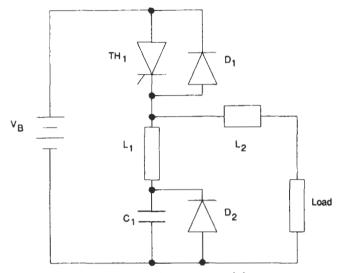

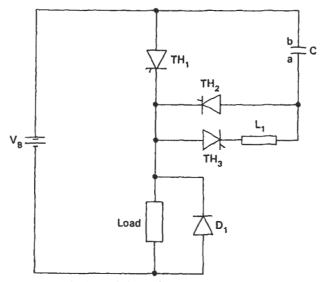

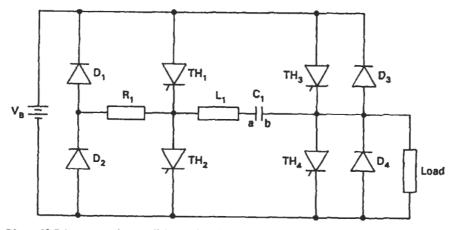

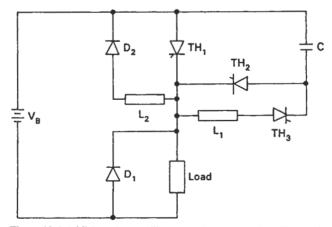

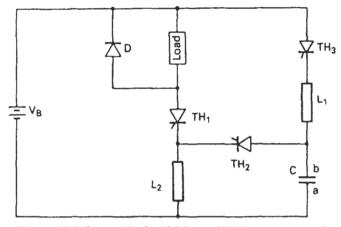

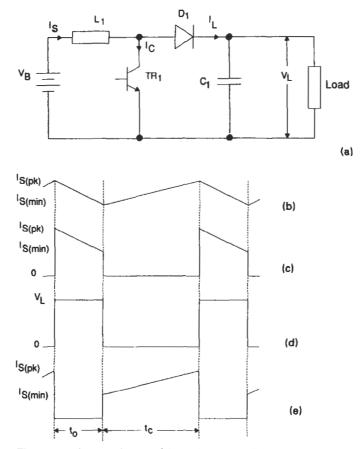

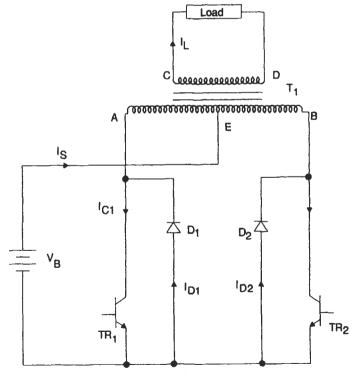

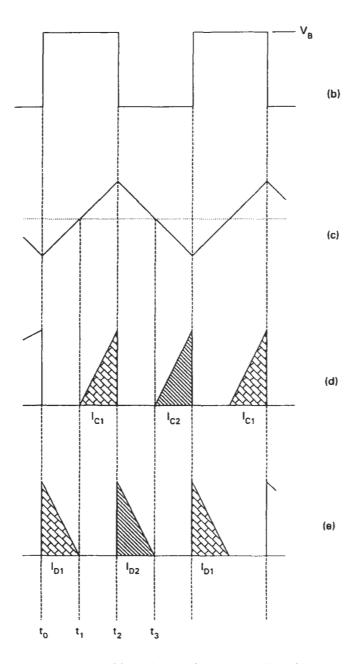

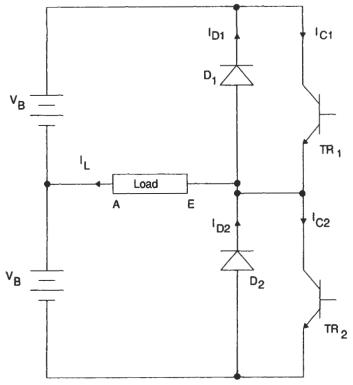

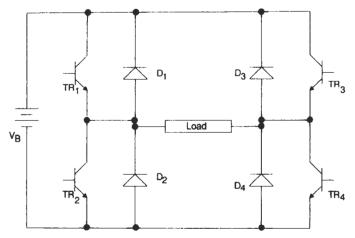

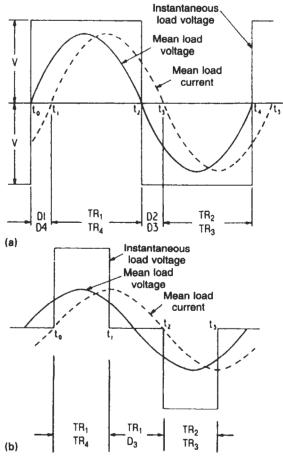

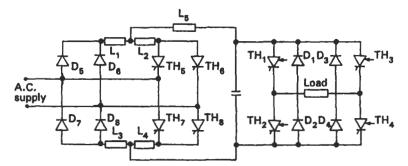

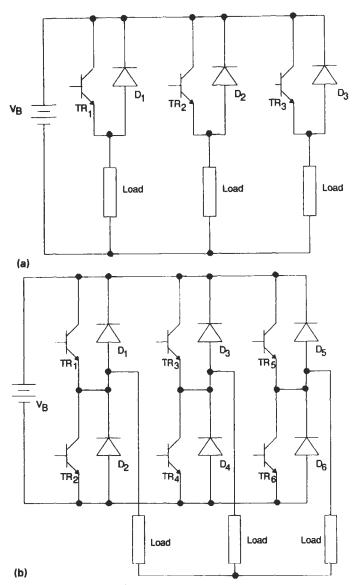

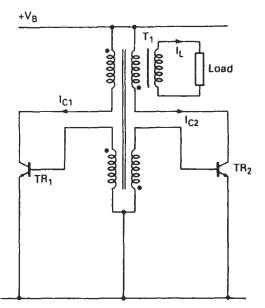

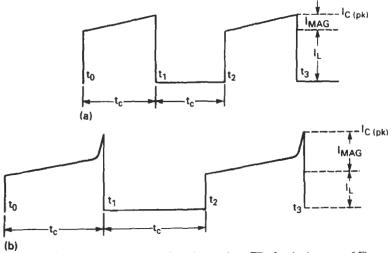

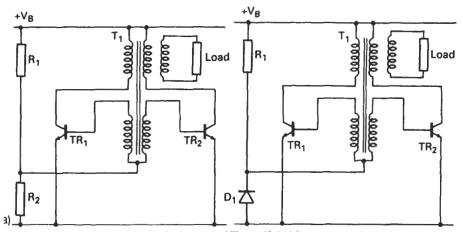

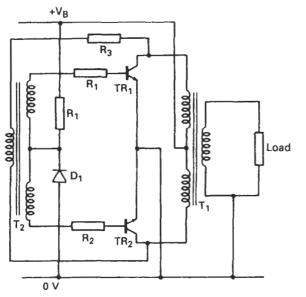

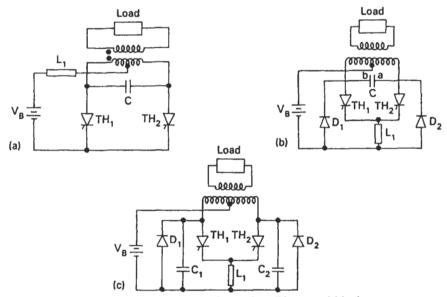

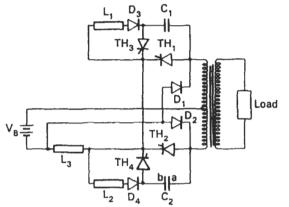

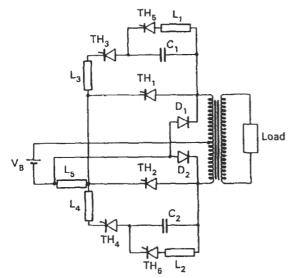

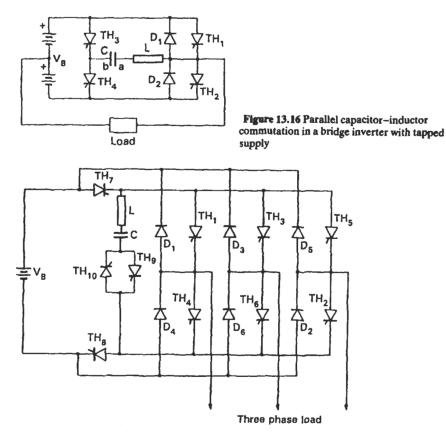

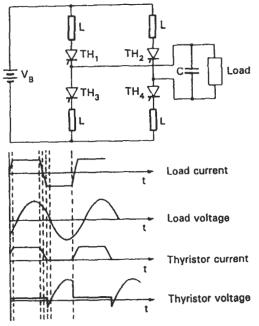

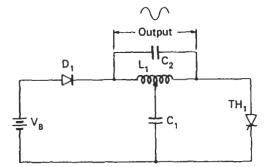

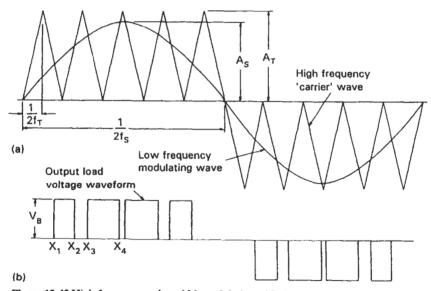

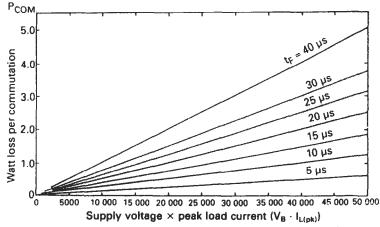

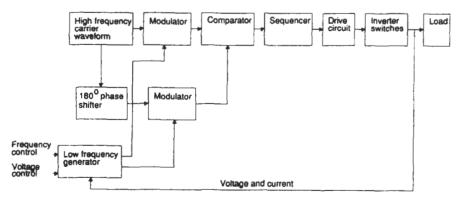

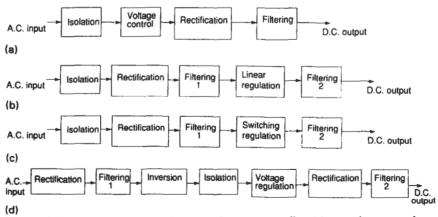

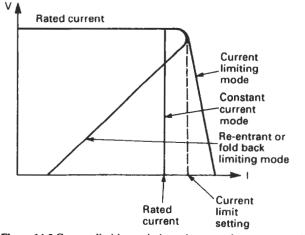

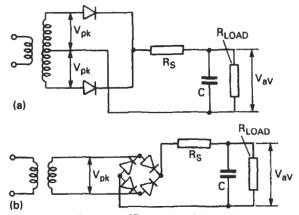

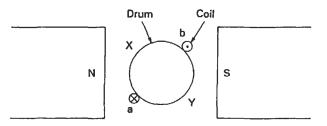

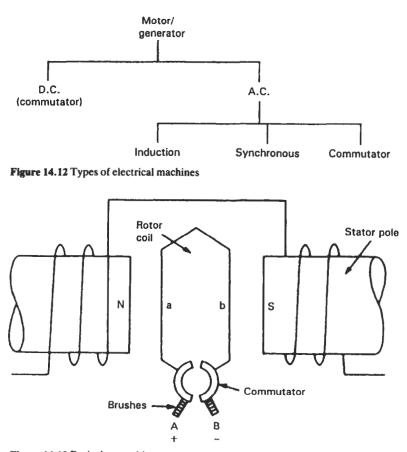

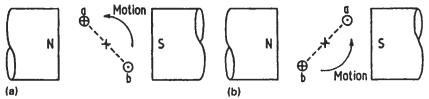

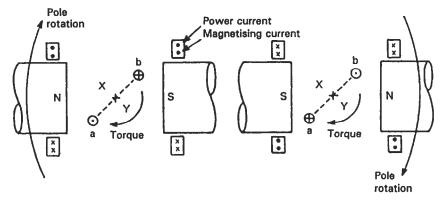

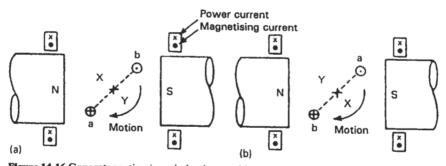

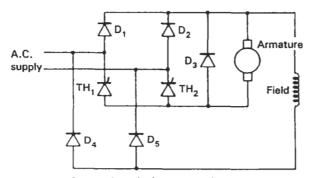

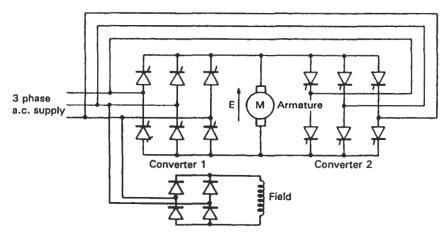

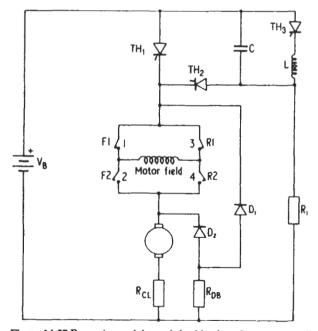

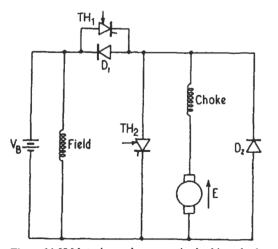

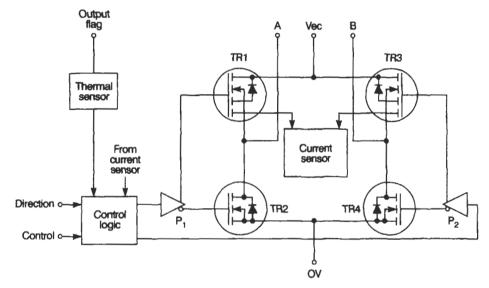

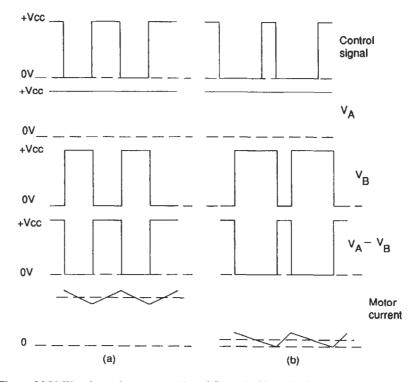

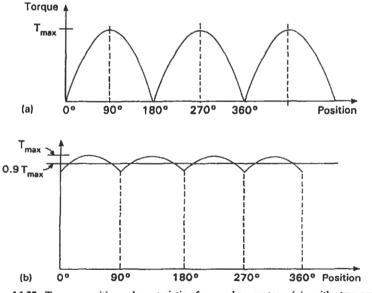

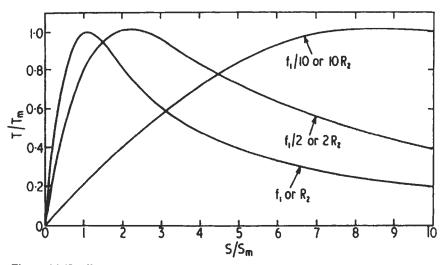

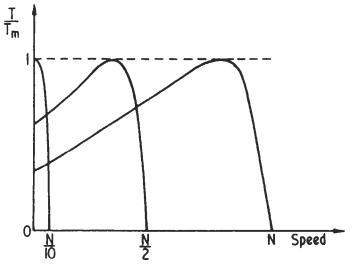

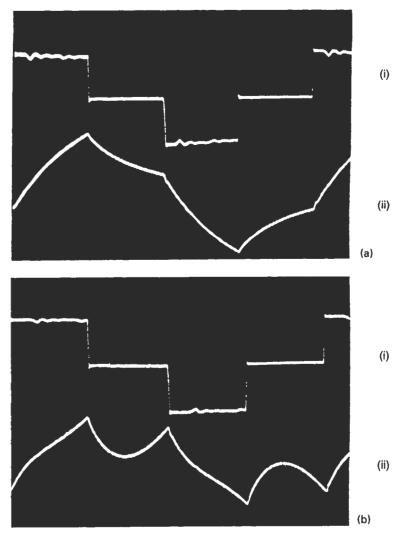

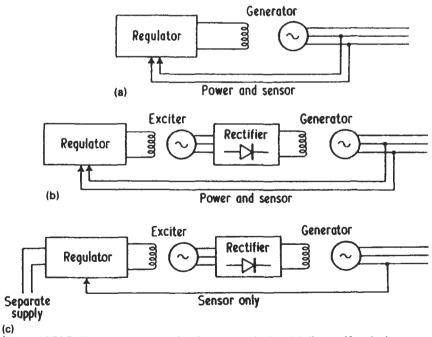

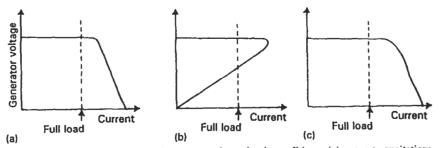

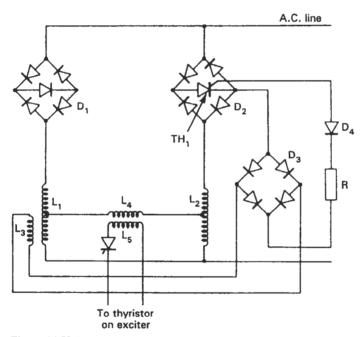

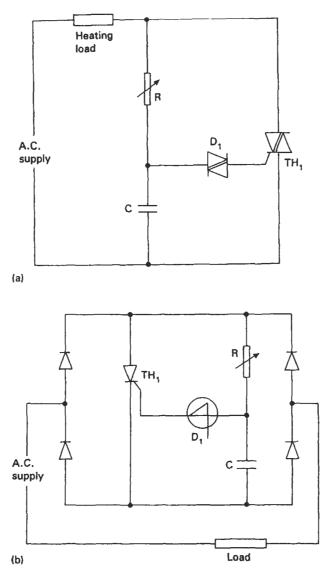

Figure 1.21 continued (d) equivalent circuit of parasitic components in (c); (e) V-groove MOS (VMOS)