Ted Huffmire Cynthia Irvine Thuy D. Nguyen Timothy Levin Ryan Kastner Timothy Sherwood

Handbook of FPGA Design Security

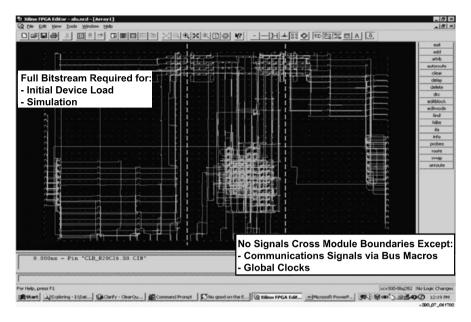

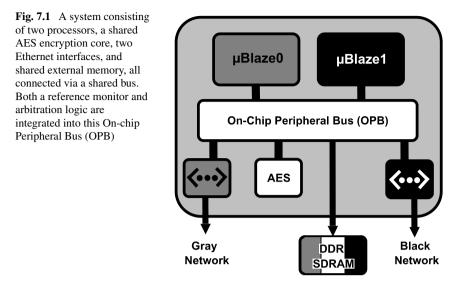

Handbook of FPGA Design Security

Ted Huffmire • Cynthia Irvine • Thuy D. Nguyen • Timothy Levin • Ryan Kastner • Timothy Sherwood

Handbook of FPGA Design Security

Dr. Ted Huffmire Department of Computer Science Naval Postgraduate School Cunningham Road 1411 93943 Monterey, CA USA tdhuffmi@nps.edu

Dr. Cynthia Irvine Department of Computer Science Naval Postgraduate School Cunningham Road 1411 93943 Monterey, CA USA

Thuy D. Nguyen Department of Computer Science Naval Postgraduate School Cunningham Road 1411 93943 Monterey, CA USA Timothy Levin Department of Computer Science Naval Postgraduate School Cunningham Road 1411 93943 Monterey, CA USA

Dr. Ryan Kastner Dept. of Computer Science and Eng. University of California, San Diego Gilman Drive 9500 92093 La Jolla, CA USA kastner@cs.ucsd.edu

Dr. Timothy Sherwood Department of Computer Science UC, Santa Barbara 93106 Santa Barbara USA

ISBN 978-90-481-9156-7 e-ISBN DOI 10.1007/978-90-481-9157-4 Springer Dordrecht Heidelberg London New York

e-ISBN 978-90-481-9157-4

Library of Congress Control Number: 2010930170

© Springer Science+Business Media B.V. 2010

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: eStudio Calamar

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

To our teachers

# Preface

The purpose of this book is to provide a practical approach to managing security in FPGA designs for researchers and practitioners in the electronic design automation (EDA) and FPGA communities, including corporations, industrial and government research labs, and academics. This book combines theoretical underpinnings with a practical design approach and worked examples for combating real world threats. To address the spectrum of lifecycle and operational threats against FPGA systems, a holistic view of FPGA security is presented, from formal top level specification to low level policy enforcement mechanisms, which integrates recent advances in the fields of computer security theory, languages, compilers, and hardware. The net effect is a diverse set of static and runtime techniques that, working in cooperation, facilitate the composition of robust, dependable, and trustworthy systems using commodity components.

We wish to acknowledge the many people who helped us ensure the success of our work on reconfigurable hardware security. In particular, we wish to thank Andrei Paun and Jason Smith of Louisiana Tech University for providing us with a Linuxcompatible version of Grail+. We also wish to thank those who gave us comments on drafts of this book, including Marco Platzner of the University of Paderborn, and Ali Irturk and Jason Oberg of the University of California, San Diego. This research was funded in part by National Science Foundation Grant CNS-0524771 and NSF Career Grant CCF-0448654.

Monterey, CA, USA

La Jolla, CA, USA Santa Barbara, CA, USA Ted Huffmire Cynthia Irvine Thuy D. Nguyen Timothy Levin Ryan Kastner Timothy Sherwood **Ted Huffmire** is an assistant professor of computer science at the Naval Postgraduate School in Monterey, California. His research spans both computer security and computer architecture, focusing on hardware-oriented security and the development of policy enforcement mechanisms for application-specific devices. He has a Ph.D. in computer science from the University of California, Santa Barbara. He is a member of the IEEE and the ACM.

**Cynthia Irvine** is the director of the Center for Information Systems Security Studies and Research (CISR) and a professor of computer science at the Naval Postgraduate School in Monterey, California. Her research interests include high-assurance security. She has a Ph.D. in astronomy from Case Western Reserve University. She is a member of the IEEE, the ACM, and the Astronomical Society of the Pacific.

**Thuy D. Nguyen** is a senior researcher of computer science at the Naval Postgraduate School in Monterey, California. Her research interests include high-assurance platforms, trusted operating systems, dynamic security services, multilevel security, security evaluation, and security requirements engineering. She has a B.A. in computer science from the University of California, San Diego.

**Timothy Levin** is an associate research professor at the Naval Postgraduate School in Monterey, California. His research interests include design, analysis and verification of high-assurance security architectures and dynamic security policies. He has a B.S. in computer science from the University of California, Santa Cruz. He is a member of the IEEE and the ACM.

**Ryan Kastner** is an associate professor in the Department of Computer Science and Engineering at the University of California, San Diego. His research interests focus on many aspects of embedded computing systems, including reconfigurable architectures, digital-signal processing, and security. He has a Ph.D. in computer science from the University of California, Los Angeles.

**Timothy Sherwood** is an associate professor in the Department of Computer Science at the University of California, Santa Barbara. His research interests include computer architecture, specifically in the development of novel high-throughput methods by which systems can be constructed, monitored, and analyzed. He has a Ph.D. in computer science and engineering from the University of California, San Diego. He is a member of the IEEE and the ACM.

# Contents

| 1 | Intr                                              | oduction and Motivation                             | 1  |  |  |

|---|---------------------------------------------------|-----------------------------------------------------|----|--|--|

|   | 1.1                                               | The Growing Reliance on FPGAs                       | 1  |  |  |

|   |                                                   | 1.1.1 FPGAs for Aerospace                           | 2  |  |  |

|   |                                                   | 1.1.2 FPGAs for Supercomputing                      | 4  |  |  |

|   |                                                   | 1.1.3 FPGAs for Video Analysis                      | 5  |  |  |

|   |                                                   | 1.1.4 FPGAs for High-Throughput Cryptography        | 5  |  |  |

|   |                                                   | 1.1.5 FPGAs for Intrusion Detection and Prevention  | 6  |  |  |

|   | 1.2                                               | FPGA Architectures                                  | 6  |  |  |

|   |                                                   | 1.2.1 The Attractiveness of Reconfigurable Hardware | 7  |  |  |

|   |                                                   | 1.2.2 The Internals of an FPGA                      | 8  |  |  |

|   |                                                   | 1.2.3 Design Flow                                   | 3  |  |  |

|   | 1.3                                               | The Many Facets of FPGA Security                    | 6  |  |  |

|   |                                                   | 1.3.1 Security Is Hard                              | 7  |  |  |

|   |                                                   | 1.3.2 Complexity and Abstraction                    | 8  |  |  |

|   |                                                   | 1.3.3 Baked in Versus Tacked on                     | 9  |  |  |

|   |                                                   | 1.3.4 Separation of FPGA Cores                      | 0  |  |  |

|   | 1.4                                               | Organization of This Book                           | 21 |  |  |

|   |                                                   | References                                          | 2  |  |  |

| 2 | High Assurance Software Lessons and Techniques 27 |                                                     |    |  |  |

|   | 2.1                                               | Background                                          | 27 |  |  |

|   | 2.2                                               | Malicious Software                                  | 27 |  |  |

|   |                                                   | 2.2.1 Trojan Horses                                 | 8  |  |  |

|   |                                                   | 2.2.2 Subversion                                    | 9  |  |  |

|   | 2.3                                               | Assurance                                           | 0  |  |  |

|   | 2.4                                               | Commensurate Protection                             | 1  |  |  |

|   |                                                   | 2.4.1 Threat Model                                  | 2  |  |  |

|   | 2.5                                               | Security Policy Enforcement                         | 4  |  |  |

|   |                                                   | 2.5.1 Types of Policies                             | 4  |  |  |

|   |                                                   |                                                     | 9  |  |  |

|   |                                                   | 2.5.3 Composition of Trusted Components             | 0  |  |  |

|   |                                                   |                                                     |    |  |  |

|   | 2.6 | Assurance of Policy Enforcement                                 | 51 |

|---|-----|-----------------------------------------------------------------|----|

|   |     | 2.6.1 Life Cycle Support                                        | 52 |

|   |     |                                                                 | 55 |

|   |     |                                                                 | 56 |

|   |     |                                                                 | 58 |

|   |     |                                                                 | 60 |

|   |     |                                                                 | 61 |

|   |     | 2.6.7 Static Analysis of Program Specifications                 | 62 |

|   |     | References                                                      | 65 |

| 3 | Har | Iware Security Challenges                                       | 71 |

| - | 3.1 |                                                                 | 71 |

|   |     |                                                                 | 71 |

|   |     | 8                                                               | 72 |

|   |     |                                                                 | 74 |

|   | 3.2 |                                                                 | 75 |

|   |     |                                                                 | 76 |

|   |     |                                                                 | 76 |

|   |     | 1                                                               | 76 |

|   |     |                                                                 | 77 |

|   |     |                                                                 | 77 |

|   |     | 3.2.6 Requirements                                              | 77 |

|   |     |                                                                 | 78 |

|   | 3.3 | Existing Approaches to Limiting Covert and Side Channel Attacks | 78 |

|   |     | 3.3.1 Shared Resource Matrix Methodology                        | 78 |

|   |     | 3.3.2 Cache Interference                                        | 79 |

|   |     | 3.3.3 FPGA Masking Schemes                                      | 79 |

|   | 3.4 | Detecting and Mitigating Covert Channels on FPGAs               | 80 |

|   |     | 6                                                               | 80 |

|   |     | 1                                                               | 80 |

|   |     | •                                                               | 81 |

|   | 3.5 |                                                                 | 81 |

|   |     |                                                                 | 81 |

|   |     |                                                                 | 81 |

|   |     | e                                                               | 82 |

|   |     | e                                                               | 83 |

|   |     | e                                                               | 83 |

|   |     | References                                                      | 84 |

| 4 | FPG | A Updates and Programmability                                   | 87 |

|   | 4.1 |                                                                 | 87 |

|   | 4.2 | Bitstream Encryption and Authentication                         | 87 |

|   |     | 4.2.1 Key Management                                            | 88 |

|   |     |                                                                 |    |

|   |     | 4.2.2 Defeating Bitstream Encryption                            | 89 |

|   |      | 4.3.1 Authentication                              | 0  |

|---|------|---------------------------------------------------|----|

|   |      | 4.3.2 Trusted Recovery                            | 1  |

|   | 4.4  |                                                   | 1  |

|   |      | -                                                 | 1  |

|   |      | 4.4.2 Hot-Swappable vs. Stop-the-World            | 2  |

|   |      |                                                   | 2  |

|   |      | •                                                 | 2  |

|   |      |                                                   | 3  |

|   |      |                                                   | 4  |

|   |      |                                                   | 5  |

| 5 | Men  | nory Protection on FPGAs                          | 7  |

|   | 5.1  |                                                   | 7  |

|   | 5.2  |                                                   | 8  |

|   | 5.3  |                                                   | 9  |

|   |      | • • •                                             | 9  |

|   |      | 5.3.2 Hardware Synthesis                          | 2  |

|   | 5.4  | A Higher-Level Specification Language             |    |

|   | 5.5  | Example Policies                                  |    |

|   |      | 5.5.1 Controlled Sharing                          |    |

|   |      | 5.5.2 Access List                                 |    |

|   |      | 5.5.3 Chinese Wall                                |    |

|   |      | 5.5.4 Bell and LaPadula Confidentiality Model     | 0  |

|   |      | 5.5.5 High Water Mark                             | 1  |

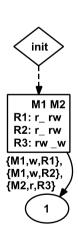

|   |      | 5.5.6 Biba Integrity Model                        | 2  |

|   |      | 5.5.7 Redaction                                   | 3  |

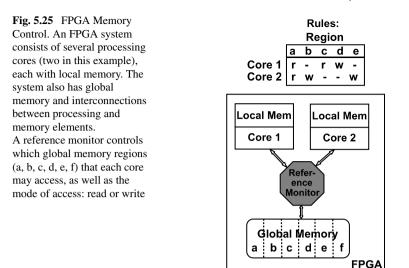

|   | 5.6  | System Architecture                               | 6  |

|   | 5.7  | Evaluation                                        | 6  |

|   | 5.8  | Using the Policy Compiler                         | 7  |

|   | 5.9  | Constructing Mathematically Precise Policies      | 0  |

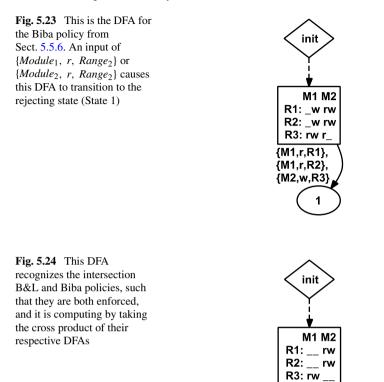

|   |      | 5.9.1 Cross Product Method                        | 0  |

|   |      | 5.9.2 Examples                                    | 1  |

|   |      | 5.9.3 Monotonic Policy Changes                    | 3  |

|   |      | 5.9.4 Formal Aspects of Hybrid Policies           | 4  |

|   | 5.10 | Summary                                           | 5  |

|   |      | References                                        | 5  |

| 6 | Spat | ial Separation with Moats                         | .7 |

|   | 6.1  | Overview                                          | 7  |

|   | 6.2  | Separation                                        | 8  |

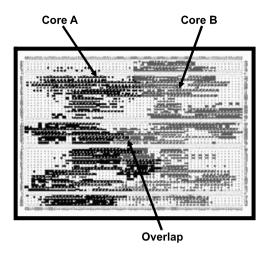

|   | 6.3  | Physical Isolation with Moats                     | 8  |

|   | 6.4  | Constructing Moats                                | 8  |

|   |      | 6.4.1 The Gap Method                              | 9  |

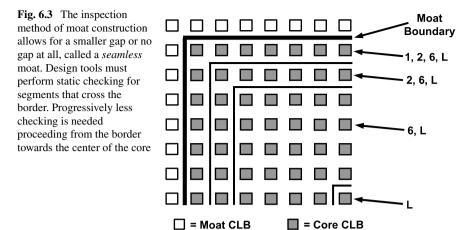

|   |      | 6.4.2 The Inspection Method                       | 0  |

|   |      | 6.4.3 Comparing the Gap and Inspection Methods 13 | 0  |

|   |      |                                                   |    |

|   | 6.5  | Secure Interconnect with Drawbridges             |

|---|------|--------------------------------------------------|

|   |      | 6.5.1 Drawbridges for Direct Connections         |

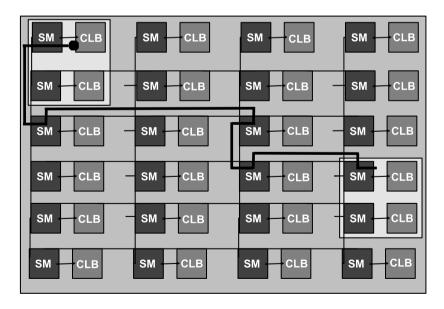

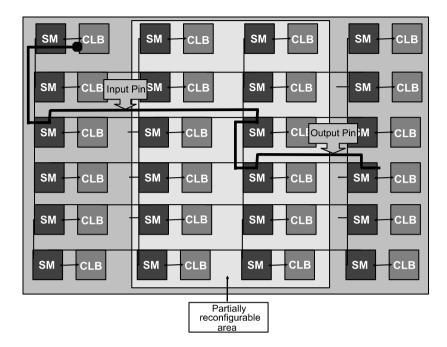

|   |      | 6.5.2 Route Tracing with Partial Reconfiguration |

|   |      | 6.5.3 Drawbridges for Shared Bus Architectures   |

|   | 6.6  | Protecting the Reference Monitor with Moats      |

|   |      | References                                       |

|   |      |                                                  |

| 7 | Putt | ing It All Together: A Design Example            |

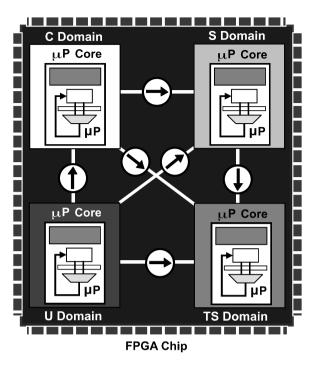

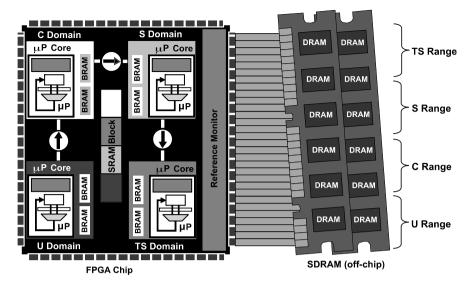

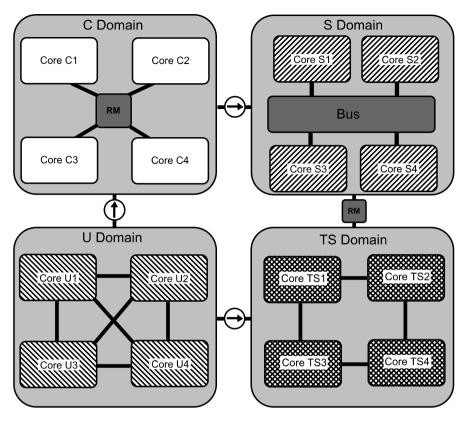

|   | 7.1  | A Multi-Core Reconfigurable Embedded System      |

|   | 7.2  | On-Chip Peripheral Bus                           |

|   | 7.3  | AES core                                         |

|   | 7.4  | Logical Isolation Compartments                   |

|   | 7.5  | Reference Monitor                                |

|   | 7.6  | Stateful Policy                                  |

|   | 7.7  | Secure Interconnect Scalability                  |

|   | 7.8  | Covert Channels                                  |

|   | 7.9  | Incorporating Moats and Drawbridges              |

|   | 7.10 | Implementation and Evaluation                    |

|   |      | Software Interface                               |

|   |      | Security Usability                               |

|   |      | More Example Security Architectures              |

|   | /110 | 7.13.1 Classes of Designs                        |

|   |      | 7.13.2 Topologies                                |

|   | 7 14 | Summary                                          |

|   | /.1  | References                                       |

|   |      |                                                  |

| 8 | Forv | vard-Looking Problems                            |

|   | 8.1  | Trustworthy Tools                                |

|   | 8.2  | Formal Verification of Secure Systems            |

|   | 8.3  | Security Usability                               |

|   | 8.4  | Hardware Trust                                   |

|   | 8.5  | Languages                                        |

|   | 8.6  | Configuration Management                         |

|   | 8.7  | Securing the Supply Chain                        |

|   | 8.8  | Physical Attacks on FPGAs                        |

|   | 8.9  | Design Theft and Failure Analysis                |

|   |      | Partial Reconfiguration and Dynamic Security     |

|   |      |                                                  |

|   | 0.11 | Concluding Remarks    158      References    160 |

|   |      |                                                  |

| Α | Com  | puter Architecture Fundamentals                  |

|   | A.1  | What Do Computer Architects Do All Day?          |

|   | A.2  | Tradeoffs Between CPUs, FPGAs, and ASICs         |

|   | A.3  | Computer Architecture and Computer Science       |

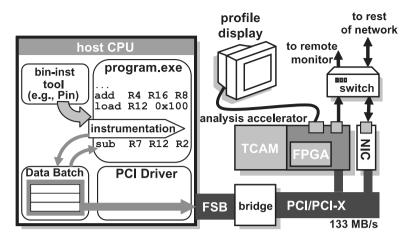

|   | A.4  | Program Analysis                                 |

|   | 11.7 | A.4.1 The Science of Processor Simulation        |

|   |      |                                                  |

|     | A.4.2   | On-Chip Profiling Engines 165 |

|-----|---------|-------------------------------|

|     | A.4.3   | Binary Instrumentation        |

|     |         | Phase Classification          |

| A.5 | Novel   | Computer Architectures        |

|     | A.5.1   | The DIVA Architecture         |

|     | A.5.2   | The Raw Microprocessor        |

|     | A.5.3   | The WaveScalar Architecture   |

|     | A.5.4   | Architectures for Medicine    |

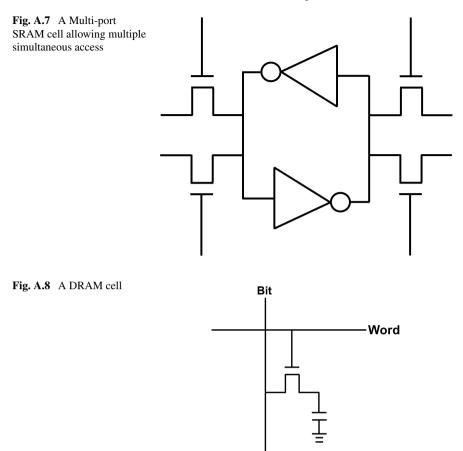

| A.6 | Memo    | ry                            |

| A.7 | Supers  | calar Processors              |

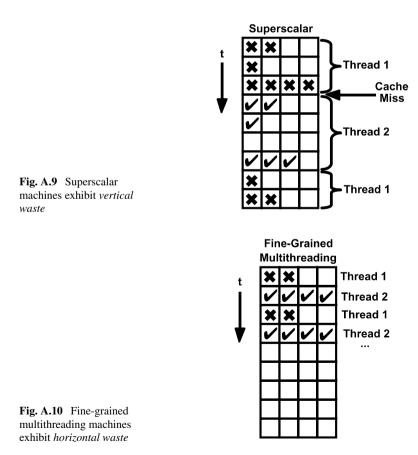

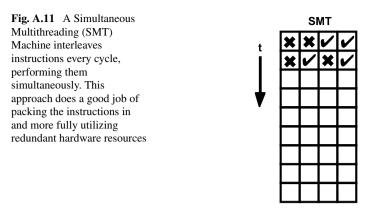

| A.8 | Multitl | hreading                      |

|     | Refere  | nces                          |

# Acronyms

| ACL   | Access Control List.                                                                       |  |

|-------|--------------------------------------------------------------------------------------------|--|

| ACM   | Association for Computing Machinery.                                                       |  |

| AES   | Advanced Encryption Standard. A common symmetric crypto algorithm.                         |  |

| API   | Application Programming Interface.                                                         |  |

| ASIC  | Application-Specific Integrated Circuit. An integrated circuit with                        |  |

|       | "hard-wired" functionality intended for use in one or a limited number<br>of applications. |  |

| BBV   | Basic Block Vector.                                                                        |  |

| B&L   | Bell-LaPadula confidentiality model.                                                       |  |

| BRAM  | Block Random Access Memory.                                                                |  |

| C&A   | Certification and Accreditation.                                                           |  |

| CAD   | Computer-Aided Design.                                                                     |  |

| CAP   | Capability Protection.                                                                     |  |

| CC    | Common Criteria.                                                                           |  |

| CCEVS | Common Criteria Evaluation and Validation Scheme.                                          |  |

| CIA   | Confidentiality-Integrity-Availability triad.                                              |  |

| CLB   | Configuration Logic Block. The basic repeated building block of an                         |  |

|       | FPGA, usually consisting of LUTs, registers, and other logic.                              |  |

| СМ    | Configuration Management.                                                                  |  |

| CMP   | Chip Multiprocessor.                                                                       |  |

| COI   | Conflict-of-Interest Class.                                                                |  |

| COTS  | Commercial Off-the-Shelf.                                                                  |  |

| CPU   | Central Processing Unit. A general-purpose processor.                                      |  |

| DARPA | Defense Advanced Research Projects Agency.                                                 |  |

| DFA   | Deterministic Finite Automaton.                                                            |  |

| DoS   | Denial-of-Service.                                                                         |  |

| DRAM  | Dynamic Random Access Memory.                                                              |  |

| DSP   | Digital Signal Processing.                                                                 |  |

| DVI   | Digital Visual Interface.                                                                  |  |

| EAL    | Evaluation Assurance Level.                                               |

|--------|---------------------------------------------------------------------------|

| EDK    | Embedded Development Kit.                                                 |

| EPROM  | Erasable Programmable Read-Only Memory.                                   |

| EEPROM | Electrically Erasable Programmable Read-Only Memory.                      |

| ESL    | Electronic System Level. ESL Design involves the compilation of a         |

|        | high-level specification of a system to a low-level hardware implemen-    |

|        | tation.                                                                   |

| FEMA   | Federal Emergency Management Agency.                                      |

| FFT    | Fast Fourier Transform.                                                   |

| FIPS   | Federal Information Processing Standard.                                  |

| FPGA   | Field Programmable Gate Array. A reconfigurable hardware device cre-      |

|        | ated as an array of logic blocks tied together with a programmable inter- |

|        | connect.                                                                  |

| FSA    | Finite State Automaton.                                                   |

| FTLS   | Formal Top Level Specification. A description of a policy that specifies  |

|        | the legal sharing of memory among cores on an FPGA.                       |

| HDL    | Hardware Description Language. A language for designing hardware          |

|        | components.                                                               |

| I&A    | Identification and Authentication.                                        |

| IBM    | International Business Machines.                                          |

| IC     | Integrated Circuit.                                                       |

| ICAP   | Internal Configuration Access Port. An interface to an FPGA for dy-       |

|        | namic partial reconfiguration.                                            |

| IDS    | Intrusion Detection System.                                               |

| IEEE   | Institute of Electrical and Electronics Engineers.                        |

| I/O    | Input/Output.                                                             |

| IOB    | Input/Output Block.                                                       |

| IP     | Intellectual Property. Hardware modules that are the building blocks of   |

|        | an embedded design.                                                       |

| ISA    | Instruction Set Architecture.                                             |

| ISE    | Integrated Synthesis Environment.                                         |

| IT     | Information Technology.                                                   |

| LCD    | Liquid Crystal Display.                                                   |

| LED    | Light-Emitting Diode.                                                     |

| LFU    | Least Frequently Used.                                                    |

| LPSK   | Least Privilege Separation Kernel.                                        |

| LRU    | Least Recently Used.                                                      |

| LUT    | Look-Up Table. The smallest FPGA logic component, the LUT can be          |

|        | programmed to imitate any logic gate by directly storing the truth table  |

|        | for that gate.                                                            |

| LVS    | Layout-versus-schematic. Comparison tools recommended by Trim-            |

|        | berger for detecting subversion in FPGA designs via non-destructive       |

|        | validation of the equivalence between the original design and the im-     |

|        | plemented design.                                                         |

|        |                                                                           |

| MATLAB  | Matrix Laboratory. Mathematical software that can be used for develop-  |

|---------|-------------------------------------------------------------------------|

|         | ing DSP algorithms.                                                     |

| MIMO    | Multiple Input Multiple Output.                                         |

| MLS     | Multilevel Security. The science of building systems that can process   |

|         | data with different security labels (e.g., SECRET and UNCLASSI-         |

|         | FIED).                                                                  |

| NFA     | Nondeterministic Finite Automaton.                                      |

| NIAP    | National Information Assurance Partnership.                             |

| NIST    | National Institute of Standards and Technology.                         |

| NP      | Nondeterministic Polynomial.                                            |

| NRE     | Non-Recurring Engineering. The masks used in ASIC fabrication are a     |

|         | large part of the NRE cost of ASICs.                                    |

| NSA     | National Security Agency.                                               |

| NSTISSP |                                                                         |

|         | rity Policy.                                                            |

| OPB     | On-chip Peripheral Bus.                                                 |

| PCI     | Peripheral Component Interconnect.                                      |

| PKI     | Public Key Infrastructure.                                              |

| PUF     | Physical Unclonable Function. A unique number generated from varia-     |

|         | tions in the manufacturing process.                                     |

| RAM     | Random Access Memory.                                                   |

| RISC    | Reduced Instruction Set Computer.                                       |

| RVM     | Reference Validation Mechanism.                                         |

| RSA     | Rivest Shamir Adelman. A common asymmetric key crypto algorithm.        |

| SDK     | Software Development Kit.                                               |

| SGI     | Silicon Graphics, Inc.                                                  |

| SKPP    | Separation Kernel Protection Profile.                                   |

| SMP     | Symmetric Multiprocessor.                                               |

| SMT     | Simultaneous Multithreading.                                            |

| SoC     | System-on-a-Chip.                                                       |

| SRAM    | Static Random Access Memory.                                            |

| SRAM    | Seymour Roger Cray. Founder of SRC Computers.                           |

| SSL     | Secure Sockets Layer.                                                   |

| TCB     | Trusted Computing Base.                                                 |

| TCSEC   | Trusted Computing Dasc.<br>Trusted Computer System Evaluation Criteria. |

| TIC     | TRUST in Integrated Circuits. A DARPA program concerned with hard-      |

| IIC     | ware subversion.                                                        |

| TLB     | Translation Lookaside Buffer.                                           |

| TOE     | Target of Evaluation.                                                   |

| TSF     | TOE Security Functionality. A set consisting of all hardware, software, |

|         | and firmware of the TOE that must be relied upon for the correct en-    |

|         | forcement of the security functional requirements.                      |

| USB     | Universal Serial Bus.                                                   |

| VHDL    | VHSIC (Very-High-Speed Integrated Circuits) Hardware Description        |

|         | Language.                                                               |

| VLIW    | Very Long Instruction Word.                                             |

|         |                                                                         |

| VM  | Virtual Machine.           |

|-----|----------------------------|

| VMM | Virtual Machine Monitor.   |

| VPN | Virtual Private Network.   |

| VPR | Versatile Place and Route. |

| WAP | Wireless Access Point.     |

| XPS | Xilinx Platform Studio.    |

|     |                            |

# Chapter 1 Introduction and Motivation

Abstract From Bluetooth transceivers to the NASA Mars Rover, FPGAs have become one of the mainstays of embedded system design. By merging properties of hardware and software, reconfigurable devices provide an attractive tradeoff between the performance of application-specific hardware and the programmability of CPUs. Although this flexibility allows developers to quickly prototype and deploy embedded systems with performance close to ASICs, this programmability can also be exploited to disrupt critical functionality, eavesdrop on encrypted communication, or even destroy a chip. Creating systems which are both efficient and flexible, yet fundamentally sound from a security point of view, is an exceedingly challenging endeavor for both researchers and practitioners. All too often the security aspects of a reconfigurable design are not addressed until far too late in the design process, resulting in systems that are protected only by their obscurity. This chapter presents an overview of Field Programmable Gate Array (FPGA) technologies from the viewpoint of security, specifically how and why these devices have grown in importance over the last decade to become one of the most trusted and critical elements of modern computer systems. This chapter also discusses their changing role from a platform for prototyping to a deployable solution, the architecture of a modern FPGA, the security ramifications of their increased use, and some of the lessons from the security community that may be applicable in this domain.

# 1.1 The Growing Reliance on FPGAs

FPGAs are at the heart of many mission critical devices, silently controlling everything from wireless access points (WAP) to commercial face recognition systems. Unlike the sequential execution provided by a general purpose processor, modern Field Programmable Gate Arrays can perform hundreds of multiplies and thousands of adds each cycle, giving them the computational power to host many different logic modules at the same time. For example, an FPGA-hosted Wireless Access Point (WAP) may employ a signal processing core, a protocol processing engine, and a packet scheduler, all sharing the same physical silicon. Furthermore, because reconfigurable hardware can be rewritten in both the lab and in the field, rapid design cycles are possible, and patches can even be downloaded to devices already deployed (e.g. bug fixes or functionality enhancements can be pushed out over the network to cell phones or wireless access points on demand).

Because of this rare combination of computation power and flexibility, reconfigurable devices are now the workhorses behind a broad variety of performancecritical embedded systems [9, 15, 19, 40, 51, 62]. In fact, many reconfigurable machines achieve 100x speedups and 100x performance gain per unit of area as compared to a similar microprocessor [12, 18, 75]. Satellites, set-top boxes, intrusion detection systems, the electrical power grid, cryptography units, aircraft, and even the Mars Rover all rely on Field Programmable Gate Arrays (FPGAs) to perform their respective functions. It is estimated that in 2005 alone there were over 80,000 different commercial FPGA design projects started [53]. The bit-level reconfigurability of these devices can be used to implement highly optimized circuits for everything from encryption to FFTs, or even entire customized multi-processor systems. In this section we describe a couple of these different domains and how FPGAs are used in them.

Design Tip: Benefits of FPGAs. FPGAs are ideal for rapid protyping of embedded designs and the development of novel computer architectures. The increasing cost of ASIC manufacturing, the performance advantages of FPGAs over general-purpose processors, and the narrowing performance gap between FPGAs and ASICs have resulted in the growing use of FPGAs in real systems. For low-volume segments of the market, such as highly trustworthy systems, FPGAs provide both cost and security advantages over ASICs. For example, with FP-GAs, sensitive designs are never sent to a foundry where they could be stolen. The parallelism available on FPGAs also makes them an attractive alternative to general-purpose CPUs for throughput-driven applications.

#### 1.1.1 FPGAs for Aerospace

Because FPGAs are able to provide a useful balance between performance, cost, and flexibility, many avionics systems now make use of them. For example, FP-GAs perform crucial functions in the Joint Strike Fighter [56], the new Boeing 787 Dreamliner [20], and the NASA Mars Rover [23, 57]. In these applications, FPGAs are used for cockpit displays, flight management, avionics, weapons guidance, and flight radar [2].

Design Tip: FPGA Basics. A bitstream specifies how to set the configuration bits of the FPGA fabric. A core is a circuit that is used as a building block of a larger embedded system. An antifuse-based FPGA uses fuses as the configuration bits; therefore, it can only be programmed once and is nonvolatile thereafter. An SRAM-based FPGA uses volatile SRAM cells as the configuration bits. A flash-based FPGA uses EEP-ROM cells as the configuration bits.

The circuits may be either antifuse-based, flash-based, or SRAM-based. While fuse-based circuits are write-once devices, SRAM- and flash-based FPGAs can be written many times, either in the lab or in the field. Flash-based circuits provide low power advantages.

Design Tip: Choosing an FPGA Type. SRAM-based, flash-based, and antifuse-based FPGAs have different security properties [76]. Despite the limitation that it is a write-once technology, an antifuse FPGA offers the advantage that theft of the design requires a painstaking and destructive sand-and-scan attack, involving removal of the packaging and the progressive etching and electron micrography of each layer to create a 3-D image of the chip. Since the fuses are nonvolatile, the bitstream does not have to be loaded from off-chip, exposing it to board-level probing attacks and attacks on the bitstream encryption mechanisms. Flash-based FPGAs also can store the bitstream on-chip, and the design does not have to be loaded from off-chip. This eliminates one avenue for attackers. However, unlike an antifuse-based FPGA, the design is changeable since flash memory can be modified. In addition, flash-based FPGAs are much easier to probe, and probing attacks are much cheaper to carry out than sand-and-scan attacks. SRAM-based FPGAs must load the bitstream every time they are powered on, and soft memory errors [28] or flaws in the implementation of bitstream decryption mechanisms may provide an opportunity for a well-funded adversary to extract the design. When powered continuously, SRAM-based FPGAs are similar to non-volatile FPGAs in that the design does not have to be loaded from non-volatile off-chip memory.

Consider the example of military avionics, in which a single chip processes both classified targeting information and unclassified fueling and maintenance information. Other multilevel security (MLS) scenarios for avionics include the sensor-shooter problem, in which the intelligence analysts who decide on targets have higher clearances than the soldiers ordered to attack those targets. In another MLS scenario, a coalition member flies in formation with his or her allies, and a policy

must specify what information may be shared with each of them. In these multilevel systems, a CPU can be *allocated* to handle a particular level (or a range of levels) of data, and it is assigned a security label (or a security label range). A separate device for each security level adds too much weight to an aircraft. To minimize weight, a single device that can process data at multiple levels is attractive, but without careful attention to security, can be dangerous. Keeping the different levels of information separate requires careful design. Since reconfigurable systems often lack the memory protection, virtual memory, and other traditional separation mechanisms available in a general-purpose system, security techniques are needed to prevent classified data from mixing with unclassified data. In addition, like software update mechanisms, it is critical that the process for remotely updating these devices is very secure to prevent sabotage. Finally, due to the sensitive nature of the intellectual property, it is very important to keep competitors or enemies from being able to reverse engineer these systems easily.

## 1.1.2 FPGAs for Supercomputing

While desktop computers continue to make incredible gains in performance, there are always problems that lie outside the capabilities of these machines, and scientists and engineers eventually turn to "big iron" when performance is needed. Many supercomputer companies, including SRC Computers [25, 71], Cray [58], and SGI [67, 68], have integrated reconfigurable hardware into their systems to improve performance [10, 16]. A good example of such a system is Cray's XD1 architecture, which combines six large Xilinx FPGAs (Virtex-4) with twelve x86 processors in each chassis. When an application is loaded on the machine, it includes a bitstream for programming the associated reconfigurable hardware. Although the past generations of FPGAs were not cost competitive with microprocessors in delivering double precision floating point [74], they can provide significant improvements (100x) in integer dominated applications. The current generation of FPGAs includes more integrated support for floating point. In the supercomputing environment, often the code and data being run are either sensitive intellectual property or even classified in nature, requiring a commensurately secure computing environment. Furthermore, supercomputing centers require strong physical security because they are very high profile targets for intruders.

The SRC Reconfigurable computer is an example of a system that uses FPGAs to provide acceleration for programs running on general-purpose processors [25, 71]. Logging into the machine is via a traditional Unix shell interface. A project folder contains both Verilog and either C or Fortran code. A Makefile invokes a Verilog compiler for the Verilog code (resulting in a bitstream), and it also invokes a C compiler for the C code (or a Fortran compiler for the Fortran code). Executing a program on the SRC requires loading the bitstream onto the reconfigurable hardware and loading the executable program onto the general-purpose hardware. From a security standpoint, if the host OS, application software, or user account has been

compromised, a malicious bitstream could be loaded onto the reconfigurable hardware. The malicious hardware could interfere with the correct function of the application or even damage the hardware. Since FPGAs are part of a larger system, the security analysis needs to consider the interactions of the CPUs and FPGAs.

#### 1.1.3 FPGAs for Video Analysis

FPGAs also provide a natural fit for complex high speed signal processing applications such as video analysis and face recognition [59]. These algorithms are most often dominated by large matrix operations and are throughput-driven, meaning that parallelism and pipelining are likely to yield large performance gains for these applications. In terms of the security ramifications of these systems, consider the problem of video redaction.

Redaction involves removing sensitive information from data such as documents, songs, and movies. Redaction may be used in the process of making unclassified portions of a secret document available to the public, or may be used to protect people's privacy. An example of the redaction of video involves blurring the faces of people captured by surveillance cameras. This is necessary when the system is being tested or maintained by a person who lacks the necessary authorization to view faces. IBM has developed such a video privacy system called PeopleVision [65]. To implement such a system on an FPGA, at least three IP cores are used: a video core for processing the video, a redaction core for blurring the faces, and an Ethernet core for transmitting the redacted video to the security guard's terminal. Each core requires off-chip memory, and the privacy of data stored in off-chip memory must be protected. For example, the video core must not be able to bypass the redaction core and send data directly to the Ethernet core. Since few applications are developed fully *in-house*, the trustworthiness of the building blocks of a composed embedded system is a growing concern, particularly since reuse of intellectual property is common in both software and hardware development.

# 1.1.4 FPGAs for High-Throughput Cryptography

Implementing crypto on FPGAs offers several advantages. Block ciphers require many bit-level operations, such as shifting or permuting bits, which can be efficiently implemented on an FPGA. FPGAs also allow algorithm parameters to be changed easily, or the entire circuit can be replaced completely. For example, if mathematicians discover a flaw in a cipher, the bitstream can easily be updated with a patched version. These advantages have been exploited in FPGA implementations of MD5 [17], SHA-2 [70], and a range of other crypto functions [17, 37, 43, 55, 60, 64, 66, 70, 77]. FPGAs are also useful for public-key crypto, such as RSA, in which the fundamental operation is modular multiplication, and Elliptic Curve Crypto, in

which the fundamental operation is point multiplication [27, 29, 48, 54]. Reconfigurable devices are also widely used in network intrusion detection systems (IDS) because of the ability to search packet streams at high throughput against multiple rule sets in parallel [4–6, 13, 14, 21, 26, 36, 72].

Most modern symmetric key cryptosystems can be characterized as performing a repeating series of rounds over a given input. Consider the *rotate* operation as an example. A rotate operation shifts the *b* bits of a word over *n* positions. The bit that was at position *i* before the rotate will now be at position  $(i + n) \mod b$ . Implementing this in software requires multiple instructions to shift and wrap the bits in the word. In contrast, an FPGA can implement this by simply rearranging the wires so that the bits arrive in their new order. All of this work focuses on using FPGAs to achieve high speed crypto but does not address the security of the reconfigurable systems themselves. Since crypto devices naturally handle secrets (e.g., keys), they are attractive targets for adversaries. A poorly implemented system will be vulnerable to a variety of timing and side channel attacks, allowing attackers to obtain secret keys. Ensuring the integrity of systems is also essential to prevent attackers from modifying the crypto functions to their advantage.

### 1.1.5 FPGAs for Intrusion Detection and Prevention

Another area related to security where reconfigurable devices are widely employed are network intrusion detection systems (IDS). Because many IDSs require that every byte of every packet be scanned for known attacks or suspicious behavior, intrusion detection is a computationally difficult problem. Network speeds now operate in the realm of gigabits per second, and an intrusion detection scheme must be able to *always* keep up with the network load. This worst-case performance requirement, coupled with the pipelined manner with which analysis is performed, makes FP-GAs a nearly perfect design choice. In fact, a wide variety of FPGA-based IDSs have been built [4–6, 13, 14, 21, 26, 36, 72]. It is important that the integrity of the IDS is maintained and that the IDS cannot be bypassed (for example by routing communication around the IDS core).

# **1.2 FPGA Architectures**

On a continuum between general-purpose processors and application-specific integrated circuits (ASICs), FPGAs lie somewhere in the middle. A CPU is a jackof-all-trades but a master of none: it can run arbitrary code, but this generality comes at a large performance cost. While compilers and programming languages have transformed computer science, making it possible for humans to easily program computers, we often forget about the high overhead of generality. ASICs, on the other hand, can achieve impressive throughput by harnessing parallelism in an optimized circuit, but they are enormously expensive to fabricate (the cost increases every year), requiring large capital investments. An ASIC is a master of one trade: all functions are hard-wired. Reconfigurable hardware, unlike ASICs and CPUs, offers the opportunity to implement a custom circuit without the expense of fabricating silicon, providing improvements in throughput on the order of one hundred times when compared with a CPU [12, 18, 75]. This section describes the nuts and bolts of a typical reconfigurable chip to illustrate its performance advantages and to provide the background needed to understand the security mechanisms for FPGAs discussed in this book.

#### 1.2.1 The Attractiveness of Reconfigurable Hardware

The roots of reconfigurable systems can be traced to Gerald Estrin's work at UCLA in the 1960s. Estrin's "fixed plus variable structure computer" [24] consisted of a standard processor augmented by an array of reconfigurable hardware. His idea was well ahead of the technology at that time, so he was only able to make a crude approximation of his vision.

Interest in reconfigurable systems was renewed in the mid-eighties with the emergence of programmable logic devices, which were used almost exclusively as a fast prototyping device for application specific integrated circuit (ASIC) designers. They allowed the designer to compile the application to reconfigurable hardware to determine whether the application exhibited the correct functionality. The prototyping removed the costly step of fabricating the circuit, especially when fabrication yielded a device that exhibited incorrect functionality (i.e. buggy hardware). Additionally, the rapid prototyping lessened the need for intense simulation to verify correctness. If the application functioned correctly in the environment when compiled to an FPGA, it was far more likely to be correct once fabricated. The main drawback of the FPGA during this era was the performance. The FPGA was far behind the ASIC in terms of the most important performance aspects, such as latency, power consumption, etc. An application implemented on an FPGA was synthesized to the static nature of an ASIC and was not taking into account the dynamic reconfigurability allowed by the FPGA; in this sense, the performance of the FPGA can never overcome that of an ASIC [40]. However, as ASIC design has become increasingly expensive, and as the design rules have become significantly more complex, many of the tricks ASIC designers would use to squeeze all the performance out of their system have become too costly or error prone to be practical, thus narrowing the gap in performance between the two [45].

The power of reconfigurable systems lies in their flexibility. This flexibility not only allows for run-time circuit reorganization based on the input parameters, operating conditions, and updates, it also allows for a single circuit to be fabricated at incredible volumes. The high volume of FPGAs means that foundries are able to create them very cheaply (one shared mask, very large production runs, etc.) and very effectively (FPGAs are often the technology leaders, always available in the most aggressive lithography and processes, and carefully tuned to minimize variation and other deep submicron effects). Due to the ability to customize the input data, many applications show speedups when implemented on reconfigurable systems. Many computing systems are fully reconfigurable at the logic level, and many devices are reconfigurable at the architectural level. In addition, reconfigurable cores are increasingly being used as components in embedded systems (e.g. microprocessors coupled with a reconfigurable component) as well as ASICs coupled with a reconfigurable component. Because of this, reconfigurable computing systems have emerged as an important organizational structure for implementing computations [9, 15, 19, 40, 51, 62]. They combine the generality of CPUs with the spatial computational style of hardware [19]. Reconfigurable systems use programmability and a regular fabric to reduce system complexity, cost, and development time.

## 1.2.2 The Internals of an FPGA

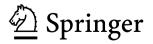

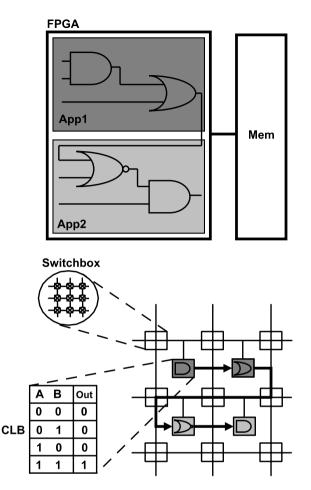

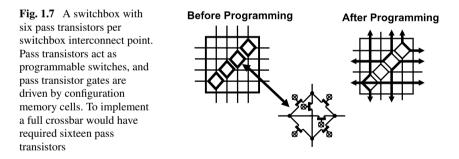

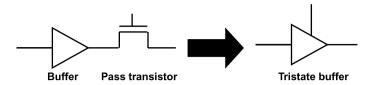

While there are many types of reconfigurable devices, FPGAs are the most common. FPGAs are configured by reprogramming logic at the *gate-level*, meaning that the device can be configured to look like any arbitrary set of interconnected logic gates. If a digital circuit schematic can be drawn for a design, then an FPGA is capable of emulating it. Physically, an FPGA is a collection of programmable gates embedded in a flexible interconnect, as shown in Fig. 1.1. These gates are implemented using lookup tables (LUTs) for computational units, flip-flops for timing, switchable interconnect for routing, and I/O blocks (IOB) for transferring data into and out of the device. Since any logic gate has a corresponding truth table, a circuit can be mapped to an FPGA by configuring the LUTs with the appropriate truth tables and by configuring bits in the switchboxes that specify which wires should be connected using pass transistors.<sup>1</sup> The data specifying how the LUTs and switchboxes should be programmed is referred to as a *configuration bitstream*.

The configuration of the FPGA may be stored in any number of ways. For example, FPGAs may use EPROM/EEPROM or antifuses (which are write-once technologies, meaning that the fuses are set and can never be unset). While many architectures make use of these write-once technologies, most architectures use SRAM as a programming point. The SRAM makes the FPGA volatile, meaning that it must be programmed every time that it is started up. Most importantly, SRAM allows for reconfiguration, which is the essence of reconfigurable computing. The SRAM programming bits are distributed across the entire FPGA, stored locally with the LUTs and switchable interconnects. While the large size of the internal configuration data may increase the amount of time required for reconfiguration, this has been partially mitigated through configuration caching and compression [33, 50].

Static RAM (SRAM) cells are built using two inverters and a couple of pass transistors (see Fig. 1.1). Data is stored or read from the SRAM cell as long as the

<sup>&</sup>lt;sup>1</sup>A transistor in which an input is not only applied to the gate but also to the drain. This technology reduces the number of transistors required to implement certain kinds of logic.

**Fig. 1.1** Architecture of a typical FPGA. Multiple Configuration Logic Blocks (CLBs) are islands surrounded by a sea of interconnect. Each CLB contains a Lookup Table (LUT) that is configured to implement a primitive logic gate. The interconnect is also configurable, and it connects CLBs together so that more complicated circuits can be composed from the primitive logic gates. The FPGA bitstream specifies the configuration of both the CLBs and the interconnect

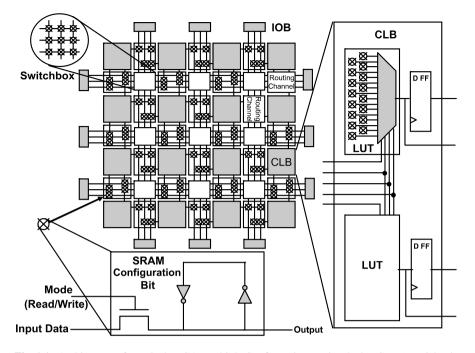

cell is powered. Without power, the SRAM cell loses its value. LUTs use SRAM cells as programming bits. A LUT is very generic because it can implement any logic gate: an *N*-input LUT can implement any *N*-input function. Although  $2^N$  bits are required to describe a LUT, it can implement  $2^{2^N}$  possible functions. Figure 1.2

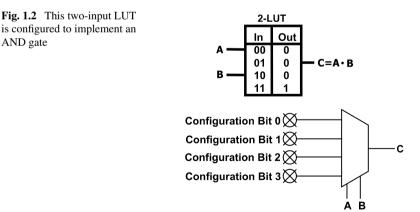

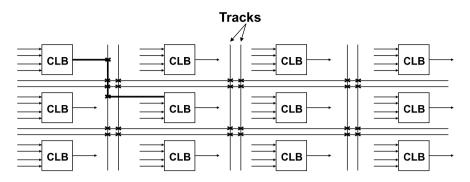

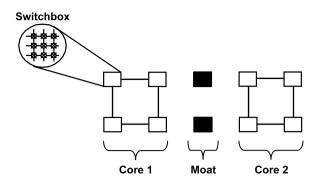

Fig. 1.3 FPGA interconnect architecture. Each CLB implements a primitive logic gate. More complex circuits are composed from primitive gates by connecting CLBs. The interconnect does the job of connecting the CLBs. Switch matrices are designed carefully because a full crossbar implementation would require  $N^2$  connections. Implementing memory logic in reconfigurable hardware is inefficient because memories, which can take on any value, require switch matrices that are full crossbars. For this reason, FPGAs embed hard-wired memory and even processors among the reconfigurable logic

shows an example of a LUT. The size of SRAM cells limits the number of inputs that a LUT may have. LUTs typically have 4–5 inputs, based on extensive empirical work on optimal size and other aspects of FPGA architecture [7]. Modern FPGA architectures are organized into larger regions known as configurable logic blocks (CLBs). A CLB is a complex block consisting of LUTs, multiplexers, and flip-flops. In addition, these CLBs may contain custom logic to help the most common circuit patterns (e.g., the carry chains in ripple carry adders) increase the performance of these particular circuits. While in recent years these CLBs have continued to grow slowly, the granularity of these blocks is still much smaller than even the smallest microprocessor.

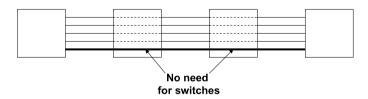

To connect the small computational blocks together, FPGAs employ an island style routing architecture. The generic island style architecture consists of two separate components for the routing architecture. The routing channel is a set of pass transistors that provide programmable connections into and out of the CLB. The switchbox provides point-to-point connections between neighboring routing channels, as shown in Figs. 1.3 and 1.4. Figure 1.5 shows how interconnect tracks are grouped into channels. Routing channels often contain *longlines*, which are used to span multiple CLBs in a row or column. The longlines create fast global connections between CLBs, which would otherwise have to pass through multiple, extremely slow switchboxes, as shown in Fig. 1.6. Figure 1.7 shows a switchbox is a different kind of switchbox that combines Hard-wired and Re-Programmable switches to increase routability [69]. Since resistance and capacitance increase quadratically in the length of the segment, longer routing segments are often driven by tri-state buffers, as shown in Fig. 1.8. The routing architecture is the major factor in both

**Fig. 1.4** Mapping the very simple circuit above to the FPGA fabric below. App1 consists of an AND gate and an OR gate, which are each mapped to a CLB. App2 consists of a NOR gate and an AND gate, which are each mapped to a CLB. The interconnect is configured such that the output of the AND gate of App1 is an input to the OR gate of App1; the output of the NOR gate of App2 is an input to the AND gate of App2; and the output of the OR gate of App1 is an input to the NOR gate of App2 gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App1 is an input to the NOR gate of App1 is an input to the NOR gate of App1 is an input to the NOR gate of App2 gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of the OR gate of App1 is an input to the NOR gate of App2 and the output of t

delay and area of the FPGA. Approximately 90% of the area of a typical FPGA is used for interconnect (the space is required for both the physical wires themselves, and the configuration bits necessary to connect those wires together to emulate arbitrary interconnection networks). While this interconnect is critical to configurability, it also complicates the building of a secure reconfigurable infrastructure, as later chapters will describe.

An FPGA is programmed using a bitstream: in many ways the bitstream is analogous to a binary executable in a traditional microprocessor system. The FPGA is configured with this binary data to perform a particular function. The bitstream

Fig. 1.5 Each logic element outputs one data bit, and the interconnect is programmable between elements. Interconnect tracks are grouped into channels

Fig. 1.6 Long segments only need switchbox connections at the end, therefore reducing the number of switches and therefore area

holds all parameters used to configure the FPGA, including the connections for the switchboxes and the data for the LUTs. Every bit in the bitstream corresponds to an SRAM configuration bit on the FPGA. To get a feel for the size of a typical bit-stream, consider the Xilinx XC2V6000. It requires roughly one million bits to program the LUTs, and fifteen million configuration bits that control the interconnect structure plus various control functions. Programming this device takes between one to three seconds, depending on the specific configuration interface (e.g., JTAG) and the internal clock cycle that the device supports, and programming can happen when the developers specify. Because the FPGA stores these bits in volatile memory, it is necessary to read this bitstream each and every time the device is powered up. As later chapters will describe, this is an attractive target for those looking to subvert the

Fig. 1.8 In the design of the FPGA fabric itself, buffers are often used with longer segments because resistance and capacitance increase quadratically in the length of the segment

FPGA-based system. Modifications to this bitstream will allow arbitrary changes to the implemented circuitry, and if the bitstream can be read directly, an unscrupulous person can simply copy the bitstream into another FPGA, giving them the ability to clone hardware at a very low cost.

#### 1.2.3 Design Flow

Usually when designing an FPGA-based system, the design flow is made to be very similar to that of a more traditional ASIC. The designs are typically developed in a hardware description language (such as VHDL or Verilog). These descriptions are then translated to a set of Boolean gates with the appropriate interconnect to route signals between them, at which point the design is typically tested with a variety of inputs. The CAD tools then translate these gates, packing them together into larger blocks, to logic functions which can map to the LUTs of the CLBs. The tools then determine the best place to locate these functional blocks across the chip (a step known simply as *placement*), and the routing between these blocks is calculated (known simply as *routing*). The design is then further analyzed to ensure that it is still correct and that it meets all the timing requirements. If there are problems with the functionality or timing, changes to the design or to the parameters given to the tools may be required. While this process has been used for a long time, ensuring correctness for large designs is a time-consuming endeavor. As such, most designs rely heavily on proprietary, *intellectual property* (IP) cores, which provide well-tested libraries that can be wired together to meet the demands of the specific application.

Code reuse, common in software engineering, is also used in designing reconfigurable systems in order to achieve cost savings and to reduce time to market. Designing a full system from scratch is not commonly done due to the high cost and development time. A commonly reused module is a soft CPU core, like the Micro-Blaze. A soft-processor is a bitstream that implements a general-purpose processor's functionality on an FPGA. An example of composing a reconfigurable system would be to combine a soft-processor with other hard or soft IP cores, such as an AES core for crypto and an Ethernet core for networking.<sup>2</sup> The provenance of a core has im-

<sup>&</sup>lt;sup>2</sup>Companies protect their intellectual property fiercely due to the high cost of designing hardware modules. Later chapters discuss several schemes to prevent the theft of IP cores from FPGAs.

portant security implications: was it developed in-house or purchased from a third party? Was it generated by a tool such as Base System Builder or downloaded from an open-source web site like opencores.org? While formal verification of crypto cores is a useful technique [49], determining whether an arbitrary hardware module is malicious is a non-computable problem, as it is with arbitrary software programs. For example, a core created by a malicious hardware designer or compromised design tool flow can exploit low-level hardware mechanisms to snoop on or disrupt system logic. Since a typical design contains millions of logic gates and ten times as many connections, designers need a way to compose trustworthy systems using multiple commodity cores on a single device without having to design each core from scratch (building everything from scratch is no guarantee of success either). Formal verification of the security of a large, complex design is a rigorous, expensive process, requiring access to the blueprints (e.g., HDL source) of all of the cores used in the design. Access to the HDL source might not be possible if it is a trade secret. Furthermore, formal verification is no silver bullet because of scalability issues. In addition, there can be a flaw in the mathematical model of the system, and there can even be a flaw in the mathematical proof applied to the model. Beware of claims that a system is *provably secure*. Flaws are frequently discovered in crypto ciphers that mathematicians "proved" to be secure [8].

*Design Tip: Tools and Cores.* An important aspect of reconfigurable system development is considering the provenance of design tools and IP, especially tools and cores downloaded from public web sites. It is a good idea to assess the security of development machines and code repositories. Later chapters will cover configuration control.

A typical FPGA-based embedded system consists of distinct cores residing on the same chip. Reconfigurable logic, hard-wired computational cores, and hard-wired SRAM and BRAM all reside on the same FPGA and can share the same off-chip memory. In many cases, cores must not be able to interfere with each other or snoop on each other via shared resources such as off-chip memory and on-chip memory and busses. As a result, the secure design of an FPGA system is challenging.

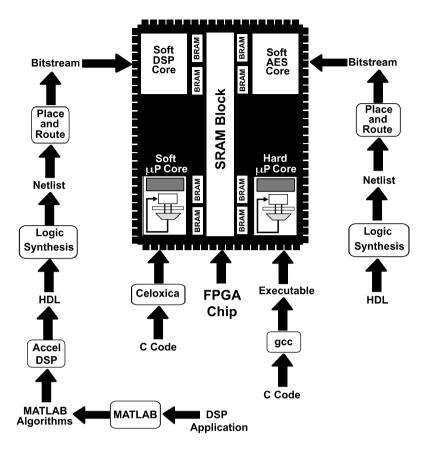

Figure 1.9 shows four possible embedded system design flows that can occur on the same FPGA:

- Logic synthesis transforms HDL code to a netlist, which is then converted to a bitstream by a process called *place and route*.

- An Electronic System Level (ESL) design tool like Celoxica transforms code written in C, a high-level programming language, to a soft processor core.

- Another ESL design flow uses AccelDSP [34] from Xilinx to convert MAT-LAB [52] algorithms to HDL, which can be converted to a custom DSP core.

- A C compiler translates code written in a high-level programming language to an executable, which is executed on a hard-wired processor core.

**Fig. 1.9** A Modern FPGA-based Embedded System: Distinct cores with varying provenance reside on the same chip. Complex tool chains are used to generate cores. An AES core can be the result of transforming HDL code to a netlist to a bitstream. A DSP core can be result of transforming a DSP application to MATLAB algorithms to HDL to a netlist to a bitstream. This is an example of Electronic System Level (ESL) Design. Celoxica is another ESL design flow that transforms C code to a soft processor core. Finally, a C compiler such as gcc can transform C code to an executable, which can run on a hard-wired processor core

These tool chains represent difficult security vulnerabilities because tools are designed by many different companies and individuals. In addition to the provenance of tools, the provenance of soft IP cores, such as an AES crypto core, are also a major and challenging security concern. Cores can come in the form of HDL (e.g., Verilog), netlist,<sup>3</sup> or bitstream. They can be designed by a person or generated by tools.

The Xilinx ML507 evaluation platform is a real-world example of a development board that comes with a DVD of tools representing multiple types of design flows.

<sup>&</sup>lt;sup>3</sup>A list of logical gates and their interconnections.

The ML507 has a Virtex-5 FXT FPGA with both reconfigurable logic and a hardwired PowerPC processor core on the same chip, and Xilinx provides an Integrated Synthesis Environment (ISE) tool for generating bitstreams from HDL. The Embedded Development Kit (EDK) [78] tool is used to create a custom processor, allowing designers to connect their own hardware modules or other peripherals to a processor. The EDK also allows designers to configure the processor (e.g., by changing the frequency, cache size, etc.) The EDK also provides an integrated Eclipse-based Software Development Kit (SDK) for compiling and debugging the software to be run on the hard-wired PowerPC core or even on a soft MicroBlaze processor core.

Since these various design flows generate a design consisting of multiple interacting cores, the resulting embedded system may only be as trustworthy as the least trustworthy design flow, depending on the security architecture. For example, protection primitives are needed to isolate crypto cores so that secret keys cannot be compromised. Just as a subverted compiler can produce malicious code, subversion of hardware design tools can produce malicious hardware modules. Widely used design tools (e.g., Xilinx, Altera, and Actel) lack the ability to ensure that their output does not include malicious functionality. Furthermore, proving that a compiler or hardware design tool does not introduce malicious functionality is an open problem, at least as difficult as determining whether an arbitrary computer program or hardware module does something malicious.

## **1.3 The Many Facets of FPGA Security**

As economics drives the growing use of FPGAs in critical systems, designers are forced to consider security, but practitioners currently lack a set of design practices to follow. In addition, providing security is made more difficult by the resource constraints in embedded systems [44]. In addition to applications of reconfigurable devices to security processing, researchers are beginning to think about the security of reconfigurable systems themselves. Since hardware designs can be copied from fielded systems, industry has invested heavily in developing methods to protect their intellectual property [11, 42, 47] and to ensure that FPGAs can only be updated by authorized parties [1, 31, 32]. However, only a few researchers have thought about malicious hardware modules on FPGAs [30]. Both Thomas Wollinger and Saar Drimer have written excellent, thorough survey papers on the subject of FPGA design security [22, 76]. Our survey papers were published in [35, 39]. Chapter 4 discusses bitstream encryption and authentication in greater detail.

A variety of attacks against FPGAs are possible. In a covert channel attack, a shared resource is used as a means of illicit communication. For example, power consumption can be modulated by a malicious core in order to send secrets to another core that observes these fluctuations [73]. Some FPGAs support remote updates of the bit-stream, and it is essential that only authorized parties be allowed to apply these updates. Otherwise, attackers could upload malicious logic that modifies the system's behavior or damages the chip by configuring the FPGA with a

short-circuit [30]. While encryption [11, 41, 42], fingerprinting, [46], and watermarking [47] help to prevent IP theft, more is needed to counter covert channel attacks, side channel attacks, and to understand malicious hardware.

#### 1.3.1 Security Is Hard

Computer security is a hard problem. Every year, the number of attacks increases despite increased spending on security. Commodity operating systems typically use a frustrating penetrate-and-patch approach, an endless cycle in which hackers compromise machines, vendors release a patch, and the hackers find and exploit new vulnerabilities. Ideally, systems should be built to be secure from the beginning, but designing a large, complex, highly trustworthy system is extremely challenging. There are no silver bullets: each security technique has its unique advantages and disadvantages. A principle-driven design and implementation strategy uses multiple complementary security concepts and techniques in concert. The goal is to increase the risk and cost for the adversary and to make attackers work hard to compromise each machine individually. Otherwise, systems can fall like dominoes once one is compromised. Relying on a single technique is akin to a Maginot Line of defense: attackers will simply take the path of least resistance to go around the Line. Systems that overly rely on the notion of a single method to create a security perimeter will encounter serious problems when the perimeter is violated. System designers should also beware of assuming that resources are safe within the perimeter.

Cryptography is a prime example of a security technique with advantages and limitations. Using crypto does not necessarily make a system secure: crypto needs to be used *properly*. Key length needs to be sufficiently long to resist a brute-force attack. Crypto processors must be designed carefully so that attackers cannot easily determine the key using a side channel attack. Keys need to be managed properly and stored securely. Ciphertext and plaintext must never mix. Flaws are occasionally found in the crypto algorithms, despite mathematical proofs of their security.

Design Tip: Apply Comprehensive Security Principles. Don't rely on a single security strategy. Each technique has advantages and limitations. Don't assume that attackers will not be able to breach arbitrary security perimeters. Just because a system uses crypto doesn't mean it's secure: keys need to be managed properly, keys need to have sufficient entropy, and the crypto mechanisms must be implemented correctly. The history of code making and code breaking tells us that there is no such thing as an unbreakable cipher. Keys that are sufficiently long today may not be sufficient in the future. Don't assume that just because data is encrypted that it will never be decrypted in the future. Finally, don't assume that you can protect your system by combining several weak security mechanisms.

#### 1.3.2 Complexity and Abstraction

One reason that security is very difficult is the size and complexity of systems. Formal security analysis works best when applied to small, simple components. As complexity increases, so does the effort required for security analysis. This growth in complexity can be exponential in the size of the target of analysis. Furthermore, two components that are secure independently might not be secure when combined. One approach to get a grip on this complexity is to use abstraction. Another way to manage complexity is to limit what the user can do. For example, an ATM has a limited interface with a small number of buttons: every possible combination of keystrokes can be analyzed to determine whether they lead to an insecure state. Even so, ATM security has been repeatedly breached in the past [3].

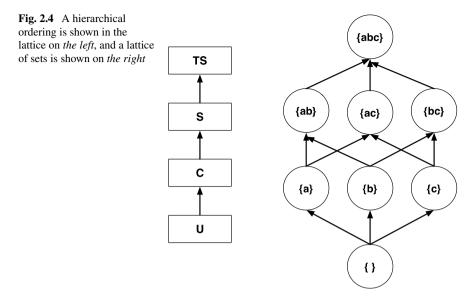

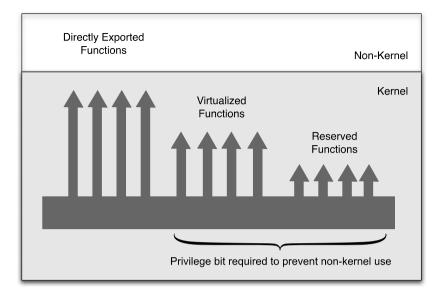

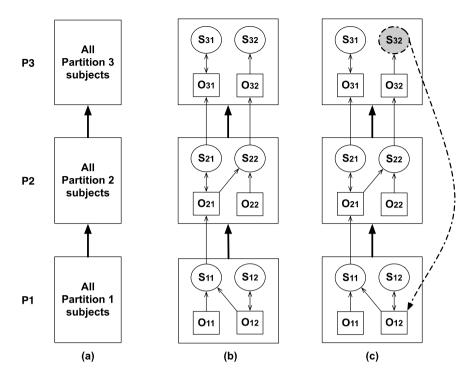

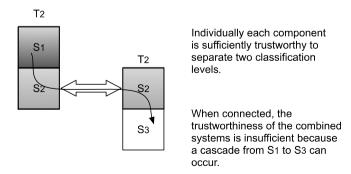

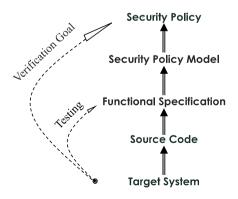

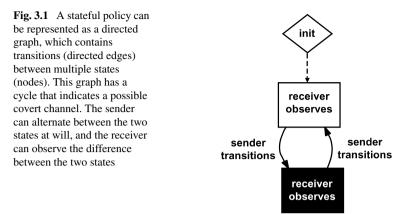

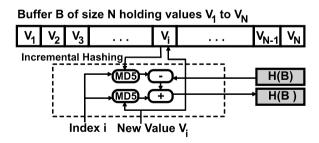

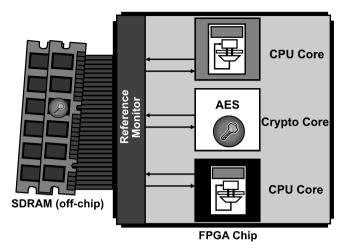

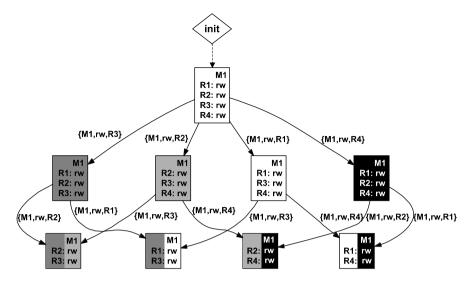

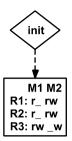

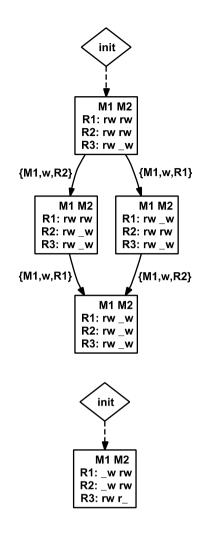

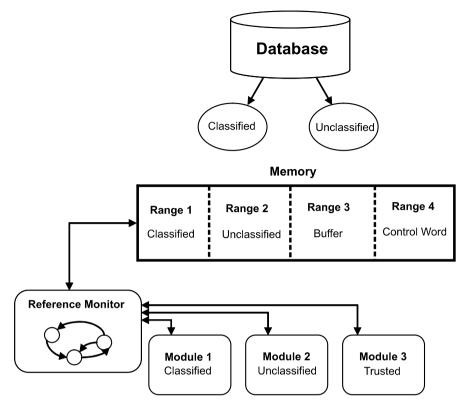

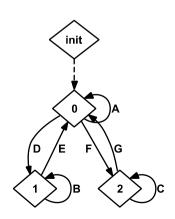

A holistic approach to system security considers how the FPGA fits into a larger system. A large, complex system is composed at several different layers of abstraction: the chip level includes the components on a single FPGA device, and the board level includes the chips soldered onto a circuit board. Larger systems (e.g., a personal computer) can be composed of multiple circuit boards connected by a motherboard, which in turn can be connected by a computer network (e.g., Ethernet) to form systems-of-systems. The composition problem refers to the fact that two systems that behave in a secure manner by themselves do not necessarily behave securely when put together. This is especially frustrating for large design projects that must build systems from both trusted components and commercial off-the-shelf (COTS) components: reuse of commodity components is an important aspect of building large, complex systems. A security architecture is a technique for reasoning at a high level of abstraction about the composition of system elements, including computational and security components. A system can be designed to enforce a security policy by organizing the components using a security architecture, configuring the security mechanisms properly, and ensuring that all components conform to a well-defined interface.