Semiconductor Materials and Devices Series

# Stephen E. Saddow Anant Agarwal editors

# Advances in Silicon Carbide Processing and Applications

...

# Advances in Silicon Carbide Processing and Applications

For a listing of recent related titles, turn to the back of this book.

# Advances in Silicon Carbide Processing and Applications

Stephen E. Saddow Anant Agarwal

Editors

Artech House, Inc. Boston • London www.artechhouse.com

#### Library of Congress Cataloguing-in-Publication Data

A catalog record for this book is available from the Library of Congress.

#### British Library Cataloguing in Publication Data

Advances in silicon carbide processing and applications.—(Artech House semiconductor materials and devices library).

1. Silicon carbide 2. Silicon carbide—Industrial applications

I. Saddow, Stephen E. II. Agarwal, Anant 321.3'8152

ISBN 1-58053-740-5

Cover design by Igor Valdman

© 2004 ARTECH HOUSE, INC. 685 Canton Street Norwood, MA 02062

All rights reserved. Printed and bound in the United States of America. No part of this book may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without permission in writing from the publisher.

All terms mentioned in this book that are known to be trademarks or service marks have been appropriately capitalized. Artech House cannot attest to the accuracy of this information. Use of a term in this book should not be regarded as affecting the validity of any trademark or service mark.

International Standard Book Number: 1-58053-740-5

10 9 8 7 6 5 4 3 2 1

To our wives, Karen and Suman, for their love and patience

# Contents

| Pref  | face                                             | X                |

|-------|--------------------------------------------------|------------------|

| Ack   | nowledgments                                     | xiii             |

|       |                                                  |                  |

|       | IAPTER 1                                         |                  |

| Silic | con Carbide Overview                             | 1                |

| 1.1   | General Properties                               | 1                |

|       | 1.1.1 Mechanical and Chemical Properties         | 2                |

|       | 1.1.2 Bandgap                                    | 2<br>2<br>2<br>3 |

|       | 1.1.3 Critical Field                             | 2                |

|       | 1.1.4 Saturated Drift Velocity                   | 3                |

|       | 1.1.5 Thermal Conductivity                       | 3                |

|       | 1.1.6 Figures of Merit                           | 4                |

| 1.2   | History                                          | 4                |

|       | 1.2.1 Berzelius and Acheson                      | 4                |

|       | 1.2.2 The Discovery of Polytypism                | 6                |

|       | 1.2.3 The First LED and the Lely Process         | 6                |

|       | 1.2.4 The Lost Decades                           | 7<br>7           |

|       | 1.2.5 The Second Wave                            |                  |

|       | 1.2.6 The Third Wave                             | 7                |

| 1.3   | Crystalline Structure                            | 8                |

|       | 1.3.1 Basic Structure                            | 8                |

|       | 1.3.2 Polytypism                                 | 8                |

|       | 1.3.3 Impurities in Different Polytypes          | 9                |

| 1.4   | Crystal Growth                                   | 11               |

|       | 1.4.1 Seeded Sublimation Growth                  | 11               |

|       | 1.4.2 High Temperature Chemical Vapor Deposition | 14               |

| 1.5   | Epitaxial Growth                                 | 18               |

|       | 1.5.1 Chemical Vapor Deposition                  | 18               |

| 1.6   | Defects                                          | 21               |

|       | 1.6.1 Micropipes                                 | 21               |

|       | 1.6.2 Stacking Faults                            | 22               |

| 1.7   | Commercial Outlook                               | 22               |

|       | 1.7.1 High-Frequency Applications                | 23               |

| 1.8   | Summary                                          | 25               |

|       | References                                       | 26               |

# CHAPTER 2

| High  | n-Temperature SiC-FET Chemical Gas Sensors                        | 29 |

|-------|-------------------------------------------------------------------|----|

| 2.1   | Introduction                                                      | 29 |

| 2.2   | Detection Mechanism of Field-Effect Gas Sensors                   | 30 |

|       | 2.2.1 Gas Sensing Principle                                       | 30 |

|       | 2.2.2 Detection of Different Molecules                            | 31 |

|       | 2.2.3 Influence of Oxygen                                         | 34 |

|       | 2.2.4 Influence of Different Metals                               | 35 |

|       | 2.2.5 Influence of Temperature                                    | 36 |

|       | 2.2.6 Sensor Arrays                                               | 36 |

| 2.3   | Field-Effect Chemical Gas Sensor Devices                          | 38 |

|       | 2.3.1 Capacitors                                                  | 38 |

|       | 2.3.2 Schottky Diodes                                             | 38 |

|       | 2.3.3 The P-N Junction Diode                                      | 43 |

|       | 2.3.4 Field-Effect Transistors                                    | 44 |

| 2.4   | Sensor Properties at Elevated Temperatures, Influence of Hydrogen | 49 |

|       | 2.4.1 Influence of Hydrogen on Capacitors                         | 50 |

|       | 2.4.2 Influence of Hydrogen on Schottky Diodes                    | 51 |

| 2.5   | More Sensor Properties                                            | 53 |

|       | 2.5.1 Speed of Response                                           | 53 |

|       | 2.5.2 Long-Term Stability                                         | 56 |

| 2.6   | Experimental                                                      | 57 |

|       | 2.6.1 Sample Preparation                                          | 57 |

|       | 2.6.2 Gate Metal Deposition                                       | 57 |

|       | 2.6.3 Mounting                                                    | 58 |

|       | 2.6.4 Device Operation                                            | 58 |

| 2.7   | 11                                                                | 59 |

|       | 2.7.1 Petrol Engine Exhausts                                      | 59 |

|       | 2.7.2 Diesel Engine Exhausts                                      | 60 |

|       | 2.7.3 Flue Gas Monitoring                                         | 61 |

| 2.8   | Outlook and Conclusions                                           | 62 |

|       | Acknowledgments                                                   | 63 |

|       | References                                                        | 63 |

| CH    | APTER 3                                                           |    |

| Silic | on Carbide Technology and Power Electronics Applications          | 69 |

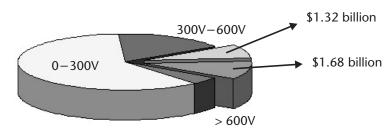

| 3.1   | DC-DC Conversion                                                  | 69 |

|       | 3.1.1 SMPC Circuit Topologies and Operation                       | 70 |

|       | 3.1.2 Silicon Carbide Devices in SMPC Applications                | 73 |

|       | 3.1.3 Other SiC Switches                                          | 78 |

|       | 3.1.4 SiC AC-DC Inverter Example                                  | 79 |

| 3.2   | DC-AC Power Conversion                                            | 80 |

|       | 3.2.1 DC-AC Power Inverter                                        | 80 |

|       | 3.2.2 Inverter Control Techniques                                 | 81 |

|       | 3.2.3 SiC DC-AC Inverter Example                                  | 82 |

| 3.3   | Pulsed-Power Applications                                         | 91 |

|       | 3.3.1 Thyristor Basics                                            | 92 |

|       |                                                                   |    |

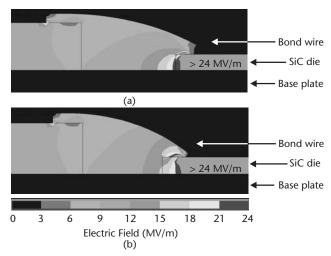

| 3.4 | 3.3.2 Evaluation of SiC Thyristors for Pulsed-Power Switching<br>Thermal Management and High-Voltage Packaging | 94<br>97 |

|-----|----------------------------------------------------------------------------------------------------------------|----------|

| Ј.т | 3.4.1 Hybrid Si-SiC Half-Bridge Module                                                                         | 98       |

|     | 3.4.2 Implementation Analysis of a High-Voltage SiC Bridge                                                     | 20       |

|     | Rectifier Module                                                                                               | 100      |

|     | 3.4.3 Electrostatic Analysis of a High-Voltage Package for SiC                                                 |          |

|     | Devices                                                                                                        | 103      |

| 3.5 |                                                                                                                | 106      |

|     | References                                                                                                     | 106      |

| СН  | APTER 4                                                                                                        |          |

|     | ances in Selective Doping of SiC Via Ion Implantation                                                          | 109      |

| 4.1 | Introduction                                                                                                   | 109      |

| 4.2 | As-Implanted Profiles                                                                                          | 114      |

|     | 4.2.1 Diagnostic Techniques                                                                                    | 114      |

|     | 4.2.2 Random Implants                                                                                          | 115      |

|     | 4.2.3 Channeled Implants                                                                                       | 124      |

| 4.3 | 1 0                                                                                                            | 128      |

|     | 4.3.1 Annealing Concepts                                                                                       | 128      |

|     | 4.3.2 Silane Overpressure Annealing Process                                                                    | 130      |

|     | 4.3.3 Implanted Ion Profiles After Annealing                                                                   | 136      |

|     | 4.3.4 Defect Evolution                                                                                         | 140      |

|     | 4.3.5 Results of Electrical Activation                                                                         | 143      |

| 4.4 | Technology Barriers and Suggestions for Future Work                                                            | 147      |

|     | References                                                                                                     | 148      |

|     | APTER 5                                                                                                        |          |

| Pow | ver SiC MOSFETS                                                                                                | 155      |

| 5.1 |                                                                                                                | 155      |

| 5.2 | SiC UMOSFET                                                                                                    | 156      |

| 5.3 | SIC DIMOSFET                                                                                                   | 163      |

| 5.4 | SiC LDMOS                                                                                                      | 169      |

| 5.5 | Summary and Future Development                                                                                 | 171      |

|     | References                                                                                                     | 172      |

| CH  | APTER 6                                                                                                        |          |

| Pow | er and RF BJTs in 4H-SiC: Device Design and Technology                                                         | 177      |

| 6.1 | Introduction                                                                                                   | 177      |

| 6.2 | Device Structures and Operation of Power BJTs                                                                  | 177      |

| 6.3 | Design of the Epitaxial Power BJT                                                                              | 181      |

|     | 6.3.1 Design of the Collector Layer                                                                            | 181      |

|     | 6.3.2 Design of the Base Layer                                                                                 | 183      |

|     | 6.3.3 Design of the Unit Cell                                                                                  | 184      |

| 6.4 | Process Integration                                                                                            | 186      |

|     | 6.4.1 Process Sequence                                                                                         | 186      |

| 6.5 | 1.2-kV Power BJTs                                                                                              | 188      |

| 6.6 | Design and Fabrication of UHF Transistors                                                                      | 192      |

| 6.7 Future Work<br>References | 199<br>200 |

|-------------------------------|------------|

| About the Editors<br>Index    | 203<br>205 |

# Preface

Recently there have been numerous books written on SiC, which is a testament to the importance of this technology and its potential impact on society. A majority of these books attempt to comprehensively cover a specific aspect of the technology and do this by a set of in-depth chapters on a particular research topic, concept, or result. While this is an excellent means to convey important aspects of the technology, the intent of Advances in Silicon Carbide Processing and Applications is to be less expansive and focus in on two of the most promising applications of SiC technology: gas and chemical sensing and electric vehicle motor drive and control. Having made this decision, we realized that the underlying device and processing issues that enable these application areas to be served by SiC technology should also be addressed. Hence a major portion of the book involves aspects of SiC technology in this key area, again with the intent (and hope) that the reader will be able to gain a broad and deep insight into the pacing issues of the technology as of this date. While there is no way to predict the wisdom of this strategy a priori, we have nonetheless tried to put ourselves into the shoes of potential readers of this book and carefully selected chapter topics that would best support this strategy.

We hope that all who read this book will benefit from the somewhat different approach we have taken. We begin with an overview of SiC as of 2003, with an attempt to provide some predictions as to the market for the technology. We then immediately jump into the application chapters, first on gas sensors, which is clearly an area where SiC can gain a significant market share compared with traditional Si technology, followed by advances in electric motor drive where, again, SiC clearly has an advantage over Si due to its robust material properties. We then step back and discuss the all-important area of SiC ion implantation technology—this is key since the properties of the SiC lattice precludes the use of thermal diffusion to achieve planar selective doping over the surface of single-crystal wafers. After discussing this topic, we then finish up with a discussion of recent advances in both SiC MOS and bipolar technology, both of which directly impact the sensor and motor drive applications. Attention was made to provide a large number references in the recognition that no single book can be fully exhaustive of such a broad subject such as SiC.

# Acknowledgments

It is with the most sincere gratitude that the editors of this book thank all of the chapter authors for their dedication and hard work in bringing this idea to fruition. Just as a work of art can be immediately appreciated by the viewer, without any understanding of the efforts expended to bring it about, so too is a well-written book easy to appreciate by the reader without an appreciation of the long hours of hard work that is involved. Special thanks go to our colleagues who reviewed specific chapters of the book; their contribution has certainly improved the quality of each chapter. In particular, we thank John Wolan of the University of South Florida for his review of Chapter 2, Omar Manasreh for his review of Chapter 3, Nelson Saks of the Naval Research Laboratory for his review of Chapter 4, and Paul Chow of RPI for his review of Chapter 6. We wish to thank all of the SiC pioneers who have come before us and all of the present researchers in the field who have pushed the technology to the point where such a book project was warranted. Stephen E. Saddow would like to personally thank all of his current and former students, especially in the SiC Group at the University of South Florida, for all of their dedication and hard work that made this book possible.

> Stephen E. Saddow Tampa, Florida

Anant Agarwal Durham, North Carolina June 2004

# Silicon Carbide Overview

Olle Kordina and Stephen E. Saddow

# 1.1 General Properties

Silicon carbide (SiC) is a semiconductor material with highly suitable properties for high-power, high-frequency, and high-temperature applications. This almost worn-out opening statement may be found in many papers dealing with SiC. Yet, it cannot be left out because it really brings forward the essence of the material's potential. Silicon carbide is a wide bandgap semiconductor material with high breakdown electric field strength, high saturated drift velocity of electrons, and a high thermal conductivity. In combination with these properties, a native substrate of reasonable size exists, and one may readily grow the material and dope it both nand p-types. In addition, SiC, like silicon (Si), has SiO, as its stable, native oxide. This fact is often overlooked but is key to any semiconductor technology, both from a processing perspective as well as opening up metal-oxide-semiconductor (MOS) device opportunities for SiC. Therefore, these properties make SiC ideally suited for a vast number of applications. In this chapter, we will discuss more details of these exciting properties and provide a realistic assessment of the material's challenges that are actively being studied to date. Indeed, one has to recognize that the unique properties of SiC-its robust structure, wide bandgap, high-temperature stability and so forth-also make it a challenge to manufacture and process into working devices. Although these challenges are not insurmountable, one needs to be aware of their implications before deciding to choose SiC as the technology for a particular application.

Therefore, the purpose of this book is to provide the reader with a realistic assessment of SiC as a technology one might select for a given application of interest. In this chapter, we will review material issues related to bulk and thin-film growth of SiC and then discuss some interesting applications of SiC. This will be followed by a discussion of one of the key process technologies that is absolutely essential to SiC—selective doping via ion implantation. We will then provide an update of several key device technologies ranging from power electronic switch development to MOS transistors and finally high-power radio frequency (RF) and bipolar devices.

The industrial application of SiC began with the blue light emitting diode (LED), which was very weak due to the indirect bandgap of SiC but was the only commercial blue electroluminescent light source at the time (the late 1980s). The SiC blue LED was soon surpassed in intensity by the gallium nitride (GaN)-based

LED due to the direct bandgap of the III-nitrides. However, due to the lack of a native substrate for GaN, sapphire or SiC substrates were and are still used. The biggest use of semiconductor-grade SiC is still for LEDs, but now it serves the role as the substrate for the active GaN layer rather than both the substrate and the active layer. Today there are high-frequency metal-semiconductor-field effect transistors (MES-FETs) offered commercially, as well as an emerging market for Schottky diodes made from SiC. We are still at the beginning of the SiC revolution, however, and the material's full potential has yet to be realized.

# 1.1.1 Mechanical and Chemical Properties

Silicon carbide is a very hard substance with a Young's modulus of 424 GPa [1]. It is chemically inert and reacts poorly (if at all) with any known material at room temperature. The only known efficient etch at moderate temperatures is molten KOH at 400–600°C. It is practically impossible to diffuse anything into SiC. Dopants need to be implanted or grown into the material. Furthermore, it lacks a liquid phase and instead sublimes at temperatures above 1,800°C. The vapor constituents during sublimation are mainly Si, Si<sub>2</sub>C, and SiC<sub>2</sub> in specific ratios, depending on the temperature.

# 1.1.2 Bandgap

The bandgap varies depending on the polytype between 2.39 eV for 3C-SiC to 3.33 eV for 2H-SiC [2]. The most commonly used polytype is 4H-SiC, which has a bandgap of 3.265 eV [2]. The wide bandgap makes it possible to use SiC for very hightemperature operation. Thermal ionization of electrons from the valence band to the conduction band, which is the primary limitation of Si-based devices during hightemperature operation, is not a problem for SiC-based devices because of this wide bandgap.

# 1.1.3 Critical Field

For power-device applications, perhaps the most notable and most frequently quoted property is the breakdown electric field strength,  $E_{max}$ . This property determines how high the largest field in the material may be before material breakdown occurs. This type of breakdown is obviously referred to as catastrophic breakdown. Curiously, the absolute value of  $E_{max}$  for SiC is frequently quoted as the relative strength of the  $E_{max}$  against that of Si. Most discussions on this subject note that  $E_{max}$  of SiC is 10 times that of Si. As with Si, there exists a dependence of  $E_{max}$  with doping concentration. Thus, for a doping of approximately 10<sup>16</sup> cm<sup>-3</sup>,  $E_{max}$  is 2.49 MV/cm, according to a study by Kostantinov et al. [3]. For Si, the value of  $E_{max}$  is about 0.401 MV/cm for the same doping [4]. As can be seen, the value for SiC is only about a factor of six higher than that of Si and not the often-claimed 10 times higher critical field strength. Why the discrepancy? It is more correct to compare the critical strengths between devices made for the same blocking voltage. Thus, an Si device constructed for a blocking voltage of 1 kV would have a critical field strength of the strength.

about 0.2 MV/cm, which should be compared with the 2.49 MV/cm of SiC. This is where the order of magnitude larger breakdown field spec comes from.

# 1.1.4 Saturated Drift Velocity

For high-frequency devices, the breakdown electric field strength is not as important as the saturated drift velocity. In SiC, this is  $2 \times 10^7$  cm/sec [5, 6], which is twice that of Si. A high-saturated drift velocity is advantageous in order to obtain as high-channel currents as possible for microwave devices, and clearly SiC is an ideal material for high-gain solid-state devices.

# 1.1.5 Thermal Conductivity

The second most important parameter for power and high-frequency device applications is the material's thermal conductivity. An increase in temperature generally leads to a change in the physical properties of the device, which normally affects the device in a negative way. Most important is the carrier mobility, which decreases with increasing temperature. Heat generated through various resistive losses during operation must thus be conducted away from the device and into the package.

It is often quoted that the thermal conductivity of SiC is higher than that of copper at room temperature. There are even claims that it is better than any metal at room temperature [7]. The thermal conductivity of copper is 4.0 W/(cm-K) [8]. That of silver is 4.18 W/(cm-K) [8]. Values of the thermal conductivity as high as 5 W/(cm-K) have been measured by Slack [9] on highly perfect Lely platelets.

More detailed studies have been made where the thermal conductivity in the different crystal directions have been determined for SiC (see Table 1.1 [5]). As can be seen, there is a dependence on the purity of the crystal as well as on the crystal direction. At the time of this study, the material was not of the high quality we see today, and more sophisticated techniques have been developed to measure thermal conductivity. Thus, as higher-quality material has been grown, values close to the theoretical values have been measured using the laser flash technique [10].

High-purity semi-insulating (SI) SiC material has the highest reported thermal conductivity with a value of 4.9 W/(cm-K). Lower values are measured for the doped crystals but they are all above 4 W/(cm-K) at room temperature [10].

| Sample<br>Type | Direction | Carrier<br>Concentration<br>(cm <sup>-3</sup> ) | Thermo<br>(W/cm<br>298K | al Conductivity<br>K)<br>373K |

|----------------|-----------|-------------------------------------------------|-------------------------|-------------------------------|

| 4H SI          | // c      | SI                                              | 3.3                     | 2.6                           |

| 4H n           | // c      | 2.0 E18                                         | 3.3                     | 2.5                           |

| 4H n           | ⊥c        | 5 E15                                           | 4.8                     | 2.9                           |

| 6H n           | // c      | 1.5 E18                                         | 3.0                     | 2.3                           |

| 6H n           | // c      | 3.5 E17                                         | 3.2                     | 2.3                           |

| 6H n           | ⊥c        | 3.5 E17                                         | 3.8                     | 2.8                           |

| 6H p           | ⊥c        | 1.4 E16                                         | 4.0                     | 3.2                           |

| Slack          | ⊥c        | ~ 1 E17                                         | ~ 5                     | ~ 3                           |

| Source: [5]    |           |                                                 |                         |                               |

Table 1.1 The Thermal Conductivity of SiC

# 1.1.6 Figures of Merit

There have been several attempts to summarize the importance of various material properties to enable comparisons between materials for high-frequency and highpower applications. Johnson suggested a figure of merit, the so-called Johnson Figure of Merit (JFOM), which considers the potential power handling and highfrequency capability of a device. The JFOM takes into account the critical field and saturated drift velocity, as shown in the following equation [11].

$$JFOM = \frac{E_B^2 v_{sat}^2}{4\pi^2}$$

(1.1)

where  $E_{\rm B}$  and  $v_{\rm set}$  are the breakdown field and saturated drift velocity, respectively. Unsatisfied with the JFOM ability to take the material's thermal properties into account, which, as mentioned, are specifically apparent during high-frequency operation, Keyes proposed another figure of merit, the Keyes Figure of Merit (KFOM) [12]:

$$KFOM = \kappa \sqrt{\frac{cv_{sat}}{4\pi\varepsilon}}$$

(1.2)

where  $\kappa$ , c, and  $\varepsilon$  are the thermal conductivity, the speed of light in vacuum, and the dielectric constant, respectively.

Unfortunately, neither of these equations is particularly accurate for power devices and consequently Baliga proposed a figure of merit for low-frequency applications, called the Baliga Figure of Merit (BFOM) [13]:

$$BFOM = \varepsilon \mu E_B^3 \tag{1.3}$$

where  $\mu$  is the carrier low-field mobility. In Table 1.2, the figures of merit for the two most common SiC polytypes are compared with Si and GaAs. All values are normalized to Si.

#### 1.2 History

#### 1.2.1 Berzelius and Acheson

Jöns Jacob Berzelius is mostly known for his discovery of Si; however, he was the first person who more than likely synthesized SiC. In 1824 he published a paper where he speculated that there was a chemical bond between Si and carbide (C) in

| and the Two Most Common SiC Polytypes<br>(Values Are Normalized to Si) |       |      |       |  |

|------------------------------------------------------------------------|-------|------|-------|--|

| Material                                                               | JFOM  | KFOM | BFOM  |  |

| Si                                                                     | 1     | 1    | 1     |  |

| GaAs                                                                   | 9     | 0.41 | 22    |  |

| 6H-SiC                                                                 | 900   | 5.0  | 920   |  |

| 4H-SiC                                                                 | 1,640 | 5.9  | 1,840 |  |

Table 1.2

Figures of Merit for Si, GaAs,

one of the samples he had produced [14]. Berzelius was born just outside of Linköping in Sweden, which is interesting to point out because the center of SiC research in Sweden is at the University of Linköping.

Years later, two inventors, Eugene and Alfred Cowles, invented the electric smelting furnace in 1885 [15]. This furnace was adopted by Acheson to produce suitable minerals that could substitute diamond as an abrasive and cutting material [16]. Acheson mixed coke and silica in the furnace and found a crystalline product characterized by a great hardness, refractability, and infusibility, which was shown to be a compound of carbon and silicon. Acheson called his product "carborundum" and gave it the proper formula SiC. It is interesting to note that Acheson made the first SiC for abrasive applications near the city of Pittsburgh in Pennsylvania before he moved the operation to Niagara Falls due to the better availability of electric power. Today, Pittsburgh is another center for SiC research, with the University of Pittsburgh and Carnegie Mellon University spearheading the research in the United States.

The Acheson process sometimes also includes sawdust and salt in lesser amounts together with the coke and silica. The sawdust creates channels that help impurities escape and the salt creates free chorine, which reacts with metal impurities that become volatile. Thus, the means to purify synthetic SiC have been employed since the beginning.

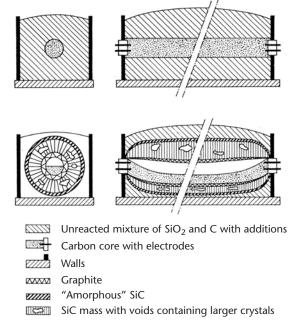

In the reacted mass of SiC, there are also voids or pockets that are characterized by the fact that they are lined with hexagonal-looking crystals, as illustrated in Figure 1.1. These pockets have a uniform thermal environment but with a slight gradient toward the center of the void. The environment favors growth of crystals that is close to homogeneous. The crystals are only attached in one point to the sides of the void and grow toward the center. These crystal flakes are called platelets. We

**Figure 1.1** The Acheson process. The figure also shows the voids in which Acheson found the SiC crystals. (*From:* [17]. © 1963 Philips. Reprinted with permission.)

will discuss later the Lely process that produced the famous Lely Platelets, which represented the first wave of SiC technology development for electronic applications.

#### 1.2.2 The Discovery of Polytypism

When Acheson found the hexagonal crystals in the voids, he sent some to B.W. Frazier, a professor at Lehigh University. Professor Frazier found that although the crystals were all silicon carbide, they differed in their crystalline structure. He had discovered the polytypism of SiC [18]. Polytypism will be explained in Section 1.3.2.

# 1.2.3 The First LED and the Lely Process

The electronic properties of SiC were investigated shortly afterward and in 1907 the first LED was produced from SiC [19]. However, the extraction of crystals was a cumbersome process that required patience, and the purity of the crystals was not controllable. As a consequence, in 1955 another crystal growth invention of significant proportions was made by J. A. Lely [20].

Lely created a mini-environment for the growth of crystals similar to the growth in the voids in the Acheson process (Figure 1.2). With Lely's method, the crystal purity and properties could, to some extent, be controlled. This created renewed interest in SiC and, at this time, SiC was even more popular than silicon and germanium. This would soon change, as we all know, mainly due to the difficulty at that time in processing high-purity SiC substrates. Until this substrate issue was solved, SiC was relegated to the arena of material scientists and physicists, who fortunately kept the science of SiC alive until technology could give it a push to commercial use.

a 1.2. The Loly process simulates the yorks in the Asheron process, yielding the herong

**Figure 1.2** The Lely process simulates the voids in the Acheson process, yielding the hexagonal crystals called Lely Platelets. (*From:* [17]. © 1963 Philips. Reprinted with permission.)

### 1.2.4 The Lost Decades

In 1958, the first SiC conference was held in Boston, Massachusetts. However, after this, the interest in SiC rapidly declined and the 1960s and 1970s are characterized by a low interest in SiC. Research was still ongoing, mainly in the former Soviet Union. In the United States, the work done by Westinghouse and the University of Pittsburgh is primarily notable. Indeed, the photoluminescence studies made by Choyke, Patrick, and Hamilton are still very relevant and often cited [21].

# 1.2.5 The Second Wave

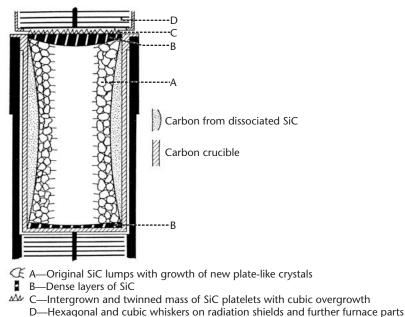

In the late 1970s, a very important invention—the seeded sublimation growth [22, 23]—was made in Russia by Tairov and Tsvetkov. Unlike the Lely process and the growth in the Acheson voids, where the growth is conducted under close-to-uniform thermal conditions, Tairov and Tsvetkov introduced a seed crystal and forced material transport from the source to the seed by a thermal gradient (Figure 1.3). The growth rates increased markedly and seeds of larger diameters and lengths could be made. The produced boules could be sliced and polished. The SiC wafer was born.

Another major invention that came only two years later was the ability to grow epitaxial SiC on Si substrates [24]. Research on SiC gained new speed, but it was a spark that never really caught on. However, there was generally a greater awareness of SiC and its potential, which was important for the years to come.

# 1.2.6 The Third Wave

In 1987, another milestone occurred when high-quality epitaxy could be made at low temperatures on off-axis substrates using "step-controlled epitaxy" [24]. Cree, Inc., was founded in 1989 as a result of this breakthrough. It manufactured the first commercial blue SiC LEDs and began to sell SiC wafers as well. At the same time, the company generated demonstrators for power devices and high-frequency devices. This was the beginning of the third and last wave of SiC. Along with improved epitaxy, continuous improvement of the diameter and quality of the wafers, and device milestones, this third wave has not died out but continues to grow in strength.

The commercial potential of SiC has to date mainly been in the materials arena. SiC is used as substrate for LEDs made from GaN, which is the largest market of semiconductor-grade SiC. Recently Infineon launched its Schottky diode product

Figure 1.3 The seeded sublimation growth or modified Lely growth invented by Tairov and Tsvetkov.

line made from SiC and Cree has also come out with a Schottky diode as well as high-frequency MESFETs. The future for SiC looks very bright indeed now that commercial products have hit the marketplace!

# 1.3 Crystalline Structure

## 1.3.1 Basic Structure

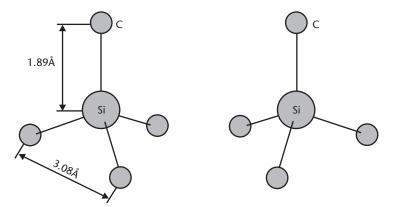

The basic building block of a silicon carbide crystal is the tetrahedron of four carbon atoms with a silicon atom in the center (Figure 1.4). There also exists a second type rotated 180° with respect to the first. The distance between the carbon and silicon atom is 1.89Å and the distance between the carbon atoms is 3.08Å [6]. SiC crystals are constructed with these units joining at the corners.

# 1.3.2 Polytypism

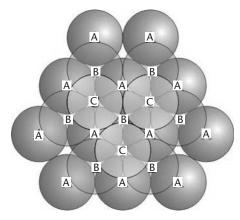

Silicon carbide exhibits a two-dimensional polymorphism called polytypism. All polytypes have a hexagonal frame of SiC bilayers. The hexagonal frame should be viewed as sheets of spheres of the same radius and the radii touching, as illustrated in Figure 1.5. The sheets are the same for all lattice planes. However, the relative position of the plane directly above or below are shifted somewhat to fit in the "valleys" of the adjacent sheet in a close-packed arrangement. Hence, there are two inequivalent positions for the adjacent sheets.

By referencing the possible positions as A, B, and C, we can begin constructing polytypes by arranging the sheets in a specific repetitive order. Thus, the only cubic polytype in SiC is 3C-SiC, which has the stacking sequence ABCABC... The simplest hexagonal structure we can build is 2H, which has a stacking sequence ABAB... The two important polytypes, 6H-SiC and 4H-SiC, have stacking sequences ABCACBABCACB... and ABCBABCB..., respectively.

The number in the notation of the resulting crystal structure determines the number of layers before the sequence repeats itself, and the letter determines the resulting structure of the crystal: C for cubic, H for hexagonal, and R for rhomohedral.

**Figure 1.4** The characteristic tetrahedron building block of all SiC crystals. Four carbon atoms are covalently bonded with a silicon atom in the center. Two types exist. One is rotated 180° around the *c*-axis with respect to the other, as shown.

**Figure 1.5** Illustration of three close-packed planes of spheres. The first layer is a layer of "A" atoms, followed by a layer of atoms on a "B" position, with a layer of atoms on "C" positions on top of that. The resulting structure in this example is 3C-SiC.

All polytypes are SiC of equal proportions of silicon and carbon atoms, but due to the fact that the stacking sequence between the planes differs, the electronic and optical properties differ. The bandgap is, for instance, 2.39 eV for 3C-SiC, 3.023 eV for 6H-SiC, and 3.265 eV for 4H-SiC [2].

The unit cell for the different polytypes will naturally vary, as will the number of atoms per unit cell. This will affect the number of electronic bands and the phonon branches for a given polytype.

# 1.3.3 Impurities in Different Polytypes

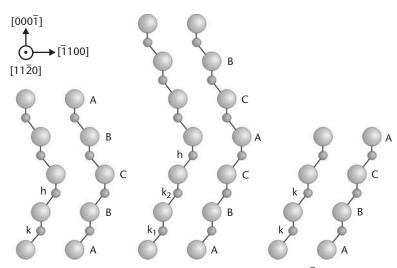

A very striking and beautiful feature of polytypism is the behavior of impurity atoms. In Figure 1.6, it may be seen that the sites are not equivalent in the hexagonal polytypes 6H-SiC and 4H-SiC. The difference is in the second-nearest neighbors.

A nitrogen atom substituting a carbon atom in the lattice can either occupy a "k" site or an "h" site in 4H-SiC. The k site is a lattice site that displays cubic symmetry, whereas the h site has hexagonal symmetry. The immediate vicinity of a nitrogen atom on either site is the same, but the second-nearest neighbors to the sites are different, which creates a slightly different core binding energy. Thus, 4H-SiC has two binding energies for the nitrogen donor, which has consequences when designing devices. 6H-SiC has three energy levels for nitrogen and 3C-SiC has only one. More complex polytypes such as rhombohedral (15R-SiC) has no less than five binding energies, although only four have been identified.

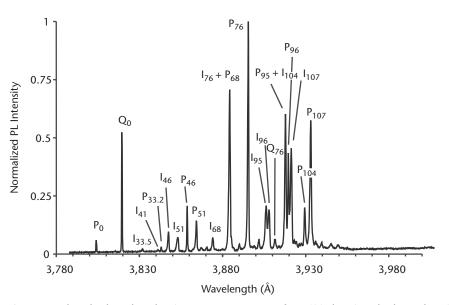

The photoluminescence (PL) spectrum in Figure 1.7 shows a number of lines related to nitrogen-bound excitons and free excitons. SiC has an indirect bandgap, thus the exciton-related luminescence is often assisted by a phonon. Bound exciton luminescence without phonon assistance can, however, occur because conservation in momentum can be accomplished with the help of the core or the nucleus of the nitrogen atom. That is why the zero phonon lines of the nitrogen atom are seen, denoted  $P_0$  and  $Q_0$ , in the spectrum but not the zero phonon line of the free exciton.

**Figure 1.6** The three most common polytypes in SiC viewed in the  $[11\overline{2}0]$  plane. From left to right, 4H-SiC, 6H-SiC, and 3C-SiC; *k* and *h* denote crystal symmetry points that are cubic and hexagonal, respectively.

The binding energies for the hexagonal and cubic nitrogen impurities are 59 meV and 102 meV, respectively [2]. According to the effective mass approximation [25], the binding energy of an electron bound to a nitrogen atom in 4H-SiC would be:

$$E_D = 136 \frac{Z^2 m}{n^2 \varepsilon_r^2 m_0} \text{ eV} \approx 6.07 \text{ meV}$$

(1.4)

**Figure 1.7** Near-band-edge photoluminescence spectrum of 4H-SiC showing the bound excitonrelated luminescence denoted  $P_h$  and  $Q_h$  (where h is the energy in meV of the phonon involved in the transition) and free exciton-related luminescence denoted  $I_h$ . (Data provided by Docent Anne Henry at Linköping University.)

where  $m^*$  and  $\varepsilon_r$  are the effective mass and dielectric constant, respectively. Z is the charge that is equal to 1 in this example and *n* is an integer equal to 1 for the ground state. The discrepancy between the actual binding energy, 59 meV, and what the effective mass approximation predicts is taken up by the core and is referred to as the central cell correction. In this example, the central cell correction is about 53 meV.

Defects with large central cell correction have very localized wave functions. The larger the correction, the more localized the wave function and the higher the probability of interaction between the core (or central cell) and the electron and/or the exciton bound to the defect. Hence the reason why the  $P_0$  line is so much smaller than the  $Q_0$  line in the spectrum, as well as the reason why the phonon replicas to the Q-line, is simply a matter of probability, since the central cell correction is so much larger for a nitrogen defect on a cubic site than a hexagonal site.

A useful feature of photoluminescence that is not limited to but very apparent in SiC is the ratio between the free exciton and bound exciton luminescence, which can give an accurate determination of the level of doping once properly calibrated [26]. In a perfectly pure crystal, the electron-hole pairs created through the absorption of above bandgap photons would bind together to form free excitons. These would move freely in the crystal until they recombine and possibly generate some light in the recombination process. If we do the same in a crystal with a small amount of nitrogen in it, some of the free excitons will likely hit on a nitrogen defect, which will attract the free exciton. The free exciton will lose some of its energy and bind to the defect center into a four-particle complex called the bound exciton. The four particles are the electron-hole pair of the free exciton, the electron of the nitrogen defect, and the core of the nitrogen atom. The bound exciton will, of course, also recombine and emit some light. Thus, by comparing the ratio between the free exciton and bound exciton luminescence, the doping level can be determined.

The paper by Henry et al. [26] continues to describe how PL may be used at higher doping levels where the free exciton is no longer seen by comparing the  $Q_0$  line and the  $P_{76}$  line. In the very high doping range, the authors correlated successfully the position of a broad nitrogen-related luminescence band with the doping concentration.

# 1.4 Crystal Growth

# 1.4.1 Seeded Sublimation Growth

#### 1.4.1.1 General Principle

As previously mentioned in Section 1.2, Tairov and Tsvetkov [22] invented seeded sublimation growth in 1978. The technique is almost exclusively used today to manufacture SiC wafers.

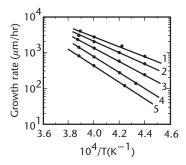

The principle is simple. A graphite crucible is partially filled with SiC powder and a seed is attached on the lid of the crucible. The whole system is closed and heated up to temperatures above which SiC starts to sublime appreciably. A thermal gradient is applied such that the seed is slightly colder than the powder source. Material will thus transport from the source to the seed where it will condense. The principal constituents during sublimation are Si, Si<sub>2</sub>C, and SiC<sub>2</sub> and the ratio between them is determined by the temperature. The control of the process is complicated and much effort has been spent to optimize the process. The pressure is kept low to enhance the material transport, as is nicely illustrated by Maltsev et al. in Figure 1.8 [27]. Typically, the pressure is kept below 50 mbar. In a study by Barrett et al., the dependence of the growth rate on the system pressure was analyzed [28]. They could determine that convective effects were present at pressures above 20 Torr (approximately 26.7 mbar). Below 20 Torr the vapor transport is diffusive, according to their study.

The temperature and temperature gradient are naturally very important factors for the growth. The growth rate is exponentially increasing with increasing temperature. Typical trends are comprehensively illustrated by Vodakov et al. [29], Barrett et al. [28], and Maltsev et al. [27].

### 1.4.1.2 Substrate Diameter

Two major challenges for SiC bulk crystals are the manufacture of large-diameter, high-quality wafers and the manufacture of SI wafers. The diameter is rapidly increasing and 4-inch wafers have already been demonstrated. The increase in wafer diameter is significantly faster than that experienced for Si and GaAs, partly as a result of the knowledge base established for these technologies [30]. There is no doubt that SiC, with the same diameter as silicon wafers, will be available in the not-too-distant future.

### 1.4.1.3 Semi-Insulating Substrates

The second challenge in making SI SiC started initially by attempting to make the crystals as pure as possible to increase the resistivity, as was done by Barrett et al. [28]. It was later discovered that the introduction of specific deep-level dopants into the SiC lattice created deep traps that captures free carriers [31]. The dopant of choice for these compensated crystals was vanadium, which was found to compensate shallow acceptors. Therefore, during growth, the material needs to be doped p-type by the addition of boron or aluminum as well as introducing vanadium in larger amounts than the p-type dopant. Unfortunately, this created some problems with yield and defects due to the large amounts of impurities present in the crystal. Nevertheless, very high resistivities exceeding  $10^{15} \Omega$ -cm were obtained at room temperature. The activation energy of the vanadium trap was determined to be 1.18 eV.

**Figure 1.8** The temperature dependence on the growth rate is shown here for different Ar pressures. The residual pressures are for curve: 1–10, 2–35, 3–50, 4–75, and 5–100 Torr. (*From:* [27]. © 1996 Institue of Physics Publishing. Reprinted with permission.)

It is hard to understand the tremendous interest in the vanadium doped crystals since, in 1993, the Westinghouse Science and Technology Center was already producing 6H-SiC wafers with resistivities as high as  $10^{5} \Omega$ -cm without the introduction of impurities by simply growing the crystals as purely as it could achieve [28]. It is particularly surprising in view of the fact that it was the same group that first introduced the vanadium doping. It is unfortunate that they did not realize that the most promising and much superior approach was to continue to improve the purity of the crystals as much as possible.

Other than poor crystalline quality and yield problems, there was one more problem with the vanadium doped SI SiC wafers; they did not work for highfrequency applications due to excessive trapping of electrons. A very elegant demonstration of this trapping can be seen in the publication by Sghaier et al., where the degradation in performance of the high-frequency device was clearly seen and it concluded that the cause for the trapping was the vanadium doped substrate [32].

Then, in 1999, the high-frequency community, in desperate need of better semi-insulating substrates, regained their confidence due to some interesting results where very pure, vanadium-free crystals had been grown that displayed SI behavior [33]. The authors found a deep level with an activation energy of 1.1 eV, though they had no clear identification of the identity of the defect. However, they speculated that it was intrinsic in nature. The resistivity was outstanding, demonstrating a resistivity in excess of  $10^7 \Omega$ -cm at 300°C, which is high enough for most power RF applications.

Another even more interesting development was occurring at the same time. This was the development of a new growth technique, called the High Temperature Chemical Vapor Deposition (HTCVD) technique [34], that produced crystals that were intrinsically semi-insulating. In a paper by Ellison et al. [34], the authors reported on a defect with an activation energy of 1.15 eV yielding an extrapolated room temperature resistivity in excess of  $10^9 \Omega$ -cm.

Further work showed that several intrinsic defects can contribute to the semiinsulating properties of the crystal, such as Si-vacancies, C-vacancies, and C-antisites. Typically, the resistivity of semi-insulating crystals containing predominately Si-vacancies is lower and the activation energy of the responsible defect is less than 1.1 eV, whereas crystals with predominately C-vacancies content have higher resistivities and the activation energy is around 1.4 eV [35]. Lately, photo-electron paramagnetic resonance (EPR) measurements revealed that the carbon vacancy acts as a deep donor with an activation energy of 1.47 eV [36]. This provides to date the strongest evidence that C-vacancies play a role in SiC similar to the well-known EL2 deep level in GaAs for producing high-purity semi-insulating wafers.

Now, 2-inch SI wafers without vanadium doping are sold commercially from several sources. Vanadium doped crystals will rapidly disappear and soon only be used as displays in museums or as book rests.

# 1.4.1.4 Prospect

A lot of research is being conducted on the seeded sublimation growth technique. The material properties are improving steadily and there should be no reason for worries. Yet, one worry is the need for off-axis substrates for high-quality epitaxial growth. The current standard of 8° off-axis from the [0001] plane on the 4H-SiC wafers was introduced in 1995 by Cree, since it had seen an improvement in the epitaxy when the off-axis angle was increased from  $3.5^{\circ}$  (which is still the standard miscut for 6H-SiC). At that time, only 30-mm wafers were available commercially, and it was not a big problem to slice the wafers somewhat more off-axis. It was only a matter of 4-mm lost material in total from the grown boule. On a 100-mm wafer, the amount of lost material is no less than 14 mm. Considering that most boules in the world are grown on-axis parallel to the *c*-axis and that the length is limited to approximately 25–30 mm, it is going to cause significant heartache to slice the boule 8° off-axis and lose half of the material.

The trend must be to reduce the off-axis angle. Fortunately, if we peek at what has happened previously in the Si and GaAs worlds, the standard was to use off-axis substrates initially, but as the material quality improved, the need for off-axis substrates was reduced and on-axis substrates are now used for epitaxy. This is likely going to be the trend in SiC too. The need for better epitaxial procedures and higher-quality substrates than what is available today is important.

Boule lengths are also likely to increase. More powder may be introduced into the growth chamber, however, thermal considerations become an issue as the boules increase too much in length. Even if the surface is kept at constant distance in the chamber, the distance from the source will vary as the material is depleted and the growth conditions change.

The source material will release excess silicon in the beginning of the growth cycle and be more carbon-rich in the end due to preferential depletion of silicon. This is a known problem and it is a matter of detailed control and an understanding of the dynamic transport mechanisms in combination with thermodynamics. Nevertheless, the result is invariably that SiC boules grown by seeded sublimation growth are Si-rich in the beginning and C-rich near the end, which creates yield issues. Simulation of the process is necessary to improve the situation.

The turnaround time for a boule growth run is several days. It takes time to prepare the source, load the crucible, attach the seed, evacuate the system carefully, gradually heat up the crucible under controlled conditions, and finally grow the boule and then cool down. The turnaround time itself is not a problem, however, the cost of manufacturing a wafer needs to decrease so the price of the wafers can be reduced in order for SiC to gain acceptance in the market.

Seeded sublimation growth is a mature and needed tool for the SiC industry today. There are still major challenges. Specifically, boules will need to be grown on off-axis substrates, or the off-axis angle needs to be eliminated, which will only be possible if a combined effort of improving wafer quality, polishing procedures, and epitaxial procedures is pursued.

# 1.4.2 High Temperature Chemical Vapor Deposition

In 1995, a new technique, called HTCVD, was presented for the growth of SiC boules. This technique uses gases instead of a powder as source material. It was first presented at ICSCRM '95 in Kyoto, Japan, but the first publication of HTCVD in a journal was in 1996 [37]. More recent publications are available where the technique is better described [38].

#### 1.4.2.1 General Principle

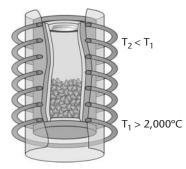

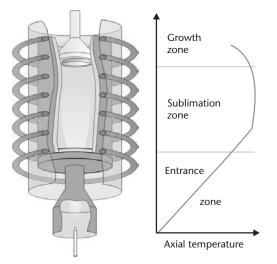

The HTCVD apparatus can be described as consisting of three separate zones: An entrance zone, a sublimation zone, and a growth (or condensation) zone. The gases used are mainly silane, ethylene, and a helium carrier. The carrier flow is very low. A schematic of the HTCVD system is shown in Figure 1.9.

Silane and ethylene are present at very high concentrations so that homogeneous nucleation dominates the process. As the gases enter into the hot part of the injector, the silane will decompose and form small Si liquid droplets or solid microcrystals, depending on the temperature. The ethylene will also take part in the reaction, forming microparticles of Si<sub>x</sub>C<sub>y</sub>. It has been noted [39] that even a small addition of hydrocarbons converts the Si droplets to stable particles of Si<sub>x</sub>C<sub>y</sub> (or nonstoichiometric SiC). The stability may, in a hand-waving circumstantial way, be intuitively understood from a solubility point of view. The solubility of carbon in silicon is very low, thus, when carbon is added to the Si droplets, the phase will be solid rather than liquid.

The process can work without additions of a hydrocarbon, in which case the carbon is supplied through a reaction between the hot silicon and the graphite walls. This is usually not the preferred growth mode and additions of hydrocarbons are needed to obtain a high growth rate.

The formed microparticles of  $Si_xC_y$  will move into the hot chamber or the sublimation zone with the aid of the inert helium carrier gas. Once in the sublimation zone, the microparticles will sublime to form Si, Si<sub>2</sub>C, and SiC<sub>2</sub>, as in the case of seeded sublimation growth. A thermal gradient is applied, as illustrated in Figure 1.9, so that the sublimed species will condense on the seed, as in the case of seeded sublimation growth.

There are similarities between seeded sublimation growth and HTCVD in that solid particles sublimate in the reactor and the vapor condenses on a seed crystal maintained at a lower temperature. However, the differences are quite dramatic and the outcome even more so. Take, for instance, the dynamics governing the growth

**Figure 1.9** HTCVD process. Microparticles are formed in the inlet region of the system and transported to the sublimation zone, where the particles sublime to finally condense on the growth surface.

rate. The heating of the particles in the sublimation zone must be efficient so that they sublime properly. Insufficient sublimation results in particles appearing as "smoke" coming out from the crucible. This is obviously not a good scenario and material quality, as well as growth rate, will suffer.

The growth rate is naturally influenced by the amount of input precursors, however, too high concentrations will give rise to too large nuclei, which will be difficult to sublime. As may have been deduced, if the thermal gradient between the seed and the sublimation zone is increased, the potential for sublimation will increase so that larger microparticles may be sublimed, thus larger amounts of precursors may be introduced and the growth rate will increase.

The process is usually carried out at somewhat reduced pressures, though not at as low a pressure as seeded sublimation growth, where the pressure is greatly reduced to aid the material transport. HTCVD has its own material transport through the small but steady flow of helium, so reduced pressure is not needed to enhance growth species transport. However, the lower pressure will result in smaller particle sizes due to a suppression of homogeneous nucleation. Lowering the pressure will thus increase the maximum amount of precursors without observing "smoke" at the outlet.

Thus, there are several ways to improve the growth rate, as can be seen. But in the end it all comes down to the size of the particles that need to be sublimed in the sublimation zone. Typical maximum growth rates are in the order of 0.8 mm/hr–1 mm/hr.

What is also interesting about the HTCVD is the material transport. Why does the silane not decompose and grow directly on the walls of the inlet? There are two reasons for this. First, the injector is a coaxial injector, as illustrated in Figure 1.9 [40]. The silane and ethylene are transported in the inner tube, whereas there is only carrier gas in the outer tube. Thus the silane will not be in close proximity with a wall when it decomposes and will preferentially form nuclei through homogeneous nucleation. Second, the ethylene will make these particles very stable and hence they will not be prone to growth on the walls at all.

As is well known, when hydrocarbons transported in an inert gas such as helium are heated, carbon or pyrolytic graphite will deposit on the walls. In the HTCVD, the ethylene helps make the particles stable and, in doing so, carbon is transported into the chamber together with the silicon. It is a sort of symbiosis in the transport between the silicon and carbon.

# 1.4.2.2 Material Properties

One of the prime advantages of the HTCVD approach is the resulting crystal properties. Due to the high purity of the gases, the material comes out intrinsically semiinsulating. Also, since the source material is produced on demand, the stoichiometry can always be kept the same, unlike the case with seeded sublimation growth. This will improve the yield of the grown material.

It is also interesting to note that the technique is shown to reduce micropipes by 80% during each run [35]. The micropipes close at the interface by some type of hollow core-closing effect. Very low micropipe densities have been recorded using this technique, which is clearly much faster in improving material quality than seeded sublimation growth. The resistivity of the SI wafers has been measured to be in excess of  $10^{11} \Omega$ -cm at room temperature [35]. As mentioned earlier, a deep level defect was found to have an activation energy of 1.4 eV. MESFETs manufactured on these wafers show an increased performance in the sense of reduced trapping, which the authors explain as being primarily due to a reduction of the shallow impurities in the material.

### 1.4.2.3 Challenges

Some of HTCVD's initial challenges have been solved. For example, using a coaxial injector solved the blocking of the inlet. Another issue is the purity of the graphite material, which may be overcome using properly coated graphite crucibles.

The outlet is a major problem because the material grows not only on the surface of the crystal but also around it and on the walls. When the outlet blocks, thegrowth must be interrupted and hence the length of the crystals is limited. Work is ongoing to solve this specific issue and it has, to some extent, been fruitful. Crystals with a length in excess of 15 mm have been grown [A. Ellison, private communication].

New problems will arise as the crystal increases. It will, for instance, be necessary to pull the crystal during growth so that the growth surface remains at the same position in the crucible. When the crystals become long the thermal profile may change and will need to be controlled. Fortunately these are all problems that can be easily managed with proper engineering design and process simulation. As a result, there appear to be no real limitations to this approach.

The growth rates today can be approximated to about 1 mm/hr, which means that roughly 20 mm of material may be grown each day, including 4 hours for the turnaround heat-up and cool-down time. Although this is better than what the seeded sublimation growth can achieve, growth rates will need to be increased further to drive wafer costs down.

The cost of manufacture is often used as an argument against HTCVD. The reactors are, as may be understood, significantly more complex and hence also more expensive, compared with seeded sublimation growth. Graphite materials are somewhat more expensive for HTCVD, whereas the gases are likely to be less expensive than high-purity powder material in bulk quantities. However, with a potentially higher throughput when using the HTCVD technique, and provided the volumes are high, it will actually be less expensive to use this technique than seeded sublimation growth since the cost will largely be driven by volumes. The cost comparison becomes even more favorable for HTCVD if the improved yields of low micropipe material, particular low micropipe SI material, are taken into account.

However, such comparison is a meaningless exercise. A comparison of silicon, sapphire, GaAs, or other established materials, rather than other SiC growth techniques, should occur instead. The blue and white LEDs can, for instance, be made on either sapphire or SiC substrates. From a performance point of view, there appear to be advantages with the SiC substrate but the substrate cost is lower on sapphire, therefore making it the most-used substrate. Granted, once larger substrates of SiC are made available, it is doubtful that the LED cost will be lower on sapphire.

Ultimately, SiC will not only be going up against sapphire but also against such giants as silicon and GaAs, which will require significant cost-reduction measures

in the materials growth for SiC to become a viable technology. HTCVD is clearly a step in the right direction, but the SiC community still has a long way to go in this regard.

# 1.5 Epitaxial Growth

Several techniques for epitaxial growth exist today and it is therefore beyond the scope of this chapter to explain all of them. Chemical vapor deposition (CVD) is the only technique that is used for commercial applications of SiC and the description of epitaxy will be limited to this technique.

Several different types of CVD reactors exist. The cold wall design, which used to be the most common type of reactor, is now less frequently used and the hot-wall reactor has filled its place. Some new and interesting concepts exist as well. These are referred to as chimney-type reactors. The main difference between the hot- or old-wall type reactors and the chimney-style reactor is the transport of materials, which will be explained in the following sections.

# 1.5.1 Chemical Vapor Deposition

CVD of SiC normally uses silane and a hydrocarbon as the precursor gases and a hydrogen carrier gas. The gases pass over a heated graphite susceptor that is coated by SiC or tantalum carbide (TaC).

The velocity of the gases is high but it is always laminar flow. Over the susceptor there will be a boundary, or stagnant, layer where the velocity gradient decreases to zero. As the gases are heated, the silane and hydrocarbon will decompose and the species will diffuse through the boundary layer to grow on the reactor walls or on the substrate. A comprehensive study of this may be found in a paper by M. Leys and H. Veenvliet [41].

The concentration of precursor gases will decrease with respect to the flow direction over the susceptor due to the consumption of growth species, which results in a tapered layer thickness. This effect is known as depletion. To compensate for the depletion it is common to taper the susceptor such that the velocity of the gases increases along the flow direction over the susceptor and thus the boundary layer will be pushed downward, resulting in a shorter diffusion for the active species to the substrate.

It is sometimes not enough to taper the susceptor to achieve good homogeneity of thickness and doping, hence other more complicated measures are applied, such as rotation of the substrate as described in the literature [42]. In this paper, the authors also use a blend of argon and hydrogen as carrier gas, which has been shown to be advantageous to achieve better homogeneity [43].

The flow of hydrogen is generally very high and the pressure is reduced. This is not so much on account of the flow dynamics but more due to reducing the homogeneous nucleation of Si, which is significant when silane is used. The silicon cluster formation was first noticed and studied in detail by Rupp et al. in a single wafer Emcore reactor with a very high thermal gradient [44].

# 1.5.1.1 Doping Control

This can be done by introducing nitrogen for n-type and trimethylaluminum (TMA) for p-type layers. To obtain a better range of doping, it has been elegantly demonstrated that by changing the C/Si ratio of the input gases the doping concentration will change without changing the flow of nitrogen or TMA. This effect is known as site competition [45]. Unfortunately, when changing the stoichiometry, the morphology is affected somewhat and it is therefore not always desirable to do this if thick layers are to be grown.

When doping is used and multiple layers are grown with different carrier type and conductivity, it is important that the doping level decreases rapidly after the source of the dopant is shut off. Otherwise one does not achieve abrupt junctions. This is known as the memory effect and it can be reduced by various tricks. For instance, one can vary the stoichiometry, provide a short purge without any dopant but continue to flow the normal precursor gases, or even perform an in-situ etch back before the next layer is grown. Although an Al memory effect was a concern in the early 1990s, this problem has been solved and it is no longer a concern.

# 1.5.1.2 Hot-Wall Reactor

Prior to the introduction of hot-wall reactors in 1993 [46], thick, low-doped layers for very high voltages had not been achieved. This type of reactor proved it possible to grow very thick, low-doped layers of good morphology and high quality, which are needed for high-voltage power devices [47].

Hot-wall CVD reactors have become increasingly popular due to the ease of obtaining high- quality layers. The stochiometry is usually selected with respect to optimum morphology and doping is varied by changing the partial pressures of the dopants.

The reactor also displays a remarkably high uniformity in both thickness and doping. Even without wafer rotation, uniformities as tight as 1% in thickness and 2% in doping have been reported [48]. More recently, rotation has been introduced, primarily to increase the capacity (i.e., to have the same high uniformity over several wafers [49]). The reproducibility was also reported to be very good, within  $\pm 10\%$  in doping.

The behavior of the hot-wall reactor has been investigated thoroughly. A short but comprehensive study by Wagner and Irmscher captures the main points [50].

# 1.5.1.3 Multiwafer Reactors

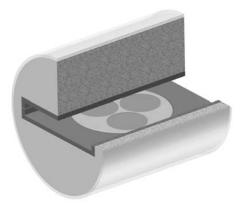

Wafer rotation, as previously mentioned, has been introduced in the hot-wall reactor (see Figure 1.10), which gives it a capacity of  $3 \times 2$ -inch (that is, three 2-inch wafers can be run simultaneously to increase reactor throughput). The uniformity in this reactor is routinely 1–2% in thickness and 5–7% in doping [Rune Berge, Epi-gress, private communication].

Aixtron has manufactured both a cold-wall planetary reactor and a hot-wall planetary reactor for  $7 \times 2$ -inch wafer capacity or  $5 \times 3$ -inch. The cold-wall reactor has provided very good uniformities and its performance has been described in

Figure 1.10 The hot-wall reactor with a  $3 \times 2$ -inch rotating platter. The mode of rotation is generally gas-foil rotation.

several papers [51]. For the  $7 \times 2$ -inch reactor, they report on thickness uniformities around 4% and doping uniformities of 5% and 7%, depending on the doping level.

The  $7 \times 2$ -inch hot-wall version has shown outstanding uniformities and high material quality [52]. Uniformities in thickness of 0.4%, and doping of 5–6% have been demonstrated. Wafer-to-wafer uniformities are 0.6% in thickness and 3.6% in doping, which are outstanding results. Results for the  $5 \times 3$ -inch version of the same reactor are meager but the hot-wall version of the  $5 \times 3$ -inch reactor behaves much the same as the  $7 \times 2$ -inch (i.e., approximately the same uniformities [Rune Berge, Epigress, private communication].

# 1.5.1.4 The Chimney Reactor

An elegant new reactor concept for the growth of SiC epitaxial layers was introduced by Ellison et al. [34, 53] and is called the chimney reactor. This technique is similar to the HTCVD technique in that it is a vertical system and the material transport is achieved by allowing large clusters of Si to form. This is achieved by reducing the carrier flow, which thereby increases the partial pressure of the precursors. Hydrogen is used as the carrier gas but, again, only very small flow rates are required.

The silicon clusters are formed in the inlet region at relatively low temperatures. As the temperature increases the formed Si clusters will thermally decompose and be available for growth. This is very similar to HTCVD; however, in this case there is no sublimation, only a decomposition of the Si clusters.

Very high growth rates and outstanding purity has been achieved using this technique. Growth rates between  $15-50 \,\mu$ m/hr and background doping in the low  $10^{13}$  cm<sup>-3</sup> have been reported by Zhang et al. [54].

Typically, the temperatures used for growth are somewhat higher than those used in regular CVD, however, it need not be much higher. The high growth rates are obtained at higher temperatures as the dissociation of the Si clusters is more efficient. Other groups have also worked on the same concept. Specifically, Tsuchida et al. have achieved very good results using this technique [55]. Their reactor is heated through radiation using a cylindrical heating element surrounding a wedge-shaped substrate holder. The substrate temperature is lower (around 1,600°C) than what is usually used for chimney reactors but the surrounding heating element is significantly hotter.

Kimoto et al. has also achieved high-quality results using the chimney technique. They report doping concentrations below  $10^{13}$  cm<sup>-3</sup> [56].

# 1.6 Defects

It is important to discuss the major defects present in SiC. The intent is not to create an encyclopedia of SiC defects but rather highlight two that have become the favorite lament of device researchers and which create significant heartache and debate.

# 1.6.1 Micropipes

In previous sections, micropipes have been discussed, and these are indeed the most important defect present in SiC. Micropipes may be caused by several screw dislocations bunching together to form a giant screw dislocation, making it energetically favorable to open up a hollow core in the center [57]. A different way of forming micropipes may be simply by system contamination, where particles are trapped in the growing crystal, thus forming a micropipe, as described by Augustine et al. [58]. The third way micropipes form, according to the same authors, is by vacancy condensation at a helical dislocation.

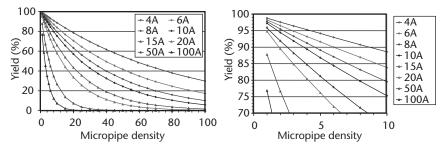

Micropipes are basically a hollow core penetrating the entire wafer along the *c*-axis direction. Placing any device directly on top of the micropipe is bound to cause failure. These defects are particularly disturbing for large-area devices such as high-power devices because the probability of placing your device on a micropipe increases, as shown in Figure 1.11. To obtain decent yields in excess of, say, 80% for a 10-A Schottky device, micropipe densities must be in the order of 8 mp/cm<sup>2</sup>. For a 50-A Schottky one would need material with a micropipe density better than 2 mp/cm<sup>2</sup>.

**Figure 1.11** Simulation of the yield of various sizes of Schottky diodes versus micropipe density for randomly distributed micropipes. The right-hand figure is a detail of the left-hand figure. Micropipes located on the active area or JTE region render a failed device, however, micropipes located in between the devices are considered harmless.

Figure 1.11 is a simulation of randomly distributed micropipes, however, there is normally a tendency to cluster the micropipes, which would give somewhat better yields. Also, a significant amount of micropipes land in between the devices where the wafers are diced and these are considered harmless in the simulation.

There is interesting research going on with respect to minimizing the micropipes by growing boules on the  $[03\overline{3}8]$  plane [59]. The plan is to let the micropipes and stacking faults propagate diagonally to prevent them from reaching the top surface of the boule. The researchers did indeed find micropipe-free areas and it will be interesting to follow future work on this.

Similar research has been done on planes perpendicular to the [0001] basal plane. Micropipe-free material has been grown, however, new defects appear as reported by the authors [60].

#### 1.6.2 Stacking Faults

The second defect that needs to be discussed does not have as grand a history as micropipes because it only recently became popular. This defect is the stacking fault, which creates degradation of bipolar devices. Reports by Lendenmann [61] and Bergman [62] reveal that a PiN diode operating under normal conditions begins to degrade. While the diode is operating, defects, which the authors interpret as stacking faults, evolve with an accompanying reduction in carrier lifetime. The defects thus act as recombination centers for the carriers.

Furthermore, the stacking order has been identified as that of the 3C-SiC polytype and, according to the study by Stahlbush, an explanation to the recombinative behavior of the stacking fault is that the 3C-SiC, having a lower bandgap than 4H-SiC, acts as a quantum well, thereby enhancing the recombination [63]. It is a very serious materials issue that must be solved prior to the realization of commercial bipolar devices.

Work is ongoing to reduce defects in SiC material. One of the more interesting concepts is the reduction of defects through epitaxial growth on porous SiC substrates [64]. This approach has clearly demonstrated a reduction in intrinsic defects, as evidenced by photoluminescence measurements. It is too early to tell whether this technique can provide a path forward for the bipolar devices but it will clearly find its applicability in several areas where SiC will have a market.

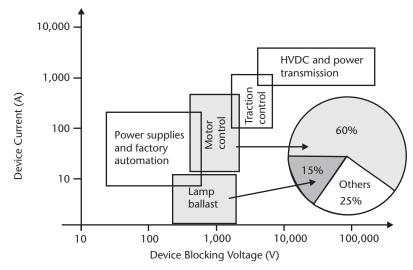

# 1.7 Commercial Outlook

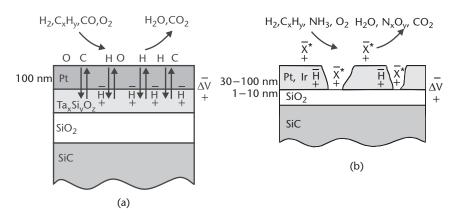

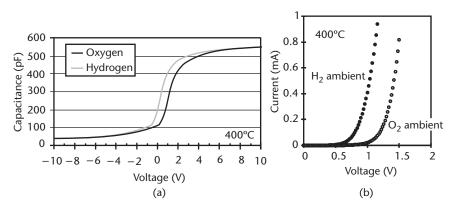

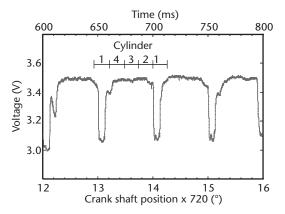

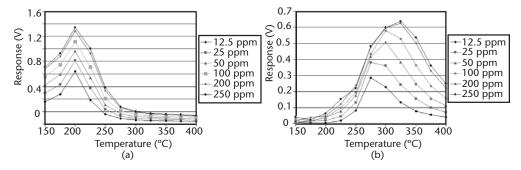

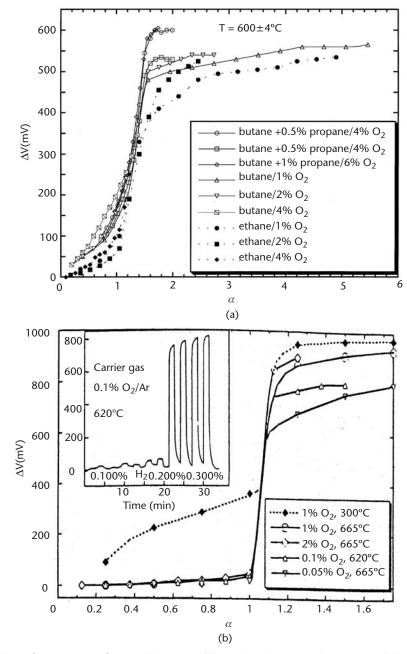

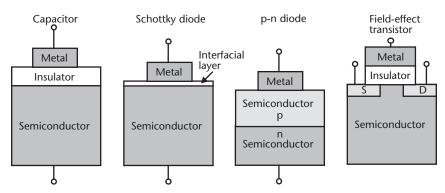

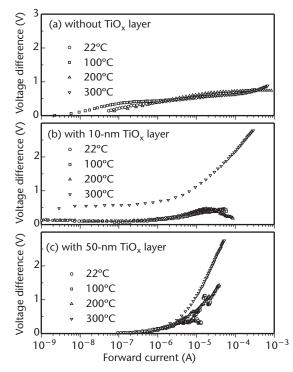

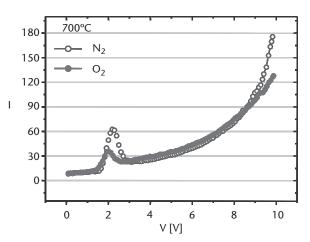

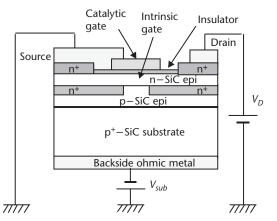

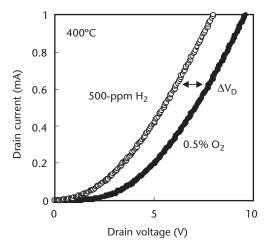

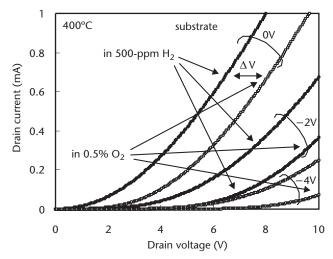

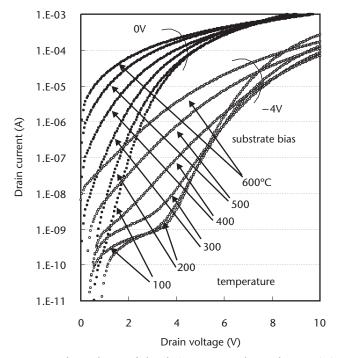

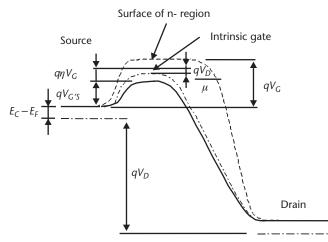

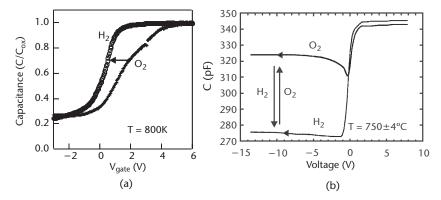

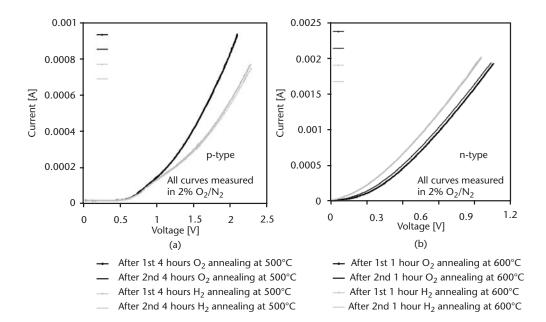

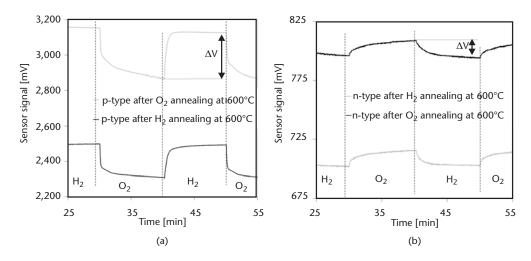

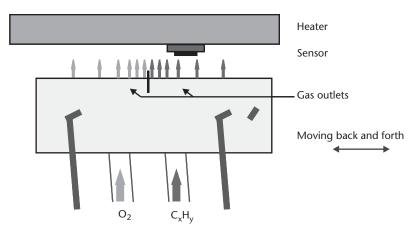

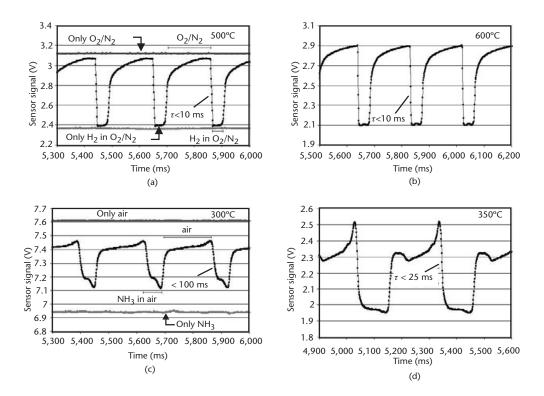

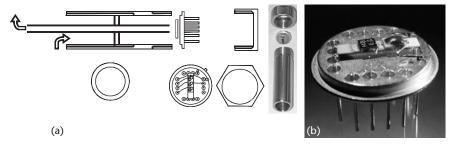

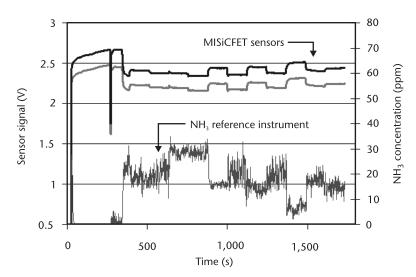

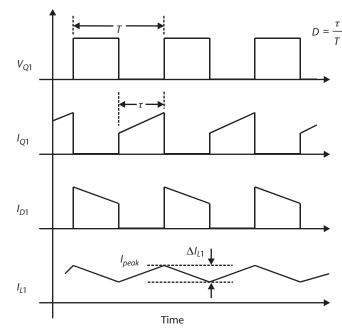

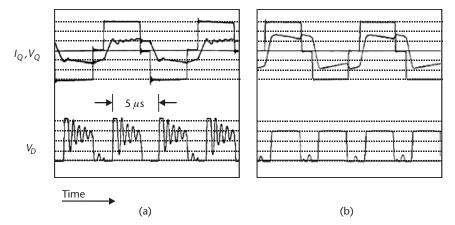

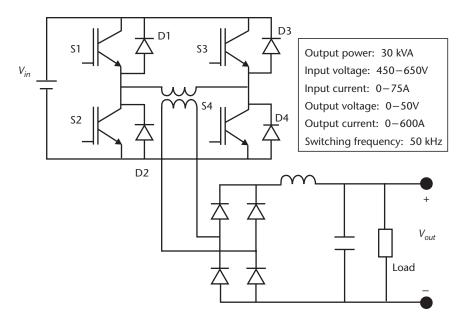

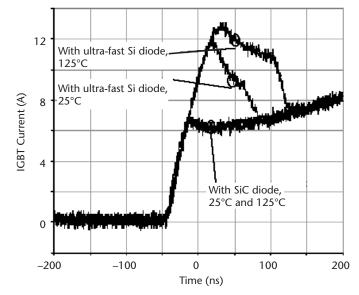

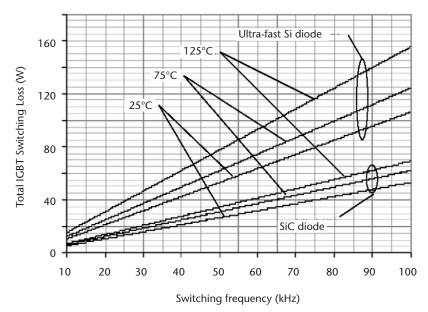

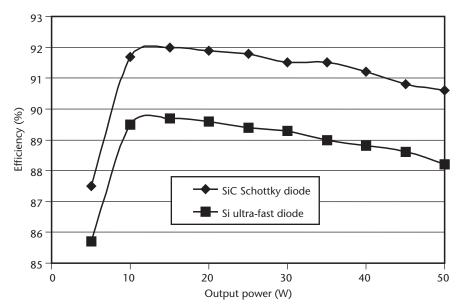

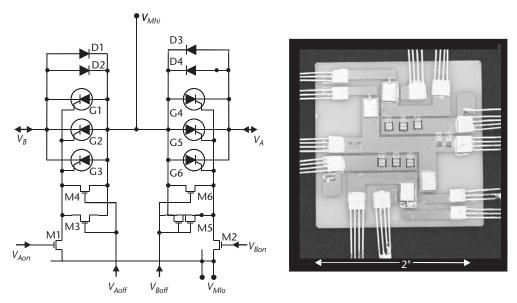

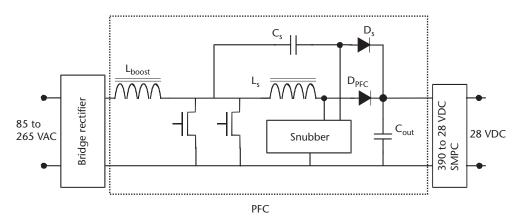

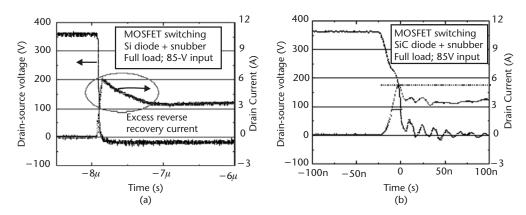

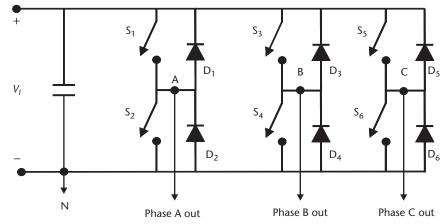

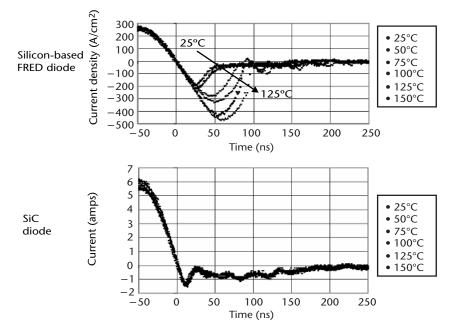

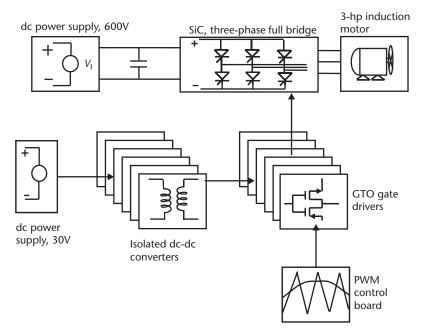

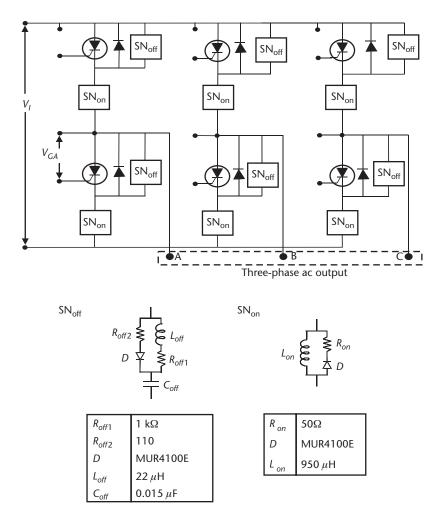

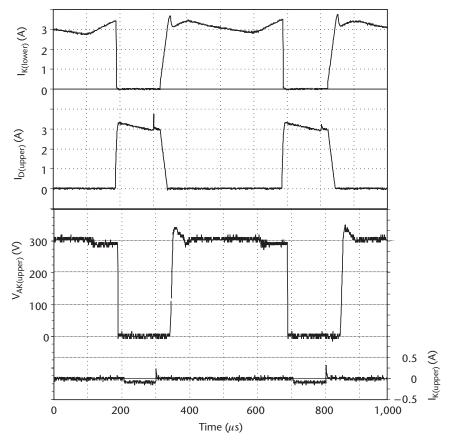

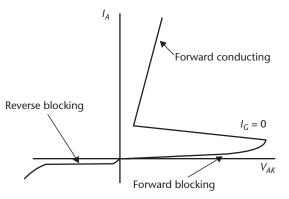

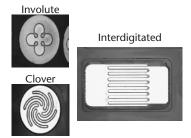

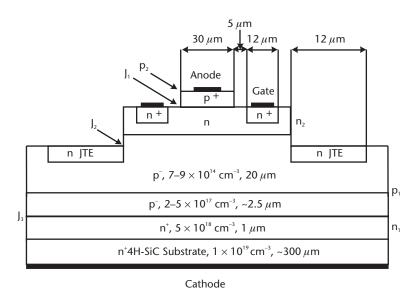

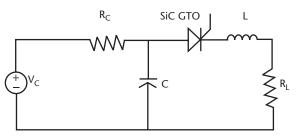

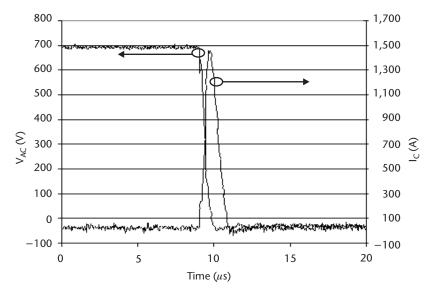

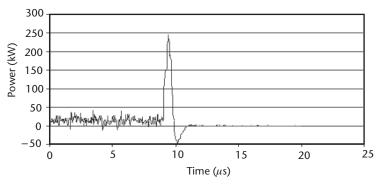

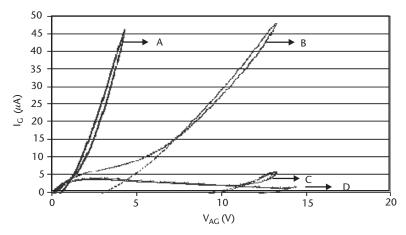

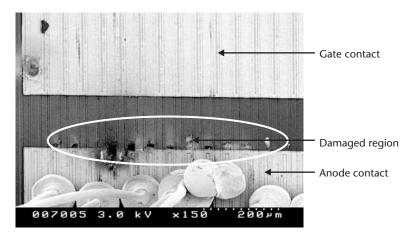

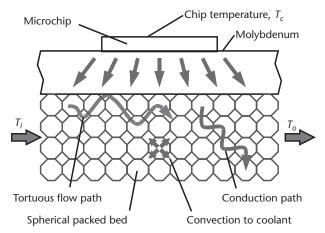

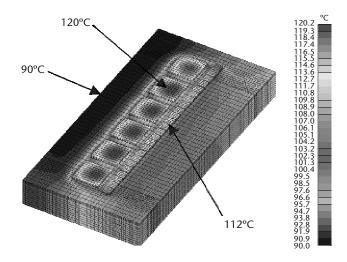

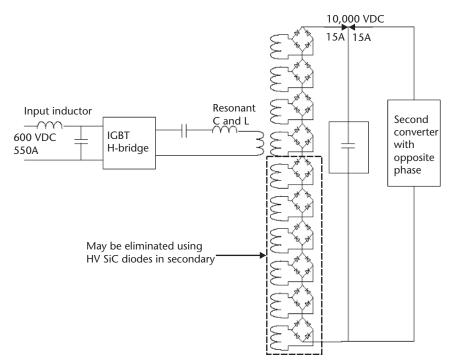

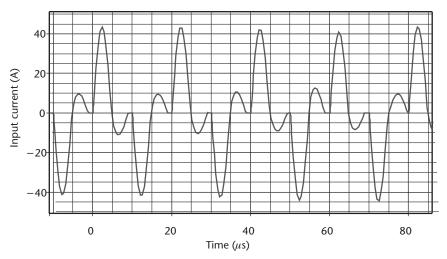

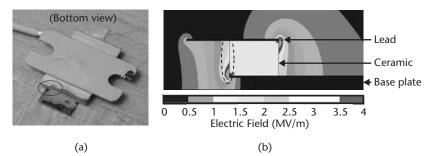

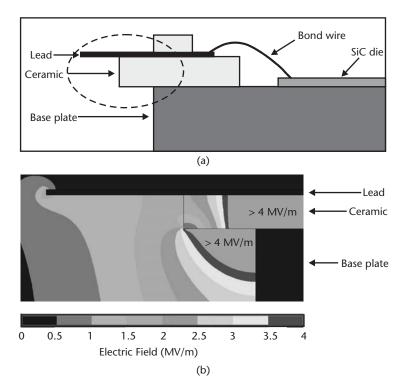

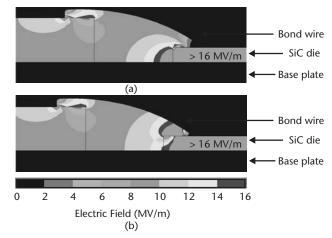

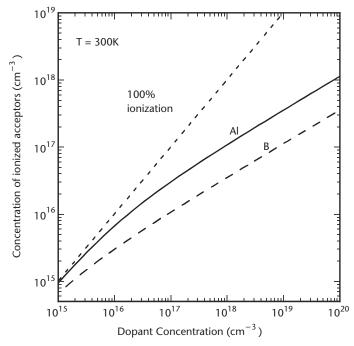

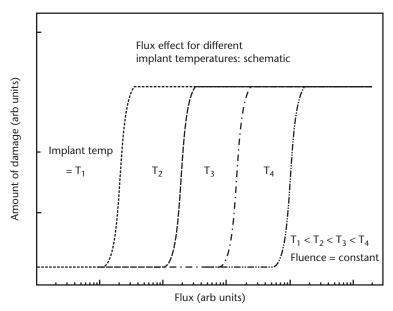

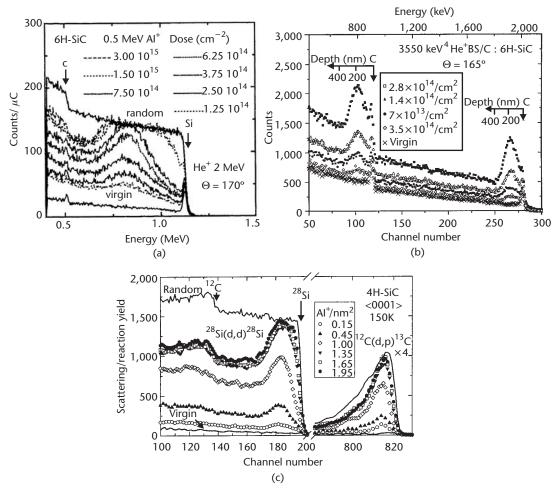

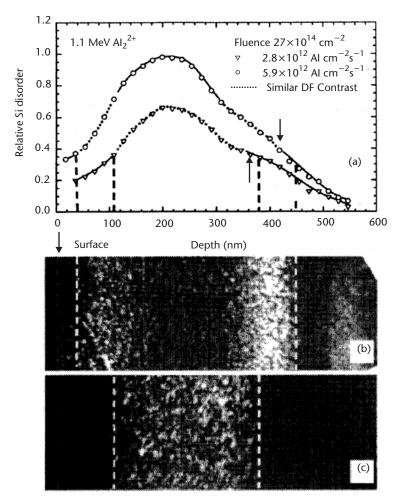

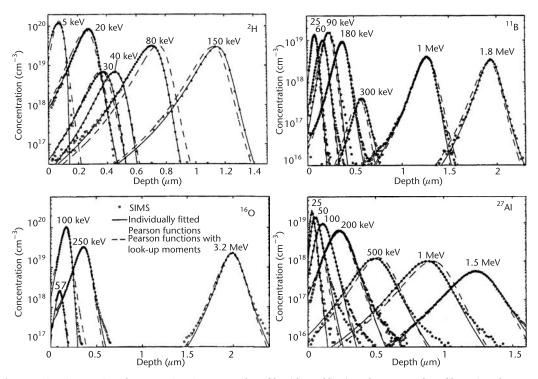

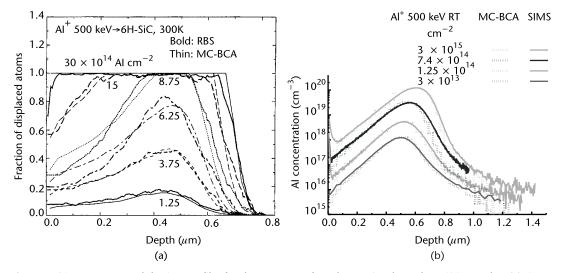

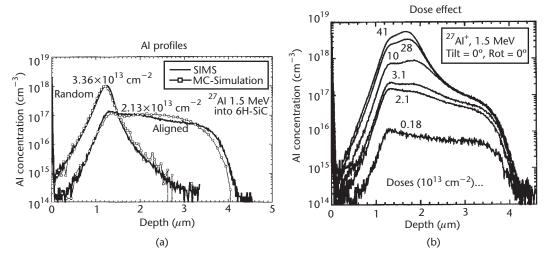

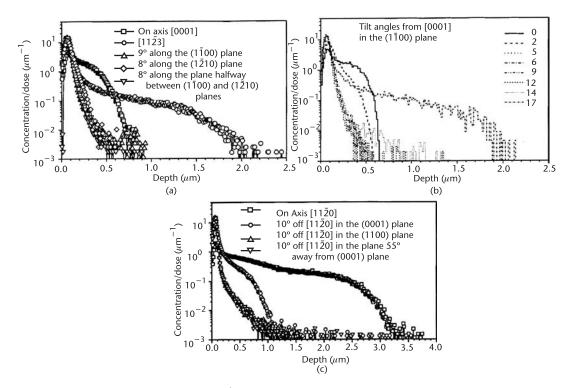

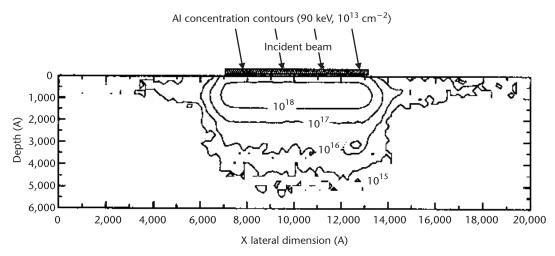

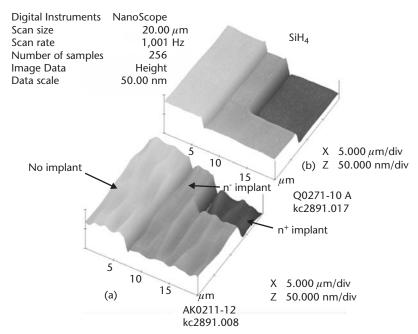

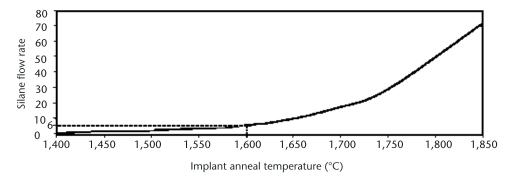

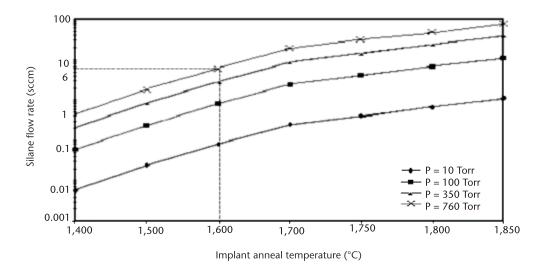

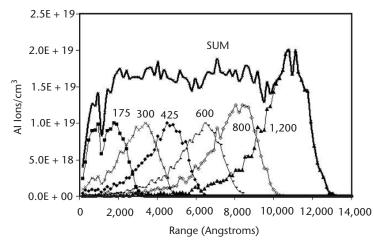

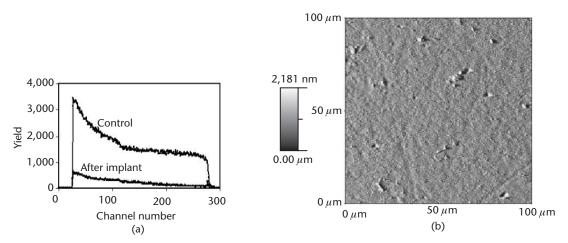

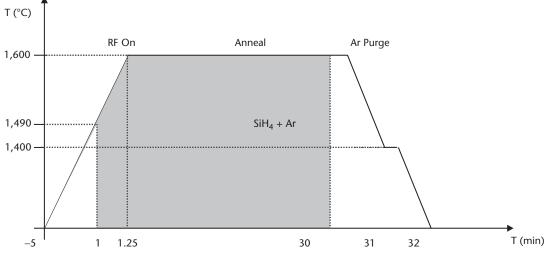

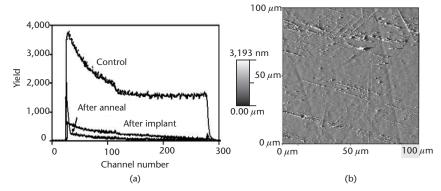

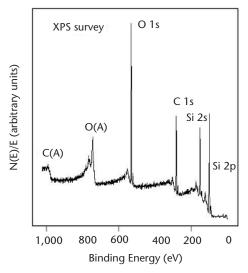

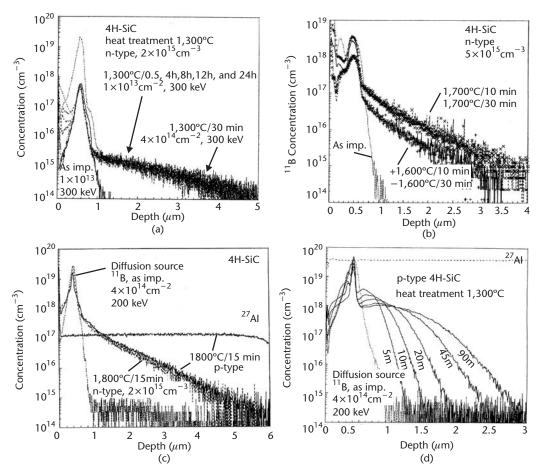

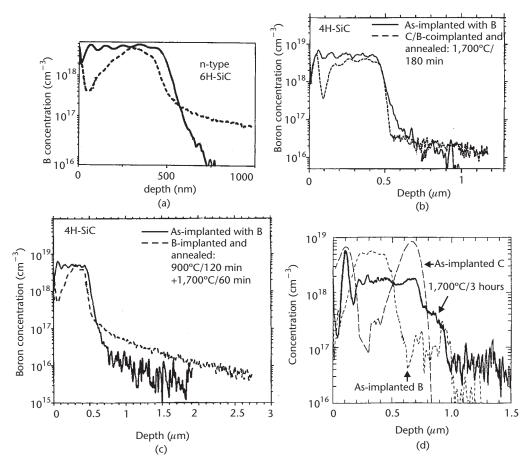

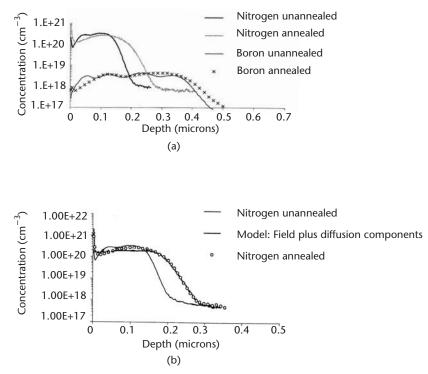

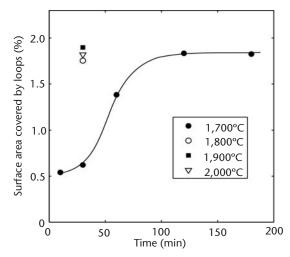

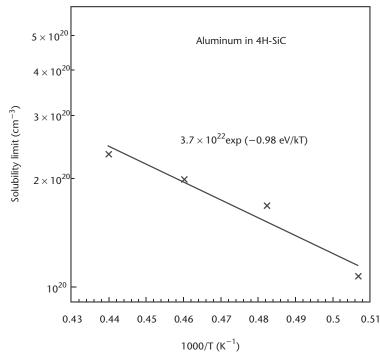

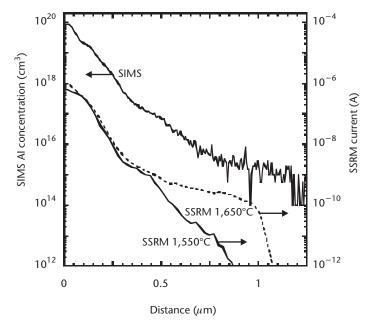

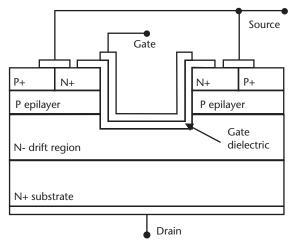

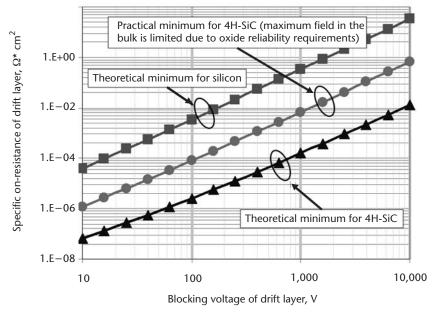

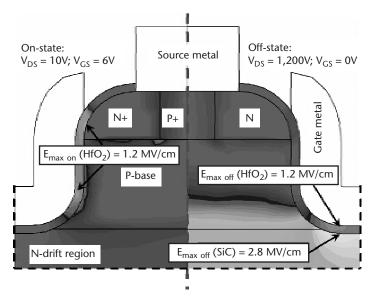

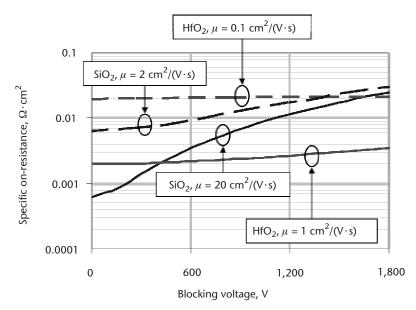

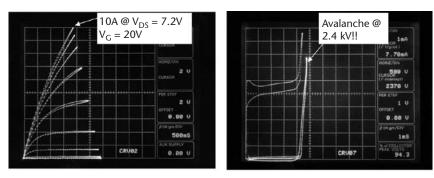

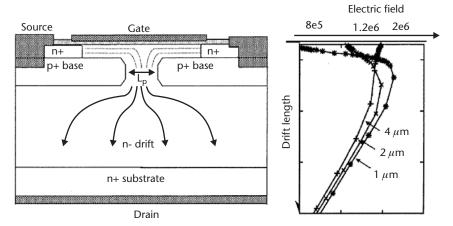

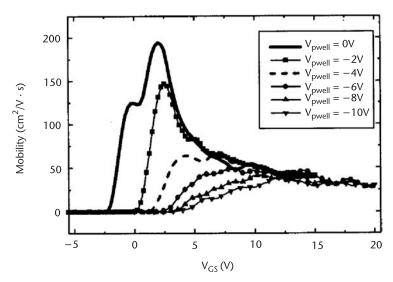

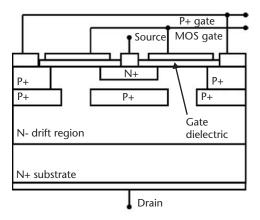

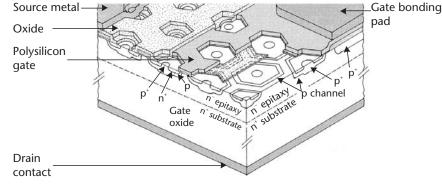

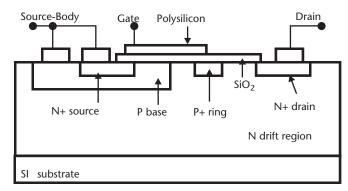

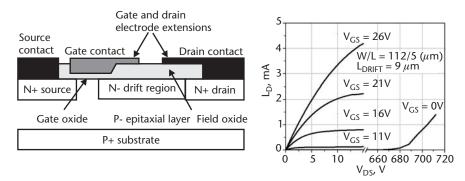

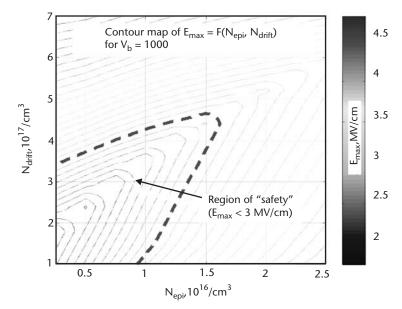

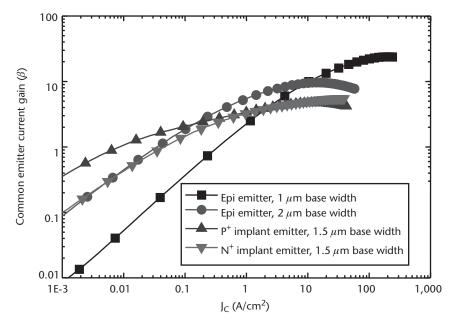

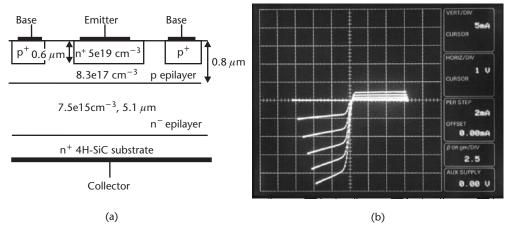

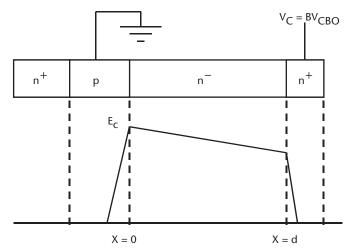

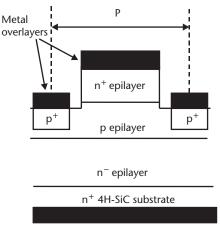

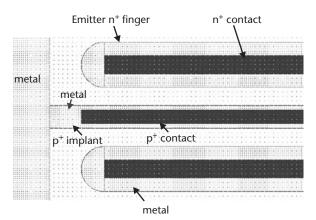

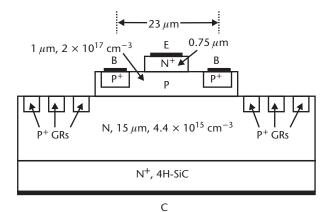

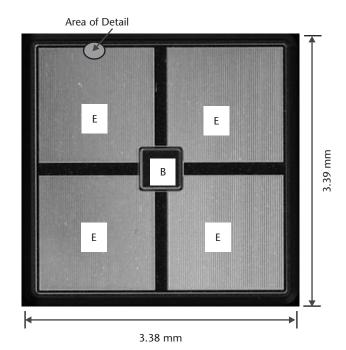

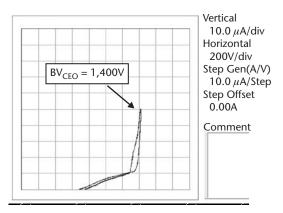

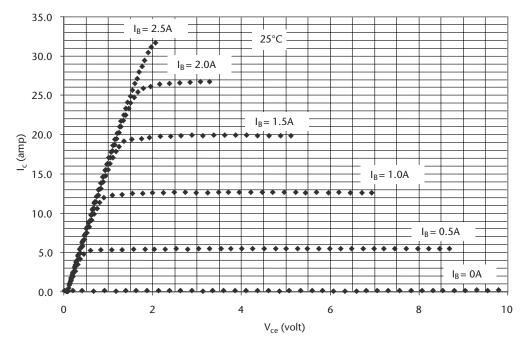

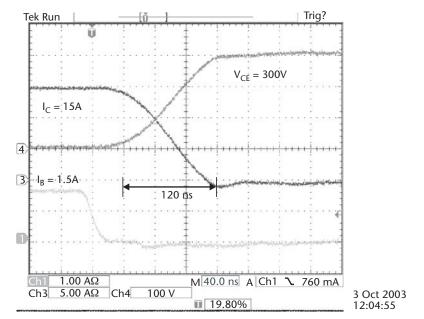

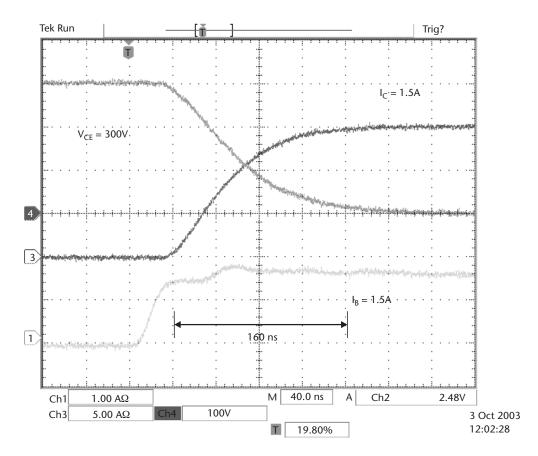

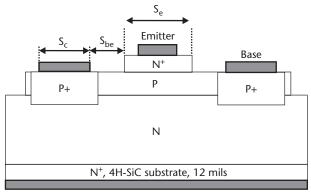

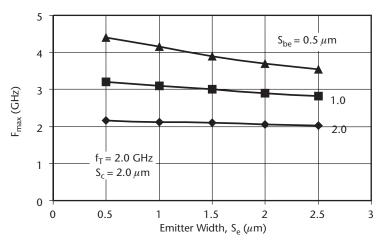

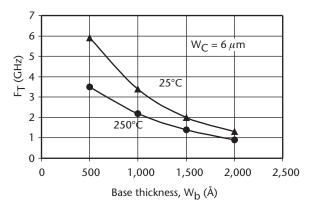

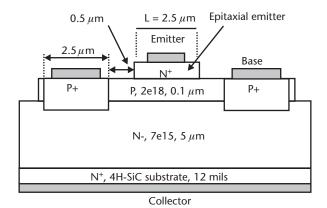

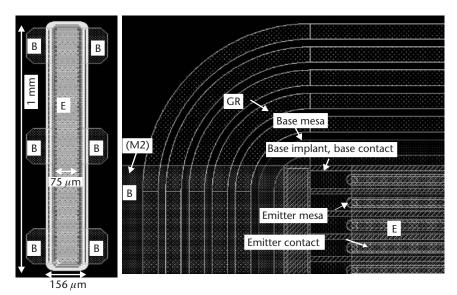

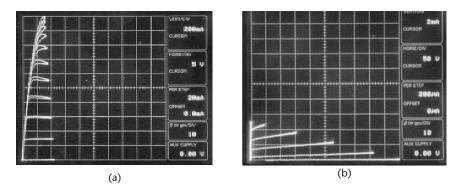

Silicon carbide has a clear place in society today, yet it has only one major commercial application today, which basically is materials or, more specifically, substrates for LED applications. This is perhaps not such a glamorous place to be in the commercial market but it does represent a significant starting point for SiC.