FRET 37 FRONTIERS IN ELECTRONIC TESTING

Mohammad Tehranipoor

# Emerging Nanotechnologies

Test, Defect Tolerance, and Reliability

Emerging Nanotechnologies

## **Frontiers in Electronic Testing**

| Series Editor: | Vishwani Agrawal  |

|----------------|-------------------|

|                | Auburn University |

|                | Auburn, Alabama   |

Emerging Nanotechnologies: Test, Defect Tolerance, and Reliability Mohammad Tehranipoor (Ed.) Volume 37, ISBN 978-0-387-74746-0, 2008

Oscillation-Based Test in Mixed-Signal Circuits G. Huertas Sánchez, D. Vázquez Garcia de la Vega, A. Rueda Rueda, and J.L. Huertas Díaz Volume 36, ISBN 978-1-4020-5314-6, 2006

The Core Test Wrapper Handbook: Rationale and Application of IEEE Std. 1500<sup>TM</sup> Francisco da Silva, Teresa McLaurin, and Tom Waayers Volume 35, ISBN 978-0-387-30751-0, 2006

Defect-Oriented Testing for Nano-Metric CMOS VLSI Circuits, Second Edition Manoj Sachdev and José Pineda de Gyvez Volume 34, ISBN 978-0-387-46546-3, 2007

Digital Timing Measurements: From Scopes and Probes to Timing and Jitter Wolfgang Maichen Volume 33, ISBN 978-0-387-31418-1, 2006

Fault-Tolerance Techniques for SRAM-Based FPGAs Fernanda Lima Kastensmidt, Luigi Carro, and Ricardo Reis Volume 32, ISBN 978-0-387-31068-8, 2006

Data Mining and Diagnosing IC Fails Leendert M. Huisman Volume 31, ISBN 978-0-387-24993-3, 2005

Fault Diagnosis of Analog Integrated Circuits Prithviraj Kabisatpathy, Alok Barua, and Satyabroto Sinha Volume 30, ISBN 978-0-387-25742-6, 2005

Introduction to Advanced System-on-Chip Test Design and Optimization Erik Larsson Volume 29, ISBN 978-1-4020-3207-3, 2005

Embedded Processor-Based Self-Test Dimitris Gizopoulos, A. Paschalis, and Yervant Zorian Volume 28, ISBN 978-1-4020-2785-7, 2004

Advances in Electronic Testing: Challenges and Methodologies Dimitris Gizopoulos (Ed.) Volume 27, ISBN 978-0-387-29408-7, 2006

Testing Static Random Access Memories: Defects, Fault Models and Test Patterns Said Hamdioui Volume 26, ISBN 978-1-4020-7752-4, 2004

Verification by Error Modeling: Using Testing Techniques in Hardware Verification Katarzyna Radecka and Zeljko Zilic Volume 25, ISBN 978-1-4020-7652-7, 2004

Elements of STIL: Principles and Applications of IEEE Std. 1450 Gregory A. Maston, Tony R. Taylor, and Julie N. Villar Volume 24, ISBN 978-1-4020-7637-4, 2003

Fault Injection Techniques and Tools for Embedded Systems Reliability Evaluation Alfredo Benso and P. Prinetto (Eds.) Volume 23, ISBN 978-1-4020-7589-6, 2003 Mohammad Tehranipoor Editor

# **Emerging Nanotechnologies**

Test, Defect Tolerance, and Reliability

Editor Mohammad Tehranipoor Department of Electrical and Computer Engineering University of Connecticut Storrs, CT 06269 USA

Series Editor Vishwani Agrawal Department of Electrical and Computer Engineering Auburn University Auburn, AL 36849 USA

ISBN 978-0-387-74746-0

e-ISBN 978-0-387-74747-7

Library of Congress Control Number: 2007933699

© 2008 Springer Science+Business Media, LLC

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper.

987654321

springer.com

# Preface

The foundations of nanotechnology have emerged over many decades of research in various fields. Over the years, computer circuits have been becoming smaller and chemicals have been getting more complex. Biochemists have learned more about how to study and control the molecular basis of organisms. Mechanical engineering has been getting more precise which resulted in, for instance, emerging nanoelectro-mechanical systems (NEMS). Computer engineering have been getting a great deal of knowledge on how to design circuits with defective components. Today, in the young field of nanotechnology, scientists and engineers of various fields are taking control of atoms and molecules individually, manipulating them and putting them to use with an extraordinary degree of precision which was considered impossible many years ago. Word of the promise of nanotechnology is spreading quickly, and the air is thick with news of nanotech breakthroughs especially over the last few years. Public awareness of nanotech is clearly on the rise, too, partly because references to it are becoming more common in popular culture and everyday life.

The wires and switches inside computer chips have been getting steadily smaller for decades. They have already crossed the 100-nm threshold, sufficient to be considered nanotechnology by the National Nanotechnology Initiative (NNI) definition. As they continue to shrink, quantum effects will become increasingly important, and future designs will stop working if not carefully taken into consideration. Researchers in academia and industry are working on various technologies, but among those there are few nanoscale technologies that could potentially take over in near future. One is molecular electronics: the use of single molecules (or sometimes, small clusters of molecules) to build wires and switches. Another is quantum dots: instead of letting electrons flow through wires, the electrons are tethered in place and only shift back and forth. This shift causes nearby electrons to shift also, which is useful for signaling and computation. Finally, carbon nanotube (CNT) based interconnects and transistors; CNTs have shown promising electrical behavior compared to copper used in Complementary Metal Oxide Semiconductor (CMOS) technology.

#### **Technology Scaling Challenges and Effects**

As functional density and operating frequency increase, the number of interconnects and length of interconnects are expected to increase as well. Over the years, the number of metal layers has incrementally increased from the original one. Using six to ten metal layers in industry is a common practice nowadays. Increasing number of metal layers in turn increases the number of vias where it is proven that vias are the main sources of defects. The situation will grow worse since the number of metal layers will even further increase going up to 12 within the next few years.

The material of the layers used in fabrication processes has also undergone a major change from aluminum to copper. Using copper provides a better scalability compared to aluminum. As technology scales and more transistors are integrated on a chip, the interconnects become longer. For high-speed nanometer technology designs the interconnect delay dominates gate delay. It is predicted that in the near future the longest path in the design will be the critical one not the paths with more gates. In nanometer technology era, crosstalk will be a major contributor to interconnect delay. To keep the resistance of the wires low as technology scales, the interconnects are becoming narrower and taller. This results in large cross-coupling capacitances which are now dominating substrate capacitances.

To reduce the power and minimize the negative impact of hot career, which causes reliability issues overtime, the power supply is reduced. However, the transistor voltage threshold is not scaling proportionally which results in increase in the circuit sensitivity and reduction in noise margin. The scaling also increases the leakage current. In 65 nm technology, the static power consumption contributes to 50% of total power consumption while it is expected to further increase in 45 and 32 nm technologies. Negative bias temperature instability (NBTI) is considered a growing threat to device reliability in sub-100 nm technologies as well.

Technology scaling also poses many challenging design and test issues. The power and speed are two important parameters in today's designs. The low power supply has increased circuits sensitivity to noise caused by IR-drop, crosstalk, and process variations. The voltage threshold does not scale proportionally resulting in reduced noise margin. The wavelength of the light used for imaging the geometries is longer than the geometry desired for printing. For example, a designer uses an almost 200 nm light source for a 130 nm gate length. The circuit speed will be limited by quantum effects along with high power and temperature in future designs. Temperature variation can significantly affect circuit performance. The process variation increases clock skew resulting higher switching activity, hence higher temperature and power supply noise. The continuous decrease in transistor feature size has been pushing the CMOS process to its physical limits caused by ultra-thin gate oxides, short channel effects, doping fluctuations, and the unavailability of lithography in nanoscale range. To be able to continue the size/speed improvement trends

according to Moore's Law, research investments are growing on a wide range of emerging devices and technologies.

#### **Emerging Technologies**

This book covers various technologies that have been suggested by researchers over the last decades such as chemically assembled electronic nanotechnology, Quantum-dot Cellular Automata (QCA), nanowires (NWs), and carbon nanotubes (CNTs). Each of these technologies offers various advantages and disadvantages. Some suffer from high power, some work in very low temperature and some other need indeterministic bottom-up assembly. These emerging technologies are not considered as a direct replacement for CMOS technology and may require a completely new architecture to achieve their functionality.

Molecular logic devices are based on electron transport properties through a single molecule. Two terminal molecular devices currently being explored consists of thousands of molecules operating in parallel as digital switches or analog diodes. In both cases, a voltage applied to a molecular layer (group of molecules in parallel) results in reconfiguration of the molecular components. This creates a nano-switch where the reconfiguration capability provide us with the opportunity for computing. A near term opportunity of molecular electronics is in integration of molecular devices with sub-50 nm CMOS components to form a hybrid system. A full-molecular system is considered a potential long-term opportunity. In addition to two terminal switches, few other molecular components emerged over the past few years, e.g. bistable switch, molecular NEMS, and spin-based molecular devices.

Carbon nanotube is a subset of molecular electronic materials. It is a cylinder formed from an atomic sheet of carbon atoms. The carbon atoms are bounded together into an array of hexagons which forms a planar sheet. This sheet is rolled up to form a tube. Carbon nanotubes can have diameters up to 15 nm and lengths up to few microns. The diameter and the way the sheet is rolled up determine whether the carbon nanotube has metal or semiconductor properties. The semiconductor tube can be doped n-type and p-type, making it possible to create n-p junction. Carbon nanotubes have shown strong current capability which makes it interesting to IC designers to replace copper with carbon nanotube, however, the integration will be expensive.

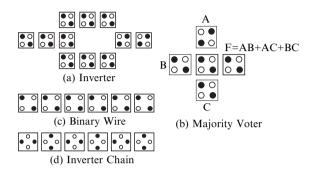

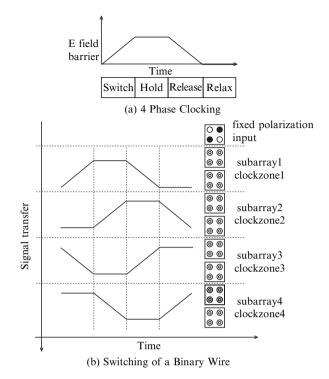

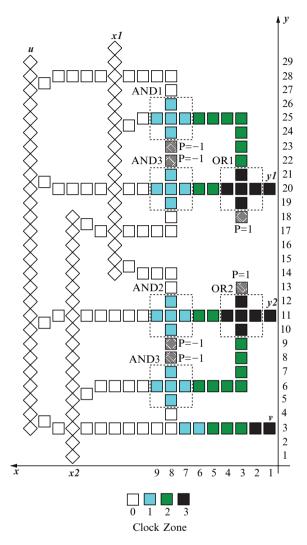

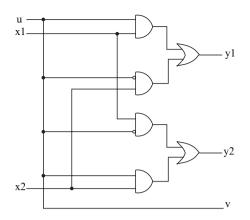

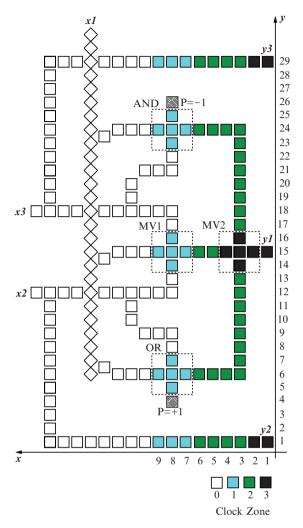

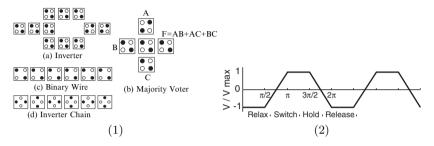

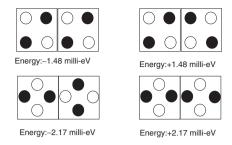

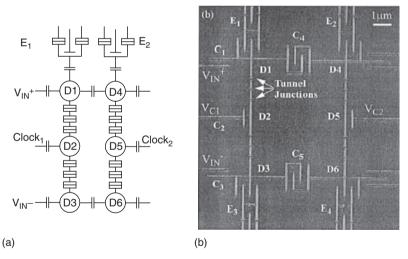

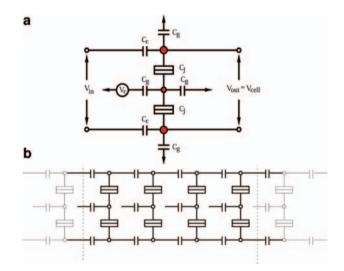

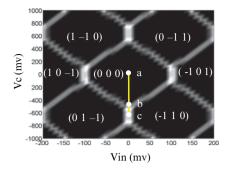

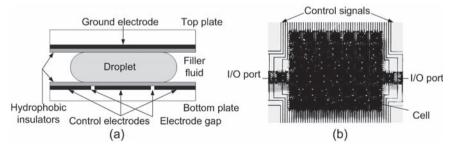

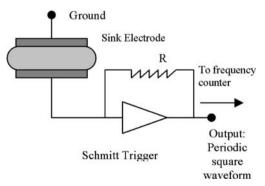

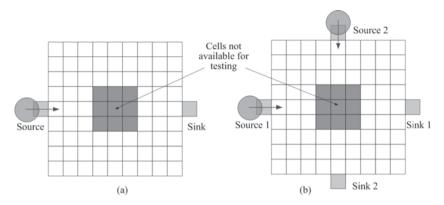

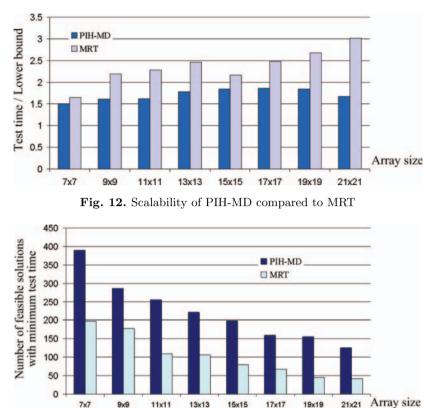

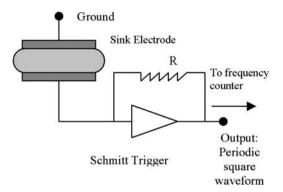

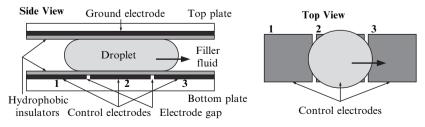

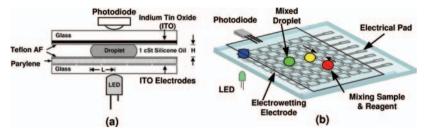

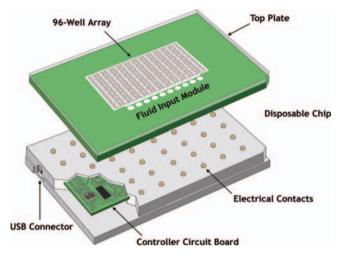

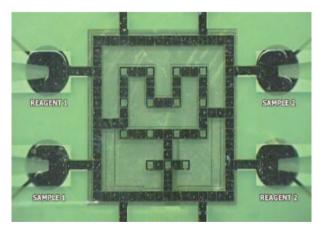

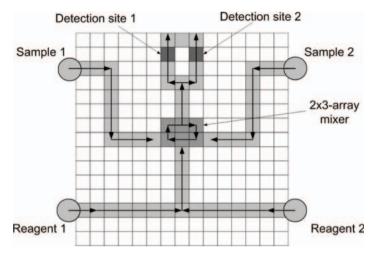

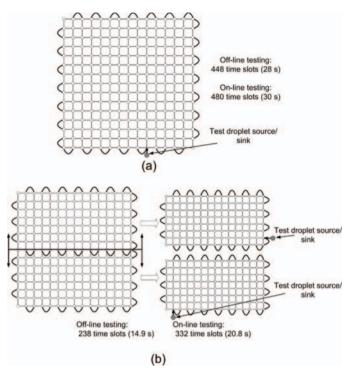

A novel mechanism for transmitting and processing information has been extensively investigated in theoretical work on quantum-dot cellular automata (QCA). This work assumes arrays of cells built from quantum dots, on a molecular scale, from individual redox centers. The charges move within the cells in response to external electric fields. It is fascinating that based on such scheme, there is no need to let charges flow through the cells. Wires, AND/OR gates, clocked QCA cells, QCA memory cell, and a shift register are the components that have been successfully demonstrated. Today, standard solid state Quantum-dot Cellular Automata cell design considers the distance between quantum dots to be about 20 nm, and a distance between cells of about 60 nm. Compared to CMOS technology, QCA is expected to present less variability at this scale. Digital microfluidics is an alternative technology for lab-on-a-chip systems based upon micromanipulation of discrete droplets. Microfluidic processing is performed on unit-sized packets of fluid which are transported, stored, mixed, reacted, or analyzed in a discrete manner using a standard set of basic instructions. Recent advances in microfluidics technology have led to the design and implementation of miniaturized devices for various biochemical applications. These microsystems have shown promises to revolutionize biosensing, clinical diagnostics, and drug discovery. Such applications can benefit from the small size of biochips compared to conventional laboratory methods.

Developments in these nanoscale technologies provide the hope that current trend of integration of electronic devices can be continued. Due to their small feature sizes and self-assembly-based fabrication methods, nanoscale devices present many challenges in the area of testing, defect tolerance, and reliability. As nanoscale fabrication technologies evolve over the next few years, testing and reliability are expected to emerge as major roadblocks to system integration.

Most of the suggested technologies offer very high defect density (up to 10%). Increasing defect density decreases yield and with such a high defect density in nano-devices the manufacturing cost can be prohibitively high and discarding a defective nano-chip will no longer be possible. As a result, to achieve high reliability, nanoscale devices must be thoroughly tested, diagnosed and the location of defects must be found. Novel defect tolerance methods and architectures must be developed to deal with such high defect densities. For example, architectures similar to field programmable gate array (FPGA) have been suggested to use crossbars built from nanowires/nanotubes. Such crossbars can be programmed and the defects can be avoided if the location of defects is known. Similarly, in other nano-devices and architectures, a reliable system can be created using defective devices.

This book is divided into five sections. Section 1 includes five chapters that discuss different aspects of test and defect tolerance for crossbarbased nanoscale devices. The reconfiguration feature of the proposed nanoarchitectures provides an ability to test these devices and avoid the defective ones. Section 2 contains four chapters focusing on test, defect tolerance and reliability for QCA circuits.

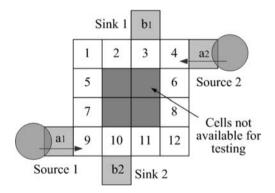

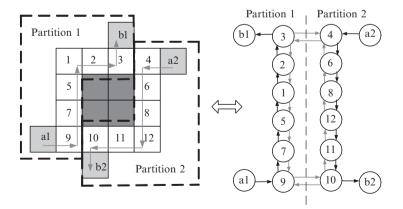

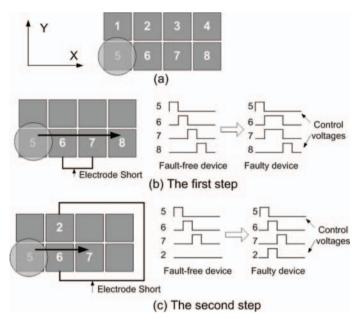

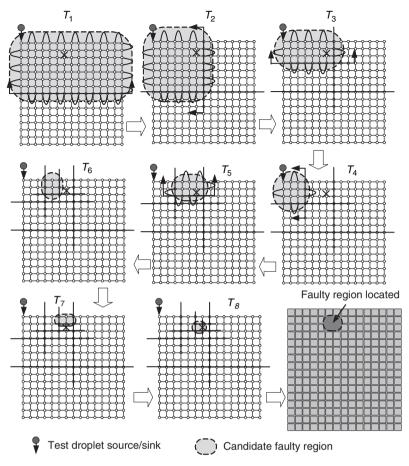

There are two chapters in Sect. 3 which present methods for testing and diagnosis of realistic defects in digital microfluidic biochips. Due to the underlying mixed-technology and mixed-energy domains, biochips exhibit unique failure mechanisms and defects. Finally, Sect. 4 contains three chapters dealing with reliability of CMOS scale devices, developing nanoscale processors and future molecular electronics-based circuits.

$Mohammad\ Tehranipoor$

July 2007 University of Connecticut

# Contents

| Section 1: Test and Defect Tolerance for Crossbar-Based         Architectures         M. Tehranipoor                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1: Defect-Tolerant Logic with Nanoscale Crossbar         Circuits         T. Hogg and G. Snider         5                                   |

| Chapter 2: Built-in Self-Test and Defect Tolerance         in Molecular Electronics-Based Nanofabrics         Z. Wang and K. Chakrabarty            |

| Chapter 3: Test and Defect Tolerance for Reconfigurable         Nanoscale Devices         M. Tehranipoor and R. Rad       63                        |

| Chapter 4: A Built-In Self-Test and Diagnosis Strategy<br>for Chemically-Assembled Electronic Nanotechnology<br>J.G. Brown and R.D. (Shawn) Blanton |

| Chapter 5: Defect Tolerance in Crossbar Array<br>Nano-Architectures<br>M.B. Tahoori                                                                 |

| Section 2: Test and Defect Tolerance for QCA Circuits <i>M. Tehranipoor</i>                                                                         |

| Chapter 6: Reversible and Testable Circuits for Molecular<br>QCA Design<br>X. Ma, J. Huang, C. Metra, and F. Lombardi                               |

| Chapter 7: Cellular Array-Based Delay-Insensitive<br>Asynchronous Circuits Design and Test for Nanocomputing<br>Systems<br>J. Di and P.K. Lala                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 8: QCA Circuits for Robust Coplanar Crossing<br>S. Bhanja, M. Ottavi, S. Pontarelli, and F. Lombardi                                                         |

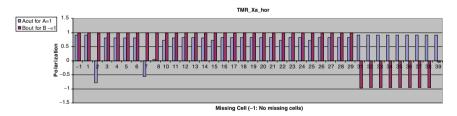

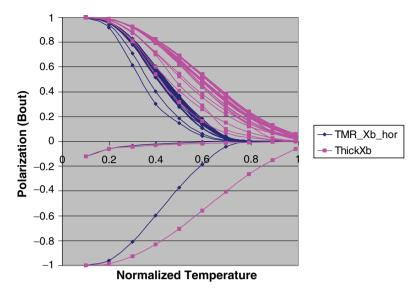

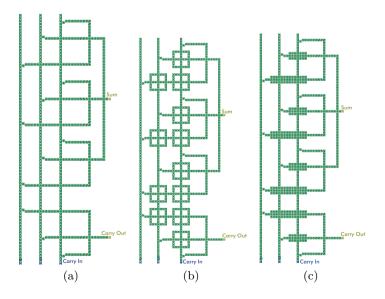

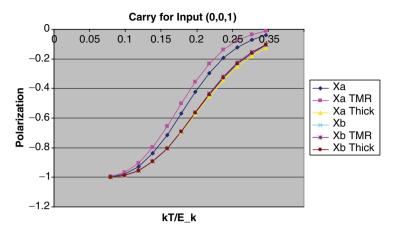

| Chapter 9: Reliability and Defect Tolerance in Metallic<br>Quantum-Dot Cellular Automata<br>M. Liu and C.S. Lent                                                     |

| Section 3: Testing Microfluidic Biochips<br>M. Tehranipoor                                                                                                           |

| Chapter 10: Test Planning and Test Resource Optimization<br>for Droplet-Based Microfluidic Systems<br>F. Su, S. Ozev, and K. Chakrabarty                             |

| Chapter 11: Testing and Diagnosis of Realistic Defects<br>in Digital Microfluidic Biochips<br>F. Su, W. Hwang, A. Mukherjee, and K. Chakrabarty287                   |

| Section 4: Reliability for Nanotechnology Devices <i>M. Tehranipoor</i>                                                                                              |

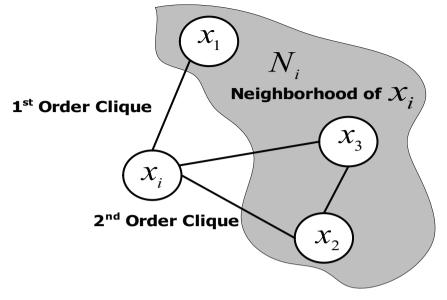

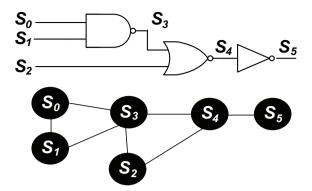

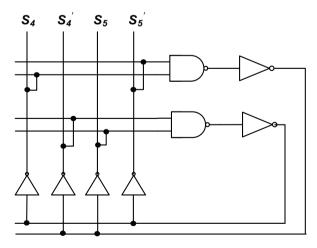

| Chapter 12: Designing Nanoscale Logic Circuits<br>Based on Principles of Markov Random Fields<br>K. Nepal, R.I. Bahar, J. Mundy, W.R. Patterson, and A. Zaslavsky315 |

| Chapter 13: Towards Nanoelectronics Processor Architectures<br>W. Rao, A. Orailoglu, and R. Karri                                                                    |

| Chapter 14: Design and Analysis<br>of Fault-Tolerant Molecular Computing Systems<br>D. Bhaduri, S.K. Shukla, H. Quinn, P. Graham, and M. Gokhale373                  |

| Index                                                                                                                                                                |

# List of Contributors

**R. Iris Bahar** Brown University Division of Engineering Providence, RI 02912

Debayan Bhaduri Virginia Polytechnic Institute and State University dbhaduri@vt.edu

Sanjukta Bhanja Department of Electrical Engineering University of South Florida Tampa, (FL) 33620, USA bhanja@eng.usf.edu

**R.D. (Shawn) Blanton** Carnegie Mellon University

Jason G. Brown Carnegie Mellon University

Krishnendu Chakrabarty Duke University

**Jia Di** University of Arkansas

Maya Gokhale Los Alamos National Laboratory Paul Graham Los Alamos National Laboratory

**Tad Hogg** HP Labs, 1501 Page Mill Road Palo Alto, CA

Jing Huang Department of Electrical and Computer Engineering Northeastern University Boston, MA 02115 hjing@ece.neu.edu

William Hwang Oxford University

Ramesh Karri Polytechnic University

Parag K. Lala Texas A&M University at Texarkana

Craig S. Lent Department of Electrical Engineering University of Notre Dame Notre Dame, IN 46556 USA lent@nd.edu

Mo Liu Department of Electrical Engineering University of Notre Dame Notre Dame, IN 46556 USA mliu1@nd.edu

## Fabrizio Lombardi

Department of Electrical and Computer Engineering Northeastern University Boston, (MA) 02115, USA lombardi@ece.neu.edu

## X. Ma

Department of Electrical and Computer Engineering Northeastern University Boston, MA 02115 xma@ece.neu.edu

## Cecillia Metra

Department of Electrical Engineering University of Bologna Bologna, Italy cmetra@deis.unibo.it

Arindam Mukherjee University of North Carolina at Charlotte

**J. Mundy** Brown University Division of Engineering Providence, RI 02912

Kundan Nepal Bucknell University Department of Electrical Engineering Lewisburg, PA 17837

Alex Orailoglu University of California, San Diego

Marco Ottavi Department of Electrical and Computer Engineering Northeastern University Boston, (MA) 02115, USA mottavi@ece.neu.edu

Sule Ozev Duke University

W. R. Patterson Brown University Division of Engineering Providence, RI 02912 Salvatore Pontarelli

Dipartimento di Ingegneria Elettronica Università di Roma "Tor Vergata" Rome, 00133, Italy pontarelli@ing.uniroma2.it

## Heather Quinn

Los Alamos National Laboratory

Reza Rad University of Maryland Baltimore County reza2@umbc.edu

**Wenjing Rao** University of California, San Diego

Sandeep K. Shukla Virginia Polytechnic Institute and State University shukla@vt.edu

**Greg Snider** HP Labs, 1501 Page Mill Road Palo Alto, CA

**Fei Su** Intel Corporation

Mehdi B. Tahoori Northeastern University Boston, MA

Mohammad Tehranipoor University of Connecticut tehrani@engr.uconn.edu

**Zhanglei Wang** Cisco Systems, Inc.

**A. Zaslavsky** Brown University Division of Engineering Providence, RI 02912

# Section 1: Test and Defect Tolerance for Crossbar-Based Architectures

M. Tehranipoor

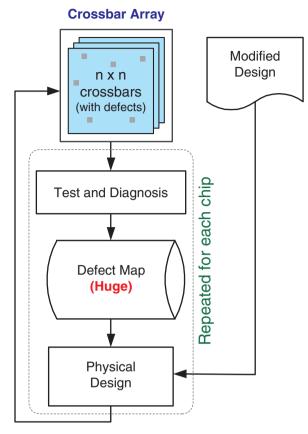

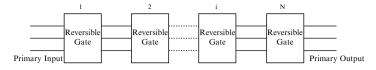

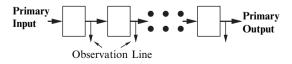

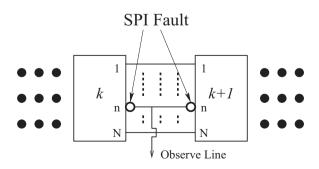

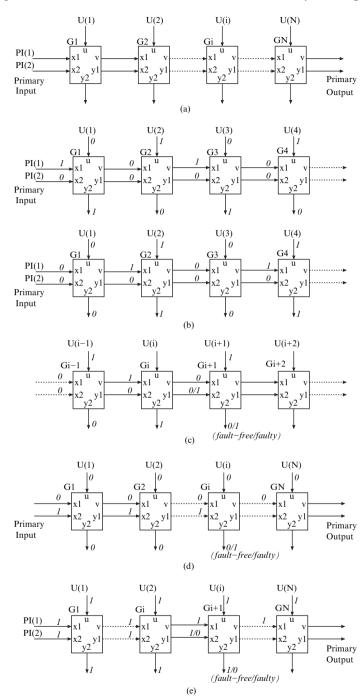

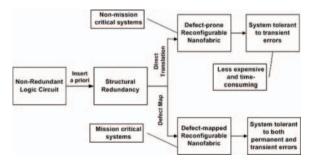

As complementary metal oxide semiconductor (CMOS) devices are scaled down into the nanometer regime, new challenges at both the device and system levels are arising. New devices and structures are being researched within the device community including regular and reconfigurable nano-crossbar arrays. Crossbar architectures are one approach to molecular electronic circuits for memory and logic applications. However, currently feasible manufacturing technologies for molecular electronics introduce numerous defects so insisting on defect-free crossbars would give unacceptably low yields. Conventional test and defect tolerance methods employed for CMOS reconfigurable devices such as FPGA are not applicable to emerging nanoscale devices due mainly to the high defect rates in nanotechnology. This section contains five chapters that present novel methods of test and defect tolerance for such high defect density nano-devices. The proposed methods try to alleviate problems such as (1) defect identification, localization and isolation, (2) defect map generation and defect avoidance, (3) test under very high defect rates, and (4) design flow under high defect rates condition.

The first chapter, entitled "Defect-Tolerant Logic with Nanoscale Crossbar Circuits", argues that increasing the area of the crossbar provides enough redundancy to implement circuits in spite of the defects. The authors identify reliability thresholds in the ability of defective crossbars to implement boolean logic. These thresholds vary among different implementations of the same logical formula, allowing molecular circuit designers to trade-off reliability, circuit area, crossbar geometry and the computational complexity of locating functional components. These choices are illustrated in this chapter for binary adders. For instance, one adder implementation yields functioning circuits 90% of the time with 30% defective crossbar junctions using an area only 1.8 times larger than the minimum required for a defect-free crossbar. The authors also describe an algorithm for locating a combination of functional junctions that can implement an adder circuit in a defective crossbar.

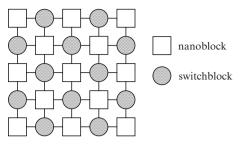

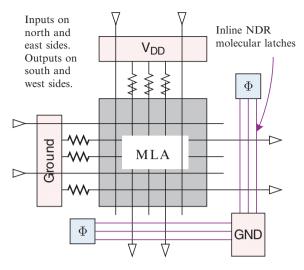

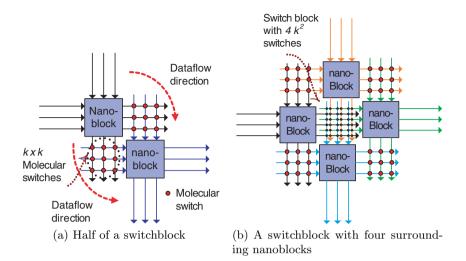

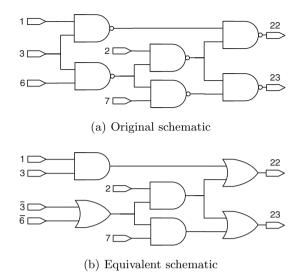

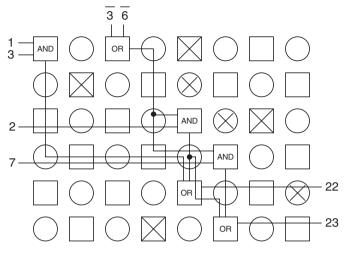

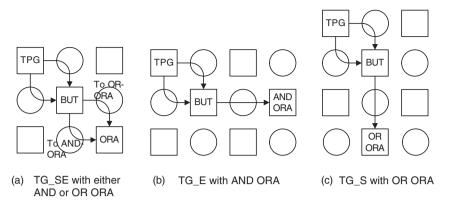

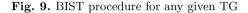

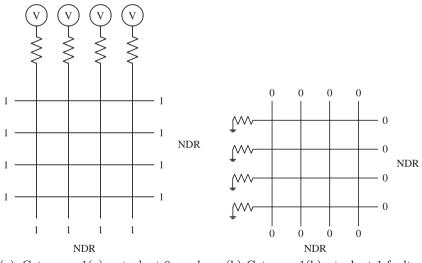

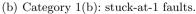

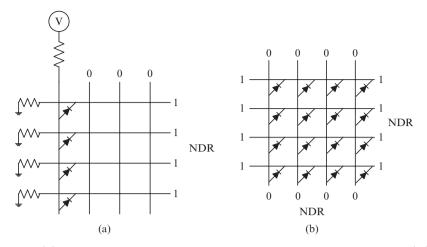

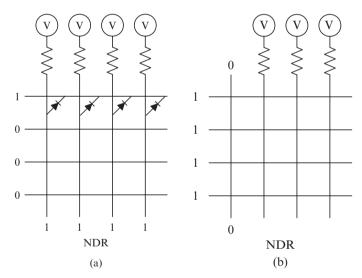

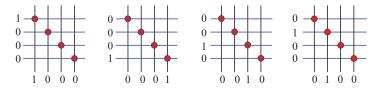

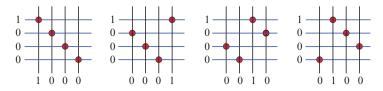

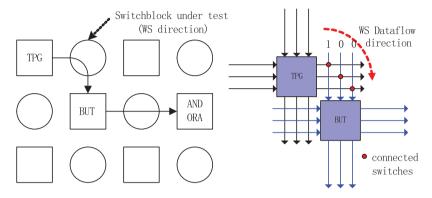

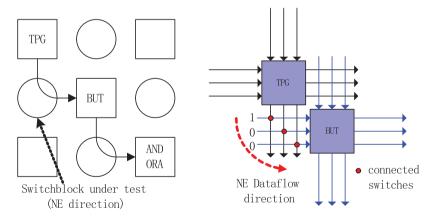

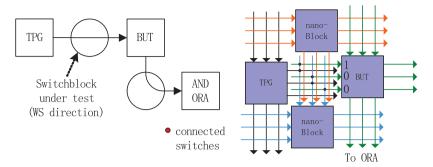

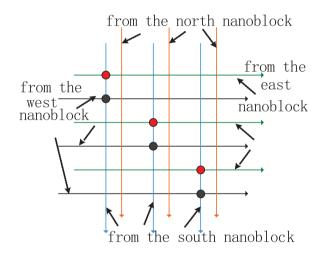

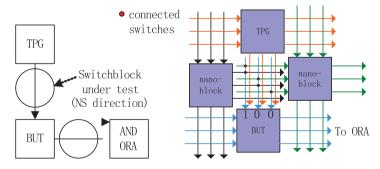

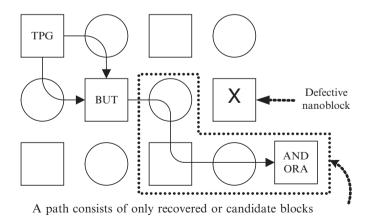

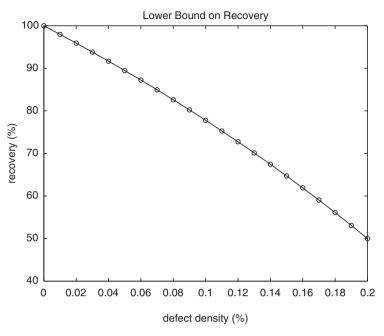

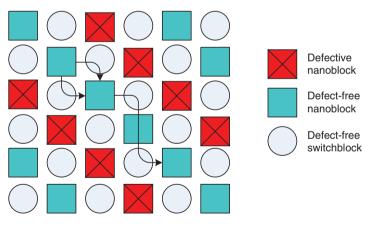

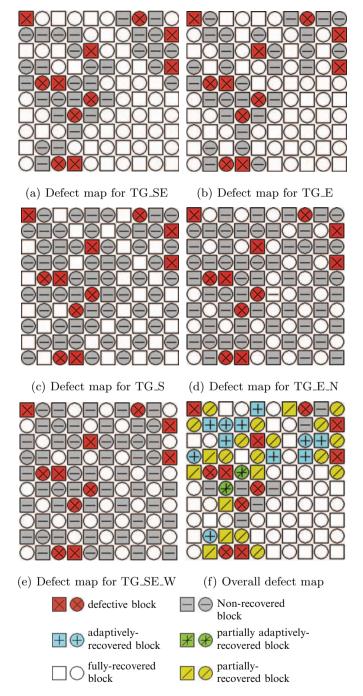

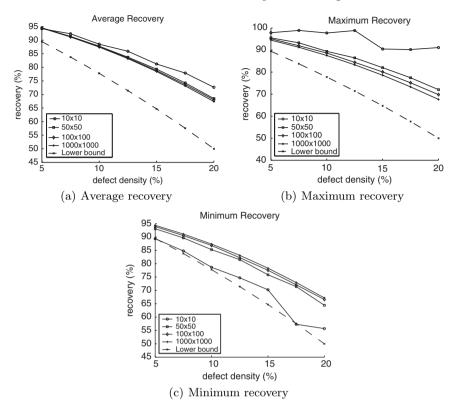

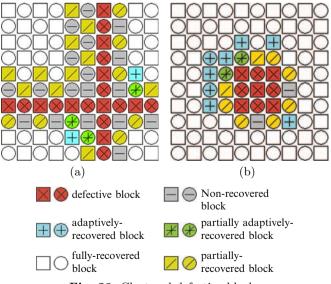

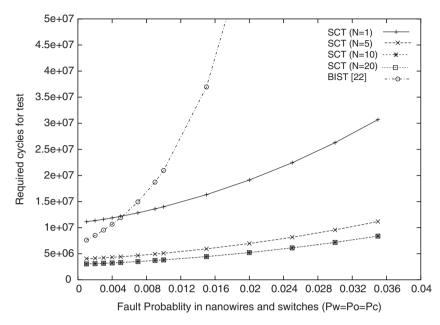

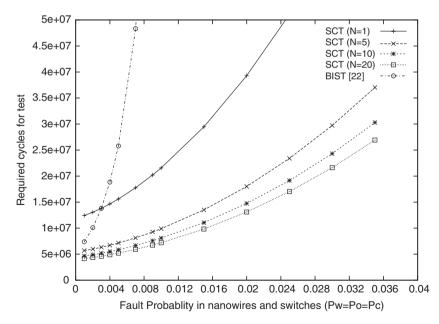

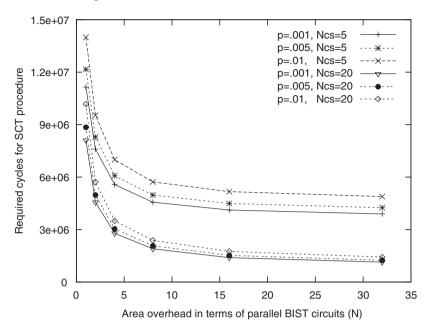

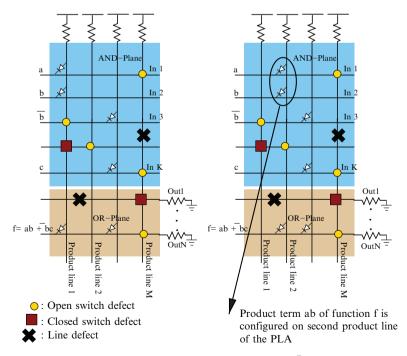

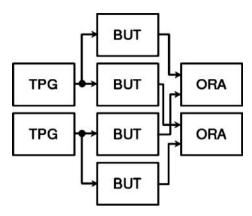

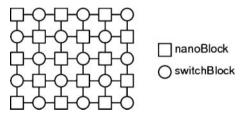

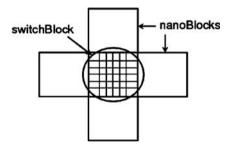

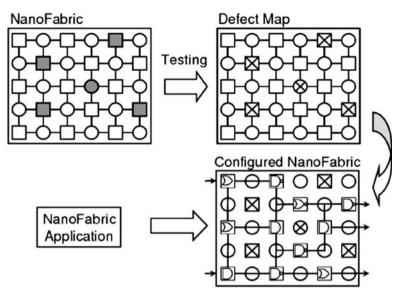

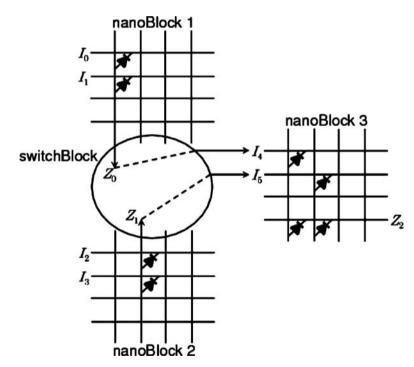

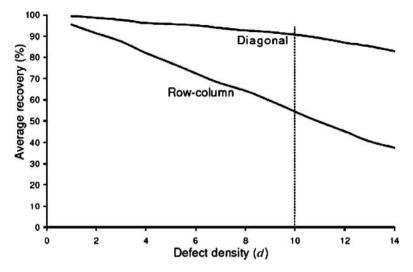

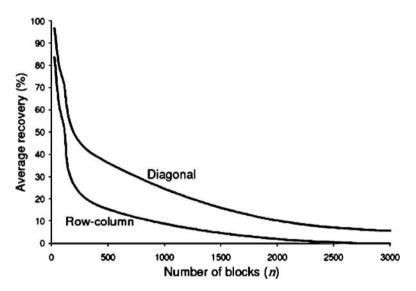

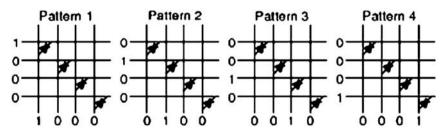

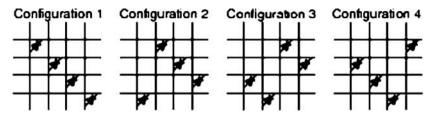

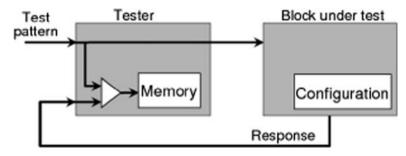

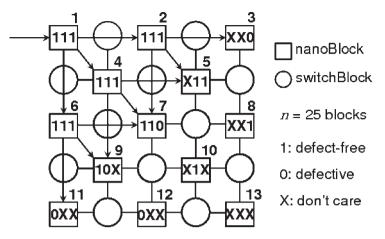

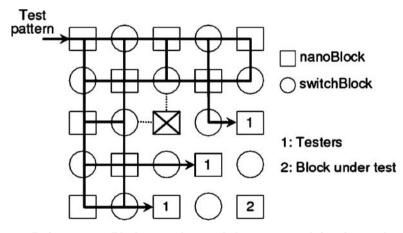

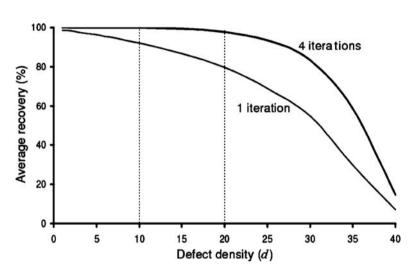

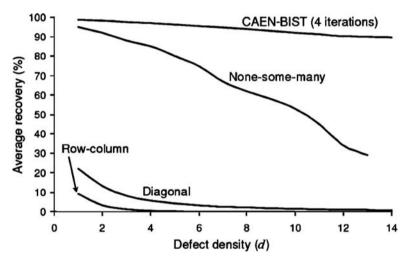

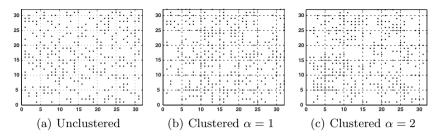

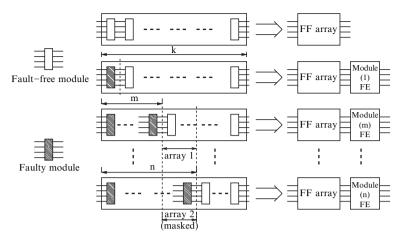

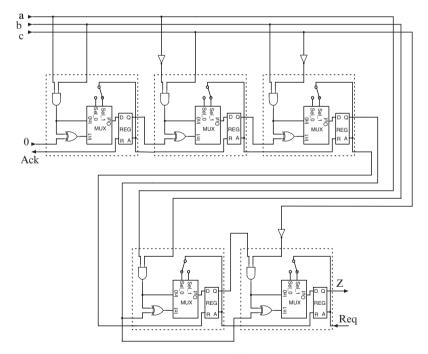

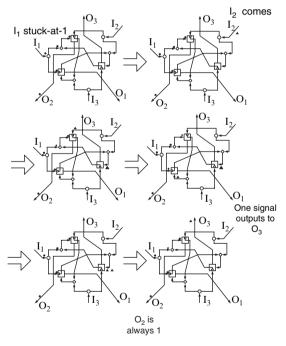

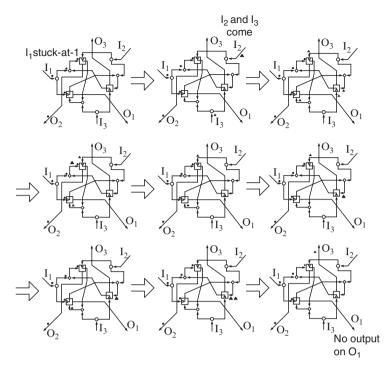

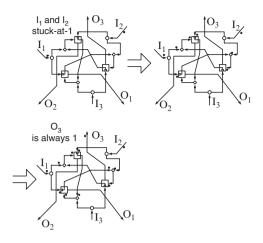

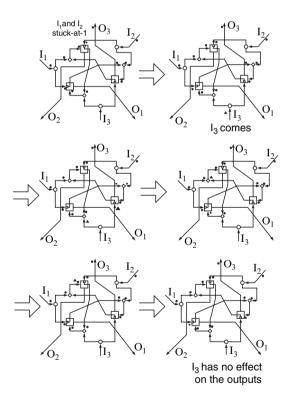

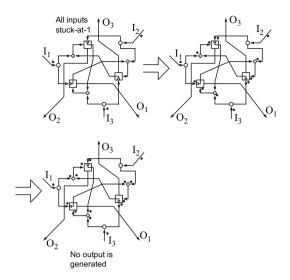

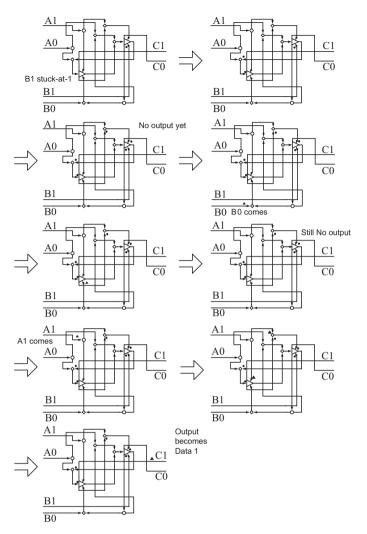

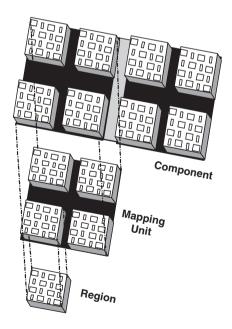

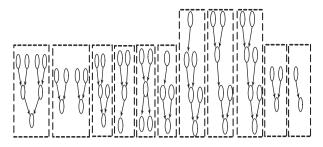

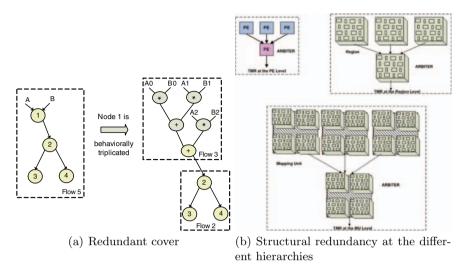

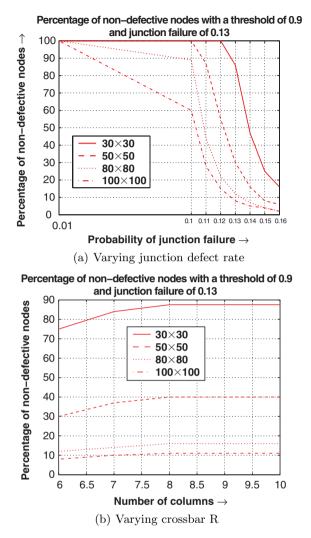

Chapter 2, entitled "Built-In Self-Test and Defect Tolerance in Molecular Electronics-Based Nanofabrics", presents a method to test nanoblocks and switchblocks in a nano-architecture and identify the location of defects. The authors in this chapter propose a built-in self-test (BIST) procedure for nanofabrics implemented using chemically assembled electronic nanotechnology. Several fault detection configurations are presented to target stuck-at faults, shorts, opens, and connection faults in nanoblocks and switchblocks. The detectability of multiple faults in blocks within the nanofabric is also considered. The authors also present an adaptive recovery procedure through which defect-free nanoblocks and switchblocks in the nanofabric-under-test can be identified. The proposed BIST, recovery, and defect tolerance procedures, in this chapter, are based on the reconfiguration of the nanofabric to achieve complete fault coverage for different types of faults. It is shown that a large fraction of defect-free blocks can be recovered using a small number of BIST configurations. The authors also present simple bounds on the recovery that can be achieved for a given defect density. Simulation results are presented for various nanofabric sizes, different defect densities, and for random and clustered defects.

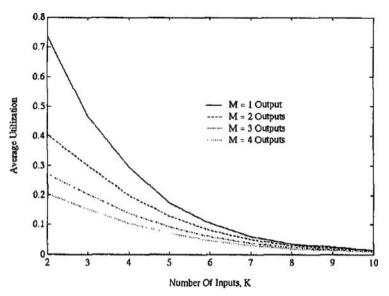

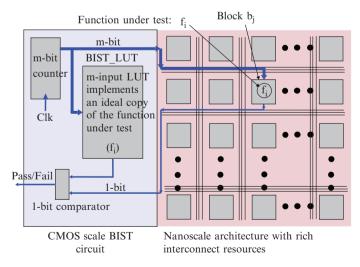

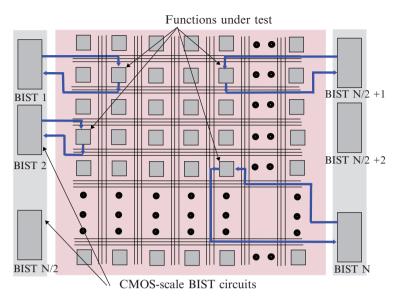

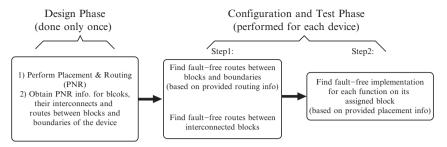

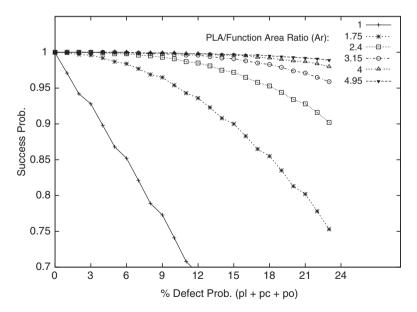

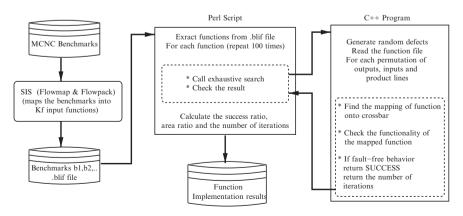

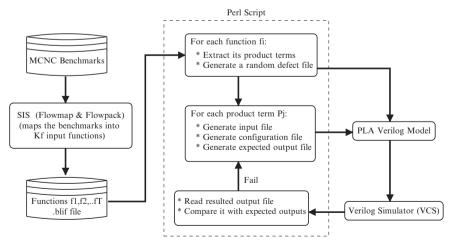

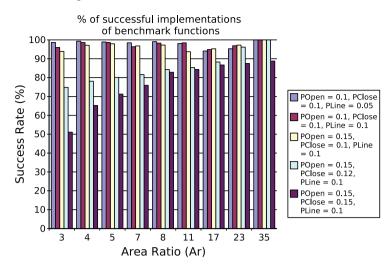

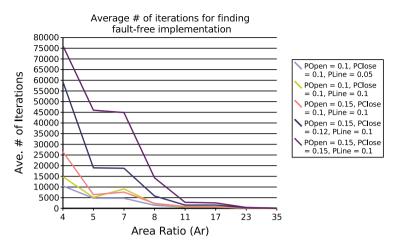

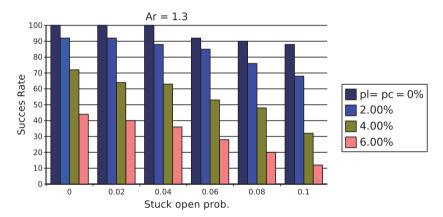

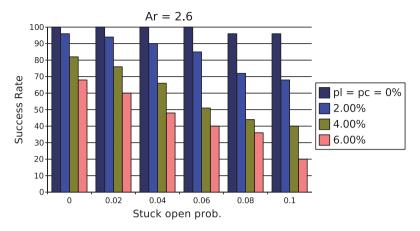

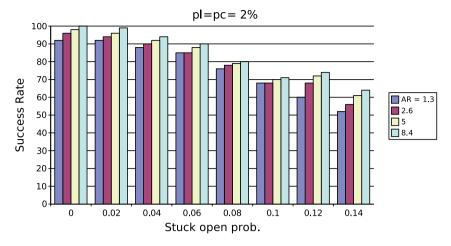

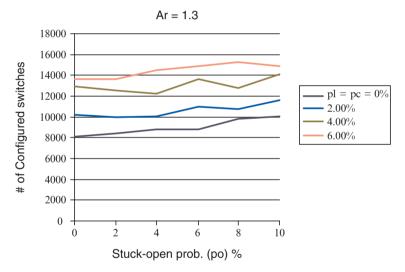

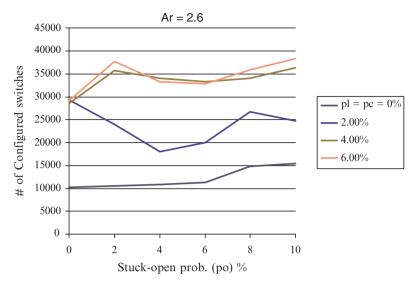

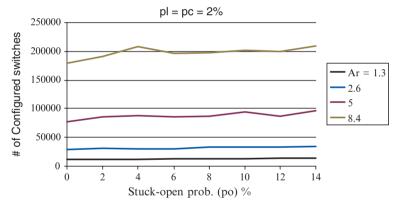

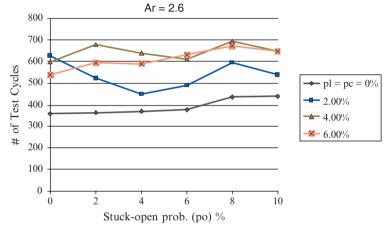

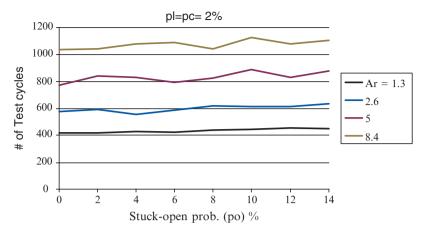

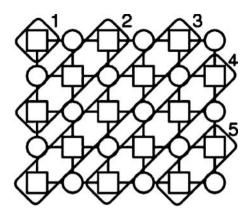

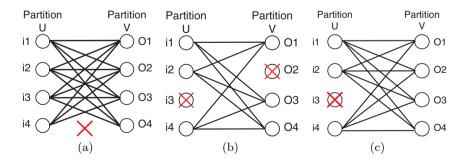

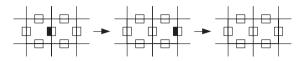

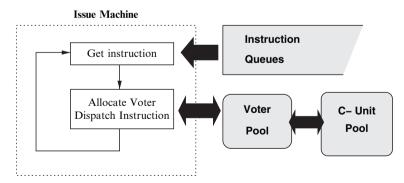

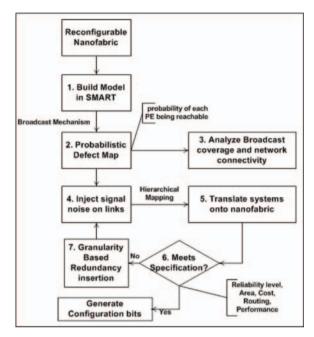

The third chapter entitled "Test and Defect Tolerance for Reconfigurable Nanoscale Devices" presents a solution to dealing with issues such as storing large defect map size and per chip placement and routing. In this chapter, the authors present a new test method in addition to novel defect avoidance methods for reconfigurable nanoscale crossbar-based devices. The proposed defect tolerance methods are independent on defect map and avoid per chip placement and routing. The test procedure proposed in this chapter is a builtin self-test method that tests the function implemented on a logic block instead of testing the block itself. The method avoids generation of large defect map and speeds up the configuration process. Probabilistic analyses are presented to show efficiency of the methods in avoiding defects in such high density devices. Two simulation programs are developed and several experiments are performed on MCNC benchmarks to evaluate the proposed methods in terms of yield and timing requirements.

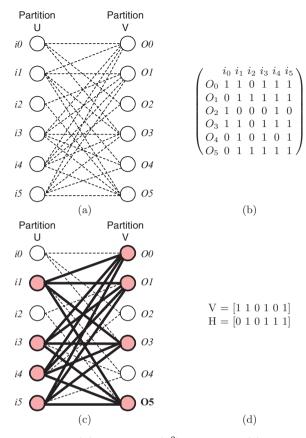

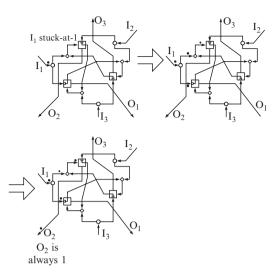

Chapter 4, entitled "A Built-in Self-test and Diagnosis Strategy for Chemically Assembled Electronic Nanotechnology", illustrates that the highly defective nanosclae circuits will require a completely new approach to manufacturing computational devices. In order to achieve any level of significant yield, it will no longer be possible to discard a device once a defect is found. Instead, a method of using defective chips must be devised. A testing strategy is developed for chemically assembled electronic nanotechnology (CAEN) that takes advantage of reconfigurability to achieve 100% fault coverage and nearly 100% diagnostic accuracy.

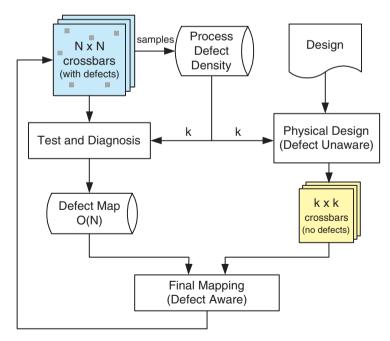

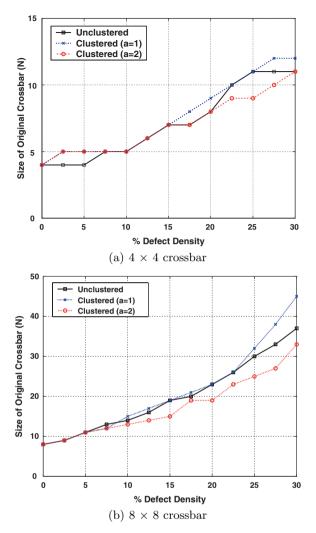

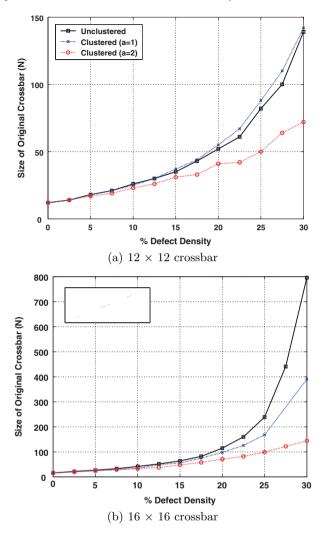

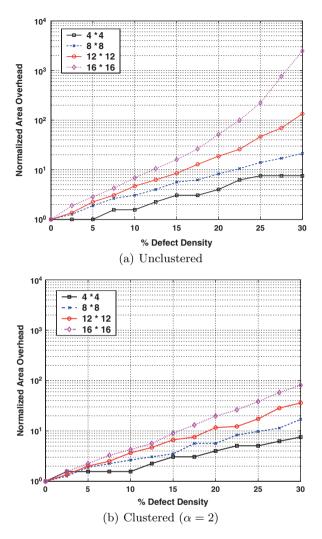

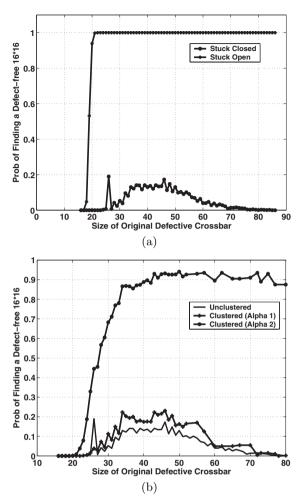

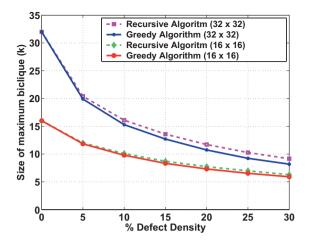

Finally, the fifth chapter in this section entitled "Defect Tolerance in Crossbar Array Nano-Architectures" presents an application-independent defecttolerant design flow to minimize customized post-fabrication design efforts to be performed per chip. In this flow, higher level design steps are not needed to be aware of the existence and the location of defects in the chip. Only a final mapping step is required to be defect-aware. Application independence of this flow minimizes the amount of per chip design steps, making it appropriate for high volume production. The manufacturing yield of molecular crossbars is analyzed under different defect distribution models. The authors report on the size of the minimum crossbar to be fabricated such that a defect-free crossbar of the desirable size can be found with a guaranteed manufacturing yield.

# Chapter 1: Defect-Tolerant Logic with Nanoscale Crossbar Circuits

T. Hogg and G. Snider

## 1 Introduction

Molecular electronics offers the possibility of significantly denser circuits than current lithography-based manufacturing. Achieving this potential requires circuit designs exploiting the capabilities of molecular electronics while compensating for limitations of current fabrication approaches, particularly defects. Creating such circuits in spite of fabrication defects requires economic trade-offs. For instance, accepting lower yields or improving fabrication could reduce defect rates, but increase production cost. Algorithmic configuration strategies for defect-tolerant systems [28], discussed in this chapter, provide higher defect tolerance, but add to manufacturing cost with the additional testing and analysis required. Evaluating this strategy requires determining what defect rates are tolerable *at all*, i.e., is there some level of defects beyond which constructing circuits is not practical? If we can accommodate defects, how much area overhead is required and how is it affected by choice of circuit geometry? This chapter is an empirical exploration of these questions.

We consider a particular type of molecular circuit, the crossbar described in Sect. 2. For nanoscale crossbars, the main type of defect is that introduced during manufacture (so-called "static defects") rather than during operation. This is reasonable for plausible fabrication technologies, which involve high temperatures during manufacture, and hence a relative ease of introducing defects, but low temperature during operation, with much less chance of creating new defects. In this situation, an appropriate systems architecture consists of a compiler to arrange for desired circuit behaviors by only using correctly functioning components of a given crossbar circuit, as determined from a testing phase after manufacture [15]. This approach of avoiding known defects gives a defect-tolerant system architecture. It contrasts with methods dealing with faults that may appear during the operation of the device, perhaps intermittently, e.g., using majority votes from replicated hardware [32]. This leads to the central question addressed in this chapter: given a defect rate and a certain size crossbar, how likely is it we can find a way to implement a particular logical formula in the crossbar? Determining whether such a circuit exists, and if so, finding one, is a combinatorial search problem. Thus a related question is the computational difficulty for the compiler to identify an implementation, or conclude no implementation is possible. For a given desired circuit and crossbar size, decreasing the defect rate will generally require more difficult and costly manufacturing. On the other hand, increasing the allowable defect rate will make it less likely the desired circuit can be implemented and can also result in longer runtimes for the compiler to identify a way to implement the circuit while avoiding the defects.

Furthermore, a logical formula can be written in various logically equivalent forms, e.g.,

## (a OR b) AND c(a AND c) OR (b AND c)

are logically equivalent. These *rewrites* can involve different numbers of terms, and hence require different crossbar areas and shapes to implement. They can also differ in their likelihood of being implementable on crossbars with defects.

After describing the molecular crossbar hardware and the defect model evaluated in this chapter, we consider a simple example of implementing AND logic gates. We then turn to a more interesting circuit: the binary adder. We first describe two approaches to implementing adders using crossbars, and then show their feasibilities in the face of defects. We thus show how crossbar architectures can implement logic circuits, even with numerous manufacturing defects.

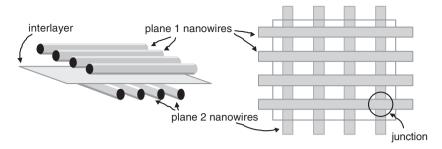

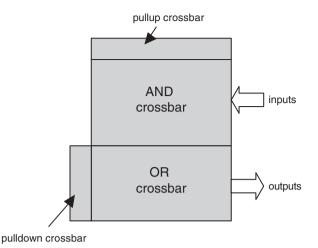

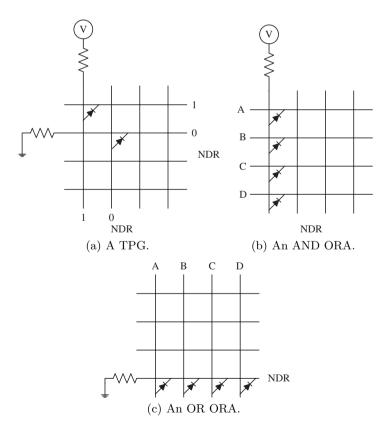

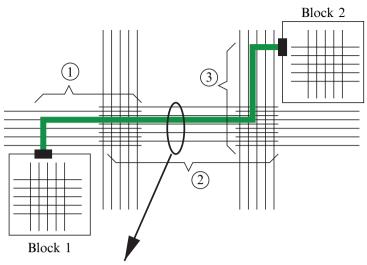

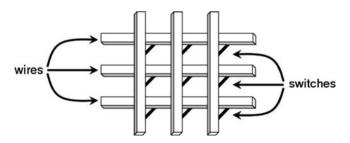

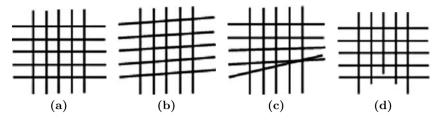

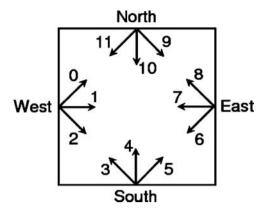

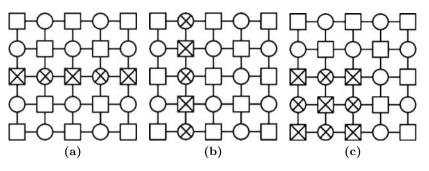

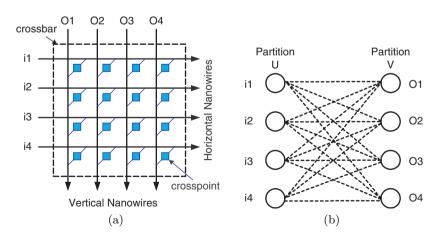

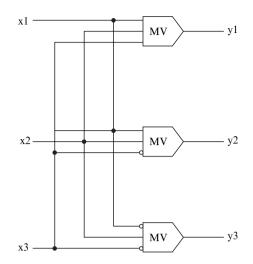

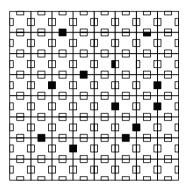

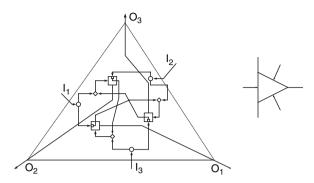

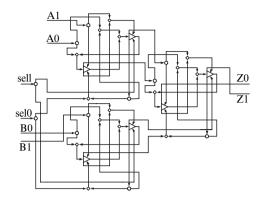

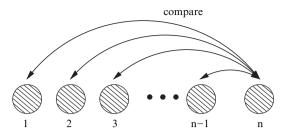

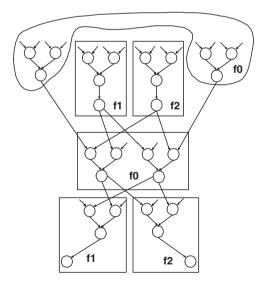

## 2 Crossbar Architecture

The crossbar architecture is a general approach for molecular circuits [2–4, 6, 14, 19, 21, 25, 30]. A molecular crossbar consists of two parallel planes of molecular wire arrays separated by a thin layer of a chemical species (called the "interlayer") with particular electrochemical properties (Fig. 1). Each plane consists of a number of parallel molecular wires (also called "nanowires"), with each wire in a plane being of the same type. The wires in one plane cross the wires in the other plane at a right angle. The region where two perpendicular wires cross is called a junction or crosspoint. Depending on the nature of the interlayer and nanowires, each junction may be configured to implement an electronic device, such as a resistor, diode or field effect transistor [22], or may be left unconfigured so the two crossing wires do not interact electrically. We consider crossbars whose junctions can only be configured as either resistors or diodes, since those are easier to fabricate with current technology than configurable transistors.

**Fig. 1.** Schematic view of a molecular crossbar from two different perspectives. Each junction may be independently configured to behave as an electronic device

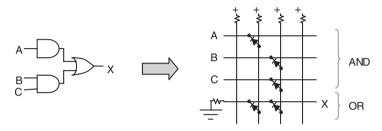

**Fig. 2.** Implementing the AND/OR function X = A + BC with a diode crossbar and resistors

The crossbar structure is an attractive architecture for molecular electronics since it is relatively simple and inexpensive to fabricate using either chemical self-assembly or nanoimprint lithography.

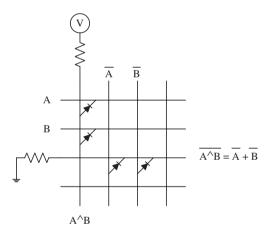

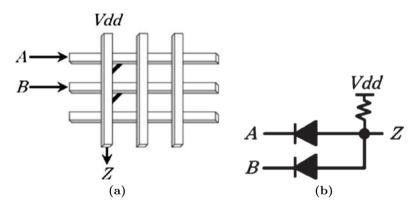

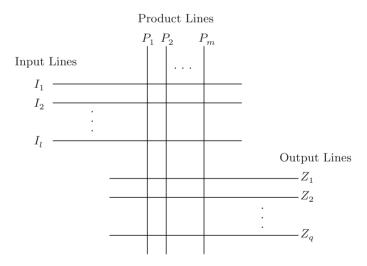

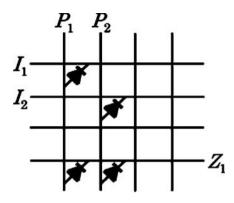

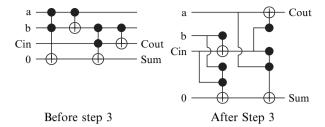

By suitable selection of the type of connections at each crosspoint (e.g., no connection, or a diode in one direction or the other), crossbars can be set to evaluate any logical formula expressed as a combination of AND and OR operations. Figure 2 shows one example. To see this, consider the output wire, labeled "X". It is connected to ground through a resistor, and via diode junctions to the second and third vertical wires. If both vertical wires are at low voltage ("off"), then the output wire X will also be at low voltage due to its connection to ground. On the other hand, if either of the connected vertical wires is at high voltage ("on"), the diode connection from the high voltage vertical wire(s) will give a high voltage to the output wire (since, by design, the diode resistance in the forward direction is much smaller than the resistor connecting the output wire to ground). If only one of the vertical wires is on, the high resistance of the diode junction in the reverse direction ensures that the output wire remains at high voltage. Thus this combination of resistors and diode connections makes the output X equal to the logical-OR of the inputs on the two vertical wires. Similarly, the connections from the inputs A, B and C implement logical-ANDs. Typical voltage drop across a forward-biased diode is about 0.6 V, and resistors are about  $100 \text{ k}\Omega$ .

The crossbar of Fig. 2 connects each column, through a *pullup* resistor, to a positive voltage source. With the diode directions shown here, each column implements the logical-AND of its inputs (the horizontal wires). Each output row, connected to ground through a *pulldown* resistor, implements the logical-OR of the columns connected to it through diode junctions. Although this is not the only way to configure crossbar circuits, it provides a simple functional form in which each output is the logical-OR of a number of terms, each of which is the logical-AND of some inputs.

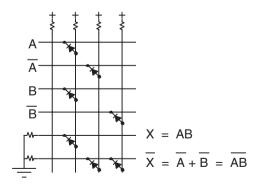

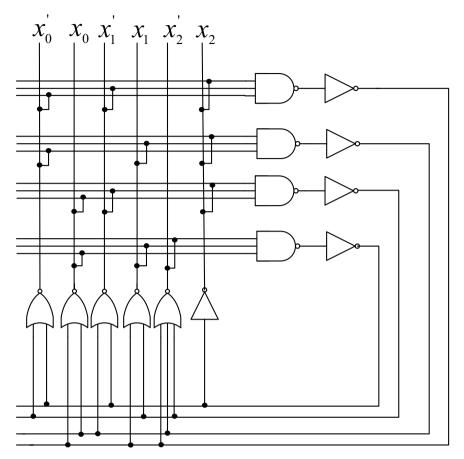

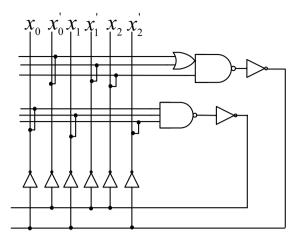

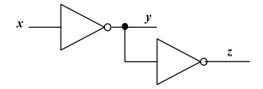

Diode/resistor logic cannot implement logical inversion (i.e., a NOT gate). However, by presenting the circuit with two wires for each input (i.e., one wire representing the true input value, the other representing its complement), the crossbars can produce internal signals in both the original and complemented forms. Combining these signals using just AND and OR operations then allows evaluating any logical formula. The complemented inputs to the crossbar are readily produced by the external circuit, fabricated using conventional technology, to which the crossbar is connected for input and output. Thus by doubling the number of wires and presenting all primary inputs in both true and complemented forms, the diode crossbar architecture can implement any logical formula just using combinations of AND and OR operations, as illustrated in Fig. 3.

Inputs and outputs of a nanoscale circuit ultimately need to be connected to the external, sub-micron world. One might use an approach similar to Likharev's architecture [31] to accomplish this, by having the external wires from the crossbar to spread out to a spacing large enough to match lithographically. In such an architecture, generally only a small fraction of the crossbar junctions (e.g., about 1%) are used. Thus, such an increased spacing reduces the high density benefit of molecular electronics. Nevertheless, such connection limitations allow tolerating high defect rates [31].

Alternatively, the high density of molecular electronics can be maintained by using nanoscale latches [24] at the inputs for driving the logic functions,

Fig. 3. DeMorgan's theorem allows generating a given logical AND/OR function along with its complement. This generally requires all input signals to be presented in both original and complemented forms

and at the outputs for signal regeneration. We consider this approach in our study, to examine defect tolerance of circuits fully exploiting the density improvement of molecular electronics, though with less tolerance for defects than sparser circuits. In this case, inputs can be provided via demultiplexer circuits [7, 8, 16, 20]. While demultiplexers require significant additional area for the small circuits discussed in this chapter, Rent's Rule states that the number of external connections scales approximately with the square root of the number of inputs and outputs on a single logic crossbar will be to other nanocrossbars. Such larger circuits face the same issues of defect-tolerant design as discussed in this chapter.

## 3 Model of Crossbar Defects

We restrict attention to defects leading to inoperative connections (i.e., with no ability to activate them to make diode connections), rather than defects that break or short out a wire, or prevent routing the output of one gate to the input of another. Moreover, for a given defect rate p, we assume errors occur independently, i.e., without any spatial correlation among defect locations.

Many researchers have explored the problem of finding such defects in crossbars with high defect rates [1, 27, 33].

In this scenario, we can test the circuits to determine which crosspoints are defective, and then use the remaining ones to implement the circuit. That is, a compiler uses the required logic formula and a table of defects to find a way to implement the formula.

Our focus is on crossbars whose configurable junction devices (e.g., diodes) have fixed parameters if they are functional (e.g., resistances in forward and reverse directions). A complementary analysis to that presented here could examine the consequences for circuit performance of various values of these parameters, as has been applied to a different adder implementation than discussed in this chapter, namely using a look-up table to evaluate all the combinations of inputs [34].

We do not consider errors in connections to external circuits. These include the inputs and outputs to the crossbar device, any feedback connections or inverters that may be needed to create complementary inputs and resistive connections to larger wires for the pullup and pulldown resistors. Other work has addressed connecting molecular electronics to larger scale circuits through the use of demultiplexer circuits with defects [7,8,16,20].

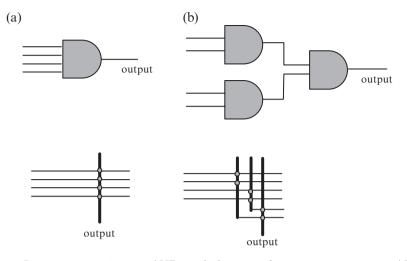

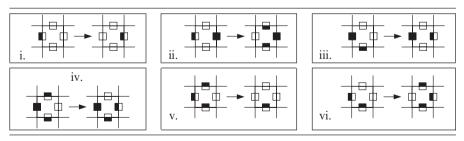

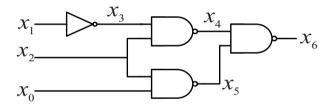

## 4 An AND Gate

A simple logic circuit created from the crossbar architecture is the logical AND of k inputs. One implementation is as a single k-input AND gate, i.e., using k connections to a single output wire. Another implementation is to decompose

**Fig. 4.** Logic gates: a 4-input AND, and the same function using 2-input AND gates. Also shown is an implementation of these circuits using parts of a crossbar network

the AND into a circuit of several AND gates with fewer inputs. For example, k - 1 2-input AND gates connected in a tree structure implements a k-input AND when k is a power of 2, as illustrated for k = 4 in Fig. 4.

For this example we suppose the assignments of input signals to input wires are fixed, e.g., either from external connections or from outputs of another part of a larger overall circuit. More generally, the circuit design could also involve searching for a suitable choice of these input wires among a larger number of rows in the crossbar network, as we discuss for the adder circuit in Sect. 5.

We also suppose the only defects in the crossbar are those preventing configuration as logical ANDs, rather than also considering other defects such as in the routing connections shown in Fig. 4. If each connection in the crossbar is defective with independent probability p, the probability a given column wire in the crossbar can be used to form a gate with k given inputs (i.e., row wires) is  $(1-p)^k$ . Thus in a crossbar with N columns, the probability that at least one column will be able to implement the k-input gate is

$$P_{\text{gate}}(k,N) = 1 - \left(1 - (1-p)^k\right)^N.$$

(1)

Computing the logical AND of k inputs using a single column, the probability to find a functional circuit is  $P_{\text{circuit}} = P_{\text{gate}}$ . If we use k - 1 2-input gates to compute the same logical value, the probability to find a functioning circuit is complicated due to the requirement that each gate must use a distinct column. We can illustrate the consequences of different implementations by using simple bounds on the probability. For an upper bound on the probability, we ignore the requirement for distinct columns. In this case, each gate's implementation is independent of all the others giving the upper bound

$$P_{\text{circuit}}^{\text{upper}}(k,N) = P_{\text{gate}}(2,N)^{k-1}.$$

(2)

For a lower bound on the probability, we attempt to implement the gates in a fixed order without regard for difficulties implementing subsequent gates. This results in a lower bound for the probability since a failure to find an implementation with this procedure may still allow constructing a circuit by backtracking to make another choice for one of the earlier gates in the sequence. In this procedure, the first gate can use any of the N columns, allowing implementation with probability  $P_{\text{gate}}(2, N)$ . The second gate cannot use the column already selected for the first gate, allowing implementation with the somewhat smaller probability  $P_{\text{gate}}(2, N - 1)$ . Each additional gate has one fewer column to use. Continuing with all k - 1 2-input gates gives the lower bound on probability to construct a circuit of

$$P_{\text{circuit}}^{\text{lower}}(k,N) = \prod_{i=0}^{k-2} P_{\text{gate}}(2,N-i)$$

(3)

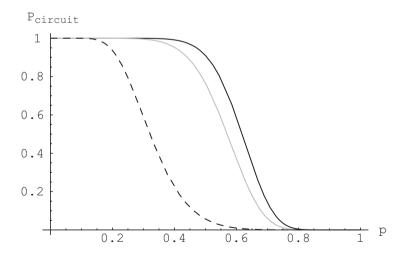

Figure 5 shows the behavior of these expressions as a function of defect probability p. In this example, with low p values, both circuits for evaluating the logical expression are likely to be constructible. As p increases, the chance of finding a single-gate circuit drops more rapidly: it is easier to find seven column wires with functioning connections for 2-input gates than to find one column to implement a single 8-input gate. This difference becomes more extreme as the size of the circuits increases. The figure also illustrates the

Fig. 5. Probability to be able to find a correct circuit in a crossbar with N = 15 columns as a function of defect probability p. The *dashed curve* is for a single 8-input AND gate, and the *solid curves* are for the upper and lower bounds on equivalent logical expression made with seven 2-input gates (*black and gray curves*, respectively)

threshold nature of the behavior: most of the drop in success probability occurs over a short range of p values.

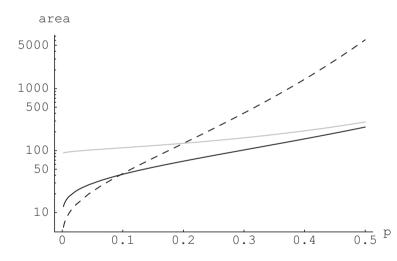

Another way to characterize the ability to find functional circuits in spite of defects is by the number of additional columns, or, equivalently, increased circuit area, necessary to give at least, say, a 95% probability of being able to find a functioning circuit. For the single k-input gate, inverting (1) gives the minimum number of columns N required to have a success probability at least  $\alpha$ . Similarly, inverting (2) and (3) give corresponding bounds on the number of columns required.<sup>1</sup>

With N columns, the circuit for the k-input gate has total area kN. With k-1 2-input gates, each gate has 2 inputs (distinct from all the rest) and the connections among the gates do not add to the overall area, as seen in Fig. 4. Thus in this case the circuit area is 2(k-1)N.

Figure 6 illustrates the behavior of the area requirements for the two implementations of the logical AND of k inputs. When p is low, both methods have a high chance of success (as also seen in the threshold behavior illustrated in Fig. 5). In this case, the smaller size of the k-input AND gate is

Fig. 6. Logarithmic plot of area required to have at least 95% probability to be able to find a correct circuit as a function of the defect probability p. The *dashed* curve is for a single 8-input AND gate, and the solid curves are upper and lower bounds for the equivalent logical expression made with seven 2-input gates (gray and black curves, respectively). Actual circuits must have an integer number of columns, resulting in slightly larger areas and step-functions in these plots, but with qualitatively the same behavior

<sup>&</sup>lt;sup>1</sup> Actual circuits have integer numbers of columns. So the actual minimum number of columns is the smallest integer greater than or equal to the values obtained by inverting these equations. This slight increase in the number of columns and will give somewhat higher success probabilities than  $\alpha$ .

more important than the slightly higher success probability with the combination of 2-input gates. As p increases, the success probability for the k-input gate drops more rapidly, leading to faster growth in area required, than the 2-input gates. Thus for large circuits, it is better to use more gates with few inputs than fewer gates with more inputs.

This discussion considers only two possible implementations of the logic formula. Additional possibilities include using a mixture of gates with different numbers of inputs, or combining 4-input, rather than 2-input, gates (so a k-input AND operation would be built from (k-1)/3 4-input AND gates). This give qualitatively similar behaviors to those shown in Fig. 5 and additional choices for circuit implementations.

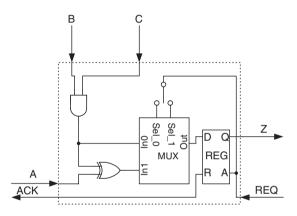

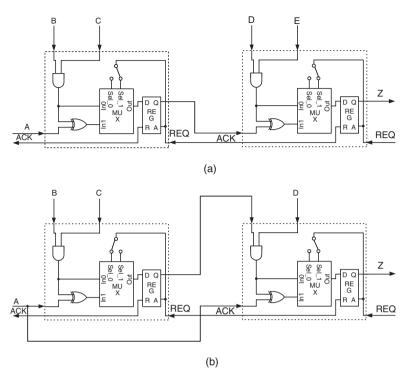

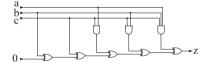

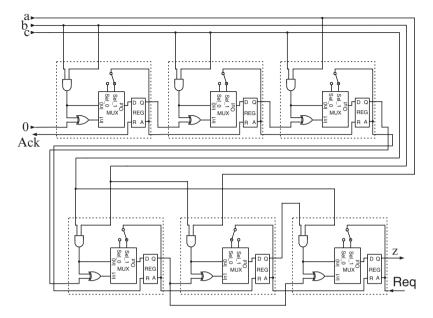

## **5** Adder Circuits

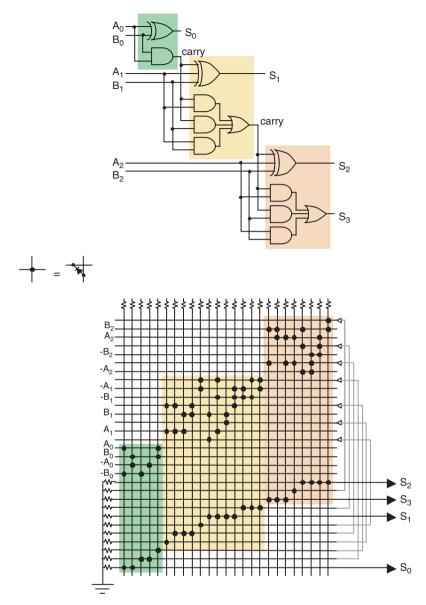

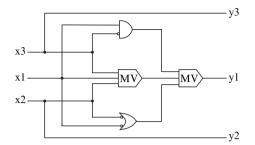

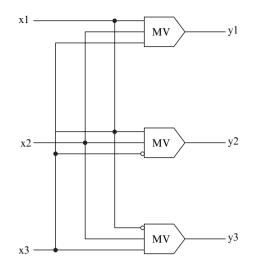

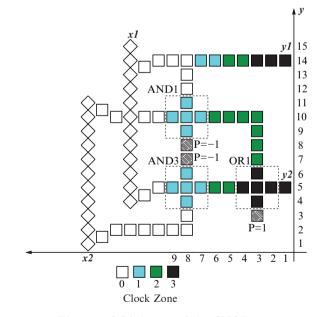

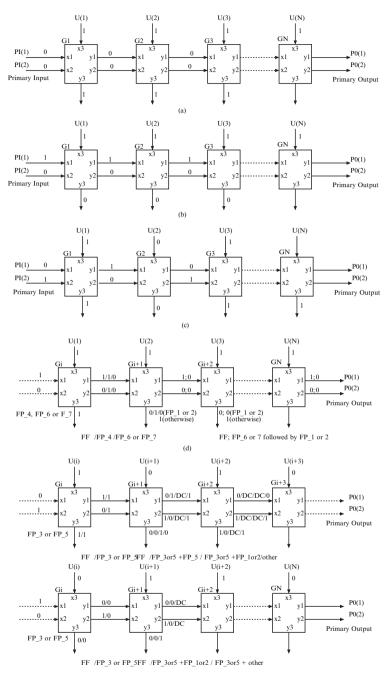

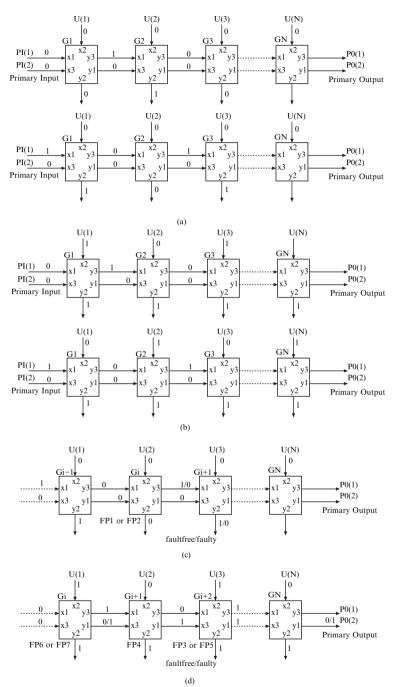

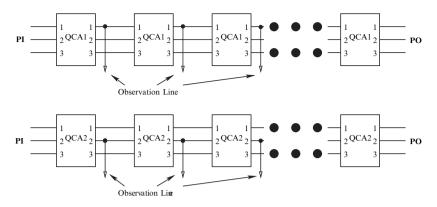

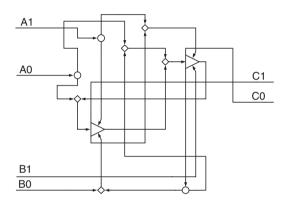

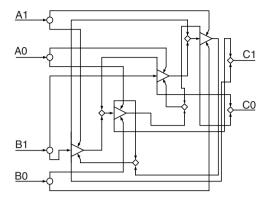

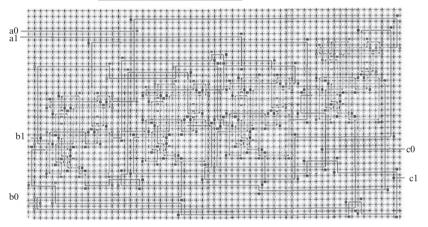

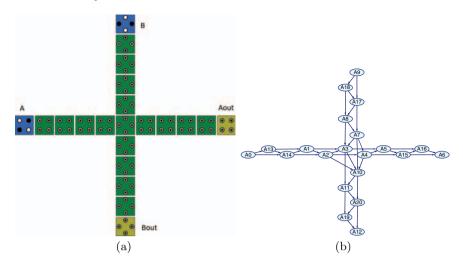

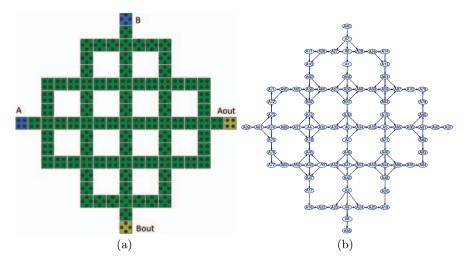

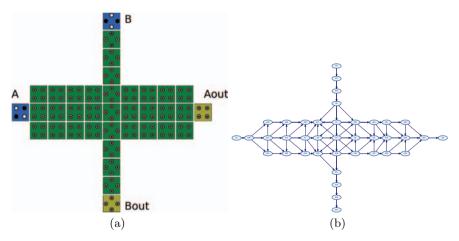

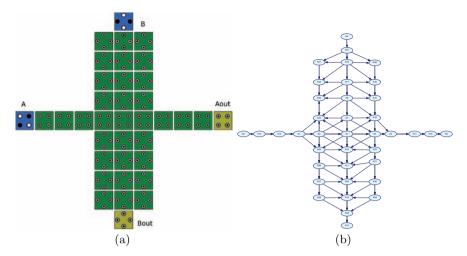

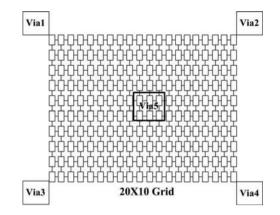

We now consider the mapping of small adder circuits onto crossbars. There are several ways to implement such circuits, with differing sensitivities to defects [18]. Figure 7 shows a straightforward 3-bit, ripple-carry adder that is essentially a direct translation of the logic circuit shown at the top, producing four output bits  $S_0 \ldots S_3$  representing the sum of two 3-bit numbers. For instance the bottom wire of the crossbar and the leftmost two columns compute the least significant bit of the sum,  $S_0$ , as  $S_0 = A_0 \overline{B_0} + \overline{A_0} B_0$ . This logical formula is equivalent to the exclusive-OR of the two least-significant bits of the numbers to be added, i.e.,  $A_0$  and  $B_0$ .

Because this implementation uses several levels of logic, some of the intermediate output signals must be fed back to some of the inputs, possibly requiring signal regeneration in the process to compensate for degradation due to diode voltage drops. The signal restoration can be accomplished at the nanoscale using, for example, a restorative latch [23,24]. The circuit uses 12 input wires: each of the two numbers to be added has 3 bits, and each bit must be presented as original and complementary values. The circuit has 4 outputs. The addition of the feedback signals gives a total of 30 rows. Forming the required logical operations on these values uses 25 columns, as shown in Fig. 7. This implementation, which uses 78 junctions configured as diodes, thus requires a minimum crossbar area of  $30 \times 25 = 750$  junctions.

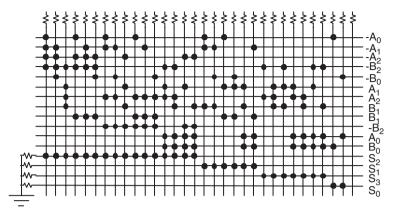

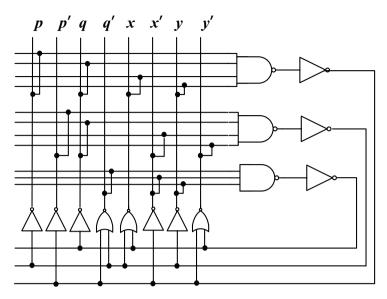

A second approach to the 3-bit adder is shown in Fig. 8. Here the entire circuit uses only two logic levels. It requires only enough rows to handle the input and output wires, i.e., 16 rows. The circuit requires 31 column wires to perform logic operations on the inputs, for a minimum crossbar area of  $31 \times 16 = 496$ . Again  $S_0$  is computed as  $S_0 = A_0 \overline{B_0} + \overline{A_0} B_0$ , using the bottom wire of the crossbar and the second and third columns from the right. This implementation eliminates the need for feedback and requires less area. On the other hand, it requires more diode junctions (147) and uses a greater number of diodes along some of the vertical and horizontal wires. For instance, the circuit in Fig. 7 never uses more than four diodes on any wire, while the circuit

Fig. 7. A 3-bit adder which adds two 3-bit numbers (denoted as the bits  $A_2A_1A_0$ and  $B_2B_1B_0$ , respectively) to produce a 4-bit sum (with bits  $S_3S_2S_1S_0$ ). The ripplecarry logic implementation (top) translates directly to a diode crossbar implementation (bottom) using feedback from some of the outputs to the inputs (gray lines). Regenerative buffers (left pointing triangles) between stages regenerate signals degraded by diode and resistor voltage drops. The input wire marked  $-A_0$  gives the complement of input bit  $A_0$ , and similarly for the other inputs. The carry bit between successive stages of the crossbar implementation must be presented in both original and complemented forms

Fig. 8. A 3-bit adder implemented as 2-level logic in a single diode crossbar. Although this approach uses more diodes, it consumes less area, avoids the feedback and regenerative buffers between stages, and will likely offer less propagation delay. Inputs and outputs are labeled as in Fig. 7. The rightmost column wire is not used in this circuit

in Fig. 8 requires as many as 16. Thus we can expect this circuit, packing more diodes in a smaller area, will be more difficult to implement on a crossbar with defects than that of Fig. 7.

Both of these adder circuits produce output bits corresponding to the sum. This is suitable when these circuits are considered as stand-alone components whose outputs are delivered to an external circuit composed of conventional technology (which can implement inversion). If instead the crossbar adder is to be used as part of a larger molecular-scale circuit, the adder will need to be extended to also produce complement values of each of the output bits so subsequent crossbars, using the results of the adder, will have access to both original and complement values for their inputs. Such extensions are readily included, as described with the discussion of Fig. 3, and will result in doubling the number of output wires, as well as additional logic computations within the crossbar. For simplicity, we focus on the adders treated as stand-alone circuits without the need for complement values for the outputs.

In the remainder of this section, we first describe the algorithm used to find a mapping of an adder circuit implementation to a crossbar with a known set of defects. We then use this algorithm to produce implementations on simulations of defective crossbars to identify their ability to give functional adder circuits.

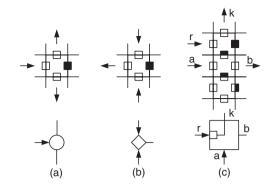

#### 5.1 Allocation Algorithm

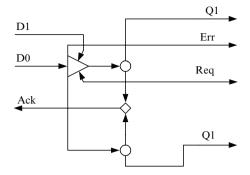

The diode/resistor fabric which we map onto is modeled as a set of four crossbars tiled together to form a mosaic, illustrated schematically in Fig. 9 and more explicitly with the example circuits of Figs. 2 and 3. The pullup and

Fig. 9. Model of diode array as a set of four connected crossbars. The AND and OR crossbars have configurable diode junctions, while the pullup and pulldown crossbars have configurable resistor junctions. Any junction in any crossbar may be defective, though the defect rate for junctions in the pullup and pulldown crossbars is much lower than for other junctions

pulldown "crossbars" are only one wire tall and wide, respectively, but the resistors there can be defective just like the diodes in the diode crossbars, so it simplifies allocation to use a single model for all of the components. However, the consequence of a defective pullup or pulldown resistor is to disable the entire column or row, respectively, to which it is connected. Fortunately, these resistors, at the edge of the crossbar, are formed from junctions between the nanowires and much larger, microscale, wires. Thus the junction area per device is significantly larger than that for the diode junctions used in the AND and OR crossbars. This increased junction area means the chance of a defective resistor is far smaller than having a defective diode.

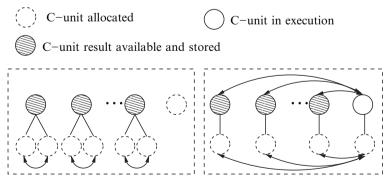

Even though the AND and OR crossbars share the same junction type and could be represented with a single crossbar, it is helpful to keep them separate since input signals may only be bound to horizontal wires entering the AND crossbar and output signals only bound to horizontal wires leaving the OR crossbar. The allocation problem, then, is to implement a circuit in the crossbars given a set of defective junctions in each. The allocation for the adder circuits also considers alternate choices for the input and output wires. However, input connections can only be made among wires preselected to be part of the AND crossbar, and output connections only among wires in the OR crossbar.

The allocation problem cannot be divided into separate crossbar allocation subproblems when the crossbars contain defects because a particular allocation of resources in one tile may actually preclude a successful allocation in another. We must also respect other constraints, such as input/output signal restrictions (in the case where the crossbars are embedded in a larger system) and asymmetric junctions, where component direction or polarity (such as for diodes) must be respected. We address the problem by searching globally for a solution that meets all constraints (defect avoidance, input/output constraints, junction polarity, and crossbar interaction) simultaneously.

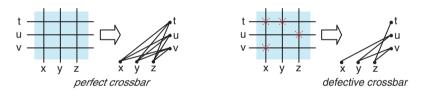

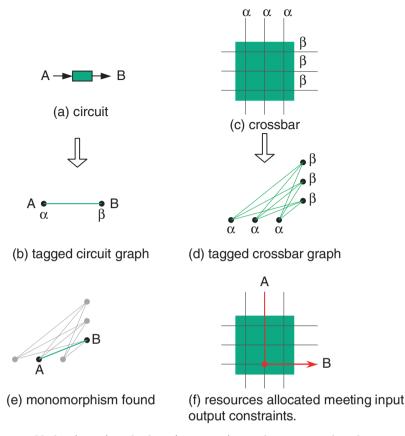

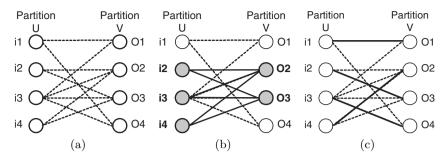

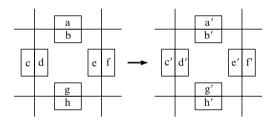

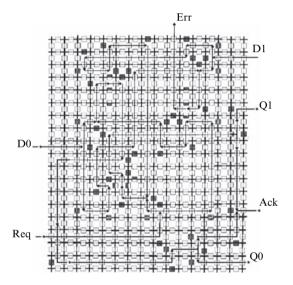

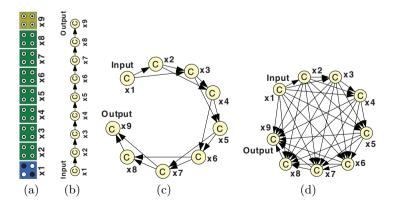

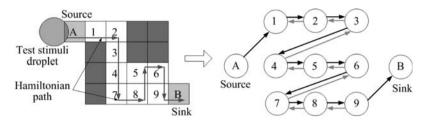

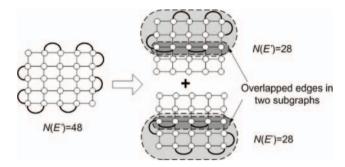

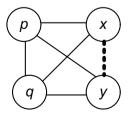

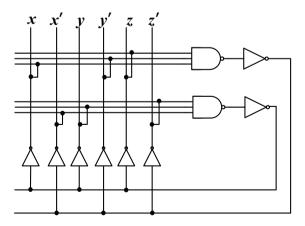

Our allocation algorithm uses graphs with annotated edges and nodes to represent both the original circuit to be mapped onto a set of crossbars as well as the crossbars themselves. Figure 10 shows how a crossbar is represented with a graph: a wire in the crossbar is represented by a node in the graph, and a junction is represented by an edge between the two nodes representing the wires that define the junction. A perfect crossbar (left) has an edge for every junction. A defective crossbar (right) has edges only for usable junctions.

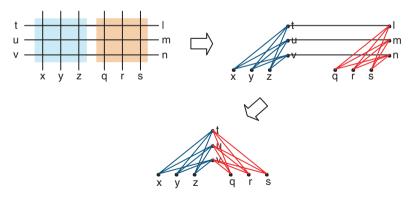

Graphs for multiple crossbars are constructed by first creating a graph for each individual crossbar (Fig. 11, *top left*) and then interconnecting them (*top right*). The resulting graph may then be (*optionally*) optimized by merging identical nodes (*bottom*).

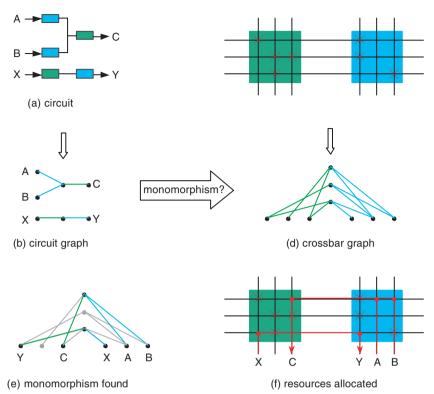

Allocation is accomplished by (1) creating graphs representing the desired circuit and compound crossbars; and (2) searching for an embedding or monomorphism between the circuit graph and the compound crossbar graph.

Fig. 10. Representing a crossbar with a graph. Wires and junctions in the crossbar correspond to nodes and edges of the graph, respectively. Defective junctions are shown marked with an "X"

Fig. 11. Representing composite crossbars with a graph. Edges are colored to represent the functionality of the junction that each one represents, since each crossbar might have different functionality

Fig. 12. Resource allocation: searching for a monomorphism between a circuit graph and a crossbar graph. The corresponding algorithm steps are described in the text

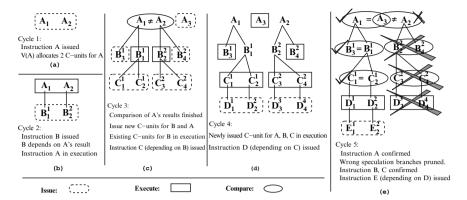

A graph monomorphism is the embedding of a small graph into a larger one, by specifying the correspondence between the nodes of the small graph and a subset of nodes in the larger graph so that the small graph forms a subgraph of the larger one. Figure 12 illustrates this in detail. The steps for allocation are:

- 1. For the desired circuit (Fig. 12a) create a circuit graph (Fig. 12b) representing it: wires and junctions in the circuit are represented by nodes and edges in the circuit graph, respectively.

- 2. For the desired target compound crossbar (Fig. 12c), create a compound tile graph (Fig. 12d) representing it. As in circuit graph case, wires and junctions in the crossbars are represented by nodes and edges in the compound tile graph, respectively. A defective junction in a crossbar is represented by the absence of its corresponding edge in the crossbar graph.

- 3. Annotate the edges of the circuit graph and the crossbar graph with annotations representing the functionality of those edges (junctions in the circuit represented by the graph). For example, edges in both graphs representing resistors would all be tagged with identical annotations.

- 4. Annotate the nodes of the circuit graph and crossbar graph with annotations to constrain matching between the two graphs. As will be shown later, this is done to either (a) enforce input/output constraints between the desired circuit and other circuitry that has been or will be mapped to other areas of a large compound tile graph; or (b) enforce directionality constraints on asymmetric junctions, such as diodes, that must have, for example, an input delivered on a horizontal wire and an output driven on a vertical wire; or (c) enforce both.

- 5. Search for a monomorphism (Fig. 12e) between the annotated circuit graph and the annotated target crossbar graph to do allocation (Fig. 12f), subject to the constraints that node and edge annotations must match. In other words, a node in the circuit graph can only be matched with a node in the crossbar graph if they both have identical annotations or both have no annotations. Similarly, edges can only be matched if they both have identical (or non-existent) annotations. Algorithms for searching for a graph monomorphism are well known [5,10,29]. They are efficient for problems with many solutions, but can be computationally expensive when there are few solutions.

- 6. Use the monomorphism to complete the allocation or mapping of wires and junctions in the desired circuit graph onto wires and junctions of the crossbar. For example, a node, A, in a circuit graph matched to a node, B, in the crossbar graph will be used to allocate the crossbar wire represented by B in the crossbar graph to carry the signal represented by A in the desired circuit. Similarly, an edge, X, in a circuit graph matched to an edge, Y, in the crossbar graph will be used to allocate the junction in the crossbar represented by Y in the crossbar graph for the electrical component represented by X in the desired circuit.

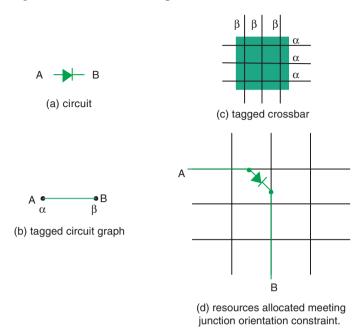

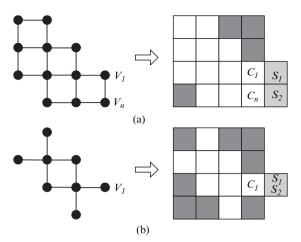

Edges in the circuit graph and crossbar graph are "colored" to reflect the component and junction functionality, respectively. These edge colors are additional constraints when searching for a monomorphism or embedding, since an edge in the circuit graph may only be matched with an edge in the compound tile graph with the same color. The edge coloring and the implied matching constraint are referred to as "edge annotation." Similarly, nodes may be annotated with the same matching constraint, namely that a node in a circuit graph may only be matched to a node in the crossbar graph with the same annotation. As shown in Fig. 13, this is useful to meet input/output constraints for a circuit. In this example the simple circuit (Fig. 13a) is to be mapped onto a set of crossbars (Fig. 13c). External constraints may require mapping the A signal onto a vertical wire and the B signal onto a horizontal wire. This constraint can be met by tagging the computation graph vertices (Fig. 13b) and the crossbar graph vertices (Fig. 13d) with legal matching tags. In this case, the input signal, A, is tagged with the  $\alpha$  tag as are the three vertical wires in the crossbar graph. Similarly, B is tagged with a  $\beta$  tag as are the three horizontal wires in the crossbar graph. When a monomorphism is found (Fig. 13e), it meets the input/output constraints for the allocation (Fig. 13f).

Fig. 13. Nodes (*wires*) and edges (*junctions*) may be annotated with a matching constraint

Node annotation is also useful for asymmetric junctions. The diode in Fig. 14 may only be configured correctly in the target compound tile in one direction. Annotating the vertices of the circuit graph and the compound tile graph appropriately assures the diode will be allocated with the proper orientation.

This allocation algorithm is a *complete* search method: if it does not find a possible circuit implementation in the crossbar with given defects, then no such implementation exists. In practice, the computational cost of such search methods can be prohibitive, especially for circuits with many components. In that case, one could instead use an *incomplete* search method, which often solves combinatorial problems more rapidly than complete methods, but offers no guarantee that failure to find a solution means no solution exists. For the simulation results discussed below, we employed an incomplete search method obtained by simply imposing a bound on the number of graph matching attempts allowed for the allocation algorithm. If a match is not found within

Fig. 14. Node annotation to support allocation of asymmetric junctions

this number of attempts, we consider the defective crossbar to be a failure. In a mass-production manufacturing context, the choice of the bound on the algorithm results in a trade-off between increasing the computing and testing time spent determining whether a crossbar is functional and decreasing the yield of functional circuits.

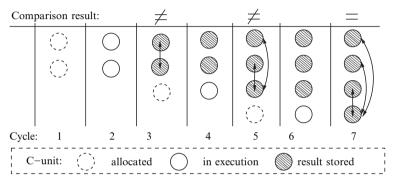

#### 5.2 Simulation Results for Adder Circuits

To examine the behavior of implementing adder circuits on defective crossbars, we created a number of simulated test cases. Specifically, for a given adder implementation (e.g., single or multiple stage) and crossbar size, we mark each junction of the AND and OR crossbar as defective independently with probability p. Because the pullup and pulldown resistors have much lower defect rates, for simplicity, we restrict our attention to cases with no defective resistors. We then run the allocation algorithm, recording whether it found an allocation (within at most 30 s of CPU time, corresponding to about  $7 \times 10^7$  graph matchings) and the number of steps required to reach a decision. We repeat this procedure on new crossbars with randomly selected defects (using the same parameters).

The limit on search time for the allocation algorithm was significantly larger than the typical number of matchings needed in the cases that produced a successful match. From a pragmatic standpoint, the need to rapidly test circuits after fabrication would preclude spending an inordinate amount of time trying to distinguish a crossbar with a possible, but difficult to find, circuit implementation from one with no possible implementations. Thus, imposing a bound on CPU time is a simple approach to avoiding this excessive search cost, with the tradeoff of slightly reducing the yield.

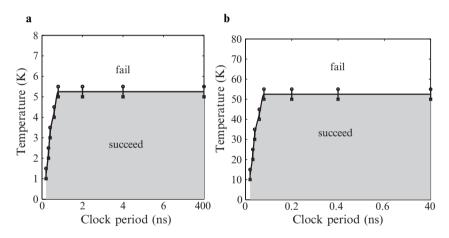

#### **Threshold Behavior**

From the set of simulation trials, we estimate  $P_{\text{circuit}}$ , the probability an implementation exists for a set of parameters. Suppose we successfully find an allocation s times out of n trials. Because each trial uses an independently generated crossbar, the probability to observe s successful circuits out of n trials is the binomial distribution  $\text{Bi}(n, s; P_{\text{circuit}})$  where

$$\operatorname{Bi}(n,k;p) \equiv \binom{n}{k} p^k (1-p)^{n-k} \tag{4}$$

Thus the likelihood that  $P_{\text{circuit}}$  equals the value f is proportional to  $f^s(1-f)^{n-s}$ . Maximizing this quantity gives f = s/n as the maximum-likelihood estimate of  $P_{\text{circuit}}$ . Evaluating the range of f values accounting for, say, 95% of the likelihood indicates how well our simulation determines the value.

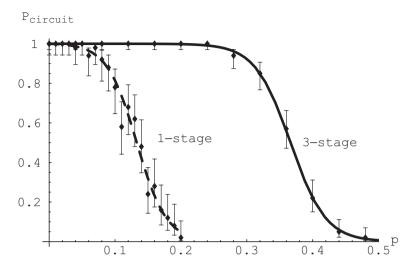

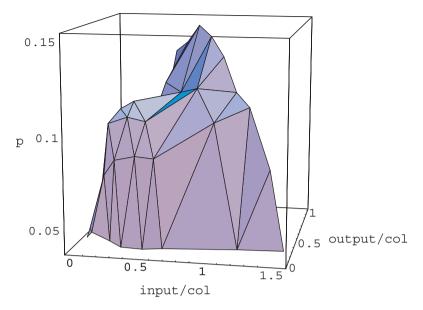

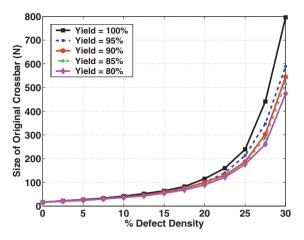

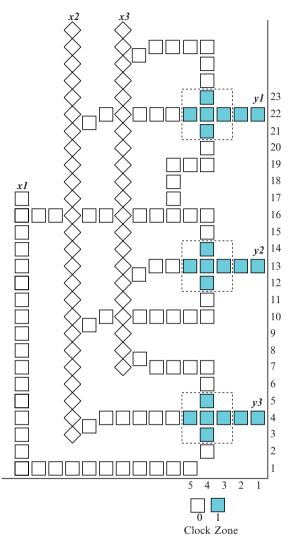

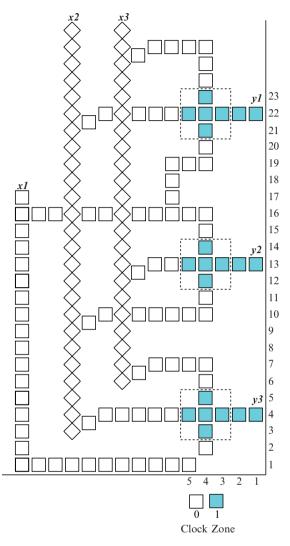

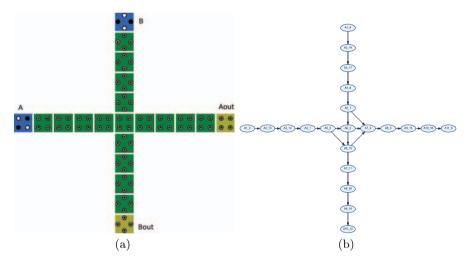

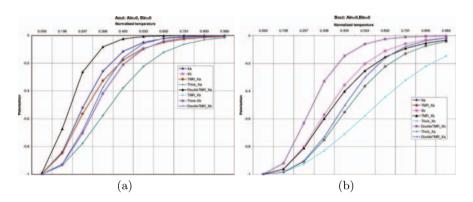

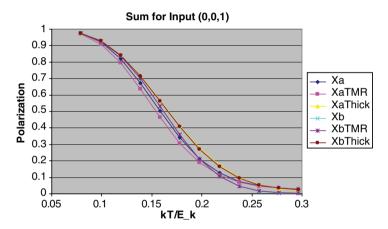

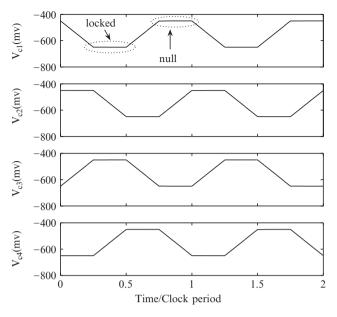

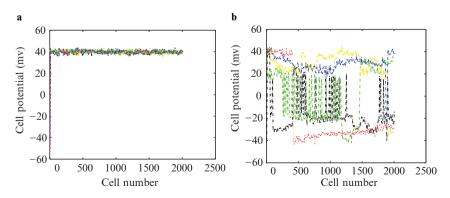

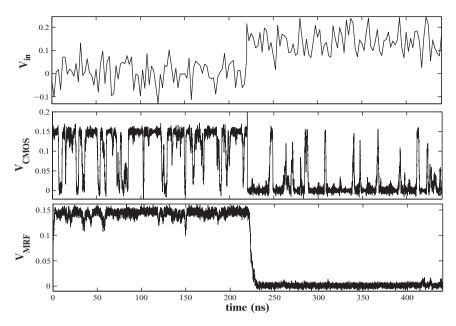

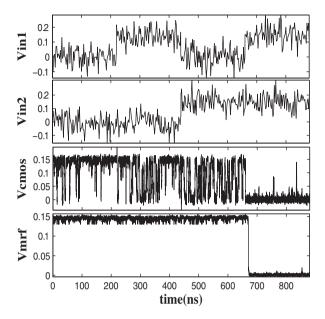

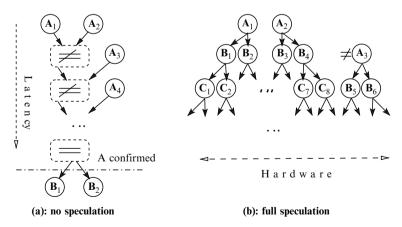

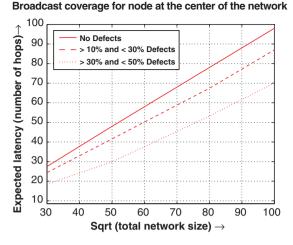

Figure 15 is an example of the behavior of implementing a 3-bit adder circuit, using the two rewrites discussed in Sect. 5: a single stage and three stages. In this and subsequent figures, each point for the 1-stage adder is the result of 50 simulation trials at the corresponding defect rate p; and each point for the 3-stage adder is from 100 trials. We see a threshold behavior as  $P_{\text{circuit}}$  drops abruptly over a fairly short range of p values. The 3-stage adder can tolerate higher defect rates than the single-stage implementation.

As p increases, the probability of finding a given circuit monotonically decreases. As a simple summary of the results from multiple sets of trials, each using a different value of p to generate defective crossbars, we use a twoparameter sigmoidal form relating  $P_{\text{circuit}}$  to p. A sigmoid allows matching the location and steepness of the threshold behavior to the simulation results, and incorporates the monotonicity in the relation between  $P_{\text{circuit}}$  and p. As one specific choice for a sigmoidal function, let

$$S(x) = \frac{1}{1 + e^{a(x-b)}}.$$

(5)

Here the parameter a determines the sharpness of the threshold and b its location. Since  $P_{\text{circuit}}$  is zero when p = 1, and  $P_{\text{circuit}} = 1$  when p = 0 (provided the crossbar is at least the minimum size required for the circuit), we shift and scale this sigmoid to match these extremes. Thus we use

$$P_{\text{circuit}} = \frac{S(p) - S(1)}{S(0) - S(1)} \tag{6}$$

Fig. 15. Probability  $P_{\rm circuit}$  to be able to find a correct circuit for a 3-bit adder in a crossbar as a function of defect probability p. The points show the estimates from the simulation runs, with error bars indicating the 95% confidence intervals in the estimates of  $P_{\rm circuit}$ . The *curves* show the maximum-likelihood fits of a sigmoid function, for the single and three-stage adders (*dashed and solid*, respectively). The crossbar sizes for the two circuits are 768 and 896 for the single and three-stages adders, respectively

With multiple sets of trials, we select a and b to maximize the likelihood of obtaining the observed results from the simulation. Since each trial is independent of the others, this amounts to maximizing the product of the individual likelihoods, described above, for each p value. Figure 15 shows examples of the resulting fits.

To understand the existence of this threshold behavior, and how it depends on the circuit and crossbar area, consider a simplified version of the allocation in which we ignore all constraints on the locations of the functioning diodes. By ignoring these constraints, we obtain an upper bound on  $P_{\text{circuit}}$  and rough guides to the location and steepness of the threshold. Specifically, a crossbar with area A has k defective junctions with probability Bi(A, k; p) given by (4). The expected number of defects is  $\mu = Ap$  with standard deviation  $\sigma = \sqrt{Ap(1-p)}$ . A circuit requiring d diode junctions is very likely to exist when the number of defects is likely to be less than A - d. Conversely, when the number of defects is usually larger than this value, the crossbar is unlikely to be able to implement the circuit. More precisely, when A - d is several standard deviations above or below  $\mu$ ,  $P_{\text{circuit}} \approx 1$  or 0, respectively. This discussion predicts the threshold near the value of p for which  $\mu = A - d$ , i.e.,

$$p \approx 1 - d/A. \tag{7}$$

The change between these extremes takes place mainly over a range of p values corresponding to about a standard deviation around the mean, i.e., from the value where  $\mu + \sigma = A - d$  to that where  $\mu - \sigma = A - d$ . The corresponding range in p values is  $\frac{1}{A+1}\sqrt{1+4d-4d^2/A}$  or  $\sim \sqrt{1+4d}/A$  for large areas.

These specific values, derived by ignoring all constraints on the locations of the functioning devices, differ from the location and width of the threshold seen in the simulations. Nevertheless, they give some qualitative insight into the behaviors we observe. For instance, as the crossbar area increases, the threshold moves to larger values of p: as one would expect, larger crossbars provide more chances to find the required number of functioning junctions. The threshold width is small when the area is close to the minimum possible (i.e., just enough to hold the required number of functioning diodes) or when the area is very large. For a given area, comparing two implementations with different numbers of diodes, we see the implementation with more diodes, i.e., larger d, has a lower threshold: it is less tolerant of defects. As a final observation, consider the scaling to larger circuits (e.g., k-bit adders for k > 3). Taking the crossbar area to be a fixed factor larger than the required number of diodes, i.e., A = rd gives a fixed threshold location of 1 - r while threshold width decreases as  $O(1/\sqrt{d})$ . That is, for larger circuits the threshold behavior becomes sharper.

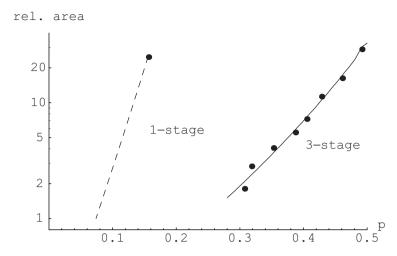

#### Crossbar Area

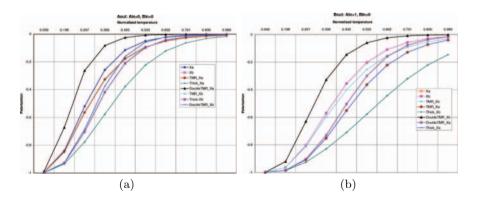

Figure 15 shows the behavior for a fixed size crossbar. Since the single and 3-stage adder circuits require different areas, it is also useful to compare the area required to obtain a fixed value of  $P_{\text{circuit}}$ . To estimate the behavior of the adder circuit for different areas, we used the sigmoidal fit of (6). This fit has two parameters, a and b, characterizing the width and location of the transition from  $P_{\text{circuit}} \approx 1$  to  $P_{\text{circuit}} \approx 0$ . For definiteness, we consider arrays of fixed shapes (i.e., ratio of number of columns to numbers of rows allocated for the AND and OR operations), and show the resulting behavior in Fig. 16. Specifically, for the single-stage adder, we examined arrays whose numbers of columns, input rows and output rows had the ratios 4:2:1. By comparison, the minimum size array that can implement the circuit, with 31 columns, 12 inputs and 4 outputs, has ratios 31:12:4=7.75:3:1. Thus the shape we use allocates relatively more of the array area to the rows, especially those for the outputs, than would be the case from uniformly scaling up the minimum array. This allocation is beneficial because the single-stage circuit is particularly sensitive to defects in the rows due to the need for large numbers of functioning diodes, especially for the outputs, as seen in Fig. 8. For the three-stage adder, various shapes close to scaled-up versions of the minimum size array (25 columns, 19 inputs, 11 outputs) had similar behaviors. As a convenient ratio to simulate with different sizes, we used 28:20:12.

Over the range of crossbar areas we examined via simulation, the transition width had only small variation with area. On the other hand, the location of

Fig. 16. Relative area required to have at least 90% probability to be able to find a correct 3-bit adder circuit as a function of defect probability p, based on interpolating the fit to the simulation results. The *dashed* and *solid curves* correspond to single and three-stage adders, respectively. The points correspond to values estimated from individual sigmoid fits to results from each crossbar area, for a fixed choice of array shapes. With the shapes used here, the lowest simulation point on each curve is the smallest possible functional array with that shape, and have somewhat larger area than the minimum area for each case (indicated by the bottoms of the two curves). Areas are relative to that required for a single-stage adder on a defect-free crossbar, i.e., 496 junctions

the threshold increased with area. Motivated by the discussion leading to (7), we suppose the sigmoid parameters a, b vary with area A according to

$$a = \alpha A^{\delta}$$

$$b = 1 - \beta A^{-\eta}$$

where  $\alpha$ ,  $\delta$ ,  $\beta$  and  $\eta$  are parameters with nonnegative values. We fit these four parameters to the simulation results for with different areas to produce a single functional form relating  $P_{\text{circuit}}$  to A and p for a given circuit and array shape. The resulting functional form fits the results for single areas about as well as sigmoid functions optimized individually for each area. This fit allows interpolating the behavior for other areas and defect rates than those evaluated via the simulation. In particular, it allows estimating the crossbar area required to have at least a given desired yield, i.e., value of  $P_{\text{circuit}}$ . For instance, Fig. 16 shows the resulting estimates for the area required to achieve  $P_{\text{circuit}} = 90\%$ . Thus, we have about 90% yield with the 3-stage adder at 30% defect rate and area 896, which is 1.8 times the minimum area of 496 junctions. We see the single-stage adder is much more sensitive to defects, so requires larger areas to compensate. The lowest points on the curves in Fig. 16 correspond to the minimum crossbar size that can implement the adder: 496 and 750 for the one and three-stage circuits, respectively. These values do not occur at p = 0 because the minimum areas are determined by the required numbers of logic operations, inputs and outputs rather than the number of diode junctions. Hence even the minimum area crossbars can tolerate some defective junctions. Comparing the two adder implementations, we see that for p < 0.085, the single-stage adder gives 90% success with crossbars whose size is too small to also implement the three-stage adder. For 0.085 , the three-stage adder on the smallest possible crossbar that can implement it gives over 90% success, while the area required for the single-stage adder increases significantly. With <math>p > 0.3, required areas of both circuits increase, though the three-stage implementation requires much less area. This discussion illustrates how achievable defect rate, choice of circuit implementation and available crossbar area interact to determine the circuit yield.

## Array Shape

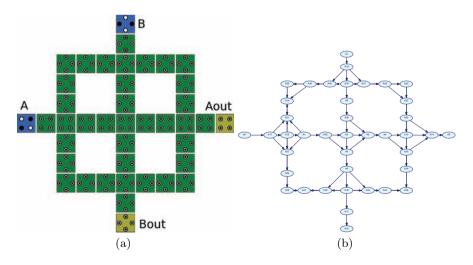

In addition to the area of a crossbar array considered above, its shape also influences the likelihood of being able to implement a circuit in spite of defects. A successful circuit requires not only enough functioning junctions, but also the ability to properly connect them to each other and the inputs and outputs. Thus  $P_{\rm circuit}$  is, in general, a function separately of the three numbers characterizing the crossbar: the number of columns, the number of rows allocated for AND operations on inputs, and the number of rows for OR's on the results of the ANDs to produce the circuit outputs. For example, the one-stage 3-bit adder uses 12 input wires (two for each of the 3 input bits for each of the two numbers to be added) and 4 outputs, for a total of 16 rows. It uses 31 columns to form the required logic operations. Thus a crossbar with fewer than 16 rows could never implement this circuit, no matter how many columns or how low a defect rate it had. More generally, scaling up the number of rows and columns by the same factor may not be the best way to improve performance from a given crossbar area. For example, it may be better to increase number of rows more than number of columns for an implementation requiring many diodes on the same row, vs. a different implementation using many diodes on a single column.

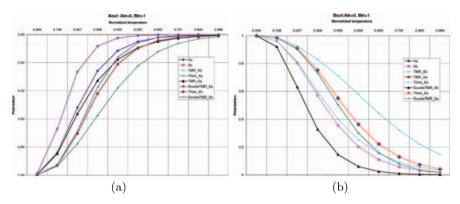

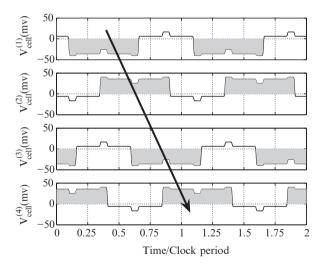

Figure 17 shows an example of how array shape affects implementing the single-stage 3-bit adder, shown in Fig. 8. In this example, we examined various shaped arrays, all with the same area, 1,728, which is about 3.5 times the minimum array size for this circuit. For each shape, we fit the sigmoid of (6) to the simulation results and used this fit to estimate the defect rate with 90% probability to implement the circuit. The shapes cover a range from a very wide array (108 columns, 12 inputs, 4 outputs) to the narrowest possible arrays with area 1,728 still capable of implementing the circuit even when there are no defects, which have 32 columns and 54 rows, with allocations of

Fig. 17. Defect rate, p, at which a single-stage 3-bit adder circuit can be found with 90% probability as a function of array shape for area equal to 1728. The shape is specified by the ratios of numbers of input and output rows to the number of columns in the crossbar

those rows ranging from having 12 inputs and 42 outputs to 50 inputs and 4 outputs.

The best performance in Fig. 17 is for the array with 32 columns, 24 inputs and 30 outputs, giving at least 90% probability to produce a circuit with  $p \leq 0.15$ . This shape tolerates about three times as many defects as the worst shapes shown in the figure (which allocate only four wires to the outputs). Because the one-stage adder requires many diode connections on the outputs, this best performing array shape devotes a relatively large portion of the area to redundant output wires. By contrast, the shape used in Fig. 16 to illustrate behavior as a function of area arrays whose numbers of columns, input rows and output rows had the ratios 4:2:1, a shape with intermediate performance among those shown in Fig. 17, i.e., allowing  $p \leq 0.11$ .

We also found variation due to shape in the three-stage adder, and that the best choice of shape varies somewhat with array size.

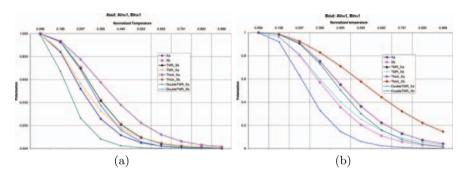

#### Scaling and Allocation Run Time

For comparison, we also examined 1, 2 and 4-bit adder circuits. They gave the same qualitative behaviors, and show the threshold behavior becomes more abrupt as circuit size increases. Thus the threshold becomes more significant as circuit size increases, thereby giving a useful design criterion for the maximum allowable defect rate for a given desired circuit and crossbar area.

For a given circuit, we found the typical run time of the allocation algorithm increases with p up to the threshold region. For even higher p values, most crossbars cannot implement the circuit and the algorithm terminates by reaching the bound on its run time. Nevertheless, to examine the allocation cost behavior for larger p, we also ran the algorithm to completion (i.e., with no bound on the run time) for a smaller circuit, namely a 1-bit adder. We found that the median allocation cost peaked near the threshold at which  $P_{\text{circuit}} \approx 0.5$  and then decreased for larger p values, as the additional constraints introduced with additional defects allows the allocation algorithm to prune large sets of possibilities and more rapidly conclude no implementation is possible. This behavior is consistent with that seen in many other studies of combinatorial search problems [17]. That is, as problems become more constrained, there is an abrupt transition from almost always to almost never having a solution, and the typical search cost for a variety of search methods peaks near this transition.

## 6 Discussion