## Alexander Biedermann H. Gregor Molter (Eds.)

# Design Methodologies for Secure Embedded Systems

Festschrift in Honor of Prof. Dr.-Ing. Sorin A. Huss

## Volume 78

Cover Image: Hard'n'Soft © Konstantin Inozemtsev 2008 obtained from istockphoto.com Alexander Biedermann and H. Gregor Molter (Eds.)

## Design Methodologies for Secure Embedded Systems

Festschrift in Honor of Prof. Dr.-Ing. Sorin A. Huss

Alexander Biedermann Technische Universität Darmstadt Department of Computer Science Integrated Circuits and Systems Lab Hochschulstr. 10 64289 Darmstadt, Germany E-mail: biedermann@iss.tu-darmstadt.de

H. Gregor Molter Technische Universität Darmstadt Department of Computer Science Integrated Circuits and Systems Lab Hochschulstr. 10 64289 Darmstadt, Germany E-mail: molter@iss.tu-darmstadt.de

ISBN 978-3-642-16766-9

e-ISBN 978-3-642-16767-6

DOI 10.1007/978-3-642-16767-6

Library of Congress Control Number: 2010937862

© 2010 Springer-Verlag Berlin Heidelberg

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilm or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Typeset: Scientific Publishing Services Pvt. Ltd., Chennai, India.

Printed on acid-free paper

987654321

springer.com

Sorin A. Huss

#### Preface

This Festschrift is dedicated to Mr. Sorin A. Huss by his friends and his Ph.D. students to honor him duly on the occasion of his 60th birthday.

Mr. Sorin A. Huss was born in Bukarest, Romania on May 21, 1950. He attended a secondary school with emphasis on mathematic and scientific topics in Dachau near Munich and after his Abitur he studied Electrical Engineering with the discipline information technology at the Technische Universität München.

1976 he started his career at this university as the first research assistant at the newly established chair for design automation. Due to his very high ability he was a particularly important member of the staff especially in the development phase. In his research Mr. Huss dealt with methods for design automation of integrated circuits. The results of his research activities and his dissertation "Zur interaktiven Optimierung integrierter Schaltungen" were published in very highranking international proceedings and scientific journals. In his dissertation he started from the recognition that the computer-aided dimensioning of integrated circuits on transistor level normally leads to a very bad conditioned optimization problem and that this aspect played the central role in solving this problem. Mr. Huss provided important contributions to this matter which were advanced in future activities of the chair and finally resulted in the establishment of a company. Today, 15 employees of the company MunEDA are busy with the production and the world-wide sale of software tools for the design of analog components in microchips.

In 1982, Mr. Huss changed from university to industry and then worked at the AEG Concern in several positions. At last he was responsible for the development and adoption of new design methods as well as for the long-term application of the corresponding design systems as a department manager at the development center Integrated Circuits. Design tools that were developed under his direction, were used not only in the AEG Concern but also in famous domestic and foreign companies for the development of microelectronic circuits and systems. Important cross-departmental functions and the preparation of publicly funded major research projects indicate that his professional and organizational skills were well appreciated. Despite his technical-economical aim and the surrounding circumstances of internal release procedures Mr. Huss was able to document the academic level of the activities in his field of work by publications and talks outside of the company, too.

One of these publications brought forth the award of the ITG in 1988, for one of the best publications of the year. After six years of university experience and eight years of employment in industry, Mr. Huss had proved to be a well appreciated and internationally accepted expert in the field of the computeraided design of integrated circuits and systems. After having obtained a call for a C4 professorship in Computer Engineering at the Technische Hochschule Darmstadt, Mr. Huss started his work as a full professor in Darmstadt on July 1, 1990. Since that time Prof. Huss not only had a decisive impact on the technical sector of the Department of Computer Science. Since 1996 he acts as a co-professor at the Department of Electrical Engineering of the Technische Universität Darmstadt. With his assistance, the field of study Information System Technology (IST) was founded as cooperation between the Department of Computer Science and the Department of Electrical Engineering. In the same year, he rejected an appointment for a C4 professorship for technical computer science at the University Bonn and an offer as a head of the Institute for systems engineering at GMD, St. Augustin, to continue research and teaching at the TU Darmstadt.

On the basis of design methods for embedded systems, the focus of his research has enlarged and now connects aspects of heterogeneous systems with IT-systems and the automotive sector. More than 140 publications evidence his research activities. His contributions to research were acknowledged inter alia in 1988 with the Literature Award of the Information Technology Society (VDE/ITG), the Outstanding Paper Award of the SCS European Simulation Symposium in 1998, and both the Best Paper Award of the IEEE International Conference on Hardware/Software Codesign-Workshop on Application Specific Processors and the ITEA Achievement Award of the ITEA Society in 2004.

Apart from his memberships in ACM, IEEE, VDE/ITG and edacentrum he is – due to his expert knowledge about the design of secure embedded systems – head of one of three departments of the Center of Advanced Security Research Darmstadt (CASED). CASED was established in the year 2008 by the Hessian campaign for the development of scientific-economical excellence (LOEWE) as one of five LOEWE-Centers. Just the research group lead by Prof Huss which deals with the design of secure hardware, has presented more than fifty international publications since then. An Award for Outstanding Achievements in Teaching in the year 2005 and other in-house awards for the best lecture furthermore evidence his success in teaching. More than a dozen dissertations that have been supported by Prof. Sorin A. Huss to the present day complete the view of an expert, who does not only have extensive knowledge in his fields of research but is also able to convey his knowledge to others.

We wish Prof. Dr.-Ing. Sorin Alexander Huss many more successful years!

November 2010

Kurt Antreich Alexander Biedermann H. Gregor Molter

## Joint Celebration of the 60<sup>th</sup> Birthdays of Alejandro P. Buchmann, Sorin A. Huss, and Christoph Walther on November 19<sup>th</sup>, 2010

Honourable Colleague, Dear Sorin,

Let me first send my congratulations to you as well as to the other two guys. You jointly celebrate your sixtieths birthdays this year. I wish you all the best for your future work at TU Darmstadt! Sorin, let me first thank you for the time you served as one of my Deputies General in that treadmill they call "Dekanat". It was difficult for you to reserve some of your spare time for that voluntary, additional job. I appreciate that you agreed to take over this purely honorary post. Your advice has always been helpful for me. Your research and teaching activities are extraordinarily successful. Your success has led to a number of awards, from which I can only mention the most outstanding ones: Literature Award of the IT Chapter of the VDE (the German association of electrical engineers), European ITEA Achievement Award, Teaching Award of the Ernst-Ludwigs-Hochschulgesellschaft. You were one of the initiators of TU Darmstadt's bachelor/master program in information systems technology. To conclude this list, I would also like to mention that you are one of the domain directors of CASED, which is an important position not only for CASED itself but for the department and for TU Darmstadt as well. You three guys are true institutions of the departments (I am tempted to speak of dinosaurs, however, in an absolutely positive sense). You have seen colleagues come and go. Due to your experience and your long time of service in the department, you have become critical nodes of the departments corporate memory network. Your experience has been deciding many discussions typically (yet not exclusively) for the better. I should mention that each of you three guys is equipped with a specific kind of spirit. Your humorous comments, always to the point, made many meetings of the colleagues really enjoyable for the audience (well, the meeting chair did not always enjoy, but thats fine). You have always combining passion with reason, spirit with analysis, vision with rationality. On behalf of the colleagues, the department, and TU Darmstadt, I wish you three guys that you will have another great time together with all of us and an even longer chain of success stories than ever. Happy Birthday!

November 2010

Karsten Weihe Dean of the Department of Computer Science Technische Universität Darmstadt

### The Darmstadt Microprocessor Practical Lab Some Memories of the E.I.S. Times

At the beginning of the 1980s, the publication of the book "Introduction to VLSI-Systems" by Mead/Conway initiated a revolution in the design of integrated circuits not only in the United States – it had a great feedback also in Germany. So it was intensively thought about establishing the design of integrated circuits as a field of study at the Technical Universities and Universities of Applied Sciences. Funded by the German Federal Ministry of Research and Technology (BMFT) the project E.I.S. (Entwurf Integrierter Schaltungen [design of integrated circuits]) was started in close cooperation with industrial concerns in 1983. The project was coordinated by the Society for Mathematics and Data Processing at Bonn (today: Fraunhofer Institute) and had the following objectives:

- Intensification of the research in the field of the design of microelectronic circuits at the Universities and progress in the theory of design methods

- Design and development of experimental CAD-software for microelectronic circuits for the use in research and teaching

- Design and test of application-specific circuits

- Enhancement of the number of computer scientists and electrical engineers with a special skill in VLSI-Design

Following the publication of the book "Introduction to VLSI-Systems" by Mead/Conway also people in Germany quickly recognized that VLSI-Design was not a kind of black magic but was based on a well-structured methodology. Only by means of this methodology it would be possible to handle the exponentially increasing design complexity of digital (and analog) circuits expected in the future.

Mr. Huss met this challenge very early and established a design lab at Darmstadt. The practical lab was intended to impart the complete design process from the behavior-oriented design model to the point of the layout. Based on a highlevel-design methodology – which was taught in an accompanying lecture – and by using a design example, the entire development should be comprehended in detail and realized by means of modern CAE-tools. The practical lab therefore allowed an integrated education in the field of high-level-design methodology which was theoretically sound and deepened in practice. The design was carried out according to the principle of "Meet in the Middle" which was common practice instead of using the "Top Down" method. VHDL was used as formal language, as it enabled a description on all levels of abstraction. The necessary transformations were explained didactical cleverly using the Y-diagram of Gajski. The main objective of the practical lab at this was not only learning the language, but to rehearse the Methodology in detail up of the design of a standard cell in a 1.5 m CMOS-technology with about 16,000 transistors. The production took place within the framework of the EUROCHIP-program. The abstract of the practical lab at the TH Darmstadt was introduced to an international group of experts at the 6th E.I.S. Workshop 1993 in T"ubingen. As the Goethe University Frankfurt ran a practical lab with a similar intention, a lively exchange of experiences arose subsequent to the E.I.S. Workshop. This fruitful cooperation in teaching later brought forth a textbook with the title "Praktikum des modernen VLSI-Entwurfs". The authors were Andreas Bleck, Michael Goedecke, Sorin A. Huss and Klaus Waldschmidt. The book was published by Teubner Verlag, Stuttgart in 1996. Unfortunately, it is no longer available due to developments in the publishing sector.

I gladly remember the cooperation with colleague Mr. Huss and his team. This cooperation later also continued in the area of research, for instance in the context of the SAMS-Project, which was funded by the BMBF and the edacentrum. For the future, I wish colleague Mr. Huss continued success and pleasure in teaching and research.

November 2010

Klaus Waldschmidt Technische Informatik Goethe Universität Frankfurt

## Table of Contents

| Towards Co-design of HW/SW/Analog Systems<br>Christoph Grimm, Markus Damm, and Jan Haase                                                                   | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Flexible Hierarchical Approach for Controlling the System-Level<br>Design Complexity of Embedded Systems<br>Stephan Klaus                                | 25  |

| Side-Channel Analysis – Mathematics Has Met Engineering<br>Werner Schindler                                                                                | 43  |

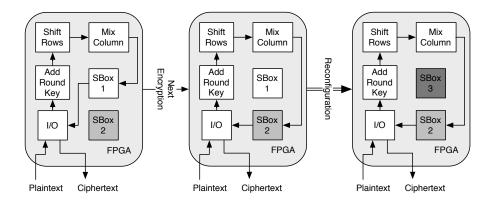

| Survey of Methods to Improve Side-Channel Resistance on Partial<br>Reconfigurable Platforms<br>Marc Stöttinger, Sunil Malipatlolla, and Qizhi Tian         | 63  |

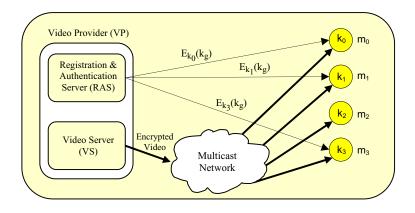

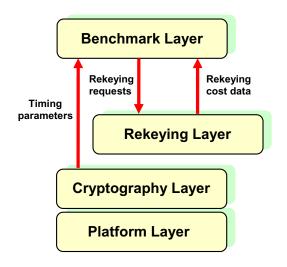

| Multicast Rekeying: Performance Evaluation<br>Abdulhadi Shoufan and Tolga Arul                                                                             | 85  |

| Robustness Analysis of Watermark Verification Techniques for FPGA<br>Netlist Cores<br>Daniel Ziener, Moritz Schmid, and Jürgen Teich                       | 105 |

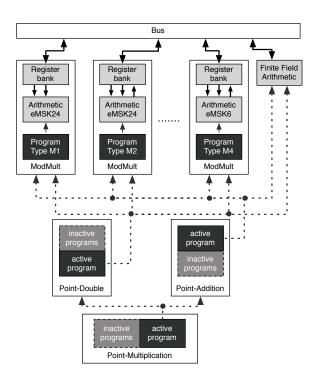

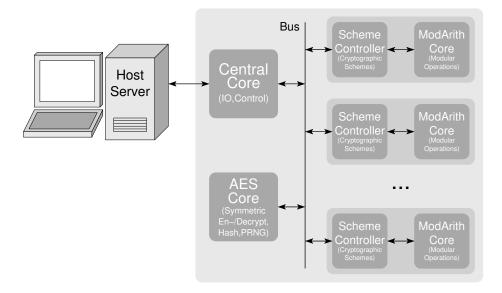

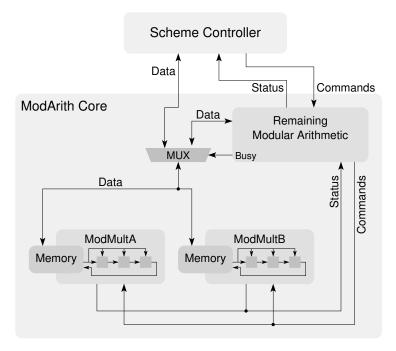

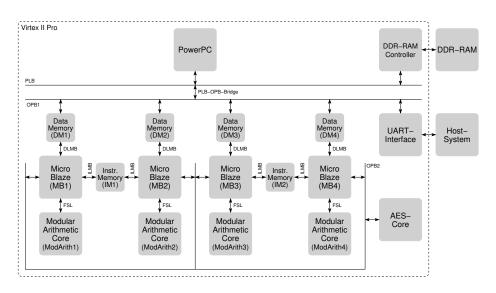

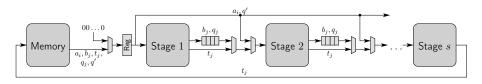

| Efficient and Flexible Co-processor for Server-Based Public Key<br>Cryptography Applications                                                               | 129 |

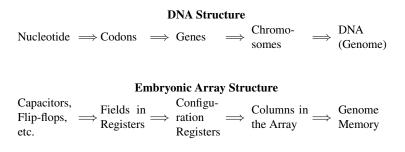

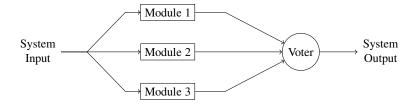

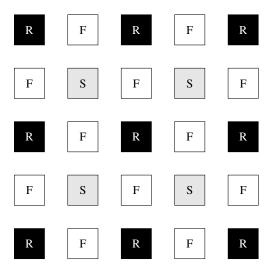

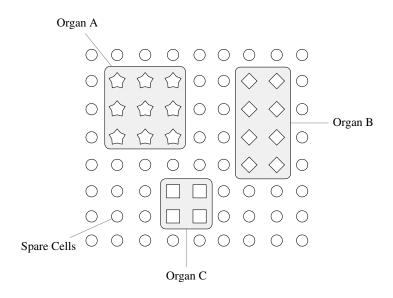

| Cellular-Array Implementations of Bio-inspired Self-healing Systems:<br>State of the Art and Future Perspectives<br>André Seffrin and Alexander Biedermann | 151 |

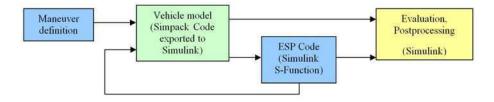

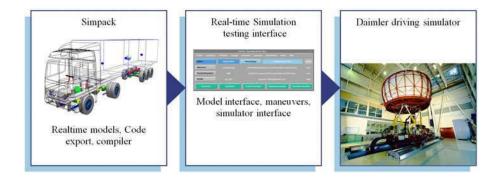

| Combined Man-in-the-Loop and Software-in-the-Loop Simulation:<br>Electronic Stability Program for Trucks on the Daimler Driving<br>Simulator               | 171 |

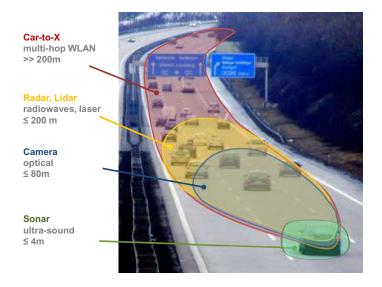

| Secure Beamforming for Weather Hazard Warning Application in<br>Car-to-X Communication                                                                     | 187 |

| Author Index                                                                                                                                               | 207 |

### Towards Co-design of HW/SW/Analog Systems

Christoph Grimm, Markus Damm, and Jan Haase

Vienna University of Technology Chair of Embedded Systems Gußhausstrae 27-29 1040 Wien, Austria {grimm,damm,haase}@ict.tuwien.ac.at

**Abstract.** We give an overview of methods for modeling and system level design of mixed HW/SW/Analog systems. For abstract, functional modeling we combine Kahn Process Networks and Timed Data Flow Graphs. In order to model concrete architectures, we combine KPN and TDF with transaction level modeling. We describe properties and issues raised by the combination of these models and show how these models can be used for executable specification and architecture exploration. For application in industrial practice we show how these models and methods can be implemented by combining the standardized SystemC AMS and TLM extensions.

**Keywords:** Analog/Digital Co-Design, KPN, Timed Data Flow, System Synthesis, Refinement, Refactoring, SystemC AMS extensions.

#### 1 Introduction

Applications such as wireless sensor networks, cognitive radio, and multi-standard communication systems consist of multi-processor hardware, complex multi-threaded software, and analog/RF subsystems. A new complexity raised by such applications is the tight functional interaction between the different domains, even at mixed levels of abstraction. Therefore, specification and architecture level design require a comprehensive approach for system level design. System level design includes the following issues:

- 1. *Executable specification* of the intended behavior including analog/RF behavior and multi-process HW/SW systems.

- 2. Architecture exploration by mapping the executable specification to abstract processors, and adding SW that improves behavior of analog/RF components (calibration, error detection/correction, etc.).

- 3. *System integration*, mostly by mixed-level simulation, upon availability of hardware designs and software programs.

Compared with HW/SW co-design, the co-design of HW/SW/Analog systems lacks models, methods and tools that go beyond modeling and simulation. A major problem for co-design of HW/SW/Analog systems is that modeling and

design of HW/SW systems at one hand, and of analog systems at the other use fundamentally different methods:

- HW/SW Co-design is done usually "top-down", relying on existing platforms that enable to some extent abstraction from realization. In contrast, analog design is rather done "bottom up".

- Design of HW/SW systems can to some extent be automated and formalized. In contrast, analog design is sometimes considered as "black magic".

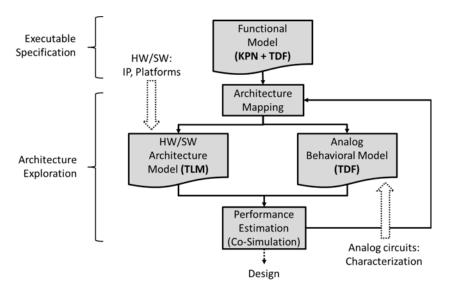

In this work we give an overview of methods that together draw the vision of a co-design methodology that is applicable to HW/SW/Analog Systems as a whole as shown by Fig. 1. We simplify the problem a lot by taking the analog (and also digital) circuit design out of the challenge. Instead we assume that "HW/SW/Analog Co-Design" gets characterized models from analog design, and validated IP or platforms from digital design. Like in HW/SW Co-Design, we propose an interactive strategy where architecture mapping selects a limited number or architectures that are evaluated by modeling and simulation based on SystemC. However, we propose to restrict modeling techniques to Kahn Process Networks (KPN), Timed Data Flow (TDF), and Transaction Level Modeling (TLM). This allows us to also address issues such as (maybe in future work automated) partitioning or system synthesis.

In the following, we first describe related work and KPN, Timed Data Flow (TDF) and Transaction Level Modeling (TLM). In Sect. 2 we discuss issues

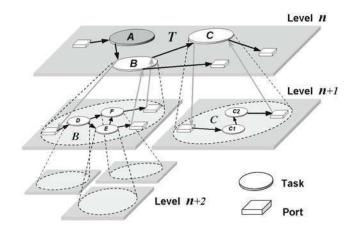

**Fig. 1.** HW/SW/Analog Co-Design with Executable Specification and Architecture Exploration consisting of architecture mapping and performance estimation by co-simulation of mixed TLM/TDF models

raised by the combination of KPN, TDF and TLM and show how they can be modelled using SystemC. In Sect. 3 we show how the combination of KPN, TDF and TLM models can be used for architecture exploration. In Sect. 4 we discuss a real-world example.

#### 1.1 Related Work

For many years, modeling languages were the main tools for designers of HW/-SW/analog systems. A prominent success was the advent of standardized and agreed modeling languages such as VHDL-AMS [1] and Verilog-AMS [2] that focus design of analog/digital subsystems. Recently, AMS extensions for SystemC have been standardized that address the co-design of mixed HW/SW/Analog systems better [3]. However, we believe that co-design should be more ambitious than just being able to co-simulate. First attempts to address co-design are made in [4,5,6,7] focusing the design of analog/mixed-signal subsystems. Interactive methodologies that tackle the transition from data flow oriented descriptions to analog/digital circuits are described in [8,9,10,11]. In order to deal with overall HW/SW/Analog systems, models from HW/SW Co-Design and from analog/RF design have to be combined.

In HW/SW Co-Design, models must show a maximum of parallelism. Task Graphs [12], Kahn Process Networks (KPN) [13] or Synchronous Data Flow (SDF) [14] are widely used in that context. Especially KPN and SDF maintain a maximum of parallelism in the specification while being independent from timing and synchronization issues, thus being useful for executable specification. Pioneering work was done in the Ptolemy Project [15,16]. Jantsch [17] gives a good summary and formalizes models of computation applied in embedded system design, including combined models. Transaction Level Modeling (TLM, [18,19]) and other means in SpecC and SystemC in contrast specifically enable to model timing and synchronization at architecture level. SysteMoC enables design of digital signal processing systems combining several models [20], but lacks support for analog/RF systems.

In analog/RF systems, behavioral representations abstract from physical quantities. However, abstraction from time is hardly possible because typical analog functions such as integration over time are inherently time dependent. Block diagrams in Simulink or Timed Data Flow (TDF) in the SystemC AMS extensions [3] therefore abstract structure and physical quantities while maintaining continuous or discrete time semantics.

It is difficult to bring the worlds of HW/SW Co-Design and analog/RF design together. Main focus of the Ptolemy project [15] was simulation and HW or SW synthesis, but not overall system synthesis. Approaches such as Hybrid Automata ([32], Model Checking) lack the ability to deal with complex HW/SW systems. Hybrid Data Flow Graphs (HDFG [5,21], Partitioning) focus the border between discrete and continuous modeling. The functional semantics of HDFG offers – in combination with functional languages for system specification – interesting perspectives for specification of parallel systems while being able to describe HW/SW/analog systems. However, due to availability of tools and languages we focus on KPN and TDF in the following as a starting point for system level synthesis, and TLM for architecture level modeling.

#### 1.2 Kahn Process Networks, Timed Data Flow, and TLM

Kahn Process Networks (KPN). KPN are a frequently used model of computation that allows easy specification of parallel, distributed HW/SW systems. In KPN, processes specified e.g. in C/C++ communicate via buffers of infinite length. Writing is therefore always non-blocking, whereas reading is blocking. KPN are an untimed model of computation: Timing is not specified and not necessary because the results are independent from timing and scheduling. KPN are specifically useful for the executable specification of HW/SW systems, because they – in contrast to sequential program languages – maintain parallelism in an executable specification and therefore enable the mapping to parallel hardware, e.g. multi-processor systems. A particular useful property of KPN is that it enables abstraction of timing and scheduling: Outputs only depend on the input values and their order (determinacy), provided all processes are deterministic. Non-determinacy can for example be introduced by a non-deterministic merge process.

In order to enable execution, scheduling algorithms (e.g. Park's algorithm [22]) may be defined that restrict the size of the buffers (Bounded KPN, BKPN). However, a limited size of buffers cannot be guaranteed in general.

**Timed Data Flow (TDF).** In order to overcome the restrictions of KPN considering scheduling and size of buffers, different subsets of KPN have been defined, most prominent of them the Synchronous Data Flow (SDF, [14]). In SDF, an undividable execution of a process consumes a constant number of tokens or samples from the inputs and generates a constant number of tokens at the outputs. Under these conditions, a static schedule with size-limited buffers can be determined before execution of the processes by solving the balancing equations for a cluster of processes. For repeated inputs, the schedule is repeated periodically. Like KPN, SDF is an untimed model of computation. Nevertheless, SDF is used for representing digital signal processing (DSP) methods, assuming constant time steps between samples.

In Timed Data Flow (TDF, [3,31]), each process execution is assigned a time step. In case of multiple samples per execution, the time step is distributed equally between the samples. Apart from specification of DSP algorithms, this enables the representation of analog signals by a sequence of discrete-time samples while abstracting from physical quantities and assuming a directed communication between analog components. A major benefit of TDF for the specification of analog and RF systems is the ability to embed other "analog" formalisms in the processes. The analog formalisms can be transfer functions H(z) or H(s) and models of computation such as signal flow graphs or electrical networks while maintaining advantages of SDF such as finite sizes of buffers, static scheduling and analysis at compile-time. A limitation is the discrete-time representation of inputs and outputs.

Transaction Level Modeling (TLM) is rather a means for abstract modeling than a model of computation. It provides means to model communication of HW/SW systems at architecture level. The idea of Transaction Level Modeling (TLM) is to bundle the various signal-level communication events (request, acknowledge, ...) into a single element called a *transaction*. The OSCI TLM 2.0 standard [19] defines a TLM extension for SystemC. The TLM extensions for SystemC use a dedicated data structure for representing a transaction (the generic payload), which contains elements like a target address, a command and a data array. Transactions – or more precisely references to them – are then passed around through the system via method interfaces, and each system part works on the transaction depending on the role of the system part. A simple example might look like this: A TLM *Initiator* (e.g. a processor module) creates a transaction, sets its command to READ, sets its target address to the address in its virtual address space it wants to read from, and reserves an appropriate data array for the data to read. It then sends the transaction through a socket to a TLM *Interconnect* (e.g. a bus or a router), which might do arbitration, and passes it on to the appropriate target device according to the address, after mapping the virtual address to the physical address within the target device. The TLM *Target* (e.g. a memory) then would copy the desired data to the transactions' data array, and return the transaction reference.

This basically implements a memory mapped bus. However, in TLM 2.0 it is possible to augment the generic payload with custom commands. An important observation is that passing the reference through the system might look like passing a token, but the data associated to that token is mostly non-atomic and can in theory be of arbitrary size.

Regarding time, the TLM 2.0 standard offers interesting possibilities. By using *temporal decoupling*, it is possible to let every TLM initiator run according to its own local time, which is allowed to run ahead of the global simulation time. This is often referred to as *time warp*. The TLM 2.0 method interface foresees a delay parameter to account for the local time offset of the initiator issuing the transaction.

Synchronization with global time only occurs when needed, or with respect to predefined time slots. This technique reduces context switches and therefore increases simulation performance, with a possible loss of simulation accuracy. Using the facilities provided by the TLM 2.0 extensions in such a manner is referred to as the *loosely timed coding style*, in contrast to the so-called *approximately timed coding style*, where each component runs in lock-step with the global simulation time, and where the lifetime of a transaction is usually subdivided into several timing points.

#### 2 Executable Specification

The executable specification of a HW/SW/Analog system must be able to capture both analog behavior and behavior of a HW/SW system. Analog behavior is usually modeled by transfer functions or static nonlinear functions, i.e. using TDF model of computation; HW/SW systems are specified by multiple threads or processes, i.e. KPN. In the following we first discuss the combination of KPN and TDF for specification of behavior of HW/SW/Analog systems. Then we show how to model behavior in these models of computation using SystemC.

#### 2.1 Combination of KPN and TDF

A combination of KPN and TDF with embedded "analog" models of computation offers properties required for both HW/SW Co-Design and design of analog systems, thus enabling HW/SW/Analog Co-Design. However, we have to define semantics of the combined KPN/TDF model of computation carefully considering the following issues:

- KPN is an untimed model of computation, but TDF requires a concept of time. One way to overcome this heterogeneity is to introduce time in KPN. However, KPN with time extensions will no longer be determinate in the sense of outputs which are independent from timing and scheduling.

- TDF is activated by advancement of time, assuming that a defined number of input samples is available (guaranteed e.g. by schedule of KPN). However, with arbitrary scheduling and timing, KPN output could produce too many or not enough samples for TDF input.

In the following we examine communication from TDF to KPN and from KPN to TDF. The communication from TDF to KPN is unproblematic: As KPN are untimed, they can execute when there are samples at the inputs, regardless of the time when they are produced by TDF. However, the communication from KPN to TDF is a more complex issue: TDF processes are executed following a static schedule that is triggered by time. The static schedule guarantees that enough samples are available at connections between TDF processes. However, this is not valid for communication from KPN (with by definition arbitrary scheduling) and TDF processes. Two different extensions solve this issue in different ways:

- 1. Assuming a KPN schedule that in time generates enough samples at the inputs of TDF.

- 2. Merging "default token" in case of absence of inputs from KPN to the TDF processes, e.g. because 1 has failed.

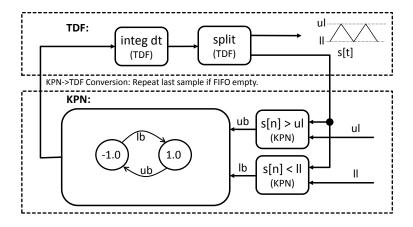

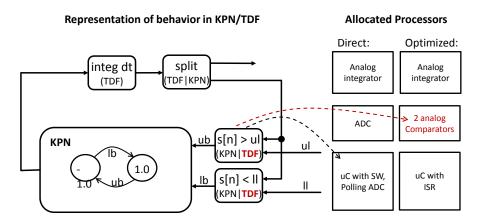

In the first case, the property of determinacy is preserved for the whole model. In the second case, determinacy is not preserved because the default tokes are merged in a non-deterministic way. **Simple Example: Executable Specification of a Signal Generator.** As an example we give a very simple signal generator shown by Fig. 2. The signal generator produces a saw tooth shaped signal. We use a TDF model to describe integration over time, and a KPN to observe the TDF output and to switch the input of the TDF depending on the limits *ul* and *ll*. The comparison is done by two KPN processes that continuously get a stream of TDF inputs, and omit an output *ub* or *lb* only if the upper or lower border is crossed.

Fig. 2. A signal generator that generates saw tooth signals within limits ul and ll can be modeled by a KPN with three processes (one specified by an automaton) and a TDF of two nodes

The output of the KPN is generated by a process that waits on an input from either comparison, then switches its internal state, and produces an output in the same rate as needed by the TDF cluster. In the given example we assume the scheduling will ensure that the TDF gets always enough inputs and we do not need to insert a special converter that would insert default outputs in case the KPN processes are not scheduled in time.

#### 2.2 Modeling and Simulation of KPN and TDF with SystemC

SystemC is a modeling language for HW/SW Co-Design that is based on C++. SystemC allows using C++ for the specification of processes. Processes are embedded in modules that communicate with each other via ports, interfaces, and channels. There are several interfaces and channels already defined in SystemC, but they can also be defined by the user. This way, various models of computation can be supported, including KPN (via the already existing sc\_fifo channel) and SDF (by extending SystemC). Time in SystemC is maintained globally by a discrete event simulation kernel. In the recently introduced AMS extensions, the TDF model of computation is provided. In the following we show how SystemC can be used to specify a mixed HW/SW/Analog system within the semantics of combined KPN and TDF. Modeling KPN using SystemC. Kahn Process Networks can be modeled by using processes (SC\_METHOD) which communicate only via FIFOs (sc\_fifo<T>) with appropriate properties: Blocking read, infinite size, and hence non-blocking write. Obviously, no implementation can offer infinite size, but in practice it is possible to have "large enough" FIFOs. In the case of a full FIFO, one can use blocking behavior and omit an error message. The following example shows a KPN process that distributes a stream of input samples u to two streams v and w:

```

SC_MODULE(split)

{

sc_fifo_in<int> u;

sc_fifo_out<int> v, w;

bool n;

SC_CTOR(split): n(true)

{

SC_THREAD(do_split); sensitive << u;</pre>

}

void do_split()

{

while(true)

Ł

if(n) v.write( u.read() ); else w.write( u.read() );

n = !n;

}

}

}

```

Modeling TDF using SystemC AMS extensions. The TDF model of computation is introduced by the AMS extensions 1.0 [3]. TDF models consist of TDF modules that are connected via TDF signals using TDF ports. Connected TDF modules form a contiguous structure called TDF cluster. Clusters must not have cycles without delays, and each TDF signal must have one source. A cluster is activated in discrete time steps. The behavior of a TDF module is specified by overloading the predefined methods set\_attributes(), initialize(), and processing():

- The method set\_attributes() is used to specify attributes such as rates, delays or time steps of TDF ports and modules.

- The method initialize() is used to specify initial conditions. It is executed shortly before the simulation starts.

- The method processing() describes the time-domain behavior of the module. It is executed at each activation of the TDF module.

At least one definition of the time step value and, in the case of cycles, one definition of a delay value per cycle has to be done. TDF ports are single-rate by default. It is the task of the elaboration phase to compute and propagate consistent values for the time steps to all TDF ports and modules. Before simulation,

the scheduler determines a static schedule that defines the order of activation of the TDF modules, taking into account the rates, delays, and time steps. During simulation, the **processing()** methods are executed at discrete time steps. The following example shows the TDF model of a mixer. The **processing()** method will be executed with a time step of 1 µs:

```

SCA_TDF_MODULE(mixer) // TDF primitive module definition

{

sca_tdf::sca_in<double> rf_in, lo_in; // TDF in ports

sca_tdf::sca_out<double> if_out; // TDF out ports

void set_attributes()

{

set_timestep(1.0, SC_US); // time between activations

}

void processing() // executed at activation

{

if_out.write( rf_in.read() * lo_in.read() );

}

SCA_CTOR(mixer) {}

};

```

In addition to the pure algorithmic or procedural description of the processing() method, different kind of transfer functions can be embedded in TDF modules. The next example gives the TDF model of a gain controlled low pass filter by instantiating a class that computes a continuous-time Laplace transfer function (LTF). The coefficients are stored in a vector of the class sca\_util::sca\_vector and are set in the initialize() method. The transfer function is computed in the processing() method by the ltf object at discrete time points using fixed-size time steps:

```

SCA_TDF_MODULE(lp_filter_tdf)

{

sca_tdf::sca_in<double>

in;

sca_tdf::sca_out<double> out;

sca_tdf::sc_in<double> gain;// converter port for SystemC input

sca_tdf::sca_ltf_nd ltf; // computes transfer function

sca_util::sca_vector<double> num, den; // coefficients

void initialize()

ſ

num(0) = 1.0;

den(0) = 1.0;

den(1) = 1.0/(2.0*M_PI*1.0e4); // M_PI=3.1415...

}

void processing()

{

out.write( ltf(num, den, in.read() ) * gain.read() );

}

SCA_CTOR(lp_filter_tdf) {}

};

```

The TDF modules given above can be instantiated and connected to form a hierarchical structure together with other SystemC modules. The TDF modules have to be connected by TDF signals (sca\_tdf::sca\_signal<type>). Predefined converter ports (sca\_tdf::sc\_out or sca\_tdf::sc\_in) can establish a connection to a SystemC DE channel, e.g. sc\_signal<T>, reading or writing values during the first delta cycle of the current SystemC time step.

As discussed above, conversion from TDF to KPN is quite easy, if we assume an unbounded FIFO. A converter just has to convert the signal type:

```

{

sca_tdf::sca_in<double> in_tdf; // TDF in-port

sc_fifo_out <double> out_kpn, // KPN out-port

void processing()

{

out_de.write( in_tdf.read() );

}

SCA_CTOR(tdf_kpn_converter) { }

};

```

However, as explained before, the conversion can lead to a situation where not enough samples from KPN are available. The following piece of code demonstrates a simple converter from KPN to TDF that inserts a "DEFAULT" value and emits a warning to the designer that determinacy is no longer a valid property of the combined KPN/TDF model.

```

SCA_TDF_MODULE(kpn_tdf_converter)

{

sc_fifo_in<double> in_kpn,

// KPN in-port

sca_tdf::sca_out<double> out_tdf; // TDF out-port

void processing()

{

if ( !in_kpn.empty() )

// FIFO empty?

out_tdf.write( in_kpn.read() );

else

// we insert default

{

out_tdf.write( DEFAULT );

// DEFAULT from somewhere

warning("Non-determinate due to merge with default values");

}

}

SCA_CTOR(kpn_tdf_converter) { }

};

```

#### 3 Architecture Exploration

For HW/SW/Analog Co-Design we need a transition from an executable specification to one or more architectures, for which quantitative performance properties such as accuracy or power consumption are estimated. We call this process

11

"Architecture Exploration". In the following, we describe first how to map the executable specification to concrete architectures. It has to be emphasized that the implementation modeled by such an architecture mapping should show similar behavior to the exploration – with the difference that communication/synchronization and timing/scheduling are modeled in more detail for allowing performance estimation by modeling/simulation. Then, we focus on modeling issues that are raised when combining SystemC AMS extensions for modeling analog behavior, and SystemC TLM 2.0 for modeling architecture of HW/SW systems.

#### 3.1 Architecture Mapping to Analog and HW/SW Processors

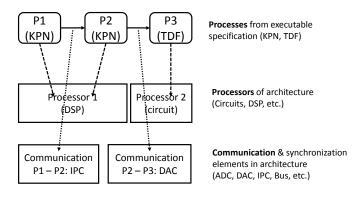

In order to come to an implementation of the executable specification, we map processes of KPN and TDF to allocated processors, and channels between KPN or TDF processes to allocated communication/synchronization elements as depicted in Fig. 3.

Fig. 3. Architecture mapping assigns processes to allocated processors and channels to allocated communication/synchronization elements that implement the specified behavior

Processors are components that implement the behavior of one or more processes. Communication/synchronization elements are components that implement the behavior of one or more channels.

TDF processes can be implemented by the following kind of processors:

- Analog subsystem. We consider an analog subsystem as an "analog processor" in the following. Analog processors cannot be shared; hence the relation between processors and processes is a 1:1 mapping in this case. The behavior of analog subsystems at architecture level can be modeled by adding the non-ideal behavior of the analog subsystem to the TDF model from the executable specification.

- DSP software running on a digital processor (DSP, Microcontroller, etc.). A DSP can implement a number of TDF processes, if the processor has appropriate performance, and a facility that takes care of discrete time scheduling

(e.g. interrupt service routing, ISR). For performance analysis, an instruction set simulator can replace the TDF processes implemented by the processor.

TDF clusters with feedback loops are a special case. The implementation depends on the delay that is inserted into the loop. If it is very small compared with time constants, the delay can be negotiated for implementation. If it is a dedicated delay used for specifying a delay in DSP methods, a switched capacitor or digital implementation is required.

KPN processes can be implemented by the following kind of processors:

- Software processes running on a digital processor. Such processors can, given an appropriate performance, implement one or more processes from one or more KPN. For performance estimation, an instruction set simulator can replace the TDF processes that are implemented by the processor.

- Application-specific co-processors. Such processors can, given an appropriate performance, implement one or more processes from one or more KPN. For performance analysis, the KPN processes can be substituted with timed models of the co-processors.

Special care has to be taken on the communication/synchronization elements. FIFOs of infinite size are obviously not an efficient implementation (although convenient for specification). For that reason the communication infrastructure in KPN and TDF is replaced with concrete communication/synchronization elements that implement similar behavior of the overall system with low cost for implementation.

The elements to be used for implementation depend on the mapping of processes to processors: Communication between KPN processes mapped on a micro-processor/DSP might use infrastructure for inter-process communication available in a real-time OS. However, in many cases an application-specific co-processor is used. In that case, one has to model communication between processor and (co-)processor at architecture level. Such communication usually goes at physical layer via memory-mapped registers or memory areas to which the communicating processes have access. Since this is a crucial part of the overall system (both considering correctness and performance), it was a focus of research in HW/SW Co-Design. Transaction-level modeling has become one of the most important means for modeling and simulation of this part. After architecture mapping, we get a model that consists of:

- TDF models that model the parts mapped to analog subsystems.

- An Instruction set simulator (ISS) that models the embedded SW parts and the used embedded platform hardware (DSP, Microcontroller). The ISS is interfacing either directly with the discrete-event simulator via TLM modeling.

- A TLM model that models the communication with specific co-processors that are modeled using the discrete-event model of computation

Obviously, many different mappings of an executable specification in KPN/TDF to processors are possible. Usually, only very few mappings are useful and often roughly known. In a number of cases the system partitioning in HW/SW/Analog systems can be determined by the following criteria:

- 1. Comparison operations are a good cut between analog and HW/SW domain if the compared values are in analog, because this saves a costly and slow A/D converter, e.g. like in the saw tooth generator example.

- 2. Signal conditioning of very small physical quantities, or at very high frequencies can only be implemented in analog, e.g. RF frontend in radio, instrumentation amplifier.

- 3. Clear hints for a digital implementation are: Signal processing in lower frequencies, high requirements for accuracy or for re-configurability, and processes with complex control-flow (e.g. automata).

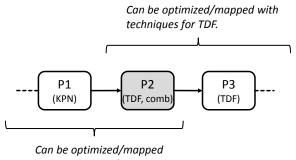

In order to optimize the mapping optimization techniques that go across the borders of different models of computation are useful as described in [5,21] using HDFG. Fig. 4 shows the principle of such optimizations.

with techniques for KPN.

Fig. 4. Optimization techniques for KPN and TDF are applicable across the borders between these models of computation under the conditions described below (details: see [5])

For such optimizations and to enable a higher flexibility in architecture mapping – note, that KPN/TDF processes can also be split into several processes – processes have to be identified whose semantics are identical, no matter if they are executed following the TDF or the KPN rules. The following rules apply:

1. Processes with time dependent function such as integration over time, or transfer functions in TDF cannot be shifted to KPN without changing overall behavior, because the non-deterministic scheduling of KPN would have impact on time of execution and hence the outputs.

- 2. Processes with internal state cannot be shifted across converters between KPN and TDF that non-deterministically insert "default" samples without changing overall behavior, because the inserted tokens would have an impact on the state and hence, the outputs.

- 3. Processes with internal state and time-independent function state can be shifted across converters between KPN and TDF if scheduling ensures samples from KPN to TDF are available, because in this case KPN and TDF both are pure stream-processing functions.

- 4. Processes with combinational function can be shifted between from KPN to TDF and vice versa, as long as the number and order of inserted default samples is not changed.

Simple Example: Architecture Mapping Signal Generator Specification. As an example we use again the simple signal generator. Of course, the KPN and TDF nodes can be mapped to (HW) processors that are close to their model of computation. The integrator in the TDF section, for example, can be implemented by an analog circuit in an easy and efficient way, while the KPN processes could be implemented using a microcontroller. The communication between microcontroller (with KPN implementation) and the analog integrator (with TDF implementation) will then require an analog/digital converter (ADC) that produces a discrete-time stream of outputs. We get another, more efficient mapping by "shifting" the border between KPN over the two comparisons s[n] > ul and s[n] < ll as shown in Fig.5. In this case we can assume that these two (initially KPN) processes become part of the TDF cluster, and hence we can also allocate an analog implementation for these processes. Because the

**Fig. 5.** Application of Repartitioning on the simple example allows finding a more appropriate architecture mapping. The nodes that observe the output (s[n]) are better implemented in continuous/discrete-time hardware that by a software that would have to poll the output of an analog/digital converter (ADC).

output of a comparison is digital, no ADC is required. The two comparators can be used to trigger interrupts that start an interrupt service routing that executes the automaton from the KPN.

Unfortunately, the most efficient architecture isn't as obviously to find as in the simple example given. For performance estimation in complex HW/SW/Analog Co-Design we have to create models that combine TDF models describing the analog part, an ISS (e.g. with TLM interfaces), and TLM models that models the HW/SW architecture and the operating system.

#### 3.2 Estimation of Quantitative Properties by System Simulation

For comparison of different architectures quantitative properties of an implementation have to be estimated. Known from HW/SW systems are estimation methods for the properties chip area, throughput, (worst case) execution time (e.g. [26]), and power consumption (e.g. [23,28]). Power profiling for complex HW/SW/Analog systems such as WSN is described in [25,27]. Although these properties are also to be considered for partitioning of HW/SW/analog systems, additional parameters are needed especially due to analog/RF subsystems. Accuracy and re-configurability are the most important criteria for partitioning if analog implementation is considered as well.

Accuracy is an important property because analog circuits have initially low accuracy that is insufficient for most applications. The art of analog design is to make an inaccurate circuit accurate by error cancellation techniques such as calibration, feedback or correlation, often involving digital signal processing. Estimation of accuracy therefore requires means to estimate accuracy across the border between discrete and continuous signal processing. First attempts in this direction have been done using a kind of automated error propagation computation by affine arithmetic [33].

*Re-Configurability* is a property that is to some extend only offered by HW/-SW implementation, but not only limited by an analog/RF implementation. Hence, the need for full re-configurability of a process requires its implementation in software. Reduced requirements for re-configurability of functionality only on occasion allow also FPGA coprocessor architectures. If re-configurability is restricted to changing parameters, or selecting a small number of alternatives, an analog implementation is possible. Partitioning strategies that specifically take care of re-configurability are described in [21].

Although the above mentioned estimation methods give some hints for improved partitioning, an overall system simulation at architecture level is absolutely essential due to complexity of most properties. Architecture level simulation should include models of all non-ideal properties of subsystems that have impact on the overall system behavior. To get architecture level models efficiently from a functional model such as the executable specification, methods from SW engineering such as refinement [11] or refactoring [9,10] are useful.

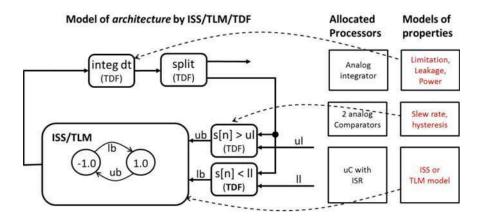

Fig. 6. Refinement of the processes from the executable specification to a model of an architecture by using models of non-ideal properties e. g. from the TU Vienna building block library

Refinement as proposed in [11] is based on a library with models of nonideal effects (e.g. [29]) such as jitter, or noise that can be used to augment the ideal, functional model with non-ideal properties for evaluation of different architectures while maintaining the abstract modeling using TDF. For example, we can model sampling jitter in the TDF model of computation by assuming an initially ideal signal x(t) that is sampled with a small delay  $\delta t$  caused by jitter. Hence, we assume that

$$\frac{x(t+\delta t) - x(t)}{\delta t} \approx \frac{dx}{dt} \tag{1}$$

and the error from jitter  $\in_{jitter}$  as  $x(t + \delta t) - x(t) \approx \delta t dx/dt$ . Hence, we can refine the ideal signal x(t) to a signal that is sampled with a jittering signal by adding  $\in_{jitter}$  to the ideal signal. In a similar way effects for most typical architecture level effects (distortions of nonlinear switches, limitation, noise, etc.) are modeled in the TUV library for communication system design.

Use of refactoring is proposed in [9,10]. Refactoring techniques are well suited to support the transition from abstract modeling in block-diagrams (e.g. in TLM model of computation) towards modeling with physical quantities and electrical networks by automatically changing the interfaces of the models.

#### 3.3 Coupling of TDF and TLM Models of Computation

For estimation of quantitative performance parameters such as accuracy (bit or packet error rates), a high-performance overall system simulation at architecture level is required. Behavioral models of analog circuits can be modeled easily using the TDF model of computation. For modeling performance of HW/SW architectures, loosely and approximately timed TLM models are useful. Therefore, a co-simulation between TDF and TLM model of computation is required. An important aspect of TDF/TLM co-simulation is how to integrate TDF data streams into TLM simulation and how to provide data streams out of TLM to TDF. In the following we describe how co-simulation between a TDF model and a *loosely* timed TLM model can be achieved. In loosely timed TDF models, the TLM initiators involved might run ahead of simulation time. Regarding the data, the approach is straightforward:

- **TLM to TDF:** The data bundled into the (write-) transactions arrives irregularly; therefore it has to be buffered into a FIFO. The TDF process then reads from this FIFO.

- TDF to TLM: The streaming data from the TDF side arrives regularly; yet the (read-) transaction requesting this data are irregular in general regarding time and data size requested. Here, a FIFO is also the solution: the TDF process writes on it, and it is emptied by the TLM side.

Of course, like in the coupling of KPN and TDF, corner cases can occur if the FIFOs run empty or (since we assume bounded FIFOs here) full. It is up to the designer how these cases are handled, since the semantics depend on the model at hand. If it is not acceptable, errors can be thrown, but providing fallback values resp. discarding values might also be an option.

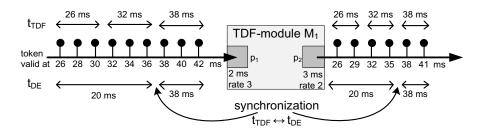

To minimize these corner cases, proper synchronization is very important. Since we assume loosely timed initiators on the TLM side, we can exploit that TDF (in the way it is implemented in the SystemC AMS extensions) also in general runs ahead of the global simulation time (especially if large data rates are used). That is,  $t_{TDF} \ge t_{DE}$  always holds, where  $t_{TDF}$  denotes the SystemC AMS simulation time, and  $t_{DE}$  denotes the SystemC simulation time.

Figure 7 illustrates this with a TDF module, which consumes 3 data tokens every 2 ms, and produces 2 data tokens every 3 ms. Beneath the tokens the point in (absolute) simulation time, where the respective token is valid, is indicated. Above and below that, the values for  $t_{\rm TDF}$  and  $t_{\rm DE}$  are given, when the tokens are processed.

At synchronization points, e.g. by accessing SystemC AMS converter ports that synchronize the SystemC discrete event (DE) kernel with TDF, the SystemC AMS simulation kernel yields to the SystemC simulation kernel such that the DE processes can catch on.

Figure 7 also shows that further time warp effects result from using multirate data flow. When a TDF module has an input port with data rate >1 it also receives "future values" with respect to tDE, and even tTDF . When a TDF module has an output port with data rate >1, it also sends values "to the future" with respect to  $t_{\rm DE}$  and  $t_{\rm TDF}$ . The difference to TLM is that the effective local time warps are a consequence of the static schedule, with the respective local time offsets only varying because of interrupts of the static schedule execution due to synchronization needs.

Fig. 7. Communication between TDF and TLM models of computation has to consider the time defined by the DE simulation kernel and the time that can run ahead in TDF and in TLM

This shows that with respect to the loosely timed TLM initiators, we have to deal with two parties which run ahead of global simulation time in their own special way. The question is when to trigger synchronization. In general, we want to trigger synchronization as infrequent as possible. But what are the conditions for triggering synchronization? The answer lies in the corner cases described above (buffer over- resp. underflow). We use these corner cases to trigger synchronization:

- **TLM to TDF:** If a buffer runs full, the transaction can simply be returned with an error message (a mechanism foreseen in TLM 2.0). If a buffer runs empty, however, we still have to feed the unstoppable TDF side. By synchronizing now we give the TLM side the chance to "catch on" and provide sufficient write transaction to fill the buffer.

- TDF to TLM: Again, an empty buffer in this case can be handled by a TLM error. A full buffer, however, needs new read-transactions to free space, which might be provided due to synchronization.

Of course, synchronization might still not resolve the respective issue. Then the designer has to specify the desired corner case behavior as described above.

The TDF to TLM conversion direction could be handled in an even more straightforward manner, if we would allow the converter (i.e. the TDF side) to act as an TLM initiator. In this case, the delay of the transaction could be set to the difference of tDE and the valid time stamp of the last token sent via the transaction (i.e.  $t_{TDF}$  + token number  $\cdot$  sampling period). Note that in this active approach there is no need for synchronization due to this delay annotation.

However, such an initiator would be very limited, since there is no natural way to obtain other transaction data like target address or command out of the streaming TDF input. Yet, it can make sense for a TLM initiator using TDF processes, for example when modeling a DSP which uses TDF models of signal processing algorithms. In this case, we have to write an application specific converter.

A possible approach for such a converter would work by dividing the TDF to TLM conversion into two parts incorporating the converter described above and using an additional wrapper, which acts on top of the "raw" converter and implements the necessary semantics (see also Sect. 2.1). In general, the wrapper would do two things: mutating transactions by interpreting their data sections, or creating new transactions.

A DSP model might get the request for a certain computation, which might be encoded by a transaction using extensions, as it is foreseen by the TLM 2.0 standard. It then would create a raw data transaction and send it (via a converter) to the appropriate TLM model performing the necessary algorithm, and insert the response data to the original transaction and return it. Another scenario might involve a raw data transaction carrying the target address encoded within its data section.

Then the wrapper would generate the new transaction target address accordingly, and delete the encoded address out of the data section. Note that the basic converters still play a crucial role in this approach, since they manage the conversion regarding time.

#### 4 Example

To demonstrate the feasibility of the approach, we implement a transceiver system using the TUV building blocks library, and show how

- The executable specification can be refined by adding non-ideal effects from analog subsystem to the behavior, and

- How we can attach a HW/SW system running on a DSP with two shared memories to the transceiver subsystems.

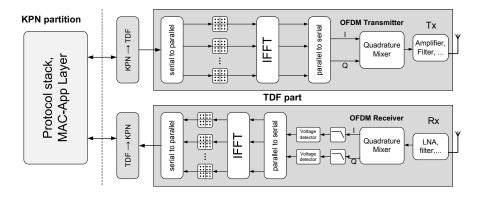

In the following, we won't describe real system synthesis. Instead, we will show that there is a seamless path from executable specification to architecture exploration and finally to the start of circuit design in analog and digital domain. As example, we use an OFDM transceiver that is modeled using the TU Vienna Building Block library for communication system design (source code: www.systemc-ams.org).

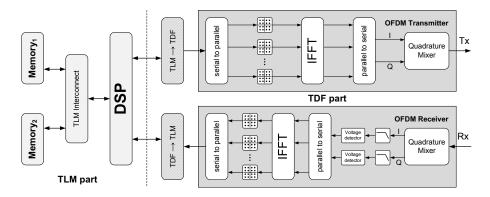

**Executable specification** – For the executable specification, most DSP tasks of the baseband processing are available in the library, modeled using the TDF model of computation. Furthermore, the executable specification includes some "analog blocks" such as quadrature mixer and LNA. These blocks are obviously analog, because they just modulate the information on specified physical quantities (modulated carrier). Apart from the pure transceiver, we assume that there is a protocol stack that handles media access (MAC layer) and other issues above this layer. Most of these tasks involve complex control flow and communication with application software. They are described best using the KPN model of computation. Figure 8 shows an overview.

Architecture Mapping and Architecture Exploration – The OFDM transceiver system offers directly a good partitioning (like most transceiver systems). Following the rules given in Sect. 3, we can map the executable

Fig. 8. Executable specification of an OFDM transceiver that combines KPN and TDF with embedded continuous-time models (filter, LNA)

specification as follows to architecture level processors, describing an initial mapping:

- Mixer, LNA, and filters must be implemented in analog due to excessively small signals and high frequencies and very low voltages (rule 2; signal conditioning)

- The baseband processing (FFT, IFFT, etc.) is described using TLM, can be implemented in SW, digital HW, or analog. Rule 3 recommends digital implementation.

- The protocol stack is modeled using KPN and has a quite complex control flow which demands implementation using SW.

Architectures to be investigated by architecture explorations are due to different mapping of the TDF part behind the mixer to DSP processor, digital, or analog hardware. The mapping of the TDF processes to DSP or dedicated digital HW basically spans the whole space of "SW defined" vs. "SW controlled radio". An interesting tradeoff specifically possible with HW/SW/Analog Co-Design is also the placing of.

Critical issues during architecture exploration are:

- Impact of jitter, noise, distortions, accuracy of A/D conversion on the dependability of communication.

- Performance of DSP subsystem under real operation conditions (i.e. shared memory architecture).

The DSP uses TDF models of an OFDM transmitter and of an OFDM receiver to receive and transmit data packets. These data packets contain WRITE and READ request, using a simple protocol, and refer to write and read transactions on the memory modules in the TLM part of the system. The DSP sends the requests to the memory via the bus, and returns the results (either the data for a READ request or an acknowledge for the WRITE request, or a fail in both cases). The TDF testbench provides the test data, and reads the results. The

**Fig. 9.** Model of OFDM transceiver for architecture exploration: Analog hardware (mixer, filter, frontend, ADC, DAC) and DSP hardware (FFT, IFFT, serializer, deserializer, etc.) are modeled using TDF model of computation; DSP for protocol stack is modeled using TLM style communication

carrier frequencies of the incoming and the outgoing data are different (10 MHz and 5 MHz, respectively).

The DSP basically constitutes the wrapper for the TLM-TDF conversion mentioned above. Since the requests have different lengths, the incoming TDF data is stored in a buffer, and it is checked whether a complete request has been received yet. If so, an appropriate transaction is created and sent to the TLM-Interconnect. Regarding the memory responses, the DSP can simply mutate the transactions (e.g. add the protocol data to the data of a READ request), and pass it to the OFDM transmitter via the TLM to TDF converter. Figure 9 shows an overview of the example system used for architecture exploration. The TLM to TDF converter used here is the one described at the beginning of the Section,

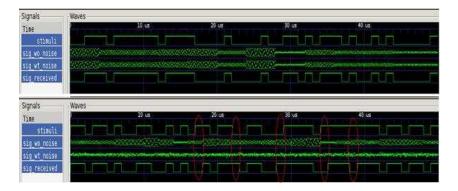

Fig. 10. Example screenshots of traces of the above model, one with an ideal channel without noise and attenuation (above), and one with noise, attenuation and resulting bit errors (below)

while the TDF to TLM converter uses the active approach described above. Figure 10 shows example traces of the system without noise and with noise and resulting errors.

#### 5 Conclusion

We have described key ingredients that might enable future tools to achieve real Co-Design of HW/SW/Analog systems: An executable specification by a combination of TDF and KPN is the first step. Architecture mapping assigns partitions of the combined TDF / KPN processes to either analog or digital (HW/SW) processors. Although we briefly described some known simple rules and techniques for estimation of quantitative parameters that might assist automatic partitioning, partitioning will still require an overall system simulation. Only such a simulation is able to estimate most - sometimes very complex - properties of different architectures. For overall system simulation, we have discussed issues in co-simulation of TDF (=analog) and TLM (=HW/SW) systems that allows to raise the level of abstraction and to increase performance of simulation.

It seems that most ingredients for automatic synthesis are available. However, the devil is in the details: Properties of analog subsystems and the overall system cannot be estimated easily. Therefore, in the near future, system partitioning will still be based on experiences. One reason for this is that for estimation of HW/SW systems, complex functional units or even whole platforms can be assumed as pre-designed components with fixed properties, usually area, delay, power consumption. This is not the case for analog components: Analog design goes rather bottom up; therefore the output of HW/SW/Analog Co-Design is rather a starting point for a design, but for which properties (area, power consumption, and accuracy) are not known in advance.

Another major drawback are the have to be estimated for system synthesis including analog/RF systems are, in addition to area, delay and power consumption the properties accuracy and flexibility resp. re-configurability. Unfortunately, accuracy is very difficult to predict at higher level of abstraction if analog circuits are involved. Furthermore, flexibility and re-configurability are currently only understood as properties of an implementation. Means to specify this property as integral part of requirements are still missing.

Nevertheless, HW/SW/Analog Co-Design and thereby integral approaches for system syntheses will gain impact: Applications such as wireless sensor networks, energy management in future smart grids, or the electric vehicle underline the need for more comprehensive design methods that also take care of analog/RF or analog power components as vital parts of IT systems. However, like - and even more - than in HW/SW Co-Design modeling and simulation will play a central role. With SystemC AMS extensions as the first standard for specification of HW/SW/Analog Systems at system level, the most important step towards HW/SW/Co-Design has been done and is being adopted by industry.

#### References

- Christen, E., Bakalar, K.: VHDL-AMS A hardware description language for analog and mixed-signal applications. IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing 46(10) (1999)

- 2. Standard: IEEE: Verilog. Verilog 1364–1995 (1995)

- Grimm, C., Barnasconi, M., Vachoux, A., Einwich, K.: An Introduction to Modeling Embedded Analog/Digital Systems using SystemC AMS extensions. In: OSCI SystemC AMS distribution (2008), Available on www.systemc.org

- 4. Huss, S.: Analog circuit synthesis: a search for the Holy Grail? In: Proceedings International Symposium on Circuits and Systems (ISCAS 2006) (2006)

- 5. Grimm, C., Waldschmidt, K.: Repartitioning and technology mapping of electronic hybrid systems. In: Design, Automation and Test in Europe (DATE 1998) (1998)

- Oehler, P., Grimm, C., Waldschmidt, K.: A methodology for system-level synthesis of mixed-signal applications. IEEE Transactions on VLSI Systems 2002 (2002)

- Lopez, J., Domenech, G., Ruiz, R., Kazmierski, T.: Automated high level synthesis of hardware building blocks present in ART-based neural networks, from VHDL-AMS descriptions. In: IEEE International Symposium on Circuits and Systems 2002 (2002)

- 8. Zeng, K., Huss, S.: Structure Synthesis of Analog and Mixed-Signal Circuits using Partition Techniques. In: Proceedings 7th International Symposium on Quality of Electronic Design (ISQED 2006) (2006)

- Zeng, K., Huss, S.: RAMS: a VHDL-AMS code refactoring tool supporting high level analog synthesis. In: IEEE Computer Society Annual Symposium on VLSI 2006 (2005)

- Zeng, K., Huss, S.: Architecture refinements by code refactoring of behavioral VHDL-AMS models. In: IEEE International Symposium on Circuits and Systems 2006 (2006)

- 11. Grimm, C.: Modeling and Refinement of Mixed-Signal Systems with SystemC. SystemC: Language and Applications (2003)

- Klaus, S., Huss, S., Trautmann, T.: Automatic Generation of Scheduled SystemC Models of Embedded Systems from Extended Task Graphs. In: Forum on Design Languages 2002 (FDL 2002) (2002)

- Kahn, G.: The semantics of a simple language for parallel programming. In: Rosenfeld, J.L. (ed.) Information Processing 1974, IFIP Congress (1974)

- 14. Lee, E., Park, T.: Dataflow Process Networks. Proceedings of the IEEE (1995)

- Eker, J., Janneck, J., Lee, E., Liu, J., Liu, X., Ludvig, J., Neuendorffer, S., Sachs, S., Xiong, Y.: Taming Heterogeneity – the Ptolemy Approach. Proceedings of the IEEE 91 (2003)

- Lee, E., Sangiovanni-Vincentelli, A.: A Framework for Comparing Models of Computation. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (1998)

- Jantsch, A.: Modeling Embedded Systems and SoCs. Morgan Kaufman Publishers, San Francisco (2004)

- Cai, L., Gajski, D.: Transaction level modeling in system level design. Technical Report 03-10. Center for Embedded Computer Systems, University of California (2003)

- Aynsley, J.: OSCI TLM-2.0 Language Reference Manual. Open SystemC Initiative (2009)

- Haubelt, C., Falk, J., Keinert, J., Schlicher, T., Streubühr, M., Deyhle, A., Hadert, A., Teich, J.: A SystemC-based design methodology for digital signal processing systems. EURASIP Journal on Embedded Systems (2007)

- Ou, J., Farooq, M., Haase, J., Grimm, C.: A Formal Model for Specification and Optimization of Flexible Communication Systems. In: Proceedings NASA/ESA Conference on Adaptive Hardware and Systems (AHS 2010) (2010)

- Parks, T.M.: Bounded Scheduling of Process Networks. Technical Report UCB/ERL-95-105. EECS Department, University of California (1995)

- Rosinger, S., Helms, D., Nebel, W.: RTL power modeling and estimation of sleep transistor based power gating. In: 23th International Conference on Architecture of Computing Systems (ARCS 2010) (2010)

- Henkel, J., Ernst, R.: High-Level Estimation Techniques for Usage in Hardware/Software Co-Design. In: Proceedings Asian Pacific Design Automation Conference (ASP-DAC 1998) (1998)

- Moreno, J., Haase, J., Grimm, C.: Energy Consumption Estimation and Profiling in Wireless Sensor Networks. In: 23th International Conference on Architecture of Computing Systems, ARCS 2010 (2010)

- Wolf, F., Ernst, R.: Execution cost interval refinement in static software analysis. Journal of Systems Architecture 47(3-4) (2001)

- 27. Haase, J., Moreno, J., Grimm, C.: High Level Energy Consumption Estimation and Profiling for Optimizing Wireless Sensor Networks. In: 8th IEEE International Conference on Industrial Informatics (INDIN 2010) (2010)

- Bachmann, W., Huss, S.: Efficient algorithms for multilevel power estimation of VLSI circuits. IEEE Transactions on VLSI Systems 13 (2005)

- Adhikari, S., Grimm, C.: Modeling Switched Capacitor Sigma Delta Modulator Nonidealities in SystemC-AMS. In: Forum on Specification and Design Languages (FDL 2010) (2010)

- Damm, M., Grimm, C., Haase, J., Herrholz, A., Nebel, W.: Connecting SystemC-AMS models with OSCI TLM 2.0 models using temporal decoupling. In: Forum on Specification and Design Languages (FDL 2008) (2008)

- 31. SystemC AMS Users Guide, OSCI (2010), www.systemc.org

- Alur, R., Courcoubetis, C., Halbwachs, N., Henzinger, T.A., Ho, P.H., Nicollin, X., Olivero, A., Sifakis, J., Yovine, S.: The Algorithmic Analysis of Hybrid Systems. Theoret-ical Computer Science 138(1), 3–34 (1995)

- Grimm, C., Heupke, W., Waldschmidt, W.: Analysis of Mixed-Signal Systems with Affine Arithmetic. IEEE Transactions on Computer Aided Design of Circuits and Systems 24(1), 118–120 (2005)

## A Flexible Hierarchical Approach for Controlling the System-Level Design Complexity of Embedded Systems

Stephan Klaus

Technische Universität Darmstadt Department of Computer Science Integrated Circuits and Systems Lab Hochschulstraße 10 64289 Darmstadt, Germany

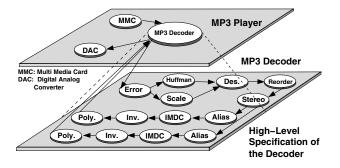

Abstract. This paper summarizes results of the PhD theses on systemlevel design of embedded systems at the Institute Integrated Circuits and Systems Lab under the survey of Prof. Dr.-Ing. Sorin Huss. A straightforward identification of suited system-level implementations of distributed embedded systems is increasingly restricted by the complexity of the solution space and the size of modern systems. Therefore, concepts are mandatory, which are able to control the design complexity and assist the reuse of components. A hierarchical, task-based design approach and two algorithms are developed, which allow to derive dynamically partial specification models for design space exploration on different levels of detail as well as task descriptions for IP encapsulation So, the descriptive complexity of specifications is considerably reduced and the execution time of system-level synthesis algorithm can be adopted to the current requirements of the designer. The task behavior is captured by Input/Output Relations, which represent a very general and powerful means of encapsulating internal implementation details and of describing data as well as control-flow information on different levels of detail. The necessity of these concepts are demonstrated by means of an MP3 decoder application example.

#### 1 Introduction

Since the beginning of computer-aided hardware synthesis in the early 70's, the progress can be characterized by a steady shift of the design entry towards higher levels of abstraction. At present, researchers focus on system-level design, which addresses the synthesis of complete systems based on coarse-grained specifications. This process can be detailed as the selection of the necessary resources (allocation) and the mapping of functional units onto the selected architecture in space (binding) and time (scheduling), whereby real-time and other constraints must be met. In particular, the non-functional requirements of embedded systems such as timing, cost, power consumption, etc., are extremely relevant for their later commercial success. This optimization process is restricted both by

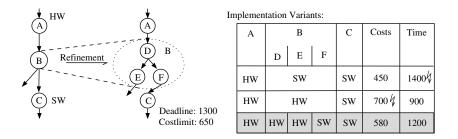

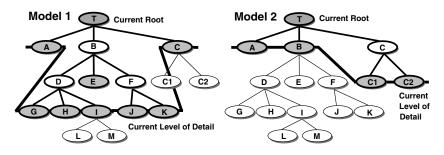

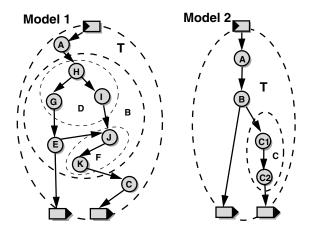

Fig. 1. Implementation Variants considering different Levels of Detail

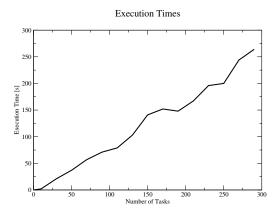

increasing complexity of systems and by shorter time to market, whereby the complexity in task-based specification models and therewith the execution of synthesis algorithms grows exponential with the number of tasks. A tasks represents a single, quite simple part of an algorithm of the complete specification, e.g. the Huffman decoding for an MP3 decoder. Even medium scaled embedded systems are so complex, that flat representations become too difficult for humans to handle and to comprehend. In the same manner as flat representations become too complex, the execution time of synthesis and design space exploration tools grows unacceptably, e.g., the simulation of an MP3 decoder takes 901s at instruction set level, while a transaction level simulation takes only 41s. Due to this fact, the design flow including all necessary implementation steps should be accomplished on a current adequate level of detail only. But the drawback of too abstract specifications is a loss of resulting quality, since the chosen level of detail directly influences the optimization potential. Figure 1 illustrates this problem by means of a hardware/software partitioning problem of task B. As it can be seen, the cost and latency deadlines can not be fulfilled if task B is completely implemented in software (first row) or hardware (second row). Instead of implementing task B completely in hardware or software, a mixed implementation is chosen, whereby task B is refined into a more detailed model consisting of the three tasks D, E and, F. So, task D and E are implemented in hardware, while F is mapped to software.

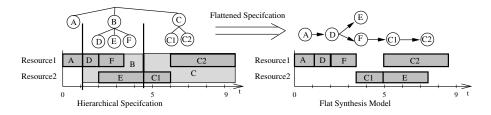

Such local refinements lead to the idea of static hierarchical synthesis algorithms. Hierarchical algorithms work recursively on the static specification hierarchy, whereat each module with its subtasks is optimized individually and the results are composed on the next higher level. This reduces the design complexity since smaller models have to be synthesized, but optimization potential is dropped away. The loss of optimization potential between static hierarchical synthesis algorithm and a global approach is depicted in Figure 2. The composition of the individual results on the next higher level does not allow to schedule task E in parallel to task C2, which is possible applying the flat synthesis process. Nevertheless, the complexity in the hierarchical case is considerably reduced, since in task-based specification models the complexity grows exponential with the number of tasks.

Fig. 2. Local versus Global Optimization