## André van Bezooijen Reza Mahmoudi Arthur van Roermund

ACSP Analog Circuits And Signal Processing

# Adaptive RF Front-Ends for Hand-held Applications

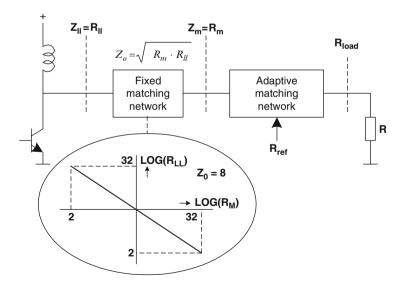

Adaptive RF Front-Ends for Hand-held Applications

#### ANALOG CIRCUITS AND SIGNAL PROCESSING SERIES

Series Editors: Mohammed Ismail Mohamed Sawan

For other titles published in this series; go to http://www.springer.com/series/7381

André van Bezooijen • Reza Mahmoudi Arthur van Roermund

## Adaptive RF Front-Ends for Hand-held Applications

André van Bezooijen EPCOS Netherlands Bijsterhuizen 11-22 6546 AS Nijmegen Netherlands andre.van.bezooijen@epcos.com

Reza Mahmoudi Eindhoven University of Technology Electrical Engineering Den Dolech 2 5600 MB Eindhoven Netherlands r.mahmoudi@tue.nl Arthur van Roermund Eindhoven University of Technology Electrical Engineering Den Dolech 2 5600 MB Eindhoven Netherlands A.H.M.v.Roermund@tue.nl

ISBN 978-90-481-9934-1 e-ISBN 978-90-481-9935-8 DOI 10.1007/978-90-481-9935-8 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: 2010937994

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### Contents

| 1 | Intr | oduction                                                   | 1  |

|---|------|------------------------------------------------------------|----|

|   | 1.1  | Context and Trends in Wireless Communication               | 1  |

|   | 1.2  | Resilience to Unpredictably Changing Environments          | 2  |

|   | 1.3  | Improvements by Adaptively Controlled RF Front-Ends        | 4  |

|   | 1.4  | Aim and Scope of This Book                                 | 5  |

|   | 1.5  | Book Outline                                               | 7  |

| 2 | Ada  | ptive RF Front-Ends                                        | 9  |

|   | 2.1  | Introduction                                               | 9  |

|   | 2.2  | RF Front-End Functionality 1                               | 10 |

|   |      | 2.2.1 Antenna Switch 1                                     | 10 |

|   |      | 2.2.2 Power Amplifier 1                                    | 1  |

|   |      | 2.2.3 Duplexer 1                                           | 13 |

|   |      | 2.2.4 Blocking Filter 1                                    | 14 |

|   | 2.3  | Fluctuations in Operating Conditions 1                     | 14 |

|   | 2.4  | Impact of Variables 1                                      | 16 |

|   |      | 2.4.1 Current Fluctuation 1                                | 16 |

|   |      | 2.4.2 Voltage Fluctuation 1                                | 18 |

|   |      | 2.4.3 Die Temperature Fluctuation 2                        | 21 |

|   |      | 2.4.4 Efficiency Fluctuation 2                             | 22 |

|   |      | 2.4.5 Discussion on the Impact of Variables 2              | 24 |

|   | 2.5  | Adaptive Control Theory 2                                  | 25 |

|   | 2.6  | Identification of Variables for Detection and Correction 2 | 27 |

|   |      | 2.6.1 Independent Variables 2                              | 28 |

|   |      | 2.6.2 Dependent Variables                                  | 29 |

|   | 2.7  | Conclusions on Adaptive RF Front-Ends                      | 32 |

| 3 | Ada  | ptive Impedance Control 3                                  | 35 |

|   | 3.1  | Introduction 3                                             | 35 |

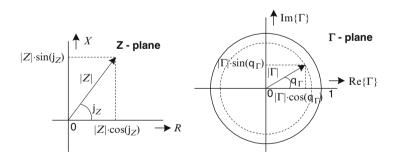

|   |      | 3.1.1 Dimensionality 3                                     | 37 |

|   |      |                                                            |    |

|   |                   | 3.1.2  | Non-linearity                                       | 39         |

|---|-------------------|--------|-----------------------------------------------------|------------|

|   |                   | 3.1.3  | Robust Control                                      | 41         |

|   |                   | 3.1.4  | Impedance Tuning Region                             | 45         |

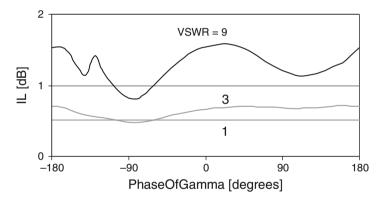

|   |                   | 3.1.5  | Insertion Loss                                      | 47         |

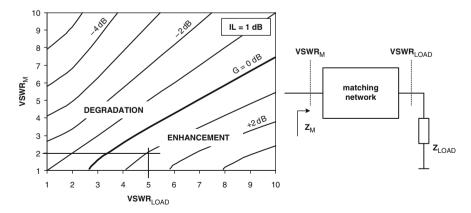

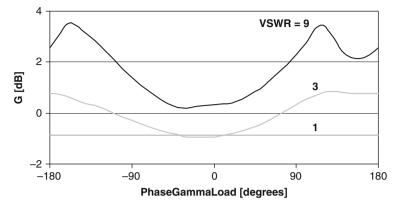

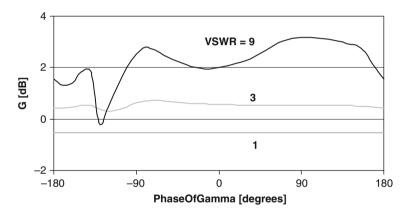

|   |                   | 3.1.6  | System Gain                                         | 48         |

|   | 3.2               | Mism   | atch Detection Method                               | 49         |

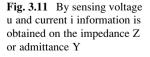

|   |                   | 3.2.1  | Sensing                                             | 49         |

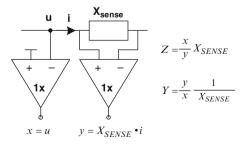

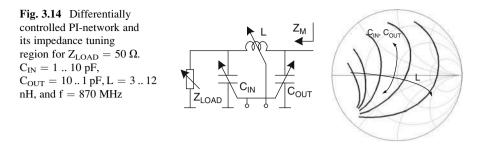

|   |                   | 3.2.2  | Detector Concept                                    | 50         |

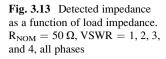

|   |                   | 3.2.3  | Simulation Results                                  | 51         |

|   |                   | 3.2.4  | Conclusions on Mismatch Detection                   | 52         |

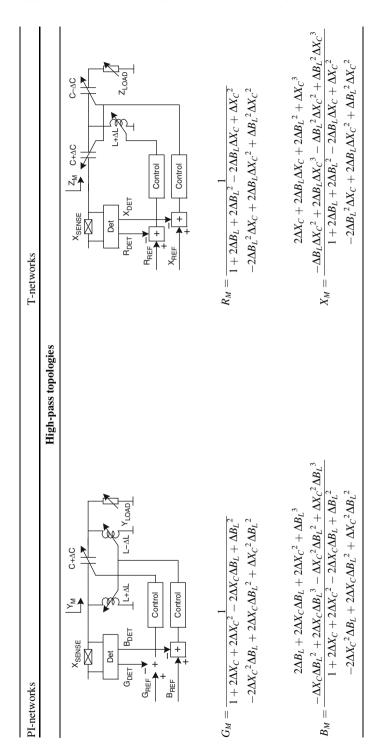

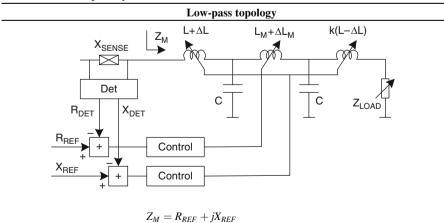

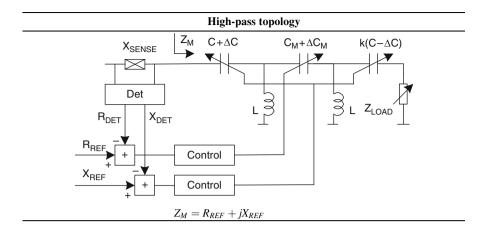

|   | 3.3               | Adapt  | ively Controlled PI-Networks Using Differentially   |            |

|   |                   | Contro | olled Capacitors                                    | 52         |

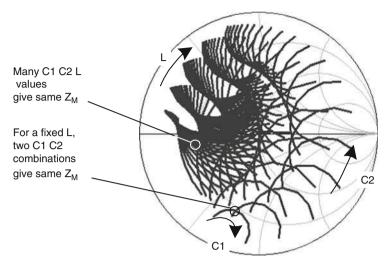

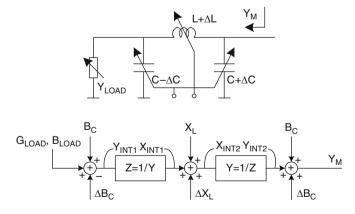

|   |                   | 3.3.1  | Concept                                             | 53         |

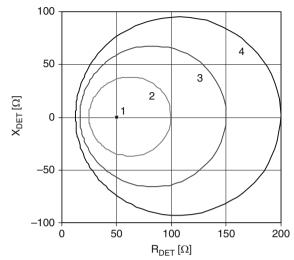

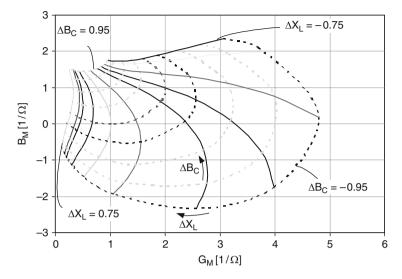

|   |                   | 3.3.2  | Differentially Controlled Single-Section PI-Network | 55         |

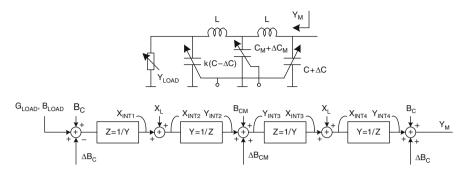

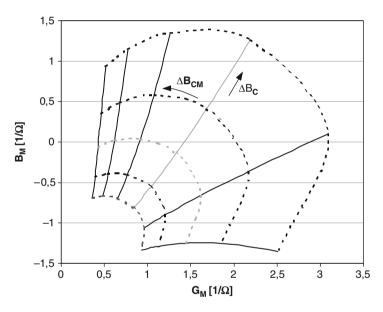

|   |                   | 3.3.3  | Differentially Controlled Dual-Section PI-Network   | 58         |

|   |                   | 3.3.4  | Simulations                                         | 59         |

|   |                   | 3.3.5  | Conclusions on Adaptively Controlled PI-Networks    | 64         |

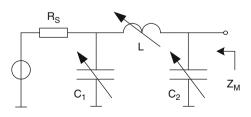

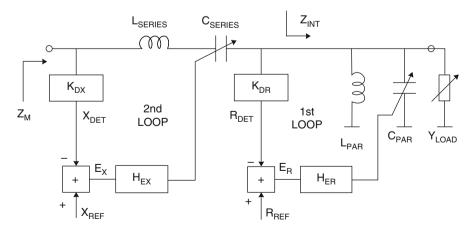

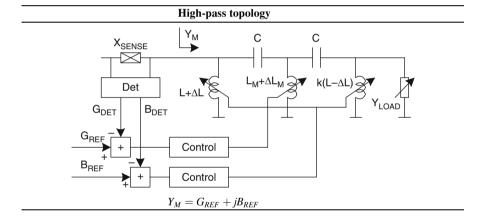

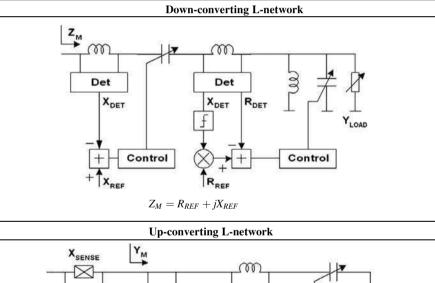

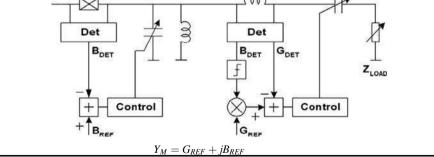

|   | 3.4               | Adapt  | ively Controlled L-Network Using Cascaded Loops     | 65         |

|   |                   | 3.4.1  | Concept                                             | 65         |

|   |                   | 3.4.2  | Actuation                                           | 66         |

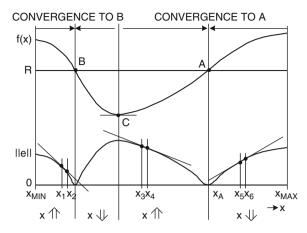

|   |                   | 3.4.3  | Convergence                                         | 70         |

|   |                   | 3.4.4  | Simulations                                         | 72         |

|   |                   | 3.4.5  | Capacitance Tuning Range Requirement                | 75         |

|   |                   | 3.4.6  | Insertion Loss                                      | 78         |

|   |                   | 3.4.7  | Tuning Range Requirement                            | 79         |

|   |                   | 3.4.8  | Conclusions on Adaptively Controlled L-Network      | 81         |

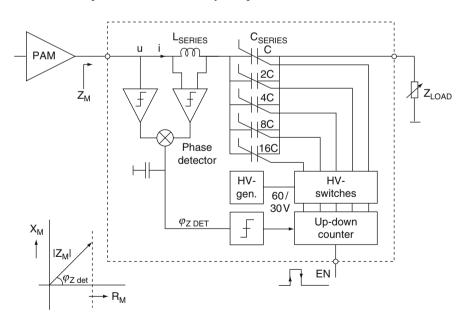

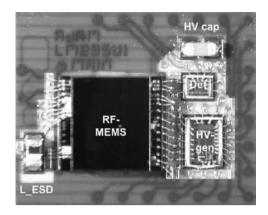

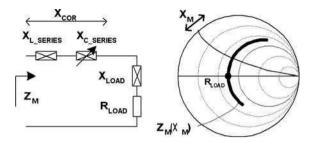

|   | 3.5               | Adapt  | ive Series-LC Matching Network Using RF-MEMS        | 82         |

|   |                   | 3.5.1  | Adaptive Tuning System                              | 83         |

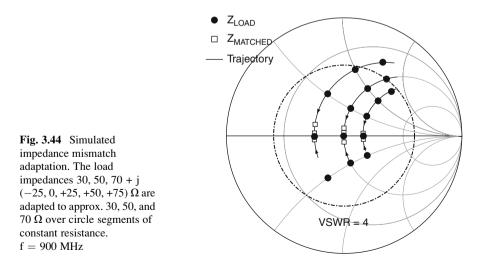

|   |                   | 3.5.2  | Adaptive RF-MEMS System Design                      | 87         |

|   |                   | 3.5.3  | Experimental Verification                           | 95         |

|   |                   | 3.5.4  | Conclusions on Adaptive Series-LC Matching Module   | 99         |

|   | 3.6               |        | Line Adaptation                                     |            |

|   |                   | 3.6.1  | Introduction                                        | 99         |

|   |                   | 3.6.2  | Concept                                             | 100        |

|   |                   | 3.6.3  | Implementation of Load Line Adaptation              | 102        |

|   |                   | 3.6.4  | Simulation Results                                  | 103        |

|   |                   | 3.6.5  | Conclusions on Load Line Adaptation                 | 105        |

|   | 3.7               | Concl  | usions on Adaptive Impedance Control                | 106        |

| 1 | A J -             |        | Dowon Control                                       | 107        |

| 4 | <b>Ada</b><br>4.1 |        | Power Control                                       | 107<br>107 |

|   | 4.1               | 4.1.1  |                                                     | 107        |

|   |                   |        | Over-Voltage Protection for Improved Ruggedness     |            |

|   |                   | 4.1.2  | Over-Temperature Protection for Improved Ruggedness | 108        |

|   | 4.2               | 4.1.3  | Under-Voltage Protection for Improved Linearity     | 109        |

|   | 4.2               | Sale ( | Operating Conditions                                | 109        |

|                                           | 4.3                                       | Power    | Adaptation for Ruggedness                           | 112 |

|-------------------------------------------|-------------------------------------------|----------|-----------------------------------------------------|-----|

|                                           |                                           | 4.3.1    | Concept                                             | 112 |

|                                           |                                           | 4.3.2    | Simulations                                         | 114 |

|                                           |                                           | 4.3.3    | Over-Voltage Protection Circuit                     | 115 |

|                                           |                                           | 4.3.4    | Over-Temperature Protection Circuit                 | 116 |

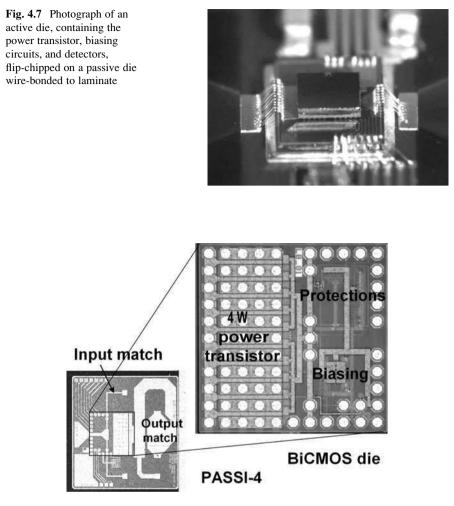

|                                           |                                           | 4.3.5    | Technology                                          | 117 |

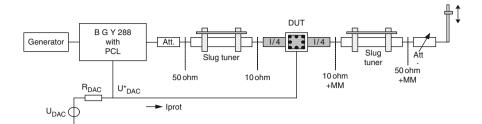

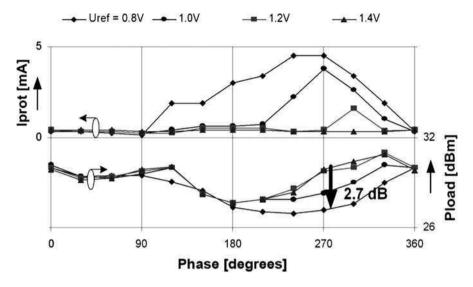

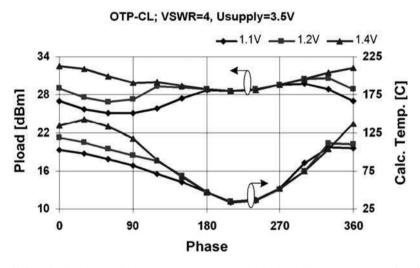

|                                           |                                           | 4.3.6    | Experimental Verification                           | 117 |

|                                           | 4.4                                       | Power    | Adaptation for Linearity                            | 121 |

|                                           |                                           | 4.4.1    | Concept                                             | 121 |

|                                           |                                           | 4.4.2    | Simulations                                         | 122 |

|                                           |                                           | 4.4.3    | Circuit Design                                      | 123 |

|                                           |                                           | 4.4.4    | Experimental Verification                           | 125 |

|                                           | 4.5                                       | Conclu   | usions on Adaptive Power Control                    | 127 |

|                                           |                                           |          |                                                     |     |

| 5                                         | Con                                       | clusion  | s                                                   | 129 |

|                                           |                                           |          |                                                     |     |

| A                                         | ppend                                     | lix A: C | Overview of Adaptively Controlled Matching Networks | 131 |

|                                           |                                           |          | Dual Danding Technique                              | 127 |

| A                                         | ppena                                     | IX B: A  | A Dual-Banding Technique                            | 137 |

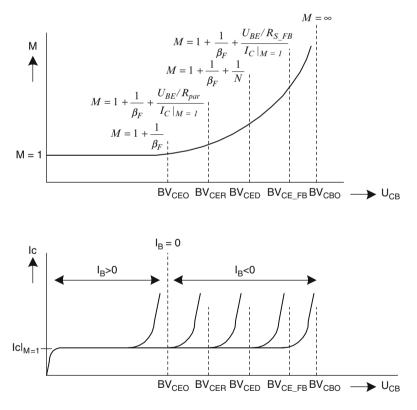

| A                                         | Appendix C: Transistor Breakdown Voltages |          |                                                     |     |

| rependix C. Transistor Dreakdown voltages |                                           |          |                                                     |     |

| Summary 1                                 |                                           |          |                                                     | 147 |

|                                           |                                           |          |                                                     |     |

| R                                         | References 14                             |          |                                                     |     |

## Abbreviations

| ACPR<br>ADS<br>AWS | Adjacent channel power rejection<br>Advanced design system<br>Advanced wireless service |

|--------------------|-----------------------------------------------------------------------------------------|

| BiCMOS             |                                                                                         |

| BST                | Bipolar-CMOS<br>Barium-strontium-titanate                                               |

|                    | Bulk acoustic wave                                                                      |

| BAW                | Duil accusic nate                                                                       |

| CdmaOne            | Code division multiple access one                                                       |

| CL                 | Closed loop                                                                             |

| CMOS               | Complementary MOS                                                                       |

| CV-curve           | Capacitance vs. voltage characteristic                                                  |

| DC                 | Direct current                                                                          |

| DS                 | Detector sensitivity                                                                    |

| EDGE               | Enhanced data rates for GSM evolution                                                   |

| EN                 | Base-band controller ENable signal                                                      |

| ESD                | Electro static discharge                                                                |

| ESL                | Equivalent Series inductance (L)                                                        |

| EVM                | Error vector magnitude                                                                  |

| FDD                | Frequency division duplex                                                               |

| FEM                | Front end module                                                                        |

| GPS                | Global positioning system                                                               |

| GSM                | Global System for mobile communication                                                  |

| GaAs               | Gallium arsenide                                                                        |

| HB                 | High band                                                                               |

| HBT                | Hetero-junction bipolar transistor                                                      |

| HSPA               | High speed packet access                                                                |

| HV-NPN             | High voltage NPN-transistor                                                             |

| IC                 | Integrated circuit                                                                      |

| IM3                | Third-order inter modulation distortion                                                 |

| LB                 | Low band                                                                                |

| LNA                | Low noise amplifier                                                                     |

| LSB                | Least significant bit                                                                   |

| LTCC               | Low temperature co-fired ceramic                                                        |

| LTE                | Long term evolution                                                                     |

|                    | -                                                                                       |

| LUT    | Look-up table                                    |

|--------|--------------------------------------------------|

| MEMS   | Micro electro mechanical system                  |

| MIM    | Metal-Insulator-Metal                            |

| MOS    | Metal-oxide-silicon                              |

| MSB    | Most significant bit                             |

| OL     | Open loop                                        |

| OCP    | Over current protection                          |

| OM     | Output match                                     |

| OTP    | Over temperature protection                      |

| OVT    | Over voltage protection                          |

| PA     | Power amplifier                                  |

| PAM    | Power amplifier module                           |

| PASSI  | Passive silicon                                  |

| PCB    | Printed circuit board                            |

| PCL    | Power control loop                               |

| pHEMT  | Pseudo-morphic high electron mobility transistor |

| PIFA   | Planar inverted-F antenna                        |

| PIN    | P-type intrinsic N-type doped regions            |

| Q      | Quality (-factor)                                |

| RF     | Radio frequency                                  |

| RMS    | Root-mean-square                                 |

| Rx     | Receiver                                         |

| SAW    | Surface acoustic wave                            |

| Si     | Silicon                                          |

| SMD    | Surface mounted device                           |

| SoS    | Silicon on sapphire                              |

| SOI    | Silicon on insulator                             |

| TDMA   | Time division multiple access                    |

| TRx    | Transceiver                                      |

| Tx     | Transmitter                                      |

| T&H    | Track-and-hold                                   |

| UMTS   | Universal mobile communications system           |

| VGA    | Variable gain amplifier                          |

| VSWR   | Voltage standing wave ratio                      |

| W-CDMA | 1                                                |

| WLAN   | Wireless local area network                      |

| WiMAX  | Worldwide interoperability for microwave access  |

## Symbols

| А                      | Capacitor plate area                                     |

|------------------------|----------------------------------------------------------|

| Ai                     | Current wave amplitude                                   |

| A <sub>IN</sub>        | Input signal amplitude                                   |

| A <sub>u</sub>         | Voltage wave amplitude                                   |

| A <sub>x</sub>         | Amplitude of detector input signal x                     |

| Ay                     | Amplitude of detector input signal y                     |

| B                      | Susceptance                                              |

| $B_{C\_PAR}$           | Susceptance of parallel capacitor                        |

| B <sub>DET</sub>       | Detected susceptance                                     |

| B <sub>INT</sub>       | Susceptance at an intermediate network node              |

| $B_{L\_PAR}$           | Susceptance of parallel inductor                         |

| B <sub>M</sub>         | Matching susceptance                                     |

| BV <sub>CBO</sub>      | Collector-base breakdown voltage for open emitter        |

| BV <sub>CEO</sub>      | Collector-emitter breakdown voltage for open base        |

| С                      | Capacitor                                                |

| C <sub>ARRAY</sub>     | Switched capacitor array capacitance                     |

| C <sub>DC</sub>        | DC-block capacitor                                       |

| C <sub>IN</sub>        | Input capacitor of differentially controlled PI-network  |

| C <sub>HOLD</sub>      | T&H circuit Hold Capacitor                               |

| C <sub>MEMS</sub>      | MEMS capacitance                                         |

| C <sub>MID</sub>       | Middle capacitor of dual-section PI-network              |

| C <sub>OFF</sub>       | OFF capacitance                                          |

| C <sub>ON</sub>        | ON capacitance                                           |

| C <sub>OUT</sub>       | Output capacitor of differentially controlled PI-network |

| C <sub>P</sub>         | Parasitic capacitor                                      |

| C <sub>PAR</sub>       | Parallel capacitance                                     |

| C <sub>SERIES</sub>    | Series capacitance                                       |

| C <sub>UNIT</sub>      | Unit cell capacitance                                    |

| CR                     | Capacitance tuning ratio                                 |

| CR <sub>ARRAY</sub>    | Array capacitance tuning ratio                           |

| CR <sub>C_SERIES</sub> | Tuning ratio of series capacitor                         |

| CR <sub>MEMS</sub>     | MEMS ON/OFF capacitance ratio                            |

| D                      | Disturbing signal                                        |

| e                   | Error                                            |

|---------------------|--------------------------------------------------|

| ER                  | Relative error                                   |

| F <sub>E</sub>      | Electro-static force                             |

| F <sub>M</sub>      | Mechanical force                                 |

| f <sub>T</sub>      | Transistor cut-off frequency                     |

| g                   | Gap height                                       |

| g <sub>0</sub>      | Gap height at zero bias                          |

| G                   | Conductance                                      |

| G                   | Gain                                             |

| $G_{C_{PAR}}$       | Conductance of parallel capacitor                |

| G <sub>DET</sub>    | Detected conductance                             |

| G <sub>LOAD</sub>   | Load conductance                                 |

| G <sub>L_PAR</sub>  | Conductance of parallel inductor                 |

| G <sub>M</sub>      | Matching conductance                             |

| G <sub>REF</sub>    | Reference conductance                            |

| G <sub>T</sub>      | Threshold amplifier gain of OTP loop             |

| G <sub>U</sub>      | Threshold amplifier gain of OVP loop             |

| $H, H_1, H_2$       | Transfer gain                                    |

| H <sub>E</sub>      | Error amplifier gain                             |

| H <sub>ER</sub>     | Error amplifier gain of real loop                |

| H <sub>EX</sub>     | Error amplifier gain of imaginary loop           |

| H <sub>R</sub>      | Matching network transfer gain of real part      |

| H <sub>T</sub>      | PA temperature transfer function                 |

| H <sub>U</sub>      | PA voltage transfer function                     |

| H <sub>X</sub>      | Matching network transfer gain of imaginary part |

| i                   | Branch current                                   |

| I <sub>AV</sub>     | Avalanche current                                |

| IB                  | Base current                                     |

| I <sub>COL</sub>    | Collector current                                |

| I <sub>C_CRIT</sub> | Critical collector current                       |

| I <sub>EM</sub>     | Emitter current                                  |

| I <sub>PROT</sub>   | Protection circuit output current                |

| I <sub>THR</sub>    | Threshold current                                |

| I(t)                | In-phase signal                                  |

| IL                  | Insertion Loss                                   |

| Io                  | Saturation current                               |

| k                   | RF-MEMS spring constant                          |

| k                   | Boltzmann's constant 1.38e-23 J/K                |

| K <sub>D</sub>      | Detector constant                                |

| K <sub>DR</sub>     | Detector constant of the resistance detector     |

| K <sub>DX</sub>     | Detector constant of the reactance detector      |

| L <sub>E</sub>      | Emitter inductance                               |

| L <sub>PAR</sub>    | Parallel inductance                              |

| L <sub>SERIES</sub> | Series inductance                                |

|                     |                                                  |

| M <sub>n</sub>                        | Avalanche multiplication factor                 |

|---------------------------------------|-------------------------------------------------|

| P <sub>DET</sub>                      | Detected output power                           |

| P <sub>DISS</sub>                     | Dissipated power                                |

| P <sub>IN</sub>                       | Input power                                     |

| P <sub>INC</sub>                      | Incident power                                  |

|                                       | Load power                                      |

| P <sub>load</sub><br>P <sub>out</sub> | Output power                                    |

| $P_{TRX}$                             | Power delivered by transceiver                  |

| $P_{REF}$                             | Reference power                                 |

| P <sub>SUP</sub>                      | Supply power                                    |

|                                       | Electric charge of a single electron 1.60e-19 C |

| q<br>Q(t)                             | Quadrature signal                               |

| r                                     | Ratio between DC-block and RF-MEMS capacitance  |

| R                                     | Resistance                                      |

| R<br>R <sub>BIAS</sub>                | Resistance of RF-MEMS biasing resistor          |

| R <sub>CROSS</sub>                    | Bond frame crossing resistance                  |

| R <sub>C_SERIES</sub>                 | Resistance of series capacitor                  |

| R <sub>DC</sub>                       | DC-blocking capacitor series resistance         |

| R <sub>DC</sub>                       | Detected resistance                             |

| R <sub>B</sub>                        | Base resistance                                 |

| R <sub>E</sub>                        | Emitter resistance                              |

| R <sub>E</sub><br>R <sub>EQ</sub>     | Equivalent resistance                           |

| R <sub>EQ</sub><br>R <sub>LOAD</sub>  | Load resistance                                 |

| RLR                                   | Return loss reduction                           |

| R <sub>L_SERIES</sub>                 | Resistance of series inductor                   |

| R <sub>M</sub>                        | Matching resistance                             |

| R <sub>MEMS</sub>                     | MEMS series resistance                          |

| R <sub>NOM</sub>                      | Nominal resistance                              |

| R <sub>REF</sub>                      | Reference resistance                            |

| R <sub>S</sub>                        | Source resistance                               |

| R <sub>SUB</sub>                      | Substrate resistance                            |

| R <sub>SUB</sub>                      | Substrate resistance                            |

| R <sub>TH</sub>                       | Thermal resistance                              |

| R <sub>THR</sub>                      | Threshold resistor                              |

| SoLG                                  | Sum of loop gains                               |

| t <sub>d</sub>                        | Dielectric thickness                            |

| t <sub>r</sub>                        | Equivalent roughness thickness                  |

| T <sub>AMB</sub>                      | Ambient temperature                             |

| T <sub>DET</sub>                      | Detected temperature                            |

| T <sub>DIE</sub>                      | Die temperature                                 |

| T <sub>j</sub>                        | Junction temperature                            |

| u                                     | Nodal voltage                                   |

| U <sub>ACT</sub>                      | RF-MEMS actuation voltage                       |

| U <sub>BAT</sub>                      | Battery voltage                                 |

| DAI                                   |                                                 |

| U <sub>BIAS</sub>    | Bias voltage                                       |

|----------------------|----------------------------------------------------|

| U <sub>BE</sub>      | Base-emitter voltage                               |

| U <sub>CB</sub>      | Collector-base voltage                             |

| U <sub>CE</sub>      | Collector-emitter voltage                          |

| U <sub>COL</sub>     | Collector voltage                                  |

| U <sub>DAC</sub> *   | Control voltage from Digital-to-Analogue Converter |

| $U_{DAC}^{*}$        | Adapted U <sub>DAC</sub>                           |

| U <sub>EQ</sub>      | Equivalent voltage                                 |

| U <sub>PI</sub>      | RF-MEMS pull-in voltage                            |

| U <sub>PO</sub>      | RF-MEMS pull-out voltage                           |

| U <sub>Q</sub>       | Bias voltage                                       |

| U <sub>REF</sub>     | Reference voltage                                  |

| U <sub>SUP</sub>     | Supply voltage                                     |

| UT                   | Thermal voltage                                    |

| v+ <sub>COL</sub>    | Incident voltage wave                              |

| V <sub>COL</sub>     | Reflected voltage wave                             |

| $v_{COL}(t)$         | Collector voltage                                  |

| V <sub>ACT</sub>     | Actuation voltage                                  |

| V <sub>CONTROL</sub> | Control voltage                                    |

| VDETECTOR            | Detected voltage                                   |

| V <sub>HOLD</sub>    | Hold voltage                                       |

| $V_{PI}$             | Pull-in voltage                                    |

| V <sub>PO</sub>      | Pull-out voltage                                   |

| V <sub>REF</sub>     | Reference voltage                                  |

| V <sub>SUPPLY</sub>  | Supply voltage                                     |

| Х                    | Reactance                                          |

| Х                    | Input signal                                       |

| $X_{C\_SERIES}$      | Reactance of series capacitor                      |

| X <sub>DET</sub>     | Detected reactance                                 |

| X <sub>INT</sub>     | Reactance at an intermediate network node          |

| $X_{L\_SERIES}$      | Reactance of series inductor                       |

| X <sub>M</sub>       | Matching reactance                                 |

| $X_{REF}$            | Reference reactance                                |

| X <sub>SENSE</sub>   | Sense reactance                                    |

| Y                    | Admittance                                         |

| Y                    | Output signal                                      |

| Y <sub>INT</sub>     | Intermediate admittance                            |

| $Y_{LOAD}$           | Load admittance                                    |

| Y <sub>M</sub>       | Matching admittance                                |

| $Y_{REF}$            | Reference admittance                               |

| Y <sub>SHUNT</sub>   | Shunt admittance                                   |

| Z                    | Impedance                                          |

| Z <sub>ANT</sub>     | Antenna impedance                                  |

| $Z_0$                | Characteristic impedance                           |

#### Symbols

| Z <sub>INT</sub>       | Intermediate impedance                                        |

|------------------------|---------------------------------------------------------------|

| $Z_{M}$                | Matching impedance                                            |

| Z <sub>LOAD</sub>      | Load impedance                                                |

| $\Delta B_{C}$         | Variable capacitor susceptance                                |

| $\Delta X_L$           | Variable inductor reactance                                   |

| βο                     | Transistor current gain                                       |

| ε <sub>r</sub>         | Relative dielectric constant                                  |

| ε <sub>0</sub>         | Dielectric constant 8.885 e-12 F/m                            |

| Γ                      | Reflection coefficient                                        |

| $\Gamma_{\rm COL}$     | Collector reflection coefficient                              |

| $\Gamma_{\text{LOAD}}$ | Load reflection coefficient                                   |

| $\Gamma_{M}$           | Matching reflection coefficient                               |

| η                      | Efficiency                                                    |

| φ                      | Base-emitter temperature dependency ( $\sim -1mV/^{\circ}C$ ) |

| $\phi_{\text{DET}}$    | Detected phase of impedance Z                                 |

| $\phi_i$               | Current wave phase                                            |

| $\phi_{u}$             | Voltage wave phase                                            |

| $\phi_x$               | Phase of detector input signal x                              |

| $\phi_{\mathbf{y}}$    | Phase of detector input signal y                              |

| φ <sub>z</sub>         | Phase of impedance Z                                          |

| θ                      | Phase of reflection coefficient                               |

| ω                      | Angular frequency                                             |

|                        |                                                               |

#### Chapter 1 Introduction

#### 1.1 Context and Trends in Wireless Communication

During the last century, technological innovations have been changing our ways of communication tremendously. The inventors and pioneering engineers of both the telephone [1] and radio [2, 3] were fascinated by the idea of exchanging real-time information over large distances, and their audience of first successful demonstrations were astonished and excited.

The big success of wired telephony and radio inspired the development of wireless mobile communication devices, like pack-sets, as forerunners of walkie-talkies and pagers [4, 5]. The first mobile radios, still using valves in those days, needed very heavy battery packs and were far from user-friendly.

Thanks to the invention of the transistor [6] and integrated circuit technology [7] their successors could be made much smaller and lighter. CMOS technology, digital circuit techniques and software paved the way for user-friendly handsets, partly due to the introduction of automatic tuning of the radio, and they enabled many features at low cost.

Nowadays, mobile communication is part of our social life [8]. Cellular networks connect people, any time anywhere, and they allow for the exchange of an ever-increasing amount of (real-time) information.

To a great extent, the information society of the twenty-first century will be mutually dependent on mobile communication networks, posing severe requirements on the quality of services. Therefore, the availability of high capacity reliable links as well as that of robust and user-friendly handsets will become even more important.

The ever increasing demand for channel capacity of mobile communication networks result in a steadily increasing number of frequency bands that are deployed in various parts of the world. Regularly, new communication standards are defined that use spectrum efficient modulation schemes and provide channel capacity that is adaptable to the users needs, of which the Advanced Wireless Service (AWS), High Speed Packet Access (HSPA), and Long Term Evolution (LTE) are recent examples [9]. Besides the RF-link that provides connection to the cellular infrastructure, many handsets can set-up an additional RF-link for short range data communication, using Bluetooth, WLAN (Wireless Local Area Network) or WiMAX (Worldwide Interoperability for Microwave Access), and have additional receivers for FM-radio, GPS (Global Positioning System) or even TV-on-mobile. The last few years, co-habitation of these radios in a small handset is getting more attention because the design of these multi-radio handsets turns out to be very challenging, for instance, because of mutual interference.

Since various wireless communication protocols are deployed in many different frequency bands, multi-mode multi-band phones (and components) are desired in order to benefit from economy of scale, and it allows the users to use their phone in many countries around the globe. Software defined radios facilitate such a flexible operation, in particular that of the digital and analog parts of the phone.

For the RF front-end part, multi-band phones commonly use several narrow-band RF signal paths in parallel because a single wide-band RF signal path cannot meet the very demanding requirements on receiver sensitivity and transceiver spurious emission.

Currently, re-configurable RF systems are being investigated [10] in order to reduce, at least partly, the number of parallel RF signal paths and hence, to reduce cost and size. These re-configurable RF systems require unusually linear, low loss switches with a large ON/OFF impedance ratio. The performance of classic PIN diode switches and pHEMT switches [11] is often insufficient to meet the requirements. But, recent advances in the development of RF-MEMS devices [12], CMOS switches on sapphire [13] as well as on high resistive silicon (HRS) will most likely enable the implementation of re-configurable RF front-ends in the near future.

The RF front-end is a very important part of a cellular phone, because typically it consumes most of the power and therefore determines the talk-time. Furthermore, since the RF front-end is optimized for efficiency it is typically the most non-linear part of the transmitter and therefore determines the quality of the RF link.

Because efficiency is so important, many efficiency enhancement techniques are under investigation, like: Envelope Tracking [16], Polar Loop [17], Doherty [18], and, since a few years, load line modulation [19]. All these techniques offer efficiency enhancement compared to a classic class-AB power amplifier, but, in addition, they often require adaptive control loops to meet the stringent linearity requirements.

#### **1.2** Resilience to Unpredictably Changing Environments

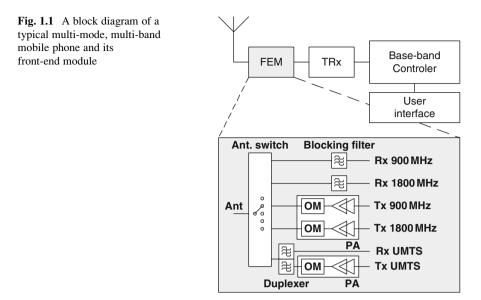

Nowadays, many different functions are built in handsets, but their main functionality remains that of a telephone combined with a radio receiver and transmitter to provide wireless connection between the handset and the cellular network infrastructure. A block diagram of this basic functionality is depicted in Fig. 1.1.

The front-end module (FEM) connects the antenna to selected transmitter (Tx) and receiver (Rx) signal paths that are frequency-band selective in order to minimize spurious emission and reception.

An important trend is that RF front-end functionality and complexity increases steadily because the number of mobile phone frequency-bands and communication standards keeps on getting larger in order to accommodate the growing need for channel capacity.

Monolithic integration of all RF front-end functionality is impossible because of the many contradicting requirements that are posed on the various functions. Therefore, RF front-ends are commonly realized as a module; an assembly of components placed on a common carrier and encapsulated into one package, while each component uses a dedicated technology.

To meet all specifications RF front-ends need to be resilient to changes in the environment in which the RF front-end module operates. The variables describing this changing environment can be categorized in two groups: *predictable*, and *unpredictable* variables.

Predictably changing variables:

- Output power

- Operating frequency

- Mode dependent modulation

Unpredictably changing variables:

- Antenna impedance variations due to:

- Body-effects

- Change in phone form factor

- Narrow antenna bandwidth

- Supply voltage variations due to:

- Battery charging and de-charging

- Temperature variations of the handset due to

- Ambient

- Dissipation determined by:

- Output power

- Antenna impedance

- Supply voltage

The variables: output power, operating frequency, and type of modulation are called *predictable* because, from a handset point of view, their absolute values and moments of change, are a priori known since they are determined by the cellular infrastructure and passed over to the handset. The variables: antenna impedance, supply voltage, and temperature are called *unpredictable* because the handset has no a priori knowledge on their absolute value nor on their rate of change.

Since the variables, from both categories, vary over wide ranges, large design margins are typically needed to realize resilient RF front-ends, which compromises the trade-offs to be made between the main performance parameters like:

- Maximum output power

- Efficiency

- Linearity

- Ruggedness

- · Receiver sensitivity

RF front-end design requirements can be relaxed by using a priori knowledge on the *predictably* varying variables to re-configure the RF front-end. For example, the base-band controller commonly selects the appropriate Rx/Tx line-up, activates biasing circuitry that is optimized per mode of operation, and adjusts the output power for optimum link quality. Such re-configurability, however, can not be used to correct for *unpredictably* changing variables due to a lack of a priori knowledge.

The problem addressed in this book is to improve mobile phone RF front-end performance, when operating in *unpredictably* changing environments.

#### 1.3 Improvements by Adaptively Controlled RF Front-Ends

In principle, the performance of a system operating in a changing environment will improve when the system is able to adapt itself to that environment [20]. The goal of the presented work is to explore adaptive control techniques [21] in order to improve one or more of the following RF front-end parameters:

#### 1.4 Aim and Scope of This Book

#### • Maximum output power

Under poor propagation conditions, the cellular infrastructure requests the handset to transmit at maximum output power. The effective maximum output power will reduce, however, when, under influence of body-effects, the load impedance of the power transistor increases. Adaptive control of the load impedance will secure the maximum output power and hence, it will improve link quality and thus the cellular network coverage under real life user conditions.

• Efficiency

At medium output power, the efficiency of a power amplifier depends on the load impedance of the power transistor and therefore, the efficiency varies under influence of fluctuating body-effects. Adaptive control of the load impedance will avoid low efficiencies and will maintain the talk-time of the phone under user conditions.

• Linearity

At high output power the amplifier linearity is strongly affected by the antenna environment and the battery supply voltage due to collector voltage saturation. Various adaptive methods can be used to prevent the power transistor from saturating and thus to preserve the modulation quality under extremes conditions.

• Ruggedness

To avoid destructive breakdown of the power transistor, while it operates under concurrent extremes in output power, antenna mismatch, and supply voltage, power amplifier optimized IC processes and large design margins are needed. Adaptive output power control techniques can be used to limit the collector peak voltage, die temperature, and/or collector current, when needed, in order to protect the power transistor against over-voltage, over-temperature, and/or over-current conditions respectively. This allows the use of standard silicon bipolar technology for the implementation of the power amplifier. Alternatively, the ruggedness of a power amplifier can be secured by adaptive techniques that reduce the extremes in antenna impedance and supply voltage.

• Receiver sensitivity Detuning of the antenna resonance frequency results in reduced sensitivity of the receiver, which can partly be recovered by adaptive correction of the antenna impedance.

#### 1.4 Aim and Scope of This Book

The aim of this book is to investigate adaptive control techniques in order to improve the performance of mobile phone RF front-ends that operate in *unpredict-ably* changing environments.

In this book two adaptive techniques are treated in particular:

- Impedance control

- Power control

These two techniques define the scope of this book. They have been investigated because both were identified as very promising methods, as discussed in Chapter 2. Each of these two approaches has distinct advantages and disadvantages.

The main advantage of adaptive impedance control is that compensation of antenna impedance fluctuations eliminates the impact of the parameter that affects RF front-end performance most.

But, system specifications pose severe requirements on insertion loss, distortion and tuning range of the variable capacitors, which are very difficult to meet. Therefore, new enabling technologies are being developed, of which RF-MEMS is one of them. Since the development of new reliable technologies usually takes many years, adaptive impedance control can be seen as a solution on the long term.

Since the power control concepts, treated in this book, are aiming for the use of standard silicon technology for the implementation of power amplifiers and their protection circuitry, these techniques can be considered as a short-term solution in making RF frond-ends more resilient to fluctuations.

The adaptive power control techniques presented are based on limiting the output power under extremes. Hence, they do not eliminate the main causes of these extremes, which forms a basic limitation of this approach.

A number of topics that are relevant in improving RF front-end performance are kept outside the scope of this book. Some of these topics are briefly discussed below. Several voltage supply adaptation techniques are well known:

- Supply voltage control of the power transistor for setting the phone output power in GSM-mode [22], using a modulation with constant envelope

- Supply voltage tracking in accordance to the average output power [23, 24] in EDGE and W-CDMA-mode, using a non-constant envelope modulations

- Envelope tracking [25] and polar modulation [26, 27] make use of supply voltage adaptation in accordance to the momentarily output power of amplitude modulated signals

Although these techniques provide power amplifier efficiency improvement, they do not eliminate the impact of unpredictable load impedance variations. They do not preserve maximum output power and do not prevent excessive collector currents nor die temperatures under worst case load conditions.

The antenna impedance matching that is achieved, adaptively, at the frequency of transmission, can be sub-optimal at the frequency of reception, especially when Tx and Rx frequencies are wide apart [28, 29]. Methods that provide optimum trade-offs in matching at Tx and Rx frequencies have not been investigated.

Adaptive impedance control techniques for receive-only modes (FM reception, television reception, GPS, etc.) have not been treated. For such modes, obtaining reliable information on mismatch is not easy.

Technologies for highly linear and low loss varactors and semiconductor switches are under development. In this book varactor and semiconductor based variable capacitors for the implementation of tunable matching networks have not been considered. For this book, the reliability of power amplifiers and RF-MEMS devices is kept out of scope.

#### 1.5 Book Outline

Chapter 2 describes the functionality of a mobile phone RF front-end. It explains why specifications on linearity, spurious emission, sensitivity, and power efficiency, etc. pose contradicting requirements that are difficult to meet, especially because the RF front-end needs to operate in a strongly changing environment. In order to provide insight on the impact of unpredictably changing variables (like antenna load impedance, battery supply voltage, etc.) on the RF front-end performance, a mathematical analysis is presented. Then, adaptive control is introduced as a solution in making systems independent of unpredictably changing environments. The variables that are most suited for detection and actuation are identified in a systematic manner, which results in a further investigation of two promising techniques: *adaptive impedance control* and *adaptive power control*, as visualized in Fig. 1.2.

In Chapter 3 *adaptive impedance control* techniques are presented that make RF front-ends resilient to antenna impedance variations. Since robust control over a wide impedance region is challenging, first some basic properties of impedance control are introduced, like its 2-dimensionality and the non-linear impedance transformation of high-order matching networks. To satisfy 2-dimensional control a true-orthogonal detector is presented that can provide mismatch information in the impedance, admittance, and reflection coefficient domain, which allows for control in the domain that suits the tunable network best. Adaptive control techniques for the following matching network topologies are presented:

- PI-networks

- · L-networks

- A series-LC network

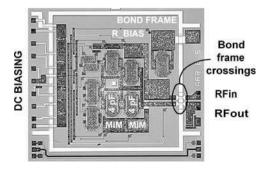

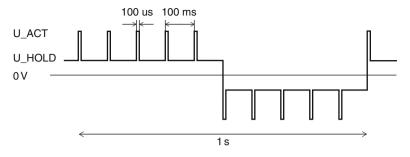

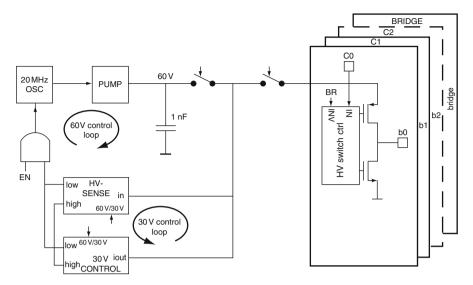

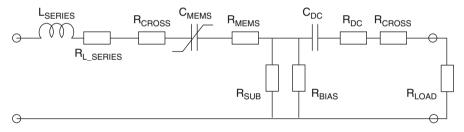

in an order of reduced impedance tuning region and a correspondingly reduced number of variable capacitors. Robust control of single-section and dual-section PI-networks over a wide impedance region is simplified by applying differential control of two capacitors. The control of L-networks is made robust by using two cascaded loops. To meet the very demanding requirements on linearity and insertion loss RF-MEMS devices are used for the implementation of an adaptively controlled series-LC network that was built as an hardware demonstrator.

Because of the strong synergy with adaptive impedance control, a load line modulation technique is presented, which uses a fixed impedance inverting network in order to obtain optimum power amplifier efficiency at maximum output power.

Fig. 1.2 Book map

To improve the performance of power amplifiers, realized in standard silicon IC-technology, *adaptive power control* techniques are presented in Chapter 4, which provide:

- Ruggedness improvement by over-voltage protection

- · Ruggedness improvement by over-temperature protection, and

- Linearity improvement by under-voltage protection

For these protections, the input power to the power transistor is limited once the detected variable exceeds a predefined value. This method is very effective in providing resilience because protection is provided irrespective of the environmental variable(s) that cause(s) the extreme.

Finally, main conclusions on *adaptive impedance control* and *adaptive power control* are drawn in Chapter 5.

#### Chapter 2 Adaptive RF Front-Ends

#### 2.1 Introduction

The RF front-end – antenna combination of a mobile phone is a vital part of the transmitter and receiver chain because its performance is very relevant to the quality of the wireless link between hand-set and cellular network base-stations.

As an introduction to RF-front-ends, in this chapter we will first discuss the main functions of an RF-front-end and explain the requirements that need to be posed on their performance. Then, the impact of fluctuations in mobile phone environment on the RF front-end performance is described as a chain of causes and effects. A theoretical analysis is presented that reveals relationships between these environmental variables and the main properties of a power amplifier: output power, efficiency, linearity, and ruggedness.

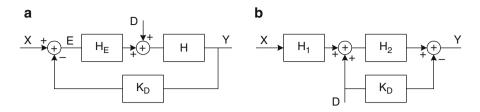

As a solution to the problems caused by fluctuations in the operating environment, adaptive control of the RF front-end is proposed. We will explain that using adaptive control based on feed-back is preferred, because it makes the RF frontend insensitive to a priori unknown fluctuations in load impedance, supply voltage, ambient temperature, as well as to spreads in component values, like the capacitance of RF-MEMS devices and the RF parasitics of impedance matching networks and power transistors.

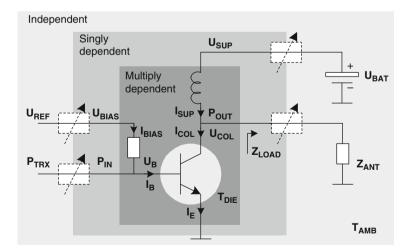

In order to identify the variables that are most suited for detection and actuation, all variables of interest are systematically grouped in three distinct categories: independent, singly dependent, and multiply dependent variables. Analysis on these categorized variables reveals that adaptive impedance control, supply voltage control, and power control are the most suited techniques in reducing the sufferings from fluctuations in operating conditions.

#### 2.2 **RF Front-End Functionality**

Nowadays, many different functions are built in handsets, but their main functions remains that of a telephone combined with a radio receiver and transmitter to provide a wireless connection between the handset and the cellular infrastructure. A block diagram of this basic functionality is depicted in Fig. 1.1.

The antenna is connected through a so-called front-end module (FEM) to the transceiver (TRx) to provide a bi-directional wireless RF link. Information is passed over, back and forwards, between the user and base-band controller via various user interfaces, like key-pads, microphone, loudspeaker and display.

The base-bands controller processes received data as well as data that needs to be transmitted and maintains synchronized connection to the cellular network.

The front-end module connects the antenna to selected transmitter (Tx) and receiver (Rx) signal paths that are frequency-band selective in order to minimize spurious emission and reception. The complexity of these front-end modules increases steadily because the number of mobile phone frequency-bands and communication standards keeps on getting larger.

In the next sections, the functionality and main specifications of the following RF front-end functions are discussed:

- Antenna switch

- Power amplifier (PA) line-up with output matching (OM) networks

- Duplexer

- Receiver blocking filter

#### 2.2.1 Antenna Switch

The main functionality of the antenna switch is to selectively connect the antenna to one or more RF line-ups and to isolate the selected line-ups from the other line-ups. Since antennas are relatively large structures, multi-band phones preferably use a single antenna that covers the various cellular frequency bands. RF receiver and transmitter line-ups must be relatively narrow-band, in order to meet the specifications. Therefore, multiple line-ups are required to cover multiple bands. To avoid interaction between the operational Rx (receiver) and Tx (transmitter) line-up and to avoid parasitic loading by inoperative line-ups, isolation is required. For the TDMA (Time Division Multiple Access) based GSM/EDGE line-ups the antenna switch provides this isolation, whereas for W-CDMA (Wide-band Code Division Multiple Access) based UMTS (Universal Mobile Communications System) line-ups the isolation between Rx and Tx is given by a duplexer and the isolation towards inoperative line-ups by the antenna switch.

Besides isolation the antenna switch has to meet other specifications that are briefly discussed below.

- Linearity of the switch is important in meeting the spurious emission requirements, in particular at the second and third harmonics in GSM-mode because in GSM-mode the maximum output power (2 W) is much larger than for EDGE (0.5 W) and W-CDMA (0.25 W) mode. In a multi-standard environment strong GSM interferers cause in-band inter-modulation products with the transmitted UMTS signal hampering the reception of weak UMTS signals. Therefore, the antenna switch third-order inter-modulation distortion (IM3) requirements are very demanding [30] and usually difficult to meet.

- The insertion loss of the antenna switch is important because it results in a reduction in power added efficiency (and thus in talk-time of the phone) and a reduction in receiver sensitivity (and thus in maximum down link capacity).

- In multi-band phones the antenna switch has to meet isolation, insertion loss and distortion requirements over a relatively wide frequency range. Therefore, narrow-band LC resonance circuits can often not be applied to improve switch performance.

For single-band phone applications, antenna switches are often implemented by PIN (P-type Intrinsic N-type doped regions) diodes because these silicon-based diodes are very cheap. For implementation of more complex switching functions, required in multi-band phones, PIN diodes are less suited because the many biasing circuits introduce too much parasitics and the forward biased diodes take too much bias current. Instead, pHEMT (Pseudo-morphic High Electron Mobility Transistor) switches are used because their gates are DC-isolated from the channel, which renders biasing circuits unnecessary and controlling these gates requires no current. Currently, CMOS switches are being developed on sapphire and silicon-on-insulator, which might offer a smaller size alternative to the use of pHEMT, because it makes DC-block capacitors redundant.

#### 2.2.2 Power Amplifier

The main function of a power amplifier is to accurately amplify the signal applied at its input and to deliver power to its loading impedance. The power amplifier, including its output-matching network, is important to the overall performance of the handset since the power amplifier typically consumes the largest part of the power in a handset when active, and is therefore the most important factor in the talk time of a handset. For that reason, power efficiency is a very important specification of a PA. The main function of the output-matching network is to provide an optimum load impedance, so-called load line, to the power amplifier transistor. This network transforms the

antenna impedance (usually assumed to be 50  $\Omega$ ), by several LC-sections, to the load impedance that results in an optimum compromise between power efficiency and linearity. As part of that optimum, the output-matching network should also provide the proper impedance at the second harmonic, or even at the third harmonic. The efficiency specification has to be achieved while meeting the many other specifications that are required for proper operation of the handset within the cellular system. These specifications are briefly discussed.

- Linearity is important especially for the most recent communication standards that use advanced modulation schemes to achieve better spectral efficiency, but which results in a non-constant envelope of the RF signal. On system level the amplifier non-linearity results in so called spectral re-growth. In-band energy is transformed into energy out of band that might disturb reception in adjacent frequency channels. In addition, non-linearity distorts the amplitude and phase information modulated onto the transmitted carrier, which hampers proper demodulation on the receiving side.

- Robustness is important because optimization of efficiency often results in voltages and currents close to the reliability limits of the technology. Extreme operating conditions, for instance due to antenna mismatch, can result in performance degradation or even complete failure of the device. Conversely, countermeasures that prevent such robustness problems often result in reduced efficiency of the power amplifier.

- Thermal behavior has a strong impact on the reliability of power amplifiers because high temperatures strongly accelerate failure mechanisms. Over-heating of the phone, for instance due to antenna mismatch, is not only inconvenient to the user, but can even result in destructive breakdown of the power amplifier.

- Stability of power efficient amplifiers is a critical design aspect, especially under load mismatch conditions. To secure stability often damping is required in order to reduce the amplifier gain at the cost of efficiency.

- Spurious emissions, which can interfere with other electronic equipment or with transmissions from other handsets or from base-stations in the same system. Therefore, the output-matching network must reject harmonic frequency components generated by the power transistor. Meeting harmonic rejection requirements is challenging, especially in GSM-mode, when the power transistor is driven in hard saturation.

- Transmitted noise, especially in the receive band of the system and co-existent systems, needs to be low since this affects the receiver sensitivity in these systems.

- The insertion loss of the output matching networks is important because the corresponding power dissipation has a significant impact on the power efficiency of the front-end module.

Most power amplifiers use a mix of technologies. GaAs HBT technology is most often used for the implementation of the multi-stage RF line-up because this technology offers the best trade-off between breakdown voltage and bandwidth. Output power control blocks, often used in GSM PAs for fast up and down ramping of the output power, are usually implemented in CMOS technology. Power amplifier implementations in standard BiCMOS and CMOS processes are subject of research. To secure ruggedness over-voltage protection circuits [31, 32] are often needed because the breakdown voltages of the NPN transistors are usually too low to withstand extreme operating conditions.

Surface mounted devices (SMD) are most often used for the implementation of the output-matching network capacitors and supply decoupling capacitors, while the inductors are often implemented into the laminate or LTCC (low temperature co-fired ceramic) substrate. Occasionally, dedicated silicon or GaAs technologies are used for the implementation of these passive functions.

Although CMOS transistors suffer from low breakdown voltages CMOS PAs are getting more attention nowadays, because they offer a higher level of integration. Special transistor circuit techniques [33] and new impedance matching circuit concepts [34] are developed that relax the breakdown voltage requirements of the devices.

#### 2.2.3 Duplexer

A duplexer consists of two band-pass filters to simultaneously connect the antenna to the Rx and Tx UMTS line-up. The frequency selectivity of the duplex filters provides the required isolation between the Rx and Tx line-up. Especially for small Rx-Tx band separation narrow pass-band filters with steep skirts are needed to meet the isolation requirements. In addition, the duplex filter protects the UMTS receiver from de-sensitizations by strong out-of-band interfering signals.

Important duplexer specifications:

- The insertion loss of duplexers has a strong impact on the transmitter power added efficiency and on the receiver sensitivity. The insertion loss of duplexers is large (typically 1.5–2 dB) compared to that of antenna switches (0.5–1 dB). Therefore, the latter are preferred in GSM/EDGE-mode.

- Power handling of duplex filters is important because of reliability. Especially surface acoustic wave (SAW) duplex filters are critical on power handling since, at high frequencies, their inter-digital metal finger structures are very narrow and thus vulnerable to electro-migration.

- Temperature drift in duplex filter frequency characteristic can be critical for duplex filters with a narrow pass-band and steep skirts. Especially Lithium Niobate SAW devices have a relatively large temperature coefficient. In some cases they need temperature compensation to fulfill attenuation specifications over the specified temperature range.

Since UMTS and LTE are expected to re-farm most of the cellular frequency bands, about 14 different Rx-Tx band combinations [35] have to be covered by various duplex filters. Nowadays two different mainstream technologies are available [36]: SAW (Surface Acoustic Wave) and BAW (Bulk Acoustic Wave). Basically, SAW is most suited for applications below 1.5 GHz because at higher frequencies their

finger structures become too small to handle power due to electro-migration. Moreover, these small finger structures cannot be produced accurately due to lithographic limitations. BAW is most suited above 1.5 GHz because at lower frequencies the piezo-electric layer becomes too thick for reliable production.

#### 2.2.4 Blocking Filter

The blocking filter provides frequency selectivity in order to protect the GSM/EDGE receiver from de-sensitizations by strong out-of-band interfering signals, similar to that of the duplex filter for the UMTS receiver. Therefore, these blocking filters must have a narrow pass-band and steep skirts.

- The insertion loss of blocking filters has a strong impact on the receiver sensitivity since the insertion loss (typically 1.5–2 dB) is significant compared to the noise figure of low noise amplifiers (LNA) (typically 2–3 dB) that are usually integrated in the TRx.

- Temperature drift of the blocking filter frequency characteristic can be critical for blocking filters, similar to that of duplex filters.

Usually blocking filters are implemented in SAW or BAW technology, similar to that of duplex filters.

#### 2.3 Fluctuations in Operating Conditions

Cellular phones operate in strongly varying environments. Fluctuations in the operating conditions have strong impacts on link quality, talk-time, and ruggedness requirements of a phone. The most important fluctuations in operating conditions are:

• Output power

The output power of a cellular phone varies between microwatts and a few watts in order to overcome the huge fluctuations in wave propagation, and thus to secure the link quality. When link budget is marginal, the base station requests for the phone to transmit at maximum power.

- Load impedance Fluctuations in power amplifier load impedance are caused by the narrow bandwidth of miniaturized high-Q antennas and by detuning of the antenna resonance frequency, due to fluctuating body-effects and changes in phone form-factor.

- Supply voltage

The power amplifier supply voltage varies due to charging and discharging of the battery.

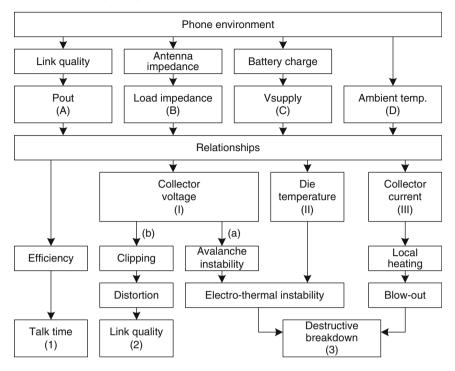

Fig. 2.1 The performance of a cellular phone RF front-end is affected by its fluctuating operating environment, which is visualized as a simplified chain of causes and effects

• Ambient temperature

The phone ambient temperature varies with changes in user and weather conditions.

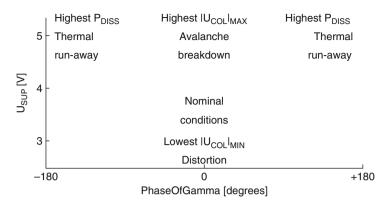

The impact of these fluctuating conditions on the performance of a cellular phone and its RF front-end is visualized in Fig. 2.1 as a chain of causes and effects. The output power (A), power transistor load impedance (B), supply voltage (C), and ambient temperature (D) determine the collector (or drain) voltage (I) and current (III), and in relation to those, the dissipated power, efficiency and die temperature (II), which, on their turn, affects talk-time (1), link quality (2), and breakdown behavior of the power amplifier (3).

The relationship between these quantities is briefly discussed below and is described mathematically in Section 2.4.

Talk-time

Usually, the power amplifier load-line is chosen for optimum efficiency at maximum output power and nominal supply voltage. Variations in output power, load impedance, and supply voltage have a strong impact on the efficiency of the PA. Since the PA consumes a relative large part of the total phone, large variations in efficiency cause a significant change in talk-time.

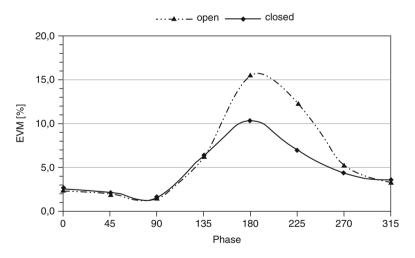

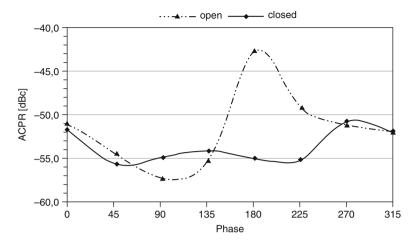

• Link quality

For transmission of EDGE and W-CDMA modulated signals using a nonconstant envelope, the power amplifier efficiency is optimized as a trade-off versus linearity that is predominantly determined by clipping. Clipping due to saturation of the power transistor deteriorates the quality of modulation, often defined as Error Vector Magnitude (EVM), and causes spectral re-growth that is often referred to as Adjacent Channel Power Ratio (ACPR). At high output power, variations in output power, load impedance, and supply voltage changes the level of clipping level. Under extremes, the channel capacity reduces strongly and even a call-drop may occur.

Breakdown

For a bipolar power transistor three different causes of break-down can be distinguished: avalanche break-down of the collector-base junction [37, 38], run-away due to electro-thermal instability [39], and interconnect blow-out due to local dissipation.

Avalanche instability and electro-thermal instability of the power transistor are strongly affected by the collector voltage and die temperature, which both varies due to fluctuations in output power, load impedance, supply voltage, and ambient temperature.

Blow-out is mainly caused by local heating of on-die interconnect or bondwires due to insufficient heat transfer to its surroundings and is directly related to the current flowing through the power transistor.

Under extremes excessively high collector voltages or large collector currents and high die temperatures may occur that may lead to electro-thermal instability and destructive breakdown of the power transistor. To avoid breakdown usually large design margins are taken.

#### 2.4 Impact of Variables

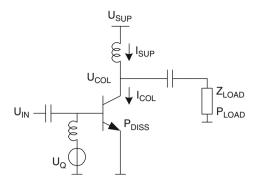

In this section we present a mathematical analysis on the behavior of a bipolar class-AB power amplifier transistor under fluctuating operating conditions. The collector current, collector voltage, die temperature and amplifier efficiency are expressed as functions of the collector load impedance, supply voltage and ambient temperature. To simplify the analysis, feedback, saturation, self-heating, and frequency dependencies are ignored (Fig. 2.2).

#### 2.4.1 Current Fluctuation

The exponential relationship between collector current  $I_{COL}$  and base-emitter voltage  $U_{BE}$  of a bipolar transistor is often expressed as

$$I_{COL} = I_o \cdot e^{\frac{U_O + A_{IN} \cdot \cos(\omega t)}{U_T}},$$

(2.1)

**Fig. 2.2** Circuit diagram of a class-AB power amplifier using a bipolar transistor

in which  $I_o$  is the saturation current of the transistor and  $U_T$  the thermal voltage. The base-emitter voltage consists of two terms: the DC bias voltage  $U_Q$ , and a sinusoidal signal of excitation with an amplitude  $A_{IN}$ . The exponential relationship can be approximated by a Taylor series and the magnitude of the harmonic components can be determined by applying a Fourier transformation [40]. This yields for the magnitude of the DC-term, and first, second, and third harmonic

$$I_{COL-DC} = I_o \cdot e^{\frac{U_o}{U_T}} \left\{ 1 + \frac{1}{4} \frac{A_{IN}^2}{U_T^2} + \frac{1}{64} \frac{A_{IN}^4}{U_T^4} + \dots \right\}$$

(2.2a)

$$I_{COL-1} = I_o \cdot e^{\frac{U_o}{U_T}} \left\{ \frac{A_{IN}}{U_T} + \frac{1}{8} \frac{A_{IN}^3}{U_T^3} + \dots \right\}$$

(2.2b)

$$I_{COL_2} = I_o \cdot e^{\frac{U_0}{U_T}} \left\{ \frac{1}{4} \frac{A_{IN}^2}{U_T^2} + \frac{1}{48} \frac{A_{IN}^4}{U_T^4} + \dots \right\}$$

(2.2c)

$$I_{COL_3} = I_o \cdot e^{\frac{U_o}{U_T}} \left\{ \frac{1}{24} \frac{A_{IN}^3}{U_T^3} + \frac{1}{384} \frac{A_{IN}^5}{U_T^5} + \dots \right\}.$$

(2.2d)

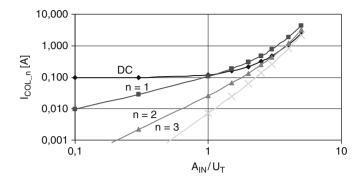

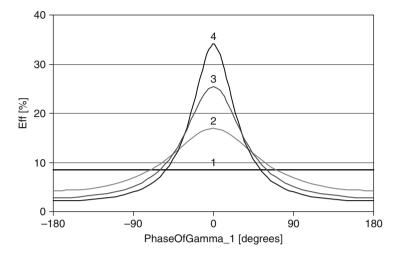

Due to the exponential transconductance of a bipolar transistor, the magnitudes of the harmonics increase more rapidly than that of the fundamental and the amplitude of the fundamental more rapidly than that of the DC component, when the input signal amplitude increases, which is illustrated in Fig. 2.3.

Usually, the bias voltage  $U_Q$  and signal amplitude  $A_{IN}$  are made temperature dependent to provide compensation for temperature dependencies in  $U_T$  and  $I_o$ . Hence, in this analysis temperature effects can be ignored.

In conclusion, according to (2.2a), (2.2b), (2.2c), and (2.2d) the DC and RF collector currents (of a non-saturated class-AB amplifier without feedback) are independent of the supply voltage and load impedance, but increase with increasing input signal amplitude. In Section 2.4.5, this conclusion will be discussed in a broader context.

**Fig. 2.3** Visualization of the harmonic collector currents  $I_{COL_n}$  as a function of the input signal  $A_{IN}$  normalized to the thermal voltage  $U_T$ .  $U_{BE} = 0.92$  V,  $U_T = 0.025$  V, and  $I_o = 1 \cdot e \cdot 17$  A/m<sup>2</sup>

#### 2.4.2 Voltage Fluctuation

In this section we derive the operating conditions at which the collector voltage is most extreme, because these extremes are relevant to avalanche break-down of the power transistor and distortion due to clipping.

The collector voltage can be expressed as the sum of vectors representing a DC-term and AC-terms

$$u_{COL}(t) = U_{SUP} + \sum \left( I_{COL_n} \cdot |Z_{LOAD_n}| \cdot \cos(n\omega \cdot t + \phi_{Z_{LOAD_n}}) \right).$$

(2.3)

The amplitudes of the harmonically related AC-terms are determined by the product of the current magnitude  $I_{COL_n}$ , as defined in (2.2a), (2.2b), (2.2c), and (2.2d), and the magnitude of the load impedance  $Z_{LOAD_n}$ . The phases of the load impedances  $\varphi_{ZLOAD_n}$  cause phase shifts of the harmonic frequency components.

Usually, a nominal load-line is chosen that provides an optimum trade-off between efficiency and linearity for a nominal supply voltage  $U_{SUP\_NOM}$  and a nominal maximum output power  $P_{LOAD\_NOM}$ . This nominal load-line  $R_{NOM}$  is often defined as

$$R_{NOM} = \frac{U_{SUP_NOM}^2}{2 \cdot P_{LOAD_NOM}}.$$

(2.4)

To include mismatch conditions [41], the collector load impedance  $Z_{LOAD_n}$  can now be expressed as a function of this nominal load-line  $R_{NOM}$  and the harmonic reflection coefficient  $\Gamma_n$  as

$$Z_{LOAD\_n} = R_{NOM} \cdot \frac{1 + \Gamma_n}{1 - \Gamma_n}.$$

(2.5)

The harmonic reflection coefficient  $\Gamma_n$  can be written in polar form as

$$\Gamma_n = |\Gamma_n| \cdot (\cos \theta_n + j \sin \theta_n). \tag{2.6}$$

The magnitude of the collector load impedance, at each harmonic, can now be rewritten as

$$|Z_{LOAD\_n}| = R_{NOM} \cdot \sqrt{\frac{1 + |\Gamma_n|^2 + 2|\Gamma_n|\cos\theta_n}{1 + |\Gamma_n|^2 - 2|\Gamma_n|\cos\theta_n}},$$

(2.7)

whereas the phases of the harmonic collector load impedances can be expressed as

$$\phi_{Z_{LOAD_n}} = \arctan\left(\frac{2|\Gamma_n|\sin(\theta_n)}{1-|\Gamma_n|^2}\right).$$

(2.8)

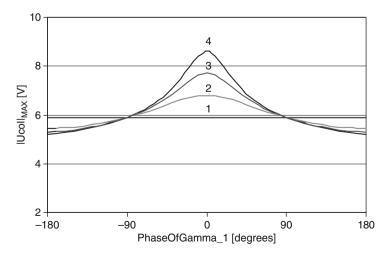

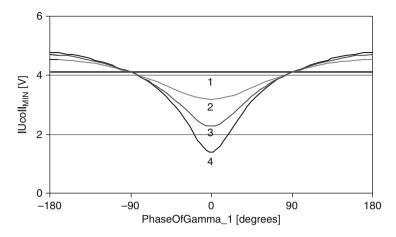

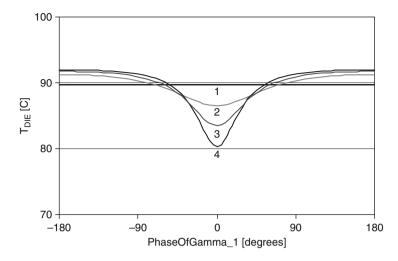

A maximum in the magnitude of the collector voltage  $|U_{COL}|_{MAX}$  occurs when, simultaneously, all harmonic frequency components add constructively, and the magnitude of each harmonic load impedance is maximum. The harmonic frequency components add constructively when, for all n, holds true

$$\cos(n\omega \cdot t + \phi_{Z_{LOAD}}) = +1. \tag{2.9}$$

Similarly, a minimum in the magnitude of the collector voltage  $|U_{COL}|_{MIN}$  occurs, 180° shifted in time, when holds true

$$\cos(n\omega \cdot t + \phi_{Z_{LOAD_n}}) = -1. \tag{2.10}$$

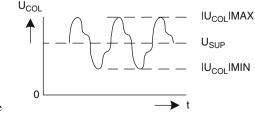

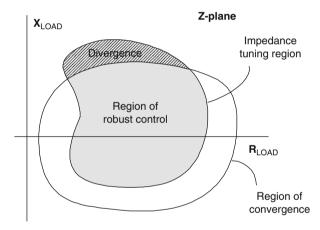

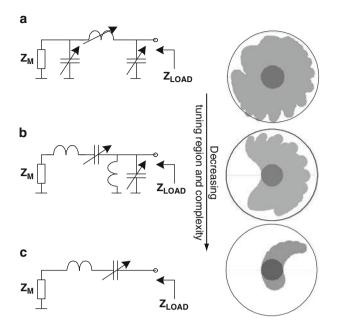

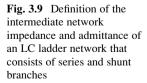

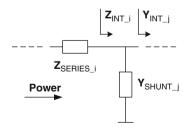

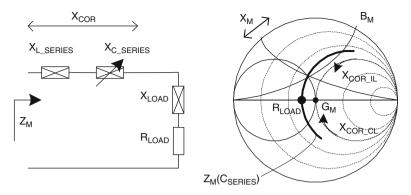

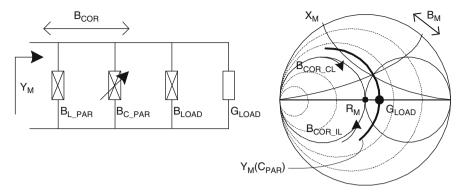

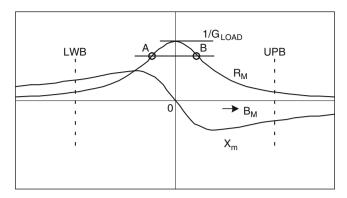

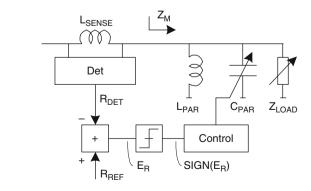

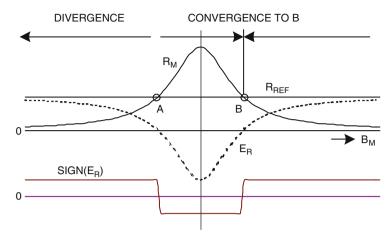

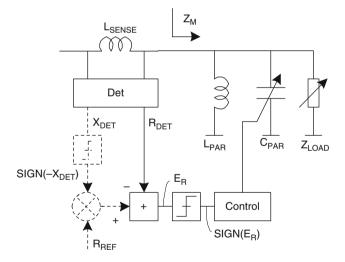

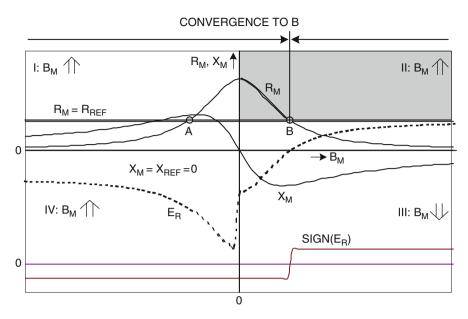

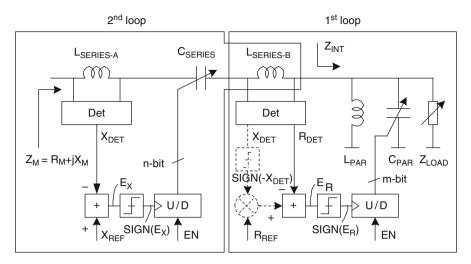

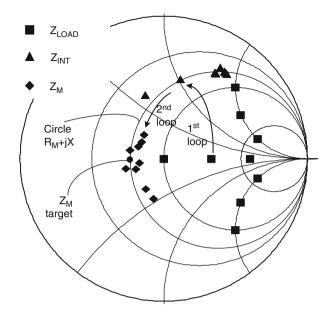

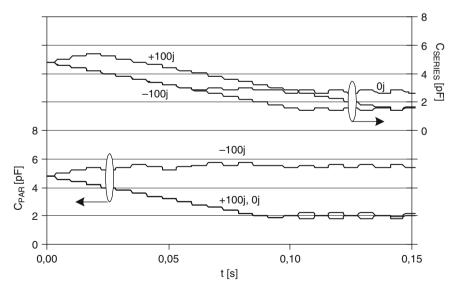

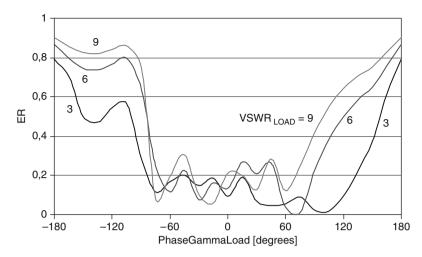

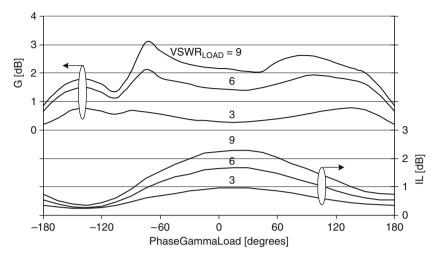

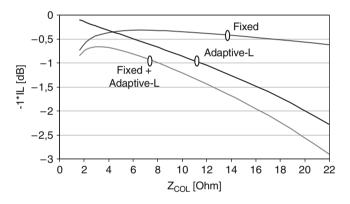

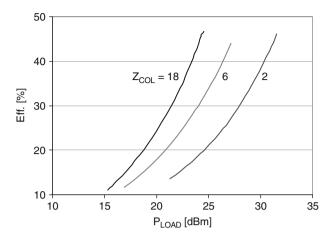

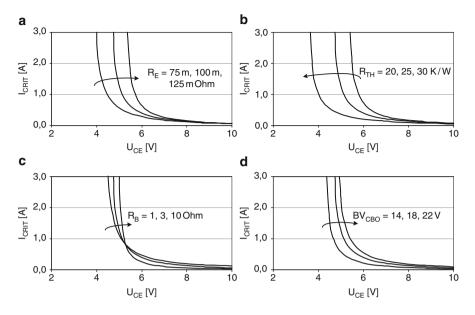

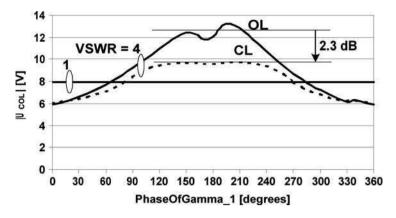

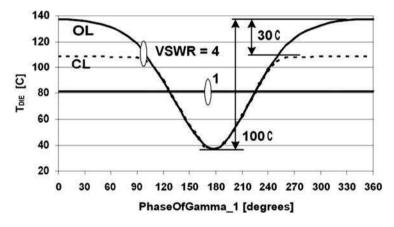

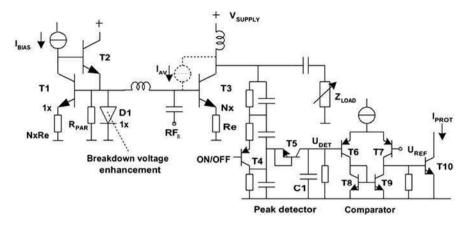

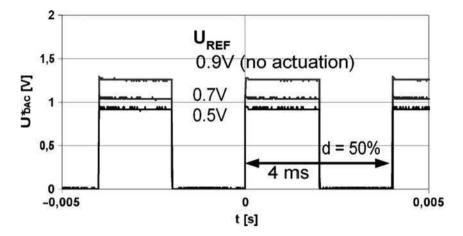

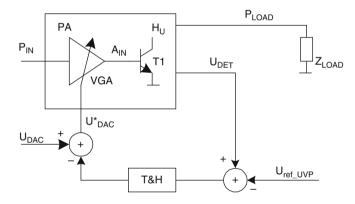

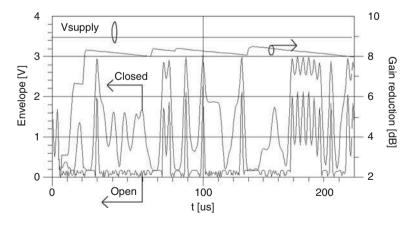

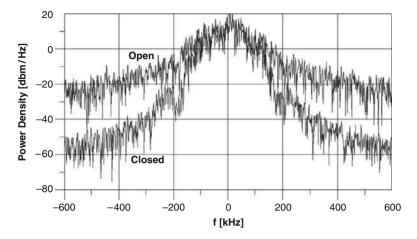

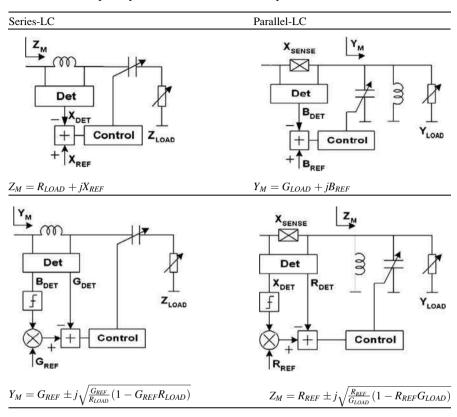

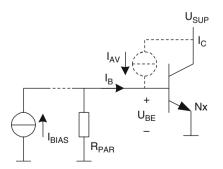

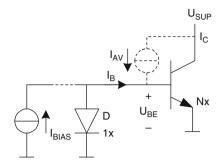

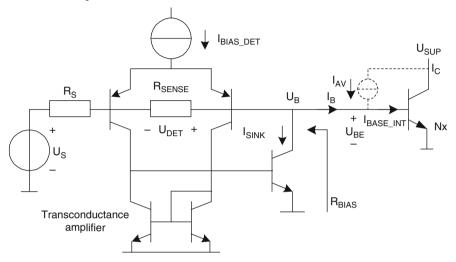

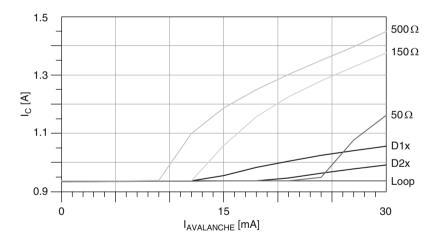

This maximum and minimum in collector voltage magnitude are visualized in Fig. 2.4.