Cristina Silvano Marcello Lajolo Gianluca Palermo *Editors*

# Low Power Networks-on-Chip

Low Power Networks-on-Chip

Cristina Silvano • Marcello Lajolo Gianluca Palermo Editors

# Low Power Networks-on-Chip

*Editors* Cristina Silvano Politecnico di Milano Dip. Elettronica e Informazione (DEI) Via Ponzio 34/5 20133 Milano Italy silvano@elet.polimi.it

Marcello Lajolo NEC Laboratories America, Inc. Independence Way 4 08540 Princeton New Jersey USA lajolo@nec-labs.com Gianluca Palermo Politecnico di Milano Dip. Elettronica e Informazione (DEI) Via Ponzio 34/5 20133 Milano Italy gpalermo@elet.polimi.it

ISBN 978-1-4419-6910-1 e-ISBN 978-1-4419-6911-8 DOI 10.1007/978-1-4419-6911-8 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2010935810

© Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

"Ma sopra tutte le invenzioni stupende, qual eminenza fu quella di colui che s'immaginò di trovar modo di comunicare i suoi più reconditi pensieri a qualsivoglia altra persona, benché distante per lunghissimo intervallo di luogo e di tempo? Parlare con quelli che son nell'Indie, parlare a quelli che non sono ancora nati né saranno se non di qua a mille e diecimila anni? E con qual facilità? Con i vari accozzamenti di venti caratteruzzi sopra una carta."

Galileo Galilei, Dialogo sopra i due massimi sistemi del mondo, Tolemaico e Copernicano, Firenze, 1632

"But surpassing all stupendous inventions, what sublimity of mind was his who dreamed of finding means to communicate his deepest thoughts to any other person, though distant by mighty intervals of place and time! Of talking with those who are in India; of speaking to those who are not yet born and will not be born for a thousand or ten thousand years; and with what facility, by the different arrangements of twenty characters upon a page."

Galileo Galilei, Dialogue concerning the two chief world systems, Ptolemaic & Copernican, Florence, 1632

# Preface

Given the increasing complexity of multiprocessor system-on-chip (MPSoC) designs, the current trends in on-chip communication architectures are converging towards the network-on-chip (NoC). The NoC-based design approach represents a high bandwidth and low energy solution. Using the NoC-based design approach has several other advantages, such as scalability, reliability, IP reusability and separation of IP design from on-chip communication design and interfacing. NoC design represents a new paradigm to design MPSoC, shifting the design methodologies from computation-based to communication-based.

Given these premises, during the last decade, we assisted an increasing research effort on NoC architectures and related design methodologies. Many key design challenges of NoC have been investigated in the past years. These challenges have recently been classified by Marculescu et al. in three main categories: the design of the communication infrastructure, the selection of the communication paradigm and the application mapping optimization. First, the problem of designing the communication infrastructure consists in turn of the following problems: network topology synthesis, the selection of the channel width, the buffer sizing problem and the NoC floorplanning problem. Second, the selection of the communication paradigm includes the routing problem and the choice of switching techniques (store-andforward, cut-through, wormhole, etc.) to be used. Third, the application mapping optimization problem consists in turn of the IP mapping and the task scheduling problems of an application onto the NoC platform. All these optimisation techniques should take into consideration several metrics of interest to be traded off. These metrics are mainly performance, energy, quality of service, reliability and security.

In this scenario, even some semiconductor industries have started to propose some NoC-based designs. Among them, we can cite the Aetheral NoC from NXP-Philips, the STNoC from STMicroelectronics and the 80-core NoC from Intel. Several industrial design flows supporting NoC design have also been proposed, such as the CHAIN works tool suite by Silistix, the NoCexplorer and NoCcompiler frameworks by Arteris and the iNOCs tools from iNoCs. The interest demonstrated by several industries and EDA providers contributed to confirm NoC as a feasible and energy-efficient approach to interconnect a scalable number of IP cores on a single die. Although many scientific books and journal papers have recently been published, many challenging topics related to NoC research are still open. The story behind this book began more than a year ago, when we started thinking with Charles Glaser from Springer about a book focusing on low-power NoC, as power and energy issues still represent one of the limiting factors in integrating multi- and many-cores on a single chip. Power-aware design techniques at several abstraction levels represent the enabling keys for an energy-efficient design of on-chip interconnection network. Starting from this idea, the book tries to answer to the necessity of a single textbook on the topic of low-power NoC, covering power- and energy-aware design techniques from several perspectives and abstraction levels. To this purpose, the present book tries to put together several outstanding contributions in several areas of low-power NoC design.

The book chapters are organized in three parts. In Part I, several power-aware design techniques on NoC are discussed from the low-level perspective. These low-level NoC design techniques address the following topics: hybrid circuit/packet switched networks, run-time power-gating techniques, adaptive voltage control techniques for NoC links and asynchronous communication. In Part II, several system-level power-aware design techniques are presented dealing with application-specific routing algorithms, adaptive data compression and design techniques for latency constrained and power optimized NoCs. In Part III of the book, some emerging technologies related to low-power NoC, namely 3D stacking, CMOS nanophotonics and RF-interconnect are discussed to envision their applicability to meet the requirements imposed by future NoC architectures.

Entering Part I on low-level design techniques, Chap. 1 introduces some issues and challenges for future NoCs with demands for high bandwidth and low energy. Starting from the analysis of some state-of-the-art approaches to design NoC architectures, the chapter presents details of how coupling packet-switched arbitration with circuit-switched data transfer can achieve energy savings and improve network efficiency by reducing arbitration overhead and increasing overall utilisation of network resources. In this hybrid network, packet-switched arbitration is used to reserve future circuit-switched channels for the data transfer, thus eliminating the performance bottlenecks associated with pure circuit-switched networks, while maintaining their power advantage. Furthermore, the chapter discusses how proximity-based data streaming can increase network throughput and improve energy efficiency. Finally, some NoC measurements and design trade offs are analysed on 45 nm CMOS technology from an industrial research perspective.

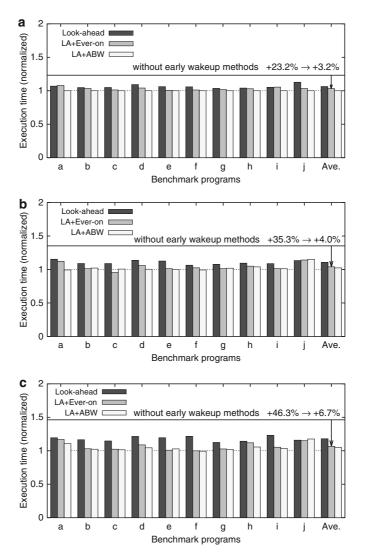

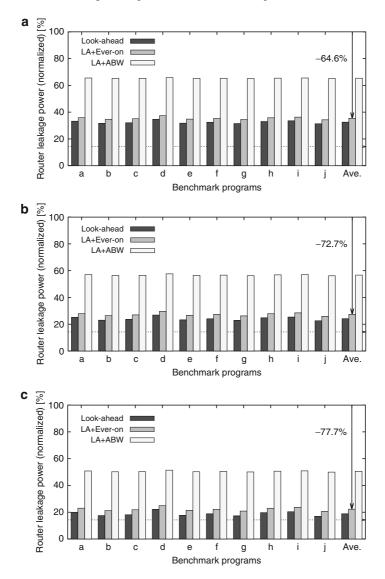

Chapter 2 surveys several power gating techniques to reduce the leakage power of on-chip routers. Leakage power is responsible for a considerable portion of the active power in recent process technologies. Then, the chapter introduces a run-time fine-grained power gating router, in which power supply to each router component (e.g. virtual-channel buffer, crossbar's multiplexer, and output latch) can be individually controlled in response to the applied workload. To mitigate the impact of wake-up latency of each power domain on application performance, the chapter introduces and discusses three wake-up control methods. Finally, the fine-grained power gating router with 35 micro power domains and the early wake-up methods are designed with a commercial 65 nm process and evaluated in terms of the area overhead, application performance and leakage power reduction.

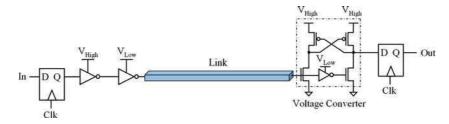

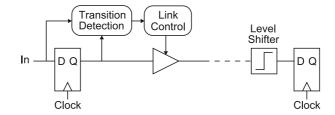

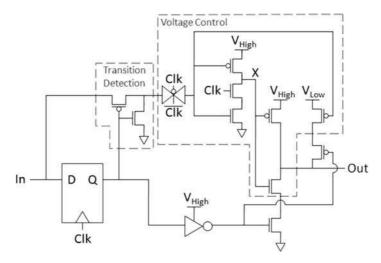

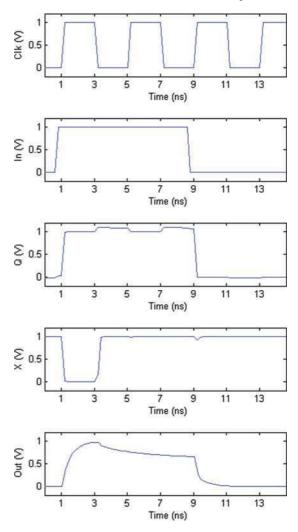

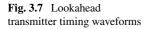

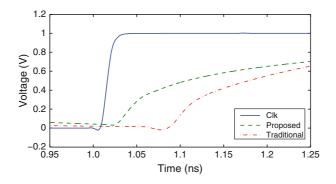

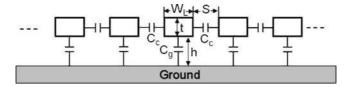

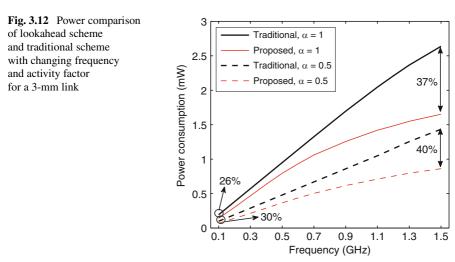

Chapter 3 surveys the state of the art in energy-efficient communication link design for NoCs. After reviewing techniques at the datalink and physical abstraction layers, the chapter introduces a lookahead-based transition-aware adaptive voltage control method for achieving improved energy efficiency at moderate cost in performance and reliability. Then, performance and limitations of the proposed method are evaluated and future prospects in energy-efficient link design are projected.

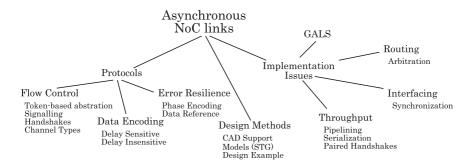

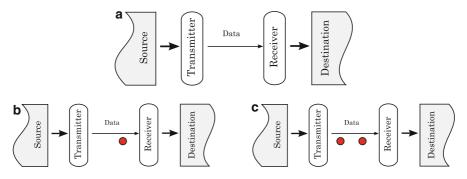

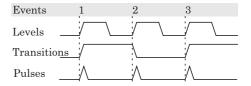

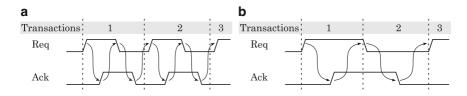

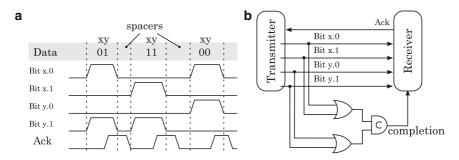

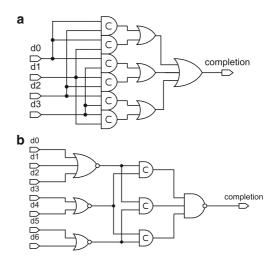

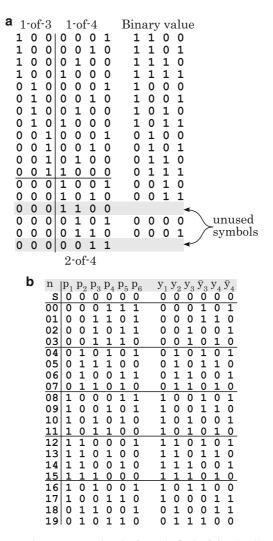

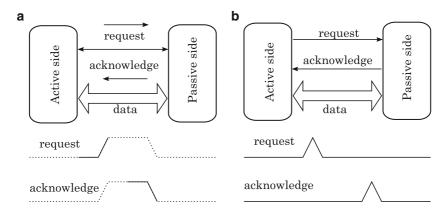

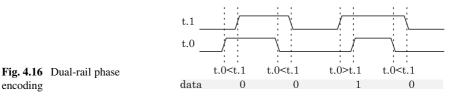

Chapter 4 provides an overview of the various asynchronous techniques that are used at the link layer in NoCs, including signalling schemes, data encoding and synchronization solutions. These asynchronous techniques are discussed with a view of comparison in terms of area, power and performance. The fundamental issues of the formation of data tokens based on the principles of data validity, acknowledgement, delay-insensitivity, timing assumptions and soft-error tolerance are considered. The chapter also covers some of the aspects related to combining asynchronous communication links to form parts of the entire network architecture, which involves asynchronous logic for arbitration and routing hardware. To this end, the chapter also presents basic techniques for building small-scale controllers using the formal models of Petri nets and signal transition Graphs.

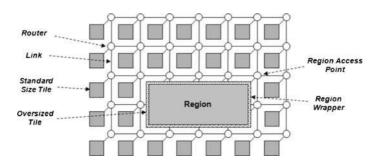

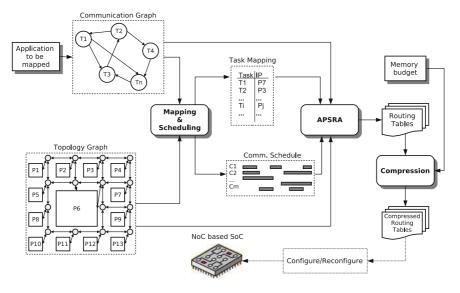

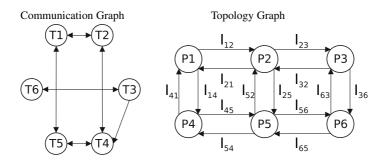

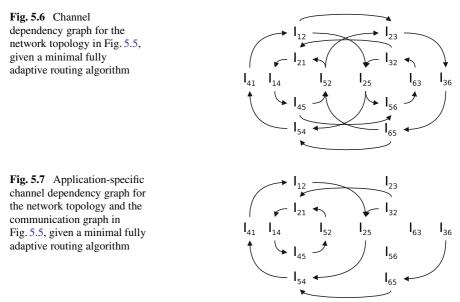

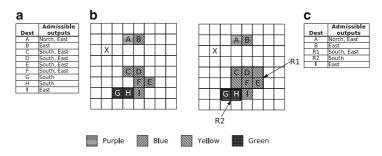

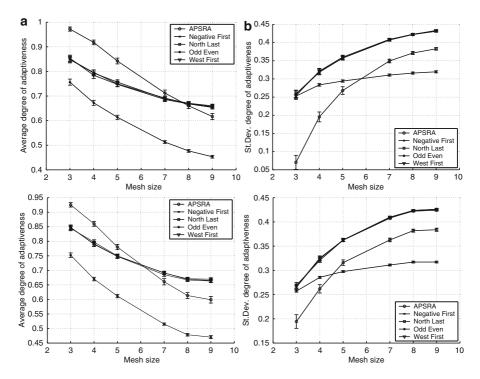

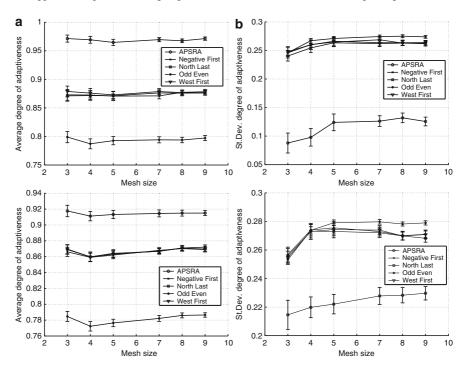

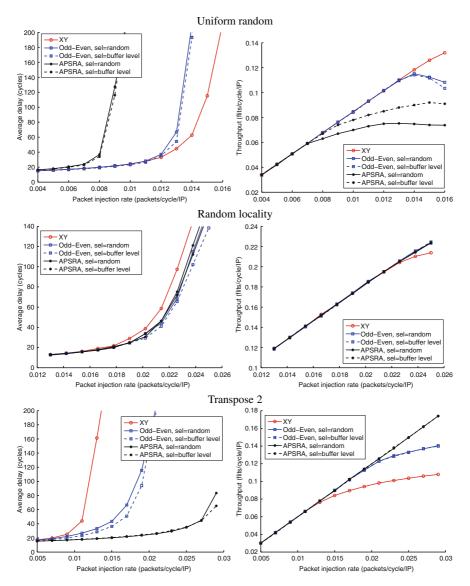

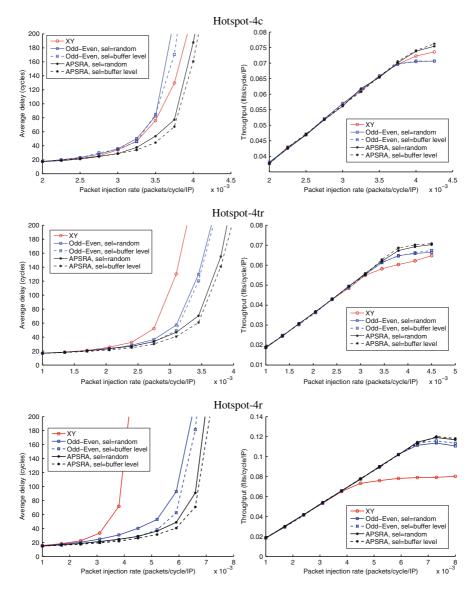

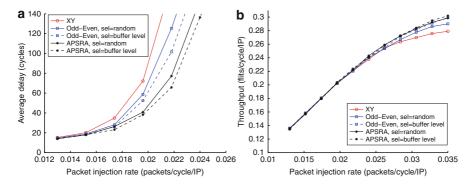

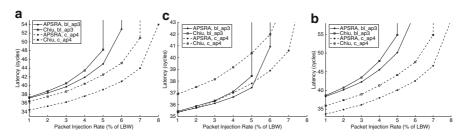

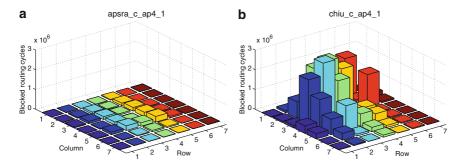

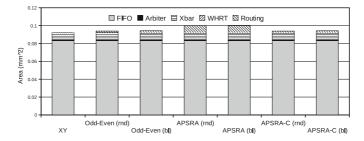

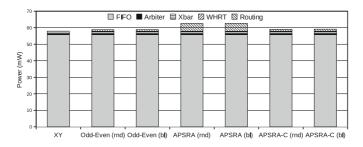

Entering Part II on system-level design techniques, Chap. 5 describes how the routing algorithm can be optimized in NoC platforms. Routing algorithm has a major effect on the performance (packet latency and throughput) as well as power consumption of NoC. A methodology to develop efficient and deadlock free routing algorithms which are specialized for an application or a set of concurrent applications is presented. The methodology, called application specific routing algorithms (APSRA), exploits the application-specific information regarding pairs of cores which communicate and other pairs which never communicate in the NoC platform. This information is used to maximize the adaptivity of the routing algorithm without compromising the important property of deadlock freedom. The chapter also presents an extensive comparison between the routing algorithms generated using APSRA methodology with general purpose deadlock-free routing algorithms. The simulation-based evaluations are performed using both synthetic traffic as well as traffic from real applications. The comparison embraces several performance indices such as degree of adaptiveness, average delay, throughput, power dissipation and energy consumption. In spite of an adverse impact on router architecture, the chapter proves that the higher adaptivity of APSRA leads to significant improvements in both routing performance and energy consumption.

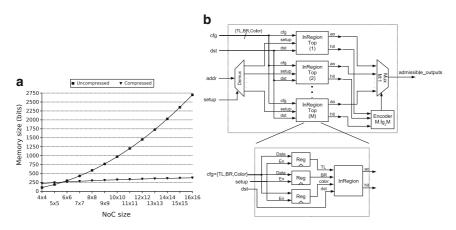

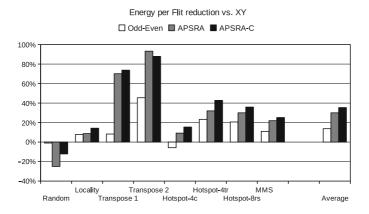

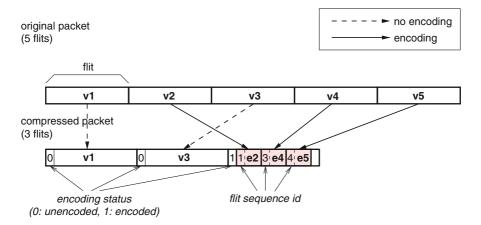

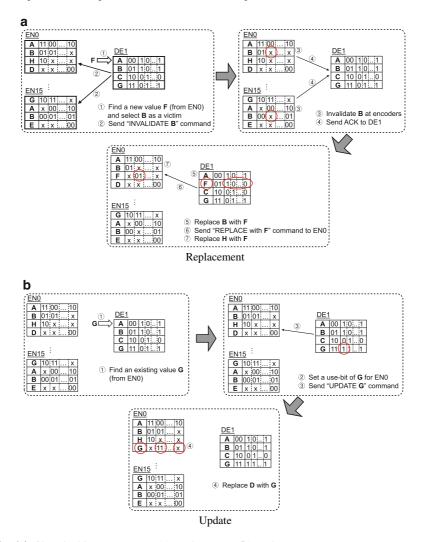

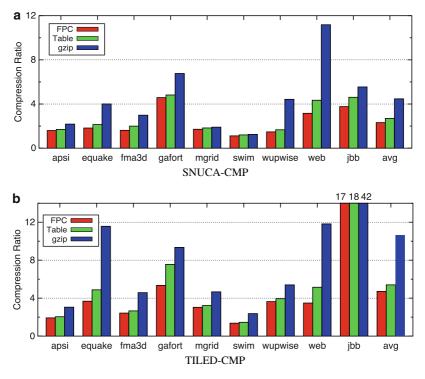

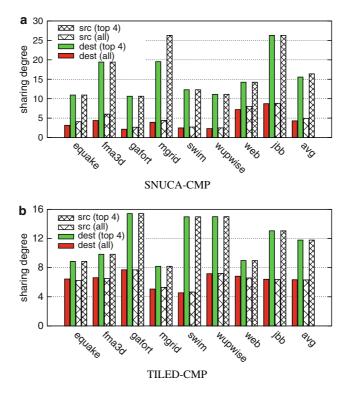

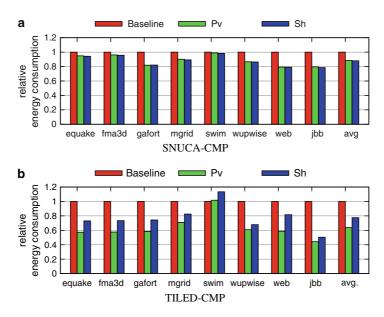

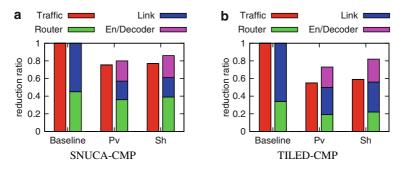

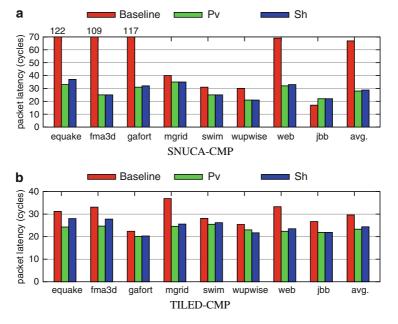

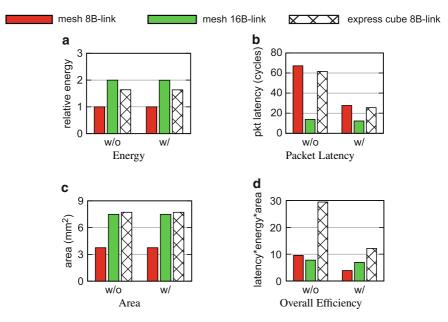

Chapter 6 presents a method to exploit a table-based data compression technique, relying on value patterns in cache traffic. Compressing a large packet into a small one saves power consumption by reducing required operations in network components and decreases contention by increasing the effective bandwidth of shared resources. The main challenges are providing a scalable implementation of tables and minimizing the latency overhead of compression. We propose a shared table scheme that needs one encoding and one decoding table for each processing element, and a management protocol that does not require in-order delivery. This scheme eliminates table size dependence on a network size, which realizes scalability and reduces overhead cost of table for compression. The chapter also presents some simulation results obtained by using the proposed compression method for 8-core and 16-core tiled designs. The experimental results are discussed in terms of packet latency and network power consumption.

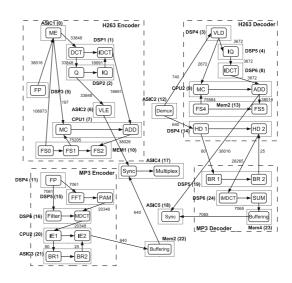

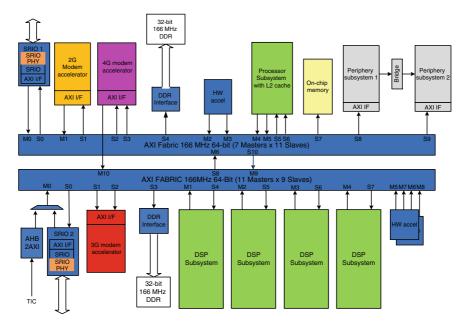

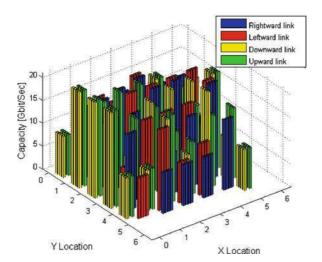

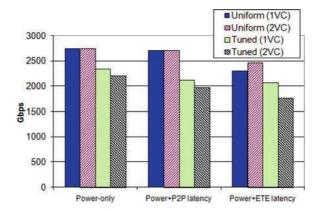

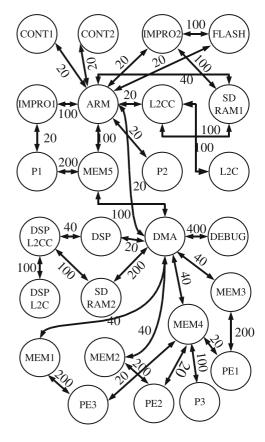

Chapter 7 describes the design process of a Network on-Chip for a high-end commercial system on-chip (SoC) application. Several design choices are discussed in the chapter focusing on the power optimization of the NoC while achieving the required performance. The chapter describes the NoC design steps including module mapping and allocation of customized capacities to links. Unlike previous studies, in which point-to-point, per-flow timing constraints were used, the chapter demonstrates the importance of using the application end-to-end traversal latency requirements during the optimization process. To compare several design alternatives, the chapter reports the synthesis results of an NoC design that meets the actual throughput and timing requirements of a commercial 4G SoC.

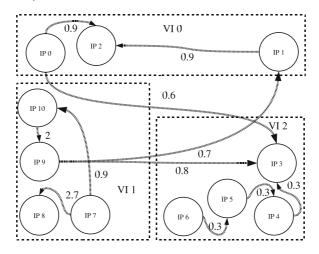

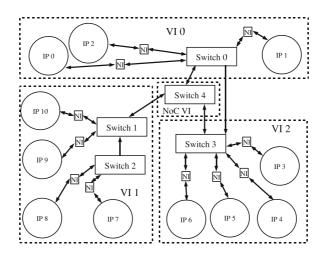

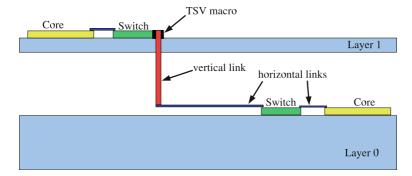

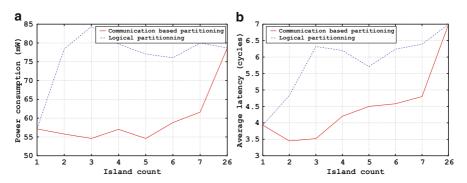

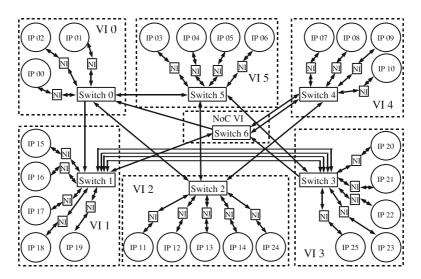

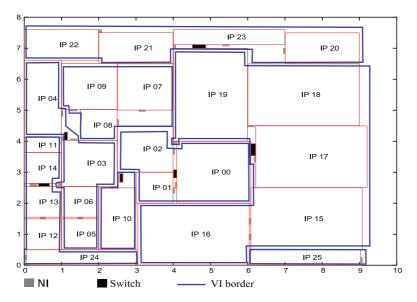

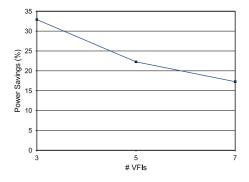

Entering Part III on future and emerging technologies, Chap. 8 addresses the problem of 2D and 3D SoC designs where the cores are grouped into voltage islands. To reduce the leakage power consumption, an island containing cores that are not used in an application can be shutdown, while the other islands can still be operational. When one or more of the islands are shutdown, the interconnect should allow the communication between islands that are operational. For this, the NoC has to be designed efficiently to allow shutdown of voltage islands, thereby reducing the leakage power consumption. The chapter presents methods to design NoC topologies that provide such a support for both 2D and 3D technologies. The chapter outlines how the concept of voltage islands needs to be considered during the topology synthesis phase itself. The chapter also analyses the benefits of migrating to 3D stacked chips for realistic applications that have multiple voltage islands.

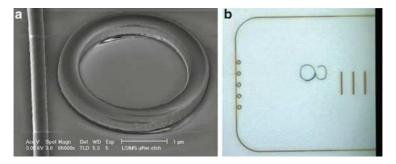

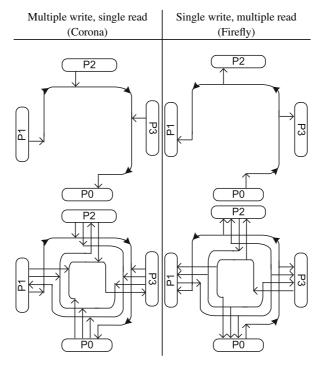

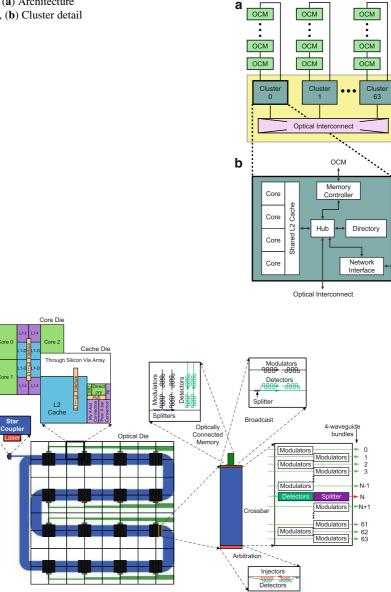

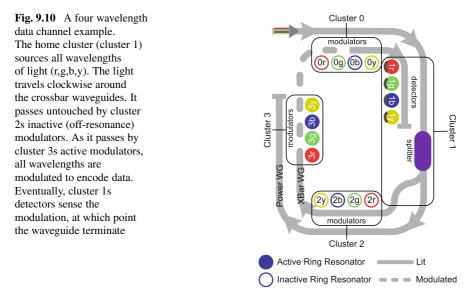

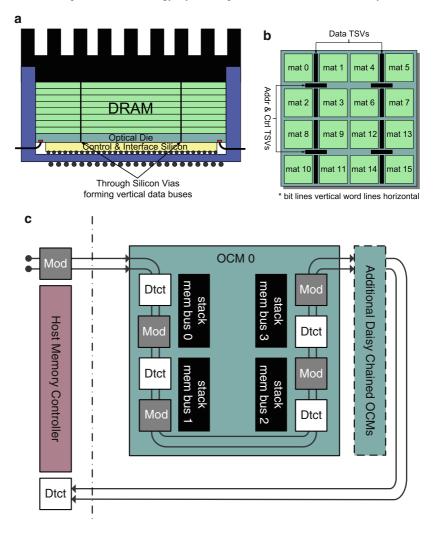

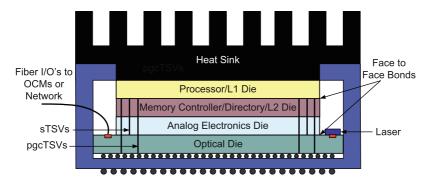

Chapter 9 introduces the emerging CMOS nanophotonic technologies representing a compelling alternative to traditional all-electronic NoCs. This is because of nanophotonic NoCs can provide both higher throughput and lower power consumption than all-electrical NoCs. The chapter introduces CMOS nanophotonic technology and considers its use in photonic chip-wide networks enabling many-core microprocessors with greatly enhanced performance and flexibility while consuming less power than their electrical counterparts. The chapter also provides, as a case study, a design that takes advantage of CMOS nanophotonics to achieve ten-teraop performance in a 256-core 3D chip stack, using optically connected main memory, very high memory bandwidth, cache coherence across all cores, no bisection bandwidth limits on communication and cross-chip communication at very low latency with cache-line granularity.

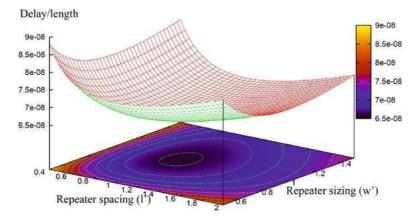

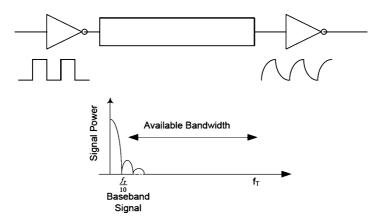

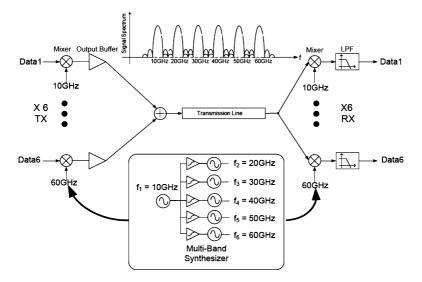

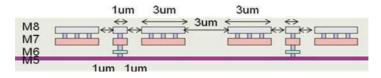

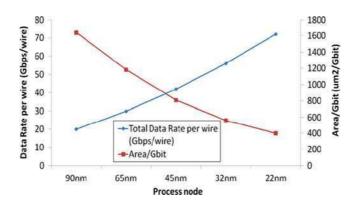

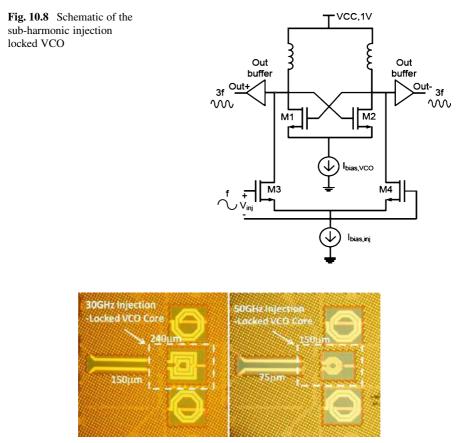

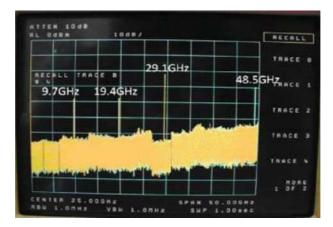

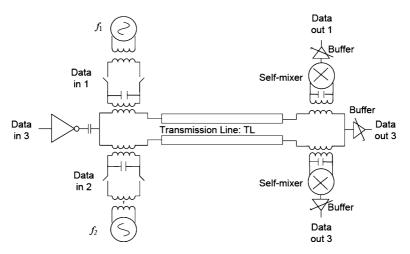

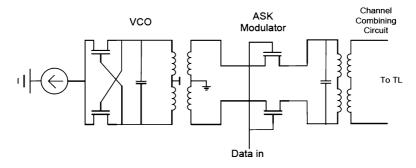

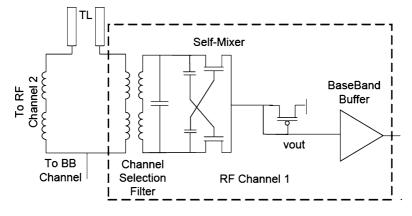

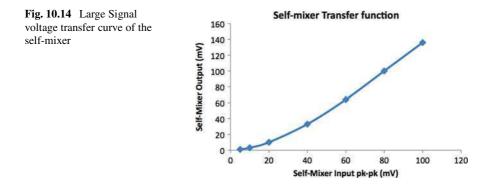

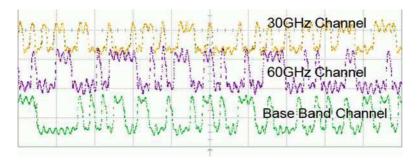

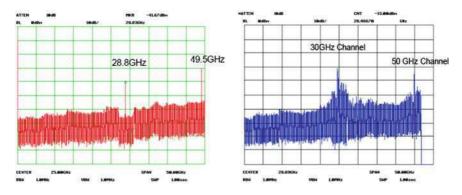

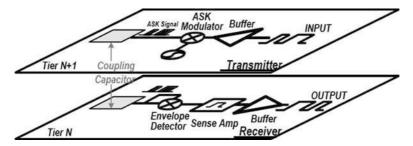

Chapter 10 explores the use of multi-band RF-interconnect for future Networkon-Chip. RF-interconnect can communicate simultaneously through multiple frequency bands with low-power signal transmission and reconfigurable bandwidth. At the same time, the chapter investigates the CMOS mixed-signal circuit implementation challenges for improving the RF-I signalling integrity and efficiency. Furthermore, the chapter proposes a micro-architectural framework that can be used to facilitate the exploration of scalable low-power NoC architectures based on physical planning and prototyping.

Due to the large number of topics discussed in the book and their heterogeneity, the background on low-power NoC is discussed chapter by chapter with a separate reference set for each chapter. This choice also contributed to make each chapter self-contained.

Overall, we believe that the chapters cover a set of definitely important and timely issues impacting the present and future research on low-power NoC. We sincerely hope that the book could become a solid reference in the next years. In our vision, the authors put a big effort in clearly presenting their technical contribution outlining the potential impact and some case studies. We would like to have the opportunity to specially thank all the authors who contributed to the book. A special thanks to Charles Glaser from Springer for encouraging us from the beginning of this book and Amanda Davis from Springer for her continuous support in reviewing the materials.

Milano, Italy Princeton, NJ, USA Milano, Italy April 2010 Cristina Silvano Marcello Lajolo Gianluca Palermo The Editors

# **About the Editors**

Cristina Silvano received the M.S. degree in electronic engineering from Politecnico di Milano, Milano, Italy, in 1987 and the Ph.D. degree in computer engineering from the University of Brescia, Brescia, Italy, in 1999. From 1987 to 1996, she was a Senior Design Engineer with the R&D Labs, Groupe Bull, Pregnana, Italy. From 2000 to 2002, she was an Assistant Professor with the Department of Computer Science, University of Milan, Milano. She is currently an Associate Professor (with tenure) in computer engineering with the Dipartimento di Elettronica e Informazione, Politecnico di Milano. She has published one scientific international book and more than 70 papers in international journals and conference proceedings, and she is the holder of several international patents. Her primary research interests are in the area of computer architectures and computer-aided design of digital systems, with particular emphasis on design space exploration and low-power design techniques for multiprocessor systems-onchip. She participated in several national and international research projects, some of them in collaboration with STMicrolectronics. She is currently the European Coordinator of the project FP7-2PARMA-248716 on "PARallel PAradigms and Run-time MAnagement techniques for Many-core Architectures" (Jan 2010 to Dec 2012). She is also the European Coordinator of the on-going project FP7-MULTICUBE-216693 on "Multi-objective design space exploration of multiprocessor SoC architectures for embedded multimedia applications" (Jan 2008 to June 2010).

Marcello Lajolo received his Master and Ph.D. degrees in electrical engineering, both from Politecnico di Torino (Italy) in 1995 and 1999, respectively. He then joined the Computer & Communication Research Laboratories (CCRL; now NEC Laboratories America) in Princeton, NJ, where he led various projects in the areas of on-chip communication design and advanced embedded architectures. He also collaborates with Advanced Learning and Research Institute (ALaRI) in Lugano, Switzerland, where he has been teaching a course on networks on chip since 2002. He has served or is serving as a program committee member for major conferences in electronic design automation and embedded system design like DAC, DATE, ASP-DAC, and ISCAS. He has given full-day tutorials at conferences like ICCAD, ASP-DAC, ICCD and others in the area of embedded system design. He is a Senior Member of the IEEE. His primary research topics are related to Networks on Chip, Hardware/Software Codesign Low Power Design, Computer Architectures, High Level Synthesis of Digital Integrated Circuits and System-on-Chip Testing.

Gianluca Palermo received the M.S. degree in electronic engineering and the Ph.D. degree in computer engineering from Politecnico di Milano, Milano, Italy, in 2002 and 2006, respectively. Previously, he was a Consultant Engineer with the Low Power Design Group, Advanced System Technology, STMicroelectronics, where he worked on network-on-chip, and also a Research Assistant with the Advanced Learning and Research Institute, University of Lugano, Lugano, Switzerland. He is currently an Assistant Professor in the Dipartimento di Elettronica e Informazione, Politecnico di Milano. His research interests include design methodologies and architectures for embedded systems, focusing on low-power design, on-chip multiprocessors, and network-on-chip. He participated in several national and international research projects.

# Contents

#### Part I Low-Level Design Techniques

| 1   | Hybrid Circuit/Packet Switched Network for Energy         Efficient on-Chip Interconnections       3         Mark A. Anders, Himanshu Kaul, Ram K. Krishnamurthy,       3         and Shekhar Y. Borkar       3 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | Run-Time Power-Gating Techniques for Low-PowerOn-Chip Networks21Hiroki Matsutani, Michihiro Koibuchi, Hiroshi Nakamura,and Hideharu Amano                                                                       |

| 3   | Adaptive Voltage Control for Energy-Efficient NoC Links45Paul Ampadu, Bo Fu, David Wolpert, and Qiaoyan Yu                                                                                                      |

| 4   | Asynchronous Communications for NoCs                                                                                                                                                                            |

| Par | t II System-Level Design Techniques                                                                                                                                                                             |

| 5   | Application-Specific Routing Algorithms for Low PowerNetwork on Chip DesignMaurizio Palesi, Rickard Holsmark, Shashi Kumar,and Vincenzo Catania                                                                 |

|     |                                                                                                                                                                                                                 |

| 6   | Adaptive Data Compression for Low-Power On-ChipNetworks151Yuho Jin, Ki Hwan Yum, and Eun Jung Kim                                                                                                               |

### Part III Future and Emerging Technologies

| 8   | Design and Analysis of NoCs for Low-Power<br>2D and 3D SoCs                    | 199 |

|-----|--------------------------------------------------------------------------------|-----|

|     | Ciprian Seiculescu, Srinivasan Murali, Luca Benini,<br>and Giovanni De Micheli |     |

| 9   | CMOS Nanophotonics: Technology, System Implications,                           |     |

|     | and a CMP Case Study                                                           | 223 |

|     | Jung Ho Ahn, Raymond G. Beausoleil, Nathan Binkert,                            |     |

|     | Al Davis, Marco Fiorentino, Norman P. Jouppi,                                  |     |

|     | Moray McLaren, Matteo Monchiero, Naveen Muralimanohar,                         |     |

|     | Robert Schreiber, and Dana Vantrease                                           |     |

| 10  | RF-Interconnect for Future Network-On-Chip                                     | 255 |

|     | Sai-Wang Tam, Eran Socher, Mau-Chung Frank Chang,                              |     |

|     | Jason Cong, and Glenn D. Reinman                                               |     |

| Ind | ex                                                                             | 281 |

# Contributors

**Jung Ho Ahn** Seoul National University, Sumon, Gyeonggi-do, Korea, gajh@snu.ac.kr

Hideharu Amano Keio University, 3-14-1, Hiyoshi, Kohoku-ku, Yokohama, Japan 223-8522, hunga@am.ics.keio.ac.jp

**Paul Ampadu** University of Rochester, Rochester, NY 14627, USA, ampadu@ece.rochester.edu

Mark A. Anders Intel Corporation, Hillsboro, OR, USA, mark.a.anders@intel.com

**Raymond G. Beausoleil** Hewlett-Packard Labs, Palo Alto, CA, USA, ray.beausoleil@hp.com

Luca Benini DEIS, Univerity of Bologna, Bologna, Italy, lbenini@deis.unibo.it

**Rudy Beraha** Qualcomm Corp. Research and Development, San Diego, California 92121, USA, rberaha@qualcomm.com

Nathan Binkert Hewlett-Packard Labs, Palo Alto, CA, USA, binkert@hp.com

Shekhar Y. Borkar Intel Corporation, Hillsboro, OR, USA, shekhar.y.borkar@intel.com

**Vincenzo Catania** Dipartimento di Ingegneria Informatica e delle Telecomunicazioni, University of Catania, Italy, vcatania@diit.unict.it

**Mau-Chung Frank Chang** Electrical Engineering Department, University of California, Los Angeles, Engineering IV Building, CA 90095, Los Angeles, USA, mfchang@ee.ucla.edu

**Israel Cidon** Electrical Engineering Department, Technion - Israel Institute of Technology, Haifa 32000, Israel, cidon@ee.technion.ac.il

**Jason Cong** Computer Science Department, University of California, Los Angeles, 4731J, Boelter Hall, Los Angeles, CA 90095, cong@cs.ucla.edu

**Giovanni De Micheli** LSI, EPFL, Lausanne, Switzerland, giovanni.demicheli@epfl.ch

#### Al Davis Hewlett-Packard Labs, Palo Alto, CA, USA, ald@hp.com

Marco Fiorentino Hewlett-Packard Labs, Palo Alto, CA, USA, marco.fiorentino@hp.com

**Bo Fu** University of Rochester, Rochester, NY 14627, USA, bofu@ece.rochester.edu

**Stanislavs Golubcovs** Asynchronous Systems Laboratory, School of EECE, Newcastle University, Newcastle upon Tyne, United Kingdom, stanislavs.golubcovs@ncl.ac.uk

**Rickard Holsmark** Department of Electronics and Computer Engineering, Jönköping University, Jönköping, Sweden, Rickard.Holsmark@jth.hj.se

**Yuho Jin** Department of Electrical Engineering, University of Southern California, 3740 McClintock Ave., Los Angeles, CA 90089, USA, yujin@usc.edu

**Norman P. Jouppi** Hewlett-Packard Labs, Palo Alto, CA, USA, norm.jouppi@hp.com

Himanshu Kaul Intel Corporation, Hillsboro, OR, USA, himanshu.kaul@intel.com

**Eun Jung Kim** Department of Computer Science and Engineering, Texas A&M University, College Station, TX 77843-3112, USA ejkim@cse.tamu.edu

**Michihiro Koibuchi** National Institute of Informatics, 2-1-2, Hitotsubashi, Chiyoda-ku, Tokyo, Japan 101-8430, koibuchi@nii.ac.jp

**Avinoam Kolodny** Electrical Engineering Department, Technion - Israel Institute of Technology, Haifa 32000, Israel, kolodny@ee.technion.ac.il

**Ram K. Krishnamurthy** Intel Corporation, Hillsboro, OR, USA, ram.krishnamurthy@intel.com

**Shashi Kumar** Department of Electronics and Computer Engineering, Jönköping University, Jönköping, Sweden, Shashi.Kumar@jth.hj.se

**Hiroki Matsutani** The University of Tokyo, 7-3-1 Hongo, Bunkyo-ku, Tokyo, Japan 113-8656, matsutani@hal.ipc.i.u-tokyo.ac.jp

Moray McLaren Hewlett-Packard Labs, Palo Alto, Bristol, UK, moray.mclaren@hp.com

**Matteo Monchiero** Hewlett-Packard Labs, Palo Alto, CA, USA, matteo.monchiero@hp.com

Srinivasan Murali LSI, EPFL and iNoCs, Lausanne, Switzerland, murali@inocs.com

Naveen Muralimanohar Hewlett-Packard Labs, Palo Alto, CA, USA, naveen.muralimanohar@hp.com

#### Contributors

**Hiroshi Nakamura** The University of Tokyo, 7-3-1 Hongo, Bunkyo-ku, Tokyo, Japan 113-8656, nakamura@hal.ipc.i.u-tokyo.ac.jp

**Maurizio Palesi** Dipartimento di Ingegneria Informatica e delle Telecomunicazioni, University of Catania, Italy, mpalesi@diit.unict.it

**Glenn D Reinman** Computer Science Department, University of California, Los Angeles, 4731-D Boelter Hall, Los Angeles, CA 90095, reinman@cs.ucla.edu

**Robert Schreiber** Hewlett-Packard Labs, Palo Alto, CA, USA, rob.schreiber@hp.com

**Ciprian Seiculescu** LSI, EPFL, Lausanne, Switzerland, ciprian.seiculescu@epfl.ch

**Eran Socher** School of Electrical Engineering - Physical Electronics, Tel Aviv University, 234 Wolfson EE Lab Bldg, Tel Aviv University, Ramat Aviv, Tel Aviv 69978, Israel, socher@eng.tau.ac.il

**Sai-Wang Tam** Electrical Engineering Department, University of California, Los Angeles, Engineering IV Building, Los Angeles, CA 90095, USA, roccotam@ee.ucla.edu

Dana Vantrease Hewlett-Packard Labs, Palo Alto, CA, USA, vantrease@hp.com

**Isask'har Walter** Electrical Engineering Department, Technion - Israel Institute of Technology, Haifa 32000, Israel, zigi@tx.technion.ac.il

David Wolpert University of Rochester, Rochester, NY 14627, USA, ampadu@ece.rochester.edu

Alex Yakovlev Asynchronous Systems Laboratory, School of EECE, Newcastle University, Newcastle upon Tyne, United Kingdom, Alex.Yakovlev@ncl.ac.uk

Qiaoyan Yu University of Rochester, Rochester, NY 14627, USA, ampadu@ece.rochester.edu

**Ki Hwan Yum** Department of Computer Science and Engineering, Texas A&M University, College Station, TX 77843-3112, USA, yum@cse.tamu.edu

# Part I Low-Level Design Techniques

# Chapter 1 Hybrid Circuit/Packet Switched Network for Energy Efficient on-Chip Interconnections

Mark A. Anders, Himanshu Kaul, Ram K. Krishnamurthy, and Shekhar Y. Borkar

Abstract Network on-Chip (NoC) is an interconnect fabric to connect sub-system blocks on a chip. The NoC should provide high bandwidth and low latency, should consume low energy, and should be compact. However, all these requirements are at odds and require tradeoffs at all levels. In this chapter, we discuss issues and challenges for future NoCs with demands for high bandwidth and low energy. Next, we present details of how coupling packet-switched arbitration with circuit-switched data transfer can achieve these goals. In this hybrid network, packet-switched arbitration is used to reserve future circuit-switched channels for the data transfer, eliminating the performance bottlenecks associated with pure circuit-switched networks while maintaining their power advantage. Furthermore, proximity-based data streaming increases network throughput and improves energy efficiency. Measurements of this NoC in 45 nm CMOS are described to analyze design tradeoffs.

#### 1.1 Network on-Chip: Past, Present, and the Future

Network on-Chip (NoC) has evolved from the good old supercomputer days where computers in a cabinet, as well as multiple cabinets, were connected together to form a complete parallel computer system. These networks were primitive indeed, such as simple Ethernet at times, nevertheless sufficient to provide the necessary bandwidth with acceptable latencies. That was then, and now, with technology scaling over several generations, you can afford to have several computers themselves on a single die, connected together by a network forming a homogeneous many-core parallel computer system. To take it even further, the integration capacity is now so vast that it is possible to integrate diverse functional blocks on a chip, to be connected by a communication network, to form a heterogeneous system, what we call a system on-chip or SoC. And the network that connects these functional blocks together is the backbone of such a system. In this chapter, we discuss the state of the art in this

M.A. Anders (S)

Intel Corporation, Hillsboro, OR, USA e-mail: mark.a.anders@intel.com field, the issues and challenges that we will face in the future, and some of the prominent work addressing these issues. We also propose a hybrid packet/circuit-switched network that combines network advantages, higher resource utilization of packet-switched networks, and low power consumption of circuit-switched networks, to improve the energy-efficiency. The energy-efficiency advantage and design trade-offs will be quantified with silicon measurements of an  $8 \times 8$  mesh NoC in 45 nm CMOS.

#### 1.1.1 State of the Art in NoCs

Evolution of the NoC occurred over the last 3 decades, from early days of single chip microcontrollers incorporating several simple functional blocks, to today's sophisticated SoCs integrating diverse functional blocks on a chip. The early NoCs were good enough for the purpose, and as the bandwidth demand increased, they morphed into even sophisticated networks, with higher order topologies implemented with complex switches. Let us examine the evolution, comparing and contrasting their benefits as they evolved.

#### 1.1.1.1 Buses

A bus is the simplest NoC used in the early days of microcontrollers, to connect a tiny processor core to other peripherals, such as memory, timers, counters, and serial controllers. The bus was typically narrow, of the order of 8 to 16 bits wide, spanning the entire chip, connecting almost all the agents together. Such a long bus seems very slow due to large RC delays associated with a long bus, but the chip frequency was limited by the transistor performance, not the bus. The most prominent feature of the bus is its simplicity, needing a small transistor budget. On one hand, bus utilization is limited because it is shared, arbitrated by all the agents to transfer data. On the other hand, such a shared bus also provides the benefit of broadcast and multicast.

#### 1.1.1.2 Rings

When transistors became faster, and the bus RC delay started to dominate the operating frequency, the obvious solution was to use repeaters in the bus to improve the delay, ultimately emerging into pipelined buses, where every repeater stage of the bus is clocked. The result is a pipelined bus, with repeated bus segments, with the clocked repeater stage at the agent itself. The result is a ring, if the two far ends are connected together [1]. The advantage of a ring is that it offers higher frequency of operation, but with potentially increased latency of a number of clocks in each hop, with average node to node latency of half the number of hops. A ring is good enough for a small number of agents; however, as the number of agents grows, the latency increases linearly.

#### 1.1.1.3 Meshes

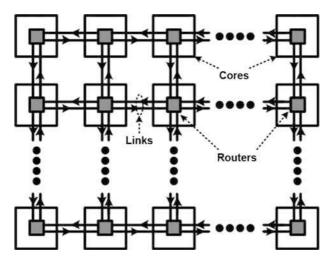

The latency limitation of rings resulted in a higher dimensional network such as a mesh or a torus [2]. A mesh too is a segmented bus in two dimensions, with switch at each agent, but with added complexity to route data across dimensions such as from X to Y. The advantage of a mesh network is that the average latency grows slowly (square root) with the number of agents, but adds more complexity into network protocols and implementation logic, and if not careful then could create hazardous conditions such as dead-locks. Such a network can be virtualized too, with virtual channels over physical links to further improve utilization [3].

#### 1.1.2 Issues and Challenges for the Future

As the technology continues to scale providing abundance of transistors for integration of diverse functional blocks, how will the NoCs keep up? We will now look into the challenges of NoCs in the future.

#### **1.1.2.1** Power and Energy

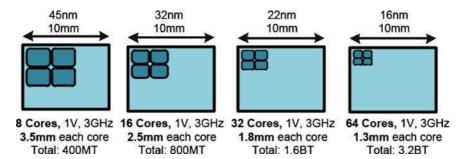

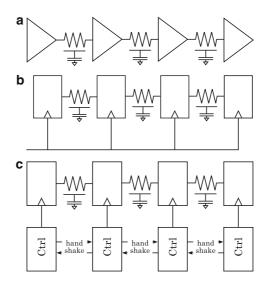

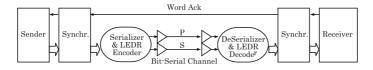

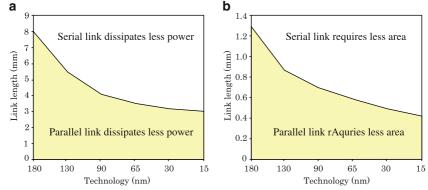

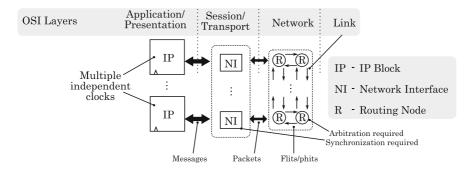

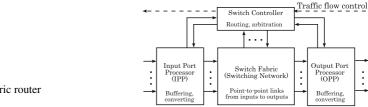

Consider an SoC on 45 nm technology, with eight agents connected on the die as shown in Fig. 1.1. Successive technology generation will double the integration capacity following Moore's Law, and expect billions of transistors, with almost 64 agents by 15 nm technology, providing terascale (Tera-ops) level performance. If the agents are connected by an  $8 \times 8$  mesh network, then the wire segments in the mesh will be of the order of 1 mm in size.

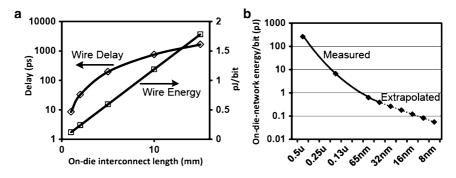

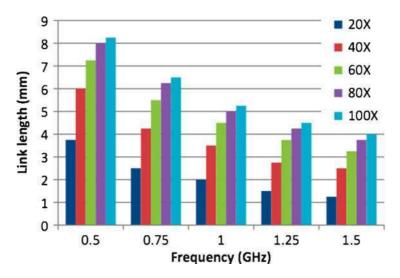

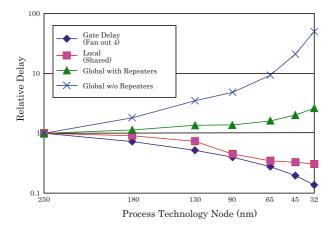

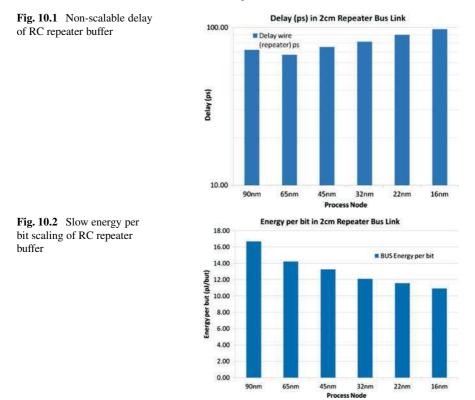

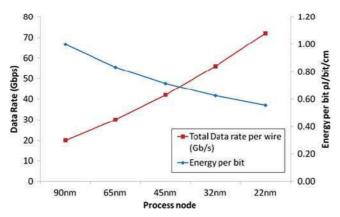

Note that as technology scales, the number of agents on the die double, and if each agent carries a switch for a mesh network, then the energy dissipated in the switches increases proportionally. The number of wires doubles too, but the length of the wire reduces. Figure 1.2a shows estimated delay and energy of a bus, and

Fig. 1.1 Future integration capacity for SoCs

Fig. 1.2 On-die interconnect delay and energy with respect to (a) length and (b) technology

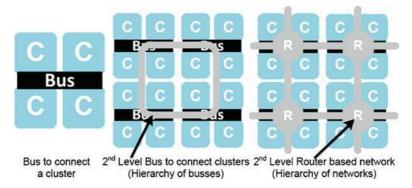

Fig. 1.3 Hierarchical, heterogeneous NoC

Fig. 1.2b shows energy expended in the switch. Using these estimates, and assuming that the Terascale SoC accesses one Tera-operand (32 bit), traversing 10 hops on an average, then the power consumption of the network alone would be too high.

#### 1.1.2.2 Heterogeneity

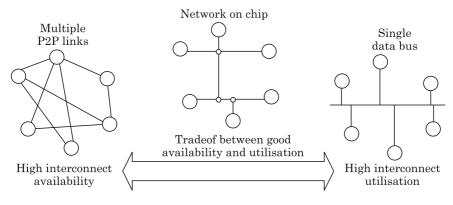

Clearly, a mesh network as a homogenous NoC is not optimum. For short distances, such as adjacent agents, a bus is a much better solution because energy and delay both can be low. Moreover, buses can be designed for low voltage swings to reduce the energy further. As the wire length increases, approaching delay close to the latency in a switch, then it is more appropriate to incorporate traditional packet switched mesh.

New approaches for a NoC are needed, as shown in Fig. 1.3. Agents in close proximity could be interconnected into clusters with traditional buses which are energy efficient for data movement over short distances. The clusters could be connected together with wide (high bandwidth) low-swing (low energy) buses, or they could be connected with packet or circuit switched networks depending on the

distance. Hence, the NoC could be hierarchical and heterogeneous, a radical departure from the traditional approach for NoC [4].

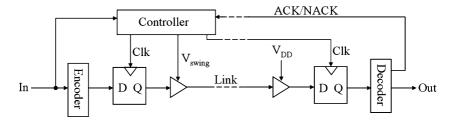

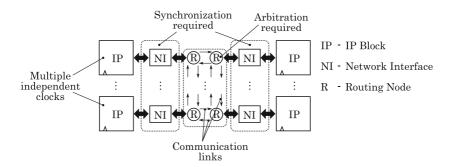

#### 1.2 Proposed Hybrid Packet/Circuit Switched NoC

As integration densities continue to increase in a power-limited environment, multicore processors provide increased performance vs. power efficiency through parallel processing at reduced voltages and frequencies. Innovations in interconnect networks for on-die communication between cores are key to enabling scalable performance as the number of cores increases [5-8]. By combining network topology and architecture advantages with efficient circuit implementations, more efficient communication can be achieved. For multi-core networks, packet-switched 2D meshes provide efficient interconnect utilization, low latencies, and high throughputs, but suffer from low energy efficiency due to data storage during routing [9,10]. Circuit-switched data transfer achieves both high bandwidth and energy efficiency by eliminating intra-route data storage [11–13]. It offers a dedicated channel during data transmission without the need for intermediate buffering or arbitration. However, by avoiding buffering and arbitration, the dedicated channel resources must be reserved prior to data transmission, possibly preventing other more optimal data transmissions from occurring. Unlike prescheduled source-directed routing schemes [2, 14], distributed routing schemes are not limited to predefined traffic patterns or applications, but determine packet routes and priorities for the reservation of resources based on incomplete real-time information. Therefore, in order to overcome challenges of resource allocation and distributed control, efficient circuits are needed that can approach throughputs of packet-switched networks while maintaining energy savings of a circuit-switched network.

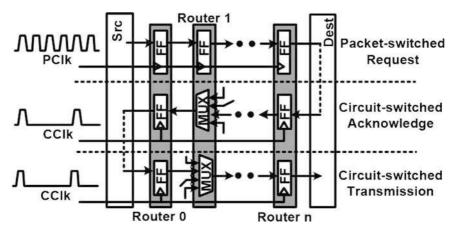

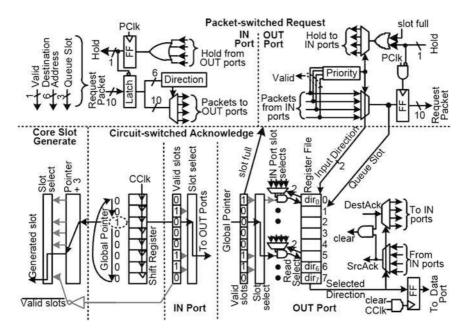

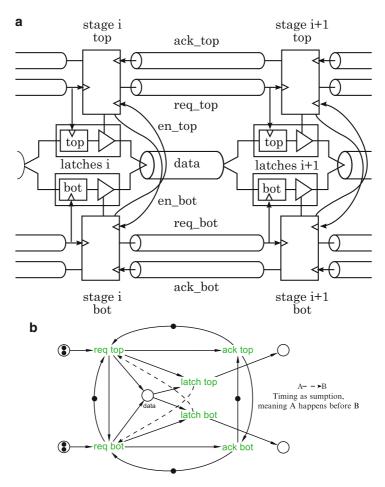

#### 1.2.1 Circuit-Switched Data with Packet-Switched Arbitration NoC

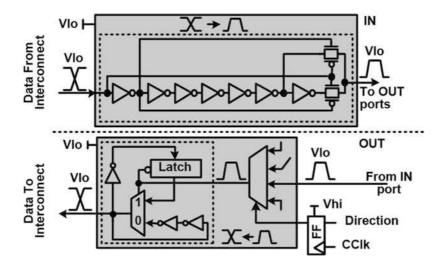

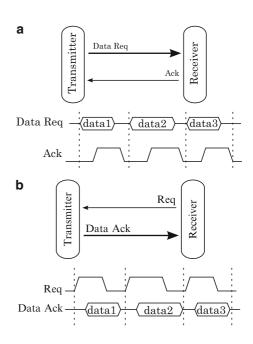

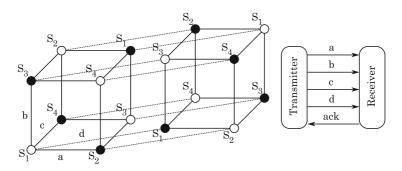

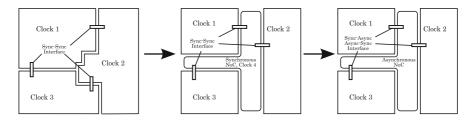

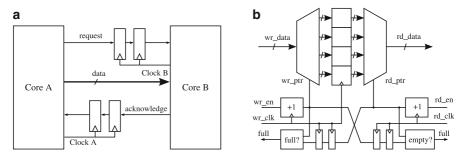

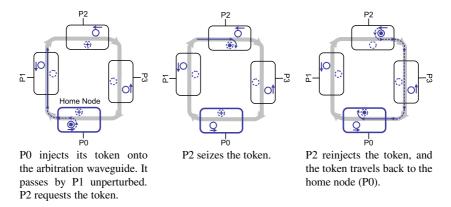

A circuit-switched 2D mesh network with packet-switched arbitration is composed of a packet-switched request address network alongside a circuit-switched acknowledge and data network (Fig. 1.4). This heterogeneous network allows delaying channel allocation for improved resource utilization, since small packets reserve channels before data transfer. However, since the data transfer uses circuit-switched paths without intermediate data storage, energy savings are also maintained. Furthermore, efficient circuits improve the overall network efficiency by reducing arbitration overhead and increasing overall utilization of network resources.

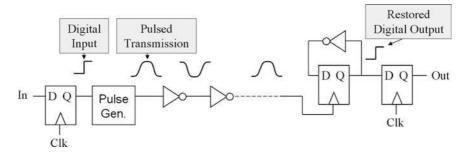

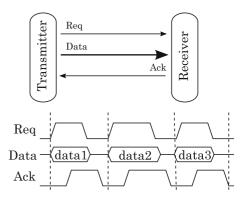

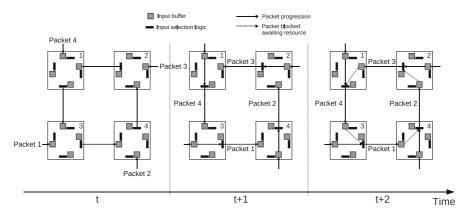

A data transmission using this hybrid network is composed of three separate phases (Fig. 1.5). During the setup phase for a circuit-switched data transmission, request packets containing the destination address are routed using the packet-

Fig. 1.4 Circuit-switched 2D mesh organization

Fig. 1.5 Circuit-switched pipeline and clocking

switched network. As the request packet passes each router and interconnect segment, the corresponding circuit-switched data channel for that segment is allocated for the future circuit-switched data transmission. When the request packet reaches its destination, a complete channel or circuit has been allocated. This channel has a latching or storage element only at the destination, with only multiplexers and repeaters along the way. Acknowledge signals indicate that the channel is ready for the data transfer, thus completing the setup phase. When the channel is ready, the source router drives the data onto its output, where it propagates to the destination without interruption by state elements. Following the reception of data at the destination, the channel is deallocated at the end of the cycle.

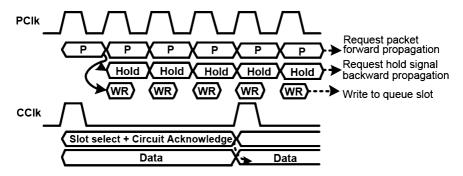

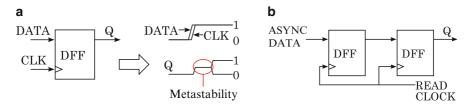

Compared to purely packet-based networks, energy is reduced by not storing data between the source and destination. Also, since only a single header packet is transmitted to allocate each channel without multiple subsequent data flits, the traffic on the packet-switched network is also reduced. During this allocation phase, packets only hold resources at their current router while storing their routing direction for future data transfer. In contrast, a purely circuit-switched network would hold resources between the source router and its current arbitration location even when blocked by other traffic. Because circuit-switched resource allocation is a distributed optimization without global control, efficient circuits such as pipelining and queue slots can further improve overall energy efficiency by increasing utilization of the wide circuit-switched data buses. Pipelining of the three routing phases improves the data throughput. Different clocks are used to synchronize the request packet-switched and data circuit-switched portions of the network (Fig. 1.5). Since each request packet travels only between neighboring cores of each cycle, it can operate with a higher frequency clock (PClk) than the circuit-switched portion (CClk), where data may travel across the whole network of each cycle. During circuit-switched data transmissions, acknowledges for future transmissions are sent (Fig. 1.6). Also, request packets are simultaneously creating new channels by storing the routing direction for future data transmissions. This pipelining removes the request and acknowledge phases from the critical path, improving circuit-switched throughput by  $3 \times$ .

In order to further improve resource utilization with distributed control, queue slots added to each router port store multiple request paths. This provides several potential paths for the circuit-switched network to choose from during the acknowledge phase. With this increase in available data transfer paths, more optimal non-interfering simultaneous data transfers occur, improving total throughput and resource utilization.

Fig. 1.6 Network timing diagram

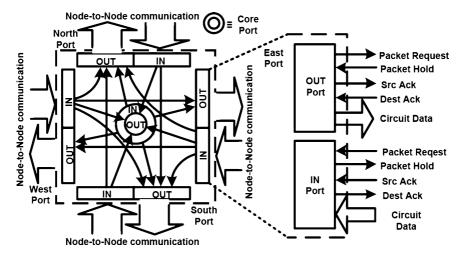

#### 1.2.2 Circuit Innovations for Circuit/Packet Switched Network Arbitration

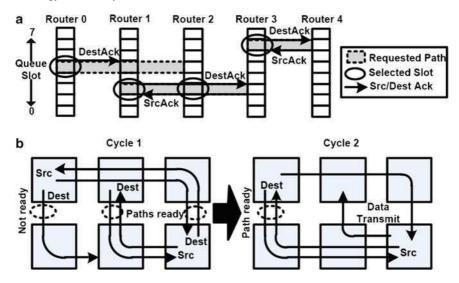

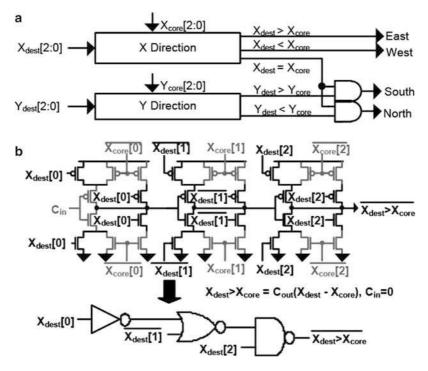

Each router within the network is divided into five separate ports: north, south, east, west, and core (Fig. 1.7). Each of these ports is further divided into IN and OUT ports, for receiving and transmitting data, respectively. All ports within a router are fully connected as a crossbar. In order to avoid deadlocks, the 2D mesh uses x-first, y-second routing, and unused paths are removed from within the router. Request packets for initial arbitration are sent between neighboring routers with packet hold signals providing flow control. Bidirectional acknowledge signals, from source (*SrcAck*) and destination (*DestAck*), indicate that a circuit-switched path is ready for data transfer during the next *CClk* cycle, completing arbitration. Finally circuit-switched data is routed from source to destination.

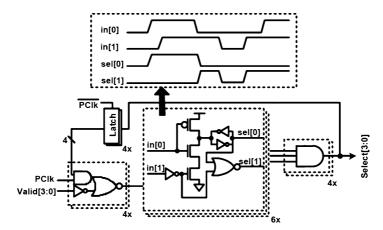

As each request packet propagates from one router to the next, its routing direction is stored in a queue slot. During a *CClk* cycle, each router port independently selects one of its queue slots, based on a rotating priority (Fig. 1.8a). The direction previously stored in that queue slot is used to route source and destination acknowledge signals. Arrival of both acknowledges at any router along the path indicates that the complete path is ready for data transmission in the next cycle (Fig. 1.8b). Paths that are not ready must wait for a future *CClk* cycle, while ready paths free their resources following data transmission. The request packet circuits route packets containing destination addresses to determine the routing direction and corresponding OUT port. Round-robin priority circuits select one of the valid packets at each OUT port and send *Hold* signals to the unselected IN ports. As each request

Fig. 1.7 Circuit-switched network router organization

Fig. 1.8 (a) Slot selection and (b) path selection and data transmission

Fig. 1.9 Arbitration and slot generation circuits

packet is transmitted, the routing direction is written to the queue slot entry within a 2b register file, creating request paths from router to router. The *Hold* signal is also asserted when the requested queue slot is full or a *Hold* signal arrives from the following router, preventing that request packet's IN port from continuing. The *Hold* signal to the previous router is delayed by one cycle using a flip-flop, reducing the *PClk* cycle time by one interconnect traversal. To accommodate the delayed *Hold* signal, an additional latch at the request packet IN port is closed whenever a *Hold* is asserted, while the previous router sends the next request packet. This results in the current packet remaining within the router, while the next packet occupies the interconnect. After the one cycle delay, the previous router will also stop transmitting. Pipelining of the flow control results in 30% *PClk* cycle time reduction. Direction circuits for the IN port coming from a core are shown in Fig. 1.10a. Each IN port compares the  $X_{dest}[2:0]$  and  $Y_{dest}[2:0]$  fields of a request packet with the fixed  $X_{core}[2:0]$  and  $Y_{core}[2:0]$  address of the router to determine routing direction. A chain of ripple-carry gates implementing 3b compare is optimally sized to account for fixed core addresses, resulting in worst-case delay of an inverter followed by two gates (Fig. 1.10b).

Following the direction circuits, the priority circuits in each OUT port choose one from among the valid request packets (Fig. 1.11). Round-robin priority selection is implemented using six circuits that select earliest arriving valid signals by comparing all pairs of valid signals in parallel, yielding 50% delay reduction compared to a tree implementation [15]. Since the circuits hold state when multiple *valid* signals arrive, deasserting the selected *valid* following transmit allows the next request packet to proceed.

Fig. 1.10 Request packet (a) direction circuits and (b) 3b comparator

Fig. 1.11 Request packet round-robin priority circuits

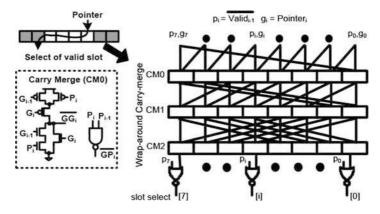

Each CClk cycle, bidirectional source, and destination acknowledges are sent across the network. A global pointer provides the starting point for a valid queue slot selection. Rotating this pointer in each cycle using a shift register improves fairness and prevents starvation. Use of a global pointer across all routers ensures that common paths are selected. The direction information stored in the selected queue slot sets the routing direction for the two acknowledges. The interface between the request packet circuits and circuit-switched routing is shown in Fig. 1.9. All register file storage is static latch-based with interrupted feedback for robust operation. At each *PClk*, the 2b direction is written to latches addressed by the 3b queue slot. At the same time, a separate latch is set to indicate to the request packet network that the slot is now full. In each CClk cycle, the full bits are transferred to a second latch indicating valid queue slots. The selected queue slot is cleared if both source and destination acknowledges are asserted, indicating that data will be transferred in the following cycle. The slot select circuit searches for the next valid queue slot starting at the pointer position (Fig. 1.12). This operation is similar to an adder carry chain in which the pointer generates a one that propagates through the chain as long as the queue slots are empty. Using a logarithmic carry tree with intermediate carries that wrap around from MSB to LSB provides this functionality after three logic gates, a 63% delay reduction. A leading one from the carry merge tree indicates the position of the one-hot slot select.

#### **1.2.3 Data Transmission Circuit Innovations**

During circuit-switched data transfer, data bits are routed through multiplexers and across interconnect and repeaters from the source to the destination. Selecting new paths in each *CClk* cycle may change the routing direction at each router, causing

Fig. 1.12 Slot select circuit

Fig. 1.13 Dual-supply circuits for data transmission

unnecessary interconnect transitions. Propagation of multiple transitions along a path significantly increases power consumption. Converting transitions to pulses through the multiplexer avoids these glitches by ensuring a common low value at all inputs when selecting new paths (Fig. 1.13). This pulse is then converted back to a transition before driving the next interconnect segment to reduce switching power on global interconnects. This reduces data switching power by up to 30%. In addition to reducing power by eliminating extra transitions, dual-supply operation (using Vlo and Vhi voltage levels), with only data transmission circuits at the lower supply, reduces power by 28% at iso-throughput while avoiding Vlo-to-Vhi level-conversion boundaries within control circuits.

Fig. 1.15 Circuits for proximity-based streaming

Since the minimum *CClk* period is determined by opposite corner mesh traversal, data sent over shorter distances arrive at destinations early. Streaming circuits exploit this slack, allowing multiple data transfers along the same channel during a *CClk* cycle (Fig. 1.14). *SClk* and *DClk* signals, clocks from both the source and destination that accompany the data, are routed in opposite directions along the path of the data; both are initially triggered from *CClk*. *SClk* arrival at the destination triggers both data capture and the next *DClk*. Arrival of *DClk* at the source triggers data transmit and the next *SClk* if more data are available. A transmit counter at the source, loaded on *CClk* and decremented every *DClk*, provides the gating *MData* signal, indicating that more data are available (Fig. 1.15). For random data transmissions, streaming increases total network throughput up to  $4.5 \times$ .

#### 1.3 NoC Measurements and Tradeoffs in 45 nm CMOS

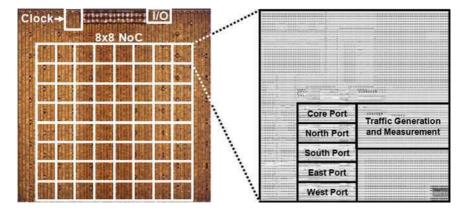

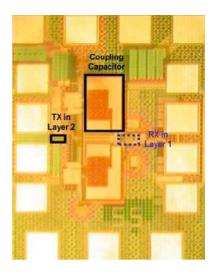

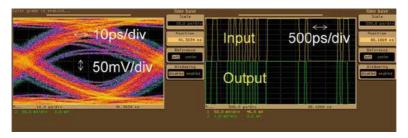

An  $8 \times 8$  mesh hybrid circuit-switched network-on-chip, consisting of packetswitched arbitration logic for 512b data width with 1b circuit-switched data interconnect, is fabricated in 45 nm High-K/Metal-gate CMOS (Fig. 1.16) [16]. Each

Fig. 1.16 Network-on-chip die micrograph in 45 nm CMOS

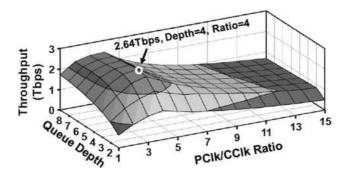

Fig. 1.17 Network performance vs. queue depth and PClk/CClk ratio

2 mm interconnect is folded  $8 \times$  to reduce area of the prototype. On-die integrated traffic generation and measurement circuits enable static or random destination addresses with per-router programmable data rates. Using a separate supply, measured 1b data interconnect power and throughput are scaled to 512b width with 50% switching activity resulting in 560 Tbps/W energy efficiency, 4.1 Tbps bisection bandwidth, and 11 ns diagonal corner-to-corner fall-through latency. The packet-switched requests propagate at a maximum measured frequency (*PClk*) of 2 GHz, while the maximum 512 MHz *CClk* allows single-cycle opposite corner circuit-switched communication. The network achieves a maximum 2.64 Tbps throughput for random data transmissions at the optimal *PClk* to *CClk* ratio of 4 at 1.1 V, 50°C (Fig. 1.17). Lowering this ratio by reducing the *PClk* frequency reduces available paths during the acknowledge phase, while increasing the clock ratio by decreasing *CClk* frequency slows the circuit-switched transmit rate. For a 64 core network, four queue slots provide 87% throughput increase with diminishing returns for additional slots. Link utilization measures average circuit-switched interconnect use to indicate

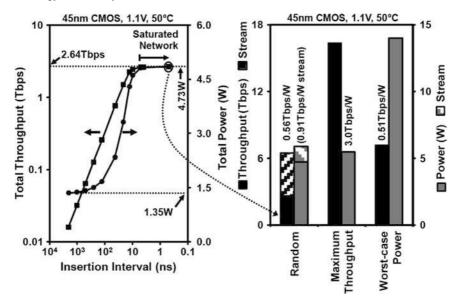

Fig. 1.18 Network throughput and power vs. data insertion rate per core and traffic

routing efficiency. Utilization of total interconnects averages 20%, while utilization of interconnects with available paths averages 50%.

Network traffic patterns vary according to destinations, whether random or static, and data insertion interval or transmit rate. Saturation of the network is achieved by increasing the rate at which data transmitted to random destinations by each of the 64 cores. The maximum throughput reaches 2.64 Tbps while average latencies increase from 8 ns to 30 ns (Fig. 1.18). Total network power peaks at 4.73 W with 0.97 W active leakage, or 74 mW/core. This power scales as network activity decreases, reaching 1.35 W or 21 mW/core with longer insertion intervals (1.1 V, 50°C). While transmissions to random destinations indicate average network performance, static traffic patterns indicate saturated network efficiency limits at maximum throughput or worst-case power (Fig. 1.19). A static traffic pattern with transmissions between neighboring Cores results in maximum throughput, increasing energy efficiency to 3.0 Tbps/W. A static pattern for worst-case power, using 88% of available circuit-switched interconnect, reduces energy efficiency to 0.51 Tbps/W.

Lowering the supply voltage decreases power consumption faster than performance, improving energy efficiency. Figure 1.20 shows the impact of supply voltage scaling on the throughput, power, and energy efficiency of a saturated network with random traffic. The energy efficiency increases from the nominal 0.56 to 1.51 Tbps/W, while operating at 634 Gbps, 420 mW measured at 550 mV, 50°C. During nominal 1.1 V operation, 83% of the total power is consumed in actual data transmission with the arbitration overhead falling to less than 10% at 550 mV.

0.5 17% 1.1V 1.1V 0.0 0.0 n Vhi: 0.50 0.75 1.00 1.25 Vhi: 0.50 0.75 1.00 1.25 VIo: 0.50 0.70 0.90 1.10 VIo: 0.50 0.70 0.90 1.10 Supply Voltage (V) Supply Voltage (V)

Fig. 1.20 Network throughput, power, energy efficiency, and arbitration overhead vs. supply voltage

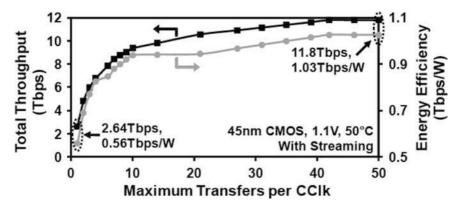

Additionally, energy efficiency of the saturated network with random destinations can also be increased by enabling streaming transfers. Streaming circuits allow multiple data transfers along a channel once the arbitration phases are complete. As this limit on maximum transfers during a *CClk* cycle is increased, the total network throughput increases by 4.5 times to 11.8 Tbps (Fig. 1.21). Since the arbitration power is amortized across larger data transfers, energy efficiency also improves from 0.56 to 1.03 Tb/s/W.

Fig. 1.21 Network performance and energy efficiency vs. streaming data transfers

# 1.4 Conclusion

NoC will be the backbone of the future SoC designs. These networks have evolved from simple buses to complex high dimensional networks of today, but will be limited by power and energy. We must consider hierarchical, heterogeneous networks, including packet switched and circuit switched networks, to fulfill the requirements of future SoCs. By leveraging the advantages of each network topology and switching style, hybrid networks can achieve higher energy efficiencies. The proposed hybrid circuit-switched network uses a packet network to reserve channels for future data transfer. This enables improved utilization of the circuit-switched resources, while eliminating intra-route data storage reduces overall power. Future SoCs will require multiple networks for different bandwidth, latency, energy efficiency, and area constraints that can benefit from combining the inherent advantages of different types of networks.

## References

- 1. Pham D et al (2005) The design and implementation of a first-generation CELL processor. International Solid State Circuits Conference 49–52

- Vangal S et al (2008) An 80-Tile Sub-100-W TeraFLOPS processor in 65-nm CMOS. IEEE Journal of Solid-State Circuits 43(1): 29–41

- Borkar S et al (1988) iWarp: An integrated solution to high-speed parallel computing. Proceedings of Supercomputing '88 330–339

- 4. Borkar S (2006) Networks for multi-core Chip—A controversial view. Workshop on On- and Off-Chip Interconnection Networks for Multicore Systems (OCIN06)

- 5. Benini L, Micheli G (2002) Networks on chips: A new SoC paradigm. Computer Magazine 35(1): 70–78

- Dally WJ, Towles B (2001) Route packets, not wires: On-chip interconnection networks. Design Automation Conference 684–689

- 7. Yu Z et al (2006) An asynchronous array of simple processors for DSP applications. International Solid State Circuits Conference 428–429

- Keckler S et al (2003) A wire-delay scalable microprocessor architecture for high performance systems. International Solid State Circuits Conference 168–169

- 9. Bell S et al (2008) TILE64 processor: A 64-Core SoC with mesh interconnect. International Solid State Circuits Conference 88–89

- 10. Taylor M et al (2003) A 16-issue multiple-program-counter microprocessor with point-to-point scalar operand network. International Solid State Circuits Conference 170–171

- 11. Wolkotte P et al (2005) An energy-efficient reconfigurable circuit-switched network-on-chip. International Parallel and Distibuted Processing Symposium 155a

- Anders M et al (2008) A 2.9Tb/s 8W 64-Core circuit-switched network-on-chip in 45nm CMOS. European Solid State Circuits Conference 182–185

- 13. Anders M et al (2010) A 4.1Tb/s bisection bandwidth 560Gb/s/W streaming circuit-switched 8x8 mesh network-on-chip in 45nm CMOS. International Solid State Circuits Conference 110–111

- 14. Wu CM, Chi HC (2005) Design of a high-performance switch for circuit-switched on-chip networks. Asian Solid States Circuits Conference 481–484

- Lee K. et al (2003) A high-speed and lightweight on-chip crossbar switch scheduler for on-chip interconnection networks. European Solid State Circuits Conference 453–456

- Mistry K et al (2007) A 45nm logic technology with high-k+Metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging. International Electron Devices Meeting 247–250

# Chapter 2 Run-Time Power-Gating Techniques for Low-Power On-Chip Networks

Hiroki Matsutani, Michihiro Koibuchi, Hiroshi Nakamura, and Hideharu Amano

**Abstract** Leakage power has already been consuming a considerable portion of the active power in recent process technologies. In this chapter, we survey various power gating techniques to reduce the leakage power of on-chip routers. Then we introduce a run-time fine-grained power-gating router, in which power supply to each router component (e.g., virtual-channel buffer, crossbar's multiplexer, and output latch) can be individually controlled in response to the applied workload. The fine-grained power gating router with 35 micro-power domains is designed using a commercial 65 nm process and evaluated in terms of the area overhead, application performance, and leakage power reduction.

# 2.1 Introduction

Network-on-Chips (NoCs) have been used not only in high-performance microarchitectures, but also in cost-effective embedded devices mostly used in consumer equipments, such as set-top boxes or mobile wireless devices. These embedded applications usually require low power, since power consumption is the dominant factor on their battery life, heat dissipation, and packaging cost.

The overall power consumption consists of dynamic switching power and static leakage power. Switching power is still the major component of the overall power consumption during active operations. In addition, we need to take care of the leakage power, since it has already been consuming a considerable portion of the active power in recent process technologies, and it will further increase while switching power becomes smaller when the technology is scaled down. Different saving techniques have been used for reducing each type of power. For example, clock gating, operand isolation, and dynamic voltage and frequency scaling (DVFS) target on switching power reduction. The design using transistors with multi-threshold voltages including power gating has been used for leakage power reduction.

H. Matsutani (🖂)

The University of Tokyo, 7-3-1 Hongo, Bunkyo-ku, Tokyo, Japan 113-8656 e-mail: matsutani@hal.ipc.i.u-tokyo.ac.jp

We mainly focus on the power gating to reduce the leakage power of NoC, since it is consumed without any packet transfers as long as the NoC is powered on. As the NoC is the communication infrastructure of various SoCs, it must be always ready for the packet transfers at any workload so as not to increase the communication latency; thus, we have studied some run-time power management techniques that dynamically stop the leakage current whenever possible [16, 17].

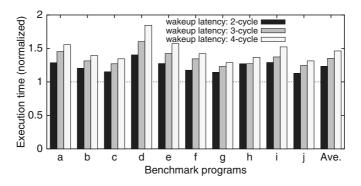

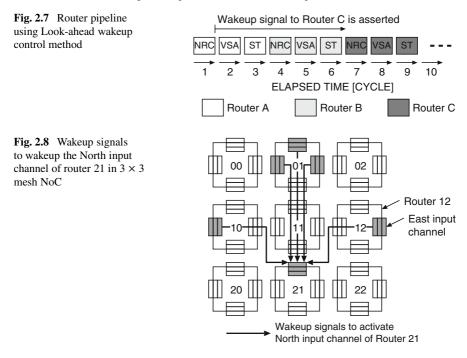

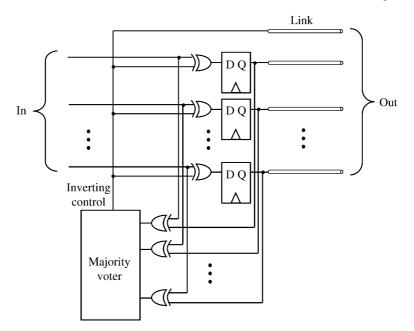

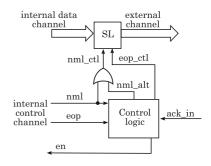

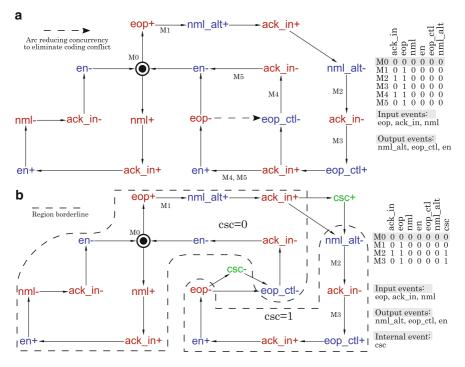

In this chapter, we introduce a run-time fine-grained power-gating router, in which power supply to each router component (e.g., virtual-channel buffer, crossbar's multiplexer, and output latch) can be individually controlled in response to the applied workload. As only the router components along an active datapath which is just transferring a packet are activated, the leakage power of the on-chip network can be reduced to the near-optimal level. However, such run-time power gating inherently increases the communication latency and degrades the application performance, since a certain amount of wakeup latency is required to activate the sleeping components. To mitigate the wakeup latency, we introduce three early wakeup methods that can detect the next packet arrival and activate the corresponding components in advance. The fine-grained power-gating router with the early wakeup methods is evaluated in terms of the application performance, area overhead, and leakage power.

The rest of this chapter is organized as follows. Section 2.2 shows architecture of a typical on-chip router and analyzes its power consumption. Section 2.3 surveys low-power techniques especially power gating for NoCs. Section 2.4 designs the fine-grained power-gating router and Sect. 2.5 proposes three early wakeup methods. Section 2.6 evaluates the power gating router with the early wakeup methods. Finally, Sect. 2.7 summarizes this chapter.

# 2.2 On-Chip Virtual-Channel Router

Before discussing low-power techniques for on-chip routers, an architecture of a simple on-chip virtual-channel (VC) router is presented, and then its dynamic and static power consumption is analyzed.

### 2.2.1 Target Router Architecture

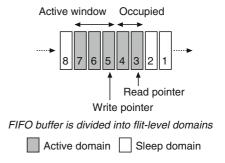

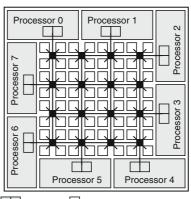

For investigation on NoC architectures, we have implemented a wormhole router with virtual channels. We also developed an NoC generator that automatically connects the routers in arbitrary network topologies. The generated NoC is synthesized, placed, and routed with a 65 nm standard cell library.

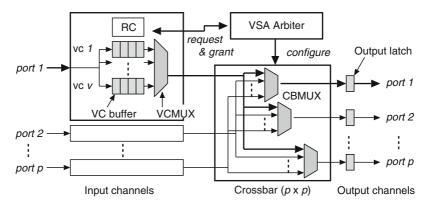

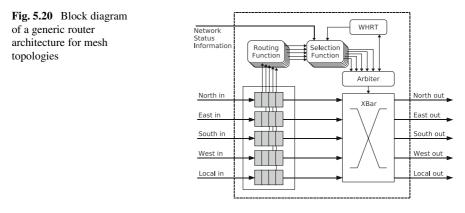

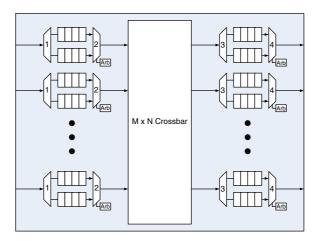

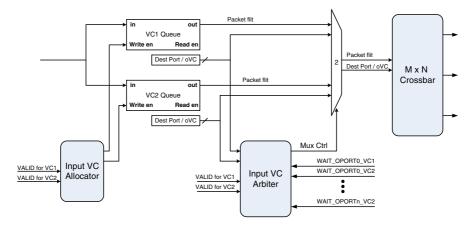

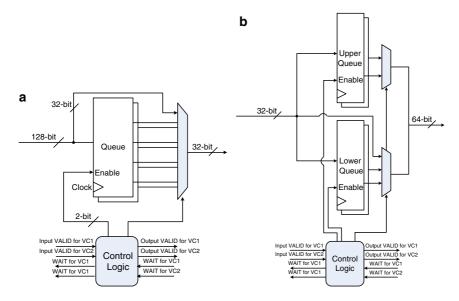

Figure 2.1 illustrates the virtual-channel router. The router has p input and output physical channels, a  $p \times p$  crossbar switch, and a round-robin arbiter that allocates a pair of output virtual and physical channels for each incoming packet. Each input

Fig. 2.1 Virtual-channel router architecture used

physical channel has a separated buffer queue for each virtual channel, while each output physical channel has a single one-flit buffer (**Output latch**) to decouple the switch and link delays.

To overcome the head-of-line blocking, a virtual-channel design sometimes uses a  $pv \times pv$  full crossbar, where p is the number of physical channels and v is the number of virtual channels. However, the crossbar complexity is significantly increased with the  $pv \times pv$  crossbar, and its performance improvement will be limited because the data rate out of each input port is limited by its bandwidth [5]. Therefore, we used a small  $p \times p$  crossbar by just duplicating the buffers. It is composed of p pto-1 multiplexers (**CBMUXes**), each of which is controlled by a select signal from the arbiter.

Each input physical channel has v virtual channels. It has a routing computation (RC) unit and a v-to-1 multiplexer (**VCMUX**) that selects only a single output from v virtual channels. Each virtual channel has a control logic, status registers, and an n-flit FIFO buffer (**VC buffer**). The RC unit in this design is very simple, because routing decisions are stored in the header flit prior to packet injection (i.e., source routing); thus, routing tables that require register files for storing routing paths are not needed.

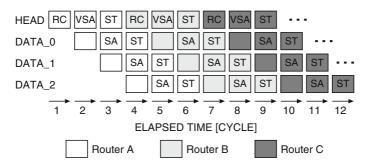

The router architecture is fully pipelined. Although some one- or two-cycle routers have been developed by using some aggressive techniques [18, 19], we selected a simple three-cycle router architecture illustrated in Fig. 2.2. In this figure, a packet that consists of a single header flit and three body flits is transferred from Router A to Router C. Each router transfers a header flit through three pipeline stages that consist of routing computation (RC) stage, virtual channel and switch allocation (VSA) stage, and switch traversal (ST) stage.

Finally, we designed an RTL model of the router. Its parameters p, v, and n are set to 5, 4, and 4, respectively. The flit width w is set to 128-bit. These FIFO buffers can be implemented with either SRAMs or flip-flops (FFs), depending on the depth of the buffers, not the width. We assume that buffers should be implemented with

Fig. 2.2 Three-stage router pipeline. A packet is transferred from router A to C

macro cells if their depths are more than 16. Otherwise buffers should simply be implemented with FFs. Since the depth of the FIFO buffers in this design is only four, the input buffers are implemented with small FFs.

# 2.2.2 Power Analysis of the Target Router Architecture

To estimate the power consumption of the router mentioned previously, the following steps are performed:

- 1. The RTL model of the router is synthesized by the Synopsys Design Compiler.

- 2. The netlist is placed and routed (including a clock tree synthesis and buffer insertion) by the Synopsys Astro.

- 3. The placed-and-routed design is simulated by the Cadence NC-Verilog, to obtain the switching activity information of the router.

- 4. The power consumption is estimated from the switching activity by the Synopsys Power Compiler.

A 65 nm CMOS process with a core voltage of 1.20 V is selected for this analysis. Clock gating and operand isolation are fully applied to the router to minimize its switching activity and dynamic power.

In step 3, the router is simulated at 500 MHz with various fixed workloads (i.e., throughputs), in the same manner as in [2]. A packet stream is defined as intermittent injections of packets that use approximately 30% of the maximum link bandwidth of a single router link. Each header flit contains a fixed destination address, while the data flits contain random values as a payload. The number of packet streams injected into the router is changed so as to generate various workloads. In this experiment, up to five streams are applied to the five-port router, and the power consumption at each workload level is analyzed.

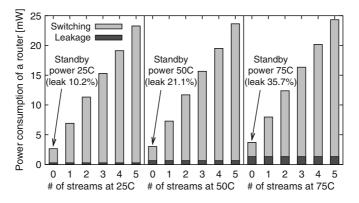

Figure 2.3 shows power consumption of the router with various workloads and temperatures. The router consumes more power as it processes more packet streams, in the following way:

$$P_{\text{total}} = P_{\text{standby}} + xP_{\text{stream}},\tag{2.1}$$

where x is the number of packet streams and  $P_{\text{stream}}$  is the dynamic power for processing a packet stream.

Fig. 2.3 Power consumption of router with various workloads (temperature:  $25^{\circ}$ C,  $50^{\circ}$ C, and  $75^{\circ}$ C)

Note that the router consumed a certain amount of power even with no traffic (i.e.,  $P_{\text{standby}}$ ). Leakage power consumes a substantial portion of the standby power, and it drastically increases as the temperature increases. For example, the leakage power consumes 35.7% of the standby power when the temperature is 75°C. The remaining standby power is the dynamic power consumed by the clock tree buffers and the latches inserted for the clock gating; hence, further reduction of the switching activity would be difficult.

The leakage power is consumed without any packet transfers as long as the NoC is powered on; thus it cannot be negligible. In this chapter, we introduce power-gating techniques to reduce the leakage power.

## 2.3 Previous Work on Low-Power Techniques

Various low-power techniques have been used for microprocessors and on-chip routers. In particular, clock gating and operand isolation are common techniques and they have already been applied to our router design. Section 2.3.1 surveys the voltage and frequency scaling techniques. Section 2.3.2 surveys the run-time power gating and network link shutdown techniques.

## 2.3.1 Voltage and Frequency Scaling Techniques

The dynamic voltage and frequency scaling (DVFS) is a power-saving technique that reduces the operating frequency and supply voltage according to the applied workload. The dynamic power consumption is related to the square of the supply voltage; thus, because a peak performance is not always required during the whole execution time in most cases, adjusting the frequency and supply voltage so as to at least achieve the required performance can reduce the dynamic power.

DVFS has been applied to various circuits, such as microprocessors, accelerators, and network links. In [21], the frequency and the voltage of network links are dynamically adjusted based on the past utilization. In [23], the network link voltage is scaled down by distributing the traffic load using an adaptive routing. The frequency is typically controlled by a PLL frequency divider, and the supply voltage can be adjusted by controlling an off-chip dc–dc converter.

### 2.3.2 Power Gating Techniques

Power gating is a representative leakage-power reduction technique, which shuts off the power supply of idle circuits blocks by turning off (or on) the power switches, which are inserted between the GND line and the blocks or between the VDD line and the blocks. Leakage current can be much reduced by the power switch made with high threshold low leakage transistors without reducing the speed of the target circuits block using low-threshold high-speed transistors. This concept has been applied to circuits blocks with various granularities, such as processor cores or IP modules [10, 11], execution units in a processor [7, 9, 20], and primitive gates. Depending on the granularity of target circuits blocks (i.e., power domains), the power gating is classified into coarse-grained approach and fine-grained one.

#### 2.3.2.1 Coarse-Grained Power-Gating Techniques

In the coarse-grained approach, a target circuits block is surrounded by a power/ ground ring. Power switches are inserted between the core ring and power/ground IO cells. The power supply to the circuits block can be controlled by the power switches. Since the power supply to all cells inside the core ring is controlled at one time, this approach is well suited to the IP- or module-level power management. The coarse-grained approach has been popularly used, since its IP- or module-level power management is straightforward and easy to control.

#### 2.3.2.2 Fine-Grained Power Gating Techniques

The fine-grained approach has received a lot of attention in recent years because of its flexibility and short wakeup latency [8,9,20,24].

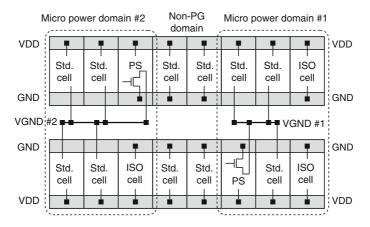

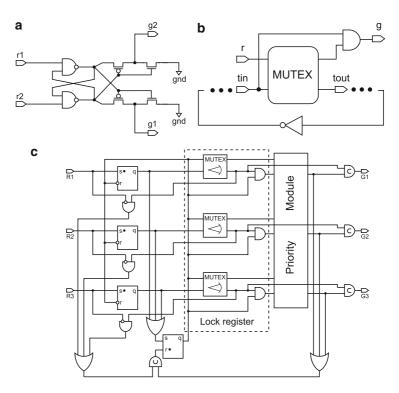

Although various types of fine-grained power-gating techniques have been proposed, we focus on the method proposed in [24]. In this method, customized standard cells, each of which has a virtual ground (VGND) port by expanding the original cell, are used. These standard cells that share the same active signal form

Fig. 2.4 Fine-grained power gating. Two micro power domains and a single non power-gating domain are illustrated. PS and ISO refer to a power switch and an isolation cell, respectively

a single micro-power domain, by connecting their VGND ports to a shared local VGND line, as shown in Fig. 2.4. Power switches are inserted between the VGND line and GND line for controlling the power supply to the micro-power domain. Figure 2.4 illustrates two micro-power domains and a single non-power-gating domain. Each micro-power domain has its own local VGND line and power switch.

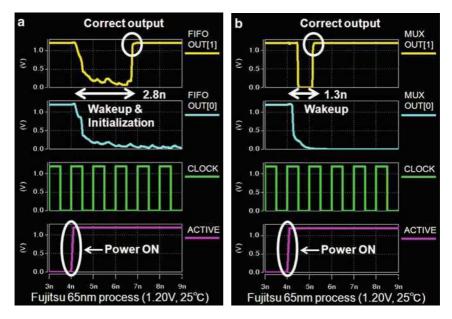

Compared with the UPF-based methodology [8], it can control the number of power switches more flexibly by considering a given wakeup latency requirement. That is, various shapes of micro-power domains can be formed by grouping the standard cells that share the same active signal. The wakeup latency of this method is typically less than a few nanoseconds (we will confirm this in Sect. 2.4.3). A real chip implementation of a microprocessor which uses this fine-grained power gating has been reported recently [9] and its feasibility has also been confirmed.

In this chapter, we only focus on fine-grained approach because coarse-grained one is difficult to be used for on-chip routers. Each input physical channel works independently of each other unless packet contentions with the other physical channels occur. In addition, all virtual channels in the same physical channel are not always used. Actually zero or only a few virtual channels are occupied at the same time in most cases. This indicates that a finer-grained partitioning can exploit the spatial and temporal communication locality and increase the power-gating opportunities.

### 2.3.2.3 Power Gating for Interconnection Networks

As the standby power consumption is becoming more and more serious, various power-gating techniques have been applied to on-chip routers to reduce the standby leakage power [16, 17, 25]. In [25], each router is partitioned into ten smaller sleep regions with control of individual router ports. An input physical channel level

power gating is studied in [17], while a virtual channel level power management is discussed in [16]. In [3], PMOS power switches controlled by an ultra-cut-off (UCO) technique are inserted in each NoC unit to maintain minimum leakage in standby mode.

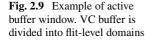

When the power-gating techniques are applied to on-chip networks, the wakeup control of power domains is one of the most important factors on the application performance. In [22], the authors provide a thorough discussion about power-aware networks whose links can be turned on and off, in terms of connectivity, routing, wake-up and sleep decisions, and router pipeline architecture. In [4], as a leakage-power aware buffer management method, a certain portion (i.e., window size) of the buffer is made active before it is accessed, in order to remove the performance penalty. By tuning the window size, the input ports can always provide enough buffer space for the arrival of packets, and the network performance will never be affected [4].

In Sect. 2.4, we introduce the fine-grained power gating router with 35 micropower domains. In Sect. 2.5, we introduce three early wakeup methods that can mitigate or completely remove the negative impact of the wakeup latency.

# 2.4 Fine-Grained Power Gating Router

Here, we first show how an on-chip router is divided into a number of micro-power domains. Then we implement these power domains using a 65 nm process and evaluate them in terms of the area overhead and wakeup latency.

# 2.4.1 Power Domain Partitioning

Before partitioning the on-chip router into a number of micro-power domains, we should estimate the gate count of each router component, since the leakage power is proportional to the device area. The RTL model of the router designed in Sect. 2.2.1 is used. As mentioned before, the router has five input physical channels, each of which has four virtual channels. Each virtual channel has a four-flit buffer queue. The flit width is 128-bit.

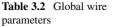

Table 2.1 shows the gate count of each router component, such as VC buffer, output latch, CBMUX, and VCMUX (Fig. 2.1). In this table, "Others" include the gate counts of routing computation units, an arbiter, VC status registers, and the other control logic, but each of these components is quite small compared to the other components. Actually, these miscellaneous logics consume only 11.9% of the router area; so they are removed from the power domain list in order to simplify the power gating router design. Consequently, the router area is divided into 35 power domains including VC buffers, Output latches, VCMUXes, and CBMUXes, which can cover 88.1% of the total router area.

| Table 2.1Total gate countof each router component(before PS insertion) [kilogates] | Module              | Count | Total gate count | Ratio |

|------------------------------------------------------------------------------------|---------------------|-------|------------------|-------|

|                                                                                    | 4-flit VC buffer    | 20    | 111.06           | 77.9% |

|                                                                                    | 1-flit output latch | 5     | 5.49             | 3.9%  |

|                                                                                    | 5-to-1 CBMUX        | 5     | 4.91             | 3.4%  |

|                                                                                    | 4-to-1 VCMUX        | 5     | 4.21             | 3.0%  |

|                                                                                    | Others              | 1     | 16.92            | 11.9% |

|                                                                                    | Total               |       | 142.58           | 100%  |

## 2.4.2 Power Domain Implementation

Here, we design all power domain types (i.e., VC buffer, Output latch, CBMUX, and VCMUX) in order to estimate their area overhead and wakeup latency.

The following design flow is used for all power domain types.

- 1. An RTL model of a power domain with an active signal is designed.

- 2. The RTL model is synthesized by the Synopsys Design Compiler.

- 3. Isolation cells are inserted to all output ports of the synthesized netlist in order to hold the output values of the domain when the power supply is stopped.

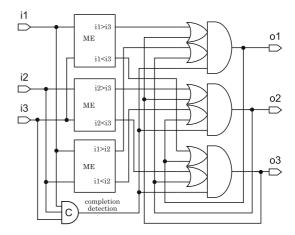

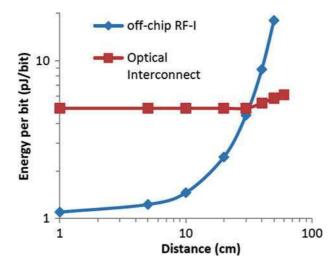

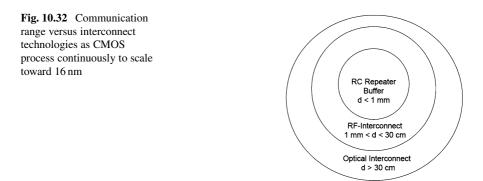

- 4. The netlist with isolation cells is placed by the Synopsys Astro.