# Cristina Silvano · William Fornaciari Eugenio Villar *Editors*

# Multi-objective Design Space Exploration of Multiprocessor SoC Architectures

The MULTICUBE Approach

Multi-objective Design Space Exploration of Multiprocessor SoC Architectures

Cristina Silvano • William Fornaciari Eugenio Villar Editors

# Multi-objective Design Space Exploration of Multiprocessor SoC Architectures

The MULTICUBE Approach

Prof. Cristina Silvano Dipartimento di Elettronica e Informazione Politecnico di Milano, Via Ponzio 34/5, 20133 Milano, Italy e-mail: silvano@elet.polimi.it

Prof. William Fornaciari Dipartimento di Elettronica e Informazione Politecnico di Milano, Via Ponzio 34/5, 20133 Milano, Italy e-mail: fornacia@elet.polimi.it Prof. Eugenio Villar Departamento de Tecnología Electrónica e Ingeniería de Sistemas y Automática (TEISA) University of Cantabria, Av. Los Castros s/n, 39005 Santander, Spain e-mail: villar@teisa.unican.es

ISBN 978-1-4419-8836-2 e-ISBN 978-1-4419-8837-9 DOI 10.1007/978-1-4419-8837-9 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011932796

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

"That is the exploration that awaits you! Not mapping stars and studying nebula, but charting the unknown possibilities of existence."

Q to Captain Jean Luc Picard Star Trek: The Next Generation, 1994.

### Foreword

The objective of the European research programme in Information and Communication Technologies (ICT) is to improve the competitiveness of European industry and enable Europe to shape and master future developments in ICT. ICT is at the very core of the knowledge based society. European research funding has as target to strengthen Europe's scientific and technology base and to ensure European leadership in ICT, help drive and stimulate product, service and process innovation through ICT use and value creation in Europe, and ensure that ICT progress is rapidly transformed into benefits for Europe's citizens, businesses, industry and governments.

Over the last years, the European Commission has constantly increased the amount of funding going to research in computing architectures and tools with special emphasis on multicore computing. Typically, European research funding in a new area (like multi/many core computing) starts with funding for a Network of Excellence. Networks of Excellence are an instrument to overcome the fragmentation of the European research landscape in a given area by bringing together around a common research agenda the leading universities and research centers in Europe; their purpose is to reach a durable restructuring/shaping and integration of efforts and institutions.

In the following years, a number of collaborative research projects may also be funded to address specific, more industrially oriented, research challenges in the same research area. It is important to note here that collaborative research projects are the major route of funding in the European research landscape in a way that is quite unique worldwide. In European collaborative research projects, international consortia consisting of universities, companies and research centers, are working together to advance the state of the art in a given area. The typical duration of such a project is three years.

In 2004 the European Commission launched the HiPEAC Network of Excellence. In 2006, the European Commission launched the Future and Emerging Technologies initiative in Advanced Computing Architectures as well as a number of projects covering Embedded Computing. In 2008, a new set of projects were launched to address the challenges of the multi/many core transition—in embedded, mobile and general-purpose computing—under the research headings "Computing Systems" and "Embedded Systems". These projects were complemented by a second wave of projects that have started in 2010 under the same research headings together with a new Future and Emerging Technologies initiative on "Concurrent Tera-device Computing". This effort continues in 2011 with two Calls for Proposals: one under the heading "Computing Systems" with 45 million euro funding and the other under the heading "Exascale Computing" with 25 million euro funding.

The MULTICUBE collaborative research project was funded to perform research on multi-objective design space exploration of multicore architectures targeting embedded applications. Results from MULTICUBE are presented in this book providing a valuable reference point to researchers and engineers.

It has been a long way, but we now have an important computing research community in Europe, both from industry and academia, engaging in collaborative research projects that bring together strong European teams in cutting-edge technologies. The book that you have in your hands is a clear demonstration of the breakthroughs that can be obtained through European collaboration.

> Dr. Panagiotis Tsarchopoulos Project Officer European Commission

## Preface

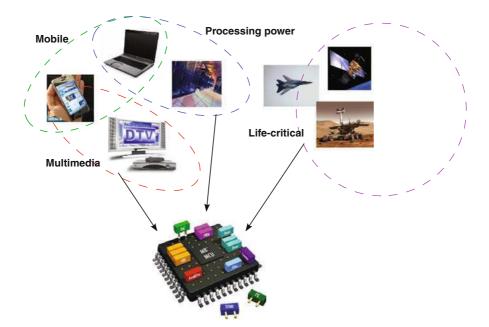

The ever increasing complexity and integration densities of multiprocessor systemon-chip (MPSoC) architectures, significantly enlarges the design space of embedded computing systems. A wide range of design choices must be tuned from a multiobjective perspective, mainly in terms of performance and energy consumption, to find the most suitable system configuration for the target application. Given the huge design space to be analysed, the exploration of tradeoffs between multiple competing objectives cannot be anymore driven by a manual optimisation process based on the intuition and past experience of the system architect. Multi-objective exploration of the huge design space of next generation multi/many core architectures needs for Automatic Design Space Exploration techniques to systematically explore the design choices and to compare them in terms of multiple competing objectives (trade-offs analysis). Ideally, a designer would try all possible design choices and choose the most suitable according to the specific system requirements. Unfortunately, such an exhaustive approach is often unfeasible because of the large number of design choices to be simulated and analysed, in some cases showing some sophisticated effects on system properties that rarely enable to easily and accurately model the system behavior. Consequently, good search techniques are needed not only to find design alternatives that best meet system constraints and cost criteria, but also to prune the search space to crucial parameters to enable an effective and efficient design space exploration.

In the age of multi/many core architectures, system optimization and exploration definitely represent challenging research tasks. Although many point tools exist to optimize particular aspects of embedded systems, an overall design space exploration framework is needed to combine all the decisions into a global search space with a common interface to the optimization and evaluation tools. The state-of-the art lacks of a Design Space Exploration (DSE) framework to help the designer in the automatic selection of the most suitable system configuration for a certain application given a set of multiple competing objectives.

Based on the idea to provide an automatic DSE framework, we started thinking about a proposal of an European project, namely MULTICUBE<sup>1</sup>, that was submitted in May 2007 in the first call of the Seventh Framework Programme on ICT under the Objective 3.3 on Embedded Systems Design. The proposal was accepted and the project started on January 2008 under the coordination of Politecnico di Milano. This book was mainly catalyzed by the main research outcomes and exploitable results of the MULTICUBE European project, where the Editors have acted in 2008–2010 timeframe. The MULTICUBE project focused on the definition of an automatic multi-objective Design Space Exploration (DSE) framework to be used to tune the System-on-Chip architecture for the target application evaluating a set of metrics (e.g. energy, latency, throughput, bandwidth, QoR, etc.) for the next generation embedded multimedia platforms.

The project aimed at increasing the competitiveness of European industries by optimizing the design of embedded computing systems while reducing design time and costs. The project defined an automatic multi-objective DSE framework to be used at design-time to find the best power/performance trade-offs while meeting system-level constraints and speeding up the exploration process. A set of heuristic optimization algorithms have been defined to reduce the exploration time, while a set of response surface modeling techniques have been defined to further speed up the process. Based on the results of the design-time multi-objective exploration, the MULTICUBE project also defined a methodology to be used at run-time to optimize the allocation and scheduling of different application tasks. The design exploration flow results in a Pareto-optimal set of design alternatives in terms of power/performance trade-offs. This set of operating points can then be used at run-time to decide how the system resources should be distributed over different application tasks running on the multiprocessor system on chip.

The MULTICUBE DSE framework leverages a set of open-source and proprietary tools for the exploration, modeling and simulation to guarantee a wide exploitation of the MULTICUBE project results in the embedded system design community. The integration of different tools is ensured by a common XML-based tool interface specification, defined to enable the independent development of modules and a seamless integration of the design tools and the data structures into a common design environment. Several industrial use cases (defined as combination of application and related architecture) have been used to assess the capabilities of the MULTICUBE design flow and tools in an industrial design process. The MULTICUBE project has been strongly industry-driven: industrial partners (STMicroelectronics and DS2) as well IMEC research center have defined the design techniques and tools requirements and then validated them to design some industrial use cases. The benefits of the introduction of the automatic DSE in the design phase of embedded computing systems (justifying its introduction in industrial design processes) have been assessed through a procedure to assess the final objective design quality and the reduction of design turnaround time by introducing such a technology on the entire design

<sup>&</sup>lt;sup>1</sup> The project acronym, MULTICUBE, stands for: "Multi-Objective design space exploration of multi-processor SoC architectures for embedded multimedia applications".

process. The benefits on the design process can be measurable and tangible like the reduction of the overall design process lead time, and qualitative or intangible like the streamlining and the reduction of human error prone repetitive operations. The DSE assessment procedure was the basis for the validation of the industrial use cases and demonstrators of the project. Validation results have been assessed based on a set of common assessment criteria.

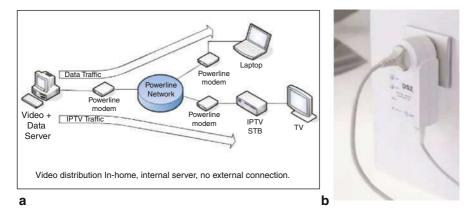

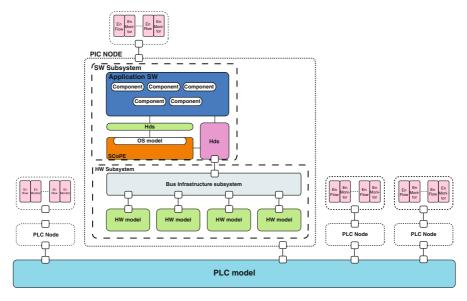

In the book, we have tried to provide a comprehensive understanding of several facets of the problem of design space exploration for embedded on-chip architectures. The book chapters are organized in two parts. In Part I, several methodologies and tools to support automatic design space exploration are discussed. In Part II of the book, the DSE methodologies and tools described in Part I have then been applied to several application domains to discuss their applicability and to envision their benefits. First, a high-level modeling and exploration approach has been applied for a powerline communication network based on a SoC, then the application of the automatic DSE flow to parallel on-chip architectures is discussed, and finally the DSE for run-time management has been applied to a reconfigurable system for video streaming.

Entering Part I on methodologies and tools, Chap. 1 introduces the MULTICUBE design-flow to support the automatic multi-objective Design Space Exploration (DSE) to tune the parameters of System-on-Chip architectures by considering several metrics such as energy, latency and throughput. One of the important goals of the DSE framework is to find design trade-offs that best meet the system constraints and the cost criteria which are indeed strongly dependent on the target application. The DSE flow is based on the interaction of two frameworks to be used at design time: the Design Space Exploration Framework, a set of open-source and proprietary architectural exploration tools, and the Power/Performance Estimation Framework, a set of modeling and simulation tools (open-source and proprietary) operating at several levels of abstraction. The DSE flow also includes the specification of an XML integration interface to connect the exploration and estimation frameworks and a Run-time Resource Manager that selects, at run-time, the best software configuration alternatives to achieve a good power/performance trade-off.

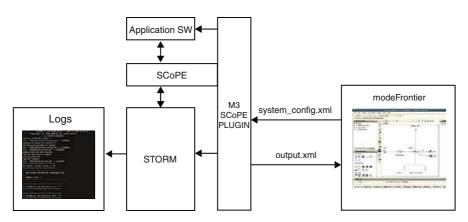

Chapter 2 introduces M3-SCoPE, an open-source SystemC-based framework for performance modeling of multi-processor embedded systems, software source code behavioral simulation and performance estimation of multi-processor embedded systems. Using M3-SCoPE, the application software running on the different processors of the platform can be simulated efficiently in close interaction with the rest of the platform components. In this way, fast and accurate performance metrics of the system are obtained. These metrics are then delivered to the DSE tools to evaluate the quality of the different configurations in order to select the best power/performance trade-offs.

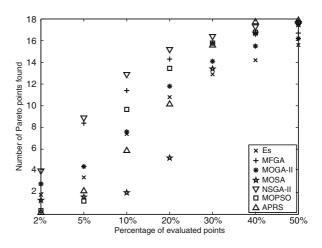

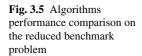

Chapter 3 presents the optimization algorithms developed in the MULTICUBE project for Design Space Exploration of embedded computing systems. Two software DSE tools implement the optimization algorithms: M3Explorer and modeFRON-TIER. The mathematical details of the given optimization problems are explained in

the chapter together with how the algorithms can exchange information with the simulators. The description of the proposed algorithms is the central part of the chapter. The focus is posed on new algorithms and on "ad hoc" modifications implemented in existing techniques to face with discrete and categorical variables, which are the most relevant ones when dealing with embedded systems design. The strategy to test the performance achieved by the optimization is another important topic treated in the chapter. The aim is mainly to build confidence in optimization techniques, rather than to simply compare one algorithm with respect to another one. The "no-freelunch theorem for optimization" has to be taken into consideration and therefore the analysis will look forward to robustness and industrial reliability of the results. The main contribution of MULTICUBE project in the research field of optimization techniques for embedded systems design is indeed the high level of the obtained compromise between specialization of the algorithms and concrete usability of the DSE tools.

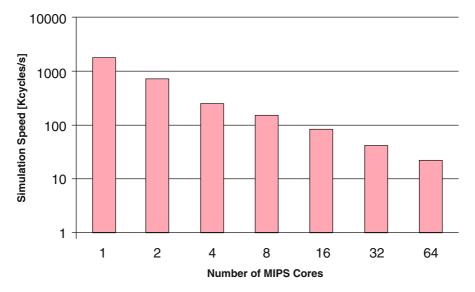

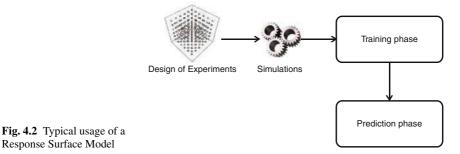

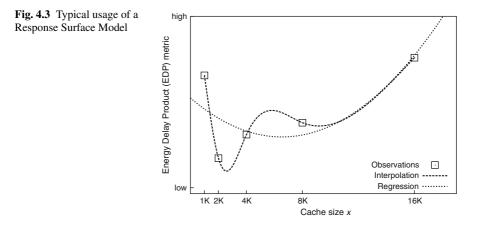

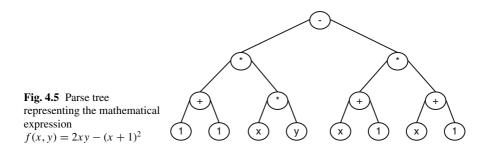

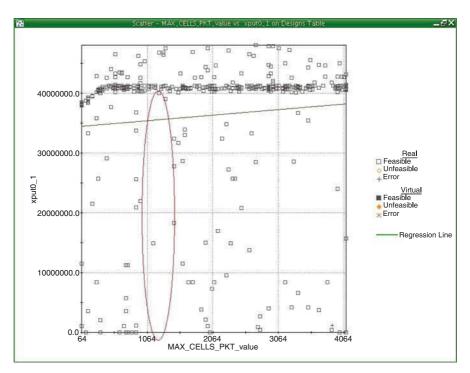

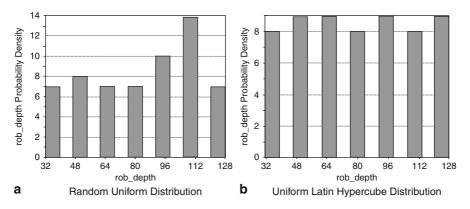

A typical design space exploration flow involves an event-based simulator in the loop, often leading to an actual evaluation time that can exceed practical limits for realistic applications. Chip multi-processor architectures further exacerbate this problem given that the actual simulation speed decreases by increasing the number of cores of the chip. Traditional design space exploration lacks of efficient techniques that reduce the number of architectural alternatives to be analyzed. In Chap. 4, we introduce a set of Response Surface Modeling (RSM) techniques that can be used to predict system level metrics by using closed-form analytical expressions instead of lengthy simulations. The principle of RSM is to exploit a set of simulations generated by one or more Design of Experiments strategies to build a surrogate model to predict the system-level metrics. The response model has the same input and output features of the original simulation based model but offers significant speed-up by leveraging analytical, closed-form functions which are tuned during a model training phase.

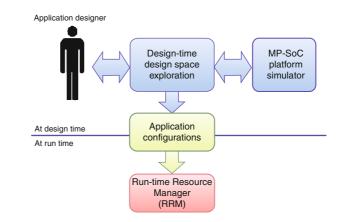

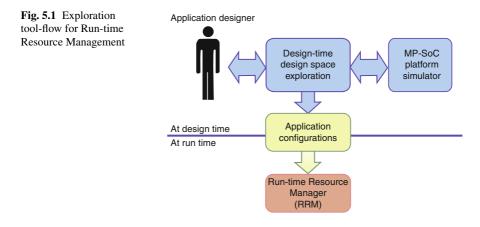

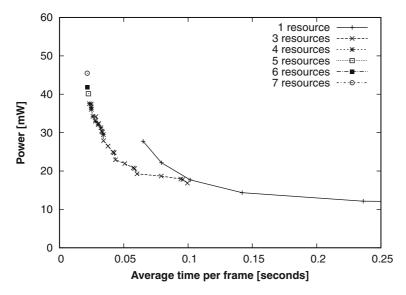

Running multiple applications optimally in terms of Quality of Service (e.g., performance and power consumption) on embedded multi-core platforms is a huge challenge. Moreover, current applications exhibit unpredictable changes of the environment and workload conditions which makes the task of running them optimally even more difficult. Chapter 5 presents an automated tool flow which tackles this challenge by a two-step approach: first at design-time, a Design Space Exploration (DSE) tool is coupled with a platform simulator(s) to get optimum operating points for the set of target applications. Secondly, at run-time, a lightweight Run-time Resource Manager (RRM) leverages the design-time DSE results for deciding an operating configuration to be loaded at run-time for each application. This decision is taken dynamically, by considering the available platform resources and the QoS requirements of the specific use-case. To keep RRM execution and resource overhead at minimum, a very fast optimisation heuristic is integrated demonstrating a significant speedup in the optimisation process, while maintaining the desired Quality of Service.

Emerging MPSoC platforms provide the applications with an extended set of physical resources, as well as a well a defined set of power and performance optimization mechanisms (i.e., hardware control knobs). The software stack, meanwhile,

Preface

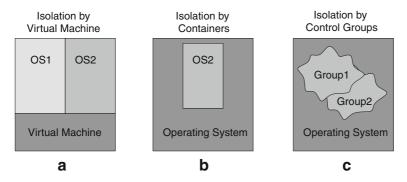

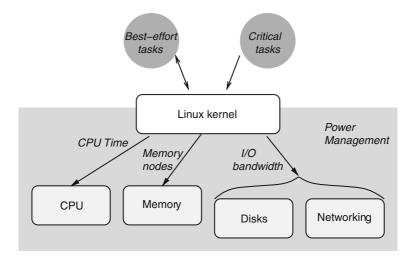

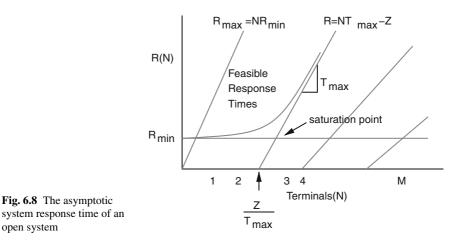

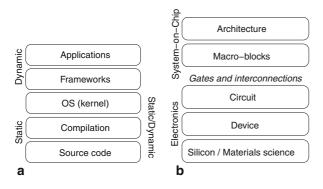

is responsible of taking directly advantage of these resources, in order to meet application functional and non-functional requirements. The support from the Operating System (OS) is of utmost importance, since it gives opportunity to optimize the system as a whole. The main purpose of Chap. 6 is to introduce the reader to the challenges of managing physical and logical resources in complex multi/many-core architectures at the OS level.

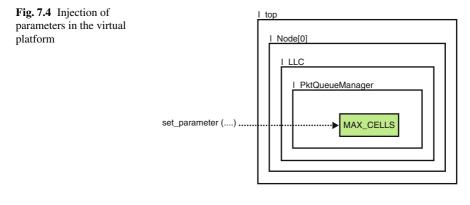

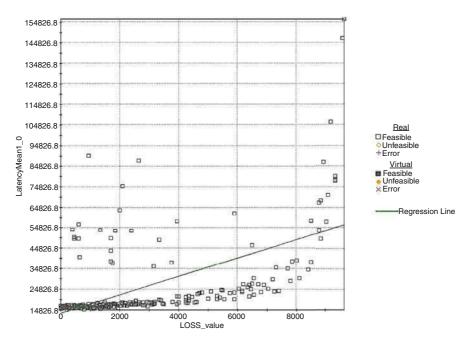

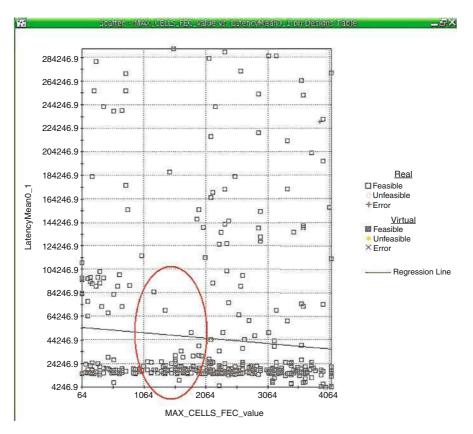

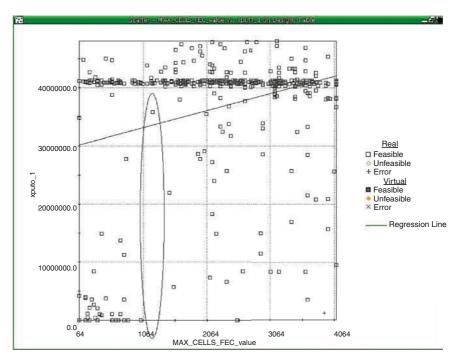

Entering Part II on application domains, Chap. 7 presents the application of MUL-TICUBE methodology to the design of an ITU G.hn compatible component for a powerline communication network based on a SoC. Powerline communication is an advanced telecommunication system enabling fast and reliable transfer of audio, video and data information using the most ubiquitous transmission system: the power lines. This transmission line is used to exchange information between different equipment connected to the network using the advanced coding techniques like such as Orthogonal Frequency Division Multiplexing. The starting point of the analysis is a high level SystemC-based virtual platform for which the chapter analyzes the effects of the variation of a pre-defined set of design parameters on a set of pre-defined metrics. This automatic analysis will drive the design choices in order to build an optimized industrial system. The chapter shows that the SystemC-based virtual platform combined with the MULTICUBE design space exploration framework can save up to 80% of designer's work time, while achieving better results in terms of performance.

Chapter 8 describes two significant applications of the automatic MULTICUBE DSE flow to parallel on-chip architectures. The first part of the chapter presents the design space exploration of a low power processor developed by STMicroelectronics by using the modeFRONTIER tool to demonstrate the benefits DSE not only in terms of objective quality, but also in terms of impact on the design process within the corporate environment. The second part of the chapter describes the application of Response Surface Models introduced in Chap. 4 to a tiled, multiple-instruction, many-core architecture developed by the Chinese Academy of Sciences. Overall, the results have showed that different models can present a trade-off of accuracy versus computational effort. In fact, throughout the evaluation, we observed that high accuracy models require high computational time (for both model construction time and prediction time); vice-versa low model construction and prediction time has led to low accuracy.

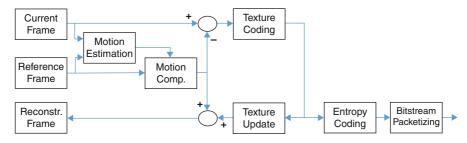

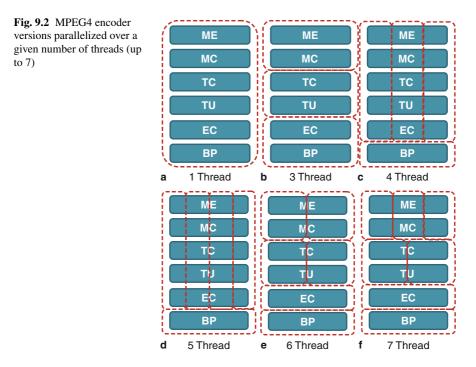

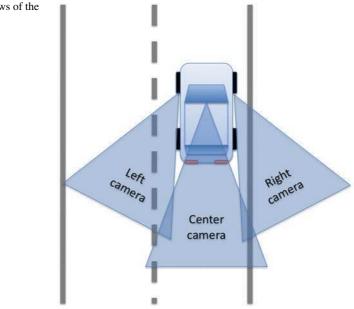

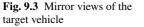

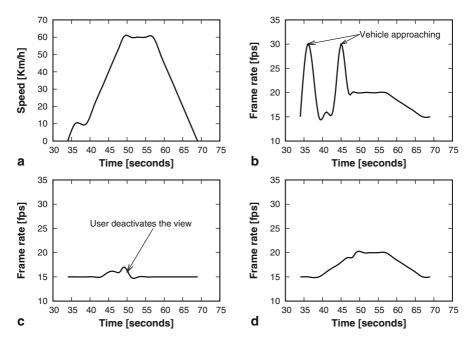

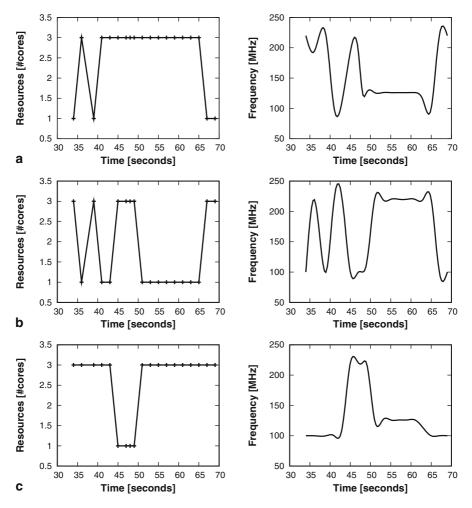

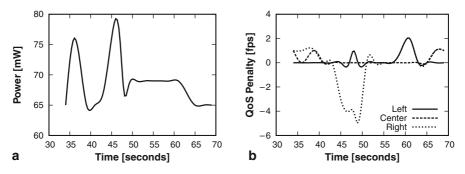

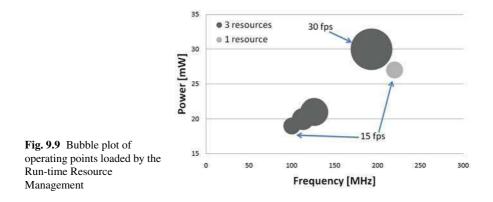

Chapter 9 reports a case study of DSE for supporting Run-time Resource Management (RRM). The management of system resources for an MPSoC dedicated to multiple MPEG4 encoding is addressed in the context of an Automotive Cognitive Safety System. The runtime management problem is defined as the minimization of the platform power consumption under resource and Quality of Service (QoS) constraints. The chapter provides an insight of both, design-time and run-time aspects of the problem. During the preliminary design-time DSE phase, the best configurations of run-time tunable parameters are statically identified for providing the best tradeoffs in terms of run-time costs and application QoS. To speed up the optimization process without reducing the quality of final results, a multi-simulator framework is used for modeling platform performance. At run-time, the RRM exploits the design-time DSE results for deciding an operating configuration to be loaded for each MPEG4 encoder. This operation is carried out dynamically, by following the QoS requirements of the specific use-case.

Due to the large number of topics discussed in the book and their heterogeneity, the background on system modeling, simulation and exploration is discussed chapter by chapter with a separate reference set for each chapter. This choice also contributed to make each chapter self-contained.

Overall, we believe that the book chapters cover a set of definitely important and timely issues impacting the present and future research on automatic DSE for embedded multi-core on-chip architectures. We sincerely hope that the book could become a solid reference in the next years. In our vision, the authors put a big effort in clearly presenting their technical contributions outlining the potential impact and benefits of the proposed approach on same case studies. Our warmest gratitude goes to the MULTICUBE team, for their continuous effort and dedication during the project and for their contribution as authors of the chapters. We would like to gratefully acknowledge our EC Project Officer, Panagiotis Tsarchopoulos and our EC Project Reviewers: Alain Perbost, Andrzej Pulka and Kamiar Sehat for their valuable comments and guidance during the MULTICUBE project. A special thanks to Charles Glaser from Springer for encouraging us to write a single textbook on the topic of design space exploration based on our experience of the MULTICUBE project.

With our work on MULTICUBE project and this book, we have pushed towards the adoption of automatic design space exploration for the design of multi-processor architectures for embedded computing systems. This book is expected to be one of the most important dissemination vehicles to spread out the knowledge developed in the MULTICUBE project in the international community after the end of the project.

Milano, Italy Milano, Italy Santander, Spain March 2011 The Editors, Cristina Silvano William Fornaciari Eugenio Villar

# Contents

#### Part I Methodologies and Tools

| 1 | The MULTICUBE Design Flow                                                  | 3   |

|---|----------------------------------------------------------------------------|-----|

|   | Cristina Silvano, William Fornaciari, Gianluca Palermo, Vittorio Zaccaria, |     |

|   | Fabrizio Castro, Marcos Martinez, Sara Bocchio, Roberto Zafalon,           |     |

|   | Prabhat Avasare, Geert Vanmeerbeeck, Chantal Ykman-Couvreur,               |     |

|   | Maryse Wouters, Carlos Kavka, Luka Onesti, Alessandro Turco,               |     |

|   | Umberto Bondi, Giovanni Mariani, Hector Posadas, Eugenio Villar,           |     |

|   | Chris Wu, Fan Dongrui, and Zhang Hao                                       |     |

| 2 | M3-SCoPE: Performance Modeling of Multi-Processor Embedded                 |     |

|   | Systems for Fast Design Space Exploration                                  | 19  |

|   | Hector Posadas, Sara Real, and Eugenio Villar                              |     |

| 3 | Optimization Algorithms for Design Space Exploration                       |     |

|   | of Embedded Systems                                                        | 51  |

|   | Enrico Rigoni, Carlos Kavka, Alessandro Turco, Gianluca Palermo,           |     |

|   | Cristina Silvano, Vittorio Zaccaria, and Giovanni Mariani                  |     |

| 4 | Response Surface Modeling for Design Space Exploration                     |     |

|   | of Embedded System                                                         | 75  |

|   | Gianluca Palermo, Cristina Silvano, Vittorio Zaccaria, Enrico Rigoni,      |     |

|   | Carlos Kavka, Alessandro Turco, and Giovanni Mariani                       |     |

| 5 | Design Space Exploration Supporting Run-Time Resource                      |     |

|   | Management                                                                 | 93  |

|   | Prabhat Avasare, Chantal Ykman-Couvreur, Geert Vanmeerbeeck,               |     |

|   | Giovanni Mariani, Gianluca Palermo, Cristina Silvano,                      |     |

|   | and Vittorio Zaccaria                                                      |     |

| 6 | Run-Time Resource Management at the Operating System Level                 | 109 |

|   | Patrick Bellasi, Simone Corbetta, and William Fornaciari                   |     |

#### Part II Application Domains

| 7              | High-Level Modeling and Exploration of a PowerlineCommunication Network Based on System-on-ChipMarcos Martinez, David Ferruz, Hector Posadas, and Eugenio Villar                                                                                                                  | 145 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8              | <b>Design Space Exploration of Parallel Architectures</b><br>Carlos Kavka, Luka Onesti, Enrico Rigoni, Alessandro Turco,<br>Sara Bocchio, Fabrizio Castro, Gianluca Palermo, Cristina Silvano,<br>Vittorio Zaccaria, Giovanni Mariani, Fan Dongrui, Zhang Hao,<br>and Tang Shibin | 171 |

| 9              | <b>Design Space Exploration for Run-Time Management</b><br>Giovanni Mariani, Chantal Ykman-Couvreur, Prabhat Avasare,<br>Geert Vanmeerbeeck, Gianluca Palermo, Cristina Silvano,<br>and Vittorio Zaccaria                                                                         | 189 |

| Conclusions    |                                                                                                                                                                                                                                                                                   | 205 |

| Index of Terms |                                                                                                                                                                                                                                                                                   |     |

# **List of Contributors**

**Prabhat Avasare** IMEC, Leuven, Belgium e-mail: avasare@imec.be

**Patrick Bellasi** Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milano, Italy e-mail: bellasi@elet.polimi.it

**Sara Bocchio** STMicroelectronics, Agrate, Italy e-mail: sara.bocchio@st.com

**Umberto Bondi** ALaRI, University of Lugano, Lugano, Switzerland e-mail: umberto.bondi@usi.ch

**Fabrizio Castro** Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milano, Italy e-mail: castro@elet.polimi.it

Simone Corbetta Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milano, Italy e-mail: scorbetta@elet.polimi.it

**Fan Dongrui** Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China e-mail: fandr@ict.ac.cn

**David Ferruz** Design of Systems on Silicon (DS2), Valencia, Spain e-mail: david.ferruz@ds2.es

**William Fornaciari** Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milano, Italy e-mail: fornacia@elet.polimi.it

**Zhang Hao** Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China e-mail: zhanghao@ict.ac.cn

**Carlos Kavka** ESTECO, Trieste, Italy e-mail: carlos.kavka@esteco.com

**Giovanni Mariani** ALaRI, University of Lugano, Switzerland e-mail: giovanni.mariani@usi.ch

**Marcos Martinez** Design of Systems on Silicon (DS2), Valencia, Spain e-mail: marcos.martinez@ds2.es

Luka Onesti ESTECO, Trieste, Italy e-mail: luka.onesti@esteco.com

**Gianluca Palermo** Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milano, Italy e-mail: gpalermo@elet.polimi.it

**Hector Posadas** University of Cantabria, Santander, Spain e-mail: posadash@teisa.unican.es

**Sara Real** University of Cantabria, Santander, Spain e-mail: realsara@teisa.unican.es

**Enrico Rigoni** ESTECO, Trieste, Italy e-mail: rigoni@esteco.it

**Tang Shibin** Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China e-mail: tangshibin@ict.ac.cn

**Cristina Silvano** Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milano, Italy e-mail: silvano@elet.polimi.it

Alessandro Turco ESTECO, Trieste, Italy e-mail: alessandro.turco@esteco.it

Geert Vanmeerbeeck IMEC, Leuven, Belgium e-mail: vanmeerb@imec.be

**Eugenio Villar** University of Cantabria, Santander, Spain e-mail: villar@teisa.unican.es

Maryse Wouters IMEC, Leuven, Belgium e-mail: woutersm@imec.be

**Chris Wu** STMicroelectronics, Beijing, China e-mail: chris.wu@st.com

Chantal Ykman-Couvreur IMEC, Leuven, Belgium e-mail: ykman@imec.be

Vittorio Zaccaria Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milano, Italy e-mail: zaccaria@elet.polimi.it

**Roberto Zafalon** STMicroelectronics, Agrate, Italy e-mail: roberto.zafalon@st.com

# Abbreviations

| 4CIF    | 4 × Common Intermediate Format                              |

|---------|-------------------------------------------------------------|

| ACCS    | Automotive Cognitive Safety System                          |

| ADRES   | Architecture for Dynamically Reconfigurable Embedded System |

| ADRS    | Average Distance from Reference Set                         |

| API     | Application Programming Interface                           |

| APRS    | Adaptive-windows Pareto Random Search                       |

| BP      | Bitstream Packetizing                                       |

| CMP     | Chip Multi Processor                                        |

| CSU     | Central Safety Unit                                         |

| DOE     | Design of Experiments                                       |

| DSE     | Design Space Exploration                                    |

| DSP     | Digital Signal Processor                                    |

| DVFS    | Dynamic Voltage and Frequency Scaling                       |

| EC      | Entropy Coding                                              |

| ES      | Evolution Strategies                                        |

| GA      | Genetic Algorithm                                           |

| HW      | Hardware                                                    |

| ILP     | Integer Linear Programming                                  |

| IP      | Intellectual Property                                       |

| IPC     | Instruction per Cycle                                       |

| MC      | Motion Compensation                                         |

| ME      | Motion Estimation                                           |

| MFGA    | Magnifying Front GA                                         |

| MMKP    | Multi-dimension Multiple-choice Knapsack Problem            |

| MOGA    | Multi Objective GA                                          |

| MOO     | Multi-Objective Optimization                                |

| MOPSO   | Multi Objective Particle Swarm Optimization                 |

| MOSA    | Multi Objective Simulated Annealing                         |

| MPA     | MPSoC Parallelization Assist                                |

| MPEG4   | Moving Picture Experts Group 4                              |

| MPSoC   | Multi-Processor Systems on Chip                             |

| NSGA-II | Non-dominated Sorting Genetic Algorithm, second version     |

|         |                                                             |

| Operating System             |

|------------------------------|

| Quality of Service           |

| Resource Manager             |

| Run-time Resource Management |

| Response Surface Model       |

| Run-Time Operating System    |

| Run-Time Resource Manager    |

| System on Chip               |

| STMicroelectronics           |

| Software                     |

| Texture Coding               |

| Task Concurrency Management  |

| Transaction-Level Model      |

| Texture Update               |

| Very Long Instruction Word   |

| eXtensible Markup Language   |

|                              |

## **About the Editors**

Cristina Silvano received the M.S. degree in Electronic Engineering from Politecnico di Milano, Milano, Italy, in 1987 and the Ph.D. degree in Computer Engineering from the University of Brescia, Brescia, Italy, in 1999. From 1987 to 1996, she was a Senior Design Engineer at R&D Labs, Groupe Bull, Pregnana, Italy. From 2000 to 2002, she was Assistant Professor at the Department of Computer Science, University of Milan, Milano. She is currently Associate Professor (with tenure) in Computer Engineering at the Dipartimento di Elettronica e Informazione, Politecnico di Milano. She has published two scientific international books and more than 90 papers in international journals and conference proceedings, and she is the holder of several international patents. Her primary research interests are in the area of computer architectures and computer-aided design of digital systems, with particular emphasis on design space exploration and low-power design techniques for multiprocessor systems-on-chip. She participated to several national and international research projects, some of them in collaboration with STMicrolectronics. She is currently the European Coordinator of the project FP7-2PARMA-248716 on "PARallel PAradigms and Run-time MAnagement techniques for Many-core Architectures" (Jan. 2010-Dec. 2012). She was also the European Coordinator of the FP7-MULTICUBE-216693 project on "Multi-objective design space exploration of multi-processor SoC architectures for embedded multimedia applications" (Jan. 2008–June 2010). She served as member and/or co-chair in the technical committees of several international conferences such as MICRO, DAC, DATE, NOCS, SASP, ARCS and VLSI-SOC.

**William Fornaciari** is Associate Professor (with tenure) at Dipartimento di Elettronica e Informazione, Politecnico di Milano, Italy. He received the Laurea (M.Sc.) degree in Electronic Engineering and the Ph.D. degree in Automation Engineering and Computer Sciences, both from the Politecnico di Milano in 1989 and 1993 respectively. He has published five books and over 100 papers in international journals and conference proceedings, collecting four best paper awards, one certification of appreciation from IEEE and holds two international patents. Since 1993 he is member of program and scientific committees and chair of international conferences in the field of computer architectures, EDA and system-level design. He has been also involved in the faculty of a joint Master program between the Politecnico di Milano and the University of Chicago at Illinois. Since 1997 has been involved in 11 EUfunded international projects and has been part of the pool of experts of the Call For Tender No. 964-2005 - WING - Watching IST INnovation and knowledGe. His current research interest includes embedded systems design methodologies, realtime operating systems, energy-aware design of SW and HW for multi-many core systems, reconfigurable computing and wireless sensor networks. Recently his involvement is manily releated to MULTICUBE, SMECY, 2PARMA and COMPLEX european projects.

**Eugenio Villar** got his Ph.D. in Electronics from the University of Cantabria in 1984. Since 1992 is Full Professor at the Electronics Technology, Automatics and Systems Engineering Department of the University of Cantabria where he is currently the responsible for the area of HW/SW Embedded Systems Design at the Microelectronics Engineering Group. His research activity has been always related with system specification and modeling. His current research interests cover system specification and design, MPSoC modeling and performance estimation using SystemC and UML/Marte. He is author of more than 100 papers in international conferences, journals and books in the area of specification and design of electronic systems. Prof. Villar served in several technical committees of international conferences like the VHDL Forum, Euro-VHDL, EuroDAC, DATE, and FDL. He has participated in several international projects in electronic system design under the FP5, FP6 and FP7, Itea, Medea and Artemis programs. He is the representative of the University of Cantabria in the ArtemisIA JU.

# Part I Methodologies and Tools

# Chapter 1 The MULTICUBE Design Flow

Cristina Silvano, William Fornaciari, Gianluca Palermo, Vittorio Zaccaria, Fabrizio Castro, Marcos Martinez, Sara Bocchio, Roberto Zafalon, Prabhat Avasare, Geert Vanmeerbeeck, Chantal Ykman-Couvreur, Maryse Wouters, Carlos Kavka, Luka Onesti, Alessandro Turco, Umberto Bondi, Giovanni Mariani, Hector Posadas, Eugenio Villar, Chris Wu, Fan Dongrui, and Zhang Hao

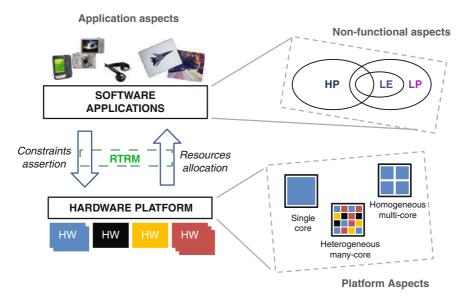

Abstract This chapter introduces the design-flow of the MULTICUBE project whose main goal is the definition of an automatic multi-objective Design Space Exploration (DSE) framework to be used to tune the parameters of System-on-Chip architectures by taking into account the target set of metrics (e.g. energy, latency, throughput, etc.). One of the important goals of the automatic multi-objective DSE framework is to find design trade-offs that best meet system constraints and cost criteria which are indeed strongly dependent on the target application. A set of heuristic optimisation algorithms have been defined to reduce the overall optimization time by identifying an approximated Pareto set of parameter configurations with respect to a set of selected figures of merit. Once the approximated Pareto set is built, the designer can quickly apply decision criteria to select the best configuration satisfying the constraints. The DSE flow is based on the interaction of two frameworks to be used at design time: the Design Space Exploration Framework, a set of opensource and proprietary architectural exploration tools, and the Power/Performance Estimation Framework, a set of modeling and simulation tools (open-source and proprietary) operating at several levels of abstraction. The DSE flow also includes the specification of an XML integration interface to connect the exploration and estimation frameworks and a Run-time Resource Manager exploiting, at run-time, the best software configuration alternatives derived at design-time to optimize the usage of system resources.

#### 1.1 Introduction

Many point tools exist to optimise particular aspects of embedded systems. However, an overall design space exploration framework is needed to combine all the decisions into a global search space, and a common interface to the optimisation and evaluation

C. Silvano (🖂)

Dipartimento di Elettronica e Informazione Politecnico di Milano, Milano, Italy e-mail: silvano@elet.polimi.it

tools. The MULTICUBE project focused on the definition of an automatic multiobjective Design Space Exploration (DSE) framework to be used to tune the Systemon-Chip architecture for the target application evaluating a set of metrics (e.g. energy, latency, throughput, bandwidth, QoS, etc.) for the next generation of embedded multimedia platforms.

On one side, the MULTICUBE project defined an automatic multi-objective DSE framework to find design trade-offs that best meet system constraints and cost criteria, strongly dependent on the target application, but also to restrict the search space to crucial parameters to enable an efficient exploration. In the developed DSE framework, a set of heuristic optimisation algorithms have been defined to reduce the overall exploration time by computing an approximated Pareto set of configurations with respect to the selected figures of merit. Once the approximated Pareto set has been built, the designer can quickly select the best system configuration satisfying the target constraints.

On the other side, the MULTICUBE project defined a run-time DSE framework based on the results of the design-time exploration to optimise at run-time the allocation and scheduling of different application tasks. The design-time exploration flow results in a Pareto-optimal set of design trade-offs with different speed, energy, memory and communication bandwidth parameters. This information is used at run-time by a small OS kernel to make an informed decision about how the resources should be distributed over different tasks running on the multi-processor system on-chip. This resource distribution cannot be done during the design-time exploration itself, since it depends on which tasks are active at that time.

The goal of MULTICUBE design flow is to cover the gap between the systemlevel specification and the definition of the optimal application-specific architecture. The MULTICUBE activities have been driven by targeting the construction of a set of tools and accurate methodologies to support the design of application specific multi-core architectures.

In this context, a SystemC-based multi-level modeling methodology for multiprocessors has been developed in the project. Once received the target architecture as input, the system model is provided to the simulator to evaluate different architectural trade-offs in terms of metrics. Then, the Design Space Exploration framework can be used to evaluate candidate configurations based on several heuristic optimisation algorithms. This step is implemented as an optimisation loop, where the selected architecture instance generated by the DSE framework is given back to the estimation framework for the metrics evaluation. The tool integration phase in MULTICUBE enabled to implement an automatic system optimisation engine to generate, for the target MPSoC architecture, either the best architectural alternative (if the exploration is done at design-time) or the best tasks scheduling and allocation (if the exploration is done at run-time).

To enable a widespread dissemination and use of the design flow in several application contexts, the following pre-requirements are introduced. First, the design flow aims at being independent from the particular language used for the description of the use case simulator. The design flow and the associated design tools should free the simulator provider from being tied to a specific programming language or model. Second, the interface between the design tools and the use case simulators should be specified and implemented by using a widely accepted and standardized interface. Standard interfaces are characterized by being supported by a large number of parsing and validation tools either in the public domain or commercially available while enabling a faster adoption of the design tool itself. Among the available interface specification languages, the most widely accepted and flexible is XML. XML enables to create efficient, customized data structures which are, at the same time, supported by industrial and academic tools for parsing, semantic evaluation and validation. These data structures can be used to facilitate the definition of tool interfaces.

The Chapter is organized as follows. Section 1.2 provides an overview of the MULTICUBE design flow, while Sect. 1.3 describes the design tools integration based on a common interface. Finally, Sect. 1.4 presents the advantages in using the automatic design space exploration approach.

#### **1.2** Overview of the Design Flow

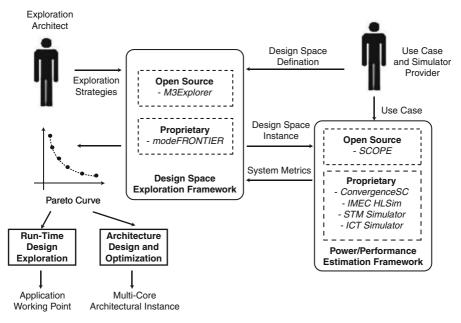

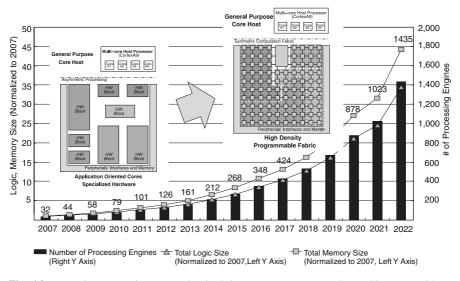

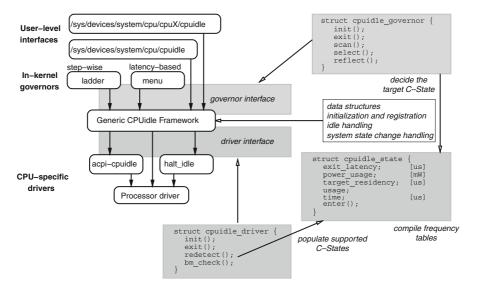

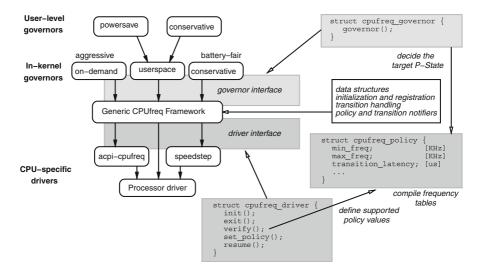

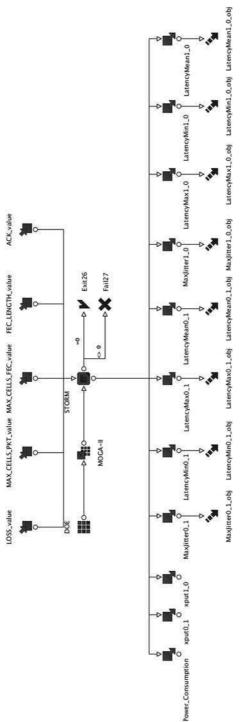

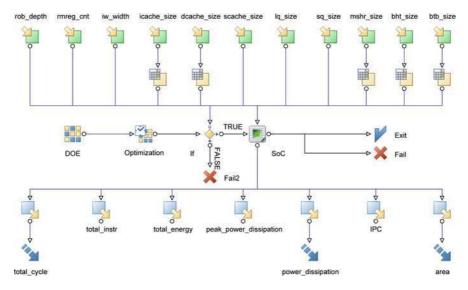

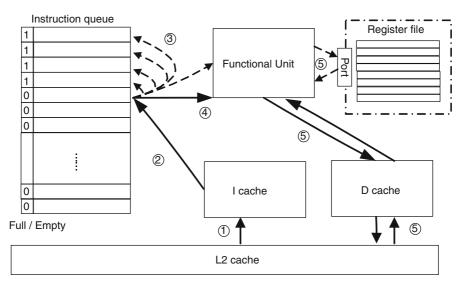

The MULTICUBE DSE flow (see Fig. 1.1) is based on the interaction of two frameworks to be used at design time: the Design Space Exploration Framework, an architecture exploration set of tools, and the Power/Performance Estimation Framework, a set of modeling and simulation tools operating at several levels of abstraction. The DSE flow also includes a Run-time Resource Manager to select at run-time the best design alternatives in terms of power/performance trade-offs generated during the design-time exploration phase.

According to the exploitation plan of the MULTICUBE project, both open-source and the proprietary exploitation models and tools co-exist into a single coherent view. This has been possible by making the design tools to adopt the same common MULTICUBE XML-based interface described in Sect. 1.3.

#### 1.2.1 The Design Space Exploration Framework

The MULTICUBE Design Space Exploration Framework (see Fig. 1.1) consists of an architecture exploration set of tools providing the designers with the most appropriate optimisation of the multi-processor SoC considering several figures of merit such as performance and energy consumption.

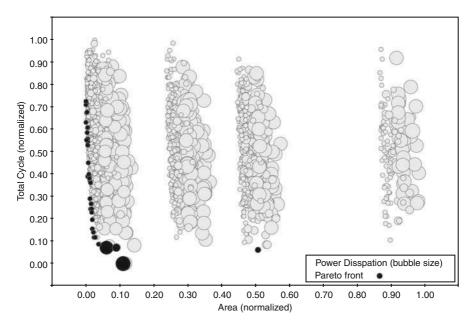

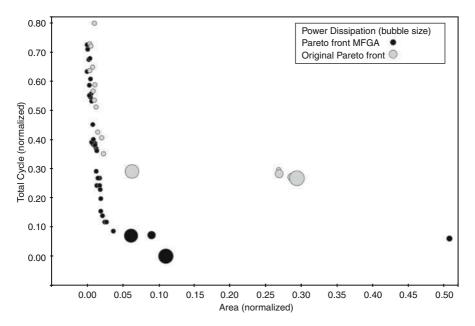

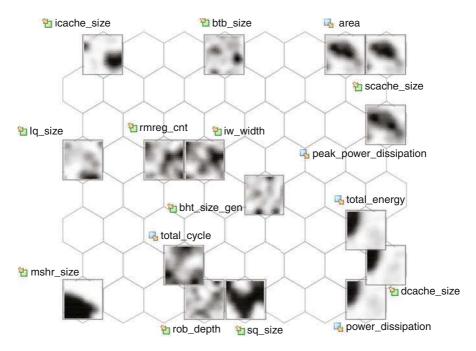

The Design Space Exploration tools can be used at design time to automatically identify the Pareto optimal solutions of a multi-objective exploration given a set of design space parameters. During the MULTICUBE project, two design space exploration tools and some optimisation and analytical techniques have been developed and validated.

Fig. 1.1 Overview of the MULTICUBE design flow

- A new open source tool (Multicube Explorer available at http://www. multicube.eu) suitable for automatic design space exploration of MPSoC architectures. The tool enables a fast optimisation of parameterized system architecture towards a set of objective functions (e.g., energy, delay and area), by interacting with a system-level simulator through an open XML-based interface. Multicube Explorer provides a set of innovative sampling and optimisation techniques to support the designer in finding the best objective functions trade-offs. It also provides a set of Response Modeling Methods for speeding up the optimisation phase.

- An existing commercial tool (modeFRONTIER from ESTECO), widely adopted in other optimisation fields, has been re-targeted to support automatic DSE in the embedded systems field. The tool includes the most recent optimisation techniques available in literature, ranging from Design of Experiments to direct optimisers. modeFRONTIER (see also http://www.esteco.com) also provides meta-modeling support for the creation of interpolating surfaces from well statistically distributed designs to be used to perform the optimisation without computing any further analysis. The tool also supports multivariate statistical analysis and data mining tools directly integrated in the exploration process to enable the user to easily analyse complex data. The graphical user interface of modeFRONTIER provides access to all features of design experiment definition, exploration and analysis in a simple and intuitive way.

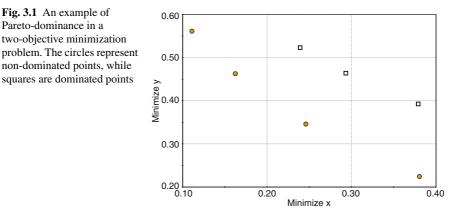

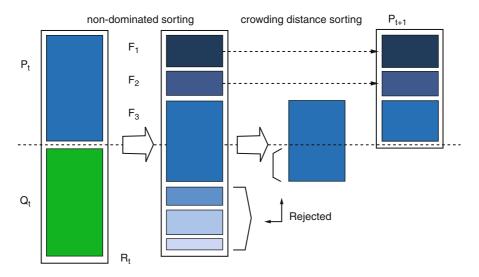

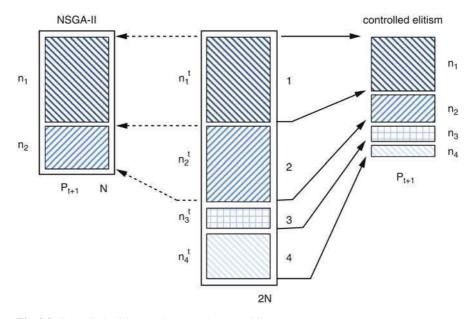

Both tools leverage a set of multi-objective optimisation algorithms that have been validated on several industrial use cases. In multi-objective optimisation problems

there are more than one objective to be optimised (maximized or minimized), meaning that the outcome of the optimisation process is not a single solution but a set of solutions. This set of solutions, which is called the Pareto front, represents the best trade-off between the different (and possibly contradictory) objectives. The set of algorithms implemented includes state-of-the-art algorithms widely used in the field of multi-objective optimisation (ranging from evolutionary and genetic algorithms up to simulated annealing and particle swarm algorithms), enhanced versions of algorithms that were specifically targeted in the project for the multi-core SoC design, and new developed algorithms. The multi-objective optimisation algorithms developed in the MULTICUBE project are described in more detail in Chap. 3 of this book.

#### 1.2.2 The Power/Performance Estimation Framework

The Power/Performance Estimation Framework (see Fig. 1.1) consists of a methodology and related tools that have been set up to provide accurate estimates for complexity, timing and power consumption at different abstraction levels and for different use cases. A set of tools has been used for the system modeling and estimation of several metrics such as energy consumption and execution time of the target MPSoC platforms among which:

- Multicube SCoPE: an extension of the open-source high-level SCoPE performance and power evaluation framework [7] developed by University of Cantabria for performing HW/SW co-simulation. Multicube SCoPE enables the definition of SystemC platform template models to evaluate performance and power consumption. Multicube SCoPE efficiency comes from the fact that performance and power estimations of the software side are performed at the application source code level by using back-annotation. The back-annotated software components are then linked to the hardware components by using standard SystemC interfaces. This modeling style is called *Timing Approximate*. Software back-annotation avoids instruction set simulation therefore decreasing of several orders of magnitude the simulation time and maintaining a fairly good accuracy with respect to cycle-accurate simulation. Multicube SCoPE also provides some hooks for enabling C/C++ software code to invoke operating system primitives compliant with POSIX and MicroC/OS. Multicube SCoPE is described in more detail in Chap. 2 of this book.

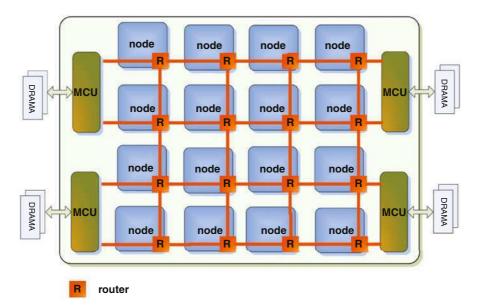

- A proprietary set of simulation tools developed by IMEC as SystemC-based transaction-level multi-core simulator built on top of the CoWare virtual prototyping environment to support platform-based design approach. The TLM-based prototype models an ADRES multi-core [6] and has been integrated with both modeFRONTIER and Multicube Explorer tools. The platform is composed of a variable number of processor nodes and memory nodes. All processor nodes

contain the IMEC proprietary ADRES VLIW processor and its scratch-pad local data (L1) memory. The processing nodes are connected to the memory nodes by a configurable communication infrastructure. It can be either a multi-layer AHB bus, which provides a full point-to-point connectivity, or a NoC model built with the CoWare AVF cross-connect IP.

- A High-Level time-annotated Simulator (HLSim, developed by IMEC) that provides a fast simulator of the ADRES platform at higher abstraction level to estimate metrics like performance and power consumption for a given platform architecture executing a parallelized version of the application. During the MULTICUBE project, HLSim has been extended with metrics on energy consumption derived from a multimedia use case for a relative comparison between different architectures and parallelizations. The introduction of HLSim in the design flow has provided several benefits such as speeding up the simulation and starting up the design exploration earlier than planned. HLSim-based explorations are much faster than TLM-based ones so as more extensive DSE was done by using HLSim to extract Pareto set information to be used at run-time.

- An instruction set simulator has been used for SP2 superscalar processor provided by STMicroelectronics and one simulator for the many-core architecture provided by ICT Chinese Academy of Science. Both simulators expose program execution time and power consumption as system-level metrics. More in detail, the ICT many-core architecture is a tiled MIMD machine composed of a bi-dimensional grid of homogeneous, general-purpose compute elements, called *tiles*. A 2D-mesh network architecture is used for connecting the cores to a non-shared memory sub-system.

- The DS2's STORM platform, a control-oriented architecture for powerline communication. The platform is used to model a PLC (Programmable Logic Controller) technology with several implementation choices. For this platform, both Ethernet QoS and internal communication are considered as metrics.

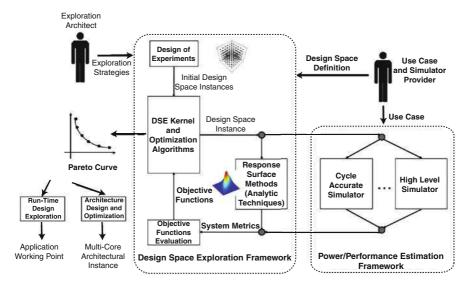

Given these target simulators, the MULTICUBE project developed a methodology, the multi-simulator based DSE approach shown in Fig. 1.2, to avoid potentially suboptimal DSE results and to speed up the DSE process by exploiting multiple platform simulators to run the application at different abstraction levels.

The main idea is to get timing information (in terms of processor cycles) for an application execution on an accurate simulator (e.g. TLM-based cycle-accurate simulator) and feed this timing information back to a high-level timed simulator (e.g. HLSim) to achieve validation across simulators. Then, the DSE is done with a large number of application runs by using faster higher-level simulators (e.g. HLSim) and then the derived interesting operating points (usually clusters of operating points) are refined by using more accurate simulators (e.g. TLM-based and/or cycle-accurate simulators). The proposed methodology exploiting the synergy of multiple simulators at several abstraction level can be used to further speed up the DSE process while guaranteeing good accuracy of the simulation results. The methodology has been validated for the MPEG4 encoder application provided by IMEC by using three different

Fig. 1.2 Overview of the multi-simulator based DSE design flow

simulators (Multicube SCoPE, HLSim and TLM-based simulator) interfaced with the two available DSE tools (modeFRONTIER and Multicube Explorer). Overall, an acceptable relative accuracy has been found [1] with a significant speed-up in simulation time.

#### 1.2.3 Response Surface Modeling Techniques

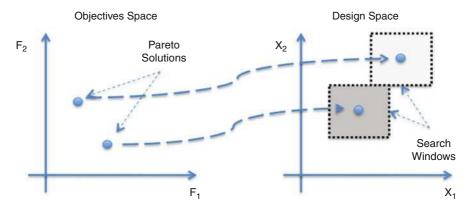

A set of analytical techniques (Response Surface Models, or RSMs) have been introduced to further speed up the design space exploration process (see Fig. 1.2). These techniques are key factors for developing a model of the system behavior without requiring the simulation of all the possible design configurations. RSMs have been proved to be an effective solution for analytically predicting the behavior of the system in terms of the target metrics without resorting to the system simulation.

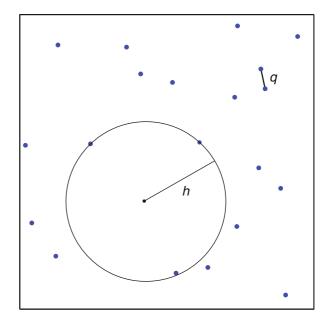

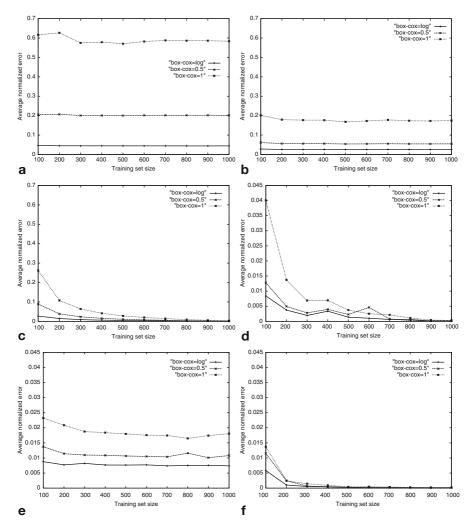

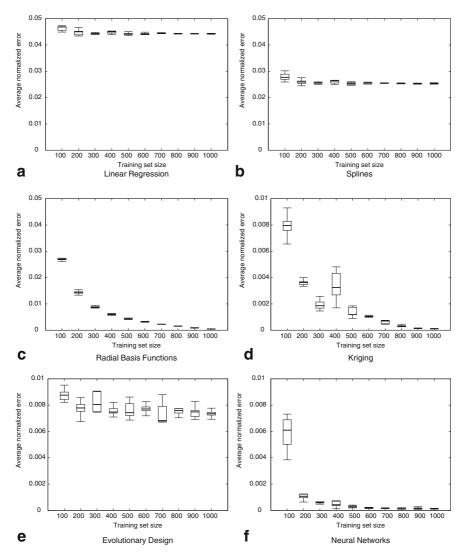

Response Surface Modeling (RSM) techniques leverage the analytical dependence between several design parameters and one or more response variables by adopting both interpolation and regression techniques. The basic principle is to use a set of simulations either generated ad hoc by a Design of Experiment (DoE) phase or obtained by an exploration strategy previously applied to the design space, in order to obtain a response model of the system behavior. In the project, several RSM techniques have been implemented, among them Radial Basis Functions [3], Linear Regression [4, 5], Artificial Neural Networks [2] and Shepard's Interpolation. Every RSM presented dramatic speed-up in terms of evaluation. Besides, it has been found that a peculiar mathematical transformation of input training set known as Box-Cox  $\lambda$  transform [4] has a great impact on the prediction accuracy. A sub-set of the above analytical techniques has been implemented and integrated in the MULTICUBE open-source tool while another sub-set was already available in the modeFRON-TIER tool. RSM techniques for DSE are described in more detail in Chap. 4 of this book.

#### 1.2.4 Run-Time Resource Management

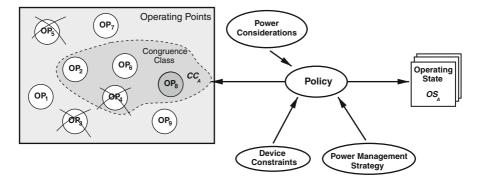

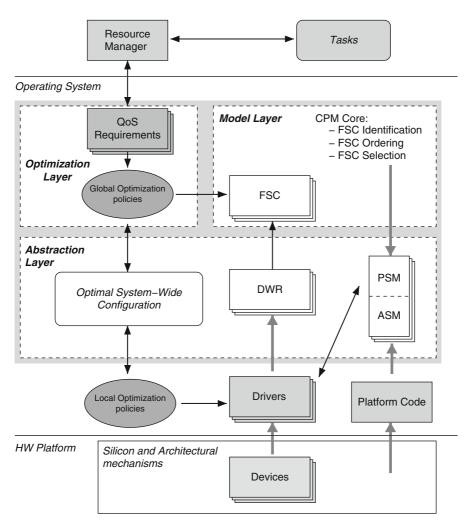

The MULTICUBE design flow has been built to provide not only design-time support but also run-time support. In this scenario, at design time, the multi-objective design space exploration framework generates a set of Pareto-optimal operating points (for each application) annotated with system metrics like energy consumption, execution time, and memory and communication bandwidth values. The Pareto set can then be exploited at run time (while the application(s) are running) to optimise the overall system behavior (see Fig. 1.3). Specifically a separate Run-time Resource Manager (RRM) has been developed to exploit the set of operating points derived at designtime for all applications to steer the overall system behavior according to the imposed user requirements (quality, power, performance, etc.). The goal of the RRM is to use the Pareto information given by the design-time exploration on the operating points (of all applications) to make at run-time a decision to allocate the system resources to active applications based on the user requirements in terms of Quality of Service. Run-time Resource Management techniques are described in Chap. 5, while some more general concepts about resources management at the Operating System layer are presented in Chap. 6.

Fig. 1.3 Overview of the run-time support

#### **1.3 Design Tool Integration based on the MULTICUBE XML Interface**

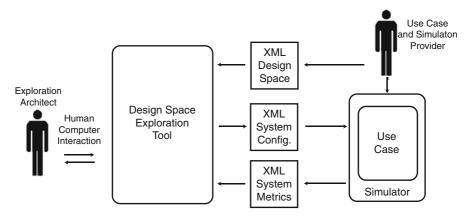

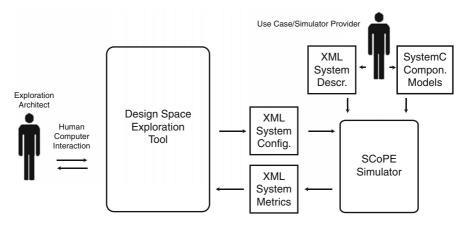

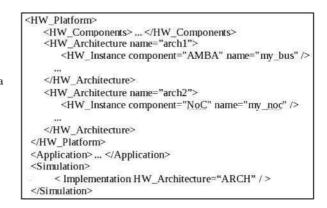

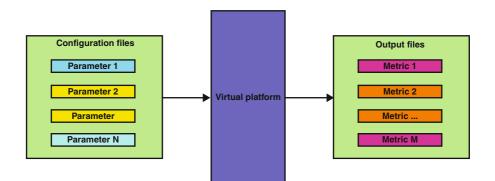

Strategic importance from the point of view of the MULTICUBE exploitation is associated to the common XML Tool Interface Specification for the integration of the different tools and use cases. The common interface enabled the independent development of software modules and a seamless integration of design tools and data structures into a common design environment. The specification is defined in terms of XML, a widely used standard notation. To introduce the notation, let us highlight that, in the MULTICUBE design flow, there are two types of user agents to interact with the framework: the *use case and simulator provider* and the *exploration architect*. The simulator is the executable model of the use case and it is a single executable file (binary or script) which interacts with the DSE tool to provide the value of the estimated metrics, given an input configuration. The MULTICUBE project addressed the formalization of the interaction between the simulator and the DSE tools, that is essentially an automatic program-to-program interaction (see Fig. 1.4):

- 1. The DSE tool generates one feasible system configuration whose system metrics should be estimated by the simulator.

- 2. The simulator generates a set of system metrics to be fed back to the DSE tool.

To automatically link the use case simulator to the DSE tool, a design space definition file should be released by the use case and simulator provider together with the executable model of the use case (simulator). This file describes the set of configurable parameters of the simulator, their values range and the set of evaluation metrics that can be estimated by the simulator. This file describes also how to invoke the simulator as well as an optional set of rules with which the generated parameter values should be compliant. The rules are only used by the exploration tool to avoid the generation of invalid or unfeasible solutions during the automated exploration

Fig. 1.4 Overview of the tool interfaces via XML

process. The above interaction has been addressed by creating a specification based on an XML based grammar for writing both the design space definition file and the simulator interface files. The grammar is defined by using the XSD schema language.

#### 1.3.1 Design Space Definition

The definition of the design space is done by using an XML file that is composed of a preamble, which defines the name-space and supported version. The current release of the MULTICUBE XML interface specification is R1.4 and it is available on MULTICUBE web page (www.multicube.eu).

```

1 <?xml version="1.0" encoding="UTF-8"?>

2 <design_space xmlns="http://www.multicube.eu/" version="1.4">

3 <simulator> ... </simulator>

4 <parameters> ... </parameters>

5 <system_metrics> ... </system_metrics>

6 <rules> ... </rules>

7 </design_space>

```

The remaining part of the file describes the simulator invocation method (<simulator> tag), the set of parameters of the simulator which can be configured (<parameters> tag), the system metrics which can be estimated by the simulator (<system\_metrics> tag) and the rules which have to be taken into account by the exploration engine to generate the feasible configurations.

#### 1.3.1.1 Simulator Invocation

The <simulator\_executable> marker is used for specifying the complete path name of the executable:

```

1 <simulator>

2 <simulator_executable path="/path/my_simulator_executable" />

3 </simulator>

```

#### **1.3.1.2** Parameters Definition

The <parameters> tag is used by the use case and simulator provider to specify the names, the types and the ranges of the parameters that can be explored by the DSE tool. The section contains a list of <parameter> markers:

```

1

<parameter>

<parameter name="ill_cache_block_size_bytes"</pre>

2

3

description="..." type="exp2" min="8" max="64"/>

4

<parameter name="bpred" description="b.p. type" type="string">

5

<item value="nottaken"/>

<item value="taken"/>

6

<item value="perfect"/>

7

<item value="bimod"/>

8

```

For each parameter an unique name must be provided. The parameters types can be divided into two categories: scalar types, variable vector types. Scalar types can be **integer**, **boolean** (a subset of integers), **exp2** (progression of power of 2) and **string** (a type for defining categorical variables). Vector types can be used to describe combination of boolean values (*on-off-masks* or *permutations*). In particular, on-off-masks can be useful for describing the space of active processors while permutations can be used to describe the mapping of tasks on the available processors.

#### 1.3.1.3 System Metrics Definition

The <system\_metrics> section is used by the use case and simulator provider to specify the names, the types and the units of the system metrics that can be estimated by the simulator:

```

1 <system_metrics>

2 <system_metric name="cycles" type="integer" unit="cycles" />

3 <system_metric name="instructions" type="integer" unit="insts"/>

4 <system_metric name="powerconsumption" type="float" unit="W" />

5 <system_metric name="area" type="float" unit="mm2" />

6 </system_metrics>

```

A complex expression of the system metrics can be defined as one of the objective of the exploration algorithm.

#### 1.3.2 Simulator Input/Output XML Interface

The simulator input file contains a preamble and a sequence of parameter> sections where, for each parameter, the name and the value is specified. The number of parameter> sections and the name of the parameters should be the same as defined in the XML Design Space description file. Similarly the simulator output file contains a preamble and a sequence of sections where, for each metric, the name and the value is specified. Besides, an appropriate error reporting syntax has been described in the specification.

#### 1.4 Advantages of Automatic DSE

The procedure to assess the benefits of the introduction of an Automatic Design Space Exploration (or Optimization Methodology) has to address, not only the final objective quality and the improvement of the target design but also the impact of such a technology on the entire design process of embedded computing platforms. The benefits on the process can be measurable and tangible like the reduction of the overall design process lead time, and qualitative or intangible like the streamlining and the reduction of human error prone repetitive operations. These benefits are particularly valuable for design problems where the number of configuration parameters to be explored is quite large, like in MP-SoC designs.

The specific design process activities can be analyzed and classified to measure the various performance indicators. In a general way, we can consider the following steps as the basis for any manual design space exploration or optimization process:

- Model Setup: preparation of an initial model of the virtual platform;

- Simulation: execution of the simulation of the executable model with a single configuration of parameters;

- Results Assessment: meaningful measures are extracted and compared with historical and expected ones;

- Model Edit: the model is manually modified and resubmitted for a further analysis.

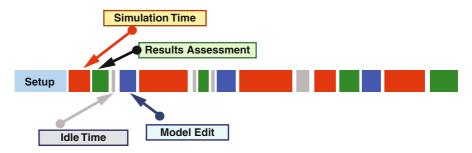

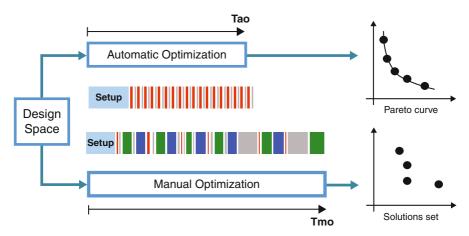

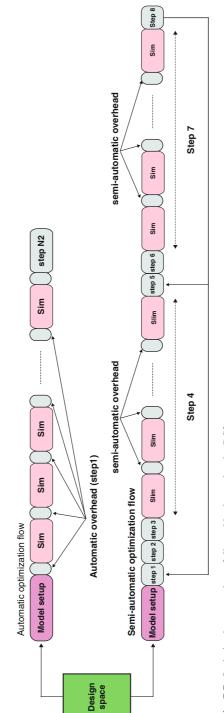

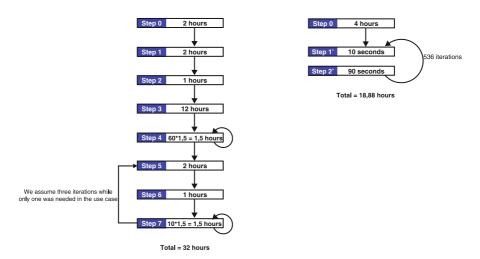

Figure 1.5 represents the steps of a typical manual exploration procedure. In a manual approach, the exploration of the design space is done by subjective assumptions of the human designer, who will modify at most one or two parameters per evaluation. The model simulation corresponds to a minimal portion of the time of the whole exploration procedure. A large amount of time is spent by the designer editing the configuration parameters and analyzing the results. There is also an Idle Time (from the point of view of the use of computational resources) that lasts from the end of the simulation till the moment in which the human operator is informed about it and handles the simulation tools to get the results. This idle time can be very short if the designer is immediately informed about the end of the simulation or can be significant if the designer is not on duty.

The automatic design space exploration process can be defined by identifying the following basic steps:

• Model setup: the model must be correctly parameterized in order to be easily managed by the automatic exploration tools;

Fig. 1.5 Manual exploration procedure

- Simulation time: the simulation of the executable model with a single configuration of parameters is carried out (this phase is similar to the one that is performed with the manual approach);

- Automatic DSE overhead: this step includes the automatic assessment of the results, the automatic selection of the next configuration to be simulated (model selection) and the data transfer operations between the simulator and the design space exploration tool and its corresponding storage into the design database.

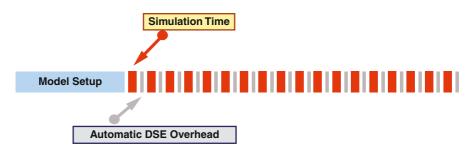

Figure 1.6 describes the automatic exploration procedure. The exploration of the design space is done by numerical/objective criteria. The Design Space Exploration tool (or "exploration engine") will change systematically all the parameters for each analysis and will evaluate the best result by adopting numerical formulas. The setup phase can be considerably longer than the set up of a manual exploration, since it usually requires an extended definition of the model to interact with the exploration engine, the definition of the proper optimization strategy and the definition of the multi-objective goals to be achieved. However, after that, the model evaluations (Simulation Time) is similar to the simulation time required in the manual approach, except for a further step (Automatic DSE overhead) that involves the automatic assessment of the results, the automatic selection of the next configuration to be simulated (model selection) and the time spent for data communication and storage.

Based on the past experience of ESTECO to deal with industrial customers, even if a single evaluation takes just a few seconds, it is difficult that a designer using a manual optimization procedure can evaluate more than seven designs of medium complexity within one hour. The designer has to go through all steps described before, editing the configuration parameters, running the analysis, reading and analyzing the results, etc. In this case, it is expected that in one person-day (10 h), the designer can run at most 70 designs. For the same problem, experience shows that an automatic approach can handle something like 600 designs per hour, which means about 14,400 designs per day. Since the automatic procedure can work 24 four hours a day, including weekends and holidays, the advantages of the automatic procedure are very clear.

However, there are other advantages of the automatic exploration procedure. In the automatic exploration, all data concerning previous evaluations are always stored in a

Fig. 1.6 Automatic exploration procedure

structured database. The designer, not only will not be stuck on repetitive operations, but can focus his/her attention (and profit from his/her experience) in analyzing the designs database in a statistical manner.

Moreover, the automatic exploration is driven by an optimization engine based on several optimization algorithms, whereas the manual exploration is based on designer ability and experience to assess the results and to move towards the next instance of the model to be simulated.

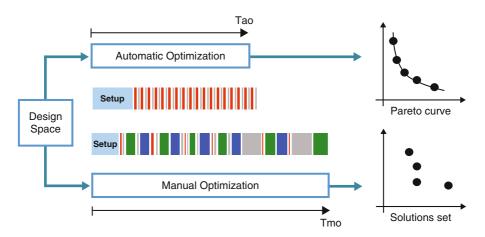

Figure 1.7 presents a direct comparison between manual and automatic optimization. The global lead time (Tmo) of the manual design exploration is determined by the number of manual iterations that are needed to reach the expected design improvement. The global lead time (Tao) in the automatic procedure case is dominated by the effective simulation time needed by the optimization strategy, given the overhead due to the automatic extraction and processing of measures, and communication latencies between the design exploration tool and the simulator. Another difference concerns the type of results produced by both types of optimization: the automatic optimization generates a set of designs that are likely to belong to the Pareto front, while the manual optimization generates just a set of designs that the designer found interesting. On the average, the manual approach suffers from the fact that it is affected by personal views, experience and background. This decreases the likelihood of finding points that belong to the Pareto front.

The reduction of the lead time of the design exploration phase is frequently reflected in the reduction of the overall time-to-market for the final product. The lead time must be always considered as one of the objectives for the introduction of the automatic exploration methodologies in industrial design processes, together with the more specific product related ones.

The general automatic DSE procedure described in this Chapter represented the common basis for the validation of each of the use cases of the MULTICUBE project. In order to apply this procedure, the responsible for each of the use cases adapted

Fig. 1.7 Comparison between manual and automatic exploration procedures

however the general procedure to the specificities of its particular application and context, but without modifying the aim and the general steps described above.

# 1.5 Conclusions

In this chapter, the main structure of the MULTICUBE design flow has been introduced to be detailed in the next chapters. The founding principles of the proposed structure are meant to cover the gap between the system-level specification and the definition of the optimal application-specific architecture. The flow is based on the interaction of two frameworks to be used at design time: the Design Space Exploration Framework, an architecture exploration set of tools, and the Power/Performance Estimation Framework, a set of modeling and simulation tools operating at several levels of abstraction. The DSE flow also includes a Run-time Resource Manager able to select at run-time the best design alternatives in terms of power/performance trade-offs generated during the design-time exploration phase.

### References

- Avasare, P., Vanmeerbeeck, G., Kavka, C., Mariani, G.: Practical approach to design space explorations using simulators at multiple abstraction levels. In: Design Automation Conference (DAC) User Track Sessions. Anaheim, USA (2010)

- 2. Bishop, C.: Neural Networks for Pattern Recognition. Oxford University Press (2002)

- Joseph, P., Vaswani, K., Thazhuthaveetil, M.: Construction and use of linear regression models for processor performance analysis. High-Performance Computer Architecture, 2006. The Twelfth International Symposium on pp. 99–108 (2006)

- Joseph, P.J., Vaswani, K., Thazhuthaveetil, M.J.: A predictive performance model for superscalar processors. In: MICRO 39: Proceedings of the 39th Annual IEEE/ACM International Symposium on Microarchitecture, pp. 161–170. IEEE Computer Society, Washington, DC, USA (2006). DOI http://dx.doi.org/10.1109/MICRO.2006.6

- Lee, B.C., Brooks, D.M.: Accurate and efficient regression modeling for microarchitectural performance and power prediction. Proceedings of the 12th international conference on Architectural support for programming languages and operating systems 40(5), 185–194 (2006). DOI http://doi.acm.org/10.1145/1168917.1168881

- Mei, B., Sutter, B., Aa, T., Wouters, M., Kanstein, A., Dupont, S.: Implementation of a coarsegrained reconfigurable media processor for avc decoder. J. Signal Process. Syst. 51(3), 225–243 (2008). DOI http://dx.doi.org/10.1007/s11265-007-0152-8

- Posadas, H., Castillo, J., Quijano, D., Fernandez, V., Villar, E., Martinez, M.: SystemC platform modeling for behavioral simulation and performance estimation of embedded systems. Behavioral Modeling for Embedded Systems and Technologies: Applications for Design and Implementation pp. 219–243 (2010)

# Chapter 2 M3-SCoPE: Performance Modeling of Multi-Processor Embedded Systems for Fast Design Space Exploration

Hector Posadas, Sara Real, and Eugenio Villar

**Abstract** Design Space Exploration for complex, multi-processor embedded systems demands new modeling, simulation, performance estimation tools and design methodologies. Recently approved as IEEE 1666 standard, SystemC has proven to be a powerful language for system modeling and simulation. In this chapter, M3-SCoPE, a SystemC framework for platform modeling, SW source-code behavioral simulation and performance estimation of multi-processor embedded systems is presented. Using M3-SCoPE, the application SW running on the different processors of the platform can be simulated efficiently in close interaction with the rest of the platform components. In this way, fast and sufficiently accurate performance metrics of the system are obtained. These metrics are then delivered to the DSE tools to evaluate the quality of the different configurations in order to select the best ones.

# 2.1 Introduction

System exploration with an optimum trade-off between performance and cost requires analyzing the performance of a large number of system configurations with a wide set of parameters, such as number and type of processors, memory architecture and sizing, mapping of SW tasks and suitability of communication infrastructure.

System simulation is a key design task widely used for design verification and evaluation. The main role of system simulation in embedded system design is to ensure the functional correctness of the design at the different abstraction levels. In Design Space Exploration (DSE), system simulation is used for performance analysis, providing to the exploration tool the required metrics such as delays, throughput, utilization rates, bandwidths, etc. Power consumption is becoming an additional, increasingly important metric to be estimated.

H. Posadas (🖂)

University of Cantabria, Santander, Spain e-mail: posadash@teisa.unican.es

Design Space Exploration requires auxiliary tools to provide the exploration engines with the metrics needed to evaluate the different system configurations. For evaluating complex HW/SW MPSoC systems [30], very flexible evaluation mechanisms are required. Static mechanisms are adequate to evaluate the effect of different parameter values in well known architectures. The analysis of internal processor components or cache configurations are examples in that context. However, to evaluate unknown or very flexible architectures, analysis methods based on mathematical equations are not applicable. Evaluation mechanisms based on simulation are then selected.

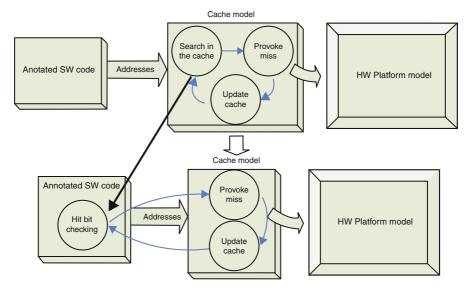

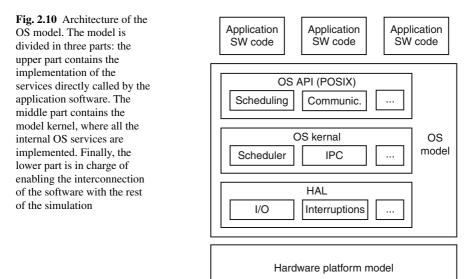

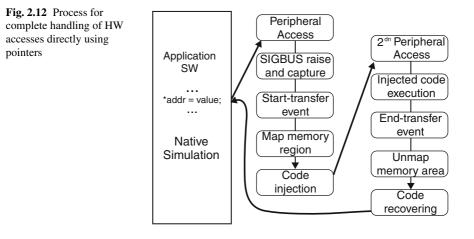

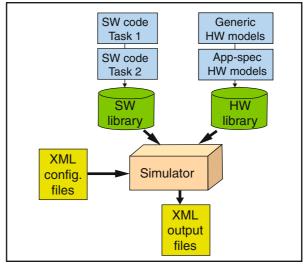

Simulation environments for DSE have to overcome several challenges. Mainly, these simulations require very fast speeds, considering the large amount of points to be simulated. Thus, modeling techniques need to evaluate all the configurations selected by the DSE tools without provoking additional delays. While HW simulation can be performed at different abstraction levels using appropriate languages such as VHDL, Verilog, System-Verilog and SystemC [58], efficient and sufficiently accurate SW simulation requires additional efforts. Electronic System Level (ESL) [4] has been proposed as an adequate abstraction level for complete system simulations [38]. At this level, there are three main methodologies used for SW simulation: Instruction-Set Simulation (ISS), virtualization with binary translation and native co-simulation.