# Fei Yuan

# CMOS Circuits for Passive Wireless Microsystems

# CMOS Circuits for Passive Wireless Microsystems

Fei Yuan

# CMOS Circuits for Passive Wireless Microsystems

Fei Yuan Department of Electrical and Computer Engineering Ryerson University 350 Victoria Street Toronto, Ontario, Canada M5B 2K3 Email: fyuan@ee.ryerson.ca

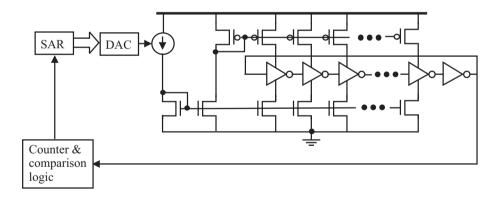

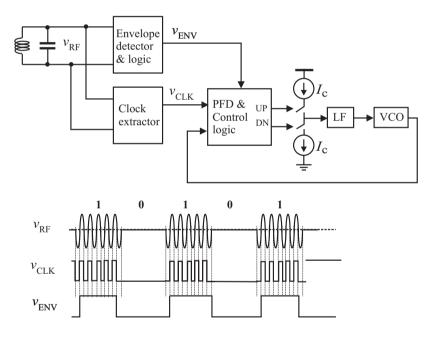

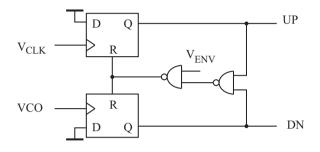

#### ISBN 978-1-4419-7679-6 e-ISBN 978-1-4419-7680-2 DOI 10.1007/978-1-4419-7680-2 Springer New York Dordrecht Heidelberg London

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

This book is dedicated to Jing

# Preface

Passive wireless microsystems harvest their operational power from radiofrequency waves or other energy sources such as vibration and solar. The absence of bulky batteries not only minimizes the physical dimension and implementation cost of these microsystems, it also removes the need for maintenance. As a result, passive wireless microsystems can be embedded in products or implanted in living bodies permanently to provide the unique identification of the products and living bodies in which they reside, to carry out precision measurement of the parameters of the products or living bodies, or to perform micron-scale control actions that otherwise cannot be performed.

Attributive to their small, wireless accessibility and programmability, and maintenance-free operation, passive wireless microsystems have found a broad range of emerging applications in biomedical implants such as cochlear implants and retinal prosthetic implants, swallowable capsule endoscopy, multisite pressure sensors for wireless arterial flow characterization, embedded micro-strain sensors for product performance and safety monitoring, wireless temperature sensors for human body and environmental monitoring, and radio-frequency identification tags for logistic automation, to name a few. Passive wireless microsystems are also a viable choice for low-cost high-security product authentication to replace existing product authentication methods such as holograms, water-marks, invisible barcodes, security threads, chemical, and DNA markers that are often too costly to be used for general goods.

This book provides a comprehensive treatment of CMOS circuits for passive wireless microsystems. It focuses on the design of the key blocks of passive wireless microsystems. These blocks include radio-frequency power harvesters, demodulators, low-power precision voltage references, system clock generation and calibration, and ultra-low power analog-to-digital converters. The materials presented in the book are compiled from recently published work in this fast-evolving field. The book is organized as the follows :

Chapter 1 provides an overview of passive wireless microsystems and highlights the key considerations and design challenges of these microsystems.

Chapter 2 begins with a brief examination of the parameters that characterize the performance of radio-frequency power harvesters. Our focus is then turned to power-matching and gain-boosting using LC networks and step-up transformers to increase the voltage at the input of voltage multipliers so as to boost their power efficiency. An emphasis is given to the power efficiency of the power-matching and gain-boosting network itself as the overall power efficiency of a power harvester is determined by the power efficiency of its power-matching and gain-boosting network, that of its voltage multiplier, and the efficiency of its antenna. The design of voltage multipliers for passive wireless microsystems is then investigated in detail.

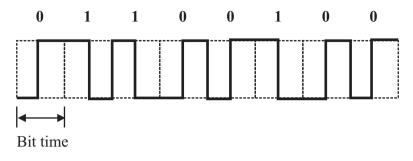

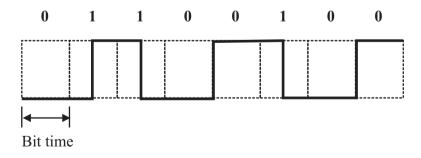

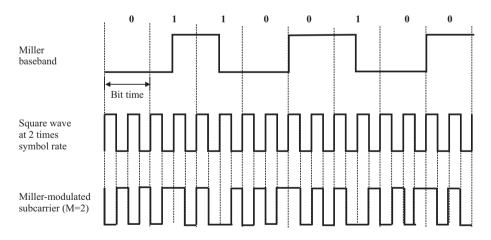

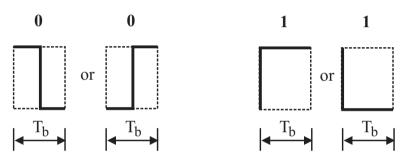

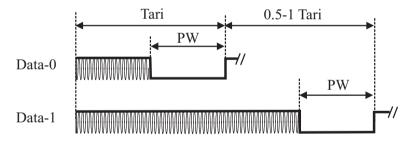

Chapter 3 examines the pros and cons of commonly used data encoding schemes for wireless communications and explores their suitability for passive wireless microsystems. Non-return-to-zero encoding popular in high-speed data communications over wire channels is studied first. It is followed by an investigation of return-to-zero encoding. Manchester encoding and its characteristics are examined. Miller encoding and Miller-modulated sub-carrier encoding are also studied. An emphasis is given to the distinct characteristics of Miller-modulated sub-carrier encoding and its usefulness in encoding data to be backscattered to base stations. FM0 encoding and pulse interval encoding that are widely used in radio-frequency identification systems are then explored. The chapter is concluded with a comparison of the performance of the encoding schemes studied in the chapter.

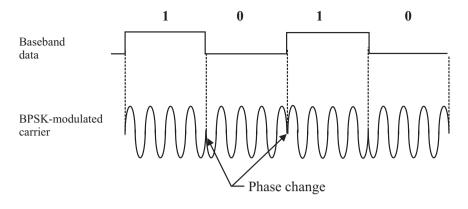

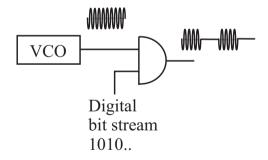

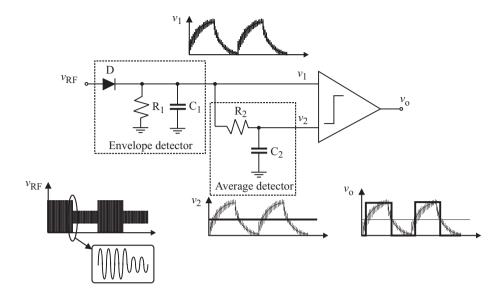

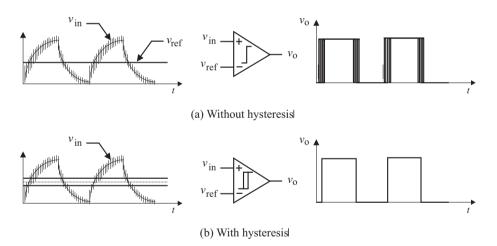

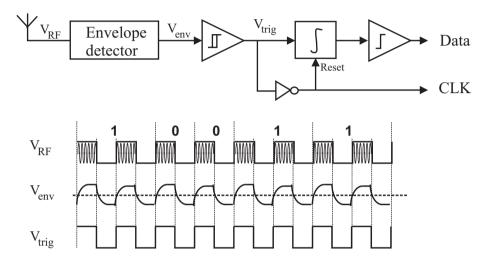

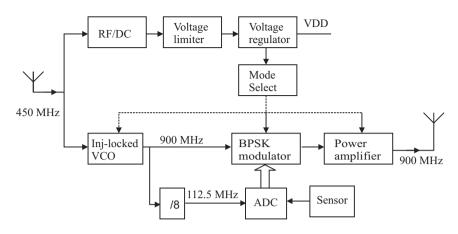

Chapter 4 deals with modulation and demodulation. The chapter starts with a close look at the three basic modulation schemes, namely amplitude-shift-keying (ASK), frequency-shift-keying (FSK), and phase-shift-keying (PSK). The pros and cons of these modulation schemes are studied and compared in detail. ASK modulators and demodulators for passive wireless microsystems are investigated. A significant portion of this section is devoted to CMOS circuits for ASK demodulators. FSK modulators and demodulators are then examined in detail. An in-depth study of the advantages and design constraints of FSK demodulators for biomedical implants is provided. The advantages of PSK modulation over FSK modulation in biomedical implants and the design challenges encountered are investigated. Both coherent and non-coherent demodulation of BPSK-modulated signals are presented. The performance of recently published ASK, FSK, and PSK demodulators for passive wireless microsystems is compared.

Chapter 5 is concerned with temperature-independent precision voltage references for passive wireless microsystems. The chapter starts with a brief examination of the figure-of-merits that characterize the performance of voltage references. It is followed by a detailed investigation of the temperaturedependent characteristics of semiconductors. First-order voltage references are studied in a great detail. An in-depth investigation of high-order voltage references follows. The performance of first-order voltage reference and that of high-order voltage references are compared. Ultra low-power voltage references where devices operate in weak inversion are also studied.

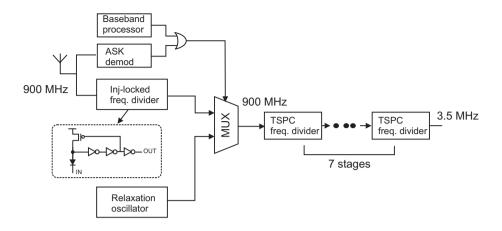

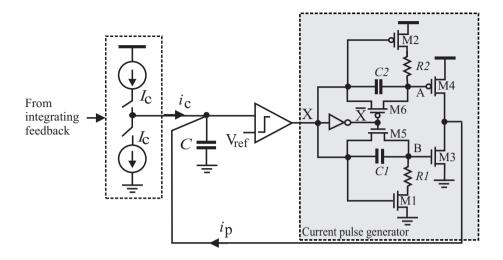

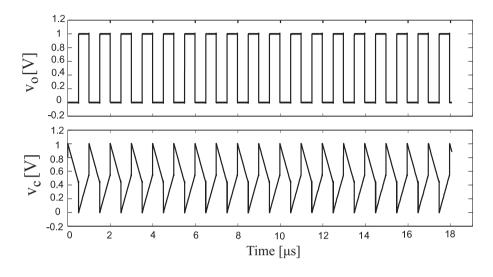

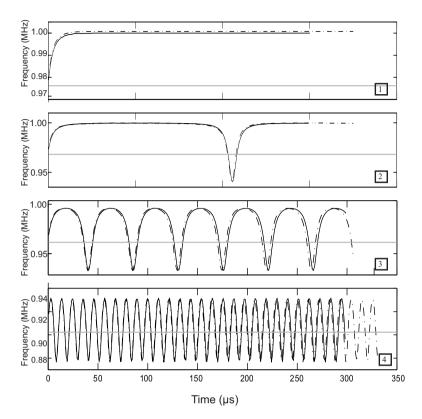

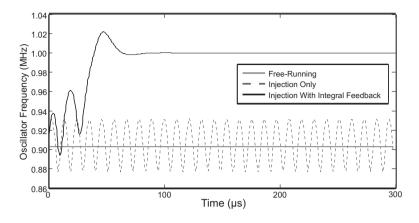

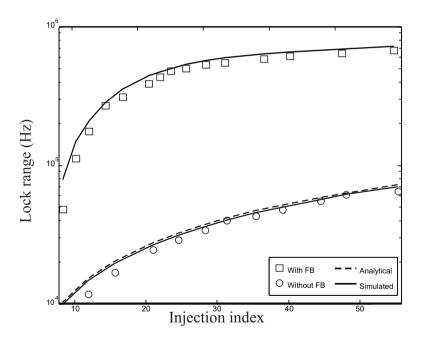

Chapter 6 deals with the generation and calibration of the system clock of passive wireless microsystems. The generation of the system clock of passive wireless microsystems directly from the carrier of the received RF signal is investigated first. It is followed by a close look at the generation of the system clock from the envelope of the received RF signal. Direct generation of the system clock from the received RF signal using injection-locked frequency division to take the advantage of its low power consumption and high frequency accuracy is investigated. The system clock of passive wireless microsystems can also be generated using a local oscillator directly. Since the frequency of the local oscillator is subject to the effect of process, voltage, and temperature (PVT) variations, calibrating the frequency of the local oscillator prior to any data communications becomes indispensable. Calibration of the frequency of the system clock using injection-locking with the carrier as the injection signal is investigated first. Frequency calibration of the local oscillator using digital trimming techniques is followed. Our focus is then turned to the presentation of frequency calibration using either phase-locked loops or frequency-locked loops. The chapter further explores the calibration of the frequency of the local oscillator using injection-locking with the envelope as the injection-locking signal. Integrating feedback is employed to increase the lock range of frequency calibration using injection-locking with the envelope as the injection-locking signal.

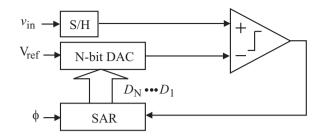

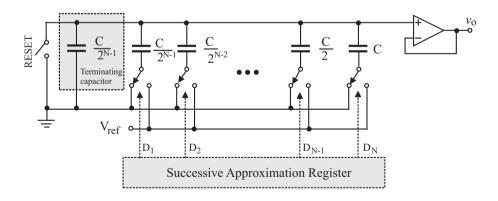

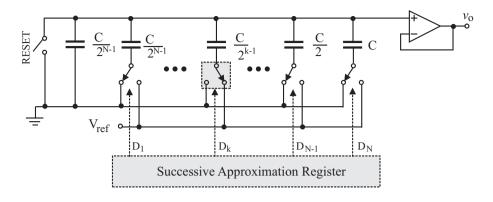

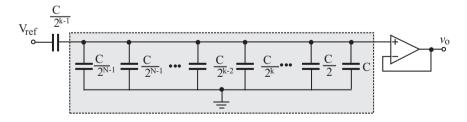

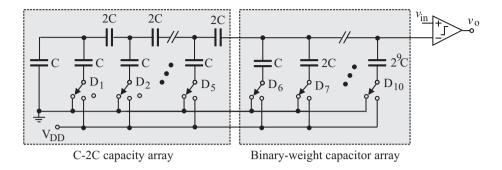

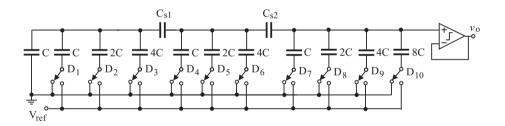

Chapter 7 focuses on the architecture and design of low-power analog-todigital converters (ADCs). The fundamentals of ADCs are studied first. It is followed by a close examination of the figure-of-merits used to quantify the performance of ADCs. Integrating ADCs are investigated. Both single-slope and dual-slope integrating ADCs, and their advantages and disadvantages are examined and compared. The design of oscillation-based ADCs for temperature measurement is explored. A close attention is paid to both relaxation oscillator and ring oscillator based temperature ADCs. Time-to-digital converter based ADCs for temperature measurement is also investigated. As compared with oscillator-based temperature ADCs, these ADCs have the advantage of low power consumption. The chapter then moves on to investigate frequencyto-digital based ADCs for temperature measurement. Charge redistribution successive approximation ADCs are investigated in a great detail. Our focus is given to the design of charge-scaling digital-to-analog converters (DACs) used in charge redistribution successive approximation ADCs. Three configurations of charging-scaling capacitor arrays, namely single-stage binary-weighted capacitor arrays, two-stage binary-weighted capacitor arrays, and C-2C capacitor arrays are studied in detail and their pros and cons are examined.

Since the objective of the book is to provide readers with the state-of-the-art of CMOS circuits for passive wireless microsystems, the details of the operation of semiconductor devices and basic microelectronic circuits are omitted due to a space constraint. Readers are assumed to have the basic knowledge of electrical networks, semiconductor devices, microelectronic circuits, signals and systems, and digital communications. A rich collection of recently published work on passive wireless microsystems is provided at the end of the book for readers to seek further information on the subjects.

Although an immense amount of effort was made in preparation of the manuscript, flaws and errors will still exist due to erring human nature and the limited knowledge of the author on the subjects. Suggestions and corrections from readers will be gratefully appreciated by the author.

Fei Yuan

July 2010

## Acknowledgments

The author is grateful to the Natural Science and Engineering Research Council of Canada, Ryerson University, CMC Microsystems, and other research partners for their support to our research. The support from the Department of Electrical and Computer Engineering of Ryerson University where I introduced and taught graduate courses EE8501 (CMOS analog integrated circuits), EE8502 (VLSI systems), EE8503 (VLSI circuits for data communications), and EE8604 (Special topics on electrical engineerings - CMOS circuits for wireless communications) is gratefully acknowledged. The students of these classes constantly motivated me to explore new things in the field of microelectronics that is mature and yet fast-evolving. Special thanks go to my graduate students, both past and present, for fruitful discussion in our research meetings where many new topologies and configurations emerged. Mr. Jason Naughton, our System Administrator, deserves a special thank-you for keeping CAD tools up-to-date and running all the time.

The editorial staff of Springer, especially Mr. Charles Glaser, Senior Acquisitions Editor, have been warmly supportive from the invitation of the book proposal to the publish of the book. This is the 4th book that I have published with Springer. It has been a wonderful experience of working with Springer.

Finally and most importantly, this book could not have been possible without the unconditional support of my family. I am indebted to my wife Jing for her love, patient, and understanding. I also want to thank our daughter and son, Michelle and Jonathan, for the joy and happiness they have brought to our life, and for their forbearance of my bad temper due to the stress of writing and proof-reading.

# Contents

| De              | dicat                                              | ion                 |                                              | V   |

|-----------------|----------------------------------------------------|---------------------|----------------------------------------------|-----|

| Pre             | eface                                              |                     |                                              | vii |

| Acknowledgments |                                                    |                     | xi                                           |     |

| 1.              | PASSIVE WIRELESS MICROSYSTEMS                      |                     |                                              | 1   |

|                 | 1.1                                                | The Sp              | pectrum                                      |     |

|                 | 1.2                                                | The Challenges      |                                              | 2   |

|                 |                                                    | 1.2.1               | Efficiency of Radio-Frequency Power Harvest  | 3   |

|                 |                                                    | 1.2.2               | Fluctuating Supply Voltage                   | 3   |

|                 |                                                    | 1.2.3               | Sensitivity to Changing Environment          | 4   |

|                 |                                                    | 1.2.4               | Precision Voltage References                 | 4   |

|                 |                                                    | 1.2.5               | Ultra-Low Power Analog-to-Digital Converters | 5   |

|                 |                                                    | 1.2.6               | Encryption and Authentication                | 5   |

|                 |                                                    | 1.2.7               | Signal Collision                             | 5   |

|                 |                                                    | 1.2.8               | Dimension of Antennas                        | 6   |

| 2.              | RADIO-FREQUENCY POWER HARVEST                      |                     |                                              | 7   |

|                 | 2.1 Characterization of Radio-Frequency Power Harv |                     |                                              | 8   |

|                 |                                                    | 2.1.1               | Power Matching                               | 8   |

|                 |                                                    | 2.1.2               | Power Efficiency                             | 10  |

|                 | 2.2                                                | Voltage Multipliers |                                              | 11  |

|                 |                                                    | 2.2.1               | Voltage Doubler                              | 12  |

|                 |                                                    | 2.2.2               | Cockcroft-Walton Voltage Multiplier          | 13  |

|                 |                                                    | 2.2.3               | Dickson Voltage Multipliers                  | 13  |

|                 |                                                    | 2.2.4               | Modified Dickson Voltage Multipliers         | 16  |

|                 |                                                    | 2.2.5               | Mandal-Sarpeshkar Voltage Multiplier         | 17  |

|                 |                                                    | 2.2.6               | Voltage Multiplier with $V_T$ -Cancellation  | 18  |

|                 |                                                    | 2.2.7               | Bergeret Voltage Multiplier                  | 20  |

|    | 2.3           | Power  | -Matching and Gain-Boosting Using LC Tanks     | 21  |

|----|---------------|--------|------------------------------------------------|-----|

|    | 2.4           | Power  | -Matching and Gain-Boosting Using Transformers | 32  |

|    | 2.5           | Chapte | er summary                                     | 45  |

| 3. | DATA ENCODING |        |                                                | 49  |

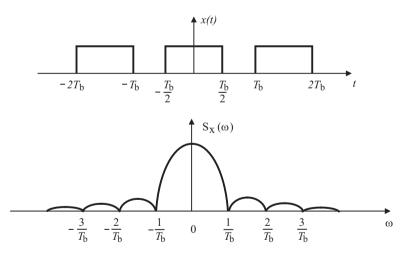

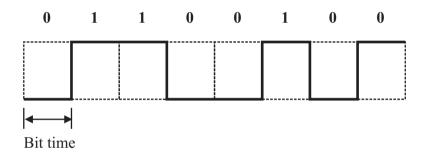

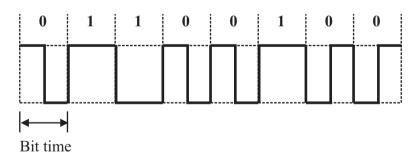

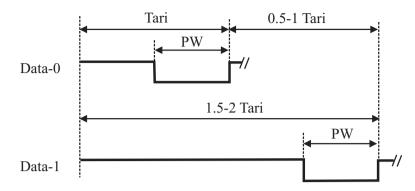

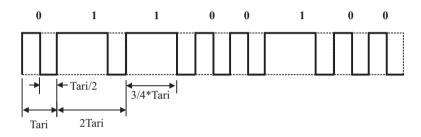

|    | 3.1           | Non-R  | Return-to-Zero Encoding                        | 51  |

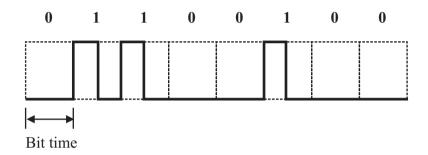

|    | 3.2           | Return | n-to-Zero Encoding                             | 52  |

|    | 3.3           | Manch  | nester Encoding                                | 53  |

|    | 3.4           | Miller | Encoding                                       | 54  |

|    | 3.5           | Miller | -Modulated Sub-carrier Encoding                | 55  |

|    | 3.6           |        | Encoding                                       | 56  |

|    | 3.7           |        | Interval Encoding                              | 56  |

|    | 3.8           |        | er Summary                                     | 57  |

| 4. | MO            | DULAT  | ORS AND DEMODULATORS                           | 61  |

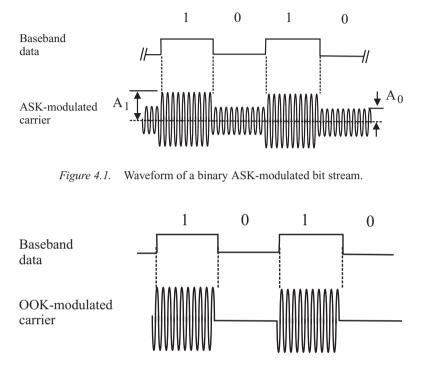

|    | 4.1           | Basic  | Modulation Schemes                             | 62  |

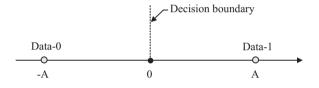

|    |               | 4.1.1  | Amplitude Shift Keying                         | 62  |

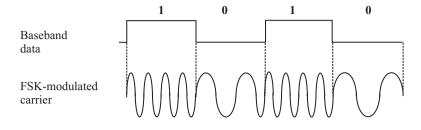

|    |               |        | Frequency Shift Keying                         | 64  |

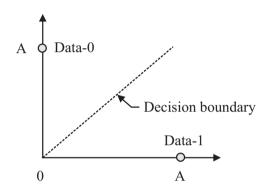

|    |               | 4.1.3  | Phase Shift Keying                             | 66  |

|    | 4.2           | ASK N  | Modulators and Demodulators                    | 66  |

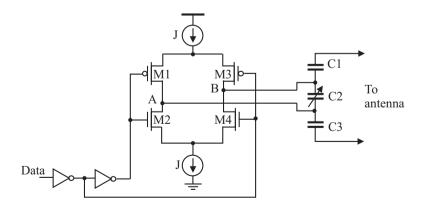

|    |               | 4.2.1  | ASK Modulators                                 | 67  |

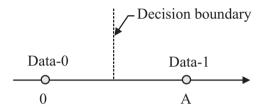

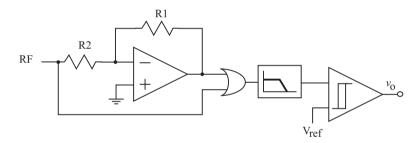

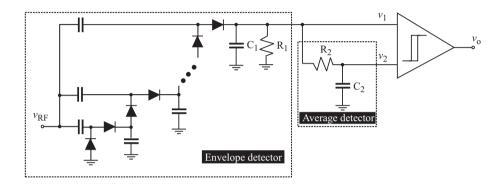

|    |               | 4.2.2  | Classification of ASK Demodulators             | 67  |

|    |               | 4.2.3  | Design Challenges of ASK Demodulators          | 68  |

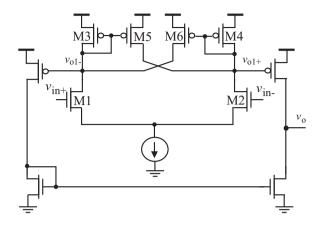

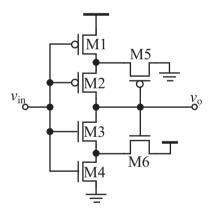

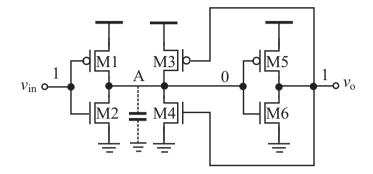

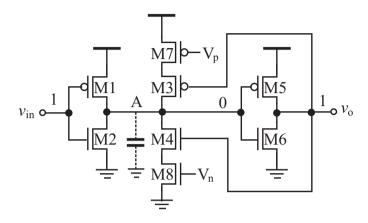

|    |               | 4.2.4  | Voltage-Mode ASK Demodulators                  | 78  |

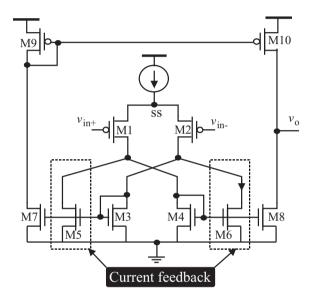

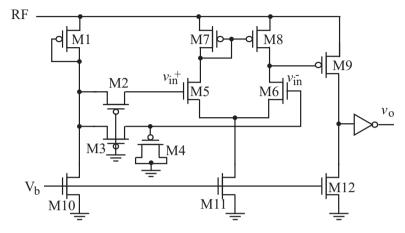

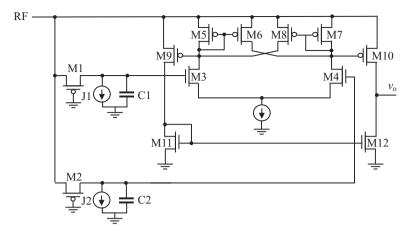

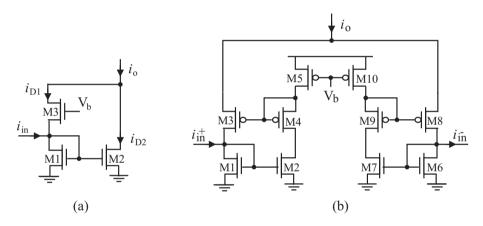

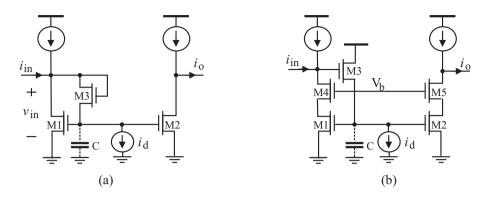

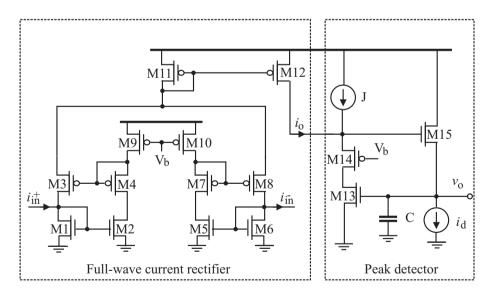

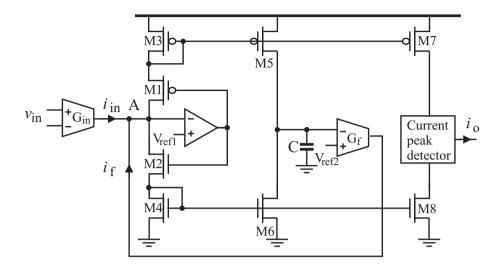

|    |               | 4.2.5  | Current-Mode ASK Demodulators                  | 85  |

|    |               | 4.2.6  | Mixed-Mode ASK Demodulators                    | 87  |

|    |               | 4.2.7  | Performance Comparison of ASK Demodulators     | 94  |

|    | 4.3           | FSK N  | Adulators and Demodulator                      | 94  |

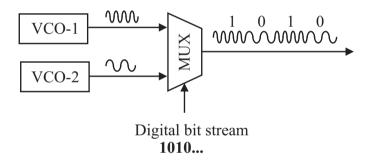

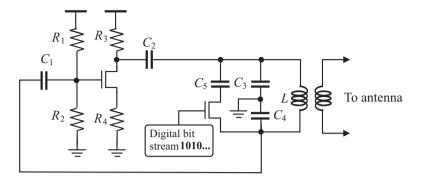

|    |               | 4.3.1  | FSK Modulators                                 | 96  |

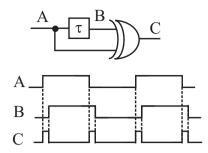

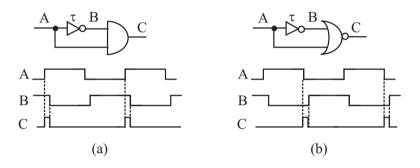

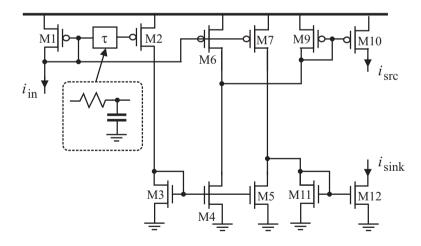

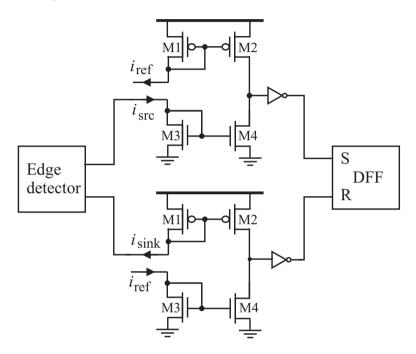

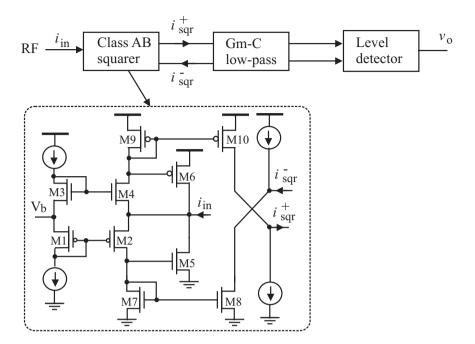

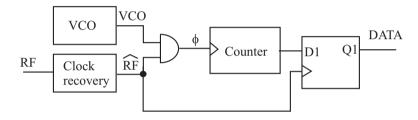

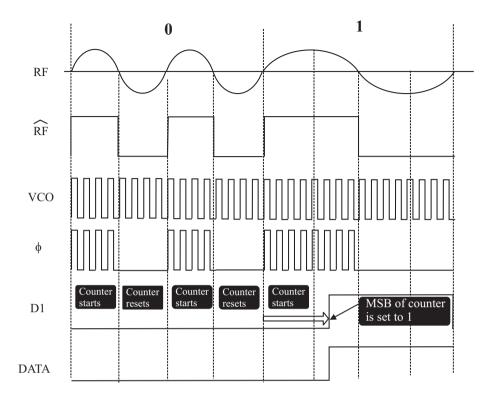

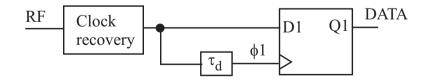

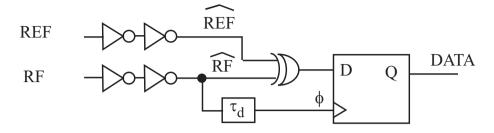

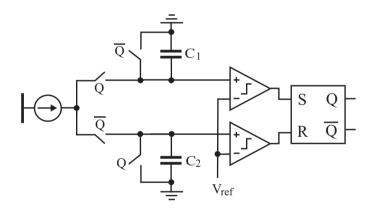

|    |               | 4.3.2  | Ghovanloo-Najafi FSK Demodulator               | 97  |

|    |               | 4.3.3  | Jung FSK Demodulator                           | 98  |

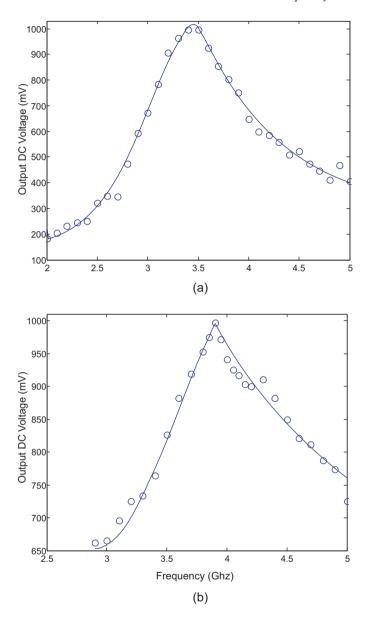

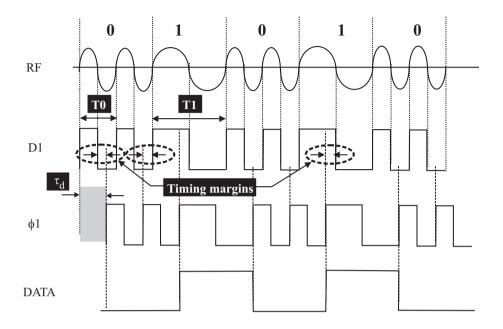

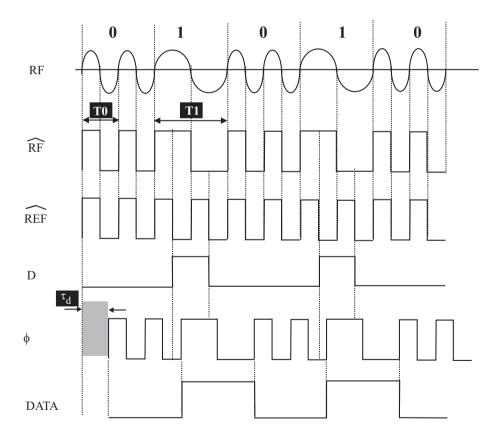

|    |               | 4.3.4  | Weng FSK Demodulator                           | 100 |

|    |               | 4.3.5  | Performance Comparison of FSK Demodulators     | 102 |

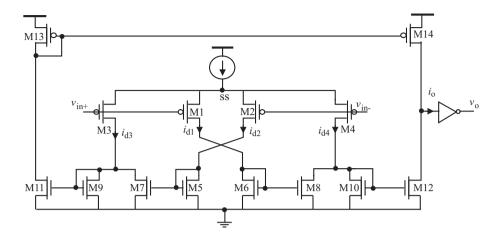

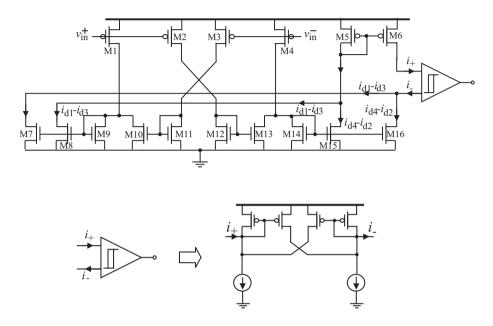

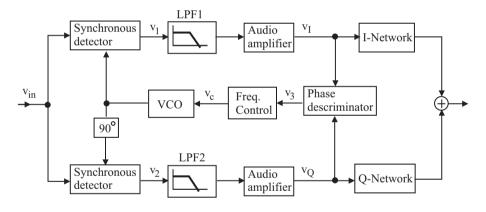

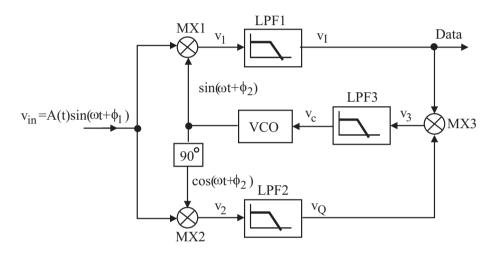

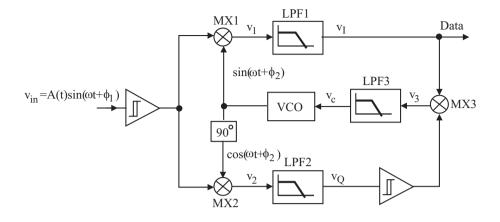

|    | 4.4           | PSK N  | Aodulators and Demodulators                    | 102 |

|    |               | 4.4.1  | PSK Modulators                                 | 103 |

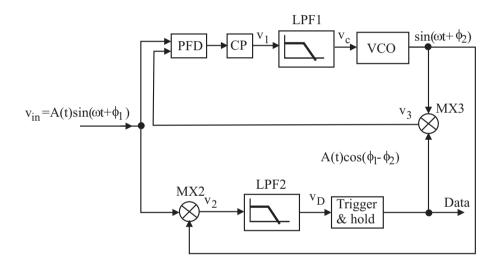

|    |               | 4.4.2  | Coherent BPSK Demodulators                     | 104 |

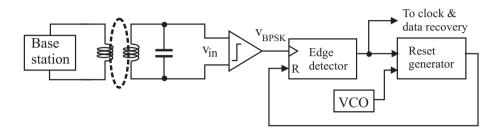

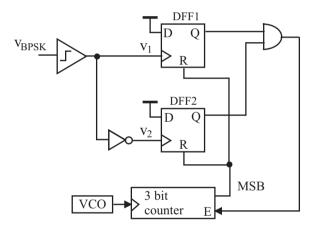

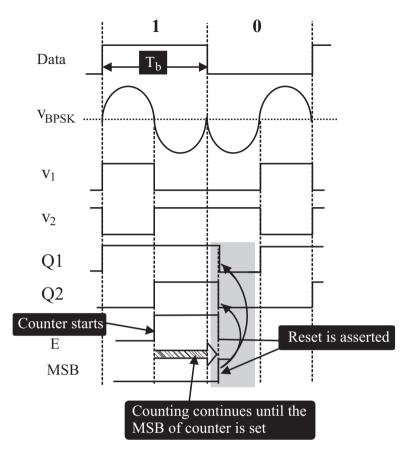

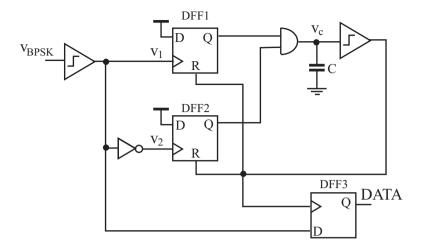

|    |               | 4.4.3  | Non-Coherent BPSK Demodulators                 | 109 |

|    |               | 4.4.4  | Performance Comparison of PSK Demodulators     | 112 |

|    | 4.5                                    | Chapte  | er Summary                                          | 113 |

|----|----------------------------------------|---------|-----------------------------------------------------|-----|

| 5. | LOW-POWER PRECISION VOLTAGE REFERENCES |         |                                                     | 117 |

|    | 5.1                                    | Charac  | cterization of Voltage References                   | 117 |

|    |                                        | 5.1.1   | Temperature Coefficient                             | 118 |

|    |                                        | 5.1.2   | Power Supply Rejection Ratio                        | 119 |

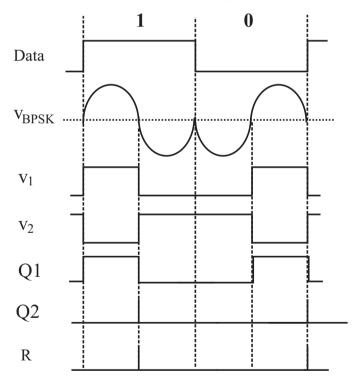

|    |                                        | 5.1.3   | Minimum Supply Voltage                              | 119 |

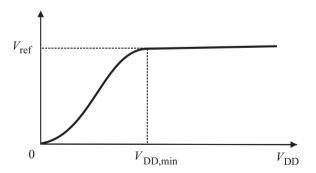

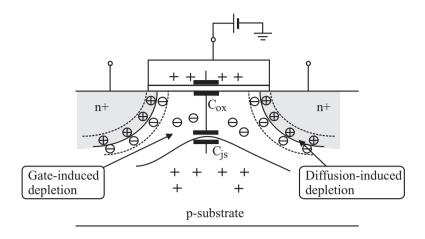

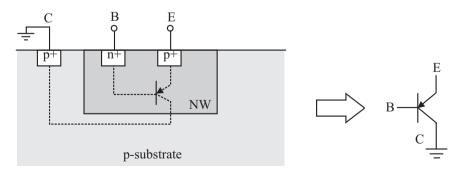

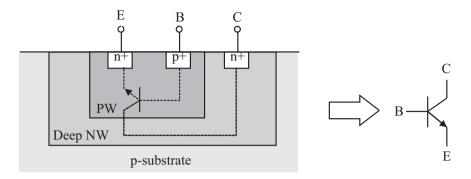

|    | 5.2                                    | Tempe   | rature Characteristics of MOS Devices               | 120 |

|    |                                        | 5.2.1   | Base-Emitter Voltage of BJTs                        | 120 |

|    |                                        | 5.2.2   | Threshold Voltage of MOSFETs                        | 127 |

|    |                                        | 5.2.3   | Gate-Source Voltage of MOSFETs in Weak Inversion    | 128 |

|    |                                        | 5.2.4   | Resistance of Diffusion and Poly Resistors          | 132 |

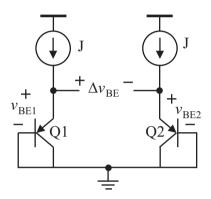

|    |                                        | 5.2.5   | PTAT Voltage / Current Generators                   | 133 |

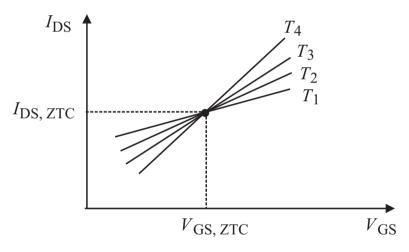

|    |                                        | 5.2.6   | Zero-Temperature-Coefficient Bias Point             | 135 |

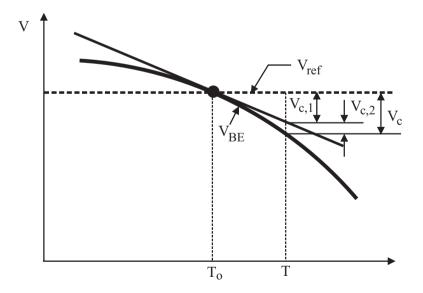

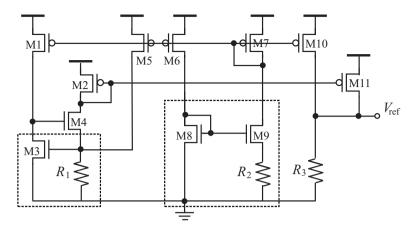

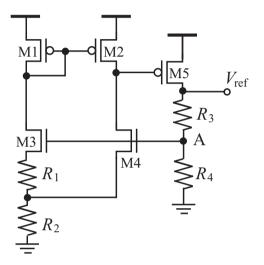

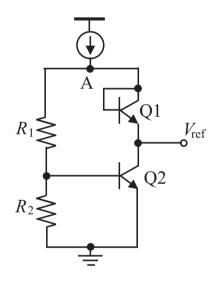

|    | 5.3                                    | First-C | Order Voltage References                            | 136 |

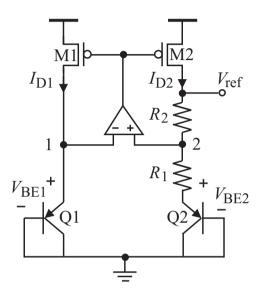

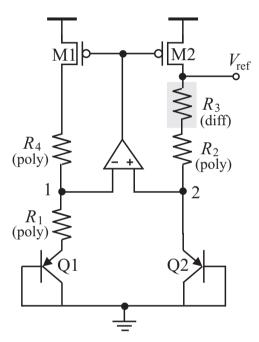

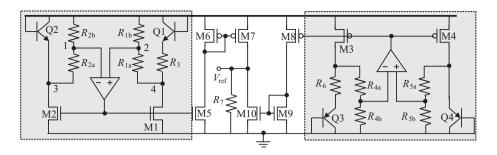

|    |                                        | 5.3.1   | Widlar Voltage Reference                            | 138 |

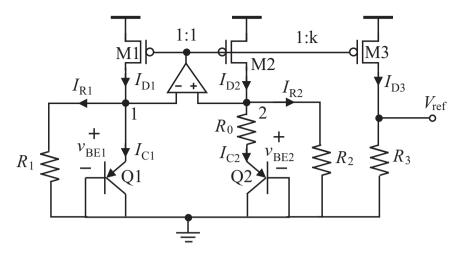

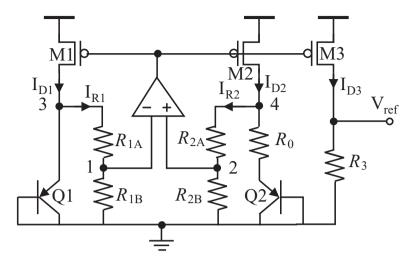

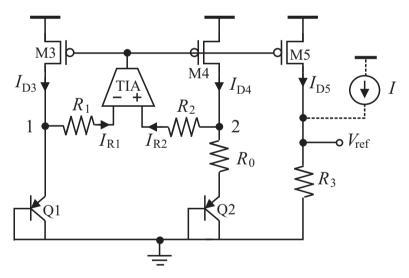

|    |                                        | 5.3.2   | Banba Voltage Reference                             | 141 |

|    |                                        | 5.3.3   | Waltari-Halonen Voltage Reference                   | 142 |

|    |                                        | 5.3.4   | Jiang-Lee Voltage Reference                         | 143 |

|    |                                        | 5.3.5   | Threshold Voltage Based Voltage References          | 144 |

|    |                                        | 5.3.6   | Buck Voltage Reference                              | 146 |

|    |                                        | 5.3.7   | Comparison of First-Order Voltage References        | 148 |

|    | 5.4                                    | High-O  | Order Voltage References                            | 149 |

|    |                                        | 5.4.1   | Piecewise-Linear Voltage Reference                  | 150 |

|    |                                        | 5.4.2   | Malcovati Voltage Reference                         | 150 |

|    |                                        | 5.4.3   | Resistor Curvature-Compensated Voltage Reference    | 153 |

|    |                                        | 5.4.4   | Ker-Chen Voltage Reference                          | 155 |

|    |                                        | 5.4.5   | Comparison of High-Order Voltage References         | 157 |

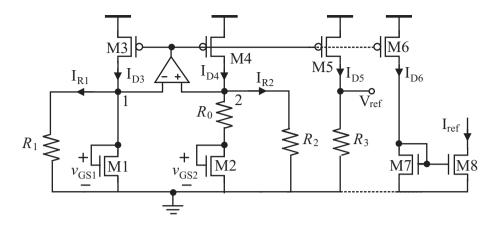

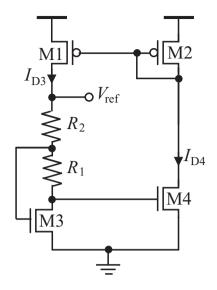

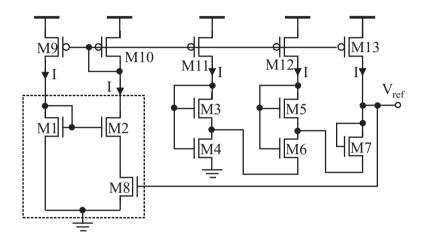

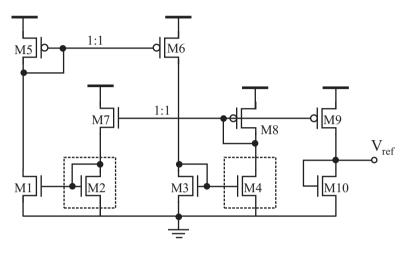

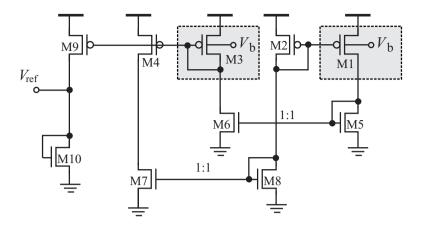

|    | 5.5                                    | Sub-th  | reshold Voltage References                          | 157 |

|    |                                        | 5.5.1   | Ytterdal Voltage Reference                          | 158 |

|    |                                        | 5.5.2   | Cheng-Wu Voltage Reference                          | 160 |

|    |                                        | 5.5.3   | Huang Voltage Reference                             | 161 |

|    |                                        | 5.5.4   | Ueno Voltage Reference                              | 163 |

|    |                                        | 5.5.5   | De Vita - Iannaccone Voltage Reference              | 164 |

|    |                                        | 5.5.6   | Sub-threshold Voltage References Without Amplifiers | 166 |

|    |                                        | 5.5.7   | Comparison of Sub-Threshold Voltage References      | 169 |

|    | 5.6                                    | Chapte  | er Summary                                          | 170 |

| 6. | CLC                                   | OCK GE                                                | ENERATION AND CALIBRATION                      | 173        |  |

|----|---------------------------------------|-------------------------------------------------------|------------------------------------------------|------------|--|

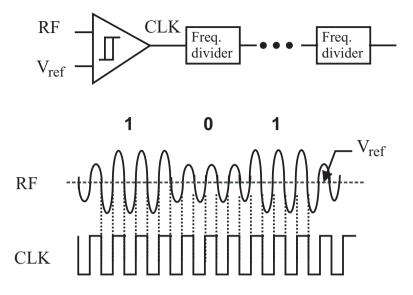

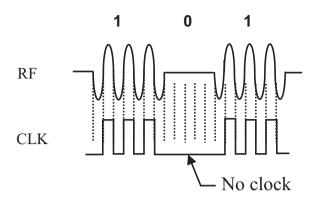

|    | 6.1                                   | Clock                                                 | Generation From Carrier                        | 174        |  |

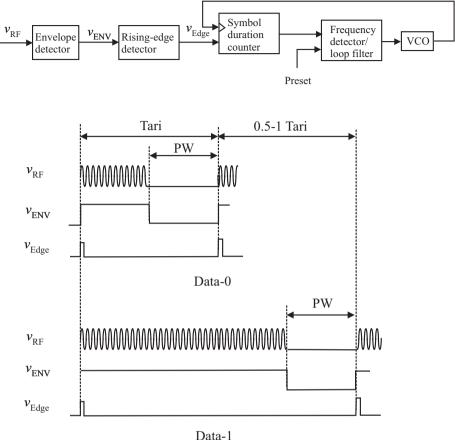

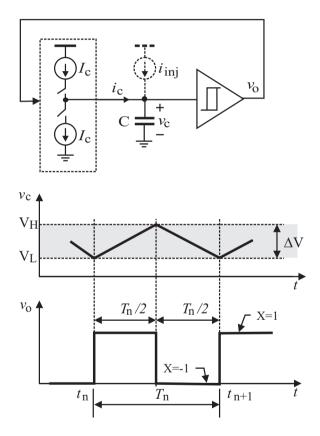

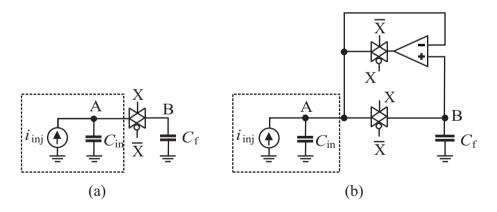

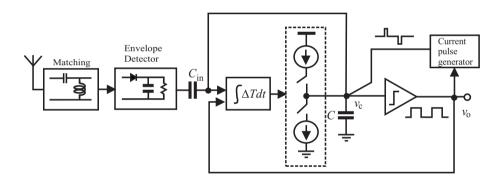

|    | 6.2                                   | Clock                                                 | ek Generation From Envelope                    |            |  |

|    | 6.3                                   | *                                                     |                                                |            |  |

|    | 6.4                                   |                                                       |                                                |            |  |

|    | 6.5                                   |                                                       |                                                |            |  |

|    | 6.6                                   |                                                       |                                                |            |  |

|    | 6.7                                   |                                                       |                                                |            |  |

|    | 6.8                                   |                                                       | mance Comparison                               | 186<br>198 |  |

|    | 6.9                                   | Chapter Summary                                       |                                                |            |  |

| _  |                                       | 1 2                                                   |                                                |            |  |

| 7. | LO                                    |                                                       | ER ANALOG-TO-DIGITAL CONVERTERS                | 201        |  |

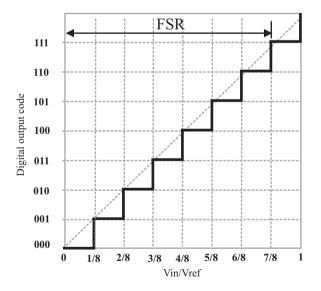

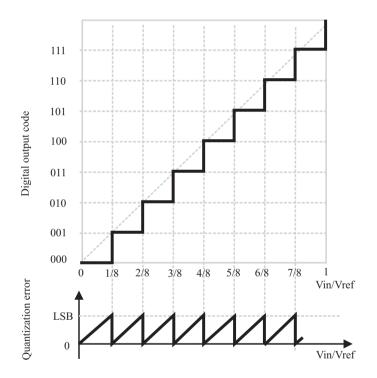

|    | 7.1                                   |                                                       | mentals of Analog-to-Digital Converters        | 202        |  |

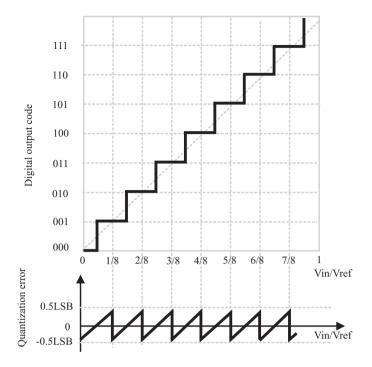

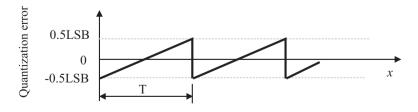

|    |                                       | 7.1.1                                                 | Quantization Error                             | 203        |  |

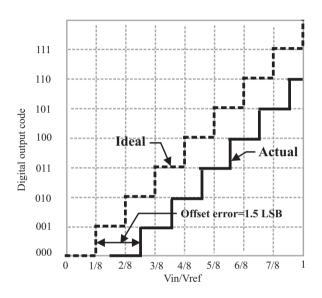

|    |                                       | 7.1.2                                                 |                                                | 205        |  |

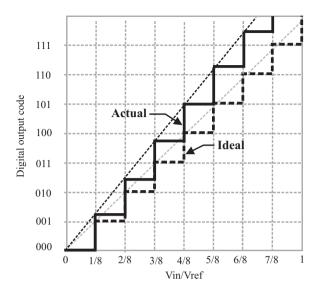

|    |                                       | 7.1.3                                                 | Gain Error                                     | 205        |  |

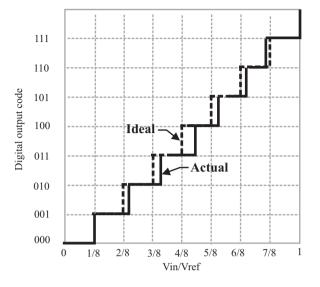

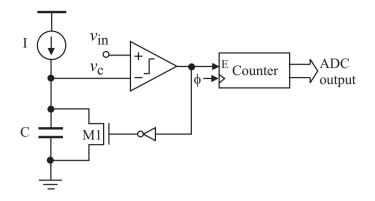

|    |                                       | 7.1.4                                                 | Differential Nonlinearity                      | 205        |  |

|    |                                       | 7.1.5                                                 | Integral Nonlinearity                          | 206        |  |

|    |                                       | 7.1.6                                                 | Dynamic Range                                  | 206        |  |

|    |                                       | 7.1.7                                                 | Signal-to-Noise Ratio                          | 208        |  |

|    |                                       | 7.1.8                                                 | Signal-to-Noise-and-Distortion Ratio           | 208        |  |

|    |                                       | 7.1.9                                                 | Effective Number of Bits                       | 209        |  |

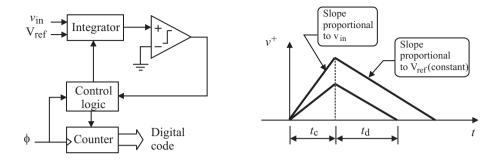

|    | 7.2                                   | Integrating ADCs                                      |                                                | 209        |  |

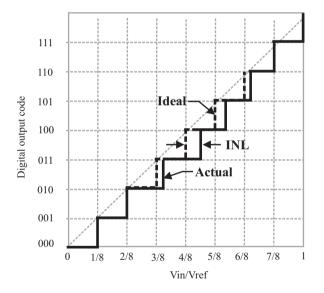

|    |                                       | 7.2.1                                                 | Single-Slope Integrating ADCs                  | 209        |  |

|    |                                       | 7.2.2                                                 | Dual-Slope Integrating ADCs                    | 211        |  |

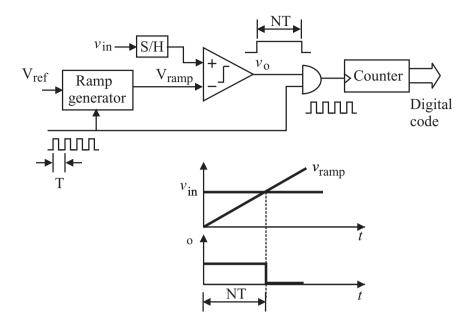

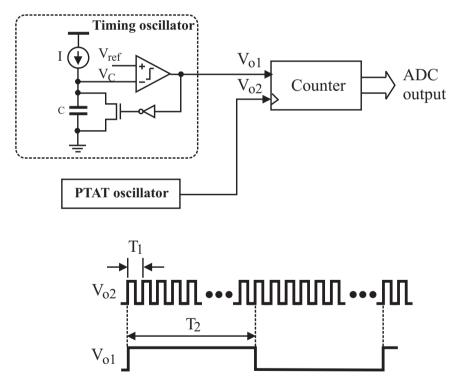

|    | 7.3 Oscillator-Based Temperature ADCs |                                                       | 213                                            |            |  |

|    |                                       | 7.3.1                                                 | Relaxation Oscillator-Based Temperature ADCs   | 213        |  |

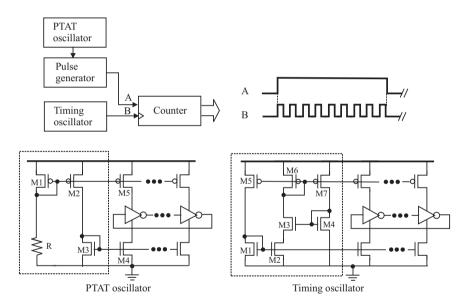

|    |                                       | 7.3.2                                                 | Ring Oscillator-Based Temperature ADCs         | 215        |  |

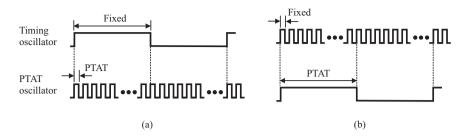

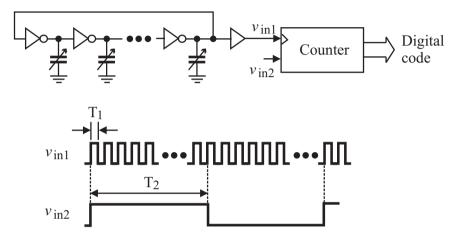

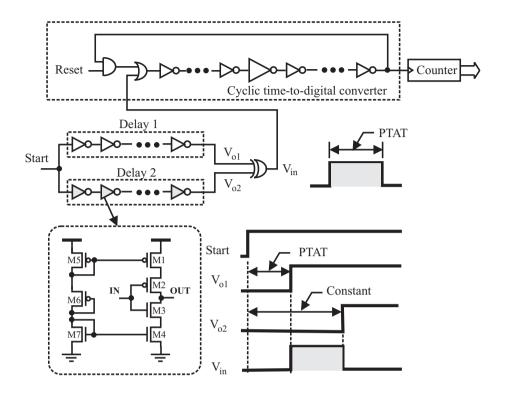

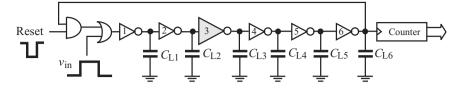

|    | 7.4                                   | 7.4 Time-to-Digital Converter Based Temperature ADCs  |                                                | 219        |  |

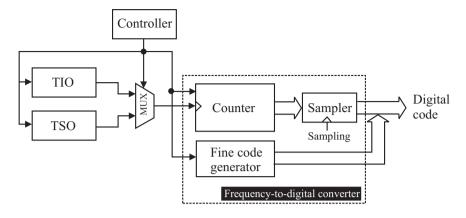

|    | 7.5                                   | Frequency-to-Digital Converter Based Temperature ADCs |                                                |            |  |

|    | 7.6                                   | Charg                                                 | e Redistribution Successive Approximation ADCs | 223        |  |

|    |                                       | 7.6.1                                                 | Charge-Scaling DACs                            | 224        |  |

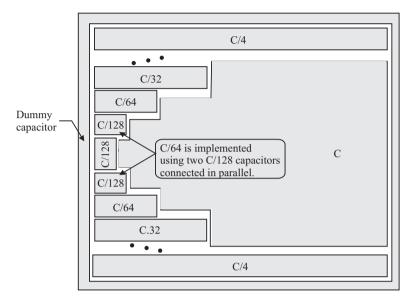

|    |                                       | 7.6.2                                                 | Accuracy of Charge-Scaling DACs                | 228        |  |

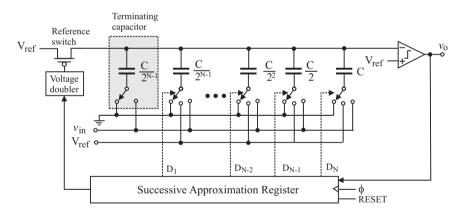

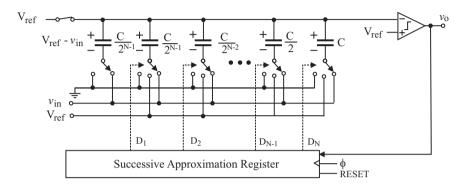

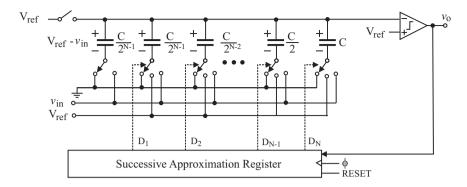

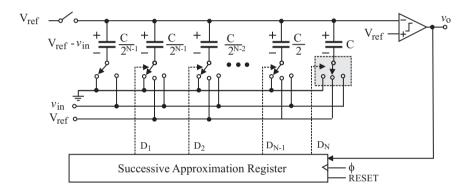

|    |                                       | 7.6.3                                                 | Charge Redistribution ADCs                     | 230        |  |

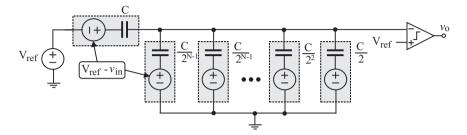

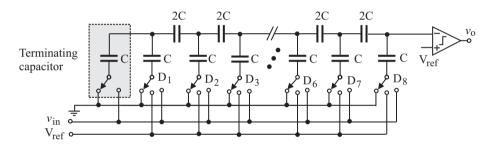

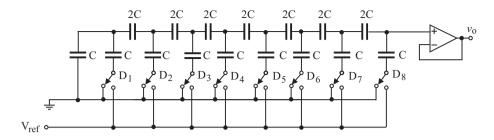

|    |                                       | 7.6.4                                                 | Single-Stage Binary-Weighted Capacitor Arrays  | 233        |  |

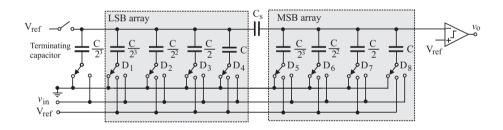

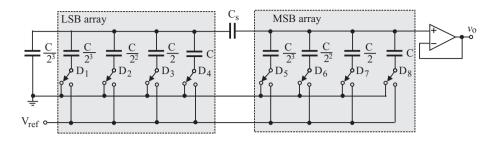

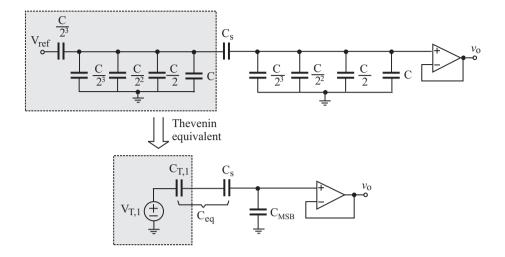

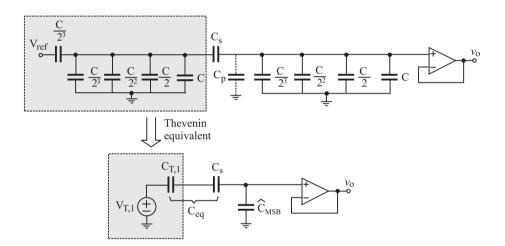

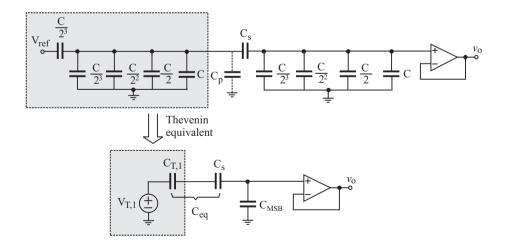

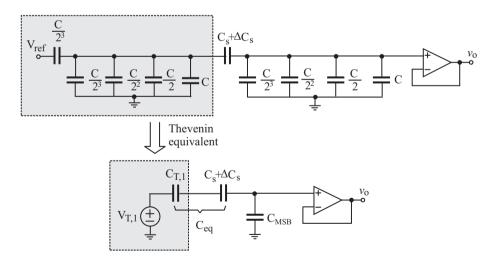

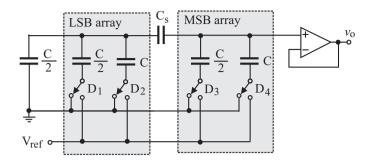

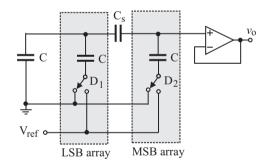

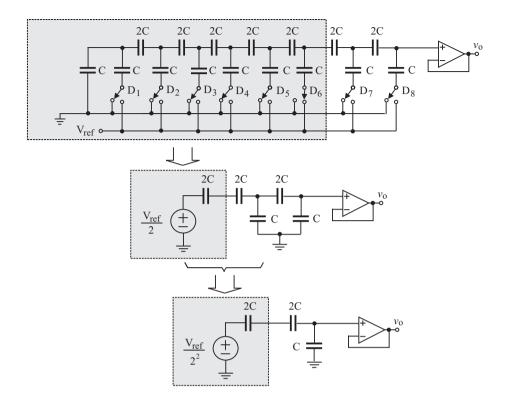

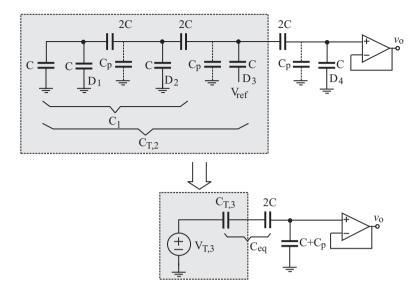

|    |                                       | 7.6.5                                                 | Two-Stage Binary-Weighted Capacitor Array      | 235        |  |

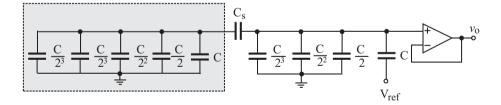

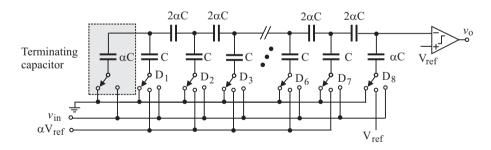

|    |                                       | 7.6.6                                                 | C-2C Capacitor Arrays                          | 245        |  |

|                                   | 7.6.7  | Switching Network               | 251 |

|-----------------------------------|--------|---------------------------------|-----|

|                                   | 7.6.8  | Hybrid Charge-Scaling DACs      | 252 |

|                                   | 7.6.9  | Multi-Stage Charge-Scaling DACs | 252 |

| 7.7                               | Perfor | 253                             |     |

| 7.8                               | Chapte | er Summary                      | 255 |

| Append                            | ices   |                                 |     |

| A Material and Physical Constants |        |                                 | 257 |

| References                        |        |                                 | 259 |

| Index                             |        |                                 | 275 |

## Chapter 1

# PASSIVE WIRELESS MICROSYSTEMS

Passive wireless microsystems such as wireless transponders, radio-frequency identification (RFID) tags, wireless microsensors, and biomedical implants, harvest their operational power either from radio-frequency waves emitted by their base station or from other energy sources such as vibration and solar. The absence of bulky batteries not only minimizes the physical dimension and implementation cost of these microsystems, it also removes the need for maintenance. As a result, passive wireless microsystems can be embedded in products or implanted in living bodies permanently to provide the unique identification of the products or living bodies in which they reside, to provide the precision measurement of the parameters of the products or living bodies, and to carry out control actions in a micron scale that otherwise cannot be performed. The key intrinsic attributes of passive wireless microsystems include small size, battery-less and maintenance-free operation, programmability, and wireless accessibility.

Passive wireless microsystems have found a broad range of emerging applications include implantable bio-microelectromechanical-systems (MEMS) pressure sensors [1, 2], retinal prosthetic devices [3–6], swallowable capsule endoscopy [7–9], multi-site pressure sensors for wireless arterial flow characterization [10], embedded micro-strain sensors for product performance and safety monitoring, wireless temperature sensors for human bodies and environmental monitoring [11–14], radio-frequency identification tags for object tracking in logistics automation [15, 16] and replacing bar codes in retailing, warehouse inventory automation, e-tickets, e-passports, and low-cost high-security product authentication keys to replace existing product authentication means such as holograms, water-marks, invisible barcodes, security threads, chemical, and DNA markers that are often too costly to be used for general goods [17].

#### **1.1** The Spectrum

Communications between a passive wireless microsystem and its base station typically take place in ISM (Industrial, Scientific, and Medical) bands. ISM bands are open frequency bands that allow for operation without a license. The most widely used ISM bands are 13.553-13.57 MHz, 902-928 MHz, 2.4-2.4825 GHz, and 5.725-5.850 GHz [18]. The maximum power of the radio-frequency waves emitted by an antenna in ISM bands is regulated by Federal Communications Commission (FCC) in the United States. Effective isotropic radiated power (EIRP), which is defined as the power that would have to be supplied to an ideal antenna that radiates uniformly in all directions in order to get the same electrical field strength that the device under test produces at the same distance, is widely used to quantify the amount of the radiation power from an antenna. EIRP is computed from [19]

$$\operatorname{EIRP} = 10\log\left(\frac{4\pi E^2 r^2}{0.377}\right),\tag{1.1}$$

where E is the electrical field strength and r is the distance from the antenna. FCC part 15 rules govern the transmission power permitted in ISM bands. For example, the maximum transmitter output power fed into an antenna is 30 dBm (1 Watt) and the maximum EIRP is 36 dBm (4 Watts) in 902-928 MHz and 2.4-2.4825 GHz ISM bands.

Wireless communications between a passive wireless microsystem and its base station can take place either in the near field or the far field of the antennas of the base station. Near-field coupling is viable for frequencies up to a few tens of MHz with the characteristics of a low data rate, a large antenna dimension, and a short link distance. The low upper bound of the frequency is mainly due to the low self-resonant frequency of the coupling coils between base stations and passive wireless microsystems. Far-field coupling occurs at ultra-high frequencies (UHF) and microwave frequencies and offers the advantages of a high data rate, a small antenna dimension, and a long link distance. Biomedical implants are located in the near field mainly due to the high loss of electromagnetic waves in living bodies at high frequencies. Other near-field passive wireless microsystems include smart cards, access cards, epassports, etc. Transponders and RFID tags are typically located in the far field of the antenna of their base station to take the advantages of the low loss of electromagnetic waves in air.

#### **1.2** The Challenges

Although the emerging applications of passive wireless microsystems are quite broad, the performance of these microsystems is commonly affected by a number of fundamental issues. These fundamental issues include a low power conversion efficiency in power harvest from radio-frequency waves, fluctuating supply voltages, the low level of data security arising from the difficulty to implement encryption algorithms on passive wireless microsystems due to their limit power resource, signal collisions when multiple microsystems coexist in a close proximity, the drift of the frequency of the system clock of passive wireless microsystems that controls the operation of their baseband blocks and the backscattering communications from the microsystems to their base station, and the need for precision voltage resources and ultra-low power analog-to-digital converters.

#### 1.2.1 Efficiency of Radio-Frequency Power Harvest

The efficiency of power harvest from radio-frequency waves determines the amount of power available for microsystems to operate. This, in turn, sets the degree of the complexity subsequently the functionality of passive wireless microsystems. The amount of the power that can be harvested by a passive wireless microsystem from a radio-frequency wave is dominated by the efficiency of the antenna, the accuracy of impedance matching between the antenna and the impedance transformation network, the efficiency of the impedance transformation network, and the efficiency of the voltage multiplier of the microsystem. The widely used diode-bridge rectification in near-field power telemetry performs poorly when passive wireless microsystems are located in the far field of the antenna of its base station simply because the amplitude of the received RF signal is small [4, 6]. To obtain a sufficiently large supply voltage and at the same time to maximize the power efficiency of voltage multipliers, many novel voltage multipliers evolved from the classic Cockcroft-Walton voltage multiplier [20] and Dickson voltage multiplier [21] emerged [22-28]. The power efficiency of voltage multipliers can be best improved by boosting the voltage at the input of the voltage multipliers. This is achieved by inserting a passive resonant network such as a LC resonator [25] or a step-up transformer resonator [29] between the antenna and the voltage multiplier of the microsystem. The ohmic loss of the impedance transformation network, however, limits the overall power efficiency of the power harvesters.

#### **1.2.2** Fluctuating Supply Voltage

Aside from RF power harvest, a unique characteristic of passive wireless microsystems is their poor supply voltage stability, arising from the time-varying nature of the power harvest from radio-frequency waves. The fluctuation of the supply voltage warrants the deployment of a voltage regulator, aiming at stabilizing the supply voltage. This, however, is at the expense of an additional amount of power consumption. Both diode-based voltage regulators [30] and

feedback op-amp voltage regulators [31, 32] are available. The former consumes less power while the latter yields a better voltage stability. In addition to voltage regulation, the circuits of passive wireless microsystems must also be designed in such a way that their performance is less sensitive to fluctuating supply voltages. Such a constraint often excludes the circuits with which we are familiar. LC oscillators and regulated cascodes are examples of these circuits.

#### 1.2.3 Sensitivity to Changing Environment

In addition to a time-varying supply voltage, the performance of a passive wireless microsystem is also severely affected by the condition of the environment in which the microsystem resides. For example, the frequency of the local oscillator of a microsystem, which provides the system clock for its baseband units and controls the backscattering communications with its base station, is sensitive to temperature variation [33, 34]. This is on top of the effect of process variation and supply voltage fluctuation. Although the effect of temperature variation can be minimized using complex compensation circuitry, the practicality of this approach largely diminishes once the limited power resource of passive wireless microsystems is considered [35, 36]. An alternative and yet more effective way to ensure the accuracy of the frequency of the system clock of a passive wireless microsystem is to use an external calibrating signal sent by its base station to the microsystem as a reference to calibrate the frequency of the local oscillator of the microsystem prior to the commence of any communications between the microsystem and its base station. The key advantage of this approach is that the reference is from the base station and is therefore independent of the condition of the environment in which the passive wireless microsystem resides. Also, since the calibration is conducted remotely, the frequency of the passive wireless microsystem can be calibrated even though the microsystem has already been embedded in products or implanted in living bodies.

#### **1.2.4** Precision Voltage References

Temperature-insensitive precision voltage references are as important as a stable system clock to the operation of passive wireless microsystems. This is because temperature-insensitive precision voltage references play a critical role in biasing analog circuitry, providing constant currents for relaxation oscillators and other blocks, and providing a precision voltage reference for analog-to-digital converters. Although bandgap voltage references have been widely studied and many bandgap voltage references are available, the low and fluctuating supply voltage, and the low-power consumption requirement of passive wireless microsystems impose stringent constraints on the design of voltage references. As a result, many of the known bandgap voltage references can not be used for passive wireless microsystems either due to their high power consumption or due to their need for a large supply voltage. A detailed study of the principles and design of high precision low-power CMOS voltage references is therefore an essential part of any text on passive wireless microsystems.

#### 1.2.5 Ultra-Low Power Analog-to-Digital Converters

Analog-to-digital conversion is essential to passive wireless microsensors. Although analog-to-digital converters (ADCs) are perhaps the most widely studied mixed analog-digital subsystems and there are many ways to perform analog-to-digital conversion such as flash ADCs, pipelined ADCs, oversampled sigma-delta ADCs, to name a few, the low and fluctuating supply voltage and the low power consumption constraints of passive wireless microsystems disqualifies many architectures of ADCs. Only a few architectures of ADCs, such as integrating ADCs, charge-redistribution successive approximation ADCs, oscillation-based ADCs, time-to-digital ADCs, and frequency-to-digital ADCs made to the the short list.

#### **1.2.6 Encryption and Authentication**

The applications of passive wireless microsystems, especially those located in the far-field of the antenna of base stations, are hindered by their vulnerability to interception by third parties, mainly due to the limited computing power of these microsystems. The large-scale deployment of these microsystems mandates the equipment of encryption for authentication. Existing authentication algorithms for computer and cellular networks are generally too complex and power-consuming to be adopted for passive wireless microsystems. Highsecurity authentication protocols with a reconfiguration capability are desirable. Mutual authentication protocols shared between a passive wireless microsystem and its base station and the optimal partition of authentication protocols between the microsystem and its base station can achieve the required level of security without excessively increasing the complexity subsequently power consumption of the passive wireless microsystem.

#### 1.2.7 Signal Collision

Signal collision occurs when multiple wireless microsystems coexist in a close proximity, arising from the fact that passive wireless microsystems typically operate in the same frequency channel. Two spread spectrum approaches, namely frequency hopping and direct sequence spread spectrum, are perhaps the most widely used techniques in dealing with multi-access wireless communications. The former avoid signal collision by allocating an unused channel in the selected ISM band while the latter spreads the signal to be transmitted

over a large frequency range of the selected ISM band using a pseudo random sequence and recovers the transmitted signal at the receiving end using de-sequencing. Frequency hopping is less attractive for passive wireless microsystems due to its high power consumption and its need for synchronization in both time and frequency domains. The intrinsic characteristics of direct sequence spread spectrum including reduced crosstalk interferences, better data integrity, low susceptibility to multi-path fading, an increased operating distance, hard to detect, intercept, and jam, make it particularly attractive for passive wireless microsystems. Although this approach has been widely used in cellular phones in the form of code-devision-multi-access (CDMA), challenges exist in applying it for passive wireless microsystems mainly due to the limited power resource, small memory, and finite computing power of these microsystems.

#### **1.2.8** Dimension of Antennas

The dimension of the antenna of microsystems also imposes a great challenge in embedding these microsystems in products and living bodies. The antenna of a passive wireless microsystem should be small in size such that the microsystem can be embedded in products or implanted in living bodies with a little difficulty. The efficiency of the antenna, on the other hand, should be high so that the voltage at the output of the antenna is sufficiently large. Recent efforts on minimizing the physical dimensions of the antennas of microsystems have been made in circular loop antennas with multiple stubs [37], text-based meander line dipole antennas [38, 37], folded-slot antennas [39–41] with an omni-directional radiation pattern in UHF ISM bands.

Since the focus on this book is on CMOS circuits for passive wireless microsystems, the design of the antennas of passive wireless microsystems is clearly beyond the scope of the book. The in-depth treatment of frequency hopping and direct sequence spread spectrum is readily available in standard texts on digital communications and will therefore not be covered.

# Chapter 2

## **RADIO-FREQUENCY POWER HARVEST**

Passive wireless microsystems harvest their operational power from the radio-frequency waves emitted from their base stations. Based on the characteristics of the wireless links with base stations, passive wireless microsystems are loosely classified as inductively-coupled also known as near-field-coupled and electromagnetically-coupled also known as far-field-coupled. The boundary that separates the near-field and far-field is defined as  $\frac{\lambda}{2\pi}$  where  $\lambda$  is the wavelength of the signals. Near-field-coupling is viable for frequencies up to a few ten MHz, mainly due to the low resonant frequency of the planar coupling coils. Near-field-coupling has been widely used in applications such as biomedical implants where a high degree of the absorption of electromagnetic waves by living bodies exists at high frequencies. The key characteristics of a near-field-coupled passive wireless microsystem include a large voltage at the coupling coils of the microsystem and weak interferences from neighboring devices due to the close distance between the base station and the passive wireless microsystem. Far-field-coupling, on the other hand, is used at ultrahigh frequencies (UHF) and microwave frequencies, such as ISM 900 MHz and 2.4 GHz bands. A high data rate, a small antenna dimension, and a long link distance are the key characteristics of far-field-coupled passive wireless The fact that the maximum EIRP of base stations in North microsystems. America can not exceed 4 W in UHF bands limits the maximum distance between a far-field-coupled microsystem and its base station to a few meters [42]. The efficiency of power harvest from RF waves determines the maximum distance over which a reliable wireless link between a base station and a passive wireless microsystem can be established. The efficiency of radio-frequency power harvest is determined by a number of factors including the efficiency of the antenna of the microsystem, the accuracy of power matching between

the antenna and the voltage multiplier, and the power efficiency of the voltage multiplier that converts the received RF signal to a dc voltage from which the microsystem is powered.

This chapter deals with power harvest from radio-frequency waves. The chapter is organized as the follows : Section 2.1 investigates the figure-of-merits that characterize the performance of RF power harvesters. Section 2.2 focuses on the design of voltage multipliers for passive wireless microsystems in the far field of the antenna of the base stations. In Section 2.3, power-matching and gain-boosting using a LC network is investigated. Section 2.4 presents power-matching and gain-boosting using a step-up transformer. Frequency tuning mechanisms for power-matching and gain-boosting using a LC network and that using a step-up transformer are also addressed. The measurement results of the proposed power-matching network, together with the measurement results of a LC power-matching network are compared. The chapter is concluded in Section 2.5.

#### 2.1 Characterization of Radio-Frequency Power Harvest

The efficiency of power harvest from a radio-frequency wave determines the maximum distance over which a reliable link between a base station and a passive wireless microsystem can be established. It also sets the complexity subsequently the functionality of the microsystem. The efficiency of a radiofrequency power harvesting system is determined by the efficiency of the antenna of the microsystem, the accuracy of impedance matching between the antenna and the voltage multiplier of the microsystem, and the power efficiency of the voltage multiplier that converts a received RF signal to a dc voltage from which the microsystem is powered.

#### 2.1.1 **Power Matching**

The radiation resistance of the antenna of passive wireless microsystems has a typical value of  $50\Omega$  at the desired frequency. The input impedance of voltage multipliers typically has a reactance component, owing to the capacitance of rectifying diodes or MOSFETs. An impedance transformation network is therefore required to transform the input impedance of the voltage multiplier to  $50\Omega$ .

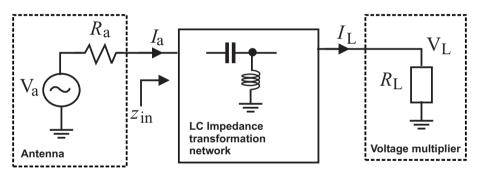

Consider Fig.2.1 where an impedance transformation network is inserted between the antenna represented by voltage source  $V_a$  and radiation resistance  $R_a$  and the voltage multiplier represented by resistor  $R_L$ . Note that to simplify analysis, the input impedance of the voltage multiplier is assumed to be purely resistive. Note that a pure resistive input impedance of voltage multipliers can be obtained by employing a shunt inductor that resonates out the reactive part of the input impedance of the voltage multiplier [42]. The function of the impedance transformation network is two-fold : (i) It provides a matching impedance to the antenna to maximize the power transmission from the antenna to the voltage multiplier and to minimize the reflection of the signals. (ii) It provides a large voltage gain such that the voltage at the input of the voltage multiplier or the output of the impedance transformation network is maximized. If we assume that the impedance transformation network is lossless, the power delivered to the impedance transformation network will be the same as that delivered to the load. A large voltage at the input port of the voltage multiplier will reduce the power loss at the voltage multiplier. As a result, the overall power efficiency of the power harvesting path is improved. The power delivered to the load  $R_L$  is given by [43]

$$P_L = \frac{V_L^2}{R_L} = \frac{A_v^2 V_a^2}{R_L},$$

(2.1)

where  $A_v$  is the voltage gain provided by the impedance transformation network.

Figure 2.1. Power-matching and gain-boosting using an impedance transformation network.

The maximum power will be delivered from the antenna to the impedance transformation network when

$$R_a = z_{in}^* \tag{2.2}$$

is satisfied, where  $z_{in}$  is the input impedance of the impedance transformation network and the superscript \* denotes complex conjugation. Since in this case

$$I_a = \frac{V_a}{R_a + z_{in}} = \frac{V_a}{2R_a},\tag{2.3}$$

we obtain the maximum power delivered from the antenna to the impedance transformation network

$$P_{L,max} = |I_a^2| \Re e[z_{in}] = \frac{V_a^2}{4R_a}.$$

(2.4)

Eq.(2.4) is also the maximum power delivered to the load provided that the impedance transformation network is lossless. Equating (2.1) and (2.4) yields the relation between the voltage gain of the impedance transformation network and the load resistance at which the power delivered to the load is maximized

$$A_v = \frac{1}{2} \sqrt{\frac{R_L}{R_a}}.$$

(2.5)

Eq.(2.5) reveals that the voltage gain of the lossless impedance transformation network is proportional to the square-root of the load resistance.

#### 2.1.2 **Power Efficiency**

The power efficiency of a voltage multiplier is defined as the ratio of the output power of the voltage multiplier, denoted by  $P_{out}$ , to the power at the input of the voltage multiplier, denoted by  $P_{in}$

$$\eta_V = \frac{P_{out}}{P_{in}}.$$

(2.6)

The power efficiency of voltage multipliers is less than 100% due to the power consumption of rectifying devices of voltage multipliers.

The power efficiency of an impedance transformation network is defined as the ratio of the power delivered to the multiplier, denoted by  $P_L$ , to the power available at the input of the impedance transformation network, denoted by  $P_{in}$

$$\eta_I = \frac{P_L}{P_{in}} \bigg|_{z_{in} = R_a}.$$

(2.7)

Note that power-matching condition

$$z_{in} = R_a \tag{2.8}$$

must be met at the input of the impedance transformation network for the maximum power transfer from the antenna to the impedance transformation network. The power efficiency of impedance transformation networks is less than 100% due to the resistive loss of these networks.

The global power efficiency of a RF power harvester is defined as the ratio of the incident power of the RF signal to the dc power at the output of the voltage multiplier

$$\eta = \frac{\text{DC output power}}{\text{Incident RF power}}.$$

(2.9)

The incident RF power, denoted by  $R_{RF}$ , is quantified by Friis relation [44]

$$P_{RF} = P_B G_B G_M \left(\frac{\lambda}{4\pi r}\right)^2, \qquad (2.10)$$

where  $P_B$  is the amount of the power that the base station provides to its antenna,  $G_B$  is the gain of the antenna of the base station,  $G_M$  is the gain of the antenna of the passive wireless microsystem,  $\lambda$  is the wave length, and ris the distance between the passive wireless microsystem and its base station. Often, the effective isotropically radiated power, denoted by  $P_{EIRP}$ , is used. It is obtained from

$$P_{EIRP} = P_B G_B. \tag{2.11}$$

#### 2.2 Voltage Multipliers

Wireless communications between a near-field passive wireless microsystem, such as a biomedical implant or a smart card, and its base station is established using an inductive link, much like a transformer with the base station connected to the primary winding of the transformer and the passive wireless microsystem connected to the secondary winding of the transformer. One of the key characteristics of this inductive link is the large voltage at the secondary winding. As a result, RF-to-DC conversion can be carried out using a diode bridge even with the voltage loss across the diodes accounted for. The dc voltage at the output of the diode bridge is sufficiently large to power the passive wireless microsystem. To minimize the voltage loss across the diodes so as to improve RF-to-DC conversion efficiency, Schottky diodes, which typically have a low forward conduction voltage, are widely used [4, 6]. Schottky diodes, however, are not available in standard CMOS processes. Instead, MOSFET-based diodes formed by connecting the gate and drain together can be used for rectification such that the voltage rectifier can be implemented using standard CMOS technologies. Not that there is a voltage loss of at least one device threshold voltage when MOSFET-diodes are used.

Wireless communications between a far-field passive wireless microsystem, such as a RFID tag or a wireless microsensor, and its base station is established

using a radio-frequency wave. Unlike near-field inductive links, the voltage at the antenna of the passive wireless microsystem is small, typically a few hundred mV. Diode bridge-based rectification approaches become very inefficient as the voltage loss across the diodes is significant as compared with the amplitude of the incoming RF signal. Voltage multipliers that are evolved from the well-know voltage doubler are required to perform RF-to-DC conversion and at the same time to yield a dc voltage that is many times the amplitude of the incoming RF signal.

This section investigates design techniques for voltage multipliers of passive wireless microsystems. The design constraints of voltage multipliers and the techniques that improve the power efficiency of voltage multipliers are studied. The principle and operation of diode bridges, both half-wave and full-wave diode bridges, are readily available in standard texts on microelectronics and will therefore not be presented here.

#### 2.2.1 Voltage Doubler

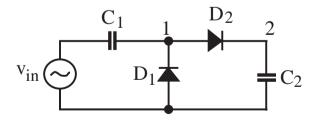

Shown in Fig.2.2 is the schematic of a widely used voltage doubler. It consists of a voltage peak detector formed by D2 and C2 and a voltage clamper formed by D1 and C1. If we assume that the diodes are ideal, i.e. the forward conduction voltage is zero, and let the amplitude of the input ac voltage be  $V_m$ , it can be shown that voltage of the output of the voltage doubler is  $2V_m$ . To demonstrate this, let us assume initially  $V_{C1} = 0$ ,  $V_{C2} = 0$ , and  $C_1 = C_2$ .

During the first negative half-cycle of the input voltage, D1 will be forward biased. C1 in this case will be charged to a voltage equal to the peak amplitude  $V_m$  of the input. During the following positive half cycle of the input voltage, D1 will be reverse biased and therefore will not conduct current. The voltage across C1 will remain unchanged and will add on to the input voltage, in other word,  $V_1 = v_{in} + V_m$  during this half cycle. Since D2 is forward biased,  $C_2$  will be changed all the way to  $2V_m$ .

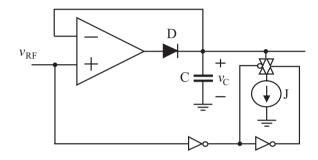

Figure 2.2. Voltage doubler.

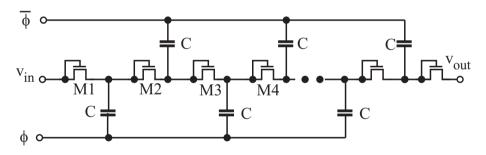

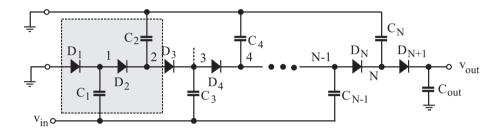

#### 2.2.2 Cockcroft-Walton Voltage Multiplier

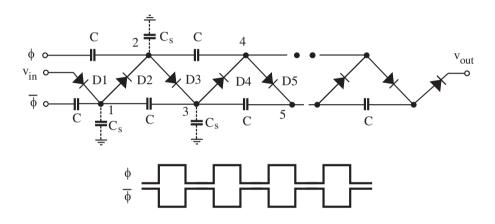

To obtain a dc voltage that is more than  $2V_m$ , a multi-stage configuration of voltage doublers is needed. Perhaps the most cited early implementation of voltage multipliers is Cockcroft-Walton voltage multiplier shown in Fig.2.3 [20]. The efficient multiplication of Cockcroft-Walton voltage multiplier will only occur if the capacitance of the coupling capacitors C is much larger as compared with the stray capacitance  $C_s$  at the coupling nodes [21]. This is because the clocking signals  $\phi$  and  $\overline{\phi}$  only drive the first two coupling capacitors. All other coupling capacitors are connected in series with the stray capacitors. The effectiveness of Cockcroft-Walton voltage multiplier largely diminishes in monolithic integration where stray capacitance  $C_s$  and C become comparable.

Figure 2.3. Cockcroft-Walton voltage multiplier [20].

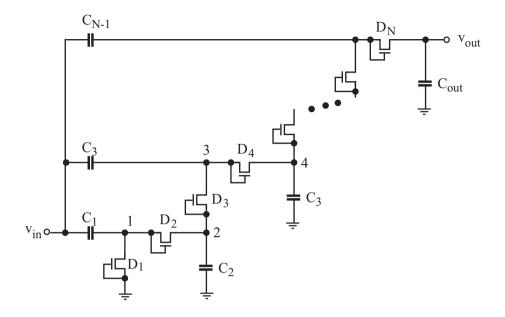

#### 2.2.3 Dickson Voltage Multipliers

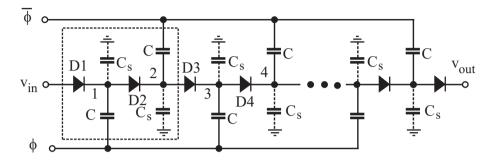

Dickson modified Cockcroft-Walton voltage multiplier by injecting clocking signals  $\phi$  and  $\overline{\phi}$  to all the coupling nodes, as shown in Fig.2.4, such that both the coupling and stray capacitors are driven by the clocking signals directly [21]. The drawback of Cockcroft-Walton voltage multiplier is therefore eliminated. Because these capacitors are connected in parallel, the shunt capacitor connected to the output node of the Dickson voltage multiplier must withstand the full output voltage. It was shown in [34] that the output voltage of a N-stage diode-based Dickson voltage multiplier is given by

$$V_{DC} = N(V_m - V_T), (2.12)$$

where  $V_T$  is the forward conduction voltage of the diodes and N is the number of stages. To boost the output voltage, the threshold voltage of the rectifying diodes must be minimized. Schottky diodes are widely used in Dickson voltage multipliers due to their low forward conduction voltage, large saturation current, low junction capacitance, and small series resistance [34].

Figure 2.4. Dickson voltage multiplier with diode switches [21].

Dickson voltage multipliers can also be implemented using MOSFET diodes, as shown in Fig.2.5. pMOS Dickson voltage multipliers can also be constructed in a similar way. The advantage of these configurations is their full compatibility with standard CMOS technologies with a main drawback of the voltage loss across the MOSFET devices of at least one threshold voltage. This is accompanied with a low power efficiency, especially when the amplitude of the input voltage is low.

Figure 2.5. Dickson voltage multiplier with nMOS diodes.

The preceding Dickson voltage multiplier with MOSFET diodes suffers from the drawback of the voltage loss of at least one threshold voltage across the MOSFETs. The observation that the voltage drop across of the drain and source of a MOSFET is low if the device is operated in the triode region suggests that the voltage loss of MOSFET diodes can be minimized by connecting a MOSFET working in the triode in parallel with each of the MOSFET diodes, as shown in Fig.2.6 [22]. We term this voltage multiplier Dickson voltage multiplier with static charge transfer switches. The operation of this voltage multiplier is depicted as follows : When  $\phi = 0$ ,  $V_1$  is initially zero and transistor M1A is on.  $C_1$  is charged by the input voltage. Note that without transistor M1B, the maximum voltage of  $V_1$  will only reach  $V_m - V_T$ , where  $V_m$  is the amplitude of  $V_{in}$  and  $V_T$  is the threshold voltage of MOSFETs. Since M2A is off, the gate voltage of M1B is at  $V_{DD}$  and M1B is in the triode. As a result,  $V_{1,max} = V_m - V_{ds1} \approx V_m$ . The drawback of the voltage loss of Dickson voltage multipliers is therefore removed. It was demonstrated in [22] that with  $v_{in} = 1.5$ V and  $I_{out} = 10\mu$ A, the output voltage of a 4-stage Dickson voltage multiplier with static charge transfer switches is approximately 4 V. The output voltage of a corresponding conventional Dickson voltage multiplier is only 2 V.

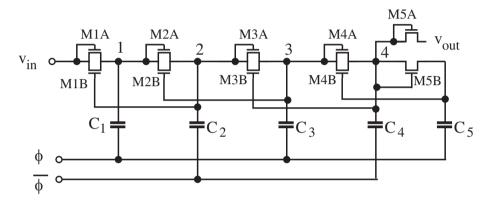

Figure 2.6. Dickson voltage multiplier with static charge transfer switches [22].

San *et al.* proposed bootstrapped gate transfer switches to replace MOSFET diodes of Dickson voltage multiplier, as shown in Fig.2.7 [23]. For each transistor, there are five additional transistors  $M_{1a,...,5a}$  and one capacitor  $C_a$  are added. When  $\phi = 1$ ,  $M_{1a,3a,5a}$  are ON while  $M_{2a,4a}$  are OFF. As a result,  $V_{B,C} = 0$ ,  $V_A = V_m$ , and  $C_a$  is charged to  $V_m$ . In the following phase where  $\phi = 0$ ,  $M_{1a,3a,5a}$  are OFF and  $M_{2a,4a}$  are ON. The voltage of the capacitor  $C_a$  is applied between the gate and drain of  $M_2$ . For MOSFETs in the triode,  $V_{DS} \leq V_{GS} - V_T$  must be satisfied. Referring to Fig.2.7(b), re-write the preceding condition for the MOSFET in the triode

$$V_D - V_S \ge V_D - V_b - V_S - V_T, \tag{2.13}$$

where  $V_b$  is the voltage applied between the gate and the drain of the MOSFET. It follows that  $V_b - V_T > 0$ . It becomes evident that if  $V_b > V_T$ ,  $M_2$  will be in the triode region and  $V_{DS2}$  will be small. In was shown in [23] that the output voltage of a 4-stage Dickson voltage multiplier with bootstrapped gate transfer switches,  $C_{1-4} = 15 \text{ pF}$ ,  $C_{out} = 30 \text{ pF}$ , f = 5 MHz, and  $V_m = 2\text{V}$ , is 9 V approximately. The output voltage is only 4 V approximately with static charge transfer switches. The power conversion efficiency is increased from 40% approximately with static charge transfer switches to above 90% with bootstrapped gate transfer switches.

Figure 2.7. Dickson voltage multiplier with bootstrapped gate transfer switches [23].

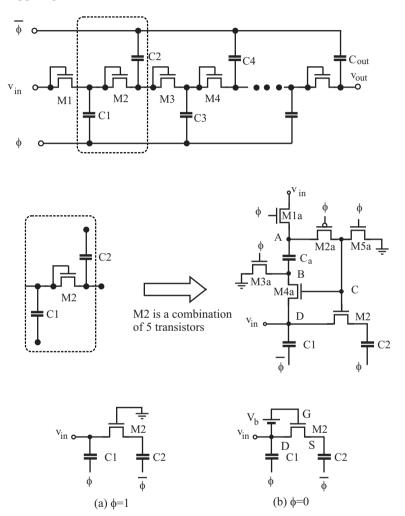

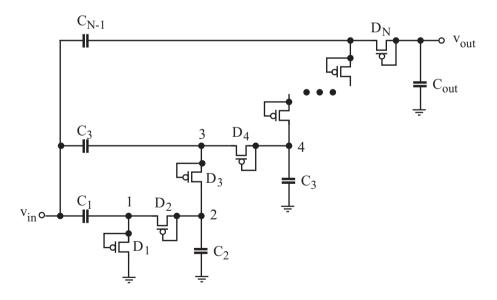

#### 2.2.4 Modified Dickson Voltage Multipliers

Dickson voltage multiplier requires non-overlapping clock signals  $\phi$  and  $\overline{\phi}$ . For power telemetry, only one RF signal is available. Dickson voltage multiplier therefore can not be used directly. The fact that the clocking signal

$\phi$  and  $\overline{\phi}$  are applied to every coupling node of Dickson voltage multiplier suggests that if  $\overline{\phi}$  and  $v_{in}$  terminals are grounded and the RF input is connected to  $\phi$  terminal, as shown in Fig.2.8, each section, as highlighted in the figure, becomes a voltage doubler. This configuration is termed modified Dickson voltage multiplier, in distinction from the original Dickson voltage multiplier studied earlier. Because the input signal is coupled to every other node of the diode chain, the effect of the stray capacitance is suppressed effectively. Clearly if a fully differential input is available,  $v_{in+}$  and  $v_{in-}$  can be coupled to  $C_{1,3,5,...}$  and  $C_{2,4,6,...}$  to further improve the performance.

Figure 2.8. Modified Dickson voltage multiplier with diode switches.

The schematic of modified Dickson voltage multipliers with nMOS-diodes is shown in Fig.2.9 and that with pMOS-diode is shown in Fig.2.10. Because the voltage drop across the drain and source of the MOSFETs is at least one threshold voltage, the efficiency of this voltage multiplier is lower as compared with that of its Schottky-diode counterpart. To overcome this drawback, native nMOS transistors whose threshold voltage is approximately zero have been used [24, 25]. The main drawback is that native MOS structure is not generally supported. Also, the large channel resistance of native MOSFETs deteriorates the performance.

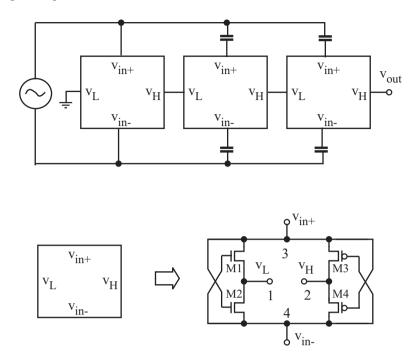

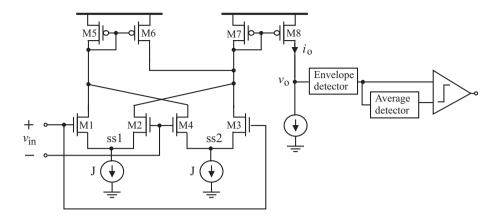

#### 2.2.5 Mandal-Sarpeshkar Voltage Multiplier

To overcome the drawback of modified Dickson voltage multiplier with MOSFET-diodes, Mandal and Sarpeshkar proposed a low-power high power efficiency voltage multiplier with its configuration shown in Fig.2.11 [26]. It is ready to verify that once a load is connected between nodes 1 and 2, the current flowing through the load is always in the same direction. A key advantage of this voltage multiplier is the low voltage drop across switching MOSFETs. As a result, a large voltage exists at the output of the rectifying cell and is given by  $V_{out,max} = V_m - (V_{DS,n} + V_{SD,p})$ . The modular configuration of Mandal-Sarpeshkar voltage multiplier offers the flexibility of adjusting the size of each stage to obtain optimal performance.

Figure 2.9. Modified Dickson voltage multiplier with nMOS transistors.

Figure 2.10. Modified Dickson voltage multiplier with pMOS transistors.

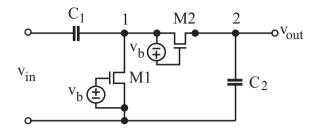

# 2.2.6 Voltage Multiplier with V<sub>T</sub>-Cancellation

Umeda *et al.* proposed an elegant mechanism shown in Fig.2.12 to minimize the voltage drop across MOSFET switches so as to increase the power efficiency of voltage multipliers [27]. For  $M_1$ , because

*Figure 2.11.* Mandal-Sarpeshkar voltage multiplier. If  $v_{in+} = V_m$  and  $v_{in-} = 0$ ,  $M_{2,3}$  are in the triode (provided that  $V_m$  is large enough) and  $M_{1,4}$  are off. The voltage drop across  $M_{2,3}$  is low [26].

$$V_{G1} = V_m + V_b, (2.14)$$

where  $V_{G1}$  is the gate voltage of M1, we have

$$V_{out} = 2(V_{GS,max} - V_T) = 2(V_m + V_b - V_T).$$

(2.15)

If we set  $V_b = V_T$ , then  $V_{out} = 2V_m$  follows. The power efficiency loss caused by the threshold voltage of MOSFETs is eliminated completely. The required compensation voltage  $V_b$  can be obtained in various ways. The approach given in [27] used an external voltage source and a switched capacitor array to generate a set of  $V_b$  for all the transistors.

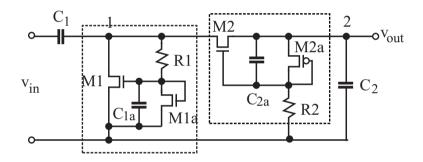

Nakamoto *et al.* proposed an internal threshold voltage generation mechanism to eliminate the voltage drop across MOSFETs without the need for an external voltage source, as shown in Fig.2.13 [28]. The voltage dividers formed by  $R_1$  and  $M_{1a}$ , and  $R_2$  and  $M_{2a}$  provide the required gate voltages for  $M_1$  and  $M_2$ , respectively. These voltages are held by  $C_{1a}$  and  $C_{2a}$ , respectively. The values of  $R_1$  and  $R_2$  should be made large to minimize the static

Figure 2.12. Umeda voltage multiplier with external threshold voltage cancellation [27].

power consumption of the compensation transistors  $M_{1a,2a}$ . Implemented in a 0.35 $\mu$ m CMOS technology with an input at 953 MHz, the power efficiency of Nokamoto voltage multiplier at 4-meter distance from a 4 W base station is 36.6% while that of Umeda voltage multiplier is only 16.6%.

Figure 2.13. Nakamoto voltage multiplier with internal threshold voltage cancellation [28].

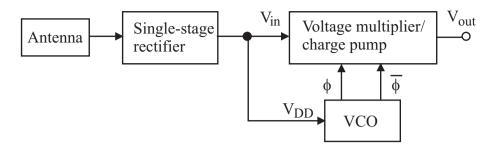

### 2.2.7 Bergeret Voltage Multiplier

Bergeret *et al.* pointed out that an important reason of the low power efficiency of Dickson voltage multipliers including modified Dickson is the propagation of high-frequency signals throughout the circuits [45]. The large area associated with multi-stage voltage multipliers gives rise to a higher substrate loss, subsequently a low power efficiency. Bergeret *et al.* modified the configuration of conventional voltage multiplier by only using a single-stage rectifier to generate a dc voltage. This voltage is then used to power a low-frequency VCO whose outputs, together with the output of the single-stage rectifier, are used to drive a high-efficiency voltage multiplier proposed in [46, 47]. It was demonstrated that this voltage multiplier improved the power efficiency by 14% over the conventional modified Dickson voltage multiplier and the output voltage is 1.5 times that of the modified Dickson voltage multiplier.

Figure 2.14. Voltage multiplier proposed by Bergeret et al. [45].

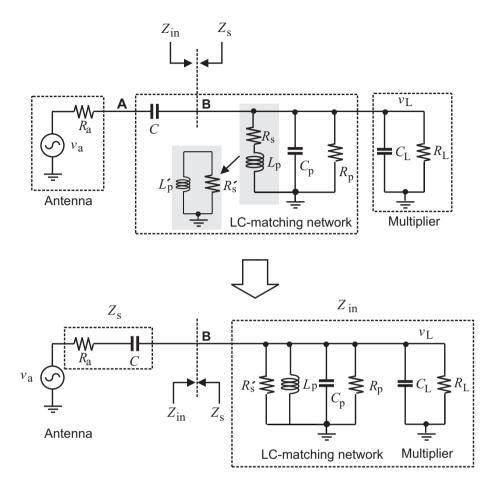

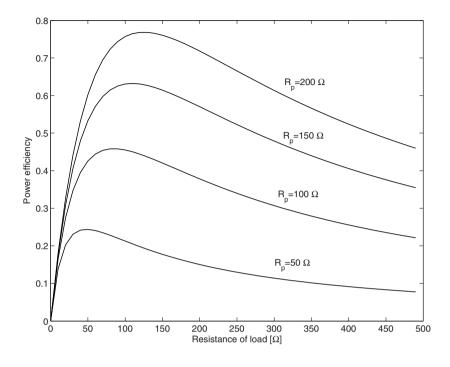

## 2.3 Power-Matching and Gain-Boosting Using LC Tanks

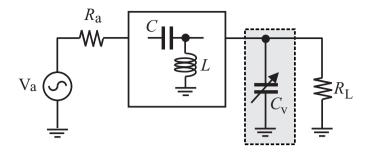

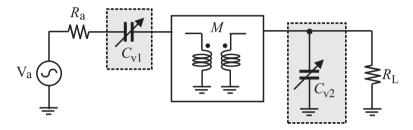

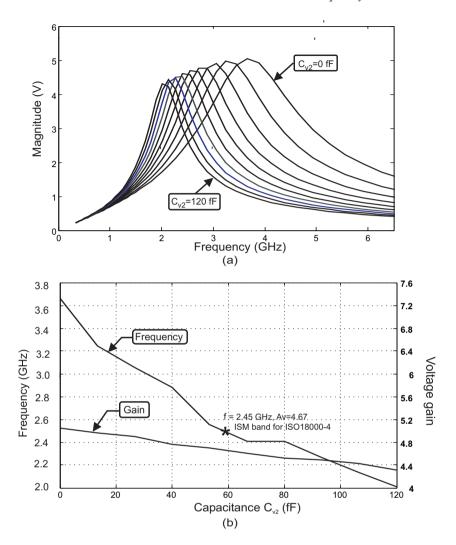

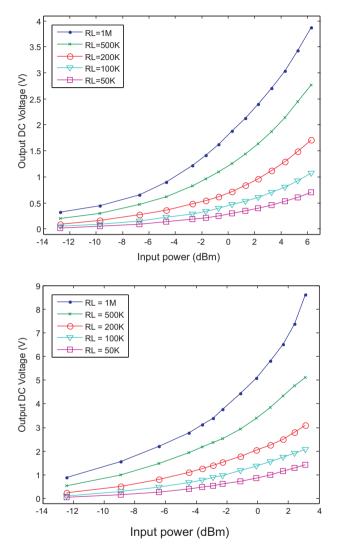

Voltage multipliers implemented in standard CMOS technologies suffer from a low efficiency. It was shown in [34] that to boost the power efficiency of the voltage multiplier, the amplitude of the voltage from the antenna of passive wireless microsystems must be maximized. The radiation resistance of the antenna of a passive wireless microsystem is determined by the dimension and type of the antenna. The finite antenna dimension of the passive wireless microsystem limits the voltage across the antenna to be small. As a result, an impedance transformation network that converts the input impedance of the downstream voltage multiplier to the matching impedance of the antenna for the maximum power transmission is inserted between the antenna and the voltage multiplier. In [48], a shunt inductor power-matching network between the antenna and voltage multiplier was employed to resonate out the capacitive part of the input impedance of the voltage multiplier. No attempt, however, was made to match the real part of the input impedance of the multiplier to the radiation resistance of the antenna, leaving the task of power-matching entirely to the voltage multiplier. De Vita and Iannaccone proposed a LC powermatching network that consists of one floating inductor, a shunt capacitor, and a grounded inductor [42]. The grounded inductor is used to resonate out the input capacitance of the downstream voltage multiplier while the LC network provides the matching impedance and voltage gain. The LC power-matching network used by Shameli et al. consists of a grounded inductor and a floating capacitor [25].

Power-matching and gain-boosting can be achieved simultaneously by inserting a passive impedance transformation network consisting of a spiral inductor and a metal-insulator-metal (MIM) capacitor between the antenna and the multiplier, as shown in Fig.2.1 [25]. The impedance transformation network provides a matching impedance to the antenna in order to maximize the power transmission from the antenna to the impedance transformation network at the carrier frequency. At the same time, it resonates at the carrier frequency such that the voltage at the output of the impedance transformation network or the input of the following voltage multiplier is maximized. Since spiral inductors suffer from both a resistive loss mainly due to the ohmic loss of the spiral and a capacitive loss due to the shunt capacitance between the spiral and the substrate, power matching, power loss, and voltage gain of the impedance transformation network must be considered simultaneously in design.

To maximize the amount of the power transferred from the antenna to the impedance transformation network, the impedance transformation network in Fig.2.1 must be designed in such a way that

$$z_{in} = R_a. (2.16)$$

Fig.2.15 shows a simplified schematic of a power-matching and gain-boosting network using a shunt spiral inductor and a series MIM capacitor. To simplify analysis, the MIM capacitor is assumed to be ideal and is represented by an ideal capacitor C. The spiral inductor is modeled using the RLC network with  $R_s$  and  $R_p$  the series and shunt parasitic resistances, respectively, and  $C_p$  the parasitic shunt capacitore. The voltage multiplier is modeled using resistor  $R_L$  in parallel with capacitor  $C_L$ .

To facilitate analysis, the branch consisting  $R_s$  and  $L_p$  is replaced with its equivalent parallel  $R'_s \sim L'_p$  network shown in Fig.2.15 with  $R'_s$  and  $L'_p$  given by [49]

$$L'_{p} = L_{p} \left[ 1 + \left( \frac{R_{s}}{\omega L_{p}} \right)^{2} \right],$$

$$R'_{s} = R_{s} \left[ 1 + \left( \frac{\omega L_{p}}{R_{s}} \right)^{2} \right].$$

(2.17)

For practical spiral inductors,  $\omega L_p \gg R_s$  holds, i.e. the reactance of the inductor is much larger than the resistance of the inductor. As a result,  $L'_p \approx L_p$  follows.

It is conveniently to show that the matching condition for the maximum power transfer at node A can be shifted to node B. Moving the impedance matching point from node A to node B will greatly simplify analysis, as to be seen shortly. The impedance matching condition in this case becomes

$$Z_{in} = Z_s^*.$$

(2.18)

Let

*Figure 2.15.* Power-matching and gain-boosting network using a shunt spiral inductor and a series MIM capacitor.

$$Z_{in} = R_{in} + jX_{in}, \qquad (2.19)$$

and

$$Z_s = R_s + jX_s, \tag{2.20}$$

where  $R_{in}$  and  $X_{in}$  are the resistance and reactance of the impedance looking into the impedance transformation network,  $R_s$  and  $X_s$  are the resistance and reactance of the impedance looking into the source network. Submitting these results into (2.18) yields

$$R_{in} = R_s,$$

$$X_{in} = -X_s.$$

(2.21)

Since

$$Y_{in} = \frac{1}{Z_{in}} = \frac{R_{in} - jX_{in}}{R_{in}^2 + X_{in}^2},$$

(2.22)

and

$$Y_s = \frac{1}{Z_s} = \frac{R_s - jX_s}{R_s^2 + X_s^2},$$

(2.23)

if

$$R_{in} = R_s$$

and  $X_{in} = X_s$ , we have

$$Y_L = Y_s^*. \tag{2.24}$$

Eq.(2.24) confirms that impedance matching is the same as admittance matching in maximizing power transfer.

The input impedance  $Z_{in}$  is given by

$$Z_{in} \approx R_{eq} || j\omega L_p$$

=  $\frac{j\omega R_{eq}^2 L_p + \omega^2 R_{eq} L_p^2}{R_{eq}^2 + (\omega L_p)^2},$  (2.25)

where

$$R_{eq} = R'_s ||R_p||R_L (2.26)$$

is the total shunt resistance. Note that we have neglected the shunt capacitances in (2.25) to simplify analysis because the gain provided by the impedance transformation network is mainly due to  $R_{eq}$ , as to be seen shortly. Matching the impedance at node B yields

$$R_{a} = \frac{\omega^{2} R_{eq} L_{p}^{2}}{R_{eq}^{2} + (\omega L_{p})^{2}},$$

(2.27)

and

$$\frac{1}{\omega C} = \frac{\omega R_{eq}^2 L_p}{R_{eq}^2 + (\omega L_p)^2}.$$

(2.28)

It follows from (2.27) that

$$\frac{R_{eq}}{R_a} = Q_p^2 + 1,$$

(2.29)

where

$$Q_p = \frac{R_{eq}}{\omega L_p} \tag{2.30}$$

is the quality factor of the shunt  $R \sim L$  network consisting of the spiral inductor and the voltage multiplier with the shunt capacitances neglected. Similarly, one can show from (2.28) that the frequency at which the impedance matching condition is satisfied is given by

$$\omega = \omega_o \sqrt{1 + \frac{1}{Q_p^2}},\tag{2.31}$$

where

$$\omega_o = \frac{1}{\sqrt{L_p C}} \tag{2.32}$$

is the resonant frequency of the ideal LC impedance transformation network.

Let us now matching the admittance at node B. Because

$$Y_{in} = \frac{1}{R_{eq}} + j \left[ \omega C'_p - \frac{1}{\omega L_p} \right], \qquad (2.33)$$

and

$$Y_s = \frac{1}{R_a + \frac{1}{j\omega C}} = \frac{\omega^2 C^2 R_a + j\omega C}{1 + (\omega R_a C)^2},$$

(2.34)

where

$$C'_{p} = C_{L} + C_{p}.$$

(2.35)

we have

$$\frac{1}{R_{eq}} = \frac{\omega^2 R_a C^2}{1 + (\omega R_a C)^2},$$

(2.36)

and

$$\omega C'_p - \frac{1}{\omega L_p} = -\frac{\omega C}{1 + (\omega R_a C)^2},$$

(2.37)

Solving (2.36) yields

$$\frac{R_{eq}}{R_a} = Q_a^2 + 1,$$

(2.38)

where

$$Q_a = \frac{1}{\omega R_a C} \tag{2.39}$$

is the quality factor of  $R_a \sim C$  network. Solving (2.37) and noting that  $Q_a \gg 1$  yield the frequency at which the admittance matching is satisfied

$$\omega \approx \frac{\omega_p}{\sqrt{1 + \frac{C}{C_p'}}},\tag{2.40}$$

where

$$\omega_p = \frac{1}{\sqrt{L_p C_p'}} \tag{2.41}$$

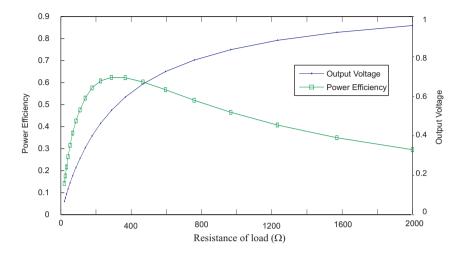

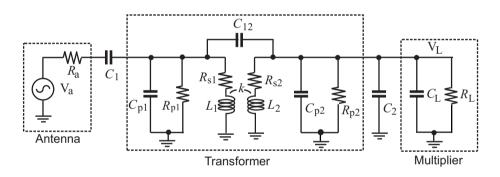

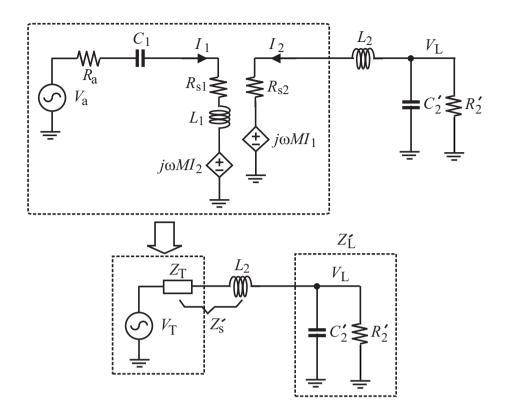

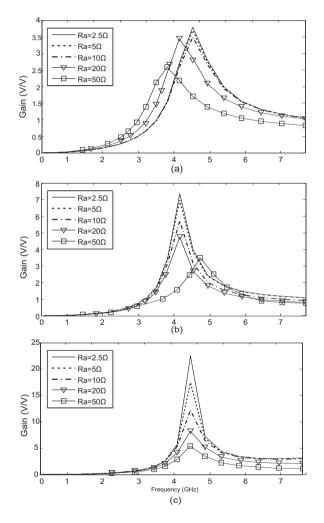

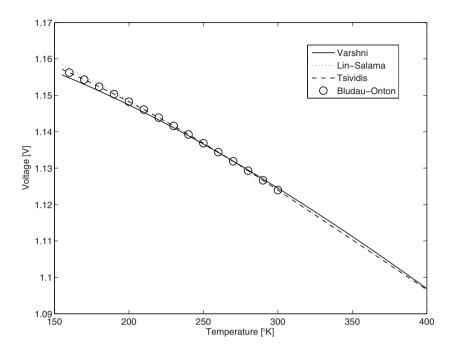

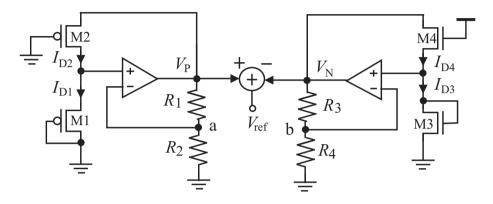

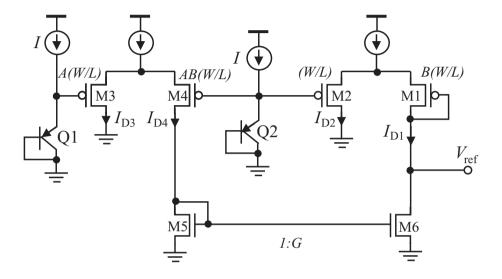

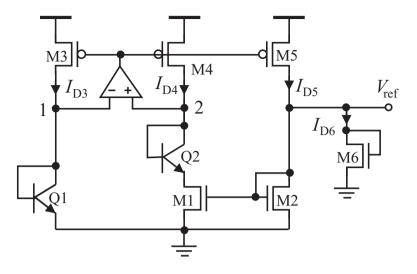

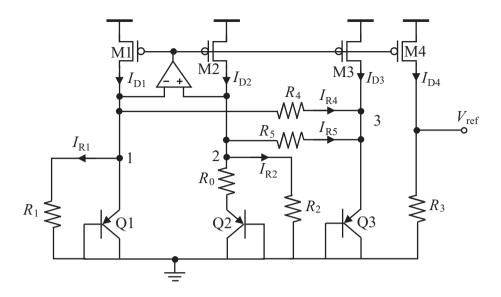

is the resonant frequency of the shunt network.