Guy Gogniat · Dragomir Milojevic Adam Morawiec · Ahmet Erdogan *Editors*

# Algorithm-Architecture Matching for Signal and Image Processing

Best papers from Design and Architectures for Signal and Image Processing 2007 & 2008 & 2009

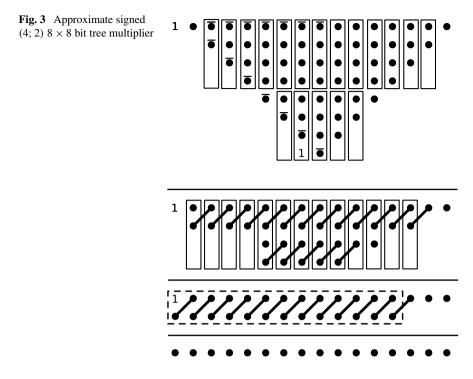

Volume 73

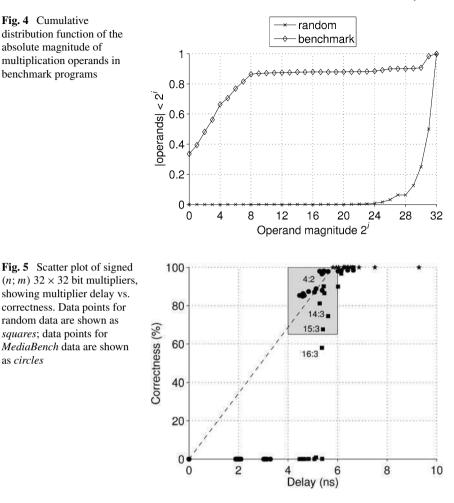

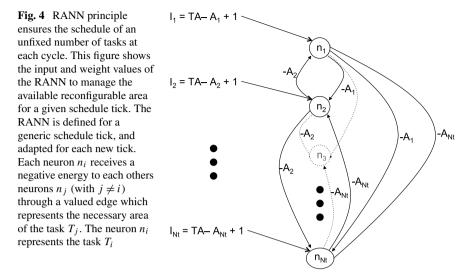

For other titles published in this series, go to www.springer.com/series/7818

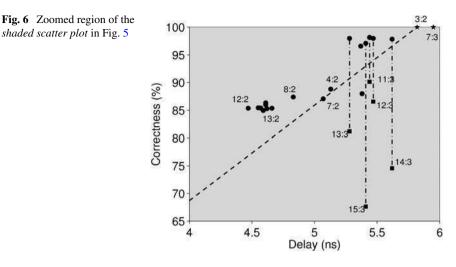

Guy Gogniat • Dragomir Milojevic • Adam Morawiec • Ahmet Erdogan Editors

## Algorithm-Architecture Matching for Signal and Image Processing

Best papers from Design and Architectures for Signal and Image Processing 2007 & 2008 & 2009

*Editors* Guy Gogniat Lab-STICC-CNRS, UMR 3192, Centre de Recherche Université de Bretagne Sud – UEB BP 92116 56321 Lorient Cedex France guy.gogniat@univ-ubs.fr

Dragomir Milojevic Université libre de Bruxelles CP 165-56, Av. FD Roosevelt 50 1050 Bruxelles Belgium dmilojev@ulb.ac.be Adam Morawiec ECSI Av. de Vignate 2 38610 Gières France adam.morawiec@ecsi.org

Ahmet Erdogan School of Engineering The University of Edinburgh Mayfield Road EH9 3JL Edinburgh United Kingdom ahmet.erdogan@ee.ed.ac.uk

ISSN 1876-1100

e-ISSN

ISBN 978-90-481-9964-8

e-ISBN

DOI 10.1007/978-90-481-9965-5

springer Dordrecht Heidelberg London New York

e-ISSN 1876-1119 e-ISBN 978-90-481-9965-5

Library of Congress Control Number: 2010938790

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: VTEX, Vilnius

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

Advances in signal and image processing together with increasing computing power are bringing mobile technology closer to applications in a variety of domains like automotive, health, telecommunication, multimedia, entertainment and many others. The development of these leading applications, involving a large diversity of algorithms (e.g. signal, image, video, 3D, communication, cryptography) is classically divided into three consecutive steps: a theoretical study of the algorithms, a study of the target architecture, and finally the implementation. Such a linear design flow is reaching its limits due to intense pressure on design cycle and strict performance constraints. The approach, called Algorithm-Architecture Matching, aims to leverage design flows with a simultaneous study of both algorithmic and architectural issues, taking into account multiple design constraints, as well as algorithm and architecture optimizations, that couldn't be achieved otherwise if considered separately. Introducing new design methodologies is mandatory when facing the new emerging applications as for example advanced mobile communication or graphics using sub-micron manufacturing technologies or 3D-Integrated Circuits. This diversity forms a driving force for the future evolutions of embedded system designs methodologies.

The main expectations from system designers' point of view are related to methods, tools and architectures supporting application complexity and design cycle reduction. Advanced optimizations are essential to meet design constraints and to enable a wide acceptance of these new technologies.

This book presents a collection of selected contributions addressing different aspects of Algorithm-Architecture Matching approach ranging from sensors to architectures design. The scope of this book reflects the diversity of potential algorithms, including signal, communication, image, video, 3D-Graphics implemented onto various architectures from FPGA to multiprocessor systems. Several synthesis and resource management techniques leveraging design optimizations are also described and applied to numerous algorithms.

The contributions of this book are split into three parts addressing major issues when designing embedded systems. The first part proposes key contributions in the domain of architectures for embedded applications and especially for image and telecommunication processing. The second part focuses on data acquisition and design techniques for embedded systems. First, an optimized sensor for image acquisition is detailed. Then several multiplication and division operators are described. The end of this part proposes several contributions in the domain of partial and dynamic reconfiguration for signal and image processing. This technology leads to complex design issues which are addressed in this chapter. The third part targets embedded systems design. RTOS for embedded systems and scheduling techniques are first addressed. Finally CAD tools for signal and image processing are detailed. The coverage of this book is large and provides an in-depth analysis of existing techniques and methodologies to design embedded systems targeting image and signal processing.

> Guy Gogniat Dragomir Milojevic Adam Morawiec Ahmet Erdogan

## Contents

#### Part 1 Architectures for Embedded Applications

| Lossless Multi-Mode Interband Image Compression and Its Hardware<br>Architecture                                                                                                  | 3  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Xiaolin Chen, Nishan Canagarajah, and Jose L. Nunez-Yanez                                                                                                                         |    |

| Efficient Memory Management for Uniform and Recursive Grid Traversal<br>Tomasz Toczek and Stéphane Mancini                                                                        | 27 |

| Mapping a Telecommunication Application on a Multiprocessor         System-on-Chip       Daniela Genius, Etienne Faure, and Nicolas Pouillon                                      | 53 |

| Part 2 Data Acquisition and Embedded Systems                                                                                                                                      |    |

| A Standard 3.5T CMOS Imager Including a Light Adaptive System for<br>Integration Time Optimization                                                                                | 81 |

| Approximate Multiplication and Division for Arithmetic Data ValueSpeculation in a RISC ProcessorDaniel R. Kelly, Braden J. Phillips, and Said Al-Sarawi                           | 95 |

| RANN: A Reconfigurable Artificial Neural Network Model for Task<br>Scheduling on Reconfigurable System-on-Chip 1<br>Daniel Chillet, Sébastien Pillement, and Olivier Sentieys     | 17 |

| A New Three-Level Strategy for Off-Line Placement of Hardware Tasks<br>on Partially and Dynamically Reconfigurable Hardware 1<br>Ikbel Belaid, Fabrice Muller, and Maher Benjemaa | 45 |

| End-to-End Bitstreams Repository Hierarchy for FPGA Partially<br>Reconfigurable Systems                                                                                           | 71 |

| Part 3 | Embedded | Systems | Design |

|--------|----------|---------|--------|

|--------|----------|---------|--------|

| SystemC Multiprocessor RTOS Model for Services Distribution on<br>MPSoC Platforms                                                                                                                  | 7 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| A List Scheduling Heuristic with New Node Priorities and Critical Child<br>Technique for Task Scheduling with Communication Contention 21<br>Pengcheng Mu, Jean-François Nezan, and Mickaël Raulet | 7 |

| Multiprocessor Scheduling of Dataflow Programs within the<br>Reconfigurable Video Coding Framework                                                                                                 | 7 |

| A High Level Synthesis Flow Using Model Driven Engineering 25<br>Sébastien Le Beux, Laurent Moss, Philippe Marquet, and Jean-Luc<br>Dekeyser                                                       | 3 |

| Generation of Hardware/Software Systems Based on CAL Dataflow         Description       27.         Richard Thavot, Romuald Mosqueron, Julien Dubois, and Marco         Mattavelli                 | 5 |

| Index                                                                                                                                                                                              | 3 |

## Contributors

Said Al-Sarawi CHiPTec, Centre for High Performance Integrated Technologies and Systems, The University of Adelaide, Adelaide, Australia, alsarawi@eleceng.adelaide.edu.au

**Ikbel Belaid** University of Nice-Sophia Antipolis/LEAT-CNRS, 250 rue Albert Einstein, 06560 Valbonne, France, Ikbel.Belaid@unice.fr

Maher Benjemaa National Engineering School of Sfax/Research Unit ReDCAD, Sfax, Tunisia, Maher.Benjemaa@enis.rnu.tn

Sebastien Le Beux Institut des Nanotechnologies de Lyon, Ecole Centrale de Lyon, 36, Avenue Guy de Collongue, 69134 Ecully Cedex, France, Sebastien.Le-Beux@ec-lyon.fr

**Pierre Bomel** LAB-STICC, Université Européenne de Bretagne, Lorient, France, pierre.bomel@univ-ubs.fr

Jani Boutellier Computer Science and Engineering Laboratory, University of Oulu, Oulu, Finland, jani.boutellier@ee.oulu.fi

Nishan Canagarajah University of Bristol, Bristol, UK, Nishan.Canagarajah@bristol.ac.uk

Xiaolin Chen University of Bristol, Bristol, UK, Xiaolin.Chen@bristol.ac.uk

**Daniel Chillet** University of Rennes 1, IRISA/INRIA, BP 80518, 6 rue de Kerampont, F22305 Lannion, France, Daniel.Chillet@irisa.fr

Jérémie Crenne LAB-STICC, Université Européenne de Bretagne, Lorient, France, jeremie.crenne@univ-ubs.fr

**Jean-Luc Dekeyser** LIFL and INRIA Lille Nord-Europe, Parc Scientifique de la Haute Borne, Park Plaza, Bât A, 40 avenue Halley, Villeneuve d'Ascq 59650, France, Jean-Luc.Dekeyser@lifl.fr

Jean-Philippe Diguet LAB-STICC, Université Européenne de Bretagne, Lorient, France, jean-philippe.diguet@univ-ubs.fr

Julien Dubois Laboratoire LE2I, Université de Bourgogne, 21000 Dijon, France, julien.dubois@u-bourgogne.fr

**Etienne Faure** SoC Department, LIP6, 4 place Jussieu, 75252 Paris Cedex, France, etienne.faure@lip6.fr

Daniela Genius SoC Department, LIP6, 4 place Jussieu, 75252 Paris Cedex, France, daniela.genius@lip6.fr

Guy Gogniat LAB-STICC, Université Européenne de Bretagne, Lorient, France, guy.gogniat@univ-ubs.fr

Victor Martin Gomez Computer Science and Engineering Laboratory, University of Oulu, Oulu, Finland, victor.martin@ee.oulu.fi

**Emmanuel Huck** ETIS Laboratory, UMR CNRS 8051, Université de Cergy-Pontoise/ENSEA, 6, avenue du Ponceau, 95014 Cergy-Pontoise, France, huck@ensea.fr

**Daniel R. Kelly** CHiPTec, Centre for High Performance Integrated Technologies and Systems, The University of Adelaide, Adelaide, Australia, dankelly@eleceng.adelaide.edu.au

Estelle Labonne TIMA Laboratory (CNRS, Grenoble INP, UJF), Grenoble, France

**Thomas Lefebvre** ETIS Laboratory, UMR CNRS 8051, Université de Cergy-Pontoise/ENSEA, 6, avenue du Ponceau, 95014 Cergy-Pontoise, France, lefebvre@ensea.fr

**Christophe Lucarz** Microelectronic Systems Laboratory, École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, christophe.lucarz@epfl.ch

**Stéphane Mancini** GIPSA-lab, INPG-CNRS, 961 rue de la Houille Blanche Domaine Universitaire-B.P. 46, 38402, Saint Martin d'Heres, France, stephane.mancini@gipsa-lab.inpg.fr

**Philippe Marquet** LIFL and INRIA Lille Nord-Europe, Parc Scientifique de la Haute Borne, Park Plaza, Bât A, 40 avenue Halley, Villeneuve d'Ascq 59650, France, Philippe.Marquet@lifl.fr

**Marco Mattavelli** SCI-STI-MM, Ecole Polytechnique Fédérale de Lausanne, CH 1015 Lausanne, Switzerland, marco.mattavelli@epfl.ch

**Marco Mattavelli** Microelectronic Systems Laboratory, École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, marco.mattavelli@epfl.ch

**Benoît Miramond** ETIS Laboratory, UMR CNRS 8051, Université de Cergy-Pontoise/ENSEA, 6, avenue du Ponceau, 95014 Cergy-Pontoise, France, miramond@ensea.fr

**Romuald Mosqueron** SCI-STI-MM, Ecole Polytechnique Fédérale de Lausanne, CH 1015 Lausanne, Switzerland, romuald.mosqueron@epfl.ch

Laurent Moss Ecole Polytechnique de Montréal, Campus de l'Université de Montréal, 2500, chemin de Polytechnique, 2900 boulevard Edouard-Montpetit, Montréal, Quebec H3T 1J4, Canada, Laurent.Moss@polymtl.ca

**Pengcheng Mu** Ministry of Education Key Lab for Intelligent Networks and Network Security, School of Electronic and Information Engineering, Xi'an Jiaotong University, Xi'an 710049, P.R. China, pengchengmu@gmail.com

**Fabrice Muller** University of Nice-Sophia Antipolis/LEAT-CNRS, 250 rue Albert Einstein, 06560 Valbonne, France, Fabrice.Muller@unice.fr

Jean-François Nezan IETR/Image and Remote Sensing Group, CNRS UMR 6164/INSA Rennes, 20, avenue des Buttes de Coësmes, 35043 Rennes Cedex, France, jnezan@insa-rennes.fr

Jose L. Nunez-Yanez University of Bristol, Bristol, UK, J.L.Nunez-Yanez@bristol.ac.uk

**Braden J. Phillips** CHiPTec, Centre for High Performance Integrated Technologies and Systems, The University of Adelaide, Adelaide, Australia, phillips@eleceng.adelaide.edu.au

**Sébastien Pillement** University of Rennes 1, IRISA/INRIA, BP 80518, 6 rue de Kerampont, F22305 Lannion, France

Nicolas Pouillon SoC Department, LIP6, 4 place Jussieu, 75252 Paris Cedex, France, nicolas.pouillon@lip6.fr

**Mickaël Raulet** IETR/Image and Remote Sensing Group, CNRS UMR 6164/INSA Rennes, 20, avenue des Buttes de Coësmes, 35043 Rennes Cedex, France, mraulet@insa-rennes.fr

Robin Rolland CIME Nanotech, Grenoble, France

**Olivier Sentieys** University of Rennes 1, IRISA/INRIA, BP 80518, 6 rue de Kerampont, F22305 Lannion, France

Gilles Sicard TIMA Laboratory (CNRS, Grenoble INP, UJF), Grenoble, France

**Olli Silvén** Computer Science and Engineering Laboratory, University of Oulu, Oulu, Finland, olli.silven@ee.oulu.fi

**Richard Thavot** SCI-STI-MM, Ecole Polytechnique Fédérale de Lausanne, CH 1015 Lausanne, Switzerland, richard.thavot@epfl.ch

**Tomasz Toczek** GIPSA-lab, INPG-CNRS, 961 rue de la Houille Blanche Domaine Universitaire-B.P. 46, 38402, Saint Martin d'Heres, France, tomasz.toczek@gipsa-lab.inpg.fr

**François Verdier** ETIS Laboratory, UMR CNRS 8051, Université de Cergy-Pontoise/ENSEA, 6, avenue du Ponceau, 95014 Cergy-Pontoise, France, verdier@ensea.fr

## Part 1 Architectures for Embedded Applications

## Lossless Multi-Mode Interband Image Compression and Its Hardware Architecture

Xiaolin Chen, Nishan Canagarajah, and Jose L. Nunez-Yanez

**Abstract** This paper presents a novel Lossless Multi-Mode Interband image Compression (LMMIC) scheme and its hardware architecture. Our approach detects the local features of the image and uses different modes to encode regions with different features adaptively. Run-mode is used in homogeneous regions, while ternary-mode and regular-mode are used on edges and other regions, respectively. In regular mode, we propose a simple band shifting technique as interband prediction and a gradientbased switching strategy to select between intraband or interband prediction. We also enable intraband and interband adaptation in the run-mode and ternary-mode. The advantage of LMMIC is to adaptively "segment" the image and use suitable methods to encode different regions. The simplicity of our scheme enables the hardware amenability. Experimental results show that LMMIC achieves superior compression ratios, with the benefits of enabling encoding any number of bands and easy access to any band. We also describe the hardware architecture for this scheme.

#### **1** Introduction

The rapid advance of multimedia technology generates huge amount of image data, most of which are multispectral images. We define "multispectral images" here as images containing more than one spectral band. This includes a wide range of images from colour images to hyperspectral images. For instance, colour images, often stored as JPEG, BMP, or TIF format, have at least three bands, e.g. red, green and blue (RGB). In most printing systems, a four-band colour space CMYK (cyan, magenta, yellow and black) is commonly used. Moreover, some high fidelity image capture systems collect the spectral reflectance measured at different wavelengths

University of Bristol, Bristol, UK

DOI 10.1007/978-90-481-9965-5\_1, © Springer Science+Business Media B.V. 2011

X. Chen (🖂)

e-mail: Xiaolin.Chen@bristol.ac.uk

G. Gogniat et al. (eds.), *Algorithm-Architecture Matching for Signal and Image Processing*, 3 Lecture Notes in Electrical Engineering 73,

in order to accurately capture the colour of a physical surface. For example, the VASARI imaging system [16, 23] developed at the National Gallery in London uses a seven-channel multispectral camera to capture paintings. In remote sensing, the LANDSAT 7 [15] satellite images have seven spectral bands, and the AVIRIS (Airborne Visible/Infrared Imaging Spectrometer) [7] hyperspectral images contain 224 contiguous bands. These images form the base of the widely used web mapping services, e.g. the Google Earth. In medical imaging, multispectral images also prevail. Examples include magnetic resonance imaging (MRI) which can simultaneously measure multiple characteristics of an object [6], and medical images formed by different medical imaging modalities such as MRI, CT and X-ray [8]. These images are normally compressed for transmission and storage. As many applications, e.g. remote sensing imaging, medical imaging, pre-press imaging and archiving [30], demand perfect reconstruction of images, lossless compression on multispectral images attracts increasing interests. Also for applications that need to transmit image data instantly after acquisition, real-time compression is desirable. As software compression often suffers from huge CPU resource occupation and memory consumption, we aim to design an efficient hardware amenable lossless image compression scheme, with the capability of real-time processing.

Unlike gray-scale image, multispectral image has not only spatial but also spectral (or called interband) redundancy among different spectral bands. Moreover, the existence of multiple spectral bands suggests two problems worth of concern: (1) to encode any number of bands, which is not offered by schemes with certain restricted structure; (2) to enable random access to whichever band such that any bands can be retrieved without processing the whole multispectral image. For example, each band of the LANDSAT image contains different information of the earth – water body or vegetation moisture contents etc., and different combinations of bands give illustrations on different issues such as mineral, soil and so on [15]. Therefore, it is desirable to have random band access. Many compression schemes in literature have achieved good compression ratios, but few consider these merits.

In literature, both transform and prediction techniques are used in interband image compression. Popular transform based interband coding techniques include vector quantization [12, 14, 21], discrete cosine transform [4], discrete wavelet transform [25], and vector-lifting schemes [2]. These techniques are efficient in reducing spectral redundancy, but their high computational complexity and sometimes jointly encoding several bands (e.g. 16 bands in [25]) are obstacles for hardware implementation and real-time processing. On the other hand, predictive coding does not only perform well in removing spatial redundancy but also spectral redundancy. Wu extended Intraband CALIC [29] to Interband CALIC [30], which is claimed to offer one of the best interband compression results in literature but requires complex interband correlation coefficients calculation and context formation. SICLIC [1] is a simple and efficient coder based on LOCO-I [28], but its 3-band joint-run mode, while offering good bit rates, constrains it from encoding any number of bands.

To relieve these problems, we propose a Lossless Multi-Mode Interband image Compression (LMMIC) scheme. The proposal of this scheme is inspired by the concept of segmentation. Segmentation, in a general sense, is to partition an image into multiple segments in order to change the representation of an image into something meaningful or easy to analyse. However, traditional segmentation, e.g. statistical model-based methods [9] and graph-based methods [5], is too complex to implement in real-time compression. The novelty of our scheme is to apply the concept of segmentation to group pixels with similar features and use different methods to encode them. We called this method multi-mode strategy, where a new ternarymode is designed to detect and encode the edges and smooth areas, and a run-length coder [28] is used to encode the homogeneous regions, while the rest of the image, say the texture regions, is coded by a regular-mode which consists of intraband and interband prediction. We propose a simple band shifting technique for interband prediction and adopt the Gradient-Adjusted Prediction (GAP) from CALIC [29] for intraband prediction. A new gradient-based switch is also designed to select the better predictor in regular-mode and to allow intraband and interband adaptation in run-mode and ternary-mode. The proposed scheme does not only offer excellent compression ratios, but also the distinctive feature of the flexibility of encoding any number of bands. As LMMIC only involves a limited number of addition and shifting, it is hardware amenable. Note that the proposed scheme in this paper is for general purpose (e.g. space, medical, archiving) images with more than one spectral bands but not specifically geared for hyperspectral images. Since some of the techniques for hyperspectral images make specific use of the structure of these images, for example, by including a band ordering process [26] or by clustering a number of bands [25], we do not include those highly specialized and not necessarily hardware amenable methods in our comparison study. However, we acknowledge that refining our techniques for specific use with hyperspectral images is an interesting topic for further research, and its findings will be reported elsewhere.

This paper is organized as follows. In Sect. 2 we present an overview of LMMIC. Then we explain the core techniques – multi-mode strategy in Sect. 3 and band shifting and gradient-based switching in Sect. 4. Context modelling is briefly described in Sect. 5. The performance comparison with other state-of-the-art schemes is presented in Sect. 6. We propose the hardware architecture to support LMMIC in Sect. 7 and conclude our work in Sect. 8.

#### 2 An Overview of LMMIC

An image contains many features, such as smooth regions, edges, texture etc. The complexity of an image is an obstacle for compression, thus segmentation (also referred to as region-based methodology) is a viable approach to help with distinguishing these features. The lossless image compression method TMW [11], which achieves the best gray-scale image compression ratio so far, uses segmentation to analyse the image in the first pass. Shen [24] took advantage of the region-growing algorithm for segmentation of lossless compression of medical images. Ratakonda [20] used multiscale segmentation to encode general images. However, they are all

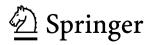

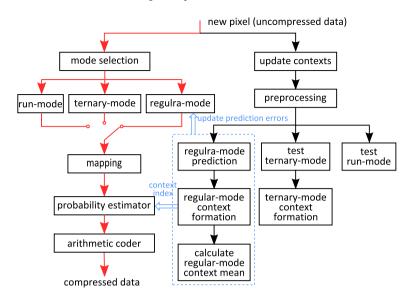

Fig. 1 Schematic of the proposed image compression system

complex two-pass schemes so cannot meet well the real-time processing requirement. Due to the complexity of segmentation, we skip the conventional segmentation methods, but instead propose to apply its concept, by using a simple switch to detect the image features adaptively, and choose suitable modes to encode these features. This switching technique resembles the function of "segmenting" the image into different areas. This is the idea that our scheme is based on.

Figure 1 shows the schematic of LMMIC. It consists of preprocessing, prediction, context modelling and arithmetic coding. At the beginning, a base band is chosen. It is encoded independently using intraband compression method. Then a preprocessing step is performed on all bands except the base band to calculate the band difference between the current band and the base band. The output of the preprocessing includes a difference band, an original band and a base band. They are then fed into the multi-mode predictor. The prediction step includes run-mode, ternary-mode and regular mode. In each mode, there is a choice between intraband and interband operations. For regular-mode, we proposed a band shifting technique for interband prediction, while the intraband prediction is based on the Gradient-Adjusted Predictor (GAP) [29]. A new gradient-based switching is designed to select the better predictor. We also enable adaptation on intraband and interband operations for runmode and ternary-mode. This multi-mode strategy applies to all bands in an image. The context modelling is constructed in a similar but simpler way as in [29] to further exploit higher order redundancy. The probability estimator and arithmetic coding are described together with the hardware architecture in Sect. 7. LMMIC offers not only very good compression ratios, but also the distinctive feature of encoding any number of bands, since the structure of our scheme does not enforce any restriction on the number of bands to be coded. The simple multi-mode strategy and switching method make it hardware amenable.

#### **3** Multi-Mode Strategy

As stated before, the multi-mode strategy is based on the concept of segmentation. As important as segmenting regions correctly in segmentation, it is crucial to carefully decide under which circumstances the system should be working under which mode, since it is exactly these entry conditions "segmenting" the image. In this section, we present how each mode works and the conditions for entering each mode. Prior to that, the preprocessing step is briefly described below.

#### 3.1 Preprocessing

In Fig. 1, to start the process, one band is chosen as base band. For instance the band G in RGB images, or the first band received in other multispectral images. The base band is coded with intraband coding only. Then a preprocessing step simply subtracts the base band from the current band to get the band difference.

$$Band_{diff} = Band_{curr} - Band_{base}.$$

(1)

This seems to be a simple act, but leads to a lot of benefits. For example in RGB images, the bands that can be used during prediction without violating the reversibility of the algorithm are

$$G, R, B, R-G, B-G.$$

(2)

Instead of having three original bands, now we have five "bands" (some are difference bands) that can be used in prediction. For images with any number of bands, there always exist an original band and a difference band for encoding each band. This enables adaptation between intraband and interband prediction. Also, in this way, each band is only coupled with the base band and no multi-band joint encoding is performed. Since the base band is coded independently, it can be retrieved any time without processing other bands. Once the base band is retrieved, the current band can be retrieved. This allows the flexibility of compressing any number of bands and enables easy access to any bands. For any bands except the base band, multi-mode strategy is applied on both the original band and the difference band.

#### 3.2 Run-Mode

Run-length coding is simple and efficient in grouping identical symbols [28]. It encodes the occurrence, i.e. the number of times that the symbol occurs consecutively, also called *run-length*. We use run-length coding to encode the homogeneous regions of the image. Figure 2 shows the neighboring pixels of the current pixel X according to their geographical positions. When W = N = NW = NE, the current pixel is assumed to be in a homogeneous region and is tried to be encoded in runmode. If X is identical to W, the run-length increases by one; otherwise "run" stops and the current run-length is encoded. The latter case means that encoding symbol in runmode.

**Fig. 2** Neighboring pixels of the current pixel

|    |    | NN | NNE |

|----|----|----|-----|

|    | NW | Ν  | NE  |

| ww | W  | х  |     |

#### 3.3 Ternary-Mode

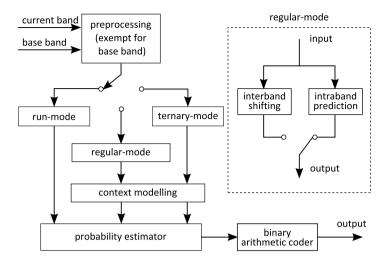

Ternary-mode is our new proposal and is inspired by the binary-mode in CALIC, which works on the binary area where there are only two different pixels in the neighborhood, e.g. black and white texts. However, unlike CALIC, our new ternarymode targets on two types of areas – clear edge areas and smooth but not exactly homogeneous areas. Edge, which appears as the abrupt changes in pixel intensity, is very difficult to predict. Therefore, instead of predicting it, we propose to record the similarity between the edge pixels and their neighbouring pixels. In areas where a sharp edge occurs, as shown in Fig. 3a, pixels on the edge tend to be the same or similar but pixels at the two sides of the edge are usually different; also, in areas where a less sharp edge occurs, as in Fig. 3b, pixel values tend to be changing gradually from non-edge area to edge area. In both cases, we assume that within a small neighborhood of the current pixel, say the seven neighbouring pixels in Fig. 2, there are no more than three distinctive symbols and the ternary-mode is triggered. In operation, pixel W as the first unique pixel value, is represented as s1. Then the other six pixels in the neighbourhood are evaluated and the second and third distinctive pixels are represented as s2 and s3, respectively. By comparing the current pixel with s1, s2 and s3, we can assign a value to the current pixel by

$$T = \begin{cases} 0, & \text{if } X = s1; \\ 1, & \text{if } X = s2; \\ 2, & \text{if } X = s3; \\ \text{escape, otherwise.} \end{cases}$$

(3)

Fig. 3 Areas where ternary-mode is performed

In other word, the current pixel can be denoted by the order of its value appearance in the neighbourhood, given the condition that the checking in the neighbourhood is always conducted in the same order. "Escape" happens when the current pixel X is not equal to any of the pixel values in the neighbourhood and thus encoding in this mode fails. It is a way of switching among different modes. Figure 3 shows the areas that the ternary-mode is performed. T indicates the symbols encoded by ternary-mode, while R indicates run-mode, and the colour is the gray-level of the symbols. The figure tells that edge areas can be largely covered by this mode.

We choose to use three distinctive pixel values but not fewer or more for the following reasons:

- 1. In the cases shown in Fig. 3, there are usually more than two distinctive pixel values in the neighbourhood. Using only two pixel values cannot adequately describe the edge conditions.

- 2. In many cases, image edges are more complicated than the ones shown in Fig. 3. However, allowing more distinctive pixel values is very likely to result in more negative than positive effect, as explained below:

- a. It makes entering the ternary-mode too easy, if four or more different pixel values are allowed in a 7 pixel neighbourhood. This would fail to characterize the specific areas that are suitable to be encoded in ternary-mode;

- b. It would lead to a lot more "escapes". Because more random areas are classified as applicable in ternary-mode, the current pixel is more likely to fail to find a match with any of the pixels in a more diverse neighbourhood;

- c. Allowing more distinctive pixel values would increase the alphabet size, and hence the bits that are needed to encode pixels.

The alphabet size for encoding in this mode is only 4 instead of 256 in the original form, so lower entropy can be obtained. Ternary-mode also works as a "backup" of the run-mode in smooth but not exactly homogeneous regions.

#### 3.4 Regular-Mode

The regular-mode is triggered, either when the entry conditions for run-mode and ternary-mode cannot be met, or when encoding in other modes fails. The regular-mode consists of intraband and inter-band prediction, which is selected according to the local features adaptively. Details of the interband prediction and switching strategy are discussed in next section.

#### 4 Band Shifting and Gradient-Based Switching

We design a simple band shifting technique for interband prediction, and adapt the GAP from CALIC [29] for intra-band prediction. However, the performance of interband prediction depends on the interband correlation. In the case of strong inter-

band correlation, interband prediction is preferred, otherwise intra-band prediction is selected. A gradient-based switching method is proposed for the selection.

#### 4.1 Band Shifting for Inter-Band Prediction

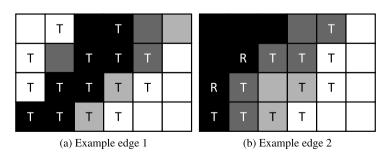

In the regions where bands are strongly correlated, pixel changes in one band often happen in another band. For instance, Fig. 4 plots the pixel values of one line in band G and band B of the image "peppers" respectively. It is clear that the dot plot of band G has a similar trend with the dash plot of band B. We also notice that although changing in a similar trend, the difference between two bands varies from areas to areas. Thus directly subtracting band B from band G tends to result in big errors. The ideal way would be to move the base band to a position that is as close to the current band as possible so that only a small difference between the current band and the shifted base band needs to be coded. There are a lot of possible ways to predict the value for band shifting. Since band shifting is only performed when the interband correlation is high, we assume that in this case the band difference is reasonably small and varies in a regular way. Therefore, we propose to use the simple Median Edge Detector [28] to predict the band shifting value. We denote the band difference at position W, N, NW as  $W_diff$ ,  $N_diff$ ,  $NW_diff$ , and calculate the band shifting by

The solid plot in Fig. 4 shows that this prediction method successfully generate a zero-mean band difference between the current band and the shifted reference band.

Fig. 4 Plots of one line in band G and band B and their difference after shifting

#### 4.2 Gradient-Based Switching

For the regular-mode in the multi-mode strategy, we use the band shifting technique for interband prediction and adopt the GAP [29] for intraband prediction. Since the performance of the two predictors varies in different regions of an image depending on the spatial and spectral correlation, it is critical to decide which predictor to use in different areas. As we aim at designing a hardware amenable scheme, complex calculation of interband correlation coefficients is not desirable. We propose a simple switching method based on the local horizontal and vertical gradients, which are calculated by

$$dh = |W - WW| + |N - NW| + |N - NE|,$$

(4)

$$dv = |W - NW| + |N - NN| + |NE - NNE|,$$

(5)

where dv and dh are the vertical and horizontal gradients, respectively. When calculating the interband gradients, W, N, NW, NE, NN, WW, NNE are substituted by the interband difference at the same positions. Interband gradients indicate how closely the two bands change in the same way. In addition to the gradients, the previous prediction error is taken into account to evaluate how well the predictor performs in the local area. Therefore, for both intraband and interband prediction, we calculate the switching coefficient *S* by

$$S = dv + dh + |e_w|,\tag{6}$$

where  $e_w$  means the prediction error at position W. The predictor that gives smaller S is selected to encode the current pixel. We counted the proportions of pixels that are treated by intraband and interband prediction in the regular-mode respectively, in band B and R on a set of RGB images in Table 1. We also calculated how often the predictor that gives smaller errors is selected, as right\_ratio. The proportions of intraband and interband prediction do not sum up to 1 because the rest pixels are processed by the run-mode or ternary-mode. On average, more than 40% interband

Image b\_intra b\_inter b\_right\_ratio r\_intra r\_inter r\_right\_ratio cmpnd1 6.41 17.66 70.13 4.62 18.64 73.33 24.10 83.63 24.91 82.21 cmpnd2 2.06 1.64 1.78 47.78 87.12 1.10 47.56 90.29 cats 5.33 44.19 76.53 3.04 45.49 82.15 water 65.90 59.36 lena 33.97 64.09 34.43 67.33 17.41 76.89 71.38 22.53 76.60 72.26 peppers 27.23 29.19 bike3 52.46 64.82 52.41 60.67 43.39 73.28 21.35 39.55 75.46 17.06 average

Table 1

Proportions of pixels using intraband and interband prediction and the ratios of the better predictor is selected in the regular mode

prediction is selected, meaning that there is a substantial amount of interband redundancy. The simple gradient-based switching technique has achieved over 70% correct choice in selecting a better predictor.

#### 4.3 Adaptation in Run-Mode and Ternary-Mode

The above gradient-based switching is not only used in selecting the intraband and interband prediction in regular-mode, but is also modified to be used in enabling adaptation in the run-mode and ternary-mode. Since the run-mode encodes pixels directly and the ternary-mode only records the similarity among pixels, there is no prediction error generated by these two modes. Therefore, we eliminate the term of error from (6) to obtain an adaptation coefficient S'.

In the run-mode, when run-length is 0, either the pixels in the current band or in the band difference is selected according to which neighbourhood gives a smaller S'. The selected pixels are used in the run-mode and a flag is used to indicate this selection. When run-length is not 0, the previously used pixel values – whether from the current band or the band difference, are used to keep the continuity of the run.

In the ternary-mode, the whole neighbourhood of pixels used for ternary-mode are selected either from the current band or the band difference based on the value of S'. Since the coefficient S' can be calculated before receiving the current pixel, it is guaranteed that the current pixel used for comparing with its neighbouring pixels is from the same source. This adaptation in run-mode and ternary-mode improves the spatial and spectral decorrelation performance of our proposed scheme in our experiments.

We show in Table 2 the effect of using the original band, difference band or the two combined in the run-mode and ternary-mode. The "adaptation" on the fourth column means choosing the bands adaptively. The resulting bit rates vary for different images, but on average, using the adaptation technique slightly improves the compression ratios.

| Image   | Current band | Difference band | Adaptation |

|---------|--------------|-----------------|------------|

| cmpnd1  | 1.117        | 1.054           | 1.057      |

| cmpnd2  | 1.037        | 0.972           | 0.969      |

| cats    | 1.813        | 1.822           | 1.823      |

| water   | 1.434        | 1.436           | 1.442      |

| lena    | 4.233        | 4.230           | 4.233      |

| peppers | 3.339        | 3.363           | 3.356      |

| bike3   | 4.274        | 4.353           | 4.289      |

| average | 2.464        | 2.461           | 2.453      |

Table 2

Compression ratios comparison on LMMIC using different neighbourhoods in the runmode and ternary-mode, in bits per pixel

#### 5 Context Modelling

Context modeling is to group the prediction residue based on some local features, named *contexts*, in order to obtain a lower conditional entropy. In the proposed scheme, context is formed in a similar manner with CALIC [29] but is simplified to reduce the memory usage. We take 6 context symbols (W, N, NW, NE, NN, WW) to compare with the predicted value to obtain a texture pattern *t*, representing the local texture feature. Also, to indicated the activity of errors in a context, the *coding contexts* are generated with the local gradients dv, dh and a previous prediction error *e* of pixel *W*. The coding contexts are then quantized into 8 levels to form the coding context indexes. Combining the texture pattern and the coding contexts, a set of 512 compound contexts are formed with 6 bits texture pattern and 3 bits coding context indexes. In the case of interband context formation, original pixel values are replaced by the band difference at the same positions. These contexts are also used to generate an error feedback to the predictor, which will be discussed in Sect. 7.1. The 8 coding contexts are used to calculate the occurrence probability of pixels in the probability estimator presented in Sect. 7.2.

#### 6 Performance Comparison

The performance of LMMIC is presented in this section. We firstly give two examples to show the areas where different modes apply in images. In example 1, Fig. 5b shows the regions where different modes are performed, comparing with the original image Fig. 5a. Run-mode works on the grey areas, which are smooth and homogeneous; ternary-mode works on the white regions, which often lie on the edge of the homogeneous regions, some smooth regions or clear edges; regular-mode works on the dark regions, which are mostly texture or noisy areas. In example 2, we only apply ternary-mode and regular-mode on image Fig. 6a to emphasize the function of ternary-mode. In Fig. 6b, white areas indicate where the ternary-mode applies, while the black areas indicate where the regular-mode applies. We can see that all the texts including those in the picture are covered by the ternary-mode, as well as some of the clear edges and homogeneous areas.

To have a quantitative measure of the proportion that the three modes apply on an image, we count the number of pixels being treated by each mode in Table 3. The "run" in the second column stands for the number of pixels being coded by the run-mode. The "ternary" in the third column means the number of pixels satisfying the entry condition of the ternary-mode, and the "successful ternary" in the fourth column means the number of pixels being successfully coded by the ternary-mode. The "successful ternary ratio" in the fifth column is the proportion of the "successful ternary" in the whole image. Table 3 shows that run-mode does not happen often except in relatively simple images like "bike3-g" and "CMPND1-G". Ternary-mode occurs more often but still takes on a small proportion, as shown in the fifth column of "successful ternary ratio". But it has a roughly 60% successful rate when comparing the fourth and the third column, which means 60% of the pixels entering the

(a) original image "bike3-g"

(b) different modes indication on image "bike3g", where grey area indicates run-mode; white dots indicate ternary-mode; dark area indicates regular-mode.

| Fig. 5 Example 1: (a | ) Original image | "bike $3-g''$ and (b) | image indicating | different modes applied |

|----------------------|------------------|-----------------------|------------------|-------------------------|

|----------------------|------------------|-----------------------|------------------|-------------------------|

| Images   | Run    | Ternary | Successful ternary | Successful ternary ratio (%) |

|----------|--------|---------|--------------------|------------------------------|

| lena     | 148    | 8117    | 4363               | 0.017                        |

| barb2    | 7492   | 10708   | 5585               | 0.013                        |

| hotel    | 2826   | 16823   | 11686              | 0.028                        |

| bike3-g  | 109012 | 146804  | 113654             | 0.158                        |

| CMPND1-G | 276114 | 31227   | 27833              | 0.071                        |

Table 3

Mode counts of LMMIC

ternary-mode can be successfully coded by it. This makes it improve the overall bit rates compared to applying the regular-mode alone.

The experimental result in terms of compression ratios is presented in Table 4. We choose a set of standard 3-band RGB images, a 4-band CMYK image "park" and a 7-band LANDSAT 7 image "coastal" from CCSDC (the Consultative Committee for Space Data Systems). The RGB images include continuous-tone images ("cats", "water", "lena" and "peppers"), compound images ("cmpnd1" and "cmpnd2") and synthetic image ("bike3"). We compare the proposed compression scheme with JPEG2000 [27], intra-band CALIC [29], IB-CALIC [30] and SICLIC [1]. The results of IB-CALIC and SICLIC are extracted from [1]. Some results are absent due to the unavailability of the programs. JPEG2000 is the current standard for image compression. The results of IB-CALIC are claimed to be one of the best in

#### Dear Pan,

I was delighted to hear from you last week. Patti and I had a wonderful time during our week-long summer vacation. The weather was excellent, and the food was absolutely exquisite. I hope that we can repeat this next year and that you will join us too.

We came back with a lot of fantastic memories, which we would like to share with you through some snapshots that we took.

Dur favorite is this picture of us aboard the "Top Hat", which I have pasted into this letter using some really neat advanced dig ital imaging technology on my home computer. We will ship the rest to you on a CD-ROM soon. Wishing you the best.

Love,

Susan

```

(a) original image "CMPND1-G"

```

(b) Ternary-mode and regular-mode indication on image "CMPND1-G", where white area indicates ternary-mode; dark area indicates regular-mode.

Fig. 6 Example 2: (a) Original image "CMPND1-G" and (b) image indicating ternary-mode and regular-mode areas

| Image   | JPEG2000 | CALIC | IB-CALIC | SICLIC | LMMIC |

|---------|----------|-------|----------|--------|-------|

| cmpnd1  | 1.44     | 1.21  | 1.02     | 1.12   | 1.05  |

| cmpnd2  | 1.30     | 1.22  | 0.92     | 0.97   | 0.97  |

| cats    | 1.75     | 2.49  | 1.81     | 1.85   | 1.82  |

| water   | 1.41     | 1.74  | 1.51     | 1.45   | 1.44  |

| lena    | 4.53     | 4.40  |          | 4.46   | 4.23  |

| peppers | 3.41     | 4.62  |          | 3.25   | 3.35  |

| bike3   | 5.17     | 4.21  |          | 4.41   | 4.29  |

| average | 2.72     | 2.84  |          | 2.50   | 2.45  |

| park    | 5.72     | 5.39  |          |        | 5.30  |

| coastal | 2.89     | 2.68  |          |        | 2.62  |

Table 4 Bit rates comparison on selected schemes, in bits per pixel per band

literature in terms of general interband image compression, but not hyperspectral image compression, which is not the scope of our proposed method either. And SICLIC is a good trade-off between compression ratio and complexity. Table 4 shows that LMMIC outperforms JPEG2000 and intraband CALIC by 10% and 14%, respectively. It is superior than SICLIC on average, though slightly inferior than IB-CALIC which has higher computational complexity. Since the interband coding in LMMIC only couples two bands, it has the flexibility of compressing images with any number of bands and easy access to any bands.

#### 7 Hardware Architecture

Hardware amenability is one of the priorities in the design of the proposed scheme. Therefore, as previously described, the whole procedure, including the prediction and mode switching, only involves a limited number of addition and shifting, and memory usage is strictly controlled. In this section we propose the suitable hardware architecture to support the proposed compression scheme, which can be mainly divided into two parts – the architectures of lossless image modelling and encoding. The modelling part includes prediction and context modelling, while the encoding part includes probability estimator and binary arithmetic coder. We will discuss them below respectively in details.

#### 7.1 Lossless Image Modelling

Lossless image modelling here serves both gray-scale and multispectral images. The user can specify which category the input image belongs to. The data flow of the image compression scheme is shown in Fig. 7.

To optimize the speed and hence the throughput, the data flow of the scheme is designed as two pipelines running in parallel, as shown in Fig. 7. Line 1, indicated by the flow on the left in blue, operates for the current symbol. It takes in the input symbol and selects the suitable mode to encode it. The mean of errors and context index calculated from Line 2 are fed into the multi-mode prediction and probability estimator. The output from the multi-mode prediction, which is either the "runs" of the symbols, or the symbol order from the ternary mode, or the prediction error from the regular mode, are used to drive the probability estimator and arithmetic coder. Line 2, indicated by the flow on the right in red, works for the next symbol. It takes the input symbol to update the contexts, and calculate the prediction value and context index under the selected mode for the next symbol. The advantage of dividing the procedure into two parallel pipelines is, while not violating the sequential constraint, to halve the execution time and hence obtain higher throughput. A summary of the operations in each pipelines is as follows.

Fig. 7 Data flow of the prediction and context modeling module

#### Line 1:

- 1. Select a suitable mode and calculate prediction error  $\epsilon = X (\hat{X} + error\_mean);$

- 2. Update the sum of errors sum and the number of pixels count in each context;

- 3. Map prediction error  $\epsilon$  to  $\tilde{\epsilon}$ ;

- 4. Update coding context index Q;

- 5. Encode the prediction error with probability estimator and arithmetic coder.

#### Line 2:

- 1. Update contexts with new symbol;

- 2. Calculate primary prediction value  $\hat{X}$  for regular mode, and evaluate the condition of entering run-mode and ternary-mode;

- 3. Calculate the texture pattern;

- 4. Calculate the error energy and the context index;

- 5. Calculate the mean of the errors *error\_mean*.

During the above process of image modelling, there are two issues worth of special care, while the rest of the process is relatively straightforward numerical computation.

• There is usually heavy memory usage in image compression algorithms, either for storing prediction context or coding context, which are defined in Sect. 5. To minimize the memory usage for prediction context, we only store three lines of image pixel values in memory. We use three pointers to indicate the line orders. New input symbols are always stored in line A. Every time when a line is filled up, the three pointers to each line rotate in such an order that the oldest line is discarded and the newly formed line is saved.

• As introduced in [29], an error feedback technique is used in the prediction step to adjust the prediction bias in each context. We adapt this approach in our scheme, but we calculate the prediction bias based on a different context formation and provide special treatment for hardware amenability. The mean of errors  $\bar{\epsilon}(C)$  in each context *C* is assumed to be the most probable prediction offset error, and hence is a good observation of the bias of the predictor. We improve the prediction by adding this term. It is calculated by

$$\bar{\epsilon}(C) = sum/count \tag{7}$$

where *sum* and *count* are the sum and occurrence count of errors in the context C, respectively. The calculation of  $\bar{\epsilon}(C)$  requires arbitrary division, which resources demanding in hardware implementation. To solve this problem, instead of having an infinite range, we store the *count* with only 5 bits  $(2^5 - 1 = 31)$ . When the count reaches its maximal value 31, it is halved by right-shifting one bit; meanwhile sum is also halved so as to maintain the mean  $\bar{\epsilon}(C)$ . For images with 8 bits per pixel, the mapped prediction error ranges from 0 to  $2^8 - 1$ . Therefore we only need 13 bits  $(2^5 \times 2^8 = 2^{13})$  plus one sign bit to store the sum of errors. Experimental results prove that this rescaling technique slightly improves the compression ratio by "aging" the observed data. However, division is always a difficult problem in hardware, especially when the dividend can be as large as 13 bits. To make this division practical, we bound the dividend sum by 10 bits for two reasons: firstly, experiments on our image test set show that the chance of the sum being larger than 1023 is less than 0.001%; secondly, extraordinary large errors tend not to reflect the true behavior of the context because prediction errors should be moderately small given an adequate predictor. Therefore, we can safely clip the *sum* value to 1023. We use the most significant bits of the divisor *count* in the division, with the dividend being rescaled accordingly to maintain the same result. Consequently, we only need a lookup table of 1 KByte  $(2 \times (2^{10}/2) = 1024)$  to complete fast division. Although the result of division is only an approximation, it does not affect the compression performance in our experiments.

#### 7.2 Probability Estimator and Arithmetic Coding

To encode the prediction errors generated from the image modelling stage, arithmetic coding is chosen in our implementation due to its best performance among other coding methods in terms of compression ratios. In actual implementation, it is advantageous to separate the arithmetic coding procedure as probability estimation and coding process [22]. Probability estimation is to calculate the probabilities of the data source adaptively and the coding process uses these probabilities to recursively calculate the proportion within the interval [0, 1), which is used to encode the input symbols. In this section, we briefly introduce the arithmetic coder we choose in our proposal and present the architecture of the probability estimator.

#### 7.2.1 Arithmetic Coding

Since probability estimator serves for the arithmetic coder, we can decide the implementation of the arithmetic coder first. A general arithmetic coder handles data source with multi-symbol alphabets. While providing good performance, it is complex and not easily amenable to hardware implementation. Alternatively, binary *arithmetic coding* has become a popular implementation of the arithmetic coding. It was proposed by Langdon and Rissanen in 1981 [10] and later adopted by the bi-level lossless image compression standard JBIG. Binary arithmetic coding works with binary source alphabet (0 and 1) and thereby the cumulative distribution vector of the alphabet, denoted by *pcum*, is simply *pcum* =  $[0 \ p_0 \ 1]$ , with  $p_0$  being the probability of symbol 0. The cumulative distribution of each symbol is required to be updated adaptively for each coded symbol in arithmetic coding. As Moffat [13] and Said [22] pointed out, this task can be much simpler in binary arithmetic coding due to the simple data structure. Binary coding also avoids implementation of some resource expensive components such as multiplication, and thus obtains efficiency gains. Due to the amenability and fast speed of binary arithmetic coder for software and hardware implementation, we adopt it in our proposed system. For more details about the binary arithmetic coder we used, the readers are referred to [13, 22]. An implementation of this binary arithmetic coder is published in previous work of our group [18].

#### 7.2.2 Probability Estimation

**Overview** As the prediction errors generated by the prediction step has a multisymbol alphabet, e.g.  $2^8 = 256$  symbols for images with 8 bits per pixel, they cannot be processed directly by a binary arithmetic coder. We construct a probability estimator to adaptively calculate the probabilities of symbol occurrence in each context and decompose these probabilities into binary symbols (0 or 1). It enables the application of a simple and efficient binary arithmetic coder and hence results in full pipelining and high throughput. This probability estimator is based on the one presented in [17]. In [17], the probability estimator is optimized for the statistical lossless general data compression algorithm which includes variable order contexts, while in our implementation we modified it for the fixed-order contexts of image compression. In particular, we studied the effect of using different amount of bits to store the symbol occurrence count and the initialization of the probability estimator. We will explain in detail soon below.

In the context modelling described here, we divide the prediction errors into different groups, which we called coding context. We assume that the prediction errors are independent identically distributed within each context. Therefore, probability estimation is performed for each coding context.

**Working Mechanism of the Context Trees** The main part of the probability estimator is a tree structure stored in a SRAM. Generally, each coding context is represented by an n + 1 level (*n* is the bits per pixel) balanced binary tree with  $2^n$

leaves associated with each symbol in the alphabet. For instance, a 9-level tree with  $2^8 = 256$  leaves should be used for each context of the prediction errors ranging from 0 to 255. In each tree node, a register is used to store the symbol occurrence count. Initially, all the symbols in the alphabet are assigned to a certain probability, which is equal probability in most of the cases, and the whole range of the probability sums up to 1. Thus each tree leave has an initial value to represent its probability, and other tree nodes have the value of the sum of the value of their two sub-trees. When a new symbol is received, the value of the corresponding tree nodes increases to reflect the change of the probability distribution of symbol occurrence.

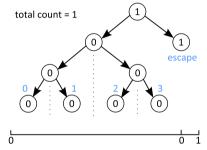

Here we demonstrate the working mechanism of the tree for probability estimation in Fig. 8. It shows a simplified binary tree with 3 level and 4 leaves, which represents a four symbol alphabet. The number in each tree node denotes the symbol occurrence. The value with underline on top of each tree leave is the symbol value represented by the leave. Firstly, all the trees need to be initialized before being used. In Fig. 8a, all the tree nodes are initialized to 0, except the tree root and the

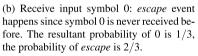

3 input symbol = 0 total count = 3 1 2 escape n escape

(a) Initialization: all the tree nodes are initialized to 0, except the root and the *escape* node are initialized to 1. This means the whole probability is assigned to escape symbol.

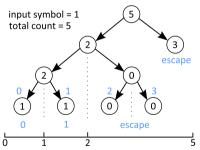

6 input symbol = 1 total count = 6 3 3 escape escape ō 2 6

(c) Receive input symbol 1: escape event happens since symbol 1 is never received before. The resultant probability of 0 is 1/5, the probability of 1 is 1/5, the probability of probability of *escape* is 1/2. escape is 3/5.

(d) Receive input symbol 1: symbol 1 can be coded successfully. The resultant probability of 0 is 1/6, probability of 1 is 1/3, the

Fig. 8 Simplified tree structure of the probability estimator

escape node. Escape here means coding is not successful. It happens when a valid probability of a symbol cannot be found. For example, when an input symbol has not occur before and hence its tree node value (symbol occurrence) is 0, the *escape* event happens and the new symbol cannot be coded directly. We will show how it affects the tree in the rest of Fig. 8 and more discussion about *escape* would follow soon. In the initialization, the *escape* node is assigned to 1 to avoid coding failure. The value of the tree root is the sum of the symbol occurrence and the *escape* events, and hence is 1. We stored the tree root value as *total count*. It is clear that at this stage, the whole range of probability is assigned to escape. In Fig. 8b, a new symbol 0 is received. This symbol is not seen before so its tree node is 0. In this case, escape happens and the escape count increases by 1. Meanwhile, the tree leave for symbol 0 should also increase to reflect the symbol occurrence. Correspondingly, the tree nodes, which symbol 0 walks pass when going down from the second level tree node, should also increase accordingly. The coordinate below the tree reveals the current probability distribution, where symbol 0 has 1/3 and *escape* takes on 2/3. A similar situation happens in Fig. 8c, where a new symbol 1 is received. Both escape and 1 increase their occurrence. This would happen to all symbols occurring first time after initialization to 0 of the tree. But when the symbol already has a valid probability (non-zero occurrence), as in Fig. 8d, the input symbol can be coded directly. Figure 8d shows when a symbol 1 arrives for the second time. This time only the tree leave of symbol 1 increases, resulting its probability to 1/3. When more symbols are received, fewer *escape* would happen and symbols are most likely to be directly coded. But there are exceptions which we will discuss in the next two paragraphs.

**Context Tree Initialization** In our proposed scheme, we use 8 trees for the regular-mode and one for the run-mode. Each tree has  $2^8 = 256$  nodes. For ternary-mode, we use 64 trees, each of which has 4 nodes corresponding to the four options (*s*1, *s*2, *s*3 and "escape") in ternary-mode. These trees are dynamically updated during the coding process and thus are called *dynamic trees*. In addition, we use two trees, one of each kind, to represent the "escape" condition. Because these two trees do not change during the coding procedure, they are called *static trees*. Symbols coded by the static trees do not achieve any compression as the static trees do not change to reflect any probability distribution changes. Therefore, *escape* is undesirable. Then why do we still want to initialize the tree nodes to 0 even though there are more *escape* happening?

We had thought of a couple of initialization possibilities: (a) to initialize the tree nodes all to 1 just to reduce *escape*; (b) as the prediction errors tend to follow a Laplacian distribution [29], we can possibly initialize the tree nodes in a Laplacian way – let the small symbol be assigned higher probability and as the symbol becomes bigger the probability decreases as the Laplacian curve. Therefore, we carry out the following experiment. We apply the same lossless image compression scheme on the image "lena". The only difference among these schemes is the initialization of the probability estimation. The comparison of compression ratios

| Initialization | Escape count | Compression ratio (bpp) |

|----------------|--------------|-------------------------|

| 0              | 697          | 4.137                   |

| 1              | 229          | 4.142                   |

| Laplacian      | 560          | 4.140                   |

Table 5

Performance comparison on different initialization of probability estimator

and *escape count* is shown in Table 5. Although the compression ratios do not vary dramatically under different initialization methods, it can help us with understanding the problem. When the trees are initialized as 0, despite the large amount of *escape* happening, it performs best because it ignores those symbols that never or rarely occur and thus reduces code space. When the trees are initialized as 1, it sets all occurrence count to 1, even for those that have never appeared. This might slightly distort the original histogram of prediction errors. When the trees are initialized as Laplacian distribution, it actually helps with building up the desirable error histogram in the first instance but this advantage might soon be overtaken by the possibly incorrect forced occurrence count for some symbols. From the above observation, we initialize the probability for all the symbols to 0.

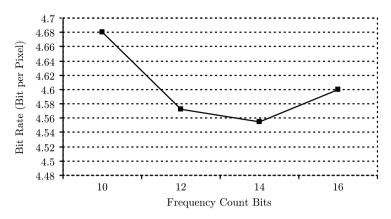

**Choice of Context Tree Node Size** *Escape* takes place when the *occurrence count* of the input symbol is 0. This does not only happens after initialization, but also occurs when the value of the tree node is rescaled. Since the occurrence count is stored in a register, the size of the register decides its limit, which is the *maximum* occurrence count. When the maximum occurrence count of a symbol is reached, the occurrence count needs to be rescaled. Rescale is done by halving the occurrence count, which can be easily executed by right shifting. In order to maintain the probability distribution, all the tree nodes need to be rescaled. Consequently, the occurrence count of symbols that have only been received less than twice will be rescaled to 0, resulting in *escape* when those symbols occur later. Therefore, the size of the register, which is the number of bits, to store the symbol occurrence count needs to be carefully chosen. We carry out experiments on the image "lena" using the same image compression algorithm but with different number of bits for storing the *occurrence count*. The results of average compression bit rates are shown in Fig. 9. We can see that the number of bits does affect the compression performance considerably. When the maximum occurrence count is too small, more escapes are likely to happen; when the *maximum occurrence count* is too big, the "aging" effect of observed data is attenuated. Therefore, we choose 14 bits according to the result of Fig. 9.

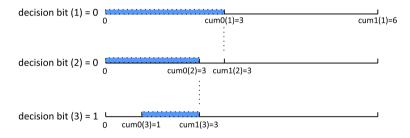

**Output of Probability Estimation** In order to drive the binary arithmetic coder, the probability estimator output three values: *decision bit*, cumulative probability of 0 (denoted as *cum0*) and cumulative probability of 1 (denoted as *cum1*).

The cumulative probabilities of 0 and 1 here means the cumulative probabilities of going left or going right in the context tree. They can be calculated from the

Fig. 9 Average bit rates under different probability precision, in bpp

Fig. 10 Arithmetic coding using the output of probability estimator

tree node values. Let us recall Fig. 8d. When the symbol 1 arrives, the total count increases from 5 to 6. Since this symbol appears before, it goes to the left branch but not *escape*. Here it outputs one *decision bit* 0. The *cum0* is the value of the current tree node, which is 3, and *cum1* is the value of its parent tree node minus the one of the current tree node (*cum0*). Figure 10 shows how these procedure works and the effect of these output. The values are assigned based on the tree in Fig. 8d. The number in parentheses denotes the level of the tree. So at the first level, cum0 = 3, cuml = 6. Because the *decision bit* is 0, the probability 1/2 is chosen. Since symbol 1 is 01 in binary, it goes to the left branch in the next level. In the selected interval from the previous level in Fig. 10, the whole range is assigned to 0 so we have cum0 = cum1 = 3. As *decision bit* is 0, the interval between 0 and *cum0* is chosen. In the last level, symbol 1 goes to the right branch of the tree. So the selected interval is between cum0 and cum1 and its probability is 2/3. The total probability of the symbol 1 can be calculated as  $(1/2) \times (2/3) = 1/3$ . In this way, the probability estimator only needs to output the *decision bit*, *cum0* and *cum1* at each clock cycle, and a total of 9 cycles are needed to encode one 8-bit symbol.

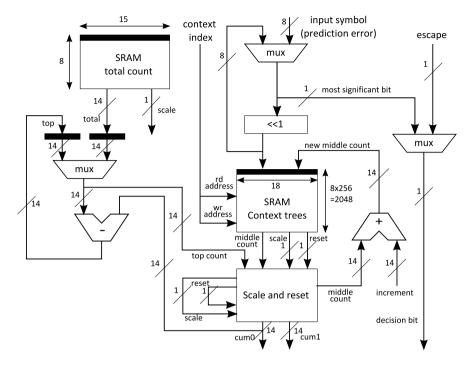

**Architecture of Probability Estimator** Figure 11 shows a simplified diagram of the probability estimator. It is modified from our previous work in [17]. As men-

Fig. 11 Architecture of the probability estimator

tioned earlier, the probability estimator in [17] works for general data compression, while this diagram is modified to work for our proposed image compression. Two SRAM memory are used to store the context trees and the *total count* for each tree respectively. The size of the SRAM for the context trees is

$$N_{con} \times S_{tree} \times W_{node} \tag{8}$$

where  $N_{con}$  is the number of contexts,  $S_{tree}$  is the number of tree nodes in each tree, and  $W_{node}$  is the width of the register used to store the information of each tree node. This not only includes the 14 bits used to store the tree node value, but also include two scale bits and two reset bits. They are used to control whether the left or right sub-tree of the current tree node needs to be rescaled or reseted. With the scale bits and reset bits, the operation of scale and reset can be done while the input symbol transverses down the tree, instead of being executed separately and wasting clock cycles. The input symbol, which is the prediction error, is shifted one bit each clock cycle. Its most significant bit is sent to the context tree for probability calculation. Meanwhile, the context index is read in to specify the corresponding context tree. The *increment* denotes the amount to be added to each tree node when a symbol walks pass. We set *increment* to 1. But it can also be set to bigger values if the user wants to accelerate the "aging" effect of rescaling. The *middle count* and *top count* are output as *cum0* and *cum1*, about which we have explained the role in calculating probability. The probability estimator maps the probability data into a set of binary decisions and cumulative occurrence counts, which enable the use of efficient binary arithmetic coding. It needs 9 clock cycles to code a 8-bit symbol, without using any extra clock cycles for rescaling and resetting. Therefore, it is highly efficient and allows high throughput. Some preliminary implementation results of the regular-mode working for grayscale images are published in [3, 19]. This part of the architecture together with the binary arithmetic coder enables the system to process one bit per clock cycle, which translates into a throughput of around 123 Mbits/s on a Xilinx Virtex 4 FPGA. Full implementation of the proposed system will be part of our future works.

#### 8 Conclusions

An original Lossless Multi-Mode Interband image Compression (LMMIC) scheme is proposed. The concept of segmentation is well ingrained in this scheme to deal with different regions in the image adaptively. The simple and efficient band shifting technique and the switching strategy successfully remove the interband redundancy. Experiments show that LMMIC achieves highly competitive compression ratios and provides the flexibility of compressing any number of bands as well as easy access to any bands, which are not offered by many other schemes. The complexity of the scheme is strictly controlled and hardware amenability is maintained. A corresponding hardware architecture is also proposed to support the functionality of the proposed algorithm.

Acknowledgements The authors would like to thank the support from EPSRC under grant EP/D011639/1.

#### References

- 1. Barequet R, Feder M (1999) SICLIC: a simple inter-color lossless image coder. In: Proc data compression conf, pp 501–510

- Benazza-Benyahia A, Pesquet J-C, Hamdi M (2002) Vector-lifting schemes for lossless coding and progressive archival of multispectral images. IEEE Trans Geosci Remote Sens 40(9):2011–2024

- Chen X, Canagarajah N, Nunez-Yanez JL, Vitulli R (2007) Hardware architecture for lossless image compression based on context-based modelling and arithmetic coding. In: Proc IEEE int system on chip conf, pp 251–254

- Dragotti PL, Poggi G, Ragozini ARP (2000) Compression of multispectral images by threedimensional SPIHT algorithm. IEEE Trans Geosci Remote Sens 38(1):416–428

- Felzenszwalb PF, Huttenlocher DP (2004) Efficient graph-based image segmentation. Int J Comput Vis 59(2):167–181

- Hu J-H, Wang Y, Cahill, PT (1997) Multispectral code excited linear prediction coding and its application in magnetic resonance images. IEEE Trans Image Process 6(11):1555–1566

- Jet Propulsion Laboratory, California Institute of Technology. Airborne Visible/Infrared Imaging Spectrometer (AVIRIS). http://aviris.jpl.nasa.gov/

- Kayyali MSE multispectral technology applications. http://www.articlealley.com/article\_ 1604\_11.html

- Kim J, Fisher JW, Yezzi A, Cetin M, Willsky AS (2005) A nonparametric statistical method for image segmentation using information theory and curve evolution. IEEE Trans Image Process 14(10):1486–1502

- Langdon GG, Rissanen JJ (1981) Compression of black–white images with arithmetic coding. IEEE Trans Commun 29(6):858–867

- 11. Meyer B, Tischer PE (1997) TMW a new method for lossless image compression. In: Proc int picture coding symp

- 12. Mielikainen J, Toivanen P (2002) Improved vector quantization for lossless compression of AVIRIS images. In: Proc XI European signal processing conf

- 13. Moffat A, Neal R, Witten IH (1998) Arithmetic coding revisited. ACM Trans Inf Sys 16(3):256-294

- 14. Motta G, Rizzo F, Storer JA (2003) Compression of hyperspectral imagery. In: Proc data compression conf, pp 333–342

- 15. National Aeronautics Space Administration (NASA): the Landsat program. http://landsat.gsfc.nasa.gov/

- 16. National gallery: visual arts system for archiving and retrieval of images. http://users.ecs. soton.ac.uk/km/projs/vasari/

- Nunez-Yanez JL, Chouliaras VA (2005) A configurable statistical lossless compression core based on variable order Markov modeling and arithmetic coding. IEEE Trans Comput 54(11):1345–1359

- Nunez-Yanez JL, Chouliaras VA (2005) Design and implementation of a high-performance and silicon efficient arithmetic coding accelerator for the H.264 advanced video codec. In: Proc IEEE int conf on application-specific systems, architecture processors, pp 411–416

- 19. Nunez-Yanez JL, Chen X, Canagarajah N, Vitulli R (2007) Dynamic reconfigurable hardware for lossless compression of image, video and general data content. In: Proc XXII conf on design of circuits and integrated systems. Invited paper

- Ratakonda K, Ahuja N (2002) Lossless image compression with multiscale segmentation. IEEE Trans Image Process 11(11):1228–1237

- Ryan MJ, Arnold JF (1997) The lossless compression of AVIRIS images by vector quantization. IEEE Trans Geosci Remote Sens 35(3):546–550

- Said A (2004) Introduction to arithmetic coding theory and practice. Imaging Systems Laboratory, HP Laboratories Palo Alto

- Saunders D, Cupitt J (2003) Image processing at the national gallery: the VASARI project. The National Gallery, Technical Bulletin 14(1):72–85. London, UK

- 24. Shen L, Rangayyan RM (1997) A segmentation based lossless image coding methods for high-resolution medical image compression. IEEE Trans Med Imaging 16(3):301–307

- Tang X, Pearlman WA, Modestino JW (2003) Hyperspectral image compression using threedimensional wavelet coding. Proc SPIE, vol. 5022. SPIE, Bellingham, pp 1037–1047

- Tate SR (1997) Band ordering in lossless compression of multispectral images. IEEE Trans Comput 46(4):477–483

- 27. Taubman DS, Marcellin MW (1996) JPEG2000 image compression fundamentals, standards and practice. Kluwer, Norwell

- Weinberger MJ, Seroussi G, Sapiro G (1996) LOCO-I: a low complexity, context-based, lossless image compression algorithm. In: Proc data compression conf, pp 140–149

- 29. Wu X, Memon N (1997) Context-based adaptive, lossless image coding. IEEE Trans Commun 45(4):437–444

- Wu X, Memon N (2000) Context-based lossless interband compression extending CALIC. IEEE Trans Image Process 9(6):994–1001

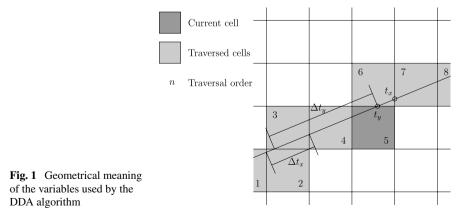

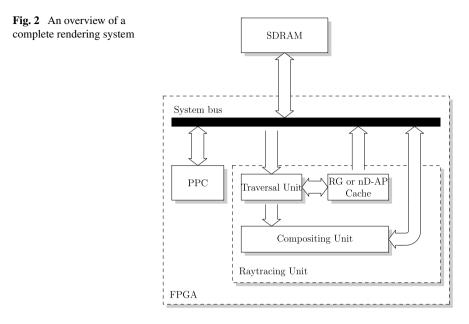

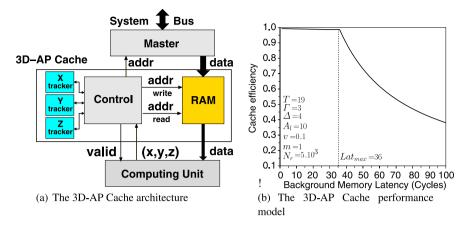

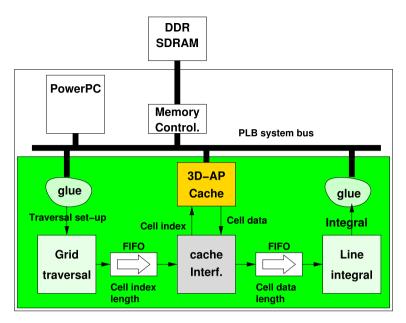

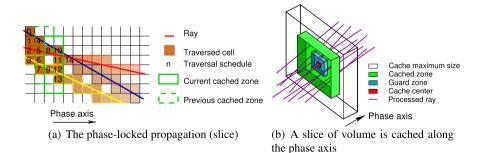

# **Efficient Memory Management for Uniform and Recursive Grid Traversal**

Tomasz Toczek and Stéphane Mancini

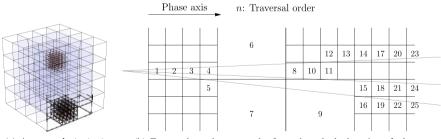

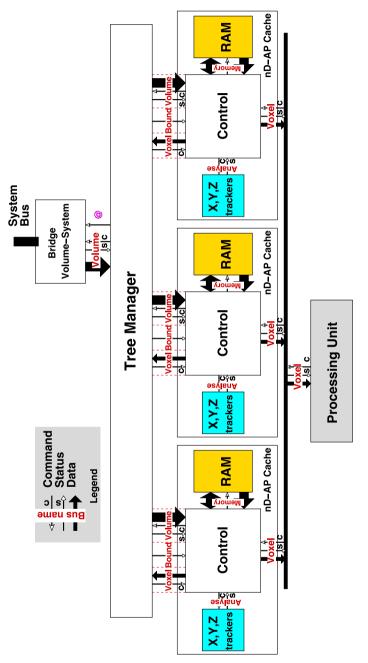

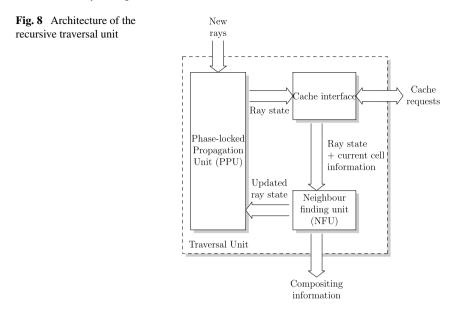

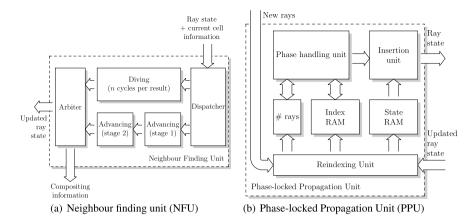

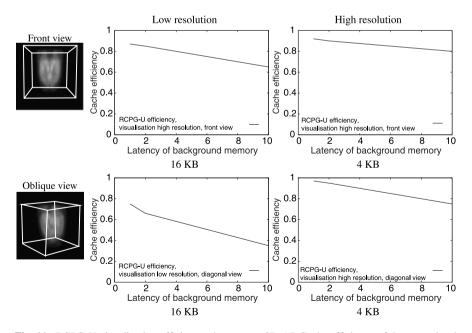

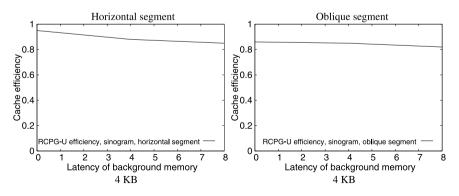

**Abstract** This chapter presents the usefulness of predictive and adaptive caching methods for the traversal of both uniform and recursive 3D grid structures. Recursive data structures are used in several image processing kernels and their efficient management is one challenge to save silicon area and reduce the power consumption due to the data transport. The described architectures greatly reduce the needs in term of bandwidth by exploiting the spatial and temporal locality of memory accesses during ray shooting in uniform and recursive grids. To maximize the cache efficiency, the original kernel is transformed to a "phase locked" ray-packet based propagation algorithm. Our results show that well-suited caching strategies can indeed yield significant performance gains during the traversal of both uniform and hierarchical grids. This emphasizes the relevance of semi-general purpose multidimensional predictive caches.

# 1 Introduction

The management of high quantities of data is a challenge for many digital systems. This problem is getting more and more complex with the increase of the quantity of memory embedded in digital integrated systems such as System on Chip (SoC). As an example, the International Technology Road-map for Semiconductors Consortium plans that memory will occupy 90% of a circuit in the next years. Then, to alleviate the well known memory wall, it is mandatory to provide efficient memory hierarchies that are optimized together with a cache friendly optimization of applications.

DOI 10.1007/978-90-481-9965-5\_2, © Springer Science+Business Media B.V. 2011

T. Toczek (🖂)

GIPSA-lab, INPG-CNRS, 961 rue de la Houille Blanche Domaine Universitaire-B.P. 46, 38402, Saint Martin d'Heres, France

e-mail: tomasz.toczek@gipsa-lab.inpg.fr

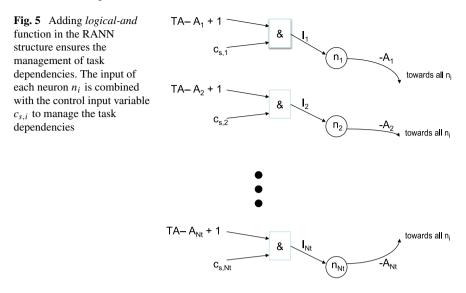

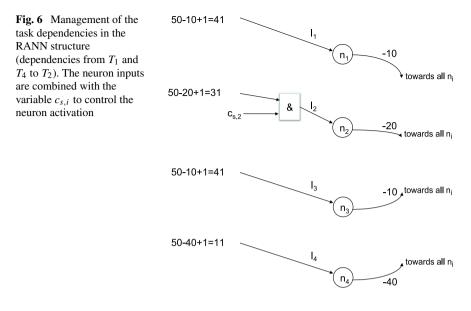

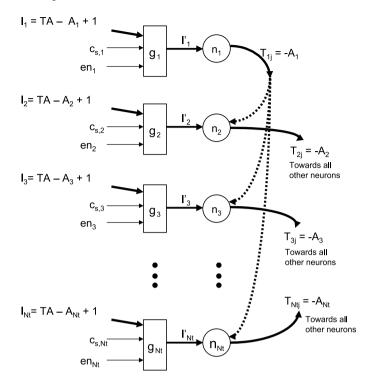

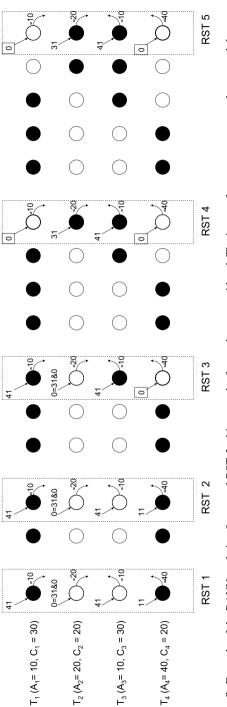

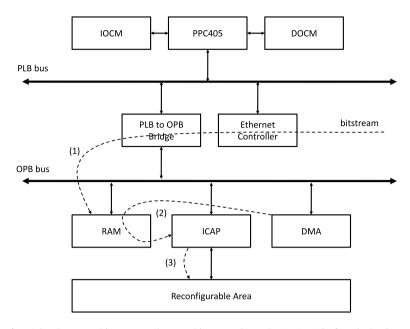

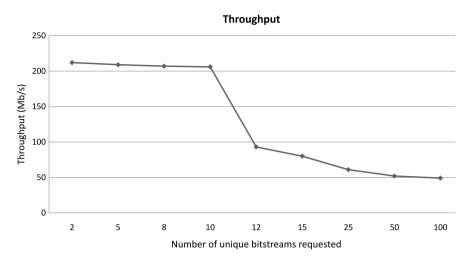

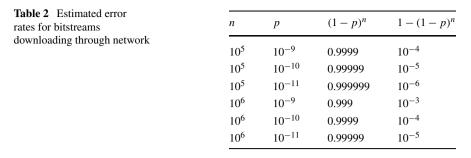

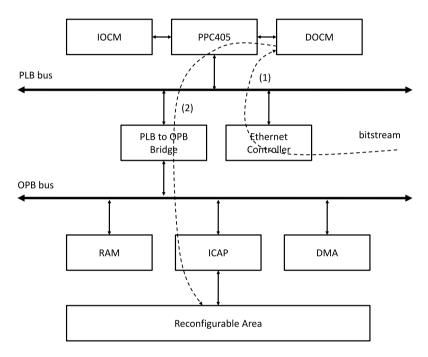

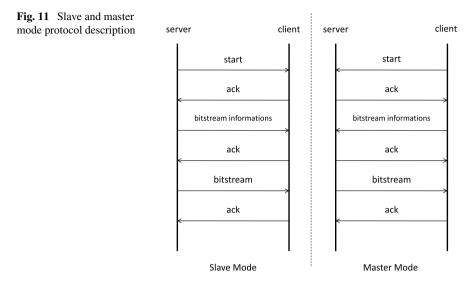

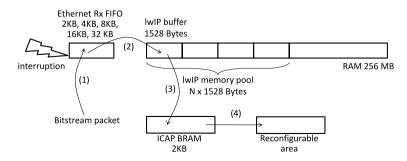

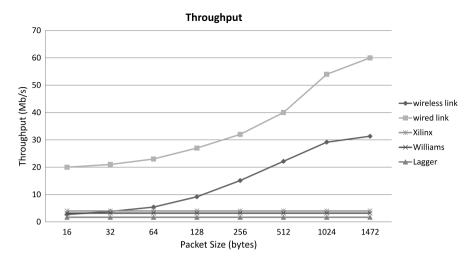

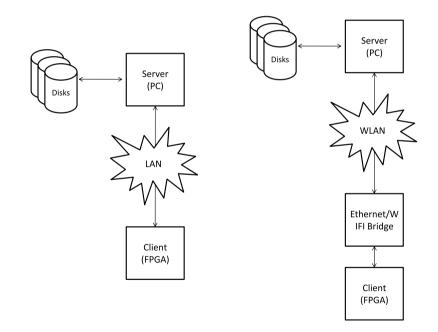

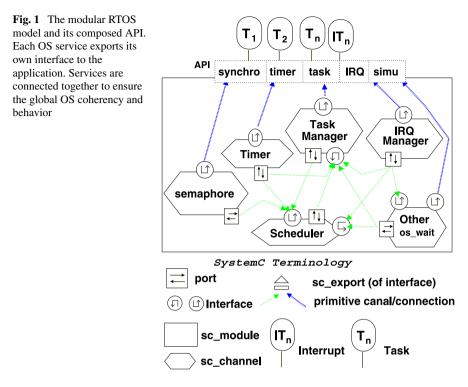

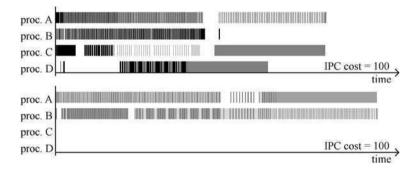

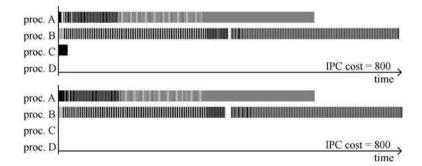

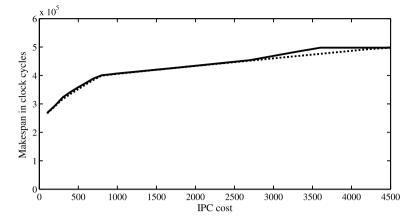

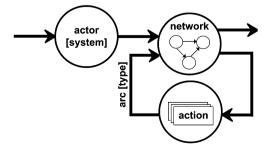

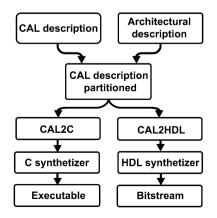

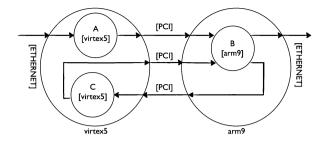

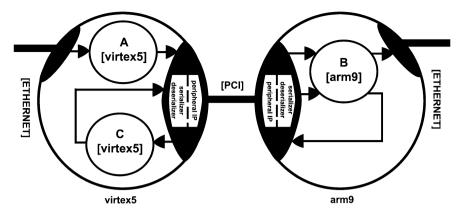

G. Gogniat et al. (eds.), *Algorithm-Architecture Matching for Signal and Image Processing*, 27 Lecture Notes in Electrical Engineering 73,