Ilya Wagner Valeria Bertacco

# Post-Silicon and Run-Time Verification for Modern Processors

# Post-Silicon and Runtime Verification for Modern Processors

Ilya Wagner • Valeria Bertacco

# Post-Silicon and Runtime Verification for Modern Processors

Ilya Wagner Platform Validation Engineering Group Intel Corporation Hillsboro, Oregon USA ilya.wagner@intel.com Valeria Bertacco Department of Electrical Engineering and Computer Science University of Michigan Ann Arbor, Michigan USA valeria@umich.edu

#### ISBN 978-1-4419-8033-5 e-ISBN 978-1-4419-8034-2 DOI 10.1007/978-1-4419-8034-2 Springer New York Dordrecht Heidelberg London

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

To my niece Ellie, who showed me the miracle of learning.

Ilya Wagner

To all my students, who make working in the field of verification such a rewarding experience.

Valeria Bertacco

# Preface

The growing complexity of modern processor designs and their shrinking production schedules cause an increasing number of errors to escape into released products. Many of these escaped bugs can have dramatic effects on the security and stability of consumer systems, undermine the image of the manufacturing company and cause substantial financial grief. Moreover, recent trends towards multi-core processor chips, with complex memory subsystems and sometimes non-deterministic communication delays, further exacerbate the problem with more subtle, yet more devastating, escaped bugs. This worsening situation calls for high-efficiency and high-coverage verification methodologies for systems under development, a goal that is unachievable with today's pre-silicon simulation and formal validation solutions. In light of this, functional post-silicon validation and runtime verification are becoming vitally important components of a modern microprocessor development process. Post-silicon validation leverages orders of magnitude performance improvements over pre-silicon simulation while providing very high coverage. Runtime verification solutions augment the hardware with on-chip monitors and checking modules that can detect erroneous executions in systems deployed in the field and recover from them dynamically.

The purpose of this book is to present and discuss the state of the art in postsilicon and runtime verification techniques: two very recent and fast growing trends in the world of microprocessor design and verification. The first part of this book begins with a high-level overview of the various verification activities that a processor is subjected to as it moves through its life-cycle, from architectural conception to silicon deployment. When a chip is being designed, and before early hardware prototypes are manufactured, the verification landscape is dominated by two main groups of techniques: simulation-based validation and formal verification. Simulation solutions leverage a model of the design's structure, often written in specialized hardware programming languages, and validate a design by providing input stimuli to the model and evaluating its responses to those stimuli. Formal techniques, on the other hand, treat a design as a mathematical description of its functionality and focus on proving a wide range of properties of its functional behavior. Unfortunately, these two categories of validation methods are becoming increasingly inadequate in coping with the complexity of modern multi-core systems. This is exactly where post-silicon and runtime validation techniques, the primary scope of this book, can lend a much needed hand.

Throughout the book we present a range of recent solutions in these two domains, designed specifically to identify functional bugs located in different components of a modern processor, from individual computational cores to the memory subsystem and on-chip fabrics for inter-core communication. We transition into the second part of the book by presenting mainstream post-silicon validation and test activities that are currently being deployed in industrial development environments and outline important performance bottlenecks of these techniques. We then present *Reversi*, our proposed methodology to alleviate these bottlenecks in processor cores. Basic principles of inter-core communication through shared memory are overviewed in the following chapter, which also details new approaches to validation of communication invariants in silicon prototypes. We conclude the discussion of functional post-silicon validation with a novel echnique, targeted specifically to modern multicores, called *Dacota*.

The recently proposed approaches to validation that we collected in part two of this book have an enormous potential to improve verification performance and coverage; however, there still is a chance that complex and subtle errors evade them and escape into end-user silicon systems. Runtime solutions, the focus of the third part of this work, are designed to address these situations and to guarantee that a processor performs correctly even in presence of escaped design bugs without degrading user experience. To better analyze these techniques we investigate the taxonomy of escaped bugs reported for some of the processor designs available today, and we also classify runtime approaches into two major groups: *checker-* and *patching-based*. In the remainder of part three we detail several runtime verification methods within both categories, first relating to individual cores and then to multicore systems. We conclude the book with a glance towards the future, discussing modern trends in processor architecture and silicon technology, and their potential impacts on the verification of upcoming designs.

# Acknowledgements

We would like to acknowledge several people that made the writing of this book possible. First, and foremost, we express our gratitude to our colleagues, who worked with us on the research presented in this book. In particular, we would like to thank Professor Todd Austin, who was a vital member of our runtime verification research and provided critical advice in many other projects. Andrew DeOrio has contributed immensely to our post-silicon validation research and has helped us greatly in the experimental evaluations of several other techniques. Both Todd and Andrew have also worked tirelessly on the original development of these works and provided valuable insights on the presentation of the material in this manuscript.

We would also like to thank many students working in the Advanced Computer Architecture Lab, and, especially, all those who have devoted their research to hardware verification: Kai-hui Chang, Stephen Plaza, Andrea Pellegrini, Debapriya Chatterjee, Rawan Abdel-Khalek have worked particularly closely to us among many others. Every day these individuals are relentlessly advancing the theory and the practice of this exciting and challenging field. We also acknowledge all of the faculty and staff at the Computer Science and Engineering Department of The University of Michigan, as well as all engineers and researchers in academia and industry who provided us with valuable feedback on our work at conferences and workshops, reviewed and critiqued our papers and published their findings, upon which much of our research was built. These are truly the giants, on whose shoulders we stand.

We also thank our families, who faithfully supported us throughout the years of research that led to the publication of this book. Each and every one of them was constantly ready to offer technical advice or a heartwarming consolation in difficult times, and celebrate the moments of our successes. Indeed, without their trust and encouragement this writing would be absolutely impossible.

Finally, we would like to acknowledge our editors, Mr. Alex Greene, Ms. Ciara Vincent and Ms. Katelyn Chin from Springer, who worked closely with us on this publication with truly angelic patience. Time and again, they encouraged us to continue writing and gave us valuable advice on many aspects of this book.

# Contents

# Part I VERIFICATION OF A MODERN PROCESSOR

| 1 | VEF  | IFICATION OF A MODERN PROCESSOR                               | 3 |

|---|------|---------------------------------------------------------------|---|

|   | 1.1  | The Birth of the Microprocessor                               | 3 |

|   | 1.2  | Verification Throughout the Processor Life-cycle              | 6 |

|   | 1.3  | Verification of a Modern Processor: a Case Study              | 8 |

|   | 1.4  | Looking Ahead                                                 | 9 |

|   | 1.5  | Summary 11                                                    | 1 |

|   | Refe | rences 12                                                     | 2 |

| • |      |                                                               | ~ |

| 2 | TH   | VERIFICATION UNIVERSE 13                                      |   |

|   | 2.1  | Pre-silicon Verification 14                                   | 4 |

|   |      | 2.1.1 From specification to microarchitectural description 14 | 4 |

|   |      | 2.1.2 Verification through logic simulation 15                | 5 |

|   |      | 2.1.3 Formal verification 19                                  | 9 |

|   |      | 2.1.4 Logic optimization and equivalence verification 24      | 4 |

|   |      | 2.1.5 Emulation and beyond 25                                 | 5 |

|   | 2.2  | Post-silicon Validation 26                                    | 6 |

|   |      | 2.2.1 Structural testing 28                                   | 8 |

|   |      | 2.2.2 Functional post-silicon validation                      | 3 |

|   | 2.3  | Runtime Verification 35                                       | 5 |

|   | 2.4  | Summary                                                       | 8 |

|   | Refe | rences                                                        | 9 |

|   |      |                                                               |   |

# Part II FUNCTIONAL POST-SILICON VERIFICATION

| 3 | POST-SILICON VALIDATION OF PROCESSOR CORES |                                                 |    |  |  |

|---|--------------------------------------------|-------------------------------------------------|----|--|--|

|   | 3.1                                        | Traditional post-silicon validation in industry | 45 |  |  |

|   | 3.2                                        | The Reversi Test Generation System              | 52 |  |  |

|   | 3.3                                        | Reversible and Non-reversible Instructions      | 54 |  |  |

|   |                                            | 3.3.1 Arithmetic and logic instructions         | 54 |  |  |

|   |                                                                                                       | <ul><li>3.3.2 Load/store instructions</li><li>3.3.3 Branch instructions</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                        |  |  |  |

|---|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|   |                                                                                                       | 3.3.4 Control register manipulation                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |  |  |  |

|   |                                                                                                       | 3.3.5 Floating point instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                                                                                     |  |  |  |

|   |                                                                                                       | 3.3.6 Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                                                                                     |  |  |  |

|   |                                                                                                       | 3.3.7 Reversi Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                                                                                     |  |  |  |

|   | 3.4                                                                                                   | Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65                                                                                                                                     |  |  |  |

|   | 3.5                                                                                                   | Experimental Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66                                                                                                                                     |  |  |  |

|   |                                                                                                       | 3.5.1 Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                                                                                                     |  |  |  |

|   |                                                                                                       | 3.5.2 Design Error Coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70                                                                                                                                     |  |  |  |

|   | 3.6                                                                                                   | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72                                                                                                                                     |  |  |  |

|   | Refe                                                                                                  | erences                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                                                     |  |  |  |

| 4 |                                                                                                       | ST-SILICON VERIFICATION OF MULTI-CORE                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |  |  |  |

|   | PR(                                                                                                   | DCESSORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75                                                                                                                                     |  |  |  |

|   | 4.1                                                                                                   | Overview of Multi-core Processor Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76                                                                                                                                     |  |  |  |

|   | 4.2                                                                                                   | The Challenge of Multi-core Processor Verification                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79                                                                                                                                     |  |  |  |

|   | 4.3                                                                                                   | Cache Coherence Verification Using String Matching                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83                                                                                                                                     |  |  |  |

|   | 4.4                                                                                                   | Verification of Memory Consistency Through Constraint Graph                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |  |  |  |

|   |                                                                                                       | Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89                                                                                                                                     |  |  |  |

|   | 4.5                                                                                                   | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92                                                                                                                                     |  |  |  |

|   | Refe                                                                                                  | erences                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92                                                                                                                                     |  |  |  |

| 5 |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |  |  |  |

| 5 |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95                                                                                                                                     |  |  |  |

| 5 | 5.1                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 96                                                                                                                                     |  |  |  |

| 5 | 5.1<br>5.2                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 96<br>97                                                                                                                               |  |  |  |

| 5 | 5.1                                                                                                   | Introduction<br>Dacota Overview<br>Activity Logging                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96<br>97<br>99                                                                                                                         |  |  |  |

| 5 | 5.1<br>5.2                                                                                            | Introduction<br>Dacota Overview<br>Activity Logging<br>5.3.1 Access vector                                                                                                                                                                                                                                                                                                                                                                                                           | 96<br>97<br>99<br>100                                                                                                                  |  |  |  |

| 5 | 5.1<br>5.2                                                                                            | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log                                                                                                                                                                                                                                                                                                                                                                                                  | 96<br>97<br>99<br>100<br>101                                                                                                           |  |  |  |

| 5 | 5.1<br>5.2<br>5.3                                                                                     | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging Example                                                                                                                                                                                                                                                                                                                                                                     | 96<br>97<br>99<br>100<br>101<br>103                                                                                                    |  |  |  |

| 5 | 5.1<br>5.2                                                                                            | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm                                                                                                                                                                                                                                                                                                                                          | 96<br>97<br>99<br>100<br>101<br>103<br>105                                                                                             |  |  |  |

| 5 | 5.1<br>5.2<br>5.3                                                                                     | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation                                                                                                                                                                                                                                                                                                               | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>105                                                                                      |  |  |  |

| 5 | 5.1<br>5.2<br>5.3                                                                                     | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction                                                                                                                                                                                                                                                                                        | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>105                                                                                      |  |  |  |

| 5 | 5.1<br>5.2<br>5.3                                                                                     | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis                                                                                                                                                                                                                                                         | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>105<br>106<br>110                                                                        |  |  |  |

| 5 | 5.1<br>5.2<br>5.3                                                                                     | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples                                                                                                                                                                                                                            | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>105<br>106<br>110<br>111                                                                 |  |  |  |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                              | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm Requirements                                                                                                                                                                                        | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>105<br>106<br>110<br>111<br>113                                                          |  |  |  |

| 5 | 5.1<br>5.2<br>5.3                                                                                     | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm RequirementsStrengths and Limitations                                                                                                                                                               | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>106<br>110<br>111<br>113<br>114                                                          |  |  |  |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                              | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm RequirementsStrengths and Limitations5.5.1Debugging with Dacota                                                                                                                                     | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>106<br>110<br>111<br>113<br>114<br>114                                                   |  |  |  |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                           | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm RequirementsStrengths and Limitations5.5.1Debugging with Dacota5.5.2Design Considerations                                                                                                           | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>106<br>110<br>111<br>113<br>114<br>114<br>114                                            |  |  |  |

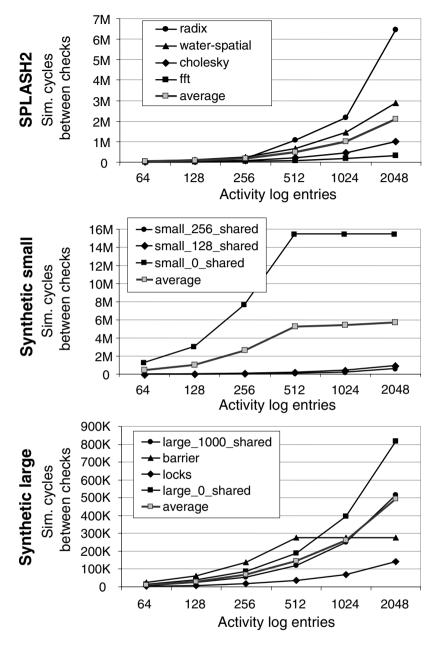

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                              | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm RequirementsStrengths and Limitations5.5.1Debugging with Dacota5.5.2Design ConsiderationsExperimental Evaluation of Dacota                                                                          | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>106<br>110<br>111<br>113<br>114<br>114<br>115<br>115                                     |  |  |  |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                           | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm RequirementsStrengths and Limitations5.5.1Debugging with Dacota5.5.2Design ConsiderationsExperimental Evaluation of Dacota5.6.1Design Error Coverage                                                | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>106<br>110<br>111<br>113<br>114<br>114<br>115<br>115                                     |  |  |  |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                           | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm RequirementsStrengths and Limitations5.5.1Debugging with Dacota5.5.2Design ConsiderationsExperimental Evaluation of Dacota5.6.1Design Error Coverage5.6.2Performance Evaluation                     | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>106<br>110<br>111<br>113<br>114<br>114<br>115<br>115<br>116                              |  |  |  |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ul>              | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm RequirementsStrengths and Limitations5.5.1Debugging with Dacota5.5.2Design ConsiderationsExperimental Evaluation of Dacota5.6.1Design Error Coverage5.6.2Performance Evaluation5.6.3Area Evaluation | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>106<br>110<br>111<br>113<br>114<br>115<br>115<br>116<br>116<br>116<br>123                |  |  |  |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> </ul> | IntroductionDacota OverviewActivity Logging5.3.1Access vector5.3.2Core Activity Log5.3.3Activity Logging ExamplePolicy Validation Algorithm5.4.1Access Log Aggregation5.4.2Graph Construction5.4.3Consistency Graph Analysis5.4.4Error Detection Examples5.4.5Checking Algorithm RequirementsStrengths and Limitations5.5.1Debugging with Dacota5.5.2Design ConsiderationsExperimental Evaluation of Dacota5.6.1Design Error Coverage5.6.2Performance Evaluation                     | 96<br>97<br>99<br>100<br>101<br>103<br>105<br>105<br>106<br>110<br>111<br>113<br>114<br>115<br>115<br>116<br>116<br>116<br>1123<br>124 |  |  |  |

# Part III RUNTIME VERIFICATION FOR MODERN MICROPROCESSORS

| 6 | RUNTIME VERIFICATION WITH PATCHING AND |         |                                                    |       |  |  |

|---|----------------------------------------|---------|----------------------------------------------------|-------|--|--|

|   | HA                                     | RDWA    | RE CHECKERS                                        | . 129 |  |  |

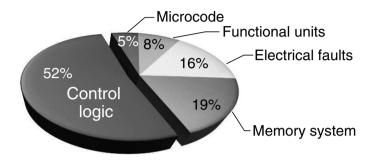

|   | 6.1                                    | Analy   | sis of Escaped Errors in Commercial Processors     | . 129 |  |  |

|   | 6.2                                    | Classi  | fication of Runtime Verification Solutions         | . 132 |  |  |

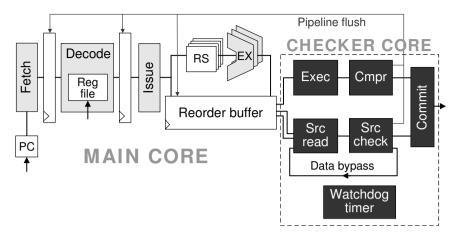

|   | 6.3                                    | DIVA    | : Dynamic Verification of Microprocessors          | . 135 |  |  |

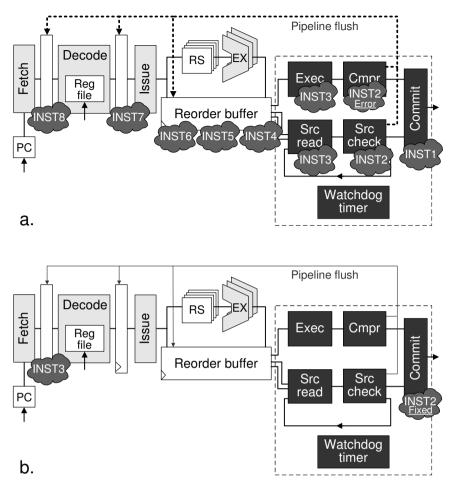

|   |                                        | 6.3.1   | Checker core operation                             | . 136 |  |  |

|   |                                        | 6.3.2   | DIVA in action                                     | . 137 |  |  |

|   |                                        | 6.3.3   | Benefits and limitations                           | . 139 |  |  |

|   | 6.4                                    | Runtii  | me Verification of Simple Cores with Argus         | . 141 |  |  |

|   | 6.5                                    | Hardw   | vare Patching Approaches for Runtime Verification  | . 144 |  |  |

|   | 6.6                                    | Concl   | usions                                             | . 148 |  |  |

|   | Refe                                   | erences |                                                    | . 149 |  |  |

| 7 | HA                                     | RDWA    | RE PATCHING WITH FIELD-REPAIRABLE                  |       |  |  |

| • |                                        |         |                                                    | . 151 |  |  |

|   | 7.1                                    |         | luction                                            |       |  |  |

|   | 7.2                                    |         | Repairable Control Logic Overview                  |       |  |  |

|   |                                        | 7.2.1   | Pattern Generation                                 |       |  |  |

|   |                                        | 7.2.2   | Matching Flawed Configurations                     |       |  |  |

|   |                                        | 7.2.3   | Pattern Compression Algorithm                      |       |  |  |

|   |                                        | 7.2.4   | Processor Recovery                                 |       |  |  |

|   |                                        | 7.2.5   | Example                                            |       |  |  |

|   | 7.3                                    | Design  | n Flow                                             |       |  |  |

|   |                                        | 7.3.1   | Overview of the Design Framework                   |       |  |  |

|   |                                        | 7.3.2   | Verification Methodology                           |       |  |  |

|   |                                        | 7.3.3   | Control Signal Selection                           |       |  |  |

|   |                                        | 7.3.4   | Automatic Signal Selection                         |       |  |  |

|   |                                        | 7.3.5   | Performance-Critical Execution                     | . 168 |  |  |

|   | 7.4                                    | Truste  | ed Hardware Design with Semantic Guardians         | . 168 |  |  |

|   |                                        | 7.4.1   | Combining Semantic Guardians and Hardware Patching | . 172 |  |  |

|   | 7.5                                    | Exper   | imental Evaluation                                 | . 173 |  |  |

|   |                                        | 7.5.1   | Experimental Framework                             | . 173 |  |  |

|   |                                        | 7.5.2   | Design Defects                                     | . 176 |  |  |

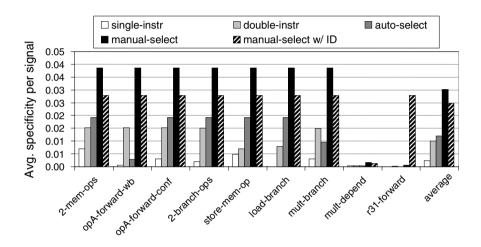

|   |                                        | 7.5.3   | Specificity of the Matcher                         | . 177 |  |  |

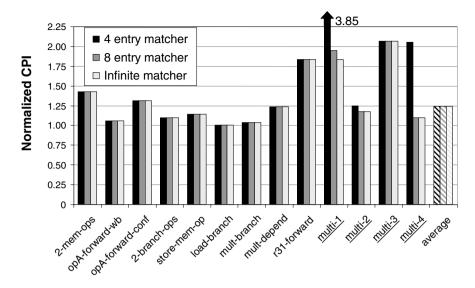

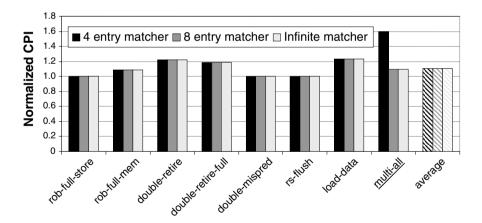

|   |                                        | 7.5.4   | State Matcher Area and Timing Overheads            | . 180 |  |  |

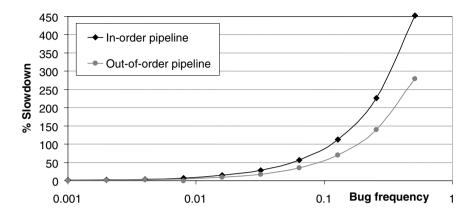

|   |                                        | 7.5.5   | Performance Impact of Degraded Mode                |       |  |  |

|   |                                        | 7.5.6   | Semantic Guardian Framework Analysis               |       |  |  |

|   | 7.6                                    | Summ    | nary                                               | . 187 |  |  |

|   | Refe                                   | erences | -                                                  | . 188 |  |  |

| 8   | RUN   | TIME VERIFICATION IN MULTI-CORES 1               | 89  |  |  |  |

|-----|-------|--------------------------------------------------|-----|--|--|--|

|     | 8.1   | Dynamic Verification of Memory Consistency 1     | 89  |  |  |  |

|     | 8.2   | Caspar: A Multi-core Patching Solution           |     |  |  |  |

|     | 8.3   | Caspar's Design 1                                | 94  |  |  |  |

|     |       | 8.3.1 Detection and Coverage 1                   | 96  |  |  |  |

|     |       | 8.3.2 Recovery and Bypass 1                      | .98 |  |  |  |

|     |       | 8.3.3 Checkpointing 1                            | .98 |  |  |  |

|     | 8.4   | Post-silicon Debugging with Caspar 1             | .99 |  |  |  |

|     | 8.5   | Experimental Evaluation                          | 201 |  |  |  |

|     |       | 8.5.1 Error Resiliency Analysis                  | 201 |  |  |  |

|     |       | 8.5.2 Checkpointing Overhead                     | 202 |  |  |  |

|     |       | 8.5.3 Caspar Recovery Performance                | 203 |  |  |  |

|     |       | 8.5.4 Area Overhead                              | 205 |  |  |  |

|     | 8.6   | Summary                                          | 205 |  |  |  |

|     | Refe  | rences                                           | 206 |  |  |  |

| 9   | ENS   | SURING CORRECTNESS IN FUTURE MICROPROCESSORS . 2 | 207 |  |  |  |

|     | 9.1   | Advances and Trends in Processor Validation      | 207 |  |  |  |

|     | 9.2   | A Proactive Approach to Verification             | 208 |  |  |  |

| Ref | erenc | <b>es</b> 2                                      | 213 |  |  |  |

| Ind | ex    |                                                  | 223 |  |  |  |

# Acronyms

- ALU Arithmetic-logic unit. A hardware block that performs integer arithmetic and logic functions, such as addition, subtraction, logic AND, *etc*.

- API Application programming interface. A set of functions and routines which describe the interface of a software application. API description is typically limited to the application interface, and does not specify the way the functionality of the program is actually implemented.

- ATPG Automatic test pattern generation. A technique for post-silicon validation of a manufactured circuit, which attempts to expose errors in fabrication of individual gates and interconnect in the design. ATPG tools use a software representation of the netlist to derive input stimuli that can expose a variety of manufacturing defects and then apply these tests to the prototype.

- BDD Binary decision diagrams. A data structure for compact representation and fast operations on Boolean logic functions. BDDs are commonly used as an underlying engine of formal verification approaches, such as symbolic simulation, reachability analysis and model checking.

- BIOS Basic input-output system. A firmware residing on the motherboard, that tests and configures various modules of a computer system upon startup.

- BMC Bounded model checking. A pre-silicon verification technique which establishes adherence of design's behavior, within a finite number of clock cycles, to formal specifications, often written as temporal logic formulas.

- CPI Cycles per instruction. A metric of processor performance, which measures the average number of clock cycles that the device needs to perform one operation.

- CPU Central processing unit. Electronic circuit capable of executing software programs, synonymous to the word "microprocessor".

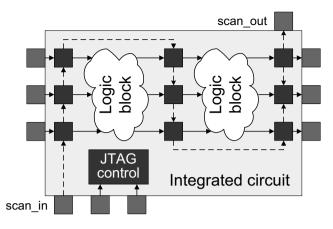

- DFT Design for testability. A class of techniques, which enable testing and debugging of digital circuits, *e.g.*, scan-chains, boundary-scan, on-chip logic analyzers, *etc*.

- ECC Error-correcting code. A special redundant encoding of the data that allows to recover the information even if some of the bits of it are corrupted. Typically used to protect computer storage, such as memory and caches.

- EDA Electronic design automation. A generic name for computer-aided tools for electronics design, as well as for the companies producing and deploying such tools.

- FPGA Field-programmable gate array. A digital circuit, which can be programmed to implement arbitrary logic functions. FPGAs are commonly used to emulate behavior of complex devices, such as microprocessors, before the first prototype is manufactured.

- FPU Floating point unit. A hardware block that performs floating point computation inside of the processor.

- FRCL Field-repairable control logic. A hardware patching solution, which augments a processor with a programmable matcher to detect and recover from erroneous control logic states.

- FSM Finite state machine. A graph description of hardware block operation. Consists of graph vertices, describing states of the machine, and edges, identifying legal transitions between the states.

- GPU Graphics processing unit. An electronic circuit dedicated to processing graphical information, before it is sent to a computer display. GPU chips are commonly placed on the motherboard or implemented as a separate graphics card.

- HDL Hardware description language. A class of programming languages that are used to describe functionality and organization of digital hardware, so the behavior of the design can be simulated.

- ILP Instruction level parallelism. A potential overlap in the execution of independent instructions. ILP measures how many operations in a program can be performed in parallel.

- ISA Instruction set architecture. A complete list of all instructions and operations that a processor can execute. ISA also often includes a complete specification of the processor interface, in terms of communication protocols, interrupt handling, *etc*.

- JTAG Joint test action group. Initially, an industry group that designed boundaryscan technique for circuit board testing. Later, term JTAG became synonymous with the boundary scan architecture.

- NMR N-modular redundancy. A resiliency technique, where *N* modules (identical or heterogeneous) compute the same function in parallel. Errors in one unit can then be detected and corrected through majority voting scheme.

- OCLA On-chip logic analyzer. A circuit, residing on a processor die, which can be programmed to monitor for specific activity of the processor and record the internal state of the chip upon occurrence of the trigger.

- OS Operating system. A software supervisor that manages the hardware and user-level programs of a computer system. An operating system provides applications with access to the hardware and coordinates the resource sharing in a computer system.

- PCI Peripheral component interconnect. A type of computer bus that connects peripheral devices of a system, *e.g.*, graphics and network cards, to the motherboard and the processor.

- PSMI Periodic state management interrupt. A technology developed at Intel, which allows to periodically stop program execution and collect the internal state of a silicon prototype for post-silicon debugging.

- QoS Quality of service. A network control mechanism that distributes resources to different classes of traffic to achieve deterministic or statistical guarantees of system performance.

- ROB Re-order buffer. A hardware block for instruction re-ordering used in complex out-of-order processor architectures. To hide the effects of long-latency operations a processor may issue instructions in an order different than that of the original program and use an ROB to ensure that the instruction stream is committed in strict program order.

- ROM Read-only memory. A class of storage of computer devices, where stored data cannot be modified. In microprocessor domain read-only memory is typically implemented as a hard-wired lookup table.

- RTG Random test generator. A software that creates randomized sequences of inputs to the design for testing purposes. Typically the test stimuli are not entirely random, but are constrained to a subset of all valid inputs to the design.

- RTL Register transfer level. An register transfer level description of a logic device consists of memory elements (registers) and functions that transfer the data between them. An RTL description is typically implemented in a hardware description language.

- SAT Boolean satisfiability. A class of problems that establishes if there exist an assignment to variables of a Boolean formula that evaluates it to true. SAT-solvers and their derivatives are often used by formal verification approaches, such as equivalence checking.

- SEU Single event upset. A change or corruption of the state of a latch (or a flip-flop), due to an energetic particle strike.

- SPICE Simulation program with integrated circuit emphasis. A class of simulation software that can evaluate the behavior of an integrated circuit from the electrical standpoint. SPICE technique solve complex differential equations, which describe how voltage and current at in various points in the design change over time, thus, operating at lower abstraction level than logic simulation solutions.

- STG State transition graph. A graph description of states and transitions between the states that hardware can assume at runtime. Synonymous to finite state machine.

- SoC System-on-a-chip. A hardware device that integrates multiple components of a computer system, *e.g.*, processing cores, non-volitile memory, peripheral controllers, *etc.* on a single silicon die.

- TLB Translation look-aside buffer. A hardware module that acts as a fast cache to a larger and slower lookup table, thus increasing processor performance for accesses that hit in the TLB.

# Part I VERIFICATION OF A MODERN PROCESSOR

This part of the book provides a high-level overview of the design and verification cycle of a modern processor, starting from the early design phases, to prototype manufacturing and testing and to product release. In the second chapter we explore each of the three major phases of the verification universe: pre-silicon verification, post-silicon validation and runtime techniques. For each phase, we discuss several key solutions and investigate their main advantages and drawbacks. Most importantly, we compare performance and coverage of verification methods across different phases, making the case for functional post-silicon and runtime verification techniques.

# Chapter 1 VERIFICATION OF A MODERN PROCESSOR

Abstract. Over the past four decades, microprocessors have come to be a vital and inseparable part of the modern world, becoming the digital brain of numerous electronic devices and gadgets that make today's lifestyle possible. Processors are capable of performing computation at astonishingly high speeds and are extremely integrated, occupying only a few square centimeters of silicon die. However, this computational power comes at a price: the task of verifying a modern microprocessor and guaranteeing the correctness of its operation is increasingly challenging, even for most established processor vendors. To deliver always higher performance to end-users, processor manufacturers are forced to design progressively more complex circuits and employ immense verification teams to eliminate critical design bugs in a timely manner. Unfortunately, too often size doesn't seem to matter in verification, as schedules continue to slip, and microprocessors find their way to the marketplace with design errors. In this chapter we overview the life-cycle of a microprocessors, discuss the challenges of verifying these devices, and show examples of hardware errors that have escaped into production silicon because of insufficient validation and their impact.

#### **1.1 The Birth of the Microprocessor**

Over the past four decades microprocessors have permeated our world, ushering in the digital age and enabling numerous technologies, without which today's life style would be all but impossible. Processors are microscopic circuits printed onto silicon dies and consisting of hundreds of millions of transistors interconnected by wires. What distinguishes microprocessors from other integrated circuits is their ability to execute arbitrary software programs. In other words, processors make digital devices programmable and flexible, so a single device can efficiently perform various operations, depending on the program that is running on it. In our every day activities we encounter and use these tiny devices hundreds of times, often without even realizing it. Processors allow us to untether our phones from the wired network and enable mobile communications, while their counterparts, deployed by phone companies, made communications richer and much more reliable. Processors monitor the health of hospital patients, control airplanes, tally election votes and predict weather. And, of course, they power millions of personal computers of all shapes and sizes, as well as the backbone of the Internet, a vital and inseparable part of modern life. The computational power of these devices grows every year at an astonishing pace: not long ago processors were only capable of executing just a few thousands operations per second, while today they can perform billions of complex computations per second. Finally, in the past few years, hardware design houses have introduced multi-core processors, that is, systems comprising multiple processors (cores) on the single silicon die. These systems, can execute several programs concurrently, thereby multiplying the overall performance delivered to the user.

However, to be so powerful, processors implement extremely complex architectures, making the design and manufacturing of these devices a major challenge for the semiconductor industry. Companies such as Intel, IBM and AMD are forced to dedicate hundreds of engineers for years at a time to continue to advance microprocessor technology and deliver the next generation processors to end-users. Moreover, as these designs grow in complexity, it becomes increasingly harder to verify them and ensure that they operate properly. Design houses report that today verification efforts significantly overweigh design activities, and that they often staff their teams with two verification engineers per designer. Unfortunately, the complexity and the number of features in each new generation of CPUs have quickly outpaced the capabilities of even the largest industrial teams. As a consequence, today it is impossible to provide high-quality verification of microprocessors with traditional means, and products released to the public are becoming less and less reliable. Furthermore, early in the development process engineers must assess the verifiability of all the features that they want to introduce into the new product: if proposed features cannot pass high-quality validation on time and within budget, they cannot be deployed in the final product and are removed from the design plan, resulting in a reduced set of capabilities and performance of the new system.

The consequences of this trend of diminishing quality in verification can be dramatic: indeed, the impact of bugs in production microprocessors can range widely from innocuous to devastating, for several reasons. For instance, it is possible for a computer system to become compromised, in terms of safety and security, because of a hardware bug. As a result, a system with a buggy processor becomes vulnerable to security attacks. Attacks of this type could be perpetrated even on systems running completely correct software, since they rely exclusively on underlying hardware flaws [Int04, Kas08]. Moreover, bugs can have a disastrous financial impact on the manufacturing company by triggering a costly recall of faulty hardware, as was the case in a past Intel processor [Mar08]; or causing significant delays in product release, similar to what happened with AMD's Phenom, released in 2007 [Val07]. The impact in both cases is estimated in billions of dollars, due to the large volume of defective components that a functional bug always entails. To prevent devastating errors from seeping into the released designs, a variety of techniques have been devised to detect and correct issues during system's design and manufacturing. Conceptually, these verification approaches can be divided into three families, based on where they intervene in a processor life-cycle: *pre-silicon*, *post-silicon* and *runtime verification solutions*.

*Pre-silicon techniques* are heavily deployed in the early stages of a processor's design, before any silicon prototype of the device is available, and can be classified as simulation-based or formal solutions. Simulation-based methods are the most common approaches to locate design errors in microprocessors. Random instruction sequences are generated and fed into a detailed software model, also called a hardware description of a design, results are computed by simulation of this model and then checked for correctness. This approach is used extensively in the industry, yet it suffers from a number of drawbacks. First, the simulation speed of the detailed hardware description is several orders of magnitude slower than the actual processor's performance. Therefore, only relatively short test sequences can be checked in this phase; for instance, it is almost impossible to simulate an operating system boot sequence, or the complete execution of a software application running on the processor. More importantly, simulation-based validation is a non-exhaustive process: the number of configurations and possible behaviors of a modern microprocessor is too large to allow for the system to be fully checked in a reasonable time.

Another family of pre-silicon solutions, formal verification techniques, solves the non-exhaustive nature of simulation, using sophisticated mathematical derivations to reason about a design. If all possible behaviors of the processor could be described with mathematical formulas, then it would be possible to prove the correctness of the device's operation as a theorem. In practice, in the best scenarios it is possible to guarantee that a design will not exhibit a certain erroneous behavior, or that it will never produce a result that differs from a known-correct reference model. The primary drawback of formal techniques, however, is that they are far from capable of dealing with the complexity of modern designs, and thus their use is limited to only a few, small components within the processor.

After a microprocessor is sufficiently verified at the pre-silicon stage, a prototype is manufactured and subjected to *post-silicon validation* where tests can, for the first time, be executed on the actual hardware. The key advantage of post-silicon validation is that its raw performance enables significantly faster verification than pre-silicon software-based simulation, thus it could deliver much better correctness guarantees. Unfortunately, post-silicon validation presents a challenge when it comes to detection and diagnosis of errors because of the limited observability provided by this technique, since at this stage it is impossible to monitor the internal components of the hardware prototype. Therefore, errors cannot be detected until they generate an invalid result, or cause the system to hang. The limited observability leads to extremely involved and time consuming debugging procedures, with the result that today post-silicon validation and debugging has become the single largest cost factor for processor companies such as Intel.

Due to the limitations of pre- and post-silicon verification, and shrinking timelines for product delivery, processor manufacturers have started to accept the fact that bugs do slip into production hardware and thus they are beginning to explore *runtime verification solutions* that can repair a device directly at the customer's site. "Patching" microprocessor bugs, however, is a non-trivial task, since the functionality of the device is already embodied in the transistors comprising the silicon die, and it cannot be easily modified at this point. To enable in-the-field patching, designers create special processor components dedicated to detecting erroneous behaviors and recovering from them. Runtime verification is currently in its early research stage: a few techniques have been recently proposed by academic research, while problem-specific solutions are starting to appear in commercial products.

#### **1.2 Verification Throughout the Processor Life-cycle**

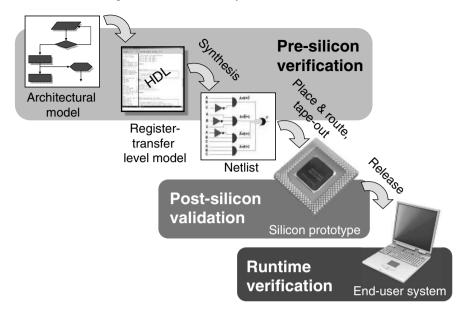

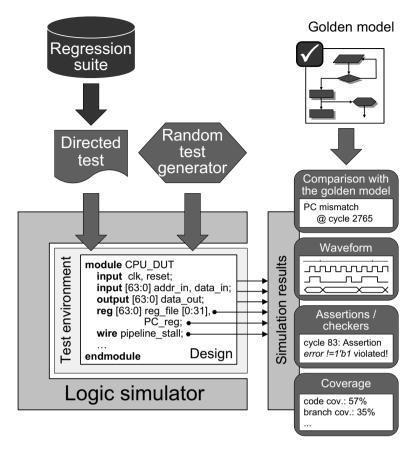

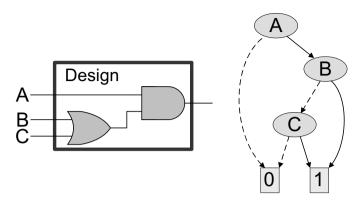

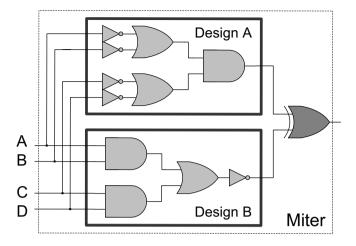

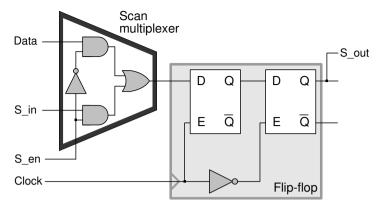

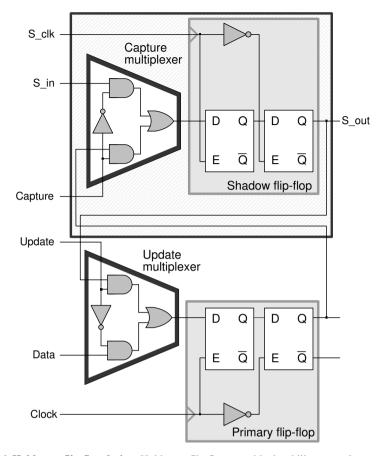

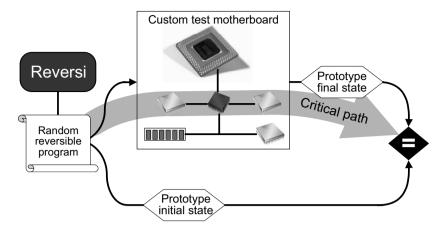

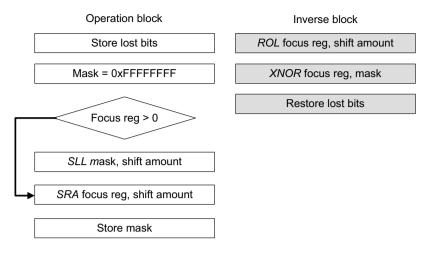

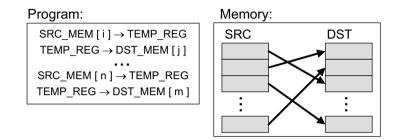

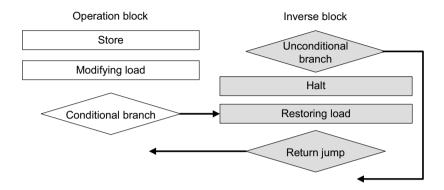

A traditional microprocessor's design and manufacturing flow (shown in Figure 1.1) consists of a series of steps that considers a high-level description of processor operation (specification), refines and transforms it, and, finally, implements the specified functionalities on a silicon die. After each step, the design is progressively verified, to ensure that, after all transformation and concretization steps, the behavior of the device still adheres to the original specification. The process starts with a high-level specification of the microprocessor's required characteristics and functionalities, often described in a natural language, and/or diagrams describing its basic structure and how the device should interface to other digital systems. This specification is then converted to an architectural model of the device, typically written in a highlevel programming language (such as C). This model represents the first formalized reference of the final system's behavior. Implementation in a hardware description language (HDL) can then start. The HDL description of the design describes the operation of individual sub-modules of the processor, as well as their interactions, and is also known as the register-transfer level (RTL) model. This RTL model is then verified to establish its equivalence to the architectural model through simulationbased and formal techniques. The outcome of simulation-based tests is compared to those of the known-correct (or "golden") architectural model and discrepancies, indicators of errors, are identified and fixed. In addition to simulation-based techniques, in pre-silicon verification, engineers often employ formal methods, which can check correctness of a design using mathematical proofs and can thus guarantee the absence of certain types of errors. Unfortunately, formal methods cannot handle complex RTL models due to their limited scalability, therefore, their usage is limited to a few, small critical blocks.

Once the RTL model is sufficiently validated, designers use synthesis software that maps HDL into individual logic gates, registers and wires, generating a *netlist* of the circuit. Since conversion from an RTL model to a netlist may incur errors, specialized verification solutions intervene again to check that this new transformation is still equivalent to the previous model. Place and route software applications then calculate how individual logic elements in the netlist can be placed on the silicon die to produce a design that fulfills the required characteristics of power, area, delay, *etc.* After placement, the final description of the design is *taped-out*, *i.e.*, sent to a fabrication facility to be manufactured. When the first hardware prototypes become

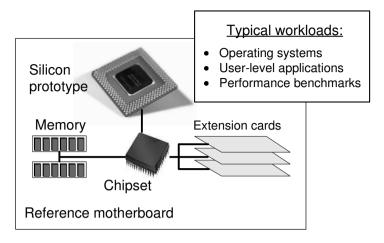

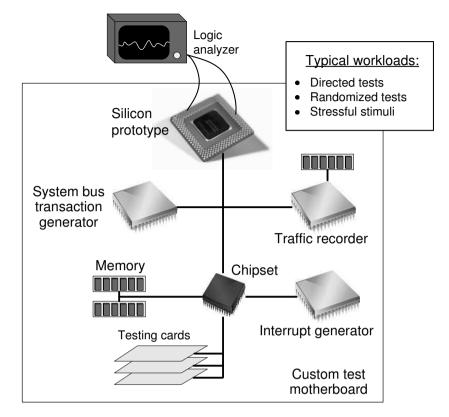

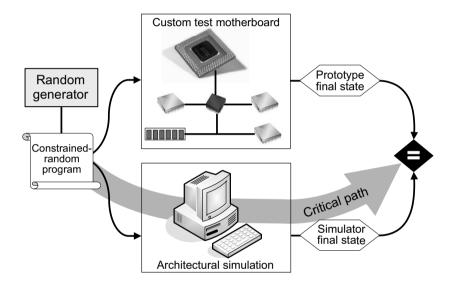

**Fig. 1.1 Modern microprocessor design and verification flow.** In the pre-silicon phase an architectural model, derived from the original design specification, is converted into an RTL implementation in a hardware description language (HDL). The RTL model can then be synthesized, producing a design netlist. Place and route software calculates where individual logic gates and wire connections should be placed on the silicon die and then a prototype of the processor is manufactured. Once a prototype becomes available, it is subjected to post-silicon validation. Only after the hardware is shown to be sufficiently stable in this validation phase, the processor is released and deployed in the market.

available, they can be inserted into a computer system for *post-silicon validation* (as opposed to the pre-silicon verification that occurs before the tape-out). One of the distinguishing features of post-silicon verification is its high performance: the same performance as the final product, which is orders of magnitude higher than simulation speeds in the pre-silicon domain. Typically, at this stage engineers try to evaluate the hardware in real life-like settings, such as booting operating systems, executing legacy programs, *etc.* The prototype is also subjected to additional random tests, in an attempt to create a diverse pool of scenarios where differences between the hardware and the architectural model can be identified to flag any remaining errors. When a bug is found at this stage, the RTL model is modified to correct the issue and the design often must be manufactured again (this process is called *re-spin*).

A processor design usually goes through several re-spins, as bugs are progressively exposed and fixed in manufactured prototypes. Ultimately, the design is stabilized and it can go into production. Unfortunately, due to the complexity of any modern processor, it is impossible to exhaustively verify its behavior either in presilicon or in post-silicon, thus subtle, but sometimes critical, bugs often slip through all validation stages. Until recently, if a critical functional bug was exposed in enduser's hardware, manufacturers had no other choice but to recall the device. Today vendors are starting to develop measures to avoid such costly recalls and allow their products to be patched in the field. Researchers in academia have also proposed solutions to ensure correctness of processor operation with special on-die checkers. Patching- and checker-based techniques are cumulatively classified as *runtime verification* approaches. In Chapter 2 we review the current techniques deployed in pre-silicon, post-silicon and runtime phases in more details, while in the remainder of the book we concentrate on several new promising solutions in the two latter domains.

### 1.3 Verification of a Modern Processor: a Case Study

The importance and difficulty of microprocessor verification is often underestimated today by casual users and electronic design industry professionals alike. One of the main causes of this is the fact that processor vendors rarely release exact data about their internal validation techniques and experiences into the public domain, and are even more cautions to disclose information about any encountered bugs. This is understandable from the business point of view to a certain degree, since a large portion of the tools and methodology used in validation by design companies are developed in-house and are used as competitive advantage against rival vendors. Likewise, information about any sort of bug, even those that had been fixed before product release, casts a negative image on the manufacturer and could potentially reveal confidential details about the inner-workings of the product. Nevertheless, there are a few publications from processor vendors that shed light on the validation of their products and give some degree of appreciation of the challenges faced by verification engineers.

One of the most comprehensive of such studies reports the pre-silicon validation effort on the Pentium 4 project, which was a new processor designed based on Intel's 7th generation NetBurst architecture [Ben05, Ben01]. In this work, authored by Bob Bentley, the daunting task of verification engineers is vividly described. The design process for Pentium 4 was started at Intel in 1996 and continued until tape-out three years later. During this time the validation team increased from 10 to 70 people, the majority of which had to be trained to use such verification tools as model checking, cluster-level simulation, etc. By tape-out time, the processor had undergone a transformation from a high-level idea and an architectural description to an RTL design of more than one million lines and was validated at cluster- and chip-level for more than 200 billions simulation cycles. This number is an astonishing feat if one takes into account that the chip-level simulation speed did not exceed 5Hz, due to sheer size of the RTL code base: that corresponds to more than a thousand years of cumulative simulation time. Consequently, the majority of pre-silicon simulation was done at cluster level, which not only allowed for faster simulation, but added much needed controllability to individual processor blocks. Moreover, as the RTL code was modified, regressions suites were executed time and again to maintain code stability throughout the development. To aid with this verification effort, the engineering team had to resort to large server farms that processed batches of tests around the clock.

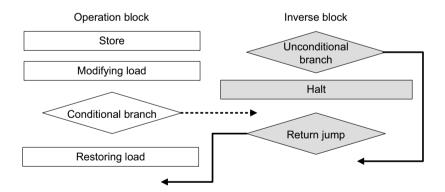

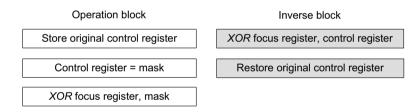

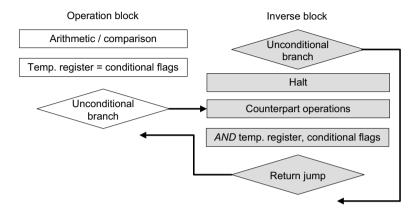

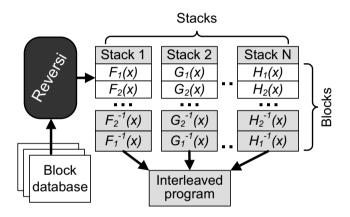

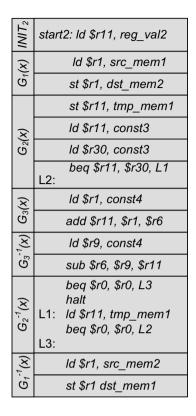

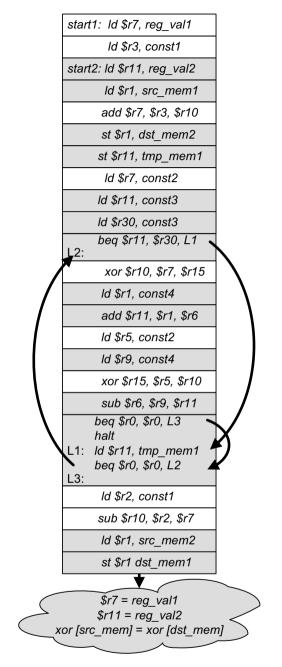

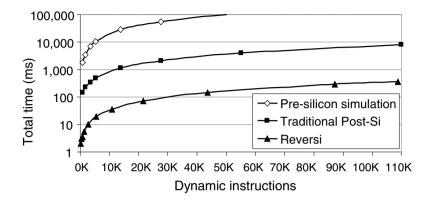

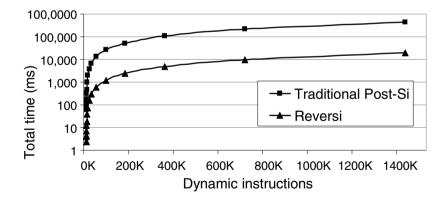

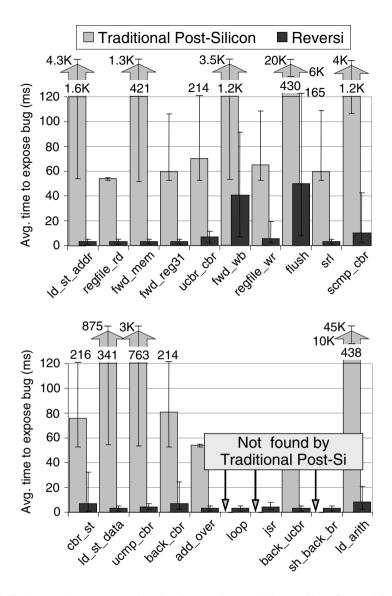

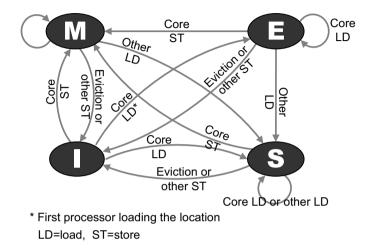

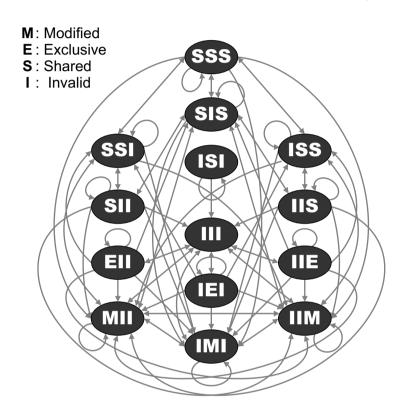

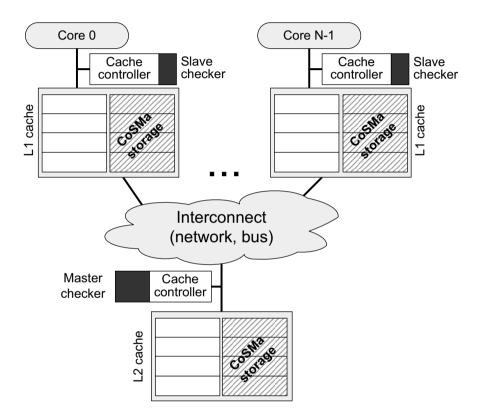

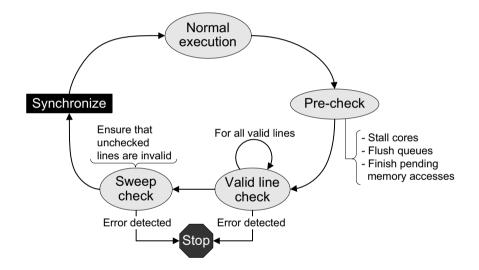

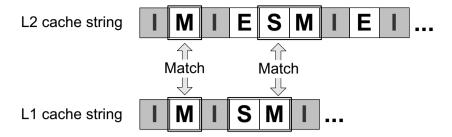

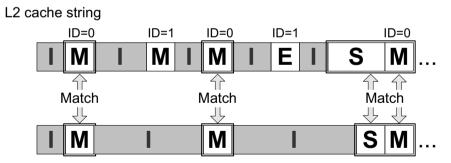

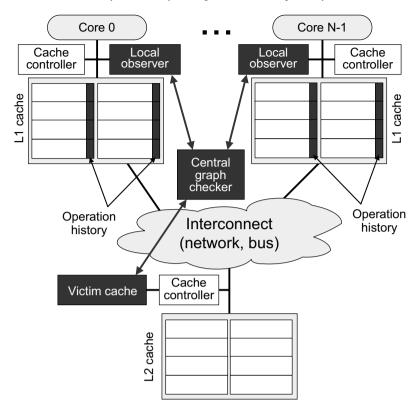

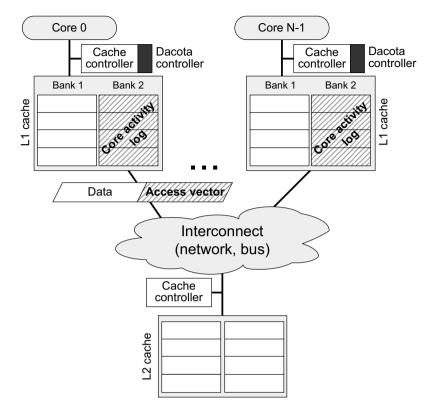

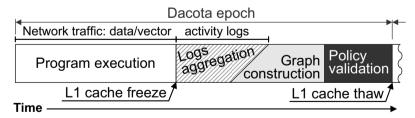

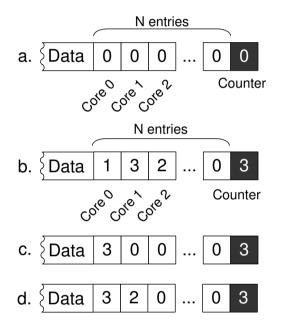

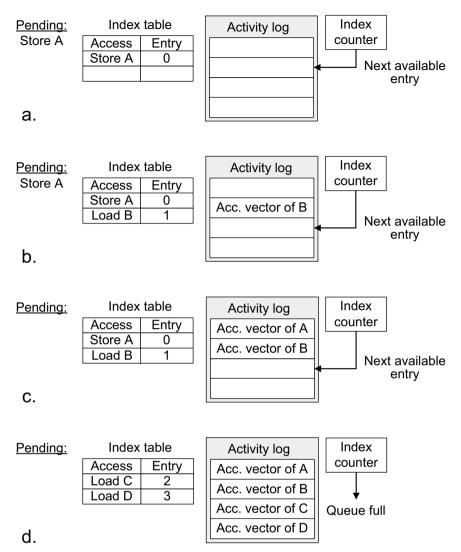

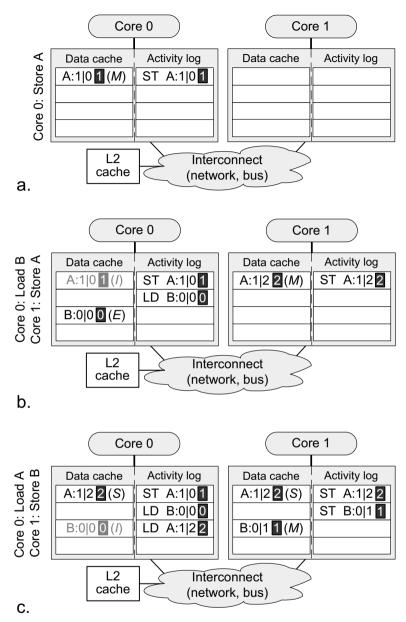

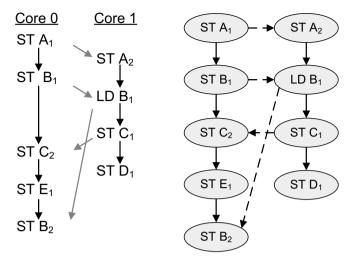

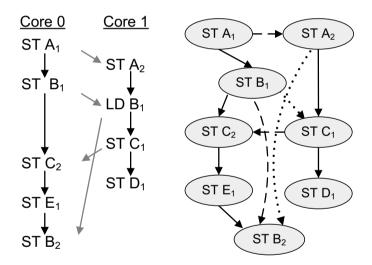

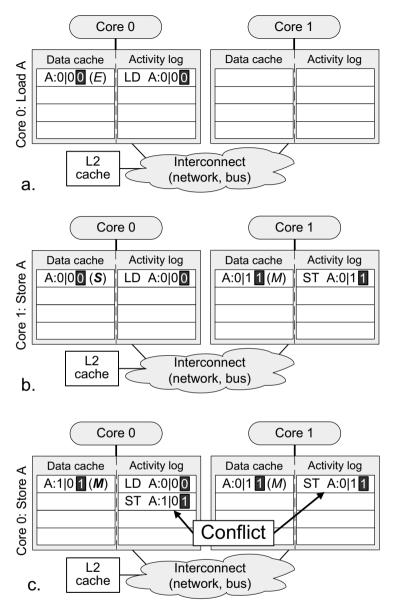

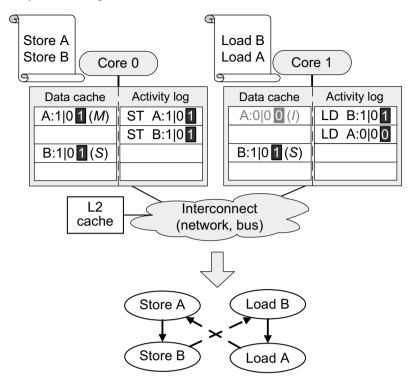

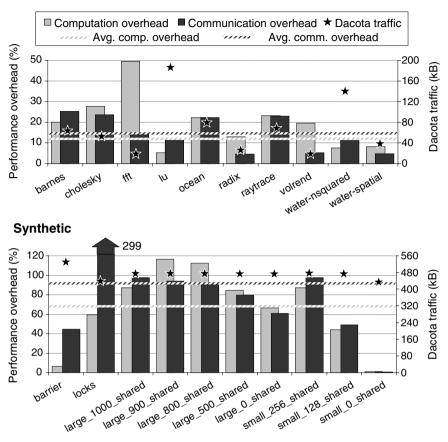

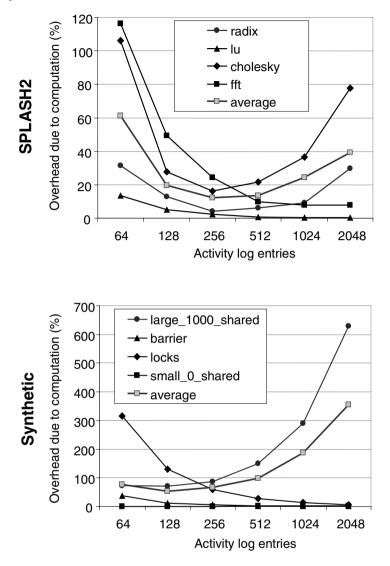

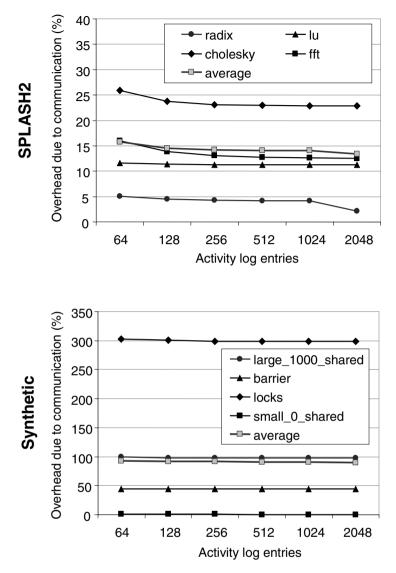

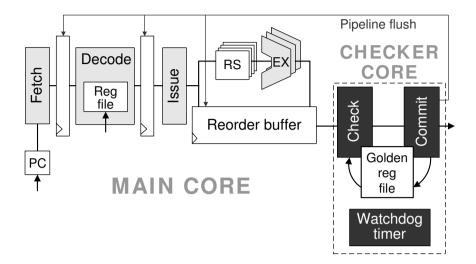

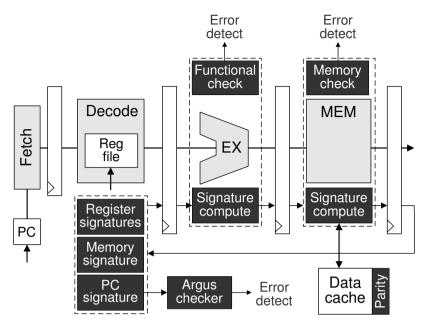

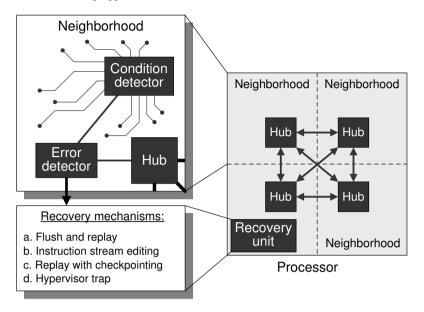

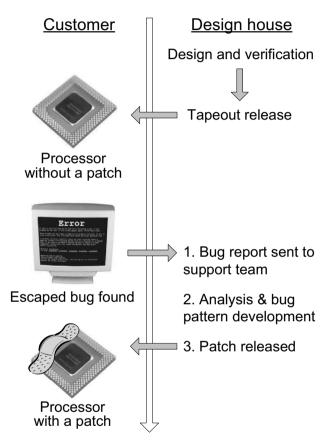

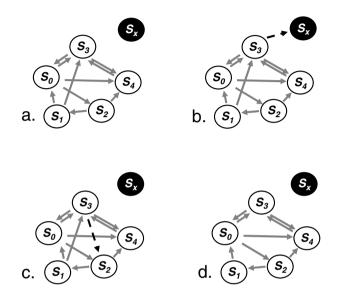

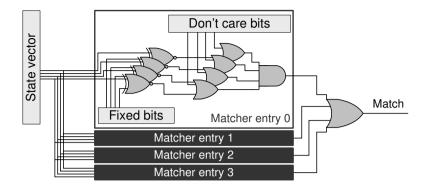

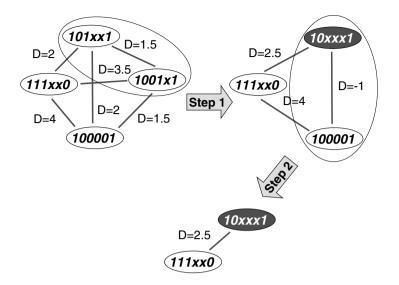

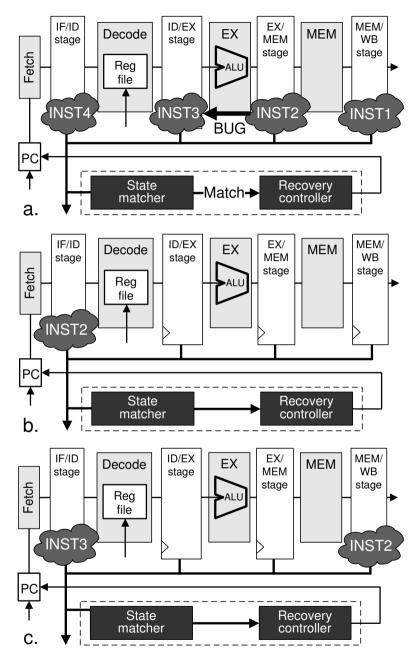

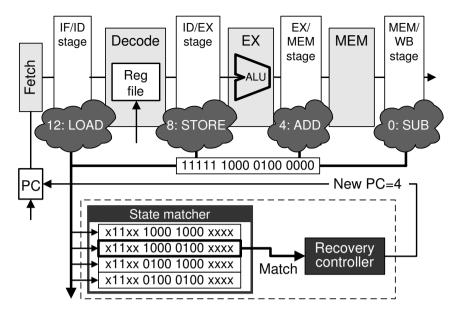

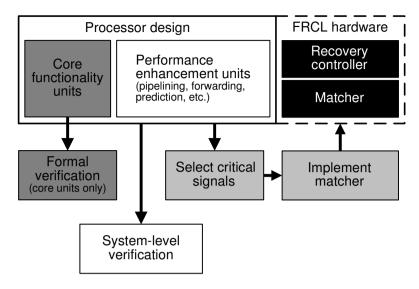

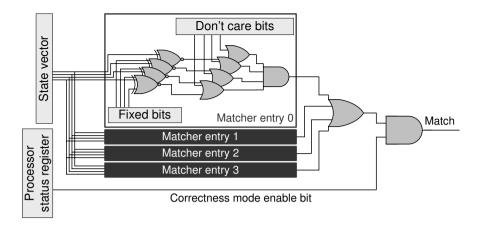

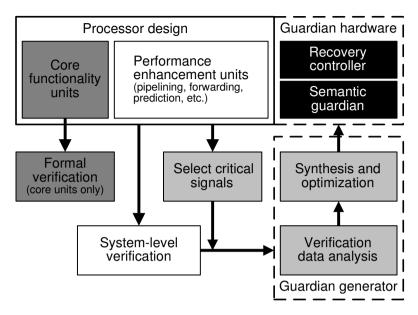

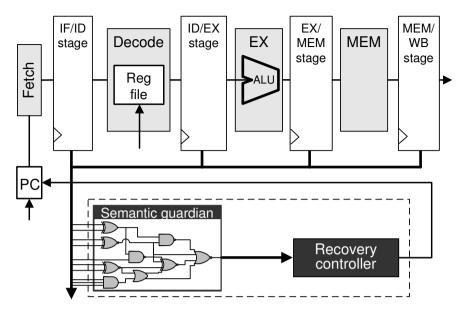

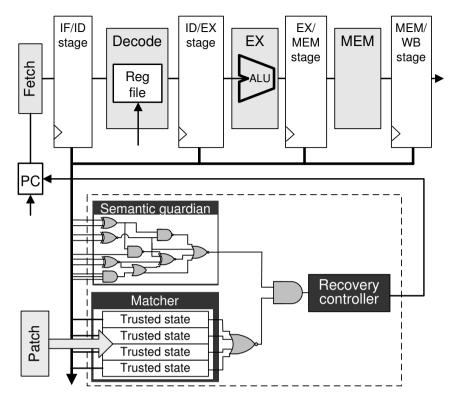

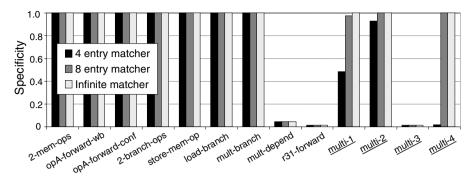

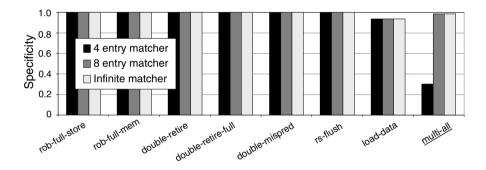

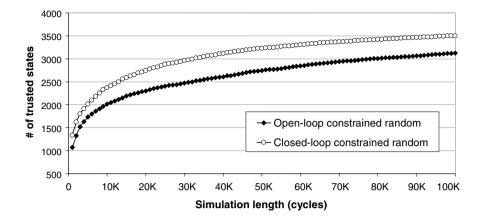

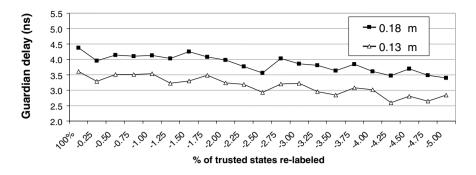

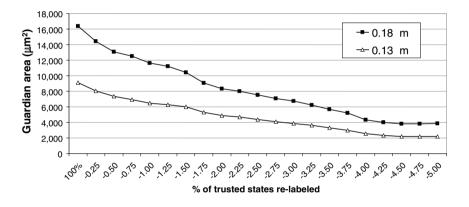

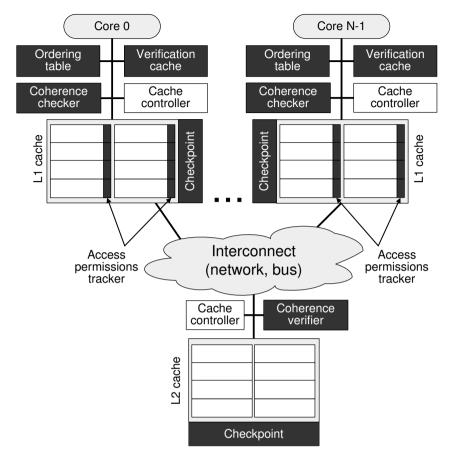

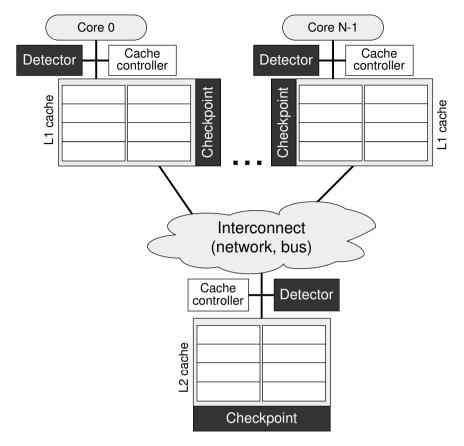

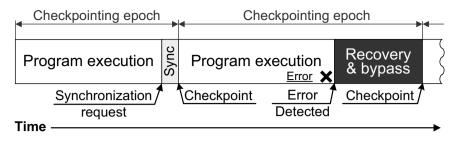

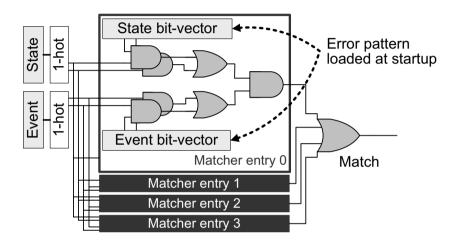

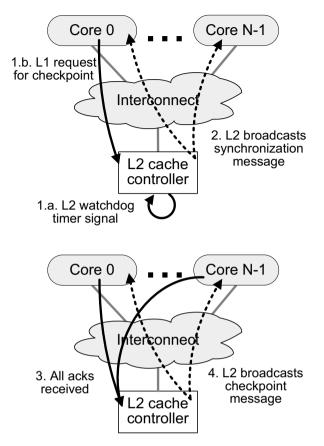

Pre-silicon validation, however, was not limited to simulation: the Pentium 4 validation project pioneered an extensive use of formal validation techniques for the microprocessor domain. Yet, those were only applied to a few critical blocks, such as the floating point unit and decoder logic, since the full design, comprising 42 million transistors, was too much for formal tools to handle. Thus, these mathematical approaches were selectively directed towards blocks that had been sources of errors in past designs. The effort payed off well, and several critical bugs were exposed and fixed before tape-out. One of those had a probability of occurrence of 1 in  $5 * 10^{20}$  floating-point instructions, thus it was very likely that it would have escaped a simulation-only verification methodology; its discovery overted a disaster that could have been critical for the company.