# Ivan Radojevic · Zoran Salcic

# Embedded Systems Design Based on Formal Models of Computation

Embedded Systems Design Based on Formal Models of Computation

Ivan Radojevic • Zoran Salcic

# Embedded Systems Design Based on Formal Models of Computation

Ivan Radojevic Defence Technology Agency New Zealand Defence Force Auckland New Zealand ivan\_radojevic@hotmail.com Zoran Salcic Computer Systems Engineering University of Auckland Auckland New Zealand z.salcic@auckland.ac.nz

ISBN 978-94-007-1593-6 e-ISBN 978-94-007-1594-3 DOI 10.1007/978-94-007-1594-3 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: 2011929884

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

One of the key problems in modern embedded systems design is the productivity gap. While the performance of computing architectures has been rapidly increasing in the past few decades, design tools have not kept pace. As a result, it is becoming increasingly difficult for embedded systems designers to handle complex applications. Delays in product delivery and even project cancellations are quite common. An obvious solution is to raise the abstraction level of design tools and at the same time enable automatic synthesis from high level specifications. A complete embedded application needs to be specified in a single system level language rather than using programming languages and hardware description languages to create an early nonoptimal hardware/software partition. From a single system specification written in a formal language, it is possible to automate design space exploration, hardware/ software partitioning, verification and synthesis, which gives an enormous boost to design productivity. However, all these design activities can be automated by design tools only if the system-level specification is constructed according to a formal model of computation, which sets the rules for communication among concurrent processes comprising the system. While several models of computation have been successfully used in certain classes of applications, their applicability in complex embedded system design is quite limited. In particular, there is a lack of suitable models for heterogeneous embedded systems that contain both control-driven and data-driven behaviours.

This book offers a new design methodology for design of heterogeneous embedded systems. At the heart of the methodology lies a model of computation called DFCharts. A complete design flow is covered, from a system specification in a formal language to an implementation on a multiprocessor architecture. Throughout the book examples are provided to illustrate main concepts. The reader is not required to have a deep understanding of models of computation. Only basic familiarity is assumed. For this reason, following the introductory Chaps. 1 and 2 describes a number of widely used models of computation and system level languages. Chaps. 3–8 then present the DFCharts based design methodology. The conclusion with future research directions follow in Chap. 9.

New Zealand

Ivan Radojevic Zoran Salcic

# Contents

| 1 | Intro | duction                                         | 1  |

|---|-------|-------------------------------------------------|----|

|   | 1.1   | Embedded Systems Design                         | 1  |

|   | 1.2   | DFCharts                                        | 4  |

|   | 1.3   | Book Organization                               | 5  |

| 2 | Mode  | els of Computation and Languages                | 7  |

|   | 2.1   | Finite State Machine                            | 7  |

|   | 2.2   | Kahn Process Networks                           | 9  |

|   | 2.3   | Synchronous Dataflow                            | 12 |

|   | 2.4   | Synchronous/Reactive Model                      | 13 |

|   | 2.5   | Discrete Event Model                            | 14 |

|   | 2.6   | Communicating Sequential Processes              | 16 |

|   | 2.7   | Petri Nets                                      | 20 |

|   | 2.8   | Statecharts/Statemate                           | 24 |

|   | 2.9   | Argos                                           | 28 |

|   | 2.10  | Esterel                                         | 29 |

|   | 2.11  | Lustre and Signal                               | 33 |

|   | 2.12  | SystemC                                         | 34 |

|   | 2.13  | Ptolemy                                         | 37 |

| 3 | Speci | fication in DFCharts                            | 43 |

|   | 3.1   | Introduction to DFCharts                        | 43 |

|   |       | 3.1.1 Operators                                 | 43 |

|   |       | 3.1.2 Transition Priorities                     | 46 |

|   |       | 3.1.3 Variables                                 | 47 |

|   |       | 3.1.4 Data Transfer Between FSM and SDF         | 49 |

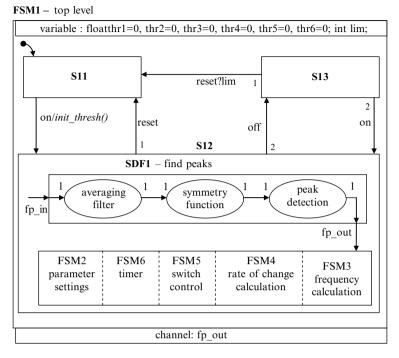

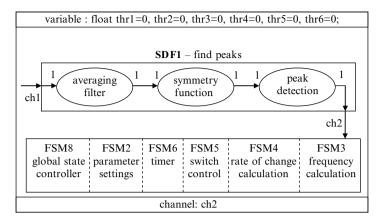

|   | 3.2   | Case Study: Frequency Relay                     | 50 |

|   |       | 3.2.1 Peak Detection                            | 51 |

|   |       | 3.2.2 Frequency and Rate of Change Calculations | 52 |

|   |       | 3.2.3 Switch Control                            | 53 |

|   |       | 3.2.4 Threshold Modification                    | 54 |

|   | 3.3  | DDFC     | Charts                                              | 55  |

|---|------|----------|-----------------------------------------------------|-----|

|   | 3.4  | Frequ    | ency Relay Extension                                | 57  |

| 4 | Sema | antics o | f DFCharts                                          | 61  |

|   | 4.1  | Auton    | nata Semantics                                      | 62  |

|   |      | 4.1.1    | FSM with Variables                                  | 66  |

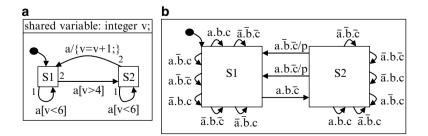

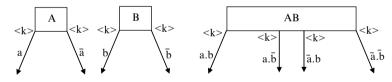

|   |      | 4.1.2    | Synchronous Parallel Operator                       | 70  |

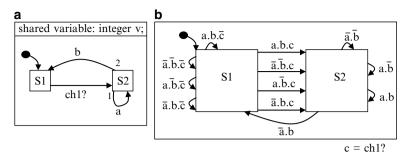

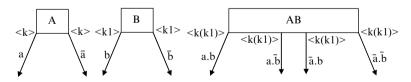

|   |      | 4.1.3    | Asynchronous Parallel Operator                      | 73  |

|   |      | 4.1.4    | Hiding Operator                                     | 77  |

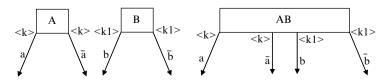

|   |      | 4.1.5    | Refinement Operator                                 | 78  |

|   |      | 4.1.6    | Mapping Syntax to Automata                          | 82  |

|   |      | 4.1.7    | Integrating SDF Graphs into Automata Semantics      | 84  |

|   | 4.2  | TSM      | Semantics                                           | 86  |

|   |      | 4.2.1    | Data Transfer from SDF to FSM                       | 88  |

|   |      | 4.2.2    | Data Transfer from FSM to SDF                       | 90  |

|   | 4.3  | The Ir   | mpact of Clock Speeds                               | 91  |

| 5 | DFC  | harte ir | n SystemC and Esterel                               | 93  |

| 3 | 5.1  |          | vsis Based on Requirements                          | 93  |

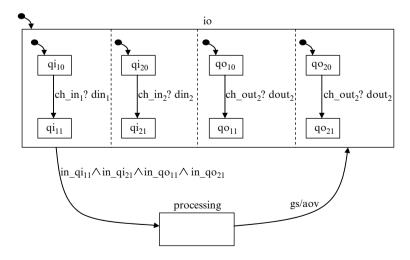

|   | 5.1  | 5.1.1    | Concurrent Processes                                | 93  |

|   |      | 5.1.2    | Rendezvous Communication                            | 94  |

|   |      | 5.1.2    | Buffers and Firing Rules for Dataflow               | 95  |

|   |      | 5.1.4    | HCFSM with Synchronous/Reactive                     | ))  |

|   |      | 5.1.4    | Communication                                       | 96  |

|   |      | 5.1.5    | Data Transformations                                | 98  |

|   |      | 5.1.6    | Multiple Processes Inside a State                   | 99  |

|   |      | 5.1.7    | Comparison Between SystemC and Esterel              | 100 |

|   | 5.2  |          | prical Results                                      | 100 |

|   | 5.3  |          | re Extensions of SystemC and Esterel                | 100 |

|   |      |          | -                                                   |     |

| 6 | -    |          | nment for DFCharts                                  | 105 |

|   | 6.1  |          | Classes                                             | 105 |

|   |      | 6.1.1    | Declaration of Reference Variables for I/O Signals, |     |

|   |      |          | States and Variables                                | 107 |

|   |      | 6.1.2    | Inner Classes for Transition Inputs                 |     |

|   |      |          | and Transition Outputs                              | 107 |

|   |      | 6.1.3    | Constructor Parameters                              | 109 |

|   |      | 6.1.4    | Signal and Shared Variable Connections,             |     |

|   |      |          | Initialization of Local Variables                   | 109 |

|   |      | 6.1.5    | Linking States, Transition Inputs                   |     |

|   |      |          | and Transition Outputs                              | 110 |

|   |      | 6.1.6    | Local Signals, Shared Variables and Channels        |     |

|   |      |          | for Lower Level FSMs and SDFGs                      | 110 |

|   |      | 6.1.7    | Instantiation of Lower Level FSMs                   |     |

|   |      |          | and SDFGs                                           | 112 |

|   |      | 6.1.8    | State Refinement                                    | 113 |

|   | 6.2  | SDFG    | G Classes                                 | 113 |

|---|------|---------|-------------------------------------------|-----|

|   |      | 6.2.1   | Constructor Parameters                    | 115 |

|   |      | 6.2.2   | Instantiation of Actors                   | 115 |

|   |      | 6.2.3   | Actor Connections                         | 116 |

|   | 6.3  | Top L   | evel Classes                              | 116 |

|   |      | 6.3.1   | Constructor Parameters                    | 117 |

|   |      | 6.3.2   | Instantiation of Input and Output Signals | 117 |

|   |      | 6.3.3   | Local Signals, Shared Variables           |     |

|   |      |         | and Channels for Top Level FSMs and SDFGs | 117 |

|   |      | 6.3.4   | Instantiation of Top Level FSMs and SDFGs | 118 |

|   |      | 6.3.5   | Top Level Refinement                      | 118 |

|   | 6.4  | Simul   | ation                                     | 119 |

|   | 6.5  | Libraı  | ry Classes                                | 119 |

|   |      | 6.5.1   | Base Classes                              | 120 |

|   |      | 6.5.2   | FSM Component Classes                     | 121 |

|   |      | 6.5.3   | FSM Communication Classes                 | 121 |

|   |      | 6.5.4   | FSM-SDF Communication Classes             | 122 |

|   |      | 6.5.5   | Synchronization Class                     | 122 |

|   | 6.6  | Frequ   | ency Relay Revisited                      | 123 |

| 7 | Hete | rogeneo | ous Reactive Architectures                |     |

| ' |      | -       | ed Systems                                | 125 |

|   | 7.1  |         | ground and Trends                         | 125 |

|   | 7.2  |         | tecture Framework – HETRA                 | 125 |

|   | 7.3  |         | ive Processors as the Elements of the     | 127 |

|   | 1.5  |         | ogeneous Architecture                     | 131 |

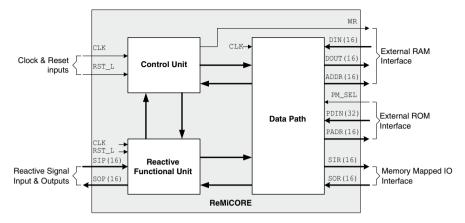

|   |      | 7.3.1   | Reactive Microprocessor – ReMIC           | 132 |

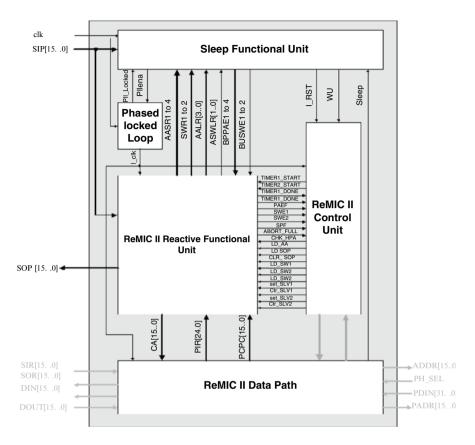

|   |      | 7.3.2   | Power Aware ReMIC-PA                      | 135 |

|   | 7.4  |         | ple of Heterogeneous Reactive             | 155 |

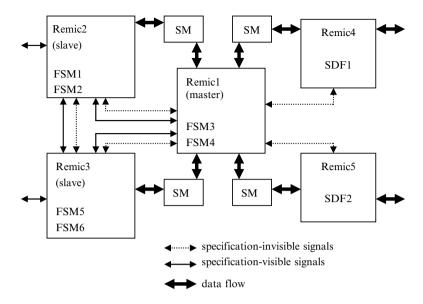

|   | /    |         | tecture – HiDRA                           | 137 |

|   |      | 7.4.1   | An Overview of HiDRA                      | 138 |

|   |      | 7.4.2   | An Implementation of HiDRA                | 139 |

|   |      |         |                                           |     |

| 8 | -    |         | tion of DFCharts on HiDRA                 | 143 |

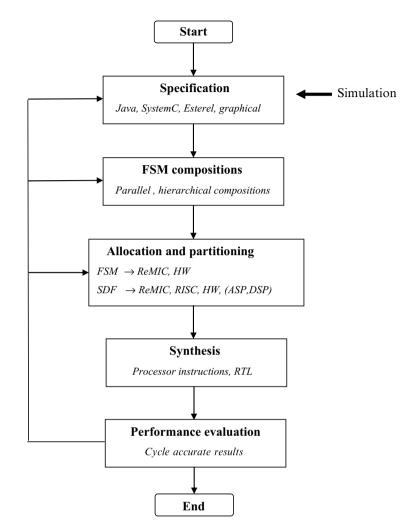

|   | 8.1  |         | arts Design Methodology                   | 143 |

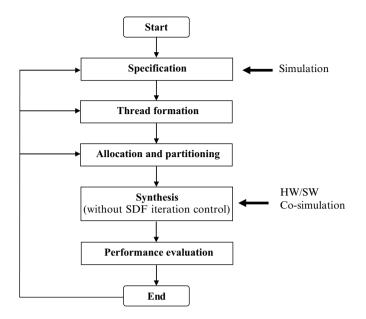

|   |      | 8.1.1   | Specification                             | 145 |

|   |      | 8.1.2   | FSM Compositions                          | 145 |

|   |      | 8.1.3   | Allocation and Partitioning               | 145 |

|   |      |         | Synthesis                                 | 147 |

|   |      | 8.1.5   | Performance Evaluation                    | 148 |

|   | 8.2  |         | tion of DFCharts Specifications on HiDRA  | 148 |

|   |      | 8.2.1   | Signals and Variables                     | 148 |

|   |      | 8.2.2   | FSM Thread                                | 152 |

|   |      | 8.2.3   | Hierarchical and Parallel Compositions    | 155 |

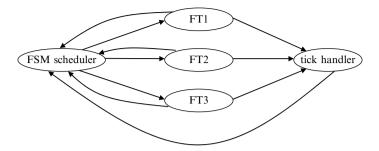

|   |      | 8.2.4   | FSM Scheduler                             | 157 |

|    |        | 8.2.5 Master Tick Handler 1                              | 159 |

|----|--------|----------------------------------------------------------|-----|

|    |        | 8.2.6 Slave Tick Handler 1                               | 162 |

|    | 8.3    | Frequency Relay Implementation 1                         | 162 |

| 9  | Conc   | lusions 1                                                | 169 |

|    | 9.1    | Summary and Overview 1                                   | 169 |

|    | 9.2    | Future Research 1                                        | 171 |

|    |        | 9.2.1 DDFCharts Design Flow 1                            | 171 |

|    |        | 9.2.2 Hardware Implementation 1                          | 171 |

|    |        |                                                          | 172 |

|    |        | 9.2.4 Including More Expressive Dataflow Models 1        | 172 |

|    |        | 9.2.5 Program State 1                                    | 172 |

|    |        | 9.2.6 Formal Verification 1                              | 173 |

|    |        | 9.2.7 Proof of Correctness for DFCharts Implementation 1 | 173 |

| Re | ferenc | es 1                                                     | 175 |

| In | dex    |                                                          | 181 |

# **List of Figures**

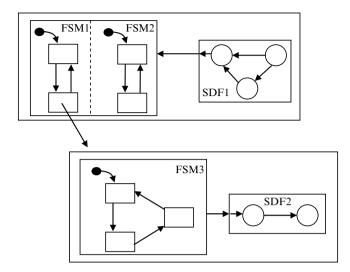

| Fig. 1.1  | Graphical syntax of DFCharts                                   | 5  |

|-----------|----------------------------------------------------------------|----|

| Fig. 2.1  | Simple state transition diagram                                | 8  |

| Fig. 2.2  | Possible trace for FSM in Fig 3.1                              | 8  |

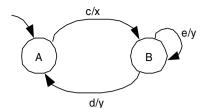

| Fig. 2.3  | FSM with valued events                                         | 8  |

| Fig. 2.4  | Mealy and Moore machines                                       | 9  |

| Fig. 2.5  | A Kahn process network example                                 | 10 |

| Fig. 2.6  | An SDF graph                                                   | 12 |

| Fig. 2.7  | Event ordering in DE and process networks.                     |    |

|           | (a) Discrete event (b) Kahn process network                    | 15 |

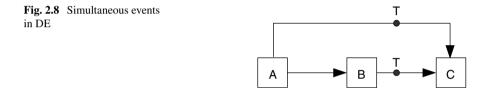

| Fig. 2.8  | Simultaneous events in DE                                      | 15 |

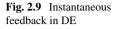

| Fig. 2.9  | Instantaneous feedback in DE                                   | 16 |

| Fig. 2.10 | Formal definition of Petri net                                 | 21 |

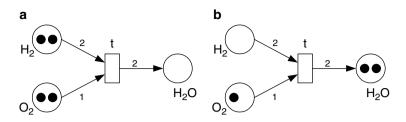

| Fig. 2.11 | Petri Net modeling chemical reaction.                          |    |

|           | (a) Before transition (b) after transition                     | 22 |

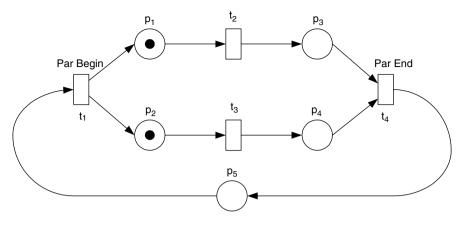

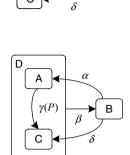

| Fig. 2.12 | Finite capacity net, its transformation and reachability graph |    |

|           | (a) Finite capacity Petri net (b) finite capacity net from     |    |

|           | (a) transformed (c) reachability graph for Petri net in (a)    | 23 |

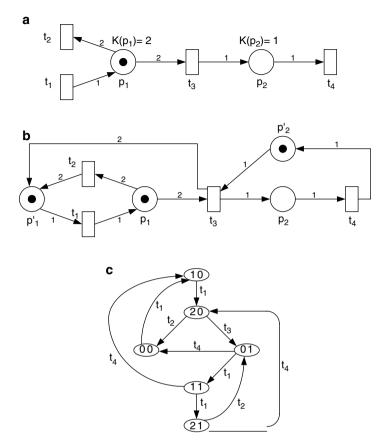

| Fig. 2.13 | A Petri net with concurrent activities                         | 24 |

| Fig. 2.14 | A basic FSM                                                    | 25 |

| Fig. 2.15 | Hierarchical equivalent of Fig. 2.14                           | 25 |

| Fig. 2.16 | Statechart with AND states                                     | 26 |

| Fig. 2.17 | Basic FSM equivalent to statechart in Fig. 2.16                | 26 |

| Fig. 2.18 | Infinite loop due to instantaneous broadcast                   | 27 |

| Fig. 2.19 | Argos example                                                  | 28 |

| Fig. 2.20 | Causality errors (a) no solution (b) multiple solutions        | 29 |

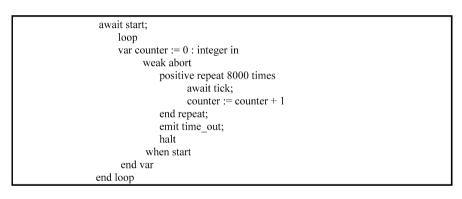

| Fig. 2.21 | Esterel example                                                | 32 |

| Fig. 2.22 | SystemC description of a counter                               | 36 |

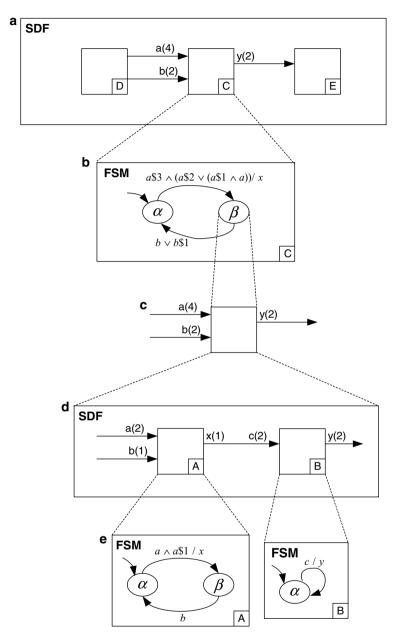

| Fig. 2.23 | Mixing FSM and SDF in Ptolemy                                  | 40 |

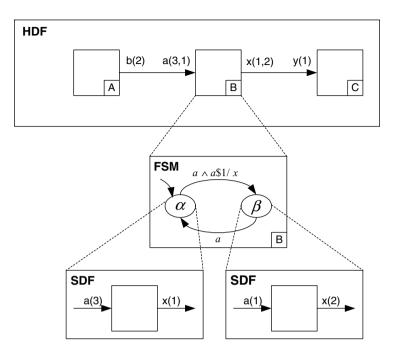

| Fig. 2.24 | HDF with FSM and SDF                                           | 41 |

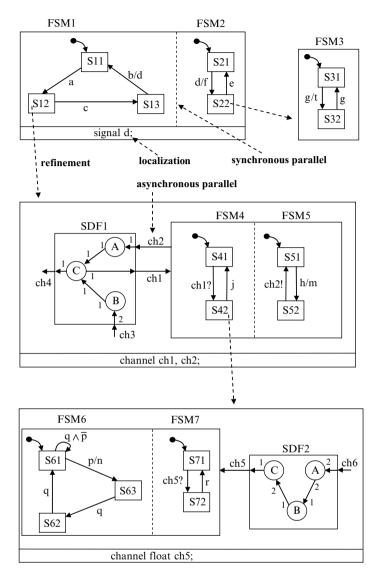

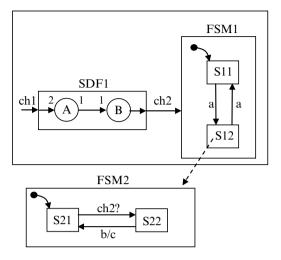

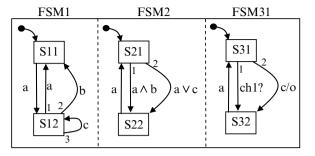

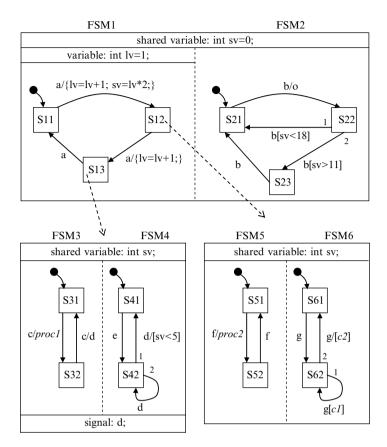

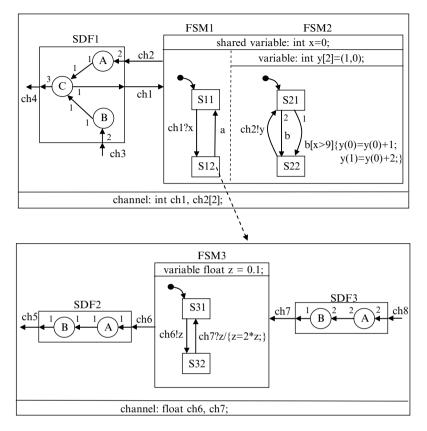

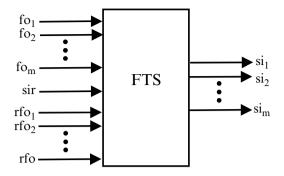

| Fig. 3.1  | A DFCharts specification                                 | 44 |

|-----------|----------------------------------------------------------|----|

| Fig. 3.2  | Communication between an SDFG                            |    |

| •         | and a lower level FSM                                    | 46 |

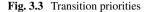

| Fig. 3.3  | Transition priorities                                    | 47 |

| Fig. 3.4  | DFCharts specification with variables                    | 48 |

| Fig. 3.5  | Communication between FSMs                               |    |

| U         | and SDFGs through variables                              | 50 |

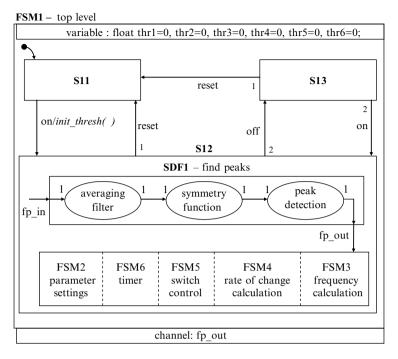

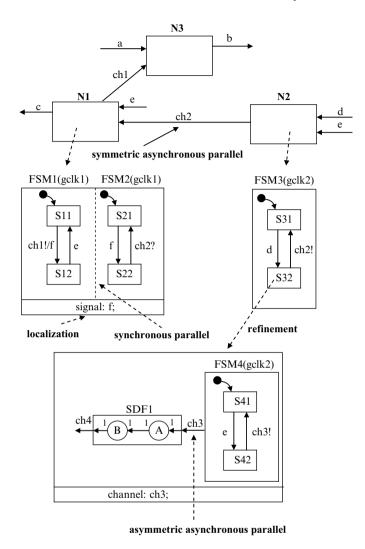

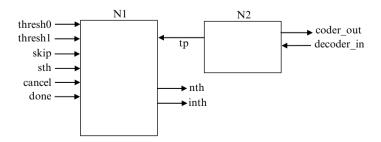

| Fig. 3.6  | Frequency relay – top level                              | 51 |

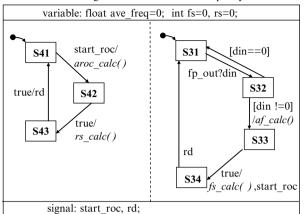

| Fig. 3.7  | Frequency and rate of change calculations                | 53 |

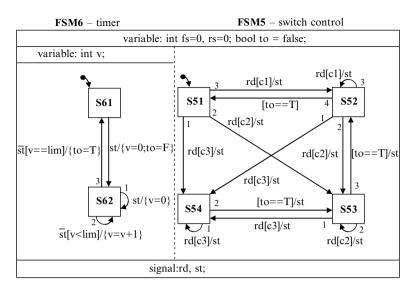

| Fig. 3.8  | Switch control and timer                                 | 54 |

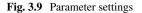

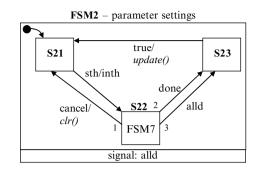

| Fig. 3.9  | Parameter settings                                       | 55 |

| Fig. 3.10 | Threshold reception                                      | 55 |

| Fig. 3.11 | A DDFCharts specification                                | 56 |

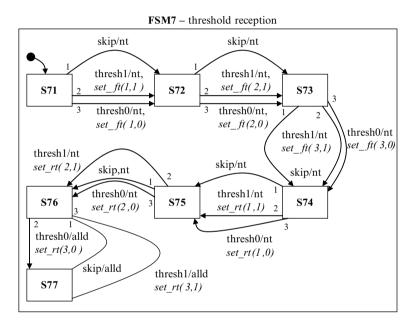

| Fig. 3.12 | Extended frequency relay – top level                     | 57 |

| Fig. 3.13 | Extended frequency relay – node N1                       | 58 |

| Fig. 3.14 | Extended frequency relay – node N2                       | 59 |

| -         |                                                          |    |

| Fig. 4.1  | Clocks in DFCharts                                       | 62 |

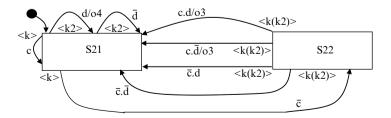

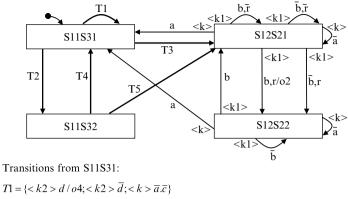

| Fig. 4.2  | Building the equivalent FSM for the example in Fig. 3.1  | 63 |

| Fig. 4.3  | Possible composition of a non-gclk FSM                   | 64 |

| Fig. 4.4  | A multiclock FSM                                         | 65 |

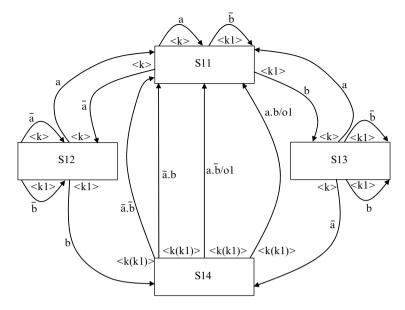

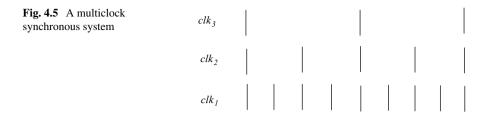

| Fig. 4.5  | A multiclock synchronous system                          | 66 |

| Fig. 4.6  | A specification with one input signal and two conditions | 67 |

| Fig. 4.7  | A specification with two input signals and one channel   | 68 |

| Fig. 4.8  | Synchronous product with a single clock                  | 69 |

| Fig. 4.9  | Synchronous product with two synchronized clocks         | 69 |

| Fig. 4.10 | Asynchronous product                                     | 69 |

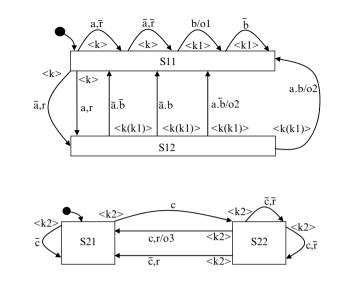

| Fig. 4.11 | FSM A1                                                   | 71 |

| Fig. 4.12 | FSM A2                                                   | 71 |

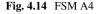

| Fig. 4.13 | $FSM A3 = A1   A2 \dots$                                 | 72 |

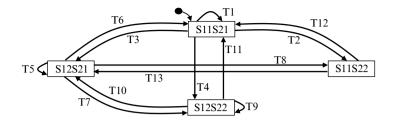

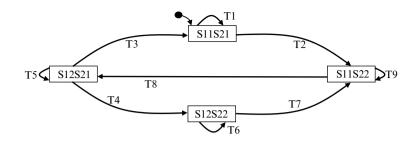

| Fig. 4.14 | FSM A4                                                   | 75 |

| Fig. 4.15 | FSM A5                                                   | 75 |

| Fig. 4.16 | FSM A6                                                   | 76 |

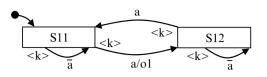

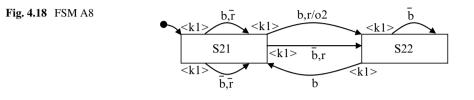

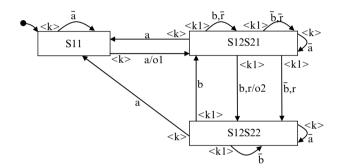

| Fig. 4.17 | FSM A7                                                   | 81 |

| Fig. 4.18 | FSM A8                                                   | 81 |

| Fig. 4.19 | FSM A9=A7 $\Downarrow_{S12}$ A8                          | 81 |

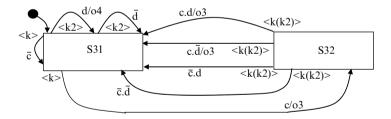

| Fig. 4.20 | FSM A10                                                  | 81 |

| Fig. 4.21 | $FSM A11 = A9 \downarrow_{S11} A10.$                     | 82 |

| Fig. 4.22 | FSM that represents SDF graph with two inputs            |    |

| C         | and two outputs                                          | 85 |

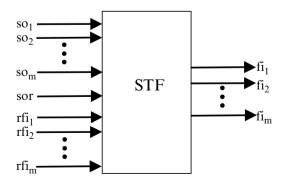

| Fig. 4.23 | Execution states of SDF1 from Fig. 3.5                   | 86 |

| Fig. 4.24 | STF process                                              | 87 |

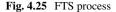

| Fig. 4.25 | FTS process                                              | 88 |

| Fig. 4.26 | A specification with behaviour sensitive                 |    |

| 0         | to clock speeds                                          | 92 |

|           | 1                                                        |    |

| Fig. 5.1     | Hierarchical FSMs in SystemC                            | 97  |

|--------------|---------------------------------------------------------|-----|

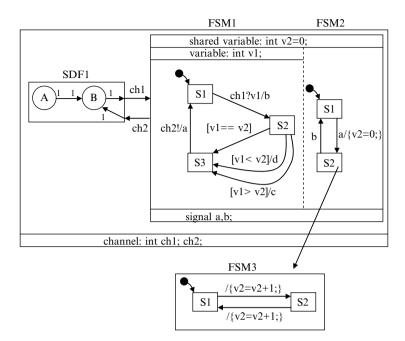

| Fig. 5.2     | Esterel specification of timer in frequency relay       | 97  |

| Fig. 5.3     | Section of SystemC code for averaging filter            |     |

| C            | in frequency relay                                      | 98  |

| Fig. 5.4     | Modified model to better suite the SystemC              |     |

| U            | specification                                           | 99  |

| <b>F'</b> (1 | -                                                       | 100 |

| Fig. 6.1     | Structure of FSM classes                                | 106 |

| Fig. 6.2     | Signals, variables and states in FSM4                   | 107 |

| Fig. 6.3     | The input for transition $S41 \rightarrow S42$ in FSM4  | 108 |

| Fig. 6.4     | The output for transition $S43 \rightarrow S41$ in FSM4 | 108 |

| Fig. 6.5     | The output for transition $S42 \rightarrow S43$ in FSM4 | 108 |

| Fig. 6.6     | Parameters of FSM4 constructor                          | 109 |

| Fig. 6.7     | Connections and initializations in FSM4                 | 110 |

| Fig. 6.8     | Creating transitions in FSM4                            | 110 |

| Fig. 6.9     | Signal start_roc, shared variable ave_freq              |     |

|              | and channel ch1 in FSM1                                 | 111 |

| Fig. 6.10    | The input for transition $S31 \rightarrow S32$ in FSM3  | 112 |

| Fig. 6.11    | Instantiation of FSM3                                   | 113 |

| Fig. 6.12    | Instantiation of FSM4                                   | 113 |

| Fig. 6.13    | Instantiation of SDF1                                   | 113 |

| Fig. 6.14    | Refinement of S2 in FSM1                                | 113 |

| Fig. 6.15    | Structure of SDF classes                                | 114 |

| Fig. 6.16    | Class that specifies SDF1                               | 114 |

| Fig. 6.17    | Averaging filter actor in SDF1                          | 116 |

| Fig. 6.18    | Structure of top level classes                          | 117 |

| Fig. 6.19    | Top level of frequency relay                            | 118 |

| Fig. 6.20    | Execution of the top level class of the frequency relay | 119 |

| Fig. 6.21    | Input file format                                       | 119 |

| e            | •                                                       | 120 |

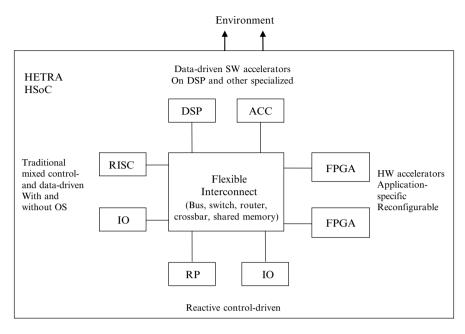

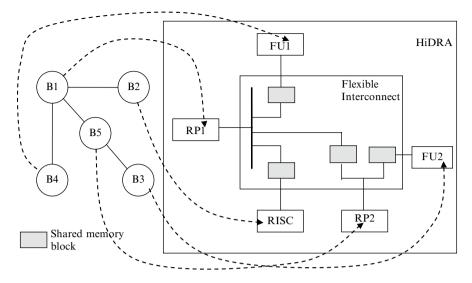

| Fig. 7.1     | Heterogeneous system on chip (HSoC) – HETRA             | 130 |

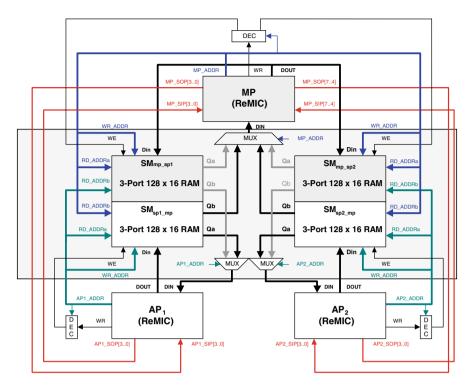

| Fig. 7.2     | REMIC block diagram                                     | 134 |

| Fig. 7.3     | ReMIC-PA block diagram                                  | 136 |

| Fig. 7.4     | Mapping of an application to HiDRA architecture         | 139 |

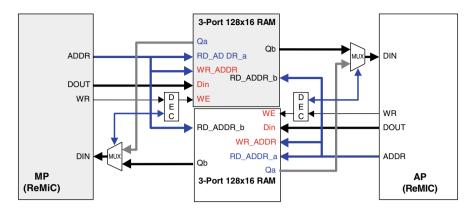

| Fig. 7.5     | SM configuration between MP and AP                      | 140 |

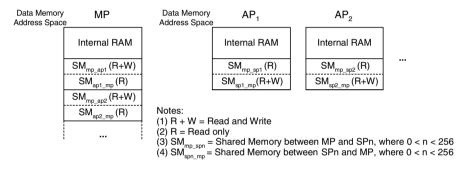

| Fig. 7.6     | Data memory address spaces of MP and SPs                | 140 |

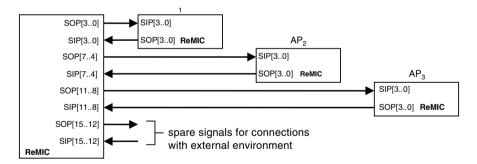

| Fig. 7.7     | Signal connections between MP and APs                   | 140 |

| Fig. 7.8     | HiDRA implementation with one MP and two APs            | 141 |

| Fig. 8.1     | DFCharts based design flow                              | 144 |

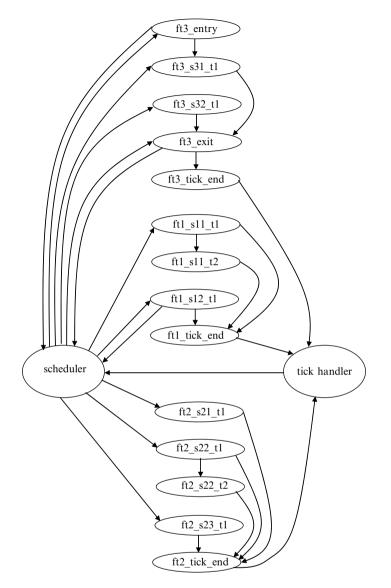

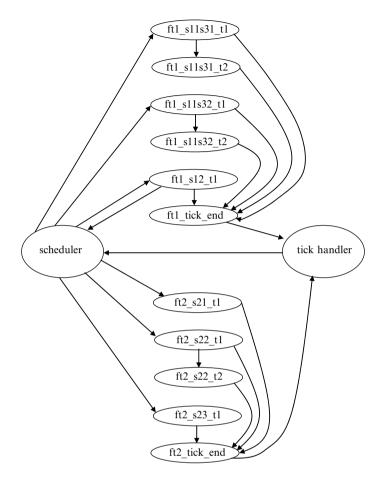

| Fig. 8.2     | Flow of control between FTs, FSM scheduler              |     |

| 0            | and tick handler                                        | 148 |

| Fig. 8.3     | Comparing memory and reactive signals                   | 150 |

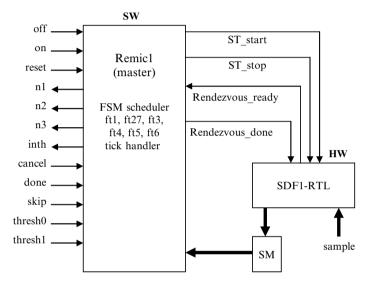

| Fig. 8.4     | Architecture for DFCharts implementation                | 151 |

| Fig. 8.5     | FSM thread                                              | 153 |

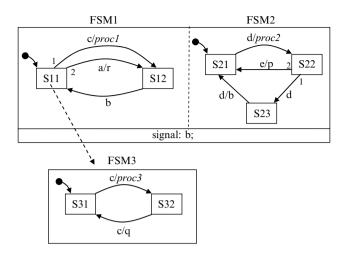

| Fig. 8.6     | A DFCharts specification consisting of three FSMs       | 156 |

|              |                                                         | 100 |

| Fig. 8.7  | Implementation of specification from Fig. 8.6      |     |

|-----------|----------------------------------------------------|-----|

|           | without any FSM compositions                       | 157 |

| Fig. 8.8  | Implementation of specification from Fig. 8.6      |     |

|           | with hierarchical composition of FSM1 and FSM3     | 158 |

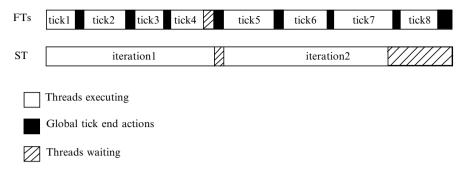

| Fig. 8.9  | FSM scheduler                                      | 158 |

| Fig. 8.10 | Master tick handler                                | 160 |

| Fig. 8.11 | Control of SDF iteration length                    | 161 |

| Fig. 8.12 | DFCharts design flow without SDF iteration control | 162 |

| Fig. 8.13 | Slave tick handler                                 | 163 |

| Fig. 8.14 | Partitioning for the second implementation option  | 164 |

| Fig. 8.15 | Frequency relay implementation with one            |     |

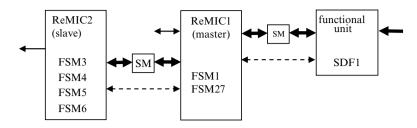

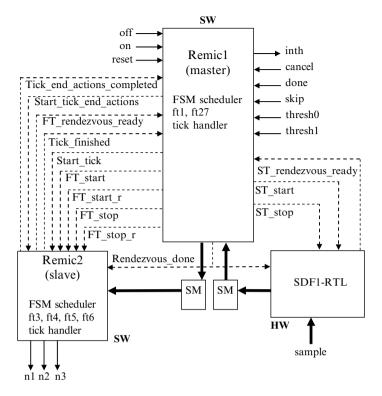

|           | ReMIC processor                                    | 164 |

| Fig. 8.16 | Frequency relay implementation with two            |     |

|           | ReMIC processors                                   | 165 |

|           |                                                    |     |

# **List of Tables**

| Table 2.1 | Esterel kernel statements                           | 30  |

|-----------|-----------------------------------------------------|-----|

| Table 2.2 | Boolean flows and clocks in Lustre                  | 33  |

| Table 5.1 | Level of support provided by SystemC and Esterel    | 100 |

| Table 5.2 | SystemC files for frequency relay specification     | 101 |

| Table 5.3 | Esterel files for frequency relay specification     | 101 |

| Table 7.1 | Reactive instruction set                            | 133 |

| Table 7.2 | ReMIC-PA additional power control instruction set   | 137 |

| Table 8.1 | Thread lengths in the first solution                | 165 |

| Table 8.2 | Program and data memories                           | 165 |

| Table 8.3 | Performance comparisons between two implementations | 166 |

## Chapter 1 Introduction

#### 1.1 Embedded Systems Design

An embedded computing system represents a set of processing elements embedded inside a larger system and usually communicates with the physical world. Although embedded systems are already widespread, the number of applications is expanding both in traditional areas such as communications, consumer electronics, aerospace, automotive, and in new ones such as biomedical.

Embedded systems differ in a number of ways from general purpose computing systems. An embedded system must be able to work at a rate imposed by the environment, which is not a requirement for a general purpose computing system. Concurrency and timing issues must be dealt with in embedded systems design. Furthermore, a range of constraints has to be faced. Some of the usual ones are performance, cost and power. While a general purpose computing system involves only software, an embedded system is often a mixture of software and hardware parts. Software runs on traditional microprocessors, digital signal processors (DSP) and various application specific processors (ASP). Hardware parts are implemented with application specific circuits (ASIC) or field programmable gate arrays (FPGA).

Traditionally, embedded system design starts with an informal specification. A decision is immediately made on how the functionality is going to be split between software and hardware. From this point, software and hardware parts are designed and verified separately. Software is written with programming languages like C/C++ and Java. Hardware description languages (HDL) like VHDL and Verilog are used for the design of the hardware part of the system. The major difficulty comes when interfaces between software and hardware parts are created. At this stage many small implementation details must be handled because there is no standard way in which software and hardware communicate. Many problems are discovered, which sometimes necessitate a complete redesign. Moreover, it is difficult to verify that the final implementation satisfies the original specification.

The traditional design methodology, which is still used in most embedded designs, may be satisfactory for smaller and medium sized systems. However, it is becoming increasingly difficult to use for large systems. The functionality and complexity of embedded systems keeps growing. Technology advances make it possible to integrate an increasing number of components on a single chip. Moore's law, which states that the number of transistors on a chip doubles every 18 months, still holds. On the other hand, design methods are improving much slower. This results in a problem, known as productivity gap [1].

Design at higher levels of abstraction is a promising solution to overcome the productivity gap [2]. It should start with a specification created with a formal language. A variety of languages have been proposed for that purpose [3]. A specification should capture only the behaviour of a system without any reference to implementation. Various names have been used to refer to this level of abstraction such as system, behavioural, algorithmic or functional level. As much as possible of the system verification should take place at the system-level. The system-level verification is much faster than the verification at lower levels of abstraction since many low level implementation details are not visible. Simulation is still the main verification method, but formal verification [4] is becoming important especially for safety critical embedded systems. After the verification has been completed, the final implementation consisting of software and hardware parts should ideally be synthesized automatically.

The behaviour of an embedded system is usually captured as a set of concurrent, communicating processes. The rules that are used for computation inside processes and communication between processes are determined by a *model of computation* [5, 6]. The computation inside each process is sequential. A finite state machine (FSM) [7] can be used to describe it, or more expressive models could be used that may have the full power of Turing machines. It is much more difficult to decide on the concurrency model that dictates the communication between processes. Currently, most embedded software design is done with threads which communicate using mutual exclusions locks, semaphores and interrupts. These communication mechanisms are difficult to use and often result in bugs that are hard to detect [8]. Sometimes a design may work for years before bugs show up and it suddenly crashes.

The alternatives to threads are various concurrency models with formal semantics. They employ different scheduling policies and communication mechanisms resulting in different orderings of events, which trigger or are associated with system operations. The most frequently used ones are discrete event [9], asynchronous dataflow [10], synchronous reactive [11], Petri nets [12] and process algebras such as communicating sequential processes (CSP) [13] and calculus of communicating systems (CCS) [14]. All these models impose some restrictions on communication but in return provide useful properties. The designer would have most freedom if communication between processes were unrestricted. However, tools would not be able to analyse such specifications and automated synthesis would not be possible. Instead, a specification would have to be refined manually to a lower level of abstraction. Because of manual refinement, it would be necessary to verify that the behaviour has been preserved.

In general there is a trade-off between analyzability and expressiveness in a model of computation. A successful model needs to strike a balance. It needs to provide a framework for analysis but at the same time it needs to be expressive enough.

An important feature of embedded systems behaviour is heterogeneity. Two major types of embedded systems behaviour can be identified: control-dominated and data-dominated. Control-dominated systems have to quickly react to events that arrive from the external environment at irregular and random time instances. A lift controller and vehicle automation are examples of control-dominated systems. Reaction time is less important for data-dominated systems which operate on samples that arrive at regular intervals. However, data-dominated systems perform computations that are much more intensive than those in control-dominated systems. Most of digital signal processing algorithms, such as FFT, FIR and IIR filters, are data-dominated. Most embedded systems contain both control-dominated and data-dominated behaviours. For example, a mobile phone has to perform data-dominated operations such as speech processing, coding, modulation but it also has to take care of control-dominated operations such as network protocols or reacting to user commands.

With the integration of analogue parts together with digital parts on a single chip, heterogeneity of embedded systems will become even more pronounced. Models that aim to address these mixed signal systems need to be able to support continuous time. In this book, we are concerned with purely digital systems. Thus, when we refer to heterogeneous embedded systems, we mean systems that represent a mixture of data-dominated and control dominated parts.

Well established models of computation have specific advantages but are not able to successfully handle entire heterogeneous embedded systems. Asynchronous dataflow models [10] consist of processes that communicate through FIFO channels with blocking reads. Using blocking reads ensures that outputs do not depend on the scheduling order and speeds of processes. Dataflow models have been successfully applied in signal processing and other transformational systems. However, they lack reactivity because of blocking reads. In the synchronous/reactive model [11], all processes read inputs and produce outputs simultaneously when a clock tick occurs. Blocking reads are not necessary for determinism. This feature is evident in synchronous language Esterel [15], which is deterministic, but has plenty of reactive statements. Synchronous/reactive model has also had success in the signal processing area with languages Lustre [16] and Signal [17], which have dataflow flavour. The requirement that all events in a system are synchronous can have a big implementation price. This especially applies in the design of large systems on chip. It may mean that all processing elements in a system must wait for each other at some point even though they are performing unrelated tasks. In the context of a pure hardware implementation, distributing a single clock can be a problem.

Modelling heterogeneous embedded systems is still an open research area with plenty of room for advancement. This is witnessed by the absence of mature, welldeveloped tools for heterogeneous systems. Esterel studio [18] is a commercial design environment from Esterel technologies, which uses Esterel language for creating specifications. It is very convenient for design of control-dominated systems but lacks features to support data-dominated behaviour. Another tool from Esterel technologies called SCADE is based around synchronous language Lustre, but it also allows insertion of FSMs to support control-dominated behaviours. The combination of Lustre and FSMs is still completely synchronous. Hence it could have implementation difficulties when applied in the design of large embedded systems. In order to produce efficient implementations, Polis [19] and its commercial successor VCC use a globally synchronous locally asynchronous (GALS) model called Codesign finite state machines (CFSM). However, their target is just control-dominated behaviour. Ptolemy [20] is a graphical environment that supports a variety of models of computation. It is still primarily used for simulation. Automatic synthesis has been demonstrated for synchronous dataflow (SDF) domain, but not for heterogeneous specifications. Simulink [21], while it does have some code generation capabilities, is also primarily a simulation environment. Recently, a heterogeneous model called SysteMOC [122, 123] has emerged. It combines dataflow and finite state machines in a relatively straightforward manner, which allows for efficient design space exploration and synthesis.

In this book, after reviewing most widely used models of computation and languages for embedded systems design, we present an approach for designing heterogeneous embedded systems based on our model of computation called DFCharts. A complete design flow from the specification to the implementation on a multiprocessor architecture is described. The methodology is demonstrated with a practical heterogeneous embedded system applied in power systems monitoring. In addition, we suggest how DFCharts based modelling can be used to improve design with two popular system level languages, SystemC and Esterel.

While DFCharts can be used for specification of distributed systems, it is not highly suitable for this task since it does not have any special features that support distributed processes. For this reason, an extension of DFCharts towards distributed systems called DDFCharts (Distributed DFCharts) has been designed. The semantics of DDFCharts will be described alongside DFCharts in this book. However, the design flow from DDFCharts specifications has not yet been completely developed and it remains an important future research direction.

#### 1.2 DFCharts

DFCharts combines hierarchical concurrent finite state machines (HCFSM) [22] with synchronous dataflow graphs (SDFG) [23]. Three communication mechanisms are employed in DFCharts: synchronous broadcast used between FSMs, FIFO channels used inside SDFGs, and rendezvous channels used between FSMs and SDFGs. The semantics of synchronous broadcast is as in Argos [24], a Statechart [22] variant with purely synchronous communication. An SDFG can be placed anywhere in the FSM hierarchy. Thus, it is possible to specify complex control logic that leads to activation and termination of SDFGs. When expressed with its graphical syntax, the DFCharts model looks as shown in Fig. 1.1.

Fig. 1.1 Graphical syntax of DFCharts

We have described the semantics of communication between FSMs and SDFGs in detail within tagged-signal model (TSM) framework [25]. Another type of semantics we use is based on automata. It is similar to the semantics of Argos. It represents the operation of an SDFG as an FSM. In this way a complete DFCharts model can be flattened to produce a single FSM. This in turn allows the model behaviour to be analysed globally. The automata based semantics can handle any dataflow model that has a clearly defined iteration and executes in bounded memory. For example, cyclo-static dataflow (CSDF) [26] can be easily incorporated in DFCharts, but Kahn process network (KPN) [27] would require an extension in the current semantics. We focus on SDF, which is suitable for a large range of applications.

All FSMs in a DFCharts model are driven by a single clock. On the other hand, each SDFG operates at its own speed. Structurally, a DFCharts model resembles an Esterel program with asynchronous tasks where asynchronous tasks are comparable to SDFGs and possibly other dataflow models placed in DFCharts. However, asynchronous tasks in Esterel are essentially part of the external environment, outside the Esterel semantics as we discussed in [28]. They are very vaguely defined. In DFCharts semantics, SDFGs are fully integrated.

#### **1.3 Book Organization**

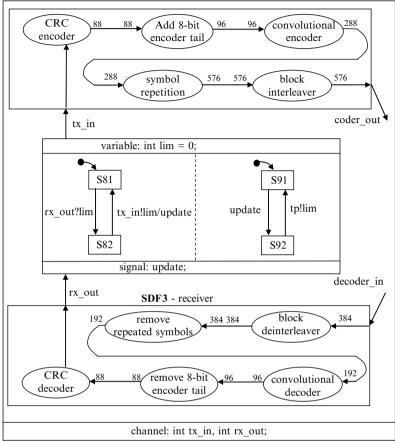

Chapter 2 provides a brief survey of models of computation that are used in embedded systems design. It also covers system level languages, which can be related to models of computation. Some of these languages are based on a single model of computation while others are capable of describing multiple ones. Chapter 3 informally describes the semantics of DFCharts using several simple examples. It also shows how DFCharts can be used to model a practical heterogeneous embedded system called frequency relay. This system is used throughout the rest of the book as a case study. In Chap. 3, we also present an extension of DFCharts towards distributed systems called DDFCharts. The modelling power of DDFCharts is demonstrated on an extended version of the frequency relay case study.

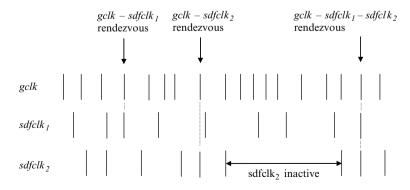

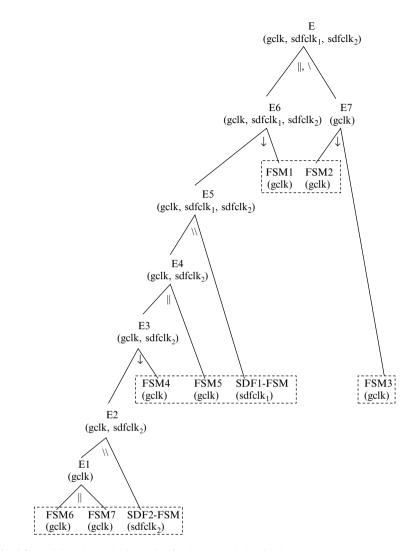

Chapter 4 presents the formal semantics of DFCharts. The core DFCharts semantics is automata based. However, the tagged signal model is also used for describing the interface between FSMs and SDFGs. An interesting feature of the automata based DFCharts semantics is its basic building block called multiclock FSM, where transitions can be triggered by more than one clock. In the usual FSM model all transitions are driven by a single clock.

Chapter 5 takes a closer look at two popular system level languages, SystemC and Esterel. It suggests how embedded system design with these two languages can be improved by incorporating DFCharts based modelling.

Chapter 6 describes Java environment for simulating DFCharts designs. While the Java packages underpinning execution and synchronization of FSMs are completely new, the simulation of SDFGs is done by invoking Ptolemy. There are very few interfacing problems in this solution since Ptolemy software has also been designed in Java.

Chapter 7 provides an overview of the current state of the art multiprocessor architectures and points to their deficiencies in implementing heterogeneous embedded systems. It then defines a new type of architecture called HETRA which has special features for supporting heterogonous embedded systems. The subset of HETRA called HiDRA has a major role in the DFCharts based design flow.

Chapter 8 describes in detail the DFCharts based design flow for heterogeneous embedded systems. It starts from a high level specification, which is refined into lower level processes that are mapped on HiDRA processing units. A major strength of the DFCharts based design flow is the ability to support a trade-off between implementation efficiency and verification effort. This is quite useful in the design of large heterogeneous embedded systems.

Finally, Chap. 9 presents a conclusion and some open future directions in research.

## Chapter 2 Models of Computation and Languages

This chapter looks at several important models of computation and languages for embedded systems design. We do not attempt to draw sharp distinctions between models and languages. Thus, the topics in this section are not divided strictly to either models of computation or languages. A model of computation is commonly used for defining the semantics of a language. However, when a model of computation is expressed with a simple syntax, it can also be called a language. For example, synchronous dataflow (SDF) is usually thought of as a model of computation. But as soon as it is expressed with a simple graphical syntax consisting of a network of blocks connected with arrows, it is not incorrect to call it a language.

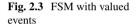

#### 2.1 Finite State Machine

An FSM [7] can be defined as a tuple of six elements:

- Q is a finite set of states

- $-\Sigma$  is a set of input symbols

- $-\Delta$  is a set of output symbols

- $\delta$  is a transition function mapping  $Q \times \Sigma$  to  $Q \times \Delta$

- q0 is the initial state

An FSM reacts to inputs by entering the next state and producing outputs as defined by the transition function  $\delta$ . The state transition diagram is a common way of representing an FSM. A simple state transition diagram is shown in Fig. 2.1.

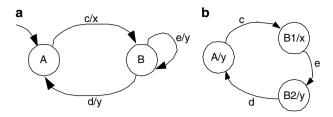

In this case Q={A,B};  $\Sigma$ ={c,d,e};  $\Delta$ ={x,y};  $\delta$ (A,c)=(x,B),  $\delta$ (B,d)=(A,y) and  $\delta$ (B,e)=(B,y), q0=A.

States are denoted by circles. Transitions are denoted by arcs. Every transition is associated with a guard and an action. This is labelled as *guard/action* on the corresponding arc. *Guard* denotes the enabling input event  $i \in \Sigma$  that causes a transition

Fig. 2.1 Simple state transition diagram

| Current state | Α | А | В | В |  |

|---------------|---|---|---|---|--|

| Input symbol  | d | с | e | d |  |

| Next state    | А | В | В | А |  |

| Output symbol | - | х | у | У |  |

Fig. 2.2 Possible trace for FSM in Fig 3.1

from one state to another. Action denotes the output event  $o \in \Delta$  that is produced as result of the transition.

If a non-enabling input event occurs in a certain state, the implicit self-transition is assumed. A sequence of reactions, sometimes called *trace*, shows a sequence of states and a sequence of output symbols caused by a sequence of input symbols. A possible trace for the FSM in Fig. 2.1 is shown in Fig. 2.2

The FSM model is closely related to the finite automata (FA) model. An FA is designed to recognize whether a sequence of input symbols belongs or does not belong to a certain language. Thus it accepts or rejects a sequence of input symbols. An FSM also produces a sequence of output symbols in addition to changing states.

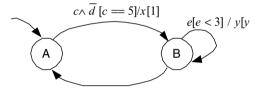

Input and output events can be *pure* or they can carry a *value*. If an event is pure, it can only be *present* or *absent*. A valued event, besides being present or absent, also has a value when it is present.

Valued events increase the expressiveness of an FSM. A Boolean expression representing the guard of a transition can contain values of events. Values of output events can be expressed in terms of arithmetic operations. An example of a state transition diagram with valued events is given in Fig. 2.3.

In the above example, "==" is used for input events to test equality, whereas "=" is used for output events as an assignment operator. A Boolean expression in a

Fig. 2.4 Mealy and Moore machines

transition guard may require that some events be absent for the transition to take place. In Fig. 2.3,  $c \wedge \overline{d}[c = 5]$  means that the transition occurs if c is present and has the value of 5 and d is absent.

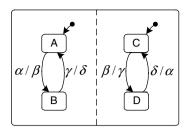

Generally, two types of FSMs are commonly used. A *Mealy machine* is an FSM where outputs are associated with the transition. A *Moore machine* is an FSM where outputs are associated with the present state of the FSM. The FSMs presented so far are Mealy machines since their outputs are associated with transitions.

A Moore machine may have more states than the equivalent Mealy machine. Figure 2.4 shows the Mealy machine (part (a)) from Fig. 2.1 with the equivalent Moore machine (part (b)).

FSMs can be specified formally in a clear way. Their strong formal properties make them attractive for safety critical applications. It is easier to avoid undesirable states with FSMs then with if-else, goto and other statements found in programming languages.

A single FSM could hardly be used to cover the entire control behaviour of a larger system because it would have an impractically large number of states. The usefulness of FSMs was largely increased when Harel introduced Statecharts (described in Sect. 2.7). In Statecharts, a single FSM state can be refined to another FSM. Thus, a hierarchical description of system behaviour is possible. The other major innovation in Statecharts is the possibility of having two or more states that are active at the same time. This helps in describing concurrent behaviours. A simple flat FSM has no means to describe hierarchy and concurrency, the two features that are commonly found in embedded systems.

#### 2.2 Kahn Process Networks

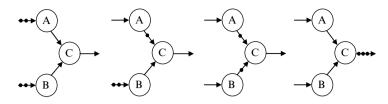

Synchronous dataflow (SDF), which is used in DFCharts, belongs to the group of dataflow models in which processes communicate through first-in-first-out (FIFO) channels using blocking reads. In order to understand the properties of SDF, we need to explore the most general model in the dataflow group, called Kahn Process Networks (KPN) [27].

KPN processes communicate through FIFO channels using blocking reads and nonblocking writes. At any point during the execution of a Kahn process network, a process

can either be waiting for an input or doing computations. Since blocking reads are used, a process cannot test a channel for the presence of data. If a process attempts to read from an empty channel it will become blocked until data arrives on the channel.

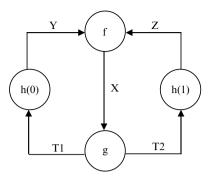

Figure 2.5 shows a KPN example that was used in [27]. The two instances of process h copy data from input to output, but initially they output 0 and 1. Without these initial tokens the network would be deadlocked from the start. Process g copies data from input channel X to output channels T1 and T2, alternately. Process f copies data alternately from input channels Y and Z to output channel X.

In the denotational semantics of Kahn process networks, processes are mathematically defined as functions that map potentially infinite input streams to output streams. A stream is a sequence of data elements  $X = [x_1, x_2, x_3, x_4...]$ , where indices are used to specify temporal features of the sequence. The empty sequence is marked by the symbol  $\perp$ . A relation on streams called *prefix ordering* [10] is useful for analyzing the mathematical properties of Kahn process networks. For example the sequence X = [0, 1] is a prefix of the sequence Y = [0, 1] which is in turn a prefix of Z = [0, 1, 2]. The relation "X is a prefix of Y or equal to Y" is written as  $X \subseteq Y$ .

A *chain* is an ordered set in which any two elements are comparable. Alternate names for a chain are *linearly ordered set* and *totally ordered set* [29]. In the context of Kahn process networks, elements of a chain are sequences and they are compared with the prefix ordering relation  $\subseteq$ . Any increasing chain  $\vec{X} = (X_1, X_2, ...)$  with  $X_1 \subseteq X_2 \subseteq ...$  has a least upper bound  $\Pi \vec{X}$  (symbol  $\Pi$  is used to denote a least upper bound). A least upper bound is a sequence whose length tends towards infinity:

$$\lim_{i\to\infty}X_i=\Pi X$$

The set of all sequences is a complete partial order (c.p.o.) with the relation  $\subseteq$ , since any increasing chain of sequences in this set has a least upper bound.

In Kahn process networks, a process f maps input streams to output streams. A process f is continuous if and only if for any increasing chain  $\vec{X} = (X_1, X_2, ...)$ :

$$f(\Pi \vec{X}) = \Pi f(\vec{X})$$

If a process is continuous, it is also monotonic (the opposite is not necessarily true). Monotonicity means that:

$$X \subseteq Y \Rightarrow f(X) \subseteq f(Y)$$

A process network can be described with a set of equations, with one equation for each process. For example, the process network in Fig. 2.5 can be represented by the following set of equations:

$$T_1 = g_1(X), T_2 = g_2(X), X = f(Y,Z), Y = h(T_1,0), Z = h(T_2,1)$$

The system of equations above can be reduced to a single equation. For instance the equation for X is:

$$X = f(h(g_1(X),0), h(g_2(X),1))$$

If all processes are continuous the set of equations has a unique least fixpoint solution. The solution represents the histories of tokens that appeared on the communication channels. For example, the solution for X is an infinite sequence of alternating 0's and 1's - X = f(Y,Z) = [0,1,0,1 ...]. The proof by induction can be found in [27].

The blocking read semantics of Kahn process networks ensures that processes are continuous. Therefore a set of equations describing a Kahn process network will have a unique least fixed point solution. This leads to a very useful property of KPN. Any execution order of processes will yield the same solution i.e. the same histories of tokens on the communication channels.

While the execution order cannot influence the histories of tokens, it can greatly impact memory requirements (buffer sizes). Since writes are non-blocking, there are no restrictions on buffer sizes. There are two major methods for scheduling Kahn process networks, data-driven scheduling and demand driven scheduling [30]. In data driven scheduling, the semantics of the Kahn process networks is satisfied in a simple way – a process is unblocked as soon as data is available. Data driven scheduling can lead to unbounded accumulation of tokens on communication channels.

An alternative strategy is to use demand driven scheduling of processes, where a process is activated only when the tokens it produces are needed by another process. Kahn and MacQueen describe a demand driven scheduling method in [31]. A process that needs tokens is marked as *hungry* and that causes the producer of those tokens to be activated. That, in turn, can cause another activation. All the scheduling is done by a single process.

Regardless of the type of scheduling employed, decisions in KPN have to be made at run time. Thus, context switching becomes inevitable if multiple processes run on a single processor. Valuable time has to be spent on saving the state of the current thread before the control can be transferred to another thread.

#### 2.3 Synchronous Dataflow

Synchronous dataflow (SDF) [23, 32] imposes limitations on KPN in order to make static scheduling possible. An SDF network is composed of *actors* that are connected by FIFO channels. When an actor fires, it consumes tokens from input channels and produces tokens on output channels. Firings of an SDF actor create a process. The firing rule of an actor specifies how many tokens are consumed on each input. In SDF, the constant number of tokens is consumed on each input in every firing i.e. the firing rule remains the same. It should also be emphasised that an SDF actor has to output a constant number of tokens on each output in every firing. Due to constant consumption and production rates of tokens it is possible to make very efficient static schedules.

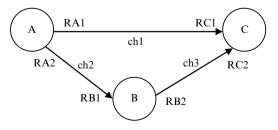

Figure 2.6 shows an SDF network that consists of three actors. Consumption and production rates are labelled on each channel. For example, from the direction of the ch1, it can be seen that its production rate is RA1 and its consumption rate is RC1.

There are two steps in constructing a static schedule for an SDF graph. The first step is to determine how many times each actor should fire during an iteration. An iteration is a series of actor firings that return the channels to their original state. The number of tokens in a channel is the same before and after an iteration. The first step is accomplished by solving the set of balance equations [32]. Balance equations state that production and consumption of tokens must be equal on all channels. The balance equations for the SDF graph from Fig. 2.6 are shown below.

$FA \times RA1 = FC \times RC1$  $FA \times RA2 = FB \times RB1$  $FB \times RB2 = FC \times RC2$

FA, FB, FC are integers showing how many times actors A, B and C fire in a single iteration. They form a *firing* or *repetition vector*. The least positive integer solution is taken. For example if RA1=2, RA2=2, RB1=3, RB2=3, RC1=6 and RC2=6 then FA=3, FB=2 and FC=1.

If the only solution to the set of equations is zeros, the SDF graph is said to be inconsistent [33]. This means that production and consumption of tokens cannot be balanced on all channels. As a result, the execution of an inconsistent SDF graph

Fig. 2.6 An SDF graph

results in unbounded accumulation of tokens on channels. The graph from Fig. 2.6 would become inconsistent if RC1 were equal to 5, for example.

The second step is to analyse data dependencies between SDF actors in order to determine the order of firings. Multiple valid execution orders can emerge from the analysis due to different interleaving of actor firings. For example, the execution orders AAABBC and AABABC can both be used for the SDF graph from Fig. 2.6.

An SDF graph can contain a cycle that is formed by two or more channels. Initial tokens must be placed on a channel in the cycle so that deadlock does not occur. This was relevant for the KPN example from Fig. 2.5 where the two h processes produced initial values.

SDF is suitable for a wide range of digital signal processing (DSP) systems with constant data rates. It has efficient static scheduling and always executes in bounded memory. These properties are very useful in embedded systems design. For this reason, SDF graphs have been adopted as a part of DFCharts. For systems with variable rates, KPN or dynamic dataflow models can be used. There are many dataflow models whose expressiveness falls between SDF and KPN, such as boolean dataflow (BDF) [34], cyclostatic dataflow (CSDF) [26], parameterized synchronous dataflow (PSDF) [35], multidimensional synchronous dataflow [36], synchronous piggyback dataflow [37] among others.

A large amount of research has been done on synchronous dataflow resulting in numerous techniques and algorithms for memory optimization [38–44], simulation [45, 46], software synthesis [47, 48], hardware synthesis [49–51], and HW/SW codesign [52–54].

#### 2.4 Synchronous/Reactive Model

The synchronous reactive (SR) model of computation [11] is the underlying model for the group of synchronous languages which includes Esterel [15], Argos [24], Lustre [16] and Signal [17]. A brief description of all four languages can be found in [55]. In the SR model of computation, time is divided into discrete instants. In each instant (tick), inputs are read and outputs are computed instantaneously. This is the central assumption in the *synchrony hypothesis* of the SR model. Instantaneous computation and communication makes outputs synchronous to inputs. The status of each signal has to be defined in each tick. It can be either present (true) or absent (false).

This model is similar to synchronous digital circuits that are driven by clocks. As a result, SR models can be efficiently synthesised into hardware. Software synthesis is also possible. In that case, the time between two successive instants is usually not constant.

The assumption of instantaneous computation facilitates hierarchical specification of systems. When a process is broken down into several other processes, they will all have instantaneous computation.

Zero delay communication represents a challenge for compilers of synchronous languages. An SR compiler has to be able to deal with causality loops that arise as a result of zero delays. When resolving the status of each signal in a tick three general outcomes are possible:

- There is a single solution. The signal is either present or absent.

- There is no solution. The model does not make sense.

- Both the presence and absence of the signal satisfy the model. Thus, the system is non-deterministic.

The first outcome is the desired one. The last two outcomes should be rejected by the compiler and an error should be reported to the user. The three possible cases are illustrated in Sects. 2.3 and 2.4 with Esterel and Argos programs.

There are two distinct styles of synchronous modelling [11], which emerged during the development of the synchronous languages. The first one is known as *State Based Formalisms* (SBF), the second one is known as *Multiple Clocked Recurrent Systems* (MCRS's). The oldest and most developed synchronous language Esterel, uses the first style. Argos is also an SBF-style synchronous language. On the other hand, declarative dataflow languages Lustre and Signal use the second style.

State based formalisms are convenient for specifying control-dominated systems but they are not efficient in dataflow modelling. It is the opposite with MCRS's. Their main use is in specifying signal processing systems but it is more difficult to specify systems that step through different states. There have been attempts to unify two styles in a single environment as in [56, 57].

Synchronous programs can always be compiled into finite state machines. This property is very important since it greatly facilitates formal verification and ensures that memory requirements are known at compile time.

In Kahn process networks and related dataflow models, events are partially ordered. Events on a single channel are totally ordered, but they in general have no relation with events on other channels. In synchronous models, events are totally ordered. This has an important impact in modelling reactive systems, which have to promptly respond to every event that comes from the external environment. Reactive systems often have to wait for several events simultaneously. A KPN process cannot wait on multiple channels at the same time since it must implement blocking reads in order to achieve determinism. On the other hand, a synchronous process can test a channel before reading it and still preserve determinism. The downside of the total ordering of events is that it may unnecessarily reduce the implementation space by overspecifying the system, especially in the case of data-dominated systems.

It is interesting to note that due to the differences in event ordering, synchronous dataflow (SDF) is not an appropriate name when KPN based dataflow models are compared against synchronous models. To avoid confusion, a better name would be statically scheduled dataflow (SSDF) as suggested in [6].

#### 2.5 Discrete Event Model

Discrete event (DE) [9] is the only MoC that incorporates the notion of physical time. Every event in DE carries a value and a time stamp. A DE block is activated when it receives an event to process. Events are processed chronologically. It is the

Fig. 2.7 Event ordering in DE and process networks. (a) Discrete event (b) Kahn process network

task of a DE scheduler to ensure that events with the smallest time stamp are processed first.

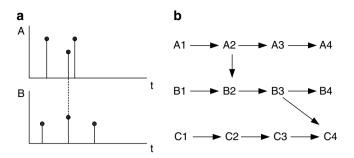

Events in DE are globally ordered. Figure 2.7 illustrates the difference in terms of ordering of events between the DE model and Kahn process networks.

In the DE model any two events are comparable even if they belong to different signals. Two events can either be simultaneous or one occurs before the other. This is shown in Fig. 2.7a. When a model employs a partial ordering scheme, as in Kahn process networks for instance, events that belong to the same signal are totally ordered but events across different signals may not be comparable at all. This is illustrated in Fig. 2.7b. There are three signals A, B and C. For example, events A1 and C1 are not related.

Total ordering of events can overspecify systems, which makes implementation more difficult. It is easier to build parallel systems when events across signals are not related. In theory the DE model should be suitable for modelling distributed systems, but creating a DE simulator for distributed systems can be a difficult task since there may be a very large number of events that need to be sorted.

It was mentioned in the previous section that events in SR are also totally ordered. However, the total ordering of events is easier to implement in SR than in DE, since every event in SR is related to the global clock. The SR compilers rely on the global clock to sort events.

Simultaneous events and feedback loops with zero delay are the two major problems in DE model. Figure 2.8 illustrates the problem with simultaneous events. Block B produces zero delay. The time stamp of an event that passes through block B remains unchanged. Therefore block C receives two events with the identical time stamp T, one from block A, and another from block B. The DE scheduler has to

determine which event block C should process first or whether it should take two events at the same time, in which case both events are covered in one firing.

There are three different methods that the current DE simulators use in dealing with this problem. The ambiguity in Fig. 2.8 may be left unresolved. The processing of the two events is scheduled randomly. The result is a nondeterministic system which is generally undesirable.

The second approach is to break the relevant time instant into microsteps with infinitesimal time delays between microsteps. By doing that, a two-dimensional time model is effectively introduced. The time between two microsteps can be marked as  $\Delta t$  for instance. For example when an event passes through block B its time stamp is increased by  $\Delta t$ . The event appears at the output of block B with the time stamp T+ $\Delta t$ . When block C is invoked it processes first the event from block B with the time stamp T+ $\Delta t$ . The infinitesimal time delays are not visible to the user. They are only used internally by the DE simulator.

The third approach is based on the analysis of data precedences statically within a single time instant, which is done in the Ptolemy [20] DE simulator. Arcs in a DE graph are assigned different priorities. The order of actions is always known when two simultaneous events appear at the same input.

Adding a feedback loop from block C to block A with C having zero processing time would create a situation that could not be resolved. This is shown in Fig. 2.9. An event circulates around the instantaneous loop without any increment in time stamp.

Digital hardware systems can be well described in DE. Both VHDL and Verilog simulators use DE as the underlying model of computation.

DE is mainly used for simulation. Global ordering of events with time stamps is expensive in real implementations.

#### 2.6 Communicating Sequential Processes

A system described in communicating sequential processes (CSP) [13] consists of processes that execute independently in a sequential manner, but have to synchronize when they are communicating. When a process reaches a point of synchronisation with another process it has to stop and wait for the other process regardless of whether

it has to read or write. Both reads and writes are blocking. Processes have to participate in common operations at the same time. This type of communication where processes have to synchronize in order to communicate is called *rendezvous*.

Every process is defined with its alphabet, which contains the names of events that are relevant to the description of the process. The actual occurrence of an event is regarded as instantaneous or atomic. When an activity with some duration needs to be represented, it should have a starting event and an ending event.

In [13] processes that describe various vending machines are used as examples. For example, a simple vending machine has only two relevant events – coin and choc (chocolate). When the machine gets a coin it gives out a chocolate. Generally upper case letters are used for processes and lower case letters are used for events. Let the process be called VM. Then its alphabet is written as

$\alpha VM = \{ coin, choc \} \alpha$  is used to denote an alphabet

In order to explain the behaviour of CSP, several key CSP operators are introduced, together with examples, in the following paragraphs. Some operators that are less frequently used are omitted. A detailed description can be found in [13].

The sequential behaviour of a process is described with the prefix operator " $\rightarrow$ ". Let x be an event and let P be a process. Then  $x \rightarrow P$  (pronounced "x then P") describes an object that which first engages in the event x and behaves as described by P. The prefix operator cannot be used between two processes. It would be incorrect to write  $P \rightarrow Q$ .

For example a simple vending machine that breaks after receiving a coin is described as:

#### $VM1 = coin \rightarrow STOP$

STOP is a process that indicates unsuccessful termination. STOP does not react to any events. A successful termination also exists in CSP and will be introduced later. If a process gets into that state, no event can occur. A simple vending machine that serves two customers before it breaks is described as follows:

$$VM2 = coin \rightarrow choc \rightarrow coin \rightarrow choc \rightarrow STOP$$

The description indicates that the event choc can happen only after the event coin. The machine will not give a chocolate unless a coin is inserted.

Many processes will never stop. After executing a certain action they will go back to their initial state. Processes of that kind can best be described recursively. CSP supports recursive definitions, i.e. definitions in which a process name appears on both sides of the equation. For example the process CLOCK has only one event called tick. Thus the alphabet of the clock is  $\alpha$ CLOCK={tick}. The process is recursively defined as

$$CLOCK = tick \rightarrow CLOCK$$

The above definition is equivalent to  $CLOCK = tick \rightarrow tick \rightarrow CLOCK$ ,

$CLOCK = tick \rightarrow tick \rightarrow tick \rightarrow CLOCK$  etc. This sequence can be unfolded as many times as necessary. Obviously recursive definitions are very useful in process descriptions.

Hoare seems to prefer another form of recursive definition that is more formal. For example a good vending machine that does not break is defined recursively in the way shown above as follows:

$$VM3 = coin \rightarrow choc \rightarrow VM3$$

The alternative and more formal definition according to Hoare is in the form of  $\mu$ X:A.F(X) where the letter  $\mu$  is used to denote a recursive expression, X is a local variable used in the recursive expression, and A is the alphabet of the expression i.e. the set of the names of events that appear in the expression. The alphabet is often omitted. Instead of X any other letter can be used, for example Y etc. VM3 is alternatively defined by  $\mu$  with the definition below:

VM3 =

$$\mu X$$

: {coin, choc}.(coin  $\rightarrow$  choc  $\rightarrow X$ )

Another important operator in CSP is the choice operator written as the bar |. The choice operator allows the environment in which the process operates to choose a sequence of actions that the process should perform. For example a vending machine may offer a choice of slots for inserting a 2p coin or a 1p coin. A customer decides which slot to use. The choice operator is used in conjunction with the prefix operator. In the expression below, two distinct events x and y initiate two distinct streams of behaviour:

$$(\mathbf{x} \rightarrow \mathbf{P} \mid \mathbf{y} \rightarrow \mathbf{Q})$$

If x occurs before y, the subsequent behaviour of the object is defined by P. Similarly if y occurs before x, the subsequent behaviour of the object is defined by Q. The environment decides which event occurs first and thus which path is taken. The choice operator has to be used with the prefix operator. It would be incorrect to write  $P \mid Q$ .

As an example for the choice operator, a vending machine that offers a choice to the customer is defined below. The customer inserts a 5p coin and then chooses which combination of change to take.

$$VM4 = in5p \rightarrow (out1p \rightarrow out1p \rightarrow out1p \rightarrow out2p \rightarrow VM4$$

$$| out2p \rightarrow out1p \rightarrow out2p \rightarrow VM4)$$

In all of the examples above only single processes were considered. In CSP processes can be made to run in parallel by using the concurrency operator  $\parallel$ . P  $\parallel$  Q means that the system is composed of two processes that are running concurrently. The two processes have to synchronize on any event that is common to their alphabets. Events that are not common are executed independently by one of the two processes.

An interesting example that illustrates the use of the concurrency operator is given in [13]. Two processes are defined and then composed into a system using  $\parallel$ . The two processes are called NOISYVM (noisy vending machine) and CUST (customer). The alphabet of NOISYVM is defined below.

$$\alpha$$

NOISYVM = {coin, choc, clink, clunk, toffee}

The machine offers chocolate or toffee. The event clink is the sound that a coin makes when it is inserted. The event clunk is another sound that the machine makes on completion of a transaction. This time the machine has run out of toffee and it only outputs a chocolate after receiving a coin.

NOISYVM =  $(coin \rightarrow clink \rightarrow choc \rightarrow clunk \rightarrow NOISYVM)$

The customer prefers to get toffee. When he doesn't get toffee he says a curse, which is included in the alphabet of CUST given below.

$\alpha$ CUST = {coin, choc, curse, toffee}

$$CUST = (coin \rightarrow (toffee \rightarrow CUST | curse \rightarrow choc \rightarrow CUST))$$

The system that results from the concurrent composition of the two processes is defined below.

(NOISYVM || CUST) =

$$\mu X.(coin \rightarrow (clink \rightarrow curse \rightarrow choc \rightarrow clunk \rightarrow X)$$

$| \text{ curse} \rightarrow \text{clink} \rightarrow \text{choc} \rightarrow \text{clunk} \rightarrow X ))$

It should be noted that the two processes are synchronized on the event choc: the machine outputs it and the customer takes it. Choc appears in both alphabets. On the other hand, the events curse and clink occur asynchronously. They can occur one before the other or simultaneously. If they occur simultaneously it does not matter which one is recorded first.

This example clearly illustrates the essence of CSP: processes have to synchronize only on common events. Otherwise, they are asynchronous. Therefore CSP is not a completely synchronous MoC like synchronous/reactive model. In the SR model all actions are executed in lock-step. In CSP, processes synchronize only at rendezvous points.

Several other operators are briefly mentioned in the rest of the section.

When two processes P and Q are composed into a system, but do not have to synchronize on any events, their composition is written as  $P \parallel \mid Q$  which is read "P interleave Q". The events of the two processes are arbitrarily interleaved.

The unsuccessful termination is represented with the process STOP. The successful termination also exists and is represented by the process SKIP. SKIP does not react to any events in the same way as STOP. If a process finishes with SKIP it may be followed by another process. This is written as P;Q. Q is started after P successfully terminates.

In the examples shown so far, events could not be classified as inputs or outputs. In CSP the distinction between inputs and outputs is made using *channels*. Channels carry events. For example a simple process that inputs a message and then outputs the same message is defined as follows

COPYBIT =  $\mu X.(in ? x \rightarrow (out ! x \rightarrow X))$

where

$\alpha in (COPYBIT) = aout (COPYBIT) = \{0,1\}$

The alphabet of the input and output channels shows that the events 0 and 1 can occur on both channels.

Around the same time CSP was being developed, another similar model was emerging. The model is called Calculus of Communicating Systems (CCS). The model was created by Milner who later wrote a book about it [14]. Generally the two models are fairly similar, partly because the developers influenced each other while working on them. The basis of CCS are also processes that independently operate but have to synchronize on common events. Both models had a large impact on the research in concurrent systems. One of the main reasons for that is a sound formal treatment behind both models. An important property of concurrent systems such as deadlock can be formally analysed in CSP and CCS. Another example of formal analysis available in CSP and CCS is determining whether an implementation of a process satisfies its specification.

## 2.7 Petri Nets

Petri nets [12] is a graphical model that emerged in 1960s. Since then, many applications have been modeled with Petri nets and many research papers related to them have been published. While Petri nets is a tool for graphical modelling, it can also be mathematically analysed. In this section, though, only the basic features of Petri nets are introduced through examples.

Petri nets can be used to describe a wide range of applications. Systems that are suitable to be described by Petri nets are asynchronous, concurrent, distributed, and nondeterministic.

A Petri net is a bipartite directed graph. It consists of two kinds of nodes: places and transitions. Places are usually represented as circles while transitions are usually represented as bars or boxes. Places and transitions are joined by arcs. An arc can be drawn between a place and a transition but it is not allowed to join two places or two transitions. An arc can go from a transition to a place in which case it is marked as  $(t_i, p_i)$  or it can go from a place to a transition in which case it is marked as  $(p_i, t_i)$ . It cannot go from a transition to a transition  $(t_i, t_j)$  or from a place to a place  $(p_i, p_j)$ . With respect to a particular transition, a place can either be *input place* if the direction of the arc is (p,t) or *output place* if the direction of the arc is (t,p).

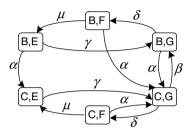

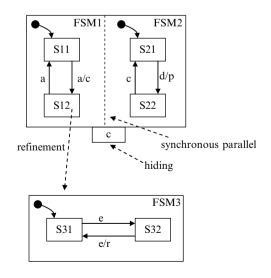

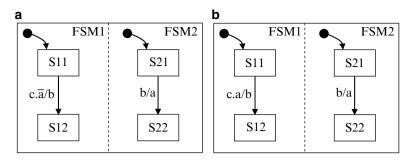

Places hold one or more tokens. Tokens are usually marked as dots inside places. When a Petri net *fires*, i.e. a transition is made, the numbers of tokens in various A Petri net is a 5-tuple,  $PN = (P, T, F, W, M_0)$  where: