Jeremy Holleman Fan Zhang Brian Otis

# Ultra Low-Power Integrated Circuit Design for Wireless Neural Interfaces

# Ultra Low-Power Integrated Circuit Design for Wireless Neural Interfaces

Jeremy Holleman • Fan Zhang • Brian Otis

# Ultra Low-Power Integrated Circuit Design for Wireless Neural Interfaces

Jeremy Holleman

Department of Electrical Engineering

and Computer Science

University of Tennessee

414 Ferris Hall

Knoxville, TN 37996-2100, USA

hollemj@u.washington.edu

Fan Zhang Department of Electrical Engineering University of Washington 185 Stevens Way Seattle, WA 98195-2500, USA fz2@u.washington.edu Brian Otis

Department of Electrical Engineering

University of Washington

185 Stevens Way

Seattle, WA 98195-2500, USA

botis@u.washington.edu

ISBN 978-1-4419-6726-8 e-ISBN 978-1-4419-6727-5 DOI 10.1007/978-1-4419-6727-5 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2010936899

### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# **Contents**

| 1 |                                                  | rences                                               | 1        |  |  |  |  |  |  |

|---|--------------------------------------------------|------------------------------------------------------|----------|--|--|--|--|--|--|

| 2 | Bio-Signal Interface Amplifiers: An Introduction |                                                      |          |  |  |  |  |  |  |

|   | 2.1                                              | Characteristics of the Recording Electrodes          | 9        |  |  |  |  |  |  |

|   | 2.2                                              | Characteristics of Bio-Signals                       | 11       |  |  |  |  |  |  |

|   |                                                  | 2.2.1 Brain Recordings                               | 11       |  |  |  |  |  |  |

|   |                                                  | 2.2.2 Muscle-Based Signals                           | 12       |  |  |  |  |  |  |

|   | 2.3                                              | Noise/Power Tradeoff                                 | 12       |  |  |  |  |  |  |

|   |                                                  | 2.3.1 Flicker Noise, 1/f Noise                       | 12       |  |  |  |  |  |  |

|   |                                                  | 2.3.2 Thermal Noise                                  | 13       |  |  |  |  |  |  |

|   | 2.4                                              | Representative Prior Art                             | 13       |  |  |  |  |  |  |

|   | Refe                                             | rences                                               | 14       |  |  |  |  |  |  |

| 3 | A La                                             | w-Power, Low-Noise, Open-Loop Amplifier              |          |  |  |  |  |  |  |

|   | for Neural Recording                             |                                                      |          |  |  |  |  |  |  |

|   | 3.1                                              | Open-Loop Amplifier Design                           | 15<br>15 |  |  |  |  |  |  |

|   | 3.2                                              | Results                                              | 17       |  |  |  |  |  |  |

|   | 3.3                                              | Effect of Non-Linearity on Neural Recordings         | 20       |  |  |  |  |  |  |

|   | 3.4                                              | Conclusions                                          | 23       |  |  |  |  |  |  |

|   | Refe                                             | rences                                               | 23       |  |  |  |  |  |  |

| 4 | Clos                                             | ed-Loop Neural Recording Amplifier Design Techniques | 25       |  |  |  |  |  |  |

|   | 4.1                                              | Design of a Closed-Loop Telescopic Amplifier         | 25       |  |  |  |  |  |  |

|   |                                                  | 4.1.1 Closed-Loop Architecture                       | 25       |  |  |  |  |  |  |

|   |                                                  | 4.1.2 Analysis of Pseudo-Resistors                   | 26       |  |  |  |  |  |  |

|   |                                                  | 4.1.3 Telescopic OTA Design Overview                 | 27       |  |  |  |  |  |  |

|   |                                                  | 4.1.4 Design Optimization                            | 28       |  |  |  |  |  |  |

|   |                                                  | 4.1.5 Stability and Common-Mode Feedback             | 29       |  |  |  |  |  |  |

vi Contents

|   | 4.2  | Design of a Closed-Loop Complementary-Input Amplifier  | 30 |

|---|------|--------------------------------------------------------|----|

|   |      | 4.2.1 Design of an Closed-Loop Fully-Differential      |    |

|   |      | Complementary-Input Amplifier                          | 30 |

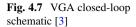

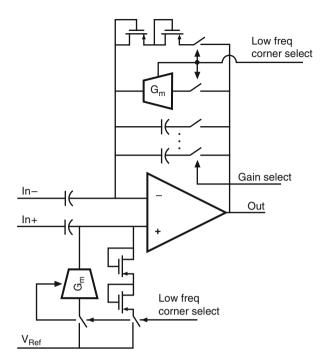

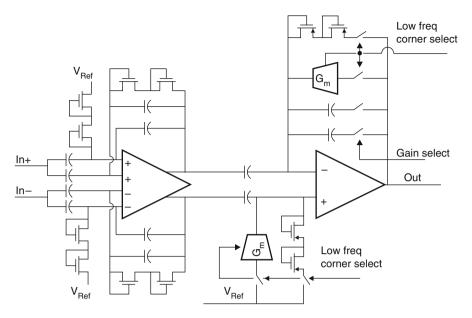

|   | 4.3  | Design of a Variable-Gain Amplifier                    | 33 |

|   | Refe | rences                                                 | 35 |

| 5 | Clos | ed-Loop Bio-Signal Amplifiers: Experimental Results    | 37 |

|   | 5.1  | Amplifier Testing                                      | 37 |

|   | 5.2  | Variable Gain Amplifier (VGA) Testing                  | 39 |

|   | 5.3  | In-Vivo Testing                                        | 41 |

|   | Refe | rences                                                 | 43 |

| 6 | Desi | gn and Implementation of Chopper-Stabilized Amplifiers | 45 |

|   | 6.1  | Chopper-Stabilization Technique                        | 45 |

|   |      | 6.1.1 Open-Loop Operation Principle                    | 45 |

|   |      | 6.1.2 Closed-Loop Operation Principle                  | 46 |

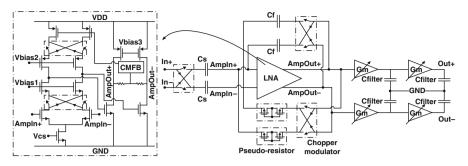

|   | 6.2  | Design of a Chopper-Stabilized Amplifier               | 46 |

|   | 6.3  | Hardware Implementation                                | 48 |

|   |      | 6.3.1 Transfer Function                                | 48 |

|   |      | 6.3.2 Amplifier Noise                                  | 49 |

|   | Refe | rences                                                 | 49 |

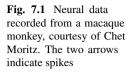

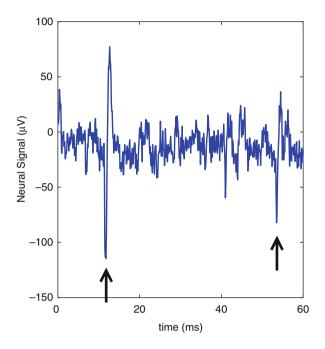

| 7 | Snik | e Detection and Characterization                       | 51 |

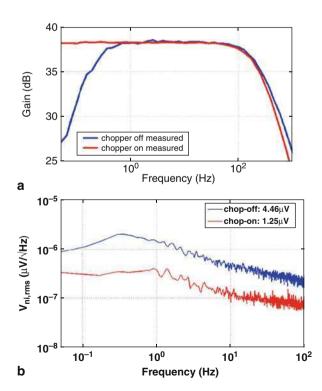

| ′ | 7.1  | The Spike Detection Task                               | 51 |

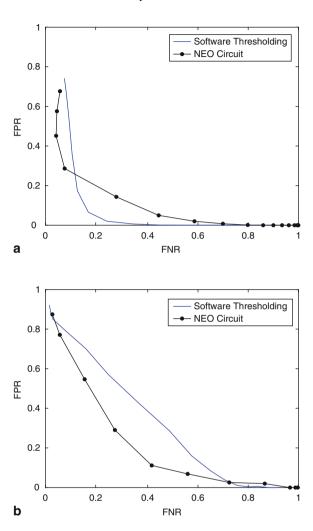

|   | 7.2  | Spike Detection Techniques                             | 53 |

|   | 7.3  | Analog and Mixed-Mode Computation                      | 54 |

|   | 7.4  | System Design                                          | 55 |

|   | ,    | 7.4.1 Spike Detector                                   | 56 |

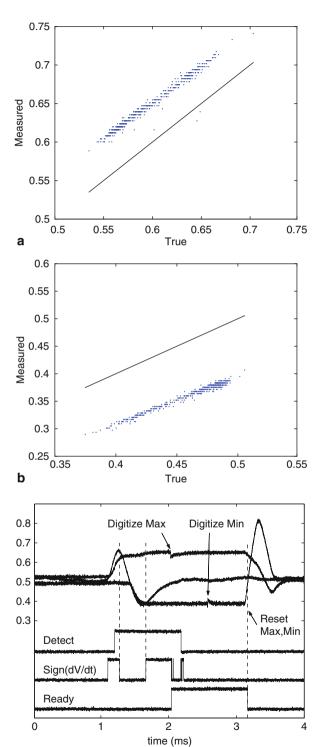

|   |      | 7.4.2 Feature Extraction                               | 57 |

|   |      | 7.4.3 Analog-Digital Converter                         | 58 |

|   | 7.5  | Results                                                | 59 |

|   |      | rences                                                 | 62 |

|   |      |                                                        | 02 |

| 8 | _    | e Sorting                                              | 65 |

|   | 8.1  | Overview                                               | 65 |

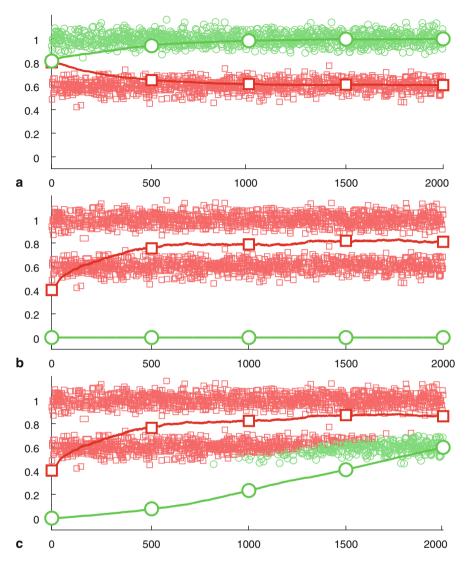

|   | 8.2  | K-Means Clustering Algorithm                           | 67 |

|   | 8.3  | Hardware Considerations for Analog On-Line Clustering  | 69 |

|   |      | 8.3.1 On-Line Median Learning                          | 69 |

|   |      | 8.3.2 Non-Ideal Computational Elements                 | 71 |

|   |      | 8.3.3 Asymmetric Updates                               | 72 |

|   | Refe | rences                                                 | 74 |

| 9 | Anal | og Clustering Circuit                                  | 75 |

|   | 9.1  | Floating-Gate Memories                                 | 75 |

|   | 92   | Device Characterization                                | 76 |

Contents vii

|     | 9.3   | Circui   | t Design                              | 79  |

|-----|-------|----------|---------------------------------------|-----|

|     |       | 9.3.1    | Clustering Circuit                    | 79  |

|     |       | 9.3.2    | Floating-Gate Memory Cell             | 81  |

|     |       | 9.3.3    | Decision Circuit                      | 83  |

|     | 9.4   | Exper    | imental Results                       | 85  |

|     |       | 9.4.1    | Update Rates                          | 85  |

|     |       | 9.4.2    | Memory Cell Retention                 | 87  |

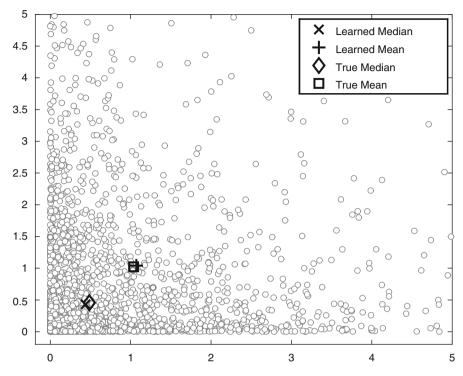

|     |       | 9.4.3    | Classification                        | 88  |

|     |       | 9.4.4    | Clustering Convergence                | 90  |

|     | 9.5   | Discus   | ssion                                 | 93  |

|     | Refe  | ences.   |                                       | 96  |

|     |       |          |                                       |     |

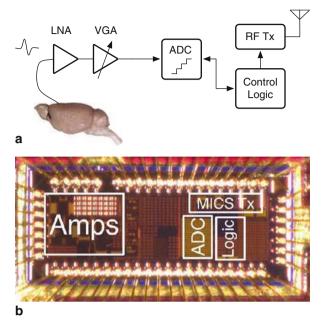

| 10  |       |          | P: A Wirelessly Powered Spike Density |     |

|     |       | _        | System                                | 97  |

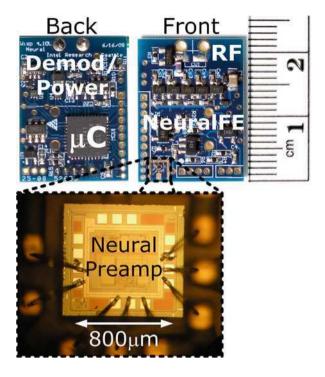

|     | 10.1  |          | ous Neural Recording Systems          | 97  |

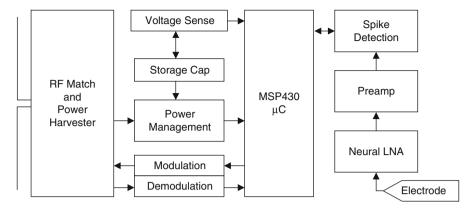

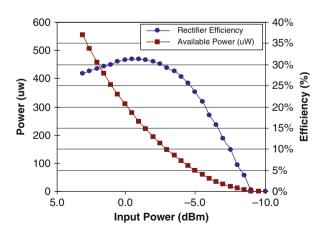

|     | 10.2  |          | n Design                              | 99  |

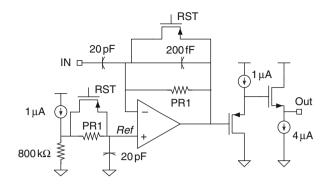

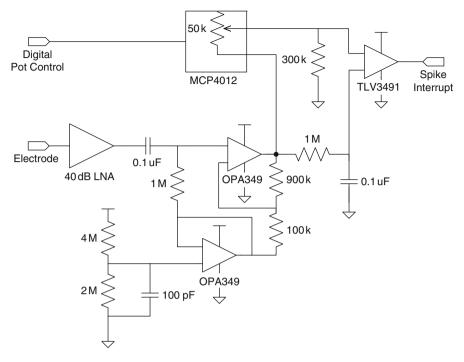

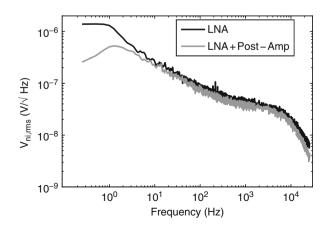

|     |       |          | Analog Signal Path                    | 100 |

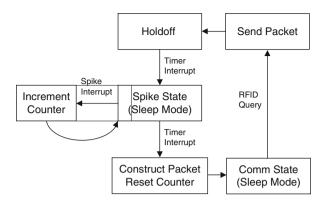

|     |       |          | Digital Control                       | 103 |

|     | 10.3  |          | lesults                               | 103 |

|     | 10.4  |          | imental Results                       | 107 |

|     | 10.5  | Concl    | usions                                | 108 |

|     | Refe  | ences.   |                                       | 109 |

| 11  | A 500 | ) ı. W V | Vireles Neural Streaming System       | 111 |

| 11  | 11.1  |          | g Front End                           | 111 |

|     | 11.2  |          | ersion and Control                    | 112 |

|     | 11.3  |          | -band Wireless Transmitter            | 113 |

|     | 11.4  |          | is                                    | 113 |

|     |       |          |                                       | 115 |

|     | TCICI | ciicos . |                                       | 113 |

| 12  | Conc  | lusions  | 8                                     | 117 |

|     | Refe  | rences.  |                                       | 118 |

| Inc | lov   |          |                                       | 110 |

|     |       |          |                                       |     |

# Chapter 1 Introduction

Neuroscientists are increasingly engaging the integrated circuit (IC) community to develop new tools for understanding the brain. Fundamental research performed on small animal models, for example, requires miniaturized instrumentation for long term freely behaving studies. Recording from non-human primates, rats, mice, and even insects is of interest. This research, in turn, will lead to advanced neuroprosthetics and brain-computer interfaces (BCI), which will demand even more functionality, robustness, and miniaturization from the electronics. Overly conservative performance goals lead to a loss of efficiency, while overly relaxed specifications lead to an ineffective system. Since there are no established standards, close interaction between IC designers and neuroscientists is critical. Our goal with this book is to present several case studies of low power circuit architectures that were designed for brain interface applications. Our chip specifications, design procedures, and measured results will be presented. Along the way, we hope to motivate the need for additional research and collaborations between engineers and brain scientists.

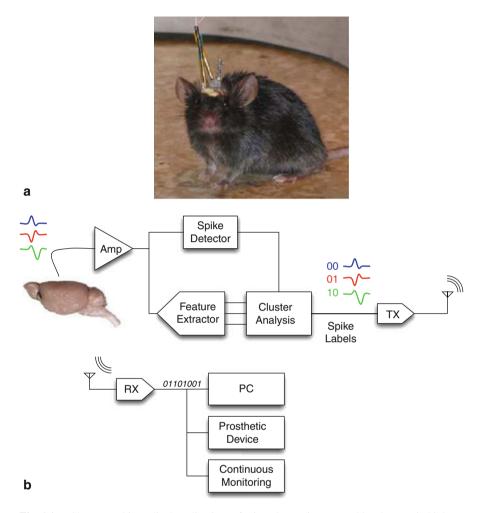

These collaborations have already led to important fundamental scientific research. For example, neural interfaces have facilitated discoveries in basic neuroscience research [4] by enabling previously impossible experiments. In the short term, these technologies are instrumental in developing implantable wireless sensors with a small form-factor and low weight. Wireless sensors will facilitate advanced biomedical research, like untethered monitoring of freely-behaving insects and small animals (Fig. 1.1a) [5]. These systems require wireless information transfer between implanted electrodes and external devices. In the long term, brain-machine interfaces (BMI) may provide new augmentative technology to help people with severe motor disabilities (Fig. 1.1b) [10]. BMIs acquire brain signals and extract specific features from them, then translate them into device control signals (e.g., controlling a mouse cursor). To people who lack any useful muscle control (e.g., due to cerebral palsy), or locked-in (e.g., end-stage ALS), BMIs could give the ability to answer simple questions quickly, control the environment, or even operate neuroprosthetic devices.

Prototype systems have demonstrated the potential to profoundly improve the quality of life for persons with severe impairments [13]. Medical applications have begun to appear, starting with the cochlear implant over three decades ago [8].

Fig. 1.1 a Short-term biomedical applications of microelectronics can enable advances in biology and medical research. For example, the wired connection to study mice shown here can be replaced with a wireless device, allowing the study of freely-behaving mice. **b** A typical neural recording architecture illustrating the concept of Brain-Machine-Interfaces (BMI) and Long-term biomedical applications of microelectronics

Currently, work is ongoing for neural interfaces to improve treatment for epilepsy and Parkinson's disease. Scientists and engineers are also investigating the possibility of neurally-controlled prosthetics: devices which would allow persons paralyzed by injury or disease to control a prosthetic through thoughts. Rudimentary neural control has been demonstrated both in humans [7] and in monkeys [12].

Current neural interfaces are limited by physical size and power consumption. One challenge in reducing power consumption is the noise requirement of the first gain stage. The small amplitude of extracellular-sensed neural signals ( $<200\,\mu V$ )

Introduction 3

necessitates low-noise amplification, which in turn requires relatively high bias currents. While some components of a neural interface, such as a wireless transceiver, may operate with a low duty cycle, the amplifiers must operate continuously. The combination of high duty cycle and low noise requirements frequently cause the amplifiers to dominate overall system power, particularly in systems with many channels.

An additional obstacle to reducing power consumption is the need for local, real-time processing of neural signals [6]. One particularly difficult and important analysis function for neural recording is spike sorting. Electrodes implanted in a brain can often detect action potentials from multiple neurons. Spike sorting, the task of distinguishing between the different neurons contributing to activity in a recording, can increase the information that a recording provides compared to simple thresholding algorithms. This extra information can improve the performance of medical devices such as neurally-controlled prosthetics, and improve the ability of neuroscientists to infer the meaning of experiments.

Unfortunately, spike sorting is a difficult function to implement within the power and area constraints of an implanted neural interface. Many spike sorting algorithms require extensive memory to store ensembles of recorded spikes, which consumes large amounts of chip area and power. For these reasons, a fully-integrated neural recording IC with on-chip spike-sorting has not yet been developed.

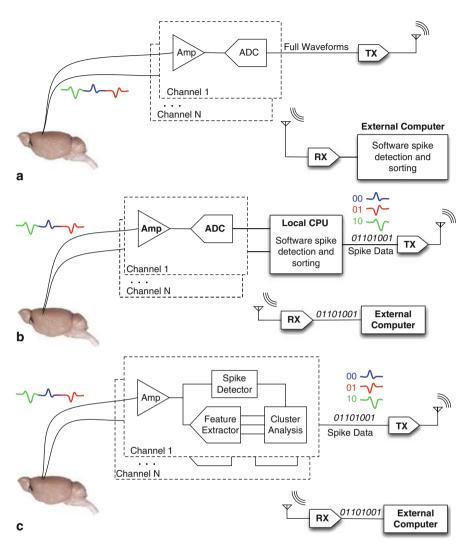

Figure 1.2 shows three possible architectures for an implantable neural recording system. In all cases, the first stage is a low-noise amplifier. One option, shown in Fig. 1.2a is to fully digitize the signals and transmit them to an external computer for processing. This strategy benefits from the flexibility and processing power of general-purpose computers. Users can choose processing algorithms to suit their needs and modify the algorithms at any time. Additionally, since no on-line spike sorting is performed, the raw data is available and any questions about the accuracy of the processing can be resolved. This architecture requires that analog-digital converters (ADC) run continuously for every channel. The illustration shows an independent ADC for every channel. A typical implementation would have several channels multiplexed to share an ADC, but a large number of channels would still require multiple area-intensive ADCs. While channel-multiplexing can reduce the area required for ADCs, it increases power consumption due to the additional buffering required [2], so that the power required for conversion can still be expected to scale at least linearly with the number of channels. The power required for analog-digital conversion can consume a significant portion of the system's power budget. Even more problematic is the wireless transmission. Because the full digitized waveform for every channel is transmitted over the wireless link, the transmitter must operate continuously and must also have very high throughput, resulting in prohibitively high power dissipation. For example, two recently published transmitters operating in the Medical Implant Communication Service (MICS) band, [1] and [9], achieved energy-pertransmitted-bit of 2.9 and 4 nJ/b and data rates of 120 and 100 kb/s, respectively. For a 100-channel system using 8-bit digitization and a 30 kS/s sample rate, similar transmitter efficiency would require 70-95 mW for the transmitter alone. For reference, an implant with 1 cm<sup>2</sup> of surface area can dissipate no more than 80 mW without risking thermal damage to tissue [11].

4 1 Introduction

**Fig. 1.2** Possible architectures for a wireless neural interface. **a** The signals are digitized and a wireless transmitter (Tx) sends the waveforms for all channels to an external computer, where they are processed in software. **b** All of the signals are digitized, then processed in software on a local CPU which is part of the implant. The output of the spike processing, which includes spike timestamps, sorting labels, and a channel index, are transmitted to an external computer, where they are collected for analysis or used to actuate a prosthetic. **c** Each channel is processed locally using dedicated analog circuits. As in (**b**), the processing results are transmitted to an external computer

A second possibility, depicted in Fig. 1.2b, is to digitize the signals and process them locally. A local CPU or DSP would detect spikes, perform spike sorting, and record the time and channel for each detected spike. The resulting spike data would then be transmitted to an external computer, where it could be collected for further

Introduction 5

analysis in the context of neuroscience research, or used to actuate a prosthesis. Such a strategy requires the same power and area for digitization as the previous architecture. The demands on the wireless transmitter are dramatically reduced since each full waveform is replaced with a set of spike descriptors. In exchange for reduced transmission, this architecture requires substantial local processing power. The CPU included in the implant must be capable of performing spike detection and sorting on all channels simultaneously and in real time. The chip must also contain sufficient memory to hold the processing software.

The processing can also be done locally using dedicated analog circuits, as shown in Fig. 1.2c. Similarly to the design in Fig. 1.2b, the burden on the communication link is relatively light because only spike descriptors are transmitted. Unlike either of the other two architectures, there is no need for a continuously-running ADC, since spikes are detected and sorted in the analog domain. In fact, the ADC could be omitted entirely, although it may be desirable to include one which can be enabled periodically to compare processing results with the raw waveform.

As noted in the above discussion, any architecture for an implantable neural interface will require a low-noise amplifier for every active channel. One of the goals of this book is the development of circuit techniques to reduce power dissipation in such an amplifier. The other primary contribution is the design of circuits which exploit the natural behavior of transistors to perform analog computation implementing spike detection, feature extraction, and clustering. Among these circuits is the first reported floating-gate memory cell using thin-oxide transistors for adaptation, which enables floating-gate circuits for machine learning algorithms to operate from supply voltages of 1.5 V. These cells are used to store spike templates, enabling a fully analog spike sorting circuit.

These circuits are the critical building blocks for an implantable neural interface using the architecture shown in Fig. 1.2c. Because they operate with extremely low power dissipation, they will enable improved implantable devices which can be used in many demanding applications.

To emphasize the circuit design challenges presented by this vision, we will briefly describe some of the specifications of the front-end neural recording amplifiers. Like the other building blocks described above, several design procedures and case studies of neural recording amplifiers will be presented in this book.

Bio-signals need to be first amplified before digitization or any signal processing. Depending on the application, several design requirements should be satisfied for the front-end amplifiers:

- Have sufficiently low input-referred noise to resolve microvolt-level spikes  $(10\,\mu\text{V})$

- Have sufficient dynamic range to convey or tolerate large local field potential (LFP) or EMG (muscle) signals (1–10 mV)

- Have much higher input impedance than the electrode-tissue interface and negligible DC input current;

- Amplify signals in the frequency band of interest (300–5 kHz for spikes, 10–100 Hz for LFP, 0.5–40 Hz for EEG, 0.5–200 Hz for ECoG, and 0.5–20 Hz for EMG).

6 1 Introduction

• Block (or cancel) DC offsets present at the electrode-tissue interface to prevent saturation at the amplifier output.

- Consume as little silicon area as possible and use few or no off-chip components to minimize size.

- Sufficient common-mode rejection ratio (CMRR) to minimize interference from 50/60 Hz power line noise, and sufficient power supply rejection ratio (PSRR) to prevent coupling from power supply noise (more severe if inductive power link is used).

- Dissipate no more than 10 mW of power.

The critical power limitation on the implantable recording electronics arises from the need to limit the chronic heating of surrounding tissue to less than 1°C. Preliminary experiments have shown that an implanted cortical 100-electrode array with integrated electronics can safely dissipate approximately 10 mW of power [3]. It follows that each channel must consume less than 100  $\mu$ W of power, excluding shared circuit blocks such as analog-to-digital converter (ADC), power regulation and transmitter.

The first few chapters describe techniques for designing neural amplifiers with low power consumption and low noise. Chapter 2 begins by describing the challenges involved in neural amplifier design. Chapter 3 describes a simple open-loop topology that achieves excellent noise/power performance, in part by sacrificing other metrics. Chapters 4 and 5 describe the design and measurements of two amplifiers. One combines a traditional architecture with low-voltage design techniques. The other incorporates the insights from the open-loop design and the low-voltage design just mentioned into a low-voltage closed-loop amplifier with very low noise and good overall performance.

The next three chapters describe circuit techniques for processing neural signals. Chapter 7 presents a chip which detects neural spikes, extracts descriptive features, and digitizes the features. Chapter 8 describes the process of spike sorting and some considerations for an analog implementation of a spike-sorting algorithm. Chapter 9 describes a circuit that uses thin-oxide floating-gate analog memories to realize an unsupervised clustering algorithm, which is the primary component of a spike sorting system.

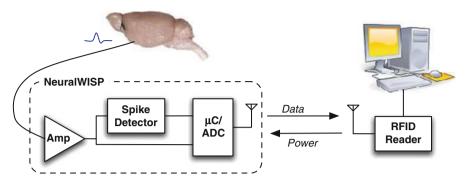

Finally, the last two chapters examine system-level integration in the context of two example systems. One is the NeuralWISP, a wirelessly-powered spike density recorder designed to work with a commercial RFID reader. The other is a neural streaming chip, which amplifies, digitizes and wirelessly transmits a neural signal. These systems are described in Chaps. 10 and 11 respectively.

### References

[1] Bohorquez J, Dawson J, Chandrakasan A (2008) A 350 μW CMOS MSK transmitter and 400 μW OOK super-regenerative receiver for medical implant communications. In: IEEE symposium on VLSI circuits, Digest of Technical Papers, Massachusetts Institute of Technology, Cambridge, MA, pp 32–33 References 7

[2] Chae M, Liu W, Sivaprakasam M (2008) Design optimization for integrated neural recording systems. IEEE J Solid-State Circuits 43(9):1931–1939

- [3] Harrison R (2008) The design of integrated circuits to observe brain activity. Proc IEEE 96(7):1203–1216

- [4] Jackson A, Mavoori J, Fetz E (2006) Long-term motor cortex plasticity induced by an electronic neural implant. Nature 444:56–60

- [5] Kipke D, Shain W, Buzsaki G, Fetz E, Menderson J, Hetke J, Schalk G (2008) Advanced neurotechnologies for chronic neural interfaces: new horizons and clinical opportunities. J Neurosci 28(46):11830–11838

- [6] Lebedev M, Nicolelis M (2006) Brain-machine interfaces: past, present and future. Trends Neurosci 29(9):536–546

- [7] Leuthardt E, Miller K, Schalk G, Rao R, Ojemann J (2006) Electrocorticography-based brain computer interface—the seattle experience. IEEE Trans Neural Syst Rehabil Eng 14(2): 194–198

- [8] Michelson R, Merzenich M, Pettit C, Schindler R (1973) A cochlear prosthesis: further clinical observations; preliminary results of physiological studies. Laryngoscope 83(7):1116–1122

- [9] Rai S, Holleman J, Pandey J, Zhang F, Otis B (2009) A 500 μW neural tag with 2 μV rms AFE and frequency multiplying MICS/ISM FSK transmitter. In: IEEE international solid-state circuits conference, Digest of Technical Papers, pp 212–213

- [10] Schalk G, McFarland D, Hinterberger T, Birbaumer N, Wolpaw J (2004) Bci2000: a general-purpose brain-computer interface (bci) system. IEEE Trans Biomed Eng 51(6):1034–1043 URL: http://www.kl-ic.com/white9.pdf

- [11] Seese T, Harasaki H, Saidel G, Davies C (1998) Characterization of tissue morphology, angiogenesis, and temperature in the adaptive response of muscle tissue to chronic heating. Laboratory investigation; J Tech Methods Pathol 78(12):1553–1562

- [12] Wessberg J, Stambaugh C, Kralik J, Beck P, Laubach M, Chapin J, Kim J, Biggs S, Srinivasan M, Nicolelis M (2000) Real-time prediction of hand trajectory by ensembles of cortical neurons in primates. Nature 408:361–365

- [13] Wise K, Anderson D, Hetke J, Kipke D, Najafi K (2004) Wireless implantable microsystems: high-density electronic interfaces to the nervous system. Proc IEEE 92(1):76–97

# Chapter 2 Bio-Signal Interface Amplifiers: An Introduction

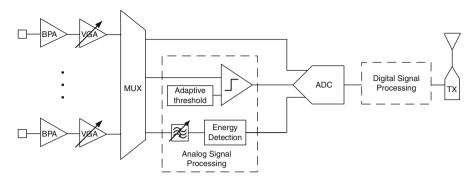

There are many design challenges involved in the circuit design of implantable neural recording systems. A generic biopotential-recording system is illustrated in Fig. 2.1. First, weak neural signals must be amplified, conditioned, and then digitized. The information then needs to be wirelessly transmitted out of the body to avoid possible infection from transcutaneous connectors. The power consumption increases with the number of recording channels and the complexity of system. However, the power dissipation of miniature implantable devices must be limited to prevent excessive tissue heating.

In a typical multi-channel system, one distinct low-noise amplifier is used per signal channel. Analog multiplexing theoretically would reduce the number of front-end amplifiers. However, in order to capture details of ever-changing neural activity across multiple electrodes, analog multiplexing requires switching times much shorter than the time constants associated with the amplifier's dynamics. Therefore, multi-channel systems typically use a separate amplifier for each channel, severely limiting the power available for each amplifier. As a result, power dissipation must be minimized as much as possible.

The next few chapters of this book will go into detail on ultra-low power low noise amplifier (LNA) design used in neural recording and other bio-signal acquisition systems. We first begin with the signal and electrode characteristics of these systems.

# 2.1 Characteristics of the Recording Electrodes

A signal/reference electrode configuration is typically used to record neural or muscle activity. The potential difference between each signal electrode and a large reference electrode is measured by the front-end differential amplifiers. The reference electrodes are usually low-impedance. However, in other applications, some signal electrodes are paired with high-impedance reference electrodes. The contact between metal electrode tip and extracellular fluid creates an electrical double layer that acts like a capacitor. Depending on the electrode area and surface roughness, the capacitance is estimated between 150 pF and 1.5 nF in common electrodes.

Fig. 2.1 A generic block diagram for a biopotential-recording system

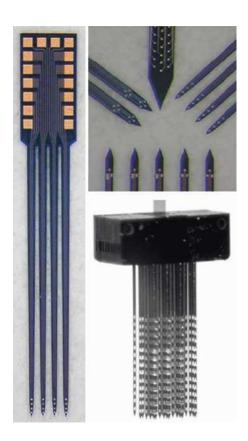

Recent advances in MEMS technology have produced small (less than 4 mm in each dimension) arrays of micro-electrodes containing as many as 100 recording sites [11].

Below we illustrate electrodes commonly used in research laboratories. Figure 2.2 shows the neural electrodes from NeuroNexus Technology. There are a total of 128

**Fig. 2.2** Typical invasive neural electrodes often used for in-vivo recording on rats or monkeys

sites with 200  $\mu$ m electrode spacing. The electrodes used to acquire the measurements in this book and in [6] are 50  $\mu$ m tungsten wires insulated with teflon. Each electrode is capacitive and has an equivalent impedance magnitude of 100 k–500 k $\Omega$  measured at 1 kHz.

# 2.2 Characteristics of Bio-Signals

# 2.2.1 Brain Recordings

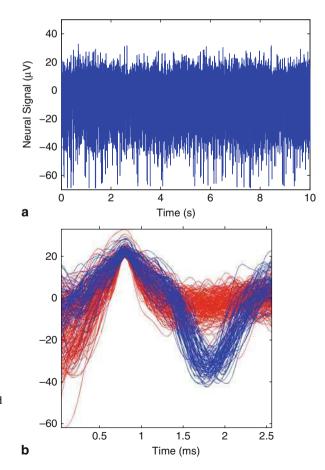

There are three main types of invasive signals that are of interest: action potentials (spikes), local field potentials (LFP), and electrocorticography (ECoG) signals. Spikes and LFPs can be obtained from single-unit recording. LFPs can be measured on the scalp as EEG signals, but experience a significant amount of attenuation. ECoG signals can be measured by invasive recording electrodes at the surface of the cortex. Typical spikes have signals occupying the 100 Hz–7 kHz band with amplitudes up to 500  $\mu$ V, while LFPs generally have energy below 100 Hz with amplitudes up to 5 mV [10]. Related to LFPs, EEG recordings have signals much attenuated to 10–20  $\mu$ V. ECoG signals have energy in roughly the 0.5–200 Hz band with amplitudes up to 100  $\mu$ V.

Neural spikes appear biphasic in in-vivo recordings with durations of 0.3–1.0 ms. The spikes fire once every several milliseconds to tens of milliseconds depending on the location of the electrode and the neuron's inherent characteristics. Spikes from different neurons usually have different shapes and firing rates, whereas spikes from the same neuron have nearly identical amplitude and duration. Spikes provide high spatial resolution at the cost of high power consumption in the recording electronics and challenging chronic implanting issues at the electrode-tissue interface.

LFPs result from the collective activity of many neurons in one region of the brain. Some neurons are too distant from the electrode to have their individual spikes resolved. LFPs have much less spatial resolution compared to neural spikes; however, it is more immune to attenuation (i.e., caused by scar tissue) and interference. Some research has demonstrated close correlation between specific arm movement and the energy of LFP signals in primates [3].

Another type of signal that is recently gaining popularity is categorized as electrocorticography (ECoG). ECoG signals are generally recorded from the surface of the cortex, and are thus less susceptible to chronic measurement issues such as tissue encapsulation and micromotion [2]. As a result, they can provide more robust measurement of signals. Although less spatially refined than spikes recorded from single-cell recordings, they are more spatially refined comparing to EEG signals (tenths of millimeters vs. centimeters [7]. Some recent research has demonstrated the effective usage of spectral decomposition of ECoG signals in neuroprosthetic applications [9, 13]. Ensemble neural firing is the biomarker for a number of clinically relevant phenomena, such as epileptic seizures and basal ganglia rhythms in Parkinson's disease [8].

|        | Bandwidth           | Amplitude           | Spatial Resolution | Invasiveness              |

|--------|---------------------|---------------------|--------------------|---------------------------|

| Spikes | 1–7 kHz             | <500 μV             | Highest            | Invasive                  |

| LFP    | $< 200 \mathrm{Hz}$ | $<5 \mathrm{mV}$    | Low                | Invasive                  |

| EEG    | $< 100 \mathrm{Hz}$ | $10-20 \mu\text{V}$ | Lowest             | Non-invasive              |

| ECoG   | 0.5 - 200  Hz       | $<100\mu\text{V}$   | Moderate           | Moderately invasive       |

| EMG    | 7–500 Hz            | 50 μ–2 mV           | _                  | Minimally or non-invasive |

Table 2.1 Characteristics of biosignals

# 2.2.2 Muscle-Based Signals

Electromyography (EMG) is another kind of signal measured from muscle cells. Measured EMG potentials range between  $50\,\mu\text{V}$  up to  $30\,\text{mV}$  in the band of  $7\text{--}500\,\text{Hz}$ , depending on the particular muscle. EMG signals are measured either by surface recording or needle (intramuscular) EMG. EMG signals are used in many types of research laboratories, including bio-mechanics, motor control, neuromuscular physiology, etc. Clinically, they are also used for the diagnosis of neurological and neuromuscular problems.

Table 2.1 is a summary of the characteristics of biosignals.

### 2.3 Noise/Power Tradeoff

As explained previously, reducing the power consumption of the circuitry is imperative to allow a practical multichannel implantable system. In order to understand how to optimize the power and noise trade-off, we first investigate types of noise and their relationship to bias current.

There are mainly two noise sources that circuit designers consider when designing low-frequency low-noise amplifiers: flicker noise and thermal noise.

# 2.3.1 Flicker Noise, 1/f Noise

Flicker noise is thought to be caused by traps associated with contamination and crystal defects [4]. These traps capture and release carriers randomly and give rise to a noise signal with energy concentrated at low frequencies. Input-referred flicker noise of a MOS can be represented by

$$\overline{v_i^2} = \left(\frac{K_f}{WLC_{ox}f}\right)\Delta f \tag{2.1}$$

### 2.3.2 Thermal Noise

In conventional resistors, thermal noise is due to the random thermal motion of the electrons, thus is directly proportional to T. Input-referred thermal noise voltage noise of a MOSFET can be represented by

$$\overline{v_i^2} = 4kT \left(\frac{2}{3g_m}\right) \Delta f \tag{2.2}$$

A common dimensionless figure of merit that summarizes this power-noise trade-off is the noise efficiency factor (NEF), first proposed in [14].

$$NEF = V_{rms,in} \sqrt{\frac{2 \cdot I_{Total}}{\pi \cdot U_T \cdot 4kT \cdot BW}}$$

(2.3)

Where  $I_{Total}$  is the total amplifier supply current,  $U_T$  is the thermal voltage  $k_T/q$ , BW is the amplifier bandwidth, and  $V_{ni,rms}$  is the amplifier's input-referred RMS voltage noise. This FOM compares the power-noise trade-off with that of a single ideal bipolar transistor.

# 2.4 Representative Prior Art

Micro-scale integrated circuits used for amplifying weak bioelectrical signals have been reported for many years [10, 11, 14]. Since then, many papers on low-noise amplifiers have been published [1, 10, 12, 14]. In 2003, [5] reported a fully integrated amplifier consuming  $80\,\mu\text{W}$  of power while exhibiting an RMS input-referred noise of  $2.2\,\mu\text{V}$ . Their impressive noise efficiency factor (4.0) has set the benchmark for amplifier designers of that time.

The amplifier in [5] is based on a simple operational transconductance amplifier (OTA) topology. A capacitive feedback network sets the midband gain of the amplifier. Any DC offset from the electrode-tissue interface is removed by capacitively coupling the inputs through capacitors. Large pseudo-resistors are used to set the low-frequency amplifier cutoff. The pseudo-resistors are used in place of bulky resistors in order to save area. They are MOS-bipolar elements that create a small-signal resistance of  $> 10^{12} \Omega$  for low-frequency operation. The noise optimization is accomplished by sizing the input stage transistors to operate in the sub-threshold region.

The topology in [5] is not optimal for a power-noise trade-off as 50% of the current is consumed in a branch that contributes no gain. The design in [15] employs a modified folded-cascode topology where the currents between the input and the folded branches are severely scaled (17:1) to save power and reduce the noise contribution from the folded branches. In addition, source degeneration is used at the input current sources to increase their output impedance and reduce their noise contribution. However, a folded-cascode topology is not a power-efficient solution

to achieve low noise because its extra branches consume more current and contribute more noise. In addition, the amplifier in [5] uses a  $\pm 5$  V, and [15] uses 2.8 V supply. With the trend towards integrating analog and digital subsystems on a single die, it has become increasingly important for analog circuitry to operate from the <1.2 V supply typical of modern digital CMOS.

In the next few chapters of this book, we will introduce several new amplifier topologies and compare their measured results to the state-of-the-art.

# References

- [1] Chandran A, Najafi K, Wise K (1999) A new DC baseline stabilization scheme for neural recording microprobes. In: Proceedings of the first joint BMES/EMBS conference, annual fall meeting of the Biomedical Engineering Society, 21st annual international conference of the Engineering in Medicine and Biology Society, Atlanta, Georgia, pp 386–387

- [2] Denison T, Consoer K, Santa W, Avestruz A, Cooley J, Kelly A (2009) A 2 μW, 100 nV/rtHz chopper-stabilized instrumentation amplifier for chronic measurement of neural field potentials. IEEE J Solid-State Circuits 42(12):2934–2945

- [3] Donoghue J, Sanes J, Hatsopoulos N, Gaal G (1998) Neural discharge and local field potential oscillations in primate motor cortex during voluntary movements. J Neurophysiol 79:159–173

- [4] Gray P, Hurst PJ, Lewis S, Meyer R (2009) Analysis and design of analog integrated circuits. Wiley, Berkeley

- [5] Harison R, Charles C (2003) A low-power low-noise cmos amplifier for neural recording applications. IEEE J Solid-State Circuits 39:122–131

- [6] Kipke D, ShainW, Buzsaki G, Fetz E, Menderson J, Hetke J, Schalk G (2008) Advanced neurotechnologies for chronic neural interfaces: new horizons and clinical opportunities. J Neurosci 28(46):11830–11838

- [7] Leuthardt E, Schalk G, Wolpaw J, Ojemann J, Moran D (2004) A braincomputer interface using electrocorticographic signals in humans. J Neural Eng 1(2):63–71

- [8] Levy R, Ashby P, Hutchison W, Lang A, Lozano A, Dostrovsky J (2002) Dependence of subthalamic nucleus oscillations on movement and dopamine in parkinson's disease. Brain 125:1175–1176

- [9] Miller K, Leuthardt E, Schalk G, Rao R, Anderson N, Moran D, Miller J, Ojemann J (2009) Spectral changes in cortical surface potentials during motor movement. J Neurosci 27(9):2424–2432

- [10] Najafi K, Wise K (1986) An implantable multielectrode array with on-chip signal processing. IEEE J Solid-State Circuits 21:1035–1044

- [11] Nordhausen C, Maynard E, Normann R (1996) Single unit recording capabilities of a 100-microelectrode array. Brain Res 726:129–140

- [12] Olsson RH III, Gulari M, Wise K (2002) Silicon neural recording arrays with on-chip electronics for in-vivo data acquisition. Paper presented at the 2nd annual international IEEE-EMBS special topic conference on microtechnologies in medicine and biology, Madison, Wisconsin, 2–4 May 2002

- [13] Shenoy P, Miller K, Ojemann J, Rao R (2008) Generalized features for electrocorticographic BCIs. IEEE Trans Biomed Eng 55(1):273–280

- [14] Steyaert M, Sansen W (1987) A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J Solid-State Circuits 22(6):1163–1168

- [15] Wattanapanitch W, Fee M, Sarpeshkar R (2007) An energy-efficient micropower neural recording amplifier. IEEE Trans Biomed Circ Syst 1(2):136–147

# **Chapter 3**

# A Low-Power, Low-Noise, Open-Loop Amplifier for Neural Recording

The signal path in a neural recording system typically starts with an amplifier in order to boost the signal levels and buffer the high source impedance. Because of the small signal amplitudes, amplifier noise must be minimized in order to avoid unnecessary degradation of the signal. Additionally, the high impedance of neural electrodes necessitates a high impedance input.

For a fixed bandwidth, an amplifier's input-referred noise scales inversely with the square of its current consumption. In order to achieve acceptable noise levels, the front-end amplifier often consumes a substantial fraction of the overall system power [5]. Recently there has been a great deal of research into the design of low-power amplifiers for neural recording [3, 4, 9]. The large majority of previous work has focused on conventional closed-loop amplifiers built from operational amplifiers.

Op-amps in closed-loop configurations have been the work-horse of analog design for decades, due to the flexibility, precise gain, and linearity that can be achieved. Open-loop amplifiers have been used primarily in high-frequency applications, such as wireless design, where the loop gain needed to realize the benefits of a closed-loop architecture is difficult to attain. However, when power dissipation is a primary consideration, an open-loop topology may become attractive even for low-frequency applications.

Open-loop amplifiers can give superior noise performance for a given power budget at the expense of linearity performance, imprecise gain control, and reduced power-supply rejection. In this chapter, we will describe a simple open-loop amplifier design which achieved the lowest NEF to date.

# 3.1 Open-Loop Amplifier Design

The design philosophy behind the use of an open-loop amplifier is the idea that the unique nature of the of the neural recording problem justifies the acceptance of a penalty in linearity and supply rejection in exchange for maximum noise efficiency.

The small signal levels of neural signals relax linearity requirements relative to those for general purpose amplifiers. If the application is the detection of action potentials, then precise signal reconstruction is not as important as preservation of

Fig. 3.1 Schematic of the open-loop amplifier

relative amplitudes, further relaxing both linearity requirements and the need for precisely defined gain. Provision of a stable power supply should be possible with careful system design. Implantation in the human body provides some shielding of the power supply against interferers such as 50/60 Hz noise. Low current consumption and low voltage requirements also ease the task of generating a stable supply.

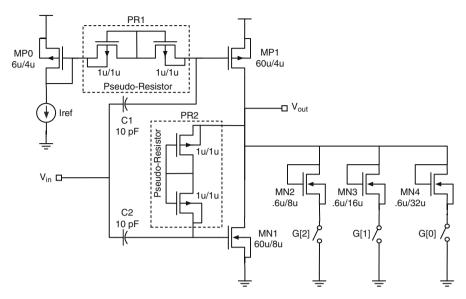

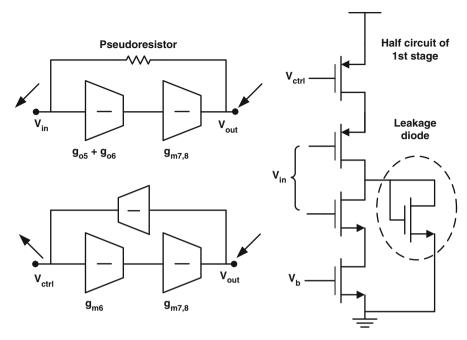

A single-ended, open-loop amplifier designed for recording action potentials is shown in Fig. 3.1 [6]. MOS-bipolar pseudo-resistors (PR) [4] are used to implement the AC coupling necessary to reject large DC offsets due to contact potentials. Each of the transistors in the pseudo-resistor is connected such that there is a MOS diode and a parasitic source-bulk diode connected in anti-parallel. If the voltage across the device is small, then neither diode will conduct strongly, and the effective resistance is very large ( $> 10~\text{G}\Omega$ ). The voltage across PR1 is limited to the magnitude of the input signal, while the voltage across PR2 is a function of the output signal. In order to keep the pseudo-resistor in the high-resistance region, two devices are connected in series.

Two strategies are utilized here to minimize the input-referred noise for a given bias current. The first is to limit the number of current branches. There is only one branch operating at full current. The reference current is ten times smaller than the amplifier bias current, so it does not contribute significantly to the total power consumption. The same RC network used to AC couple the PMOS input presents a low-pass filter to the reference transistor MP0, so noise from the current reference is not added to the signal, permitting the use of a relatively noisy low-power bias generator.

The second strategy is to drive the gates of both MP1 and MN1. A conventional common-source amplifier has a current-source load which adds noise to the signal, but performs no amplification. Because the input must be AC-coupled, it is possible to decouple the DC levels of the gates of transistors MP1 and MN1 while keeping

3.2 Results 17

them connected in the frequency band of interest. The amplifier's transconductance is effectively doubled, while output noise remains constant, reducing the input-referred noise voltage spectral density by a factor of two. Because the bandwidth is determined by the load capacitor and is set based on the application requirements, the input referred RMS noise voltage is also reduced by a factor of two.

The aspect ratios of MP1 and MN1 were chosen to place both transistors in the weak inversion regime in order to maximize  $g_m/I_D$ . The lengths of the transistors MP1 and MN1 were chosen to be large to obtain sufficient gain from a single stage and to yield an acceptable level of 1/f noise, which is inversely proportional to gate area [1]. The bias current is generated from an on-chip bias circuit based on [2] and multiplied by a 3-bit digitally-controlled current mirror. The bias current in the amplifier can be varied from 110 to 770 nA.

This amplifier includes a bank of digitally-enabled diode-connected transistors M2–M4, which allow the user to control the gain through the gain-control word G[0:2]. The aspect ratio of MN2 is 100 times smaller than that of MN1, and  $V_{GS,1} = V_{GS,2}$ , so the incremental conductance of MN2 is approximately 100 times smaller than  $g_{m,MN1}$ . In the absence of any channel-length modulation, and assuming equal subthreshold slope factors (and thus equal  $g_m$ ) for MN1 and MP1, MN2 would limit the gain to 200. This scheme was used to mitigate the risk of uncontrolled gain due to the open-loop topology. Including the effect of channel-length modulation, MN2 reduces the gain by about 6 dB, from 44.3 to 38.4 dB. With M3 and M4 enabled, the gain drops to 36.1 dB.

# 3.2 Results

This amplifier was fabricated in a  $0.5 \,\mu m$  SOI-BiCMOS process, employing CMOS devices exclusively. It occupies  $0.033 \,mm^2$  and the current reference occupies an additional  $0.013 \,mm^2$  of die area. The entire circuit can operate from a supply between 1 V and 5 V, while the measurements presented here were taken with a  $1.0 \, V$  supply.

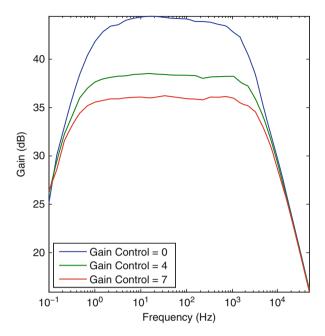

Figure 3.2 shows the frequency response over the entire range of gain settings. The current reference is configured to provide the maximum bias current, yielding  $I_{DS}=770\,\mathrm{nA}$  for MP1 and MN1. At the highest gain setting, the amplifier exhibits a gain of 44 dB and bandwidth of 1.9 kHz. The intermediate gain setting provides a gain of 38 dB and a 3-dB frequency of 3.6 kHz. With the lowest gain setting, the gain is 36 dB, and the 3-dB frequency is extended to 4.7 kHz. The remainder of this section will focus primarily on the low-gain setting, because it provides sufficient bandwidth to record action potentials. However, it is possible to extend the bandwidth at higher gain settings by increasing the bias current, either by overriding the internal bias generator, or with a modified design.

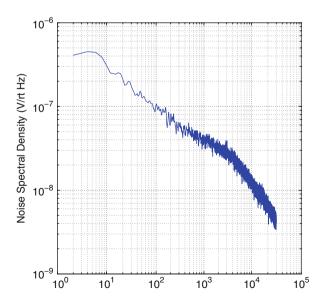

The input-referred noise spectrum of the amplifier is shown in Fig. 3.3. Despite the large transistor sizes, 1/f noise dominates. The total RMS noise at the input is  $3.5\,\mu\text{V}$ . It is difficult to discern the white thermal noise region of the spectrum because of the proximity of the 1/f noise corner to the output pole of the amplifier, but analysis predicts an input-referred thermal noise density of about  $20\,\text{nV}/\sqrt{\text{Hz}}$ .

Fig. 3.2 The frequency response of the open-loop amplifier with three different gain settings. The gain adjustment number refers to the digital gain control word G[0:2] in Fig. 3.1

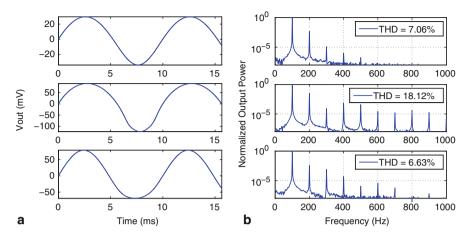

Feedback amplifiers achieve high linearity because their gain is determined by ratioed passive components. For open-loop amplifiers, nonlinearity of the transconductance and of the output impedance is manifested in a nonlinear input-output function. The linearity of the proposed amplifier can be assessed visually in Fig. 3.4a,

Fig. 3.3 Input-referred noise spectrum of the open-loop amplifier, computed as the measured output noise spectrum divided by the mid-band gain

3.2 Results

**Fig. 3.4** a Output voltage waveforms for 100 Hz sinusoidal input. (Top) Low gain setting, peak-to-peak amplitude of 1 mV. (Middle) Low gain setting peak-to-peak amplitude of 10 mV. (Bottom) High gain setting, peak-to-peak amplitude of 1 mV. **b** The output power spectrum with the amplifier input driven by a 100 Hz sinusoid. The amplitude and gain are the same as in (**a**)

which shows output waveforms corresponding to a 100 Hz input with various amplitudes. In the top waveform, with peak-to-peak input amplitude of 1 mV, the distortion is not visually noticeable. With a 10 mV input, the incremental resistance of the gain-control transistors MN2-4 decreases at the upper end of the range, causing substantial compression. For the third waveform, the amplifier is in the high-gain configuration, and the input amplitude is 1 mVpp. Figure 3.4b shows the power spectra of the same three waveforms shown in Fig. 3.4a. THD with the 10 mV input is quite high at 18.12%, but for a 1 mVpp input, THD is lower, at 7.06 and 6.63% for the low and high gain settings, respectively.

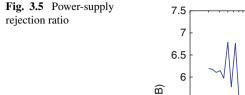

In applications where a quiet power supply cannot be guaranteed, power-supply rejection ratio must be examined. In the proposed amplifier, both MP1 and MN1 have their sources connected to a power supply and their gates capacitively connected to the input. Thus, the positive and negative supplies directly modulate the P- and N-type transconductors, respectively. Therefore one would expect that the gain from the positive power supply to the output will be approximately half the gain from input to output, resulting in a minimal PSRR of 6 dB. Figure 3.5 shows the positive power-supply rejection ratio from 20 Hz to 20 kHz, which is an average of 5.5 dB between 1 and 100 Hz. Because of the weak supply rejection, the output will be susceptible to supply noise existing in the frequency band of interest.

Table 3.1 compares the performance of this amplifier to other published biosignal amplifiers. The noise efficiency factor (NEF), introduced in [7], is used to compare the noise and power performance to other amplifiers:

$$NEF = V_{rms,in} \sqrt{\frac{2 \cdot I_{Total}}{\pi \cdot U_T \cdot 4kT \cdot BW}}$$

(3.1)

**Table 3.1** Comparison of neural amplifiers

|                             |              |              | -    |                             |                        |              |                   |

|-----------------------------|--------------|--------------|------|-----------------------------|------------------------|--------------|-------------------|

|                             | Gain<br>(dB) | $I_{Amp}$    | NEF  | υ <sub>ni,RMS</sub><br>(μV) | THD at Input<br>(mVpp) | PSRR<br>(dB) | Bandwidth         |

| Harrison and<br>Charles [4] | 39.5         | 16μΑ         | 4.0  | 2.2                         | 1% at 16.7             | ≥85          | 0.025 Hz-7.2 kHz  |

| Denison et al. [3]          | 45.5         | 1.2 μΑ       | 4.9  | 0.93                        | _                      | _            | 0.5–250 Hz        |

| Wu and Xu [9]               | 40.2         | 330 nA       | 3.8  | 0.94                        | 0.053% at 5            | 62           | 3 mHz-245 Hz      |

| Wattanapanitch et al. [8]   | 40.2         | 330 nA       | 3.8  | 0.94                        | 0.053% at 5            | 62           | 3 mHz-245 Hz      |

| This work                   |              |              |      |                             |                        |              |                   |

| Open-loop                   | 36.1         | 805 nA       | 1.8  | 3.6                         | 7.1% at 1              | 5.5          | 0.3Hz– $4.7kHz$   |

| Closed-loop                 | 38.3         | $12.5 \mu A$ | 2.48 | 1.95                        | 1% at 1                | 63           | 0.023 Hz-11.5 kHz |

where  $I_{Total}$  is the total amplifier current,  $U_T$  is the thermal voltage, BW is the amplifier bandwidth,  $V_{rms.in}$  is the input-referred RMS noise voltage.

For consistency with other work, the current specified in Table 3.1 excludes the current consumed by the bias generator, which consumes an additional 27 nA. This amplifier demonstrates the lowest NEF of any amplifier reported to date. Including the bias circuitry, the entire amplifier chip dissipates less than  $1\,\mu\text{W}.$

# 3.3 Effect of Non-Linearity on Neural Recordings

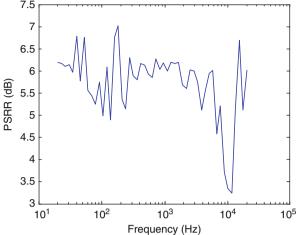

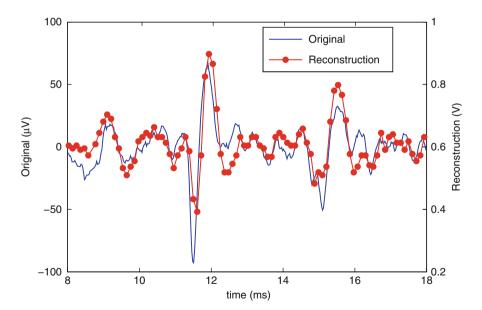

As mentioned above, the open-loop amplifier achieves its noise efficiency at the expense of linearity. Figure 3.6a shows the input-output voltage relationship. The slope of this curve at any given point gives the amplifier's small signal gain for a

Fig. 3.6 a Voltage transfer curve for the open-loop amplifier. b Amplifier gain versus input voltage

signal centered at the corresponding input voltage, and is shown in Fig. 3.6b. Because the amplifier is AC-coupled, these curves cannot be measured at DC and are therefore constructed from sinusoidal input and output measurements.

To explore the effects of amplifier non-linearity on a variety of input signals, the data in Fig. 3.6a was fit to a polynomial, then various hypothetical input signals were amplified by the nonlinear gain represented by the polynomial fit.

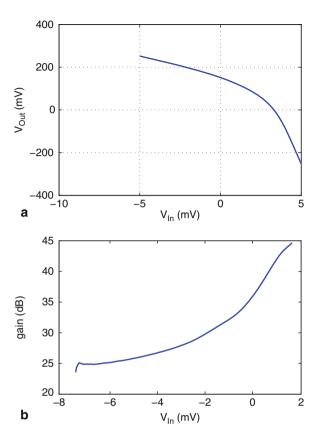

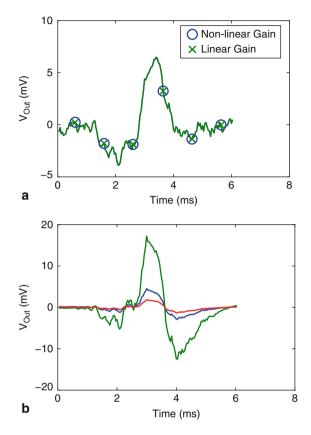

Figure 3.7a shows a  $150\,\mu V$  spike amplified by the polynomial fit and imposed on the same spike amplified with perfect linearity. The two traces are nearly indistinguishable, suggesting that the effect of the amplifier's non-linearity is negligible for signals with the amplitude of a typical neural spike.

However, extracellular neural probes will also detect local field potentials (LFPs), which occur in the frequency band below 1 kHz and can have amplitudes as high as 5 mV [4]. Additionally, 50/60 Hz interference from wall power may corrupt the signals. If LFPs are in the amplifier's passband, they will shift any action potentials to a different point in the amplifier's input/output curve, effectively causing the relevant part of the input signal (the action potentials) to experience time-varying

Fig. 3.7 a A 150 μV spike amplified with the nonlinear characteristic of the open-loop amplifier as well as with perfectly linear gain, showing that the amplifier nonlinearity is not significant for signals with the amplitude of typical neural spikes. b Three spikes amplified by the amplifier's nonlinearity after being superimposed on a much larger signal, representing interference due to LFPs or wall power

gain. In Fig. 3.7b, three spikes are added to a 5 mV sinusoid before being applied to the amplifier nonlinearity, to simulate the effect of a small spike being recorded in the presence of a large LFP interferer. In this case, the amplifier's nonlinearity does introduce significant errors, essentially subjecting the desired action potential signal to a time-varying gain.

A number of options are available to address this issue. A filter could be placed before the amplifier or built into the amplifier. For example, if the pseudo-resistors, with resistance of nearly  $1\,\mathrm{T}\Omega$ , were replaced with  $16\,\mathrm{M}\Omega$  resistances, the high-pass corner frequency would move to about  $1\,\mathrm{kHz}$ . Local field potentials at  $100\,\mathrm{Hz}$  would then be attenuated by  $20\,\mathrm{dB}$ . If any large interferers are sufficiently attenuated by a filter, then we return to the situation shown in Fig. 3.7a, where the non-linearity does not have a noticeable effect. Another option is to compensate for the error in a later processing stage. The inverse non-linearity could be applied in the digital domain to recover the original signal, or spike detection and sorting algorithms which do not rely on amplitude information could be used. Finally, one could modify the amplifier to improve linearity. Chapter 4 describes an amplifier built with this strategy in mind.

References 23

# 3.4 Conclusions

This chapter describes two novel amplifiers which achieve excellent power efficiency. The open-loop amplifier exhibits the lowest NEF published to date, at the expense of linearity, supply rejection, and gain accuracy. The low power and area provided by this design would allow the realization of a 256-channel amplifier array with an area of  $8.4 \, \text{mm}^2$  and a power dissipation of  $206 \, \mu \text{W}$ . While the noise efficiency of the closed-loop amplifier falls short of that achieved by the open-loop amplifier, it is still superior to that reported for any other closed-loop amplifier, demonstrating that the complementary-input topology used in both amplifiers is a powerful technique to improve noise-power efficiency.

The choice between a single-ended open-loop amplifier and a differential closed-loop amplifier depends on system-level considerations. The primary drawbacks of the open-loop LNA are gain inaccuracy, nonlinearity, and poor supply rejection. Because absolute amplitude is not typically a salient feature of neural recordings (due partially to other sources of amplitude uncertainty), the decision can be made based on linearity, supply rejection and power consumption considerations.

The supply rejection burden can be removed from the amplifier by using a regulator to provide a low-noise supply to all of the amplifiers in a system. In a multi-electrode system with many channels, the additional power consumption of the regulator is amortized across all of the channels. With only a small number of channels, the additional power per channel for the regulator may be greater than the power saved by using a single-ended topology. Thus, the single-ended topology becomes more attractive for higher channel-count recording systems.

It should also be noted that the three strategies employed in this amplifier—complementary input drive, open-loop topology, and single-ended input stage—are essentially unrelated. Any amplifier can be operated in an open-loop configuration. Conversely, the single-ended amplifier could be combined with an additional gain stage and a capacitive feedback network to improve linearity. The complementary input drive can also be applied to a closed-loop or differential design, as will be demonstrated in Chap. 4.

### References

- [1] Allen P, Holberg D (2002) CMOS analog circuit design. Oxford University Press, New York

- [2] Camacho-Galeano E, Galup-Montoro C, Schneider M (2005) A 2-nW 1.1-V self-biased current reference in CMOS technology. IEEE Trans Circ Syst II: Express Briefs [see also IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing] 52(2): 61–65

- [3] Denison T, Consoer K, Kelly A, Hachenburg A, Santa W (2007) A 2.2 μW 94 nV/pHz chopper-stabilized instrumentation amplifier for EEG detection in chronic implants. In: international solid-state circuits conference, Digest of Technical Papers, San Francisco

- [4] Harrison R, Charles C (2003) A low-power low-noise CMOS amplifier for neural recording applications. IEEE J Solid-State Circuits 38(6):958–965

- [5] Harrison R, Watkins P, Kier R, Lovejoy R, Black D, Greger B, Solzbacher F (2007) A low-power integrated circuit for a wireless 100-electrode neural recording system. IEEE J Solid-State Circuits 42(1):123–133

- [6] Holleman J, Otis B (2007) A sub-microwatt low-noise amplifier for neural recording. In: 29th annual international conference of the IEEE Engineering in Medicine and Biology Society (EMBS 2007), Lyon, pp 3930–3933

- [7] Steyaert M, Sansen W (1987) A micropower low-noise monolithic instrumentation amplifier for medical purposes. J Solid-State Circuits 22(6):1163–1168

- [8] Wattanapanitch W, Fee M, Sarpeshkar R (2007) An energy-efficient micropower neural recording amplifier. IEEE Trans Biomed Circuits Syst 1:136–147

- [9] Wu H, Xu Y (2006) A 1 V 2.3 μW biomedical signal acquisition IC. In: Proceedings of the 2006 IEEE international conference on solid-state circuits, Digest of Technical Papers, San Francisco, CA, pp 119–128

# Chapter 4 Closed-Loop Neural Recording Amplifier Design Techniques

As previously described, in order to accommodate weak neural signals, we need sufficient amplification and signal conditioning at the front-end of a neural-recording system. Specifically, the requirements on the front-end amplifier can be summarized as below:

- Input-referred noise voltage  $< 10 \,\mu\text{V}$

- Midband gain ≅40 dB

- Input impedance  $\geq$  a few M $\Omega$ s at 1 kHz

- Pass-band compatible with the desired signals (see Table 2.1).

- AC-coupled input in order to block DC offsets.

- Small silicon area and no off-chip components.

- CMRR, PSRR >60 dB

- Power dissipation ≪100 µW/channel

In this chapter, the design methodologies of two new closed-loop amplifier architectures are presented. The implementation details of these topologies are then compared and contrasted. Afterward, we will discuss the design of a variable-gain amplifier with six variable gain settings from 0 to 40 dB, making the amplifiers suitable to process a variety of signals.

# 4.1 Design of a Closed-Loop Telescopic Amplifier

# 4.1.1 Closed-Loop Architecture

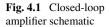

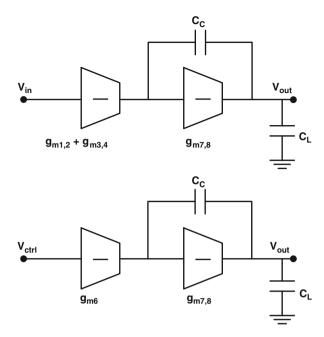

To increase the output signal swing with low supply voltages (as low as 1V), we chose a fully-differential topology. We also chose a closed-loop topology in order to improve the CMRR, PSRR, linearity, and gain precision. Figure 4.1 shows the closed-loop architecture.

The input signals are AC-coupled into the amplifier to reject large DC offsets from the electrode-tissue interface, preventing saturation at the output of the amplifier. The sizing of the input capacitors,  $C_s$ , also need to be carefully chosen. They must be

made small enough (the input impedance,  $\frac{1}{j\omega C}$  is large enough) to avoid attenuation of the input signal from the electrode, but large enough to avoid attenuation from the capacitive divider it forms with the parasitic capacitance of the input devices. As shown in (4.1), the capacitive divider also increases the input-referred noise of the LNA. Let  $\overline{v_{ni,amp}}^2$  and  $\overline{v_{ni}}^2$  represent the input-referred noise of the OTA and the LNA, respectively. The mid-band gain is set by  $C_s/C_f$ .

$$\overline{v_{ni,amp}^{2}} = \left(\frac{C_{s} + C_{f} + C_{in}}{C_{s}}\right)^{2} \overline{v_{ni}^{2}}$$

(4.1)

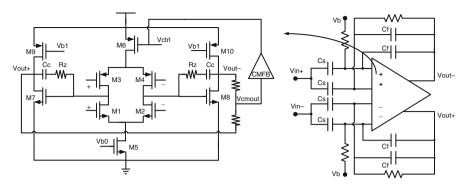

# 4.1.2 Analysis of Pseudo-Resistors

Because signals are AC-coupled into the amplifier, the gates of the input transistors need to be properly biased to ensure proper operation. At the same time, in order to pass EEG and LFP signals in the sub-Hertz band, we need to form a sub-Hertz high-pass frequency corner. To address both design concerns, we would need to use large resistors that would normally take up significant chip area. Here, we chose to use pseudo-resistors [2] to bias the gates to avoid large resistors. Pseudo-resistors (Fig. 4.2) are MOS-bipolar devices which have equivalent resistance in the order of

Fig. 4.2 Two configurations of pseudo-resistors

$100\,\mathrm{G}\Omega$  to  $1\,\mathrm{T}\Omega$  if the voltage drop across them is small enough (<0.2 V, according to [2]). When  $V_{GS}>0$ , the parasitic source-well-drain p-n-p junction acts as a diodeconnected BJT; when When  $V_{GS}<0$ , each device functions as a diode-connected pMOS transistor.

We cascaded two long-channel (50 µm), minimum-width pMOS transistors to increase the equivalent resistance of the pseudo-resistors and to ensure sufficiently large resistance with reasonable voltage drop across them. The large incremental resistance also takes into account the drop in resistance in the presence of large input amplitudes. The low-frequency cutoff  $\omega_L$  of the amplifier is then  $\frac{1}{2r_{inc}Cf}$ , with  $r_{inc}$  being the incremental resistance of the pseudo-resistor. However, this frequency corner is difficult to know a-priori as the incremental resistance at the parasitic source-well-drain p-n-p junction is poorly modeled. This sub-Hertz corner creates a large time constant, resulting in slow start-up and settling time of the amplifier. There are other possible replacement for pseudo-resistors. For instance, some bioamplifier designs have used transistors biased in the subthreshold region to approximate large-valued resistors [1]. This technique functions similarly while requiring additional biasing circuitry.

# 4.1.3 Telescopic OTA Design Overview

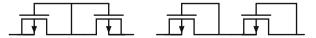

In order to lower the power consumption and ease integration with complex digital subsystems, the amplifier, shown in Fig. 4.3, should operate from a supply as low as 1 V. Although neural-recording applications can tolerate gain error, linearity requirements dictate high open-loop gain. A single-stage amplifier topology does not provide sufficient gain or output swing with a 1 V supply. Therefore, we chose to employ a two-stage fully-differential design to simultaneously satisfy the gain

Fig. 4.3 Telescopic OTA schematic

and swing requirements. Common-mode feedback is included to stabilize the output common-mode voltage.

The design of the first stage is crucial in achieving an optimal power-noise trade-off while meeting gain specifications. Although the design in [2] optimized the power-noise tradeoff nearly to the theoretical limit of its particular OTA topology, the topology itself is not optimized for power because a large portion (50%) of current is consumed in the biasing branch. Although [5] optimized the power-noise tradeoff for a folded-cascode amplifier, there is no clear advantage to using a folded-cascode topology in the first-stage. Although the folded-cascode topology increases the input common-mode range, this is typically not a concern since the low-level input signal is AC-coupled into the amplifier anyway. Furthermore, the folded-cascode topology generally consumes more current and has worse noise performance because of the extra current branches. Therefore, a telescopic-cascode topology is used in the first stage to achieve sufficient gain while conserving current. To accommodate the low supply voltage, we have omitted the pFET cascode transistors, but retained the nFET cascodes to provide input-output isolation and sufficient first-stage gain.

The second-stage uses a standard common-source topology to implement a gain stage. The tail current source in the second stage is eliminated to ensure sufficient voltage swing under low supply voltages.

# 4.1.4 Design Optimization

Transistor sizing is critical for simultaneously achieving low noise and low power. We chose  $6 \mu A$  for the bias current  $I_{bias}$ , giving  $M_1 - M_8 3 \mu A$ .

Table 4.1 shows the parameters and operating conditions of each transistor in the OTA. Neglecting the noise contribution of the second stage, the input-referred thermal noise power can be simplified to

$$V_{ni,th}^2 = \left(\frac{16kT}{3g_{m1,2}} \left(1 + \frac{g_{m5,6}}{g_{m1,2}}\right)\right) \Delta f \tag{4.2}$$

From this equation, we want to have  $g_{m5,6} \ll g_{m1,2}$  to minimize the thermal noise contribution. This can be accomplished by sizing  $(W/L)_{5,6} \ll (W/L)_{1,2}$ . Thus, the NMOS input pair  $M_{1,2}$  is pushed to weak inversion, where the  $g_m/I_D$  ratio is maximized. By sizing the input pair  $M_{1,2}$  to 624/2  $\mu$ m/ $\mu$ m, the input transistors operate in the deep subthreshold region, and the  $g_m/I_D$  ratio is maximized. The large

|                      | W/L (µm) | $I_d$ ( $\mu$ A) | Inv. Coeff | $g_m/I_d(V^{-1})$ | $ V_{GS} - Vt $ (mV) |  |

|----------------------|----------|------------------|------------|-------------------|----------------------|--|

| $\overline{M_{1,2}}$ | 616/2    | 3                | 0.023      | 27.56             | 154                  |  |

| $M_{3,4}$            | 12/5     | 3                | 0.27       | 22                | 101                  |  |

| $M_{5,6}$            | 12.2/13  | 3                | 11.3       | 6.9               | 257.7                |  |

| $M_0$                | 109.8/8  | 6                | 0.54       | 19.4              | 386                  |  |

| $M_{7.8}$            | 12/4     | 2.2              | 0.96       | 16.82             | 32                   |  |

| $M_{9,10}$           | 8.6/3    | 2.2              | 1.92       | 13.64             | 106                  |  |

| M 9,10               | 0.0/3    | 2.2              | 1.92       | 13.04             | 100                  |  |

Table 4.1 Device parameters of telescopic-cascode closed-loop biopotential amplifier

gate area also reduces 1/f noise, as discussed in the next paragraph. At the same time, by sizing PMOS load  $M_{5,6}$  to 12.2/26 µm/µm, the transistors are pushed to strong inversion, where the  $g_m/I_D$  ratio is minimized. The sizing of cascode transistors  $M_2$  is not crucial because the noise of the cascode transistors negligibly contributes to the output, especially at low frequencies [4]. Therefore, we have sized it to be in moderate inversion. However, the total capacitance  $C_x$  at the source of the cascode transistors gives rise to the contribution of the noise of the cascode transistors at high frequency (specifically, higher than  $g_{m2}/2\pi C_x$ ). In addition to the increase in the noise, the gain is also decreased as  $C_x$  shunts the signal current produced by input pair  $M_{1,2}$  to ground. However, since the frequency  $g_{m2}/2\pi C_x$  is farther out than the bandwidth of the amplifier, we could ignore these secondary high frequency effect on the noise and gain of the first-stage OTA.

The input devices should be large to reduce their flicker noise. However, large input devices increase the input parasitic capacitance  $C_{in}$ , which attenuates the signal at the OTA input via the capacitive divider (4.1). An optimization balancing these tradeoffs led to a sizing of 616/2  $\mu$ m/ $\mu$ m for the input devices.

# 4.1.5 Stability and Common-Mode Feedback

Two-stage amplifier design necessitates a compensation capacitor to split the poles at the output of the first and second stage. In order to eliminate the feed-forward zero, we added a nulling resistor with a value of approximately  $1/g_m$  of the input transistor of the second stage. For this high gain fully-differential amplifier, an internal common-mode feedback (CMFB) path must be added to establish a common mode output voltage over the frequencies of interest. We chose to sense the common-mode output voltage using two large resistors and generate a continuous-time CMFB control signal back into the differential mode path.

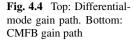

The signal propagation of the common-mode feedback path consists of two parts: from the average output  $V_{cmout}$  to the feedback control  $V_{ctrl}$ , and from  $V_{ctrl}$  to the amplifier output. The first part of the CMFB path has a wide bandwidth and small DC gain ( $\simeq$  1); the second part determines the CMFB frequency response as illustrated in Fig. 4.4. Let  $g_{m1-4,6-8}$  denote the transconductance of the corresponding transistors,  $C_c$  and  $C_L$  denote the compensation and load capacitors,  $g_{o1}$  and  $g_{o2}$  denote the total output conductances of stage 1 and 2. Then

$$A_{cmfb} = \frac{V_{out,CM}}{V_{ctrl}} = \frac{-sg_{m5,6}C_c + g_{m5,6}g_{m7,8}}{s^2C_cC_L + sC_cg_{m7,8} + g_{o1}g_{o2}}$$

(4.3)

$$A_{dm} = \frac{V_{out,DM}}{V_{in,dm}} = \frac{-s(g_{m1,2})C_c + (g_{m1,2})g_{m7,8}}{s^2C_cC_L + sC_cg_{m7,8} + g_{o1}g_{o2}}$$

(4.4)

Both the differential and common-mode gains share the same compensation capacitor  $C_c$  and  $g_{m7,8}$  stage. The similarity of the topologies leads to a stable CMFB path if the differential-mode path is unity-gain stable. The CMFB gain and bandwidth must be larger than those of the common-mode path. Although the requirement on

CMFB gain and bandwidth is relaxed as the common-mode path has small gain and bandwidth, a high CMFB gain is preferred to achieve more accurate common-mode voltage, and a high CMFB bandwidth is preferred to improve the CMRR at high frequencies. This CMFB topology achieves both high gain and bandwidth, while saving power by sharing one CMFB circuit between both the first and second stages.

# 4.2 Design of a Closed-Loop Complementary-Input Amplifier

In the last section, we discussed in detail the design of a low-noise low-power amplifier using conventional telescopic-cascode technique. In this section, we will introduce a technique that eases the trade-off between power consumption and noise performance by employing a complementary-input strategy. In the discussion below, "LNA1" will refer to the closed-loop telescopic-cascode amplifier, and "LNA2" refers to the closed-loop complementary-input amplifier.

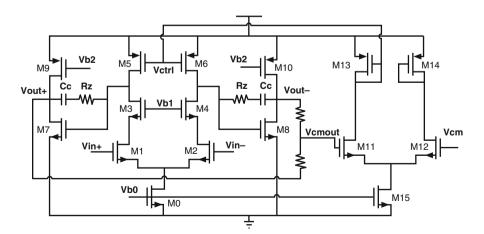

# 4.2.1 Design of an Closed-Loop Fully-Differential Complementary-Input Amplifier

AC coupling at the inputs using 20 pF capacitors and high-resistance MOS-bipolar pseudoresistors prevent offset amplification, similar as the previous section. Thick-oxide MOS transistors with large gate areas are used at the input to reduce gate leakage while minimizing 1/f noise.

Fig. 4.5 Complementary amplifier schematic [3]

As shown in Fig. 4.5, input capacitors  $C_s$  separate the signal from the bias path, which allows the input to simultaneously drive the n- and pFET transistors of the first stage. Similar to its open-loop counterpart, the input-referred noise voltage is reduced by a factor of  $\sqrt{2}$ . The input-referred thermal noise power is twice that of the single-ended design because differential branches double the output noise. If  $g_{m1} = g_{m3}$ , it can be expressed as:

$$V_{ni,th}^2 = \left(\frac{16kT}{3g_{m1} \cdot 2}\right) \Delta f \tag{4.5}$$

Similarly, (4.2) shows the input-referred noise for LNA1. If  $g_{m5} = 0$ , than (4.2) reduces to

$$V_{ni,th}^2 = \left(\frac{16kT}{3g_{m1}}\right)\Delta f\tag{4.6}$$

A comparison between (4.5) and (4.6) reveals that the input-referred noise voltage of LNA2 is approximately  $1/\sqrt{2}$  that of LNA1.

Determining the appropriate level of inversion is crucial in minimizing noise and power. Similar to LNA1,  $6 \mu A$  is chosen for the bias current in  $M_0$ , giving  $M_1 - M_8$  drain currents of  $3 \mu A$ . Table 4.2 shows the parameters and operating conditions of each transistor in the OTA. Common-centroid techniques are used for the input transistors  $M_{1-4}$ . By sizing both input pairs to  $552/2 \mu m/\mu m$ , the input transistors

| 14010 112            | Device parameters of comprehending input closed loop dispotential amplifiers |                   |            |                    |                              |

|----------------------|------------------------------------------------------------------------------|-------------------|------------|--------------------|------------------------------|

|                      | W/L (µm)                                                                     | $I_d$ ( $\mu A$ ) | Inv. Coeff | $g_m/I_d (V^{-1})$ | $ V_{GS} - Vt  \text{ (mV)}$ |

| $\overline{M_{1,2}}$ | 552/2                                                                        | 3                 | 0.022      | 27.53              | 152                          |

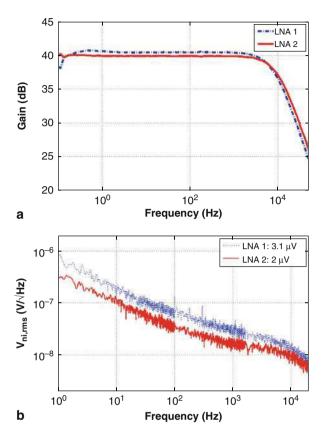

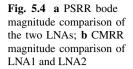

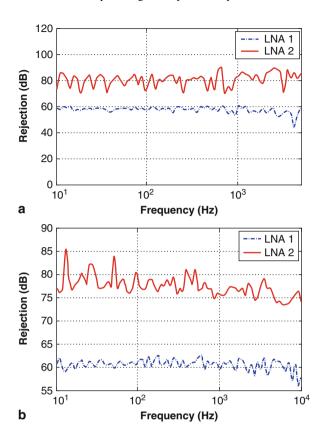

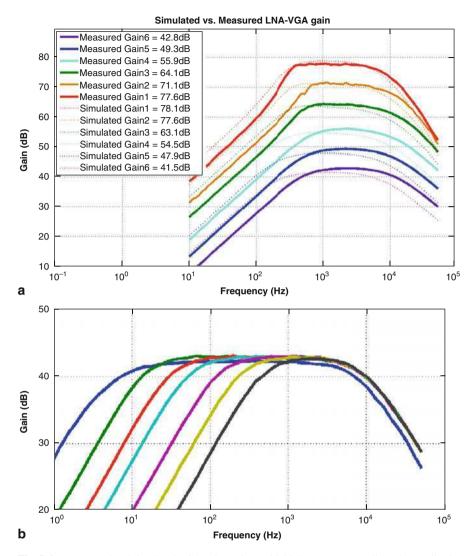

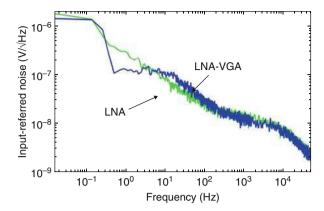

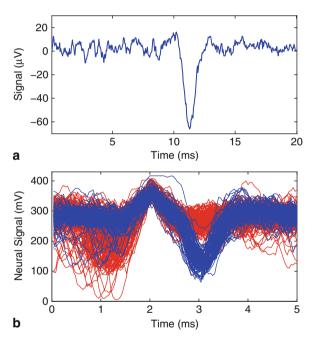

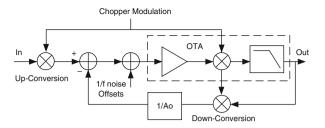

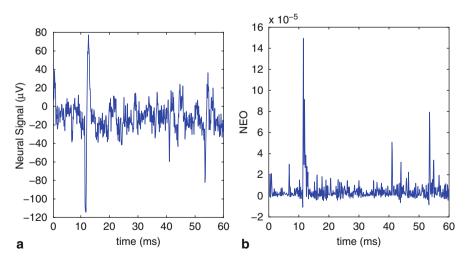

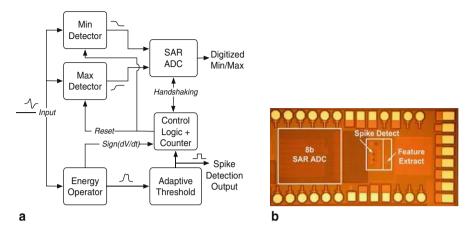

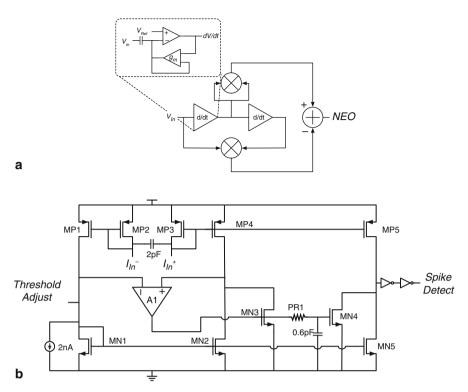

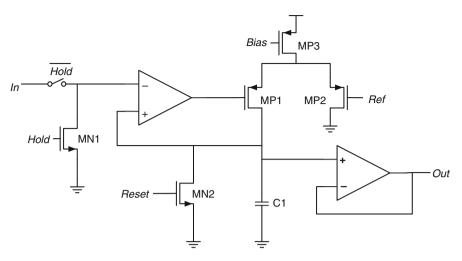

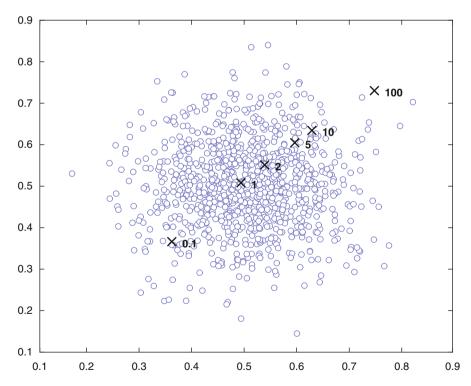

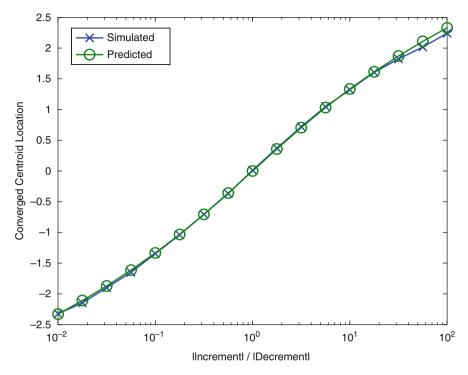

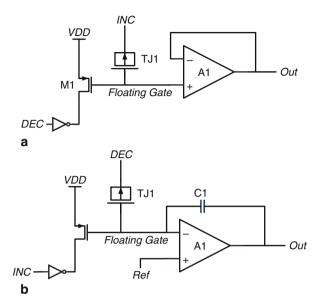

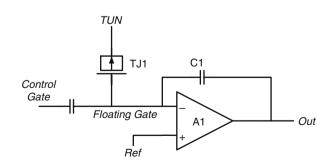

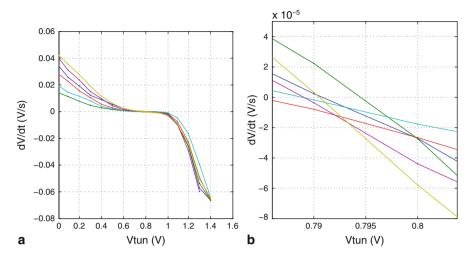

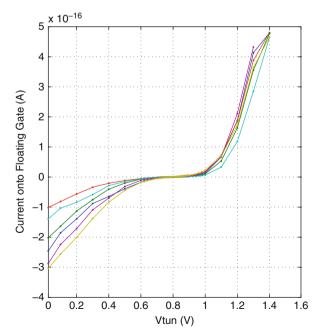

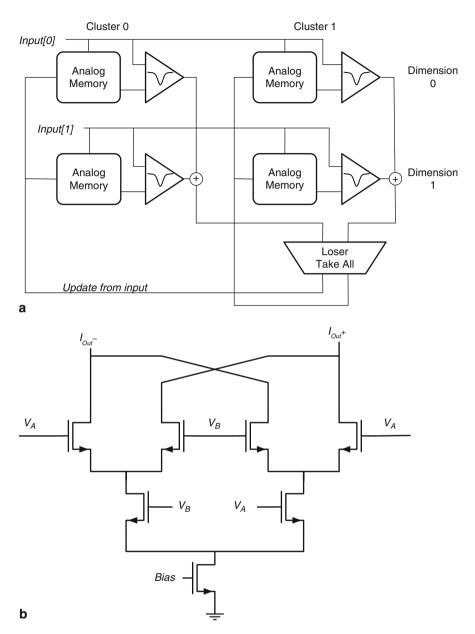

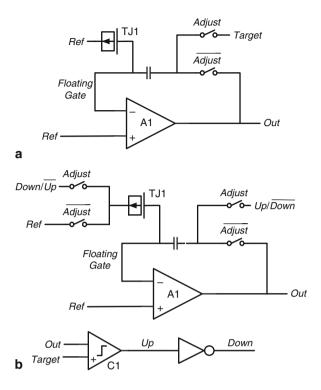

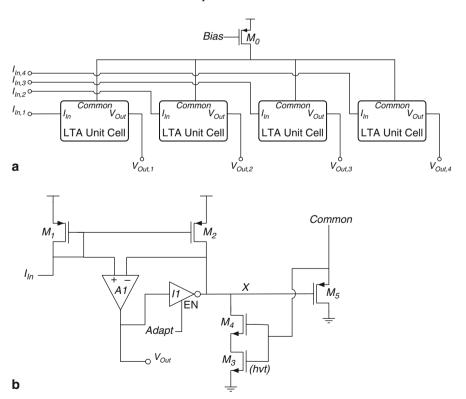

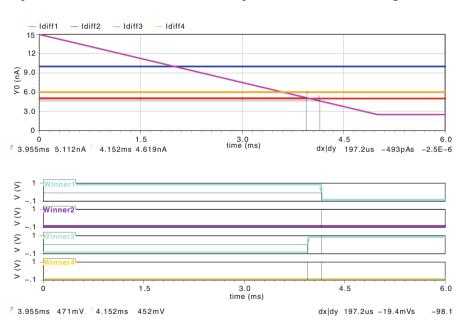

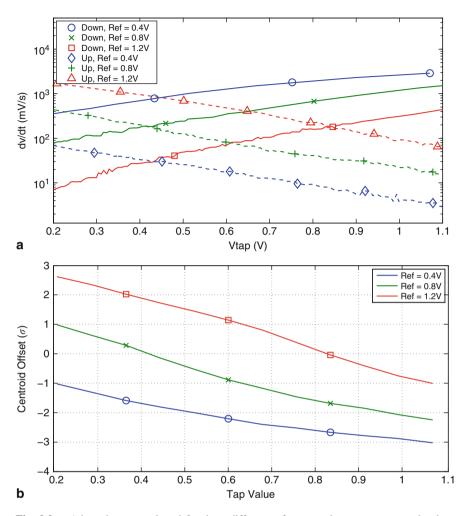

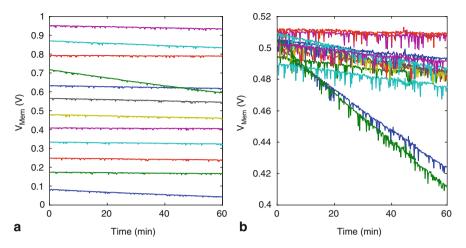

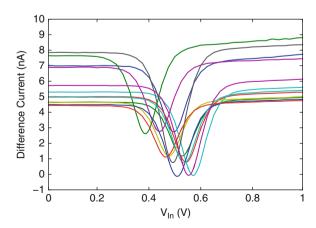

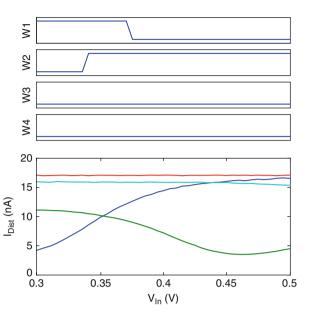

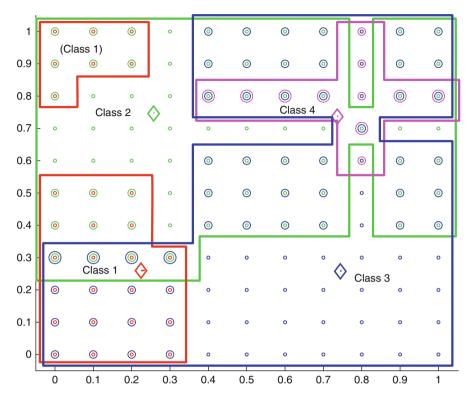

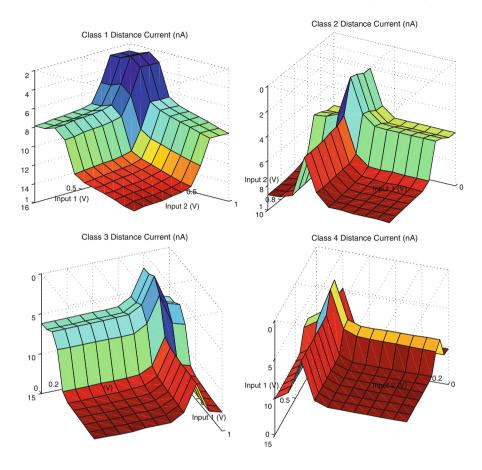

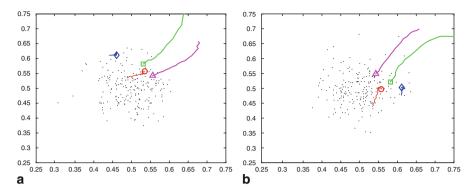

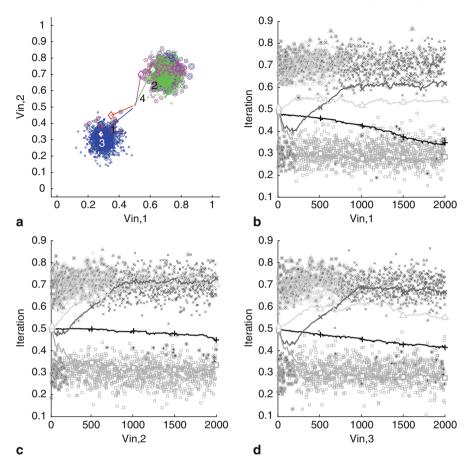

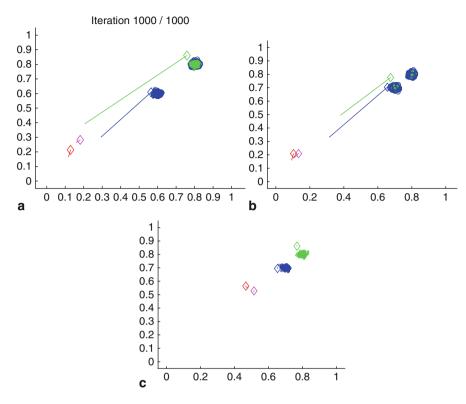

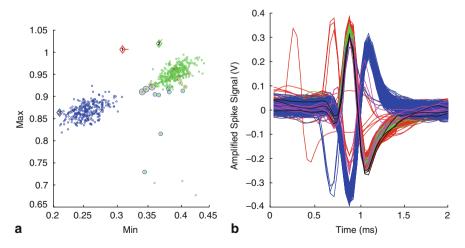

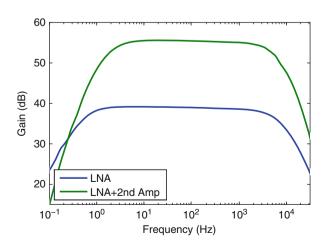

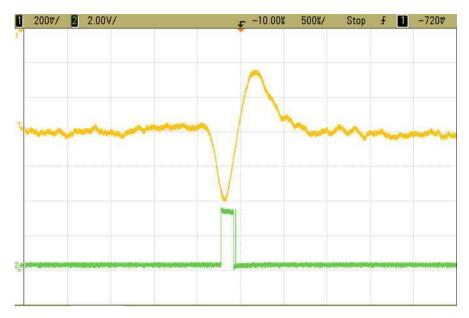

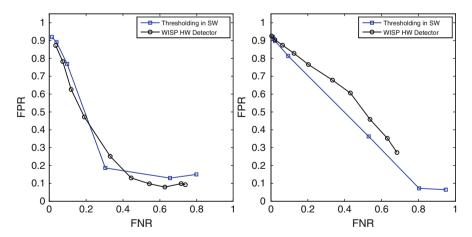

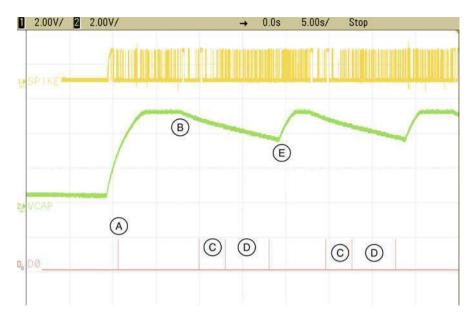

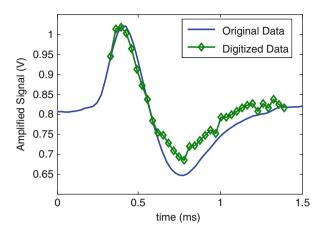

| $M_{3,4}$            | 552/2                                                                        | 3                 | 0.12       | 24.23              | 106                          |