Joachim N. Burghartz *Editor*

# Ultra-thin Chip Technology and Applications

Ultra-thin Chip Technology and Applications

Joachim N. Burghartz Editor

## Ultra-thin Chip Technology and Applications

*Editor* Joachim N. Burghartz Institut für Mikroelektronik Stuttgart (IMS CHIPS) Allmandring 30a 70569 Stuttgart Germany burghartz@ims-chips.de

ISBN 978-1-4419-7275-0 e-ISBN 978-1-4419-7276-7 DOI 10.1007/978-1-4419-7276-7 Springer New York Dordrecht Heidelberg London

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

To Ulrich Gösele 25.1.1949 – 8.11.2009

## Preface

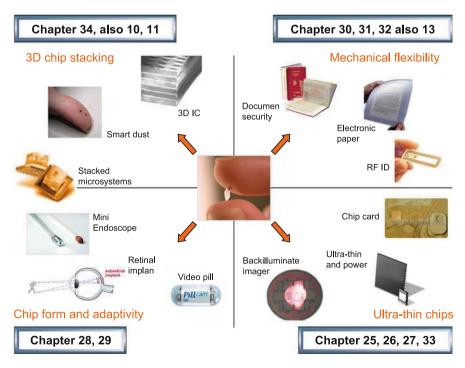

After more than 40 years of semiconductor technology advancement we have accepted the technical framework that has enabled us to bring the minimum feature size down to 45 nm, an incredible 1,000-fold reduction from the integrated circuits of the early 1970s. Going further, we may face limits in device downscaling due to the physical silicon crystalline structure. Therefore, besides the coordinated miniaturization (More Moore), according to Gordon Moore's prediction from 1965, the International Semiconductor Roadmap for Semiconductors (ITRS) now also considers applications of silicon technology that depend less on pushing down the minimum feature size (More than Moore).

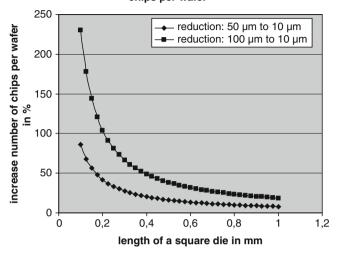

However, the basic concept of silicon wafer manufacturing applies to both More Moore and More than Moore applications and essentially is not put into question. But, to a novice to silicon technology, several questions may come up that would not likely be raised by the expert: Why do we accept considerable material loss by cutting rectangular chips from a circular-shaped silicon wafer? Or, why do we work with very thick silicon wafer substrates if we only need the upper 1% layer to integrate the circuit components? In view of the possibility that economics may become a show stopper for semiconductor manufacturing even before the physical or technological limits are in sight, these are indeed good questions. And, such questions may stimulate ideas on new applications of silicon technology.

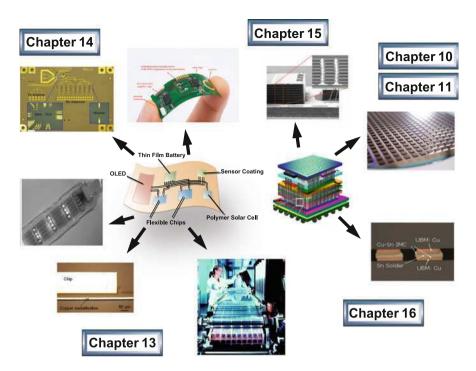

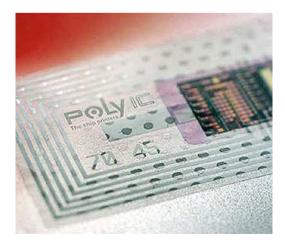

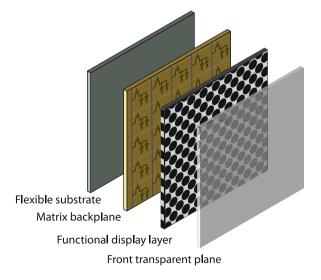

As silicon is not only the best suited semiconductor for complex circuit and system integration but also a material of excellent mechanical properties, ultra-thin chip technology and applications are to emerge as a new paradigm of silicon technology. Extremely thin and thus flexible silicon chips are expected to greatly enhance the emerging thin-film and organic semiconductor technologies by combining the well-known high performance of silicon chip technology with the large area and system-in-foil (SiF) applications. Moreover, very thin chips with through-silicon-via (TSV) interconnects will provide a means of overcoming the interconnect bottleneck of planar chip integration by allowing a migration to three-dimensional integrated circuits (3D IC). A small chip thickness also leads to a reduced thermal resistance and thus helps the management of the power density issue in modern high-performance silicon chips. Finally, there are

likely numerous new applications in microsystems that will emerge with the availability of ultra-thin chips.

However, ultra-thin chip technology features not only a new paradigm due to the thus emerging applications, but also because the fabrication of thin silicon chips will require certain adjustments and innovations in silicon process technology and circuit integration: Ultra-thin silicon chips need to have very high edge and surface qualities in order to retain the excellent inherent mechanical properties of silicon. Processing of thin wafers requires suitable handling techniques. Singulation of chips from thin wafers likely must be arranged by methods different from the conventional dicing process. The effect of stressors in increasing carrier mobility in the channel region of CMOS transistors will likely be different for extremely thin compared to thick silicon substrates. Also, ultra-thin chips will have physical properties that are different from those found on thick bulk substrates. Transistors on thin chips under variable bending stress will suffer from the piezoresistive effect shifting their operating point, which is thus an additional aspect to be considered in circuit design. The optical spectrum absorbed in a thin silicon film will be narrower compared to that absorbed on thick silicon. Also, the optical response of photo detectors on thin silicon might be affected by the properties of the back surface of the thin chip. The thermal boundary conditions of an integrated circuit on a thin silicon chip will to a large extent depend on the assembly of that chip into a rigid package or onto a foil substrate. Finally, for economic reasons, the techniques used to fabricate an ultra-thin chip will have to be optimized in terms of minimizing the density of defects to a tolerable level.

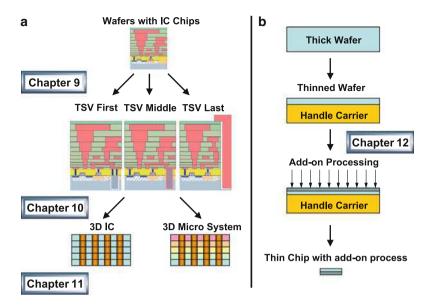

This book presents the general scope and the current status of the emerging ultrathin chip technologies and applications. It was very fortunate that 75 leading international experts from academia, the semiconductor industry and equipment manufacturers could be brought together to contribute their expertise and vision to this new topic, and to do so in 34 chapters. Part I of the book provides an introduction, explaining the reasons why silicon technology has been based on thick wafers and chips for 40 years (Chap. 1) and why recently thin silicon chips became an issue considered by the ITRS (Chap. 2). Part II describes subtractive and additive thin chip fabrication based on bulk wafer thinning (Chaps. 3 through 5), wafer thinning that exploits etch stop techniques (Chaps. 6 and 7), and a new additive concept based on sintered porous silicon and epitaxial layer growth (Chap. 8). Part III relates to add-on process steps and modules that are applied to thin wafers in order to prepare them for specific applications, such as 3D IC and SiF (Chaps. 9 through 12). The assembly and embedding of ultra-thin chips is addressed in Part IV with SiF-specific chip embedding in foil (Chaps. 13 and 14) and general purpose chip-to-wafer alignment and micro-bump assembly (Chaps. 15 and 16). Part V is devoted to characterization and modelling of mechanical (Chaps. 17 and 18), electromechanical (Chaps. 19 and 20), thermal (Chap. 23) and optical (Chap. 24) properties. Also in this part, compact modelling of CMOS (Chap. 21) and bipolar (Chap. 22) are discussed, with a focus on flexible chips. Finally, in Part VI of the book, the possible improvements of known silicon applications and the emerging applications with thin chip technology are mentioned. Those include

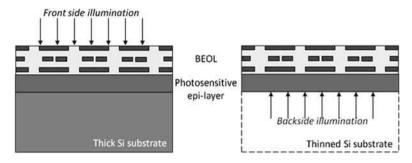

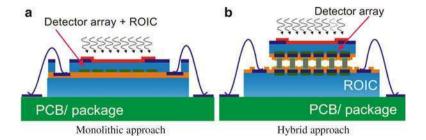

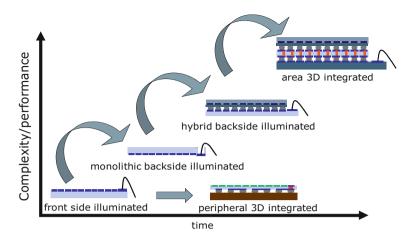

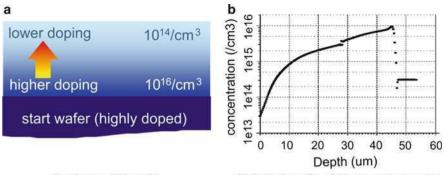

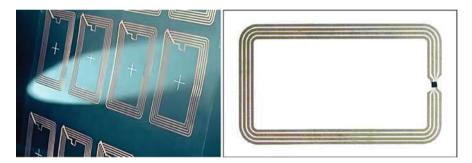

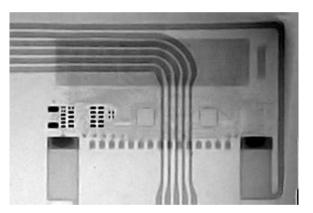

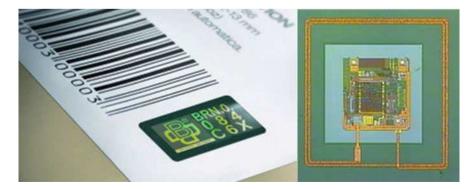

power applications (Chap. 25), back-illuminated imagers (Chap. 26), thin solar cells (Chap. 27), biomedical applications (Chap. 28), sensor applications (Chap. 29), RF-ID tags (Chap. 30), security chips (Chap. 31), drive chips for flexible displays (Chap. 32), microwave and millimeter wave (Chap. 33) and specific 3D IC (Chap. 34) applications.

I hope that this book will serve as a useful resource to researchers and engineers in industry as well as to scientists in academia in their effort to turn the new paradigm of ultra-thin chip technology and application into major new applications of silicon technology and to overcome bottlenecks in conventional silicon technology development.

I am grateful to all authors and co-authors who have contributed their time and energy to make this book a reality. In their name I also thank those people within their organisations who provided assistance to them. The compilation and editing of this book was, with great enthusiasm, supported by Astrid Hamala and Joachim Deh from IMS CHIPS. My own contribution would not have been possible without the patience and encouragement of my wife Susanne and my children Pia, Julia and Tamara, who found their husband and dad trapped behind the PC late at night for several weeks.

Stuttgart November 1, 2010 Joachim N. Burghartz

## Contents

| Pa | rt I From Thick Wafers to Ultra-Thin Silicon Chips                                                                                                    |    |  |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

| 1  | Why Are Silicon Wafers as Thick as They Are?                                                                                                          |    |  |  |  |  |  |

| 2  | Thin Chips on the ITRS Roadmap<br>Joachim N. Burghartz                                                                                                | 13 |  |  |  |  |  |

| Pa | rt II Thin Chip Fabrication Technologies                                                                                                              |    |  |  |  |  |  |

| 3  | Thin Wafer Manufacturing and Handling<br>Using Low Cost Carriers<br>Florian Schmitt and Michael Zernack                                               | 21 |  |  |  |  |  |

| 4  | Ultra-thin Wafer Fabrication Through Dicing-by-Thinning<br>Christof Landesberger, Sabine Scherbaum, and Karlheinz Bock                                |    |  |  |  |  |  |

| 5  | Thin Wafer Handling and Processing without<br>Carrier Substrates<br>Yoshikazu Kobayashi, Martin Plankensteiner, and Midoriko Honda                    | 45 |  |  |  |  |  |

| 6  | <b>5 Epitaxial Growth and Selective Etching Techniques</b><br>Evangelos A. Angelopoulos and Alexander Kaiser                                          |    |  |  |  |  |  |

| 7  | 7 Silicon-on-Insulator (SOI) Wafer-Based Thin-Chip Fabrication<br>Joachim N. Burghartz                                                                |    |  |  |  |  |  |

| 8  | Fabrication of Ultra-thin Chips Using Silicon Waferswith Buried CavitiesMartin Zimmermann, Joachim N. Burghartz, Wolfgang Appel,and Christine Harendt | 69 |  |  |  |  |  |

#### Part III Add-on Processing

| 9   | <b>Through-Silicon Vias Using Bosch DRIE Process Technology</b><br>Franz Laermer and Andrea Urban                                          | 81  |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| 10  | Through-Silicon via Technology for 3D IC<br>Eric Beyne                                                                                     | 93  |  |  |  |  |

| 11  | <b>3D-IC Technology Using Ultra-Thin Chips</b><br>Mitsumasa Koyanagi                                                                       |     |  |  |  |  |

| 12  | Substrate Handling Techniques for Thin Wafer Processing<br>Christof Landesberger, Sabine Scherbaum, and Karlheinz Bock                     | 125 |  |  |  |  |

| Par | t IV Assembly and Embedding of Ultra-Thin Chips                                                                                            |     |  |  |  |  |

| 13  | System-in-Foil Technology<br>Andreas Dietzel, Jeroen van den Brand, Jan Vanfleteren,<br>Wim Christiaens, Erwin Bosman, and Johan De Baets  | 141 |  |  |  |  |

| 14  | Chip Embedding in Laminates<br>Andreas Kugler, Metin Koyuncu, André Zimmermann,<br>and Jan Kostelnik                                       | 159 |  |  |  |  |

| 15  | Handling of Thin Dies with Emphasis<br>on Chip-to-Wafer Bonding<br>Fabian Schnegg, Hannes Kostner, Gernot Bock,<br>and Stefan Engensteiner | 167 |  |  |  |  |

| 16  | Micro Bump Assembly<br>Paresh Limaye and Wenqi Zhang                                                                                       | 185 |  |  |  |  |

| Par | t V Characterization and Modelling                                                                                                         |     |  |  |  |  |

| 17  | Mechanical Characterisation and Modelling of Thin Chips<br>Stephan Schoenfelder, Joerg Bagdahn, and Mattias Petzold                        | 195 |  |  |  |  |

| 18  | <b>Structure Impaired Mechanical Stability of Ultra-thin Chips</b><br>Tu Hoang, Stefan Endler, and Christine Harendt                       | 219 |  |  |  |  |

| 19  | Piezoresistive Effect in MOSFETS<br>Nicoleta Wacker and Harald Richter                                                                     | 233 |  |  |  |  |

| Contents |

|----------|

|----------|

| 20  | Electrical Device Characterisation on Ultra-thin Chips<br>Mahadi-Ul Hassan, Horst Rempp, Harald Richter,<br>and Nicoleta Wacker  | 245 |

|-----|----------------------------------------------------------------------------------------------------------------------------------|-----|

| 21  | MOS Compact Modelling for Flexible Electronics<br>Slobodan Mijalković                                                            | 259 |

| 22  | <b>Piezojunction Effect: Stress Influence</b><br><b>on Bipolar Transistors</b><br>J. Fredrik Creemer and Patrick J. French       | 271 |

| 23  | Thermal Effects in Thin Silicon Dies:<br>Simulation and Modelling<br>Niccolò Rinaldi, Salvatore Russo, and Vincenzo d'Alessandro | 287 |

| 24  | <b>Optical Characterisation of Thin Silicon</b><br>Michael Reuter and Sebastian J. Eisele                                        | 309 |

| Par | t VI Applications                                                                                                                |     |

| 25  | Thin Chips for Power Applications<br>Kurt Aigner, Oliver Häberlen, Herbert Hopfgartner,<br>and Thomas Laska                      | 321 |

| 26  | Thinned Backside-Illuminated (BSI) Imagers<br>Koen De Munck, Kyriaki Minoglou, and Piet De Moor                                  | 337 |

| 27  | Thin Solar Cells<br>Michael Reuter                                                                                               | 353 |

| 28  | Bendable Electronics for Retinal Implants                                                                                        | 363 |

| 29  | Thin Chip Flow Sensors for Nonplanar Assembly                                                                                    | 377 |

| 30  | <b>RFID Transponders</b>                                                                                                         | 389 |

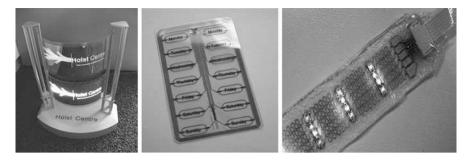

| 31  | Thin Chips for Document Security<br>Thomas Suwald                                                                                | 399 |

| 32  | Flexible Display Driver Chips                                                                                                    | 413 |

| 33  | <b>Microwave Passive Components in Thin Film Technology</b><br>Behzad Rejaei                                                                                                                                           | 425 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 34  | Through-Silicon via Technology for RF and Millimetre-Wave<br>Applications<br>Alvin Joseph, Cheun-Wen Huang, Anthony Stamper,<br>Wayne Woods, Dan Vanslette, Mete Erturk, Jim Dunn.<br>Mike McPartlin, and Mark Doherty | 445 |

| Ind | ex                                                                                                                                                                                                                     | 455 |

### **About the Editor**

**Joachim N. Burghartz** was born in Aachen, Germany, in 1956. He received the M.S. (Dipl. Ing.) from the RWTH Aachen, Germany, in 1982 and the Ph.D. (Dr.-Ing.) from the University of Stuttgart, Germany, in 1987; both the author's degrees are in electrical engineering. From 1982 to 1987 he was with the University of Stuttgart, where he developed sensors with integrated signal conversion, with a special focus on magnetic field sensors. From 1987 to 1998 he was with the IBM Thomas J. Watson Research Center in Yorktown Heights, New York. His earlier research work at IBM included device applications of selective epitaxial growth of silicon, Si and SiGe high speed

transistor design and integration processes and deep submicrometer CMOS technology. In his last four years at IBM Dr. Burghartz was engaged in the development of circuit building blocks for SiGe RF front-ends, with a special interest in the integration of high quality passive components on silicon, which also included micromachining techniques. From 1998 to 2005 Dr. Burghartz was a full professor at Delft University of Technology, where he chaired the High-Frequency Technology and Components (HiTeC) group. His research interests there continued to be focused on silicon RF technology with a broader scope, ranging from investigations on materials to the design of RF circuit building blocks. From March 2001 until September 2005 the author was Scientific Director of the Delft Institute of Microelectronics and Submicron Technology (DIMES). Since October of 2005 he has been director of the Institute for Microelectronics Stuttgart (IMS CHIPS) and full professor at the University of Stuttgart, Germany, and from March 2006, he also has headed the Institute for Nano and Microelectronic Systems at the University of Stuttgart. Research and development activities at IMS CHIPS include CMOS and add-on process technologies, ASIC design, nanostructuring and advanced lithography, as well as high dynamic range CMOS imager technology. The institute also conducts a large research program on ultra-thin chip technology and applications, which is the motivation for this new book on the subject.

Joachim Burghartz is an IEEE Fellow and a Distinguished Lecturer of the IEEE Electron Devices Society (EDS). Currently, he is the EDS Vice President of Technical Activities and an EDS AdCom Member. He has served on the technical and executive committees of numerous IEEE and IEEE-sponsored conferences, including IEDM, BCTM and ESSDERC. He recently received the 2008 Jack Raper Award for outstanding technology directions paper at the internationally leading IEEE Integrated Circuits Conference, ISSCC. In 2009 he was awarded the State Research Award of Baden–Württemberg in Germany.

Dr. Burghartz has published 280 peer-reviewed articles and holds 34 patents and patent applications.

## Contributors

Kurt Aigner Infineon Technologies Austria, Villach, Austria

#### **Evangelos A. Angelopoulos**

Institute for Microelectronics Stuttgart (IMS CHIPS), Allmandring 30a, Stuttgart 70569, Germany

#### Wolfgang Appel

Institute for Microelectronics Stuttgart (IMS CHIPS), Stuttgart, Germany

#### Ali Asif

Institut für Mikroelektronik Stuttgart (IMS CHIPS), Allmandring 30a, 70569 Stuttgart, Germany

#### Joerg Bagdahn

Fraunhofer Institute for Mechanics of Materials, Halle, Germany; Fraunhofer Center for Silicon Photovoltaics, Halle, Germany

#### **Eric Beyne**

Interuniversity Microelectronics Centre (IMEC), Kapeldreef 75, Leuven, 3001, Belgium

#### **Gernot Bock**

Datacon Technology GmbH, Innstr. 16, 6241, Radfeld, Austria

#### **Karlheinz Bock**

Fraunhofer Research Institution for Modular Solid State Technologies (EMFT), Hansastrasse 27d, 80686 Munich, Germany

#### **Erwin Bosman**

IMEC Ghent, Technologie Park 914, B-9052 Gent, Belgium

#### Jeroen van den Brand

Holst Centre, Eindhoven, KN 5605, The Netherlands

#### Joachim N. Burghartz

Institute for Microelectronics Stuttgart (IMS CHIPS), Stuttgart, Germany

Wim Christiaens IMEC Ghent, Technologie Park 914, B-9052 Gent, Belgium

#### J. Fredrik Creemer

Delft Institute of Microsystems and Nanoelectronics (DIMES), Delft University of Technology, P.O. Box 5053, 2600 GB Delft, The Netherlands

#### Vincenzo d'Alessandro

Department of Biomedical, Electronics, and Telecommunications Engineering, University of Naples Federico II, Via Claudio 21, 80125 Naples, Italy

Johan De Baets IMEC Ghent, Technologie Park 914, B-9052 Gent, Belgium

#### Piet De Moor

Interuniversity Microelectronics Centre (IMEC), Kapeldreef 75, 3001 Leuven, Belgium

#### Koen De Munck

Interuniversity Microelectronics Centre (IMEC), Kapeldreef 75, 3001 Leuven, Belgium

#### Andreas Dietzel

Holst Centre, Eindhoven, KN 5605, The Netherlands

#### Mark Doherty

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

#### Jim Dunn

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

#### Sebastian J. Eisele

Institut für Physikalische Elektronik (ipe), Universität Stuttgart, Pfaffenwaldring 47, Stuttgart, Germany

#### Stefan Endler

Institute für Mikroelektronik Stuttgart (IMS CHIPS), Stuttgart, Germany

#### **Stefan Engensteiner**

Datacon Technology GmbH, Innstr. 16, 6241 Radfeld, Austria

#### **Mete Erturk**

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

xviii

#### Contributors

#### Patrick J. French

Delft Institute of Microsystems and Nanoelectronics (DIMES), Delft University of Technology, P.O. Box 5053, 2600 GB Delft, The Netherlands

Heinz-Gerd Graf Institut für Mikroelektronik Stuttgart (IMS CHIPS), Stuttgart, Germany

**Oliver Häberlen** Infineon Technologies Austria, Villach, Austria

Christine Harendt Institute for Microelectronics Stuttgart (IMS CHIPS), Stuttgart, Germany

Mahadi-Ul Hassan Institute für Mikroelektronik Stuttgart (IMS CHIPS), Stuttgart, Germany

**Tu Hoang** Institute für Mikroelektronik Stuttgart (IMS CHIPS), Stuttgart, Germany

#### Midoriko Honda

Sales Engineering Division Marketing Group, Marketing Team, DISCO Corporation, Tokyo, Japan

Herbert Hopfgartner Infineon Technologies Austria, Villach, Austria

#### **Cheun-Wen Huang**

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

#### Alvin Joseph

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

#### **Alexander Kaiser**

Reinhardt Microtech GmbH, Wörthstrasse 85, 89077 UCM, Germany

#### Yoshikazu Kobayashi

Sales Engineering Division Marketing Group, Marketing Team, DISCO HI-TEC EUROPE GmbH, Tokyo, Japan

#### Jan Kostelnik

Robert Bosch GmbH, Corporate Research and Development–Dept. Plastics Engineering (CR/APP4), 71301 Waiblingen, Germany

#### Hannes Kostner

Datacon Technology GmbH, Innstr. 16, 6241 Radfeld, Austria

#### Mitsumasa Koyanagi

New Industry Creation Hatchery Center (NICHe), Tohoku University, 28 Kawauchi, Aza-Aoba, Aramaki, Aoba-ku, Sendai, 980-8579 Japan

#### Metin Koyuncu

Robert Bosch GmbH, Corporate Research and Development–Dept. Plastics Engineering (CR/APP4), 71301 Waiblingen, Germany

#### **Andreas Kugler**

Robert Bosch GmbH, Corporate Research and Development–Dept. Plastics Engineering (CR/APP4), 71301 Waiblingen, Germany

#### **Christof Landesberger**

Fraunhofer Research Institution for Modular Solid State Technologies (EMFT), Hansastrasse 27d, 80686 Munich, Germany

#### Walter Lang

Institute for Microsensors, -Actuators and -Systems (IMSAS), Microsystems Center Bremen (MCB), University of Bremen, Bremen, Germany

#### Franz Laermer

Robert Bosch GmbH, Corporate Research and Advance Engineering Microsystems (CR/ARY-MST), P.O. Box 106050, D-70049 Stuttgart, Germany

Thomas Laska Infineon Technologies Austria, Villach, Austria

#### Paresh Limaye Interuniversity Microelectronics Centre (IMEC), Kapeldreef 75, 3001 Leuven, Belgium

#### Mike McPartlin

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

#### Slobodan Mijalković

Silvaco Europe, Compass Point, St Ives, Cambridge, PE27 5JL, UK

#### Kyriaki Minoglou

Interuniversity Microelectronics Centre (IMEC), Kapeldreef 75, 3001 Leuven, Belgium

Mattias Petzold Fraunhofer Institute for Mechanics of Materials, Halle, Germany

Martin Plankensteiner Sales Engineering Division Marketing Group, Marketing Team, DISCO HI-TEC EUROPE GmbH, Tokyo, Japan

#### Horst Rempp

Institute für Mikroelektronik Stuttgart (IMS CHIPS), Stuttgart, Germany

#### Michael Reuter

Institut für Physikalische Elektronik (ipe), Universität Stuttgart, Pfaffenwaldring 47, Stuttgart, Germany

#### Behzad Rejaei

Department of Electrical Engineering, Sharif University of Technology, 11365 Tehran, Iran

#### Harald Richter

Institute für Mikroelektronik Stuttgart (IMS CHIPS), Stuttgart, Germany; Institut für Mikroelektronik Stuttgart (IMS CHIPS), Allmandring 30a, 70569 Stuttgart, Germany

#### Niccolò Rinaldi

Department of Biomedical, Electronics and Telecommunications Engineering, University of Naples Federico II, Via Claudio 21, 80125 Naples, Italy

#### Salvatore Russo

Department of Biomedical, Electronics and Telecommunications Engineering, University of Naples Federico II, Via Claudio 21, 80125 Naples, Italy

#### Sabine Scherbaum

Fraunhofer Research Institution for Modular Solid State Technologies (EMFT), Hansastrasse 27d, 80686 Munich, Germany

#### **Florian Schmitt**

NXP Semiconductors Germany GmbH, Stresemannallee 101, 22529 Hamburg, Germany

#### Fabian Schnegg Datacon Technology GmbH, Innstr. 16, 6241 Radfeld, Austria

#### **Stephan Schoenfelder**

Fraunhofer Institute for Mechanics of Materials, Halle, Germany; Fraunhofer Center for Silicon Photovoltaics, Halle, Germany

#### **Cor Scherjon**

Institut für Mikroelektronik Stuttgart (IMS CHIPS), Stuttgart, Germany

#### **Peter Stallhofer** Siltronic AG, Burghausen, Germany

#### **Anthony Stamper**

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

#### Hannes Sturm

Institute for Microsensors, -Actuators and -Systems (IMSAS), Microsystems Center Bremen (MCB), University of Bremen, Bremen, Germany

#### **Thomas Suwald**

NXP Semiconductors Germany GmbH, Business Unit Identification, Georg-Heyken-Str. 1, 21147 Hamburg, Germany

#### Andrea Urban

Robert Bosch GmbH, Engineering Sensor Process Technology (EPT), P.O. Box 1342, D-72703 Reutlinger, Germany

Jan Vanfleteren IMEC Ghent, Technologie Park 914, B-9052 Gent, Belgium

#### Dan Vanslette

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

#### Wayne Woods

IBM Semiconductor Research and Development Center, 1000 River Rd, Essex Junction, VT, USA

#### Nicoleta Wacker

Institut für Mikroelektronik Stuttgart, Allmandring 30a, 70569 Stuttgart, Germany; Institute für Mikroelektronik Stuttgart (IMS CHIPS), Stuttgart, Germany

#### **Michael Zernack**

NXP Semiconductors Germany GmbH, Stresemannallee 101, 22529, Hamburg, Germany

#### Wenqi Zhang

Interuniversity Microelectronics Centre (IMEC), Kapeldreef 75, 3001, Leuven, Belgium

#### André Zimmermann

Robert Bosch GmbH, Corporate Research and Development–Dept. Plastics Engineering (CR/APP4), 71301 Waiblingen, Germany

#### Martin Zimmermann

Institute for Microelectronics Stuttgart (IMS CHIPS), Stuttgart, Germany

xxii

## Part I From Thick Wafers to Ultra-Thin Silicon Chips

For more than 40 years we have been used to silicon technology based on thick and thus mechanically stiff circular-shaped wafers. We have accepted the fact that we sacrifice valuable silicon wafer real estate due to the rectangular shape of the chips that are cut from the round wafers. We have also disregarded the fact that the electronic structures only occupy the upper 1% of the wafer and, that the other 99% of the bulk wafer is apparently useless. However, this major part of the silicon wafer provides mechanical stiffness required for reliability in wafer processing and automated wafer handling. On the other hand, there are good reasons to look for possibilities to separate the thin electronic layer of a wafer from its bulk part. The interconnect dilemma in CMOS technology scaling has clearly pointed to three-dimensional (3D) circuit integration, pushing toward ultra-thin chips.

Chapter 1 explains the reasons why silicon wafers are as thick as they are. Chapter 2 highlights the need for thin chips, as projected on the International Roadmap for Semiconductors (ITRS). This first part of the book will, therefore, provide a motivation for the in-depth discussion on thin chip technology, add-on processes to thin chips, assembly and packaging, characterisation and modelling as well as ultra-thin chip applications discussed throughout the book.

## Chapter 1 Why Are Silicon Wafers as Thick as They Are?

**Peter Stallhofer**

**Abstract** Silicon wafers have been the building blocks of the electronic industry for more than 40 years. Wafer size increased from 2 in. in diameter in 1970 the wafer size increased to 300 mm in 2000, enhancing the productivity of the chip manufacturing significantly. With growing diameters, wafer thickness of wafers increased steadily, reaching 775  $\mu$ m for 300-mm diameter wafers. The primary reason for this increase was the need to ensure safe wafer manufacturing without breakage and to provide sufficient mechanical and thermal stability of the wafers in IC fabrication during processing steps of lithography and heat treatments.

Beyond this, silicon wafers also must meet certain defect kinetic properties in device processing, which depend on the wafer thickness as well and are crucial for device yield and economic feasibility.

#### 1.1 Moore's Law and Trend in Wafer Diameter

Silicon is the foundation of semiconductor electronics and forms the material basis for the technology of modern communication society. Silicon has permeated all areas of our life, doing so to such a large extent that we do not appreciate its role in our daily routines: We commonly work with computers, entrust complex operations to electronic units, store or evaluate huge mounds of data, disseminate information worldwide via the Internet in a second and expect to be reachable everywhere by mobile devices. Silicon is the material that enabled the electronic revolution by providing a suitable platform for all these electronic devices. These devices have become affordable for everybody and are available in almost unlimited quantities.

The enormous potential of integrated circuits was recognized early by Intel cofounder Gordon Moore in his visionary and famous paper of 1965 [1]. In this paper he described the paramount economic and technological importance of

P. Stallhofer (🖂)

Siltronic AG, Burghausen, Germany

e-mail: peter.stallhofer@siltronic.com

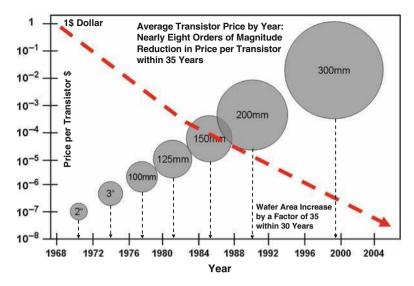

Fig. 1.1 Consequences of Moore's law: price decay trend of electronic components and increase of wafer diameter

integrated semiconductor circuits. He recognized that permanent cost reduction and steady development of wafer technology together play the key role.

Moore predicted a progressive increase in integration density and simultaneous reduction of unit costs per circuit component. Moore's statement – known as Moore's law today – hypothesised that the density of components would be doubled every 2 years, a statement that has been valid for more than 40 years. The significant enlargement of wafer size by a factor of 35 from 2-in. to 300-mm diameter contributed an additional important element to enhancement of productivity in device fabrication and lower total costs (Fig. 1.1).

The validity of Moore's law has resulted in chips with a complexity and performance that had previously been inconceivable and with prices similar to common consumer goods. Advanced microprocessors contain more than one billion transistors on a silicon chip with an area of about  $1 \text{ cm}^2$ . For decades Moore's law has been established as a realistic guideline for development in the semiconductor industry. It forms the basis for the widely accepted technology roadmap, the International Technology Roadmap for Semiconductors (ITRS) [2] for the semiconductor community. The ITRS defines a set of technological requirements per device generation considered necessary to enable further miniaturization.

#### 1.2 Wafer Size and Wafer Thickness

Larger wafer diameters are accompanied by a trend to increased wafer thicknesses. The thickness value is chosen to ensure mechanical and thermal stability during wafer manufacturing and device processing.

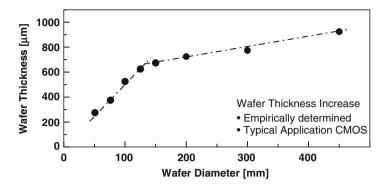

Fig. 1.2 Historical trend of wafer thickness and wafer diameter

The historical trend of wafer thickness as a function of wafer diameter is shown in Fig. 1.2. The wafer thickness was determined to be 275  $\mu$ m for 2-in. wafers, 375  $\mu$ m for 3-in. wafers, 525  $\mu$ m for 100-mm wafers and 625 and 675  $\mu$ m for 125- and 150-mm wafers, respectively. The current high volume wafers, 200- and 300-mm diameter, are produced with thicknesses of 725 and 775  $\mu$ m, respectively.

Up to the 200-mm wafer generation, wafer thickness had been almost exclusively defined empirically, without much in-depth investigation. Wafer as well as device manufacturers carried out application-oriented experiments to determine optimal thickness, and, based on these results and their experience with previous wafer diameters, agreed upon a new wafer thickness value. At each wafer generation the Semiconductor Equipment and Materials International (SEMI), an international intertrade organization of leading semiconductor manufacturers, assigned a standard value to wafer diameter.

The most critical characteristics of a silicon wafer are fracture behavior and robustness in handling and transport operations. Silicon crystals are brittle and hence exposed to the risk of breakage during wafer manufacturing. Breakage is a major issue during the processes of ingot cutting, mechanical planarization and lapping. Furthermore, defects generated in these processes can cause wafer fracture in later wafering steps. The earlier inner diameter sawing technique used for smaller wafer diameters was accompanied by a higher breakage rate.

Wire sawing was introduced in the 200-mm wafer generation. In principle this allowed a transition to thinner wafers, which is considered in determining standardized wafer thickness for a given diameter. The wire sawing technique employs a metal wire for cutting with slurry, based on a silicon carbide (SiC) cutting grain immersed in a glycol carrier medium. This process is similar to a lapping process. In comparison, the previous ingot cutting technology – the inner-diameter saw – used diamond-coated sawing blades and exposed the silicon crystal to much higher mechanical forces during cutting. The forces generated during inner-diameter sawing inherently prohibited the transition to lower wafer thicknesses due to excessive crystal damage. The key process for device miniaturization is optical lithography. It is used several times during device manufacturing and maps the fine geometric structures of the device onto the wafer surface. Lithography requires that the wafer maintain its mechanical stability throughout all process steps of device fabrication, including thermal processes such as diffusion or CVD deposition at elevated temperatures. Hence lithography requirements render it necessary to reproducibly place and accurately align the wafer on process chucks. Issues related to wafer bending, warpage and overlay problems between adjacent layers can lead to critical failures during lithography.

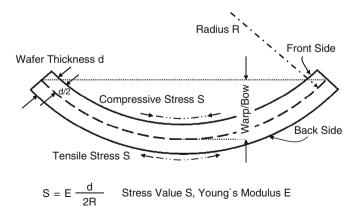

The standardized parameter describing wafer warpage is bow and is shown in Fig. 1.3. The degree of wafer warpage or twisting also depends on wafer thickness.

The bow of an unprocessed wafer has two sources: (1) every wafer has an intrinsic bow value resulting from the shape generated during wafer cutting; and (2) a bow can be generated by the weight of the wafer due to sagging. The latter is called gravitational bow.

The gravitational bow has become very relevant for the 300-mm wafer generation with a standardized thickness of 775  $\mu$ m. The 300-mm wafer sags by about 200- $\mu$ m when placed in a horizontal position and supported by three points around the wafer periphery.

Gravitational bow generates stress in the wafer (Fig. 1.3), which – amplified in thermal processes due to thermal gradients – can lead to slip and dislocation loops in the silicon crystal. Consequences of higher bow or warp are local crystalline defects, which cause functional failures in semiconductor devices and result in severe yield losses. In modern device production it has become necessary to develop appropriate support mechanisms for 300-mm wafers that allow an acceptable suspension of the wafer. Such support mechanisms are necessary to minimize the sagging effect in vertical furnaces and rapid thermal anneal (RTA) systems.

The gravity-induced bow is currently a very important issue. Extensive investigations have been performed to determine the standard thickness of the next proposed wafer generation with a diameter of 450 mm. If it were based on a three-point peripheral support mechanism, a 450-mm wafer with a thickness of

Fig. 1.3 Schematic sketch of wafer with bow and related stress

775  $\mu$ m would sag by more than 3 mm! To obtain the same sag as seen on the standardized 300-mm wafer, a thickness of 1,800  $\mu$ m for 450 mm diameter wafer would be necessary [3]. This would require a factor of 2.3 times the silicon per processed chip area, which is unacceptable for the device community. The bulk crystal cost is the most significant cost factor in wafer manufacturing, one which has led to the latest compromise in wafer thickness of 925  $\mu$ m. Present findings indicate that a thickness of 925  $\mu$ m for a 450-mm diameter would be sufficient to effectively control the bow degradation during device processing [4].

Wafer thickness must not only result in acceptable material properties and affordable wafer bulk crystal costs, it must also be standardized. Thickness is a critical parameter for the set of sophisticated equipment used in an IC line and a standard is necessary for equipment compatibility. Once thickness is standardized, changes are only possible with considerably higher effort. Process chambers, pocket depths of susceptors, pitch heights, slit widths of process and transport carriers and handling by robots are only a few examples of equipment interaction with wafer thickness. Most tools used in the device manufacturing facility require standardized thickness specifications to enable fully automated device processing.

#### **1.3** Silicon Wafer and Its Defect Kinetic Properties

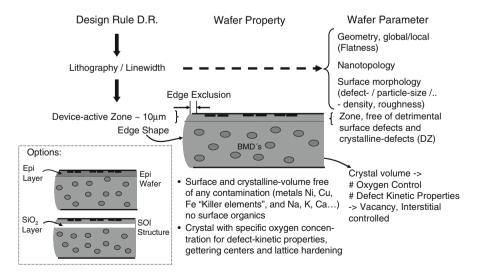

The silicon wafer not only serves as a substrate to allow lithography and map the silicon surface with the device active structures, but it must also fulfill three additional requirements [5, 6]. These requirements are closely related to the silicon crystal and its defect kinetic properties. No highly integrated circuit would work and could be produced with economic yield without these properties (Fig. 1.4):

Fig. 1.4 Silicon wafer properties and related wafer parameters for a given design rule

- 1. The formation of a defect-free layer (denuded zone, DZ) below the surface of the silicon wafer, in which the active device islands are located.

- 2. The generation of gettering capable crystalline defects within the bulk of the wafer, which attract all detrimental impurities, in particular the fast diffusing metals like Ni, Cu, and Fe. This gettering keeps the impurities away from the active device zones (internal gettering [IG] is the technical term).

- 3. The silicon crystal has to contain a certain specified oxygen concentration, which is matched to the thermal budget of the device process. In addition to playing an important role in items (1) and (2), the oxygen concentration is critical in setting the crystal hardening behavior and resistance to slip and dislocations.

If, and only if, conditions (1) to (3) are fulfilled can the functionality of highly integrated devices be guaranteed. None of today's highly integrated complementary metal oxide semiconductor (CMOS) processes would be able to reach the economic yield necessary for low manufacturing costs without the defect kinetic properties of the silicon crystal.

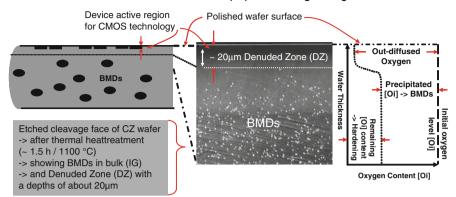

The defect kinetic properties of silicon are closely linked to the oxygen content of the silicon crystal grown by the Czochralski method. The oxygen atoms (labeled Oi in figure 1.5) are incorporated into the growing crystal in a well-controlled manner. During crystal growth oxygen atoms are transferred from the crucible into the molten silicon and are segregated into the growing crystal. At 1,400°C the oxygen atoms occupy interstitial lattice sites with concentrations below  $10^{18}$  cm<sup>-3</sup> (DIN). During device processing, high temperature steps (~1,000–1,100°C, 1 h) cause oxygen in the vicinity of the wafer surface to out-diffuse, leaving a residual concentration below  $(2-3) \times 10^{17}$  cm<sup>-3</sup>, which corresponds to oxygen solubility at ~1,000°C. In the wafer volume, a certain amount of oxygen atoms conglomerate to form defect clusters and generate precipitates, the so-called bulk micro defects (BMDs). The near surface region remains cluster free and forms the so-called denuded zone (DZ). In the crystal volume the BMDs act as internal gettering sites due to the strain field associated with them. The remaining oxygen content on the interstitial sites enhances the hardening effect of the silicon lattice, showing higher resistance against slip formation.

The temperature steps necessary for the out-diffusion of the oxygen are inherent to device fabrication, e.g., in CMOS-like processes during the p-well drive in and in bipolar processes during the emitter drive-in step. Both process steps provide a suitable temperature-time window. The wafer has the following sandwich structure after device processing (Fig. 1.5).

Close to the wafer surface a defect-free layer exists having a depth of up to  $20 \mu m$ , with the crystal volume containing the bulk micro defect region.

No other material combines all the exceptional advantages for integrated circuits as silicon does. It is readily available, allows for manufacturability of dislocationfree crystals, forms wafers with the highest possible perfection and purity and can prefectly match the defect kinetic properties to the needs of device manufacturing. All these attributes make silicon indeed it a special gift of nature.

Example for internal gettering sites (BMDs) after device processing heat cycles and the formation of a Denuded Zone (DZ) -> Defect engineering

Fig. 1.5 Silicon wafer and the formation of oxygen-related bulk micro defects (BMD) with a denuded zone (DZ) formed during thermal heat treatment

All of the wafer characteristics described in the previous lines are driven by applications requiring highest integrated circuit density. These applications benefit strongly from Moore's law and are currently in the sub 100-nm regime. CMOS technology provides the platform for making the smallest possible feature size for electronic devices such as microprocessors, memory and logic circuits. Approximately 70–80% of silicon wafers are used in feature size critical CMOS applications. They are almost exclusively manufactured on 200-mm and 300-mm diameter wafers.

#### **1.4 More than Moore Applications**

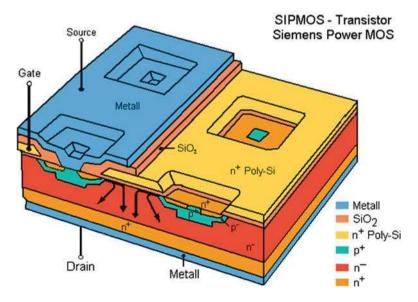

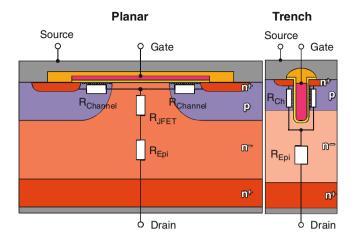

In addition to the wafers used in CMOS-based applications a further 20% of silicon wafers are used for discrete (as opposed to integrated) devices, which find applications in power electronic sensors and micro-electro-mechanical systems (MEMS). These applications are sometimes referred to as "More than Moore" because they are not driven by the leading edge lithography and miniaturization trends but from other factors.

These discrete devices are not only dependent on the near surface region properties, as in the case of CMOS, but are strongly dependent on bulk crystal properties. The bulk material is actually an active part of the device structure. An extreme example of such a device is a 5-kV Thyristor which has lateral dimensions the size of one 100-mm wafer and a space charge region depth of 100  $\mu$ m extending deep into the wafer.

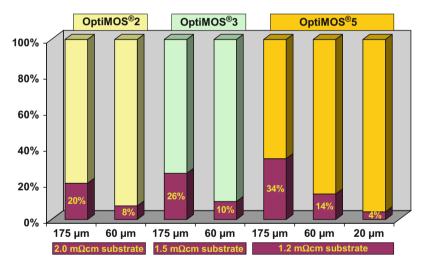

PowerMOS transistors represent another product group that depends on the bulk electrical properties. PowerMOS transistors can switch currents of some hundred amperes and some thousand volts between terminals. The current is conducted through the substrate to a backside wafer contact. The substrate needs to have a very low resistivity of some mOhm-cm in order to reduce voltage loss in the device. The resistivity values and tolerances are critical for these devices. Consequently, power-MOS is an example of a device type that requires minimum substrate thickness to reduce voltage drop in the device.

Characteristics of more than Moore applications are:

- Relaxed lithography requirements, which can be as high as 3.5  $\mu$ m minimum feature size.

- Active device area extending deep into the substrate.

- Very tight resistivity target and tolerance requirements. High resistivity of several hundred Ohm-cm or low resistivity in the mOhm-cm regime.

- Crystal volume free of critical crystal defects, i.e., very few oxygen conglomerations and prevention of BMD growth.

- Wafer diameters typically ≤150 mm, including both polished and nonpolished surfaces (lapped, etched or as-cut).

- The thickness spectrum of wafers used for these applications ranges from 200 to  $1,000 \ \mu m$ .

Crystals grown for applications driven by Moore's law require interstitial oxygen Oi in the bulk material and are grown by the Czochralski method (CZ). The high defect requirements and resistivity tolerances for More than Moore applications prefer a different crystal growth process known as the float-zone (FZ) growth method. FZ crystals are free of Oi conglomerates and hence prevent the formation of BMDs. These wafers have no inherent internal gettering mechanism and other gettering means are required; e.g., mechanical gettering on the wafer backside. FZ grown wafers are also more susceptible to slip during high temperature processing, as the Oi hardening effect is not present. Wafer slip is avoided by reducing thermal gradients in furnace processes. This can be achieved by reducing push and pull rates into and out of the furnace. Increasing the distance between adjacent wafers in the furnace also helps to reduce thermal gradients.

In summary three factors are responsible for determining the wafer thickness:

- 1. Adequate mechanical and thermal stability of the wafer during the wafer manufacturing process and the device process to avoid wafer breakage. This stability is a prerequisite for processes that the lithography steps expose the wafer.

- 2. The silicon wafer must develop adequate gettering.

- 3. Device types requirements on the bulk material need to be considered.

For the highly integrated CMOS-based devices it is absolutely necessary to form a denuded zone and form internal gettering centers. These devices are manufactured in highly automated production lines with standardized equipment and hence forbid changes in wafer thickness. The situation changes if the wafer is further processed after completing the critical lithography steps. An example of further device processing after the critical lithography steps is device stacking to form three dimensional structures. The processed wafers may be thinned from the

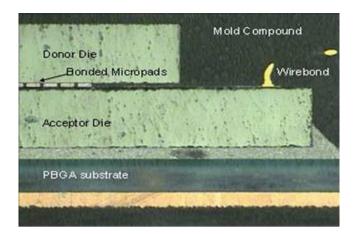

backside by grinding and/or etching to a thickness below 100  $\mu$ m. A rest thickness of 25  $\mu$ m has been demonstrated using this technology without causing damage to the CMOS-based devices. These extremely thinned wafers are very flexible and are temporarily bonded to support substrates, normally glass or ceramic, should additional processing be necessary. The support substrate may later be detached. The bonded wafer composite structure can further be processed using lithography on the wafer backside. The most frequent backside processing steps are void etching and contact metallization, which allow processed chips to be stacked on top of one another. This stacking of chips increases packaging density and reduces parasitic components by replacing lead-frame wires with very short metal contact lines. It also allows different types of chips to be stacked into one common package.

Gettering issues need careful consideration for the further processing of thin device wafers. Gettering centers that have formed during device processing (BMDs) can be removed during the thinning process. During post thinning metallization steps no getterer exists, and it is conceivable that metallic impurities can diffuse to the sensitive front-side device regions and cause contamination related failure. This failure mechanism is particularly dangerous for metals such as Cu, which diffuse quickly at relatively low temperatures ( $<600^{\circ}$ C). If the BMD gettering centers have been removed during the back thinning process then new centers can only be regenerated at high process temperatures (1,000°C). The engineering of the denuded zone and the BMD generation also needs to consider the post device processing including wafer thinning. It is also possible to bond a thinned wafer to a suitable substrate prior to device processing. In this case the denuded zone and BMD formation also need to be carefully engineered.

The details of gettering depend on the specific temperature-time profile of the device process. Two extreme cases help to understand the issues; in the first case the temperature budget is too high and interstitial oxygen diffuses out of the crystal surfaces resulting in two overlapping denuded zones. This leads to a situation where no gettering centers are formed and the Oi hardening effect is not present. In this case metallic impurities can diffuse to the critical device regions and cause failure. In the second case, the temperature budget is too low for outdiffusion of Oi atoms, and small defect centers form in the active device region resulting in either poor device characteristics or even complete functional failure.

The occurrence of gettering problems depends on the specific temperature-time profile of the specific device process. Consequently, the success of a suitable defect engineering measure depends on the specifics of the case at hand.

#### References

- 1. Moore GE (1965) Cramming more components onto integrated circuits. Electronics 38(8):114–117

- 2. http://www.itrs.net/links/2009ITRS/Home2009.htm

- 3. Kanda T, Fujiwara T, Takaishi K (12 Jan 2008) SUMCO. Semiconductor International

- 4. http://ismi.sematech.org/meetings/archives/ngf450/index.htm

- 5. Huff HR, Fabry L, Kishino S (eds) (2002) Semiconductor silicon 2002, vol 1 and 2. The Electrochemical Society, Inc., Pennington, NJ

- 6. Scheel HJ, Fukuda T (eds) (2003) Crystal growth technology. Wiley, New York

## Chapter 2 Thin Chips on the ITRS Roadmap

Joachim N. Burghartz

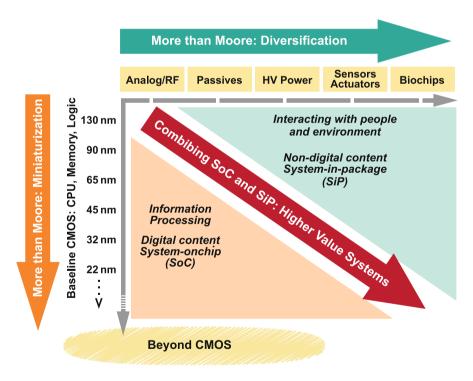

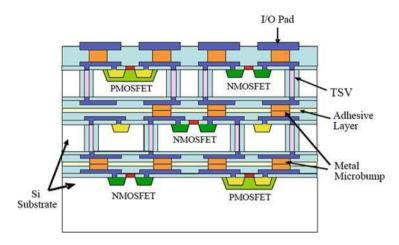

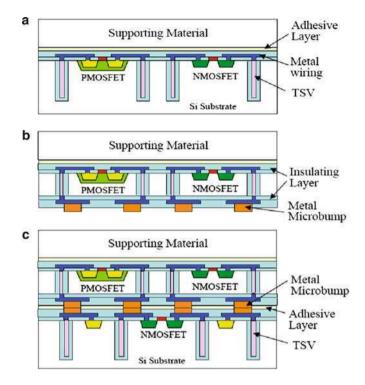

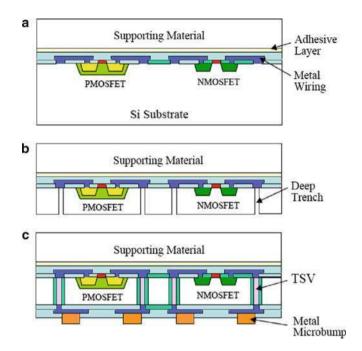

Abstract The International Technology Roadmap for Semiconductors (ITRS) projects decreasing chip thickness in support of three-dimensional integrated circuit (3D IC) solutions. The 3D IC technology potential is not yet fully leveraged due to insufficient scaling of the through-silicon via (TSV) pitch. Since technological limits restrict the TSV ratio at about 10:1, minimum chip thickness enables us to take full advantage of the 3D IC concept in support of continued miniaturisation (More Moore). Moreover, the excellent mechanical properties of silicon qualify ultra-thin chips for applications of silicon technology for added functionality (More than Moore).

#### 2.1 The ITRS Roadmap

In 1965 Gordon E. Moore presented his vision about the future exponential growth of the semiconductor industry, known today as 'Moore's Law' [1]. Following Moore's prediction the industry has kept a steady pace of miniaturisation, doubling device density every 18–24 months, doing so for 45 years now. It was not only about forecasting, but about commanding the silicon revolution. The idea has evolved into a more specific definition, a roadmap that is defined by semiconductor manufacturers and equipment providers.

Since the 1992 publication of the National Technology Roadmap for Semiconductors in the United States by the Semiconductor Industry Association (SIA), with new versions in 1994, 1997, and 1999, this treatise has been widely quoted throughout the industry [2]. Since 1998 the International Roadmap for Semiconductors (ITRS) has represented an international effort toward improving semiconductor device scaling by combining various national or regional roadmap initiatives worldwide, such as the European Electronic Component Manufacturers'

J.N. Burghartz (🖂)

Institute for Microelectronics Stuttgart (IMS CHIPS), Stuttgart, Germany e-mail: burghartz@ims-chips.de

Association (EECA), the Electronic Industries Association of Japan (EIAJ), the Korea Semiconductor Industry Association (KSIA) and the Taiwan Semiconductor Industry Association (TSIA), besides SIA. Over the years ITRS has become the global industry's metronome, setting the pace for the development of new semiconductor technologies. Due to the fast-paced nature of the industry the roadmap needs to be reviewed annually. The international ITRS consortium with experts from over 900 companies organised in working groups projects the technological needs for the next 15 years on an annual basis.

#### 2.2 Thin Chips for More Moore

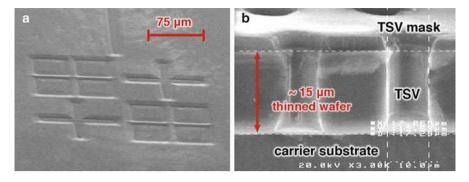

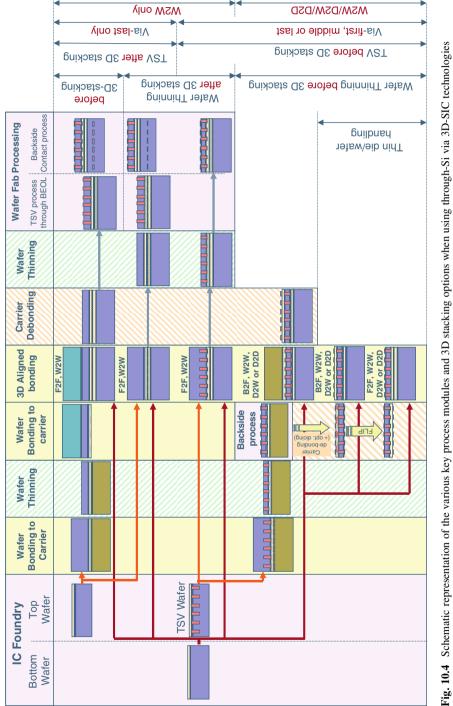

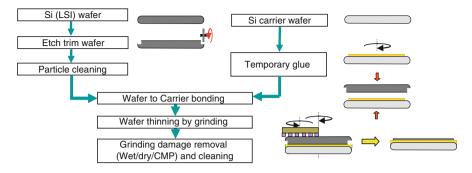

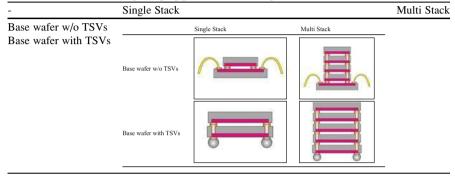

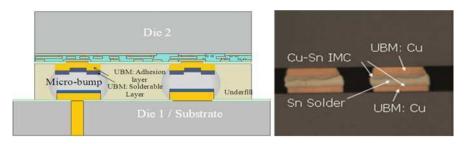

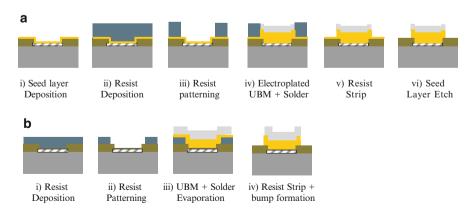

The 2001 edition of the ITRS mentions for the first time about a need for thin dies to allow for three-dimensional (3D) chip stacking in system-in-package (SiP) solutions. In the 2003 edition very thin dies are mentioned, though not yet with a defined thickness target; only a forecast on the number of stacked dies was made. The 2005 ITRS edition put a strongly increased focus on wafer thinning and handling, small and thin die assembly and packaging of thin chips. A need for chips thinner than 20  $\mu$ m was mentioned. Wafer thinning was the only technique considered for achieving thin chips. It was projected that at thicknesses below 10  $\mu$ m a sequential combination of mechanical grinding, chemical-mechanical polishing (CMP), wet etching and plasma treatment, and dry chemical etching would be required to allow for control of such small chip thickness and to produce a die free of stress. The development of new pick and place techniques was viewed as a key issue for handling and assembling ultra-thin dies. The 2007 edition placed a stronger focus on the formation of TSV.

It is interesting that the projection of chip thickness requirements on the 2005 and 2007 Roadmap editions, as well as on the 2008 update, were identical

|          | 20             | 005 20         | 006 2007       | 2008           | 2009            | 2010            | 2011           | 2012           | 2013           |

|----------|----------------|----------------|----------------|----------------|-----------------|-----------------|----------------|----------------|----------------|

| ITRS-2   | 005 50         | $)^1$ 25       | $5^1$ $20^1$   | $20^{1}$       | 15 <sup>1</sup> | 15 <sup>1</sup> | $10^{1}$       | $10^{1}$       | $10^{1}$       |

| ITRS-2   | 007            | 50             | $20^1$ $20^1$  | $15^{2}$       | $15^{2}$        | $10^{2}$        | $10^{2}$       | $10^{2}$       | $10^{2}$       |

| ITRS-2   | 008            |                | $20^{2}$       | $15^{2}$       | $15^{2}$        | $10^{2}$        | $10^{2}$       | $10^{2}$       | $10^{2}$       |

|          |                |                |                |                |                 |                 |                |                |                |

| 2014     | 2015           | 2016           | 2017           | 2018           | 2019            | 2020            | 2021           | 2022           | 2023           |

| $10^{1}$ | $8^{2}$        | 8 <sup>2</sup> | 8 <sup>2</sup> | 8 <sup>2</sup> | 8 <sup>2</sup>  | 8 <sup>2</sup>  |                |                |                |

| $10^{2}$ | 8 <sup>3</sup>  | 8 <sup>3</sup>  | 8 <sup>3</sup> | 8 <sup>3</sup> |                |

| $10^{2}$ | 8 <sup>3</sup>  | 8 <sup>3</sup>  | 8 <sup>3</sup> | 8 <sup>3</sup> | 8 <sup>3</sup> |

Table 2.1 Minimum wafer thickness projections on ITRS 2005, 2007, and 2008 update

<sup>1</sup> Manufacturing solutions exist

<sup>2</sup> Manufacturing solutions are known

<sup>3</sup> Interim solutions are known

<sup>4</sup> Manufacturing solutions are NOT known

(Table 2.1). However, confidence in technology's capacity to provide manufacturing solutions sank after the first projections were made in 2005.

This change is an indication that the challenges in wafer thinning and thin die fabrication had been underestimated and, that today manufacturing solutions are known but not in place for manufacturing.

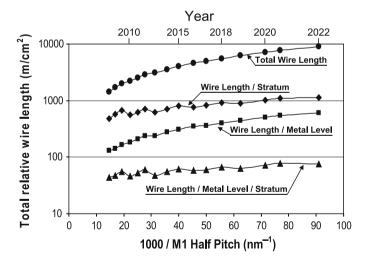

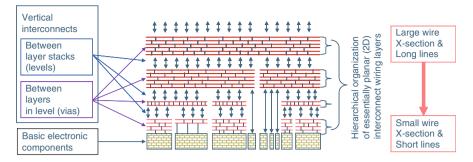

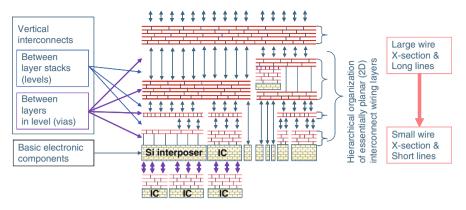

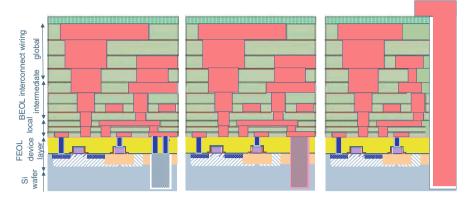

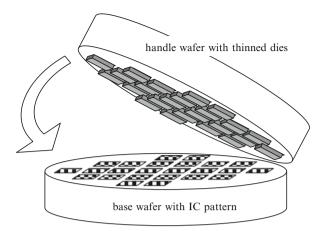

The need for ultra-thin chips today comes primarily from 3D system integration, where multiple active dies having active and lateral interconnects are vertically connected through TSVs. Such a 3D interconnect scheme allows for effectively shorter lengths of intermediate and global wires compared to the conventional planar IC.

As shown in Fig. 2.1, the effective interconnect length of the active wires will continue to increase strongly. This relates to the ever-growing complexity of interconnects. However, investment into more interconnect levels does not alleviate that problem (Fig. 2.1). The only remaining solution to overcome the interconnect bottleneck is thus to consider true 3D ICs, in which the interconnect routing can exploit both the lateral and the vertical dimensions [3]. As Fig. 2.1 shows this concept is clearly more effective than the conventional multilevel interconnects even, if only one metal level per stratum is provided. When one exploits both the maximum number of interconnect layers on chip and the maximum number of strata, the increase in active wire length over time becomes subtle. Certainly, this concept may not be feasible both from a technological and an economic point of view. The trend in wire length increase with technology advancement remains in spite of the best technological effort; this may relate to the fact that the projections

**Fig. 2.1** Evolvement of the projection by the International Technology Roadmap for Semiconductors (*ITRS*) on total active wire length (M1 and intermediate interconnects) on chip. The wire length per metal layer, the wire length per stratum based on stratum dies having one metal layer only and the wire length per metal layer and stratum are calculated based on ITRS projections on the number of interconnect layers on chip and strata in 3D chips [2]

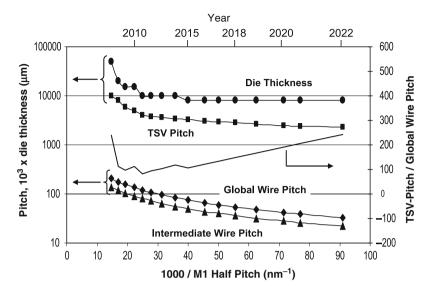

**Fig. 2.2** Projection of the International Technology Roadmap for Semiconductors (*ITRS*) on global and intermediate on-chip pitch in comparison to the through-silicon via (*TSV*) pitch depending on die thickness. The calculated ratio of TSV and global wire pitch is large and will be increasing from 2010, thus indicating that utmost attention must be given to thin chip technology

on chip thickness assumptions, and thus on TSV pitch, have been too conservative. Figure 2.2 shows that from 2010 onward the advancement of global and intermediate on-chip interconnect pitch is stronger than that of TSV pitch. Unless the projections on chip thickness are revised in the coming editions of the ITRS, the effectiveness of TSV interconnects, indicated by the TSV/global wire pitch ratio in Fig. 2.2, will worsen over time. Note that the TSV pitch is directly related to the die thickness since, with current process solutions for via metal refill limit, the TSV depth/ width ratio is 10:1 [2]. Clearly, considerably more attention must be put on ultra-thin chip fabrication techniques that can be made available for manufacturing [4].

#### 2.3 Thin Chips for More than Moore

The 2005 edition of the ITRS first projected the need for focusing not only on device integration that relies on improvements in minimum feature size (More Moore) but also on applications leveraging silicon technology to provide added functionality (More than Moore). A need for thin chips was foreseen, e.g., in flip-chip packaging and chip assembly on flexible substrates and on textiles. Such applications rely less on electronic properties and technological advantages of

silicon than on its excellent mechanical properties, which have been known for a long time [5]. Silicon features high stiffness, quite comparable to that of stainless steel and cast iron and about three times the stiffness of aluminium (Table 2.2). Silicon is known to be brittle, but its ultimate strength is eight times that of stainless steel and 35 and 15 times better than the values for cast iron and aluminium, respectively. The overall better mechanical properties of silicon when compared to stainless steel and cast iron come with a more than double higher thermal conductivity, which is only somewhat lower than that of aluminium. Silicon is also considerably lighter than the other materials listed in Table 2.2.

|                 | Young's modulus<br>(GPa) | Ultimate strength (MPa) | Thermal conductivity (W/mK) | Density<br>(g/cm <sup>3</sup> ) |

|-----------------|--------------------------|-------------------------|-----------------------------|---------------------------------|

| Silicon         | 185                      | 7000                    | 150                         | 2.33                            |

| Stainless steel | 200                      | 860                     | 43                          | 8.19                            |

| Cast iron       | 210                      | 200                     | 80                          | 7.87                            |

| Aluminum        | 70                       | 480                     | 235                         | 2.70                            |

**Table 2.2** Properties of silicon in comparison selected metals

**Fig. 2.3** Illustration of applications driven by strict miniaturisation according to Moore's law (More Moore), which may ultimately be superseded by novel device structures and physics (Beyond CMOS) and of applications of silicon technology providing added functionality and diversification (More than Moore)

### References

- 1. Moore GE (1965) Cramming more components onto integrated circuits. Electronics 38 (8):114–116

- 2. http://www.itrs.net/reports.html

- Joyner JW, Zarkesh-Ha P, Meindl JD (2001) A global interconnect design window for a threedimensional system-on-a-chip. In: Proceedings of the IITC, Burlingame, CA, pp 154–156

- 4. Burghartz JN, Appel W, Harendt C, Rempp H, Richter H, Zimmermann M (2009) Ultra-thin chips and related applications, a new paradigm in silicon technology. In: Proceedings of the ESSDERC, Athens, Greece, pp 29–36

- 5. Peterson K (1982) Silicon as a mechanical material. In: Proceedings of the IEEE, vol 70, no. 5, pp 420–457

# Part II Thin Chip Fabrication Technologies

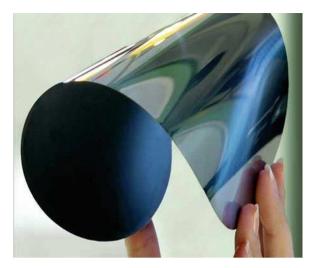

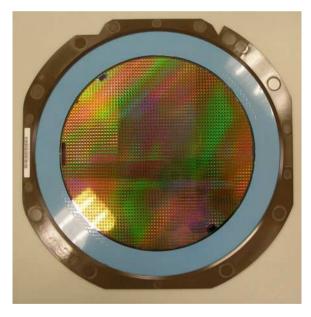

As we have explained, the past forty years microelectronic manufacturing has relied on mechanically stiff and stable wafer substrates (Chap. 1). However, the need for reducing the thermal resistance to the package and for achieving a suitable form factor for very small chips has driven techniques that allow for thinning wafers to smaller thicknesses afterwards. Such thinned wafers (100–300  $\mu$ m) are still mechanically stiff but tend to fracture and thus have to be handled with great care. Below 100  $\mu$ m they become even more fragile and in addition start to bend under their own weight. In the thickness range 50–100  $\mu$ m, fracture of wafers can be initiated even by small deflections. Below 50  $\mu$ m wafers and chips become flexible, i.e., they remain intact also with a considerable degree of deflection applied. At 10  $\mu$ m and smaller thicknesses they could tolerate bending radii of the order of 1 mm and less, which is out of the range of practical application. Such ultra-thin chips are – in principle – unconditionally stable, flexible and reliable. The ranges of wafer thickness in summary:

- >300 μm Unconditional mechanical stability

- 100-300 μm Stiffness but limited mechanical stability

- 50–100 µm Limited stiffness and limited mechanical stability

- 10-50 µm Good flexibility and good mechanical stability

- <10 µm Excellent flexibility and unconditional mechanical stability

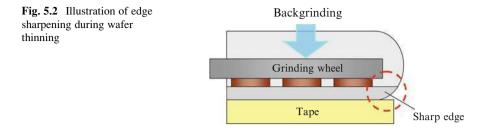

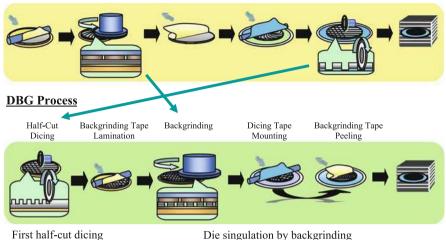

Until now wafer thinning has been a task of the assembly and packaging community. Thinning through grinding and subsequent auxiliary processes has matured to make wafers and chips available at thicknesses in the range of  $50-100 \mu m$  in costeffective manufacturing (Chap. 3). The recently increasing drive toward smaller thickness is motivated by new applications of silicon chip technology, which rely on mechanical flexibility, assembly on nonflat surfaces and chip stacking (Chaps. 9-12 and Chaps. 26-37). The excellent properties of chips having thicknesses below 50  $\mu m$  can only be leveraged if they are not noticeably degraded by the thinning process. Conventional wafer grinding and chip dicing, however, introduces crystalline defects and micro cracks at a considerable level. Therefore, new techniques such as dicing-by-grinding are adopted to prevent edge chipping effects during chip dicing (Chap. 4).

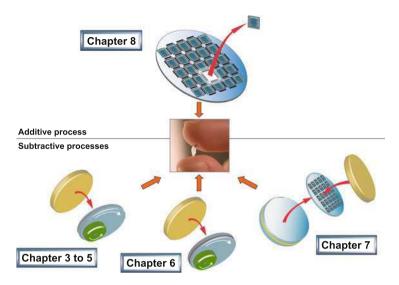

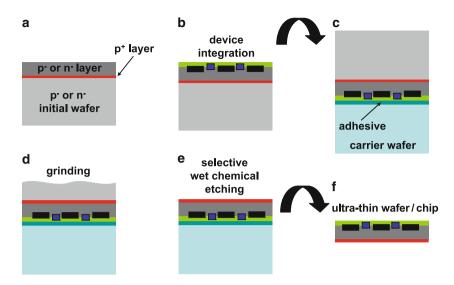

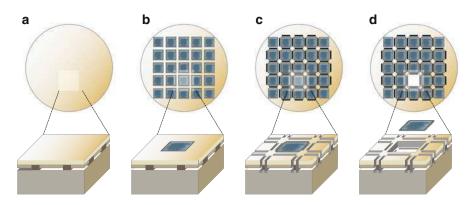

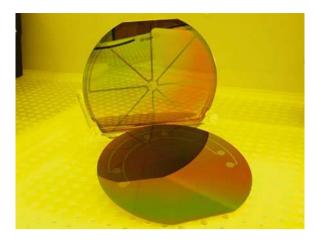

Fig. II.1 Illustrative comparison of generic subtractive technologies and one additive process technology targeted at fabrication of ultra-thin chips

Since silicon wafers at thickness below 50  $\mu$ m lack mechanical stiffness they need to be supported by auxiliary carrier substrates during grinding. Bonding to – and debonding from – carriers considerably adds to process cost and may lead to reduced overall process yield, thus increasing the production expenditure even more. Therefore, thinning techniques that do not require any handle substrates hold great interest for development (Chap. 5).

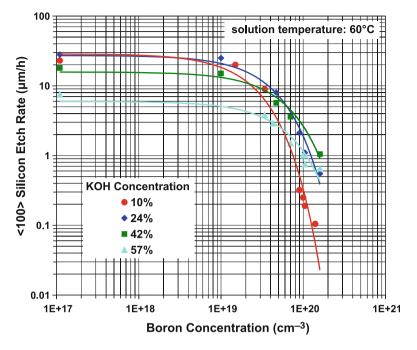

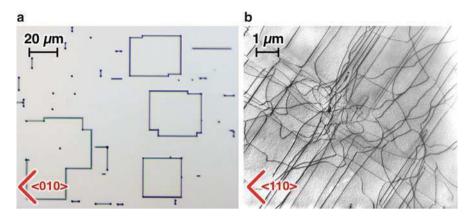

The thinning process itself may be prone to excessive thickness nonuniformity across the wafer, particularly for an extremely small thickness target. Considerable progress has been made by using *in situ* thickness monitoring during wafer grinding, though it is uncertain if chip thickness far below 50  $\mu$ m will be feasible in - cost-effective manufacturing. Better thickness uniformity requires the implementation of etch barriers into the wafer substrate. Such an etch barrier can be based on an epitaxially grown electrochemical etch stop layer (Chap. 6); alternatively, SOI wafer substrates can be employed (Chap. 7). Those technologies, particularly SOI substrates, will lead to much higher cost and are thus preferable for high-end applications. Evidently, all such subtractive thin chip fabrication processes lead to considerably higher cost and process effort as chip thickness decreases. A consequent step toward realising ultra-thin chips at reasonable cost is to consider additive thin chip fabrication, which offers hope for excellent chip thickness control. The recently introduced Chipfilm<sup>TM</sup> technology, e.g., features excellent thickness control by epitaxial growth and even reuse of the bulk silicon substrate (Chap. 8).

In general, different fabrication methods for thin wafers and chips (Fig. II.1) offer prospects for the new applications of silicon technology, exploiting the unique features of ultra-thin chips under the economic constraints of the semiconductor industry.

## **Chapter 3 Thin Wafer Manufacturing and Handling Using Low Cost Carriers**

Florian Schmitt and Michael Zernack

This chapter focuses on thin wafer fabrication and processing that uses low cost sub carriers. It describes the state of the art and the technical boundaries of the application of foils for wafer support and protection. First, the thinning technology and the applied materials are described in terms of process capability and maturity. Methods of thin wafer characterization are presented. Subsequently, the impact of front end design on ultra-thin wafer manufacturing is highlighted. Finally, processes after wafer thinning that enable the "perfect" die are described.

#### 3.1 Wafer Thinning Technologies for Different Thickness Ranges

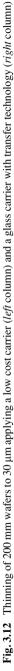

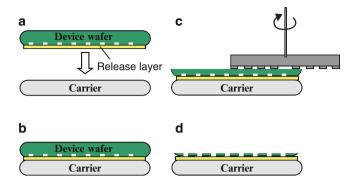

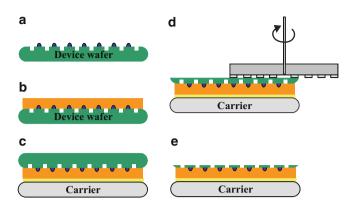

During the standard industrial process flow, semiconductor wafers are thinned on wafer level after front end manufacturing and before integration of silicon chips into packages. Based on one dedicated circuit design, different chip thicknesses enable a broad range of different applications. Final wafer and chip thicknesses depend on application requirements such as package size (form factor), heat dissipation, electronic properties of the substrate, mechanical and thermal stability and flexibility. Wafer thickness of 150  $\mu$ m is common and widespread and can be manufactured using standard grinding methods and equipment. Below 150  $\mu$ m according wafer support is inevitable for a safe handling. Depending on wafer properties such as bow and warp, the structure and composition of active layers including topology and edge profile, wafers can be moved and processed on low cost grinding foils down to a thickness of 30  $\mu$ m. Beyond that size rigid wafer carrier systems have to be applied in order to allow adequate wafer handling and thinning processes. However the step required for mounting and removing rigid carriers adds a significant contribution to the overall manufacturing costs.

F. Schmitt (🖂)

NXP Semiconductors Germany GmbH, Stresemannallee 101, 22529 Hamburg, Germany e-mail: florian.schmitt@nxp.com

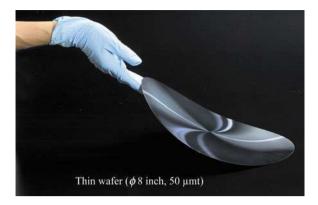

Fig. 3.1 Flexible 50 µm wafer

Fig. 3.2 Fifty micrometers wafer on film frame carrier

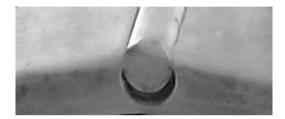

Below 150  $\mu$ m thickness silicon wafers become increasingly flexible (Fig. 3.1). On the one hand flexibility of chips reduces the fracture strength when they are used in flexible card or board applications; on the other hand it complicates handling and subsequent manufacturing processes. The default delivery form today for wafers thinner than 150  $\mu$ m is on dicing foil and film frame carrier (Fig. 3.2).

Fig. 3.3 Thin wafer process from wafer test to wafer separation

However, the wafer does not only have to be stabilised for transport after thinning, but also during the complete wafer thinning process. Wafer thinning encompasses several steps: lamination of a grinding tape on the active side of the wafer (protection from process chemistry and mechanical carrier), multigrinding step (coarse and fine grinding), stress relief (chemical-mechanical polishing or, alternatively, wet or dry etching), wafer mounting onto dicing foil and film frame carrier and grinding tape removal. The process sequence requires continuous handling of the thin wafer on a substrate. The thinning process module is fully integrated into a general purpose wafer treatment flow that enables the delivery of known good (tested) ultra-thin dies (Fig. 3.3). The process flow concept tolerates variations like wafer test after wafer thinning, separation on specialised probing equipment as well as laser separation of wafers.

#### 3.2 Thinned Wafer Properties

Subsequent assembly processes and product specifications are highly demanding on the thinning process, and with respect to the applied materials. Principal requirements are:

- Thinning after bumping, i.e., embedding of topographic features

- · Low target thickness and low total thickness variations

- Defect-free ultra-thin wafers

- · High mechanical stability of chips

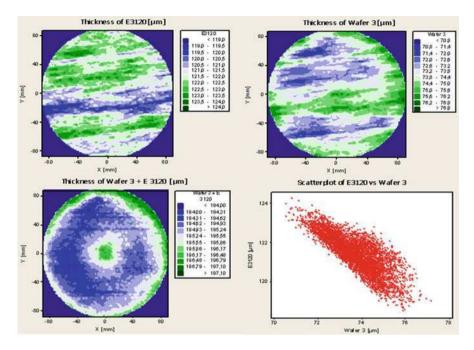

Figure 3.4 shows the impact of grinding tape inhomogeneities (upper left plot) on the thickness of the wafer (upper right plot). This effect can exceed the total thickness variation contributed by the grinding/polishing equipment itself.

Grinding tapes are composed of at least two layers, a harder polymeric backbone and a softer oligomeric or monomeric (UV) adhesion film. Although greater

Fig. 3.4 Influence of grinding foil thickness on wafer thickness

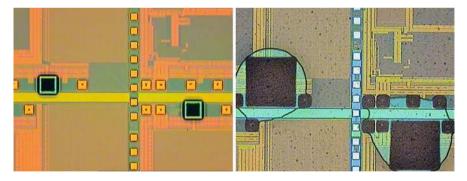

**Fig. 3.5** Incomplete embedding of 400  $\mu$ m bumps (*left* photo) and complete embedding of 100  $\mu$ m bumps into the adhesion layer of the grinding tape (*right* photo)

stiffness of the grinding tape supports its carrier function, the thickness and viscosity of the adhesive film also determines the capability to embed elevated structures (Fig. 3.5), which in turn will affect the thinning process performance and the tape peel-off behaviour.

For process qualification, statistical process control and outgoing visual inspection the following method will be applied once the wafer thickness decreases to below 100 µm: After thinning, wafers are measured by optical coherence interferometry in the IR range of light. This contactless method enables the measurement of wafers on chip scale and of dicing foil thicknesses at micrometre resolution. It allows the monitoring and studying of thickness variations in critical areas like the wafer edge and in the vicinity of contact structures (due to topology).

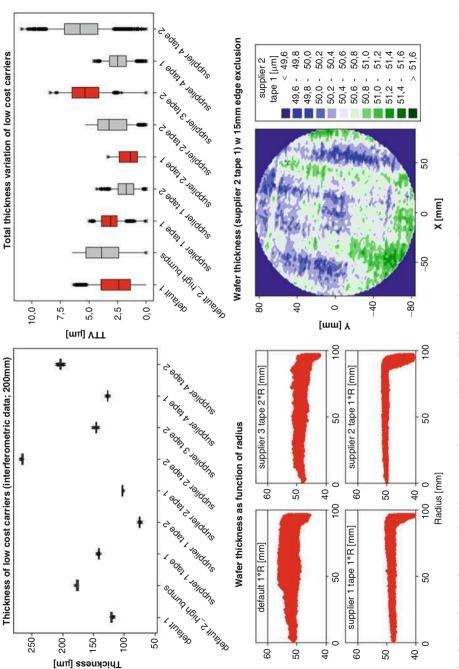

Figure 3.6 depicts the wide thickness range (including the adhesive layer) of state of the art grinding tapes. The right graph shows that selected grinding tapes offer a thickness uniformity of less than 2  $\mu$ m (upper right graph, box plots correspond to 80th percentile). Over a radius of more than 85 mm a wafer thickness variation of approximately 2  $\mu$ m can be achieved (lower right graph). The mechanical tolerances of the thinning equipment are in the range of 1  $\mu$ m.

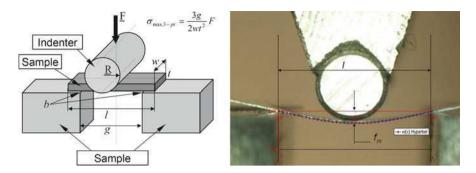

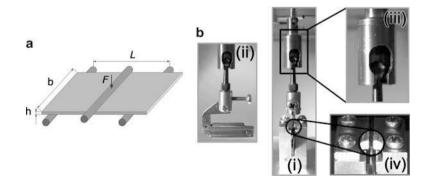

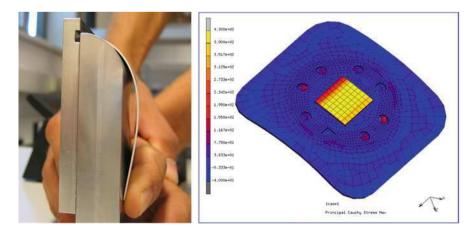

The mechanical robustness of thinned wafers and chips is a not just a default requirement but a key differentiator for their application in flexible modules and chip cards. For the qualification of new thinning processes, ball-on-ring fracture tests are applied that provide information about the surface quality after grinding and polishing [1]. For the qualification of the complete preassembly process including wafer separation, three-point bending tests are applied (Fig. 3.7). The effective bending modulus puts stress on the chip surface and edges and is similar to the applied load of a silicon chip inside a card under field conditions.

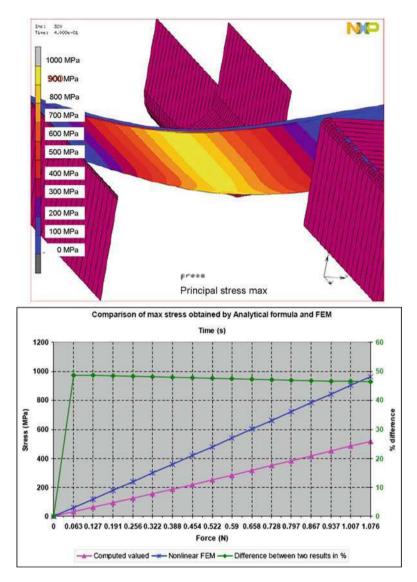

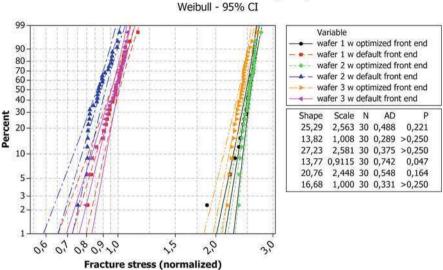

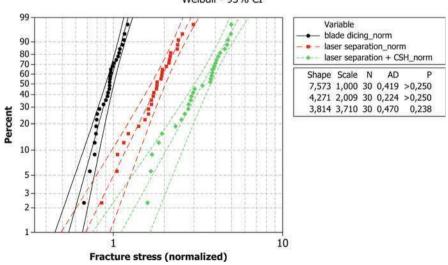

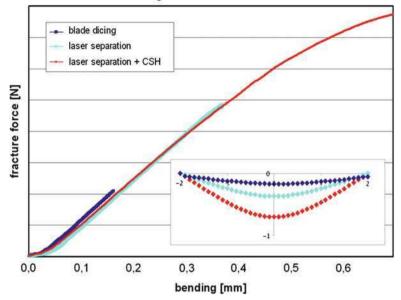

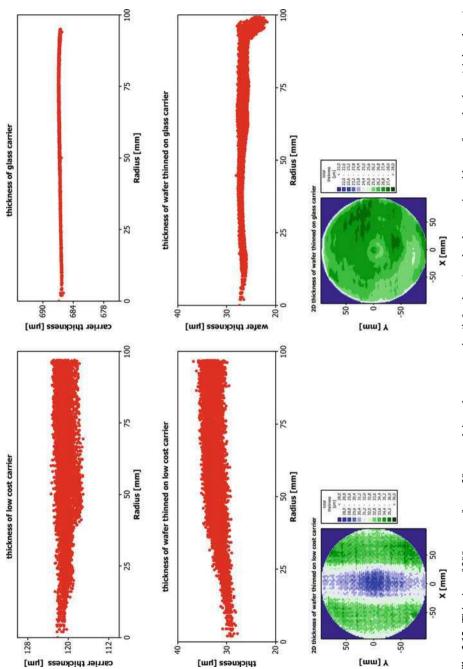

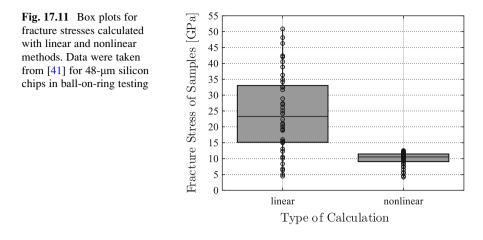

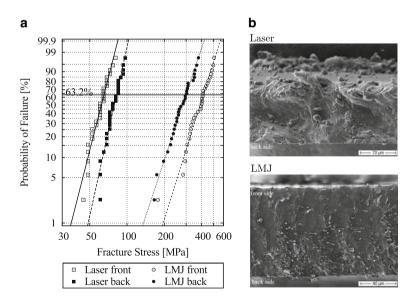

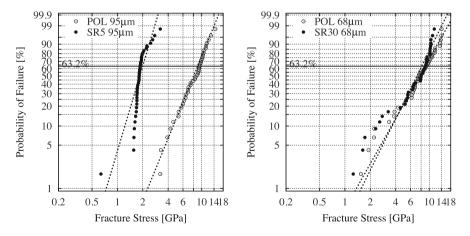

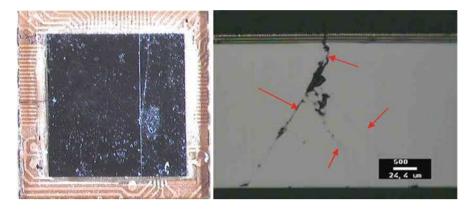

The measured fracture forces are transformed into fracture stress data. By default, a defined number of chips well distributed over the wafer are broken. A force sensor measures fracture strength of the sample front- or back-side. These data can be transformed into fracture stress values and plotted as Weibull distribution graph [2]. Weibull modulus and characteristic stress are intrinsic values that depend on the pre-processing, but not on the thickness of the samples. However, the analytical equations that calculate maximum stress before fracture are valid up to a deflection roughly on the order of the chip thickness. For chips that are thinner than 100  $\mu$ m only relative comparison between differently processed samples can be drawn. Absolute characteristic stresses cannot be deduced from this. FEM simulations result in significantly lower stress values for the bending of ultra-thin silicon chips (Fig. 3.8).

The thinner silicon wafers and chips get, the higher is the risk of microscopic defects, e.g., hair cracks due to particles in the thinning process. Automatic optical inspection of 100% at chip level is indispensable if the process is to satisfy low ppm failure requirements and exclude any mechanical failure mechanisms that would lead to field losses.

#### 3.3 Impact of Wafer Frontside Design

Integral wafer handling is only one stringent prerequisite for thin wafer processing below 150  $\mu$ m thickness. Moreover, the impact of front end design on ultra-thin wafer manufacturing has to be taken into consideration. Contacts with large area and stand-up heights present an additional challenge for the grinding foil material, as, on the one hand, it needs to embed topology into a soft adhesion layer, but on the

Fig. 3.6 Variation of measured thickness and thickness variation of different grinding tapes for ultra thin wafer processing (upper row) and resulting 50 µm wafer thickness uniformity (lower row)

Fig. 3.7 Three-point bending test method with relation between fracture stress and force (*left*) and bending of 75  $\mu$ m product sample (*right*)

other hand serve as a mechanical backbone of the ultra-thin wafer. The front end materials and design (metals, low and high k materials, multilayer metal stacks, etc.) do not only induce stress and cause wafer bow and warp, but also have a major influence on the mechanical robustness of ultra-thin wafers and chips. While the chip may be loaded with similar stresses on both sides in its final application, the ultra-thin wafer will be subjected to selective, high stress on either side (front/ back) depending on its position within the process flow.

Particles on a vacuum chuck table, for instance during the thinning process, may result in cross cracks, and put the backside of the wafer under tensile stress. Delamination of the grinding tape from the active wafer side also puts the wafer under a tensile stress that may cause edge breakage.

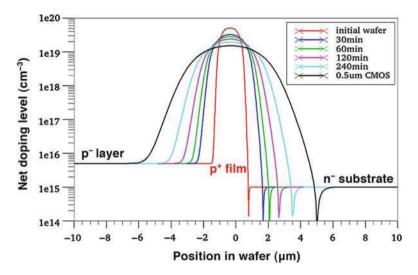

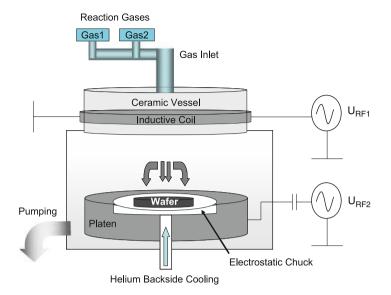

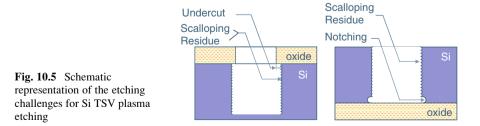

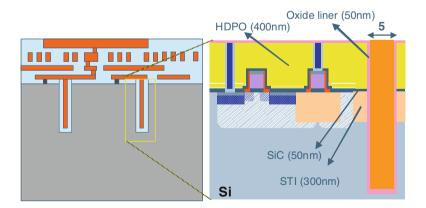

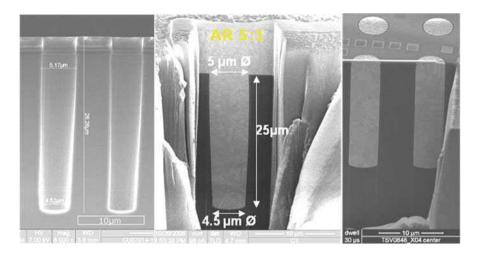

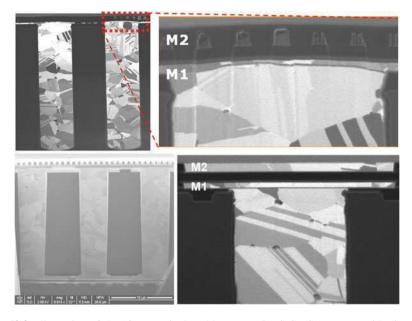

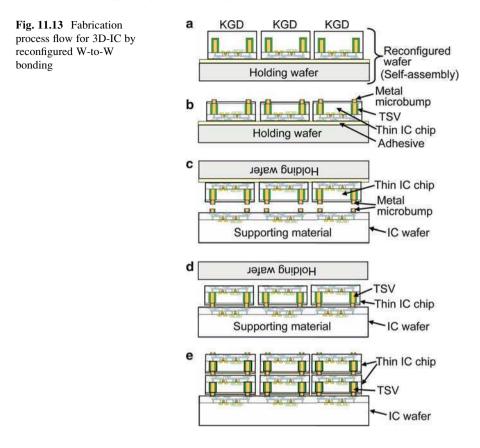

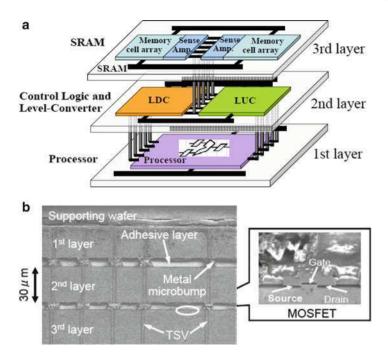

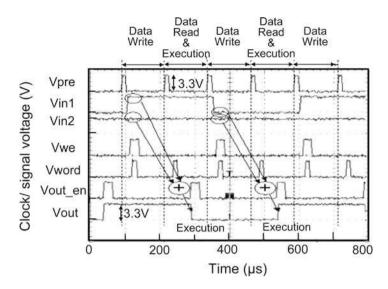

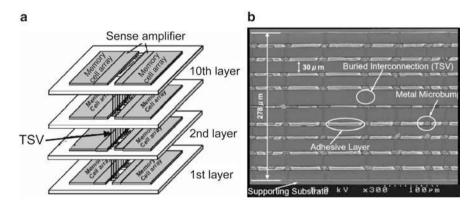

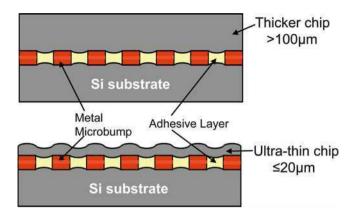

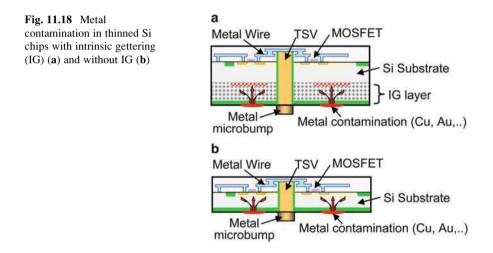

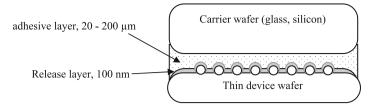

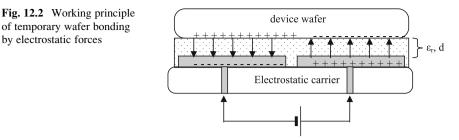

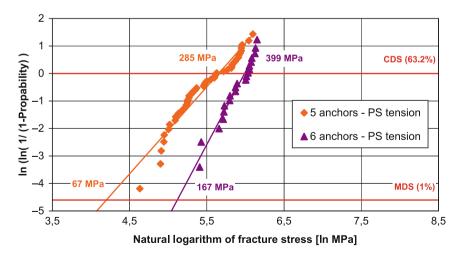

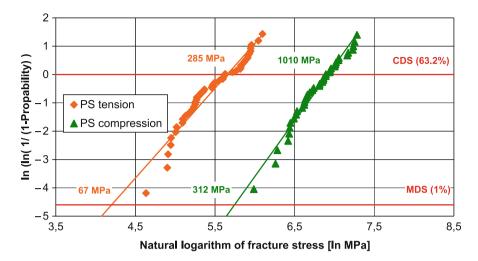

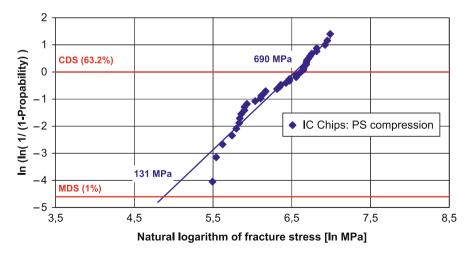

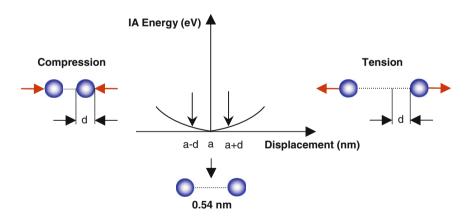

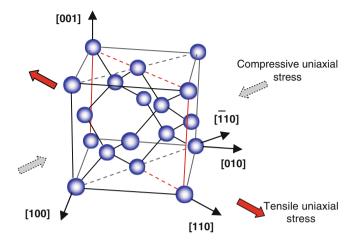

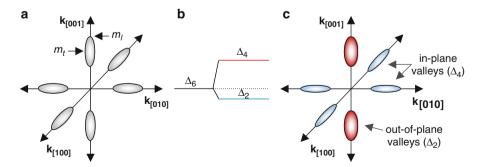

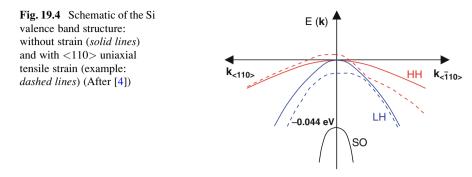

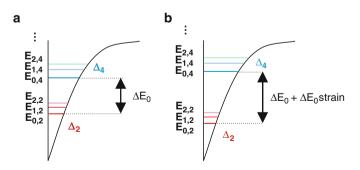

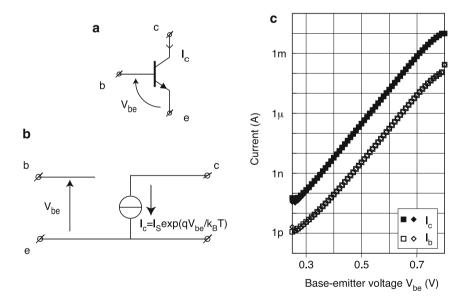

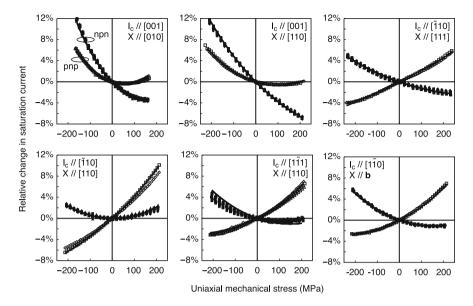

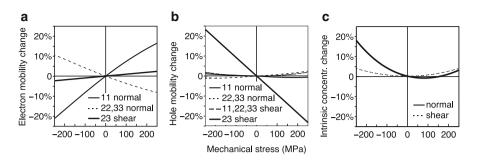

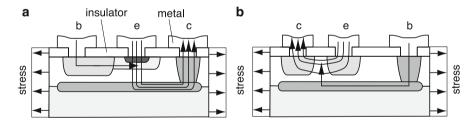

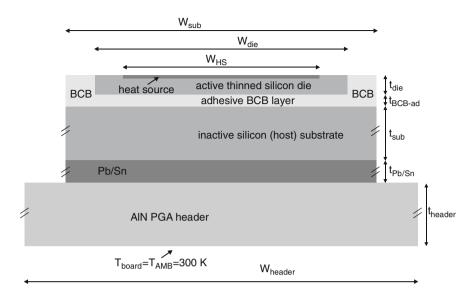

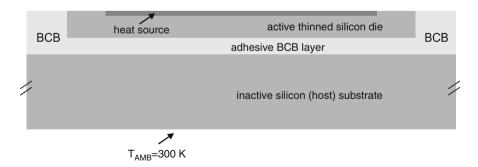

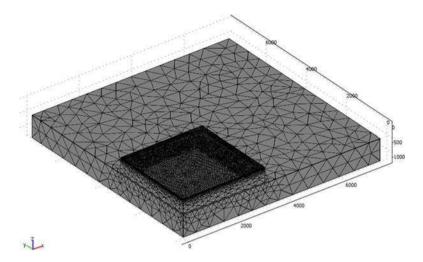

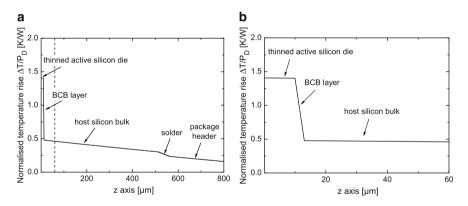

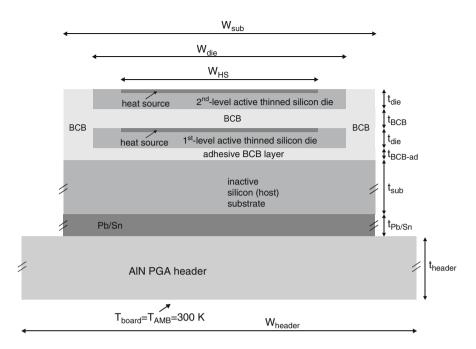

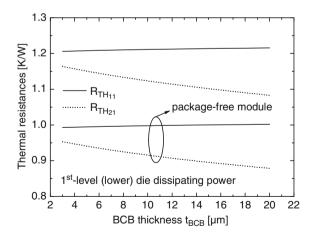

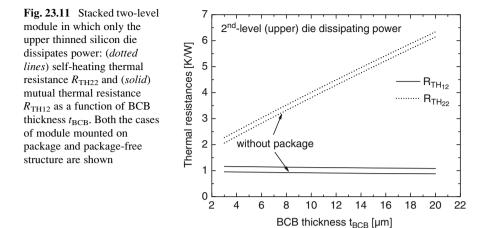

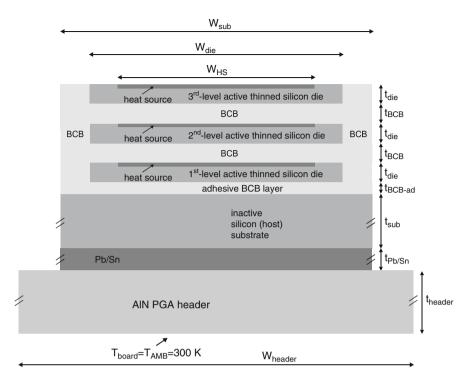

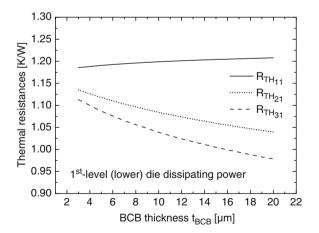

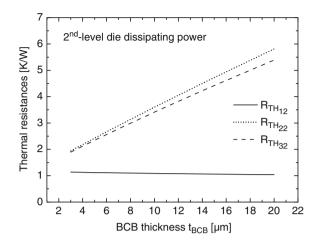

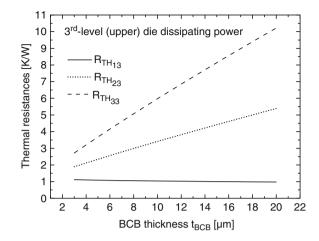

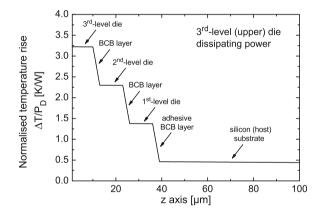

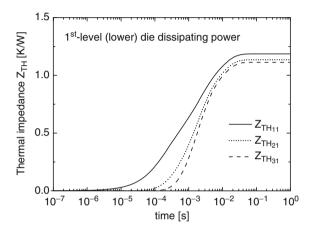

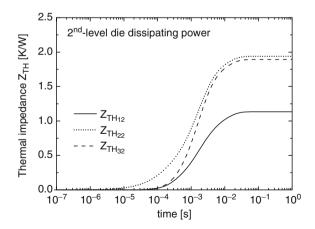

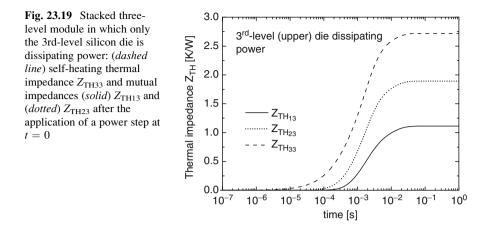

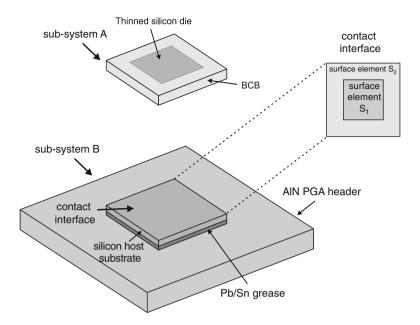

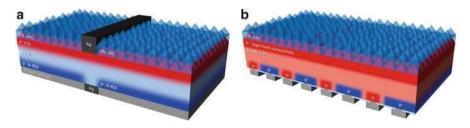

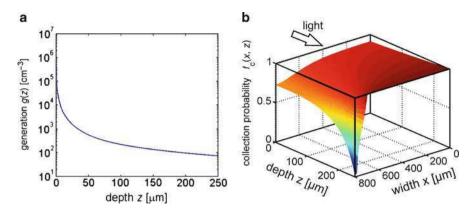

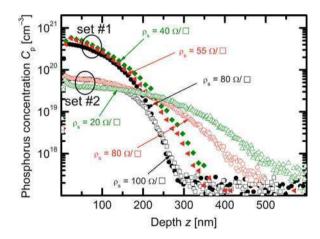

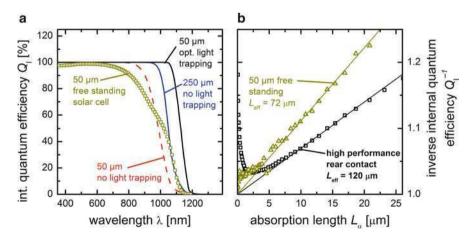

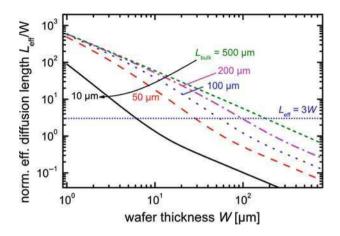

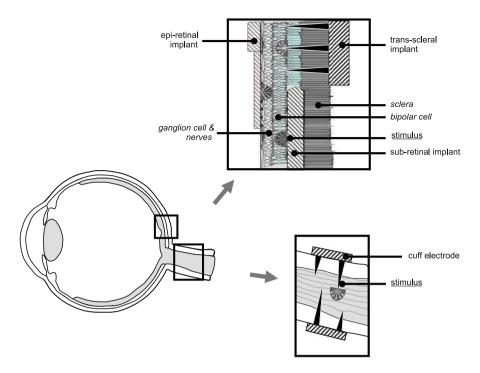

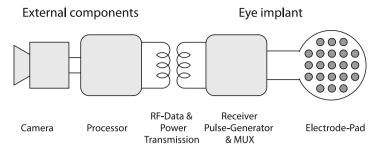

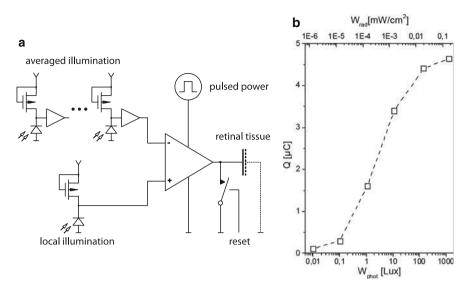

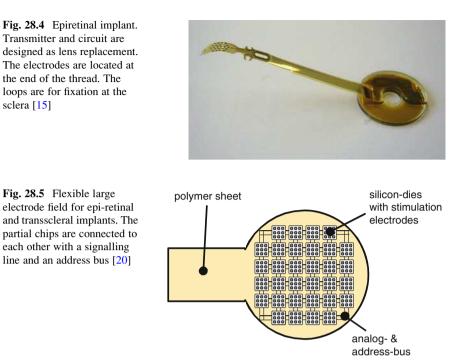

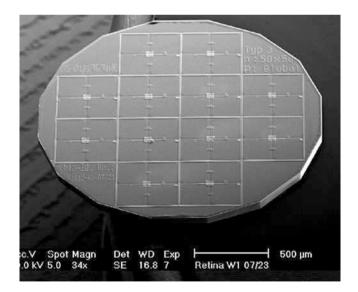

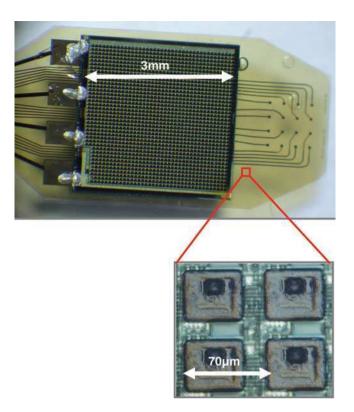

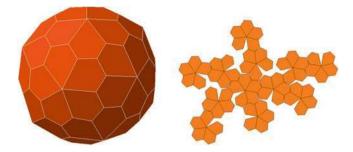

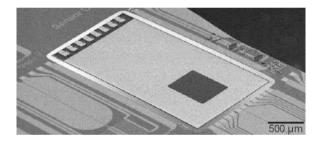

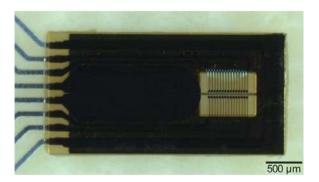

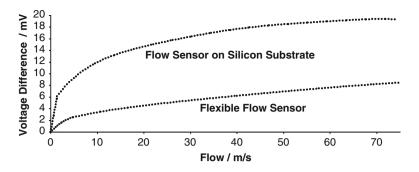

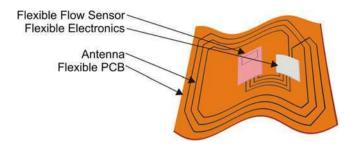

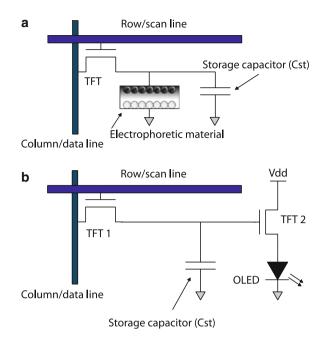

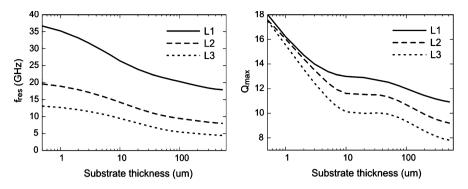

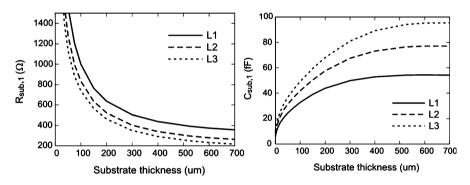

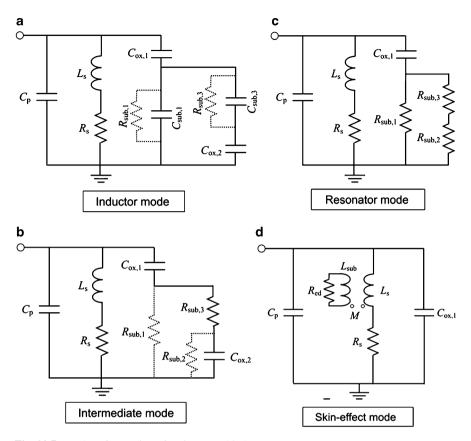

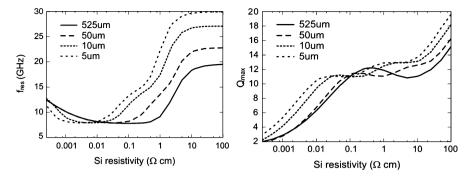

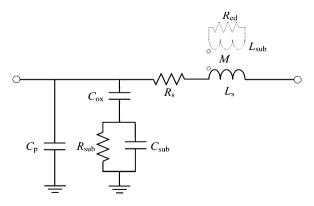

Particles on the wafer backside, however, that occur during subsequent process steps like wafer separation, put the wafer frontside under tensile stress. Consequently, the front end process needs to be optimised in order to achieve a similar robustness compared to the backside.