Sunil P. Khatri Kanupriya Gulati *Editors*

# Advanced Techniques in Logic Synthesis, Optimizations and Applications

Advanced Techniques in Logic Synthesis, Optimizations and Applications

Sunil P. Khatri · Kanupriya Gulati Editors

## Advanced Techniques in Logic Synthesis, Optimizations and Applications

*Editors* Sunil P. Khatri Department of ECE 333F WERC, MS 3259 Texas A&M University College Station, TX 77843-3259, USA sunilkhatri@tamu.edu

Kanupriya Gulati Intel Corporation 2501 NW 229th Ave Hillsboro, OR 97124, USA kanupriya.gulati@intel.com

ISBN 978-1-4419-7517-1 e-ISBN 978-1-4419-7518-8 DOI 10.1007/978-1-4419-7518-8 Springer New York Dordrecht Heidelberg London

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not

Printed on acid-free paper

they are subject to proprietary rights.

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

The last few decades have seen a stupendous growth in the speed and complexity of VLSI integrated circuits. This growth has been enabled by a powerful set of electronic design automation (EDA) tools. The earliest EDA tools were twolevel logic minimization and PLA folding tools. Subsequently, EDA tools were developed to address other aspects of the VLSI design flow (in addition to logic optimization) such as technology mapping, layout optimization, formal verification. However, research in logic synthesis and optimization continued to progress rapidly. Some of the research in logic synthesis tools saw broader application, to areas far removed from traditional EDA, and routinely continue to do so. While observing the recent developments and publications in logic synthesis and optimization, we felt that there was a need for a single resource which presents some recent significant developments in this area. This is how the idea of this edited monograph came about. We decided to cover some key papers in logic synthesis, optimization, and its applications, in an effort to provide an advanced practitioner a single reference source that covers the important papers in these areas over the last few years.

This monograph is organized into five sections, dealing with logic decomposition, Boolean satisfiability, Boolean matching, logic optimization, and applications of logic techniques to special design scenarios. Each of the chapters in any section is an expanded, archival version of the original paper by the chapter authors, with additional examples, results, and/or implementation details.

We dedicate this book to the area of logic synthesis and hope that it can stimulate new and exciting ideas which expand the contribution of logic synthesis to areas far beyond its traditional stronghold of VLSI integrated circuit design.

College Station, Texas Hillsboro, Oregon Sunil P. Khatri Kanupriya Gulati

| Intro | Introduction                                 |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

| Sunil | P. Khatri and Kanupriya Gulati               |  |  |  |  |  |  |

| 1.1   | Logic Decomposition                          |  |  |  |  |  |  |

| 1.2   | Boolean Satisfiability                       |  |  |  |  |  |  |

| 1.3   | Boolean Matching                             |  |  |  |  |  |  |

| 1.4   | Logic Optimization                           |  |  |  |  |  |  |

| 1.5   | Applications to Specialized Design Scenarios |  |  |  |  |  |  |

| Refe  | rences                                       |  |  |  |  |  |  |

## Part I Logic Decomposition

| 2 | Logi         | c Synthesis by Signal-Driven Decomposition                                                                                                                                                                                                                        | 9                                |

|---|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | Anna         | Bernasconi, Valentina Ciriani, Gabriella Trucco, and Tiziano Villa                                                                                                                                                                                                |                                  |

|   | 2.1          | Introduction                                                                                                                                                                                                                                                      | 9                                |

|   | 2.2          | Decomposition Methods                                                                                                                                                                                                                                             | 11                               |

|   | 2.3          | P-Circuits                                                                                                                                                                                                                                                        | 17                               |

|   |              | 2.3.1 Synthesis Algorithms                                                                                                                                                                                                                                        | 19                               |

|   | 2.4          | Multivariable Decomposition                                                                                                                                                                                                                                       | 21                               |

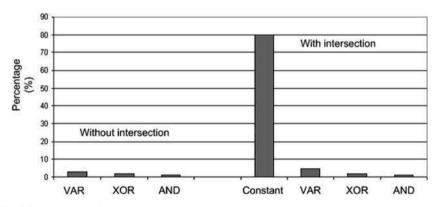

|   | 2.5          | Experimental Results                                                                                                                                                                                                                                              | 24                               |

|   | 2.6          | Conclusion                                                                                                                                                                                                                                                        | 28                               |

|   | Refe         | rences                                                                                                                                                                                                                                                            | 28                               |

|   |              |                                                                                                                                                                                                                                                                   |                                  |

| 3 | Sequ         | ontial Logic Synthesis Using Symbolic Pi decomposition                                                                                                                                                                                                            |                                  |

|   |              | ential Logic Synthesis Using Symbolic Bi-decomposition                                                                                                                                                                                                            | 31                               |

|   | Victo        | or N. Kravets and Alan Mishchenko                                                                                                                                                                                                                                 | 31                               |

|   | Victo<br>3.1 |                                                                                                                                                                                                                                                                   |                                  |

|   |              | r N. Kravets and Alan Mishchenko<br>Introduction and Motivation                                                                                                                                                                                                   | 31                               |

|   | 3.1          | r N. Kravets and Alan Mishchenko<br>Introduction and Motivation<br>Preliminary Constructs                                                                                                                                                                         | 31                               |

|   | 3.1          | or N. Kravets and Alan Mishchenko         Introduction and Motivation         Preliminary Constructs         3.2.1       "Less-Than-or-Equal" Relation                                                                                                            | 31<br>33                         |

|   | 3.1          | or N. Kravets and Alan Mishchenko         Introduction and Motivation         Preliminary Constructs         3.2.1       "Less-Than-or-Equal" Relation         3.2.2       Parameterized Abstraction                                                              | 31<br>33<br>33<br>34             |

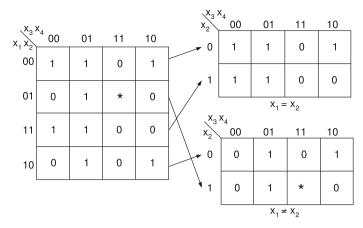

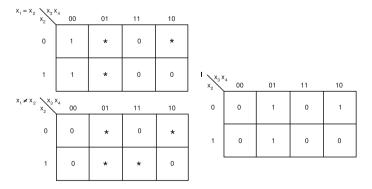

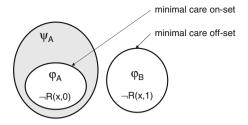

|   | 3.1<br>3.2   | or N. Kravets and Alan Mishchenko         Introduction and Motivation         Preliminary Constructs         3.2.1       "Less-Than-or-Equal" Relation         3.2.2       Parameterized Abstraction         Bi-decomposition of Incompletely Specified Functions | 31<br>33<br>33<br>34<br>35       |

|   | 3.1<br>3.2   | or N. Kravets and Alan Mishchenko         Introduction and Motivation         Preliminary Constructs         3.2.1 "Less-Than-or-Equal" Relation         3.2.2 Parameterized Abstraction         Bi-decomposition of Incompletely Specified Functions             | 31<br>33<br>33<br>34<br>35<br>35 |

|    | 3.4  | Parame   | eterized De | composition                                  | 37 |

|----|------|----------|-------------|----------------------------------------------|----|

|    |      | 3.4.1    |             | meterization                                 |    |

|    |      | 3.4.2    | XOR Par     | rameterization                               | 38 |

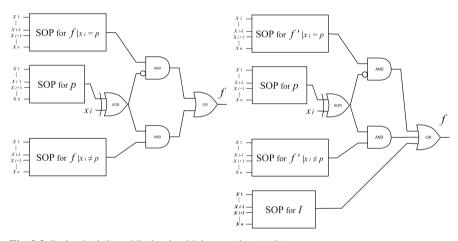

|    | 3.5  | Implen   | nentation D | Details of Sequential Synthesis              | 39 |

|    |      | 3.5.1    |             | on of Incompletely Specified Logic           | 39 |

|    |      | 3.5.2    |             | g Decomposition Choices                      | 40 |

|    |      | 3.5.3    |             | s Algorithm                                  | 41 |

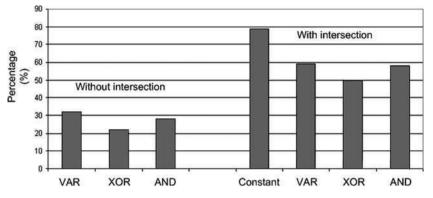

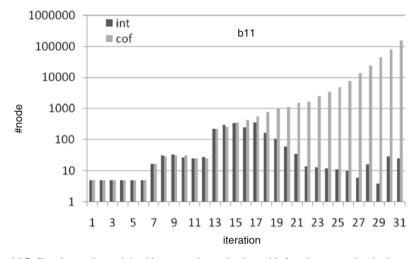

|    | 3.6  | Experi   |             | luation                                      | 42 |

|    | 3.7  |          |             | Future Work                                  | 44 |

|    |      |          |             |                                              | 45 |

| 4  | Bool | ean Fact | oring and   | Decomposition of Logic Networks              | 47 |

| Τ. |      |          | -           | ishchenko, and Satrajit Chatterjee           | 77 |

|    | 4.1  |          |             |                                              | 47 |

|    | 4.2  |          |             |                                              |    |

|    | 4.3  | _        |             | bint Decompositions                          |    |

|    | 4.4  |          |             | r networks                                   |    |

|    | 7.7  | 4.4.1    | -           | fiew                                         |    |

|    |      | 4.4.2    |             | putation                                     |    |

|    |      | 4.4.3    |             | h a DSD Structure                            |    |

|    |      | 4.4.4    |             | ght                                          |    |

|    |      | 4.4.5    |             | osition and Network Update                   |    |

|    |      | 4.4.6    |             | the Maximum Support-Reducing                 | 57 |

|    |      | 7.7.0    | •           | osition                                      | 58 |

|    |      | 4.4.7    | -           | al Details                                   | 60 |

|    |      | 1.1.7    | 4.4.7.1     | Using Timing Information to Filter Candidate | 00 |

|    |      |          | 1.1.7.1     | Bound Sets                                   | 60 |

|    |      |          | 4.4.7.2     | Restricting Bound Sets for Balanced          | 00 |

|    |      |          | 1.1.7.2     | Decompositions                               | 60 |

|    |      |          | 4.4.7.3     | Opportunistic MUX-Decomposition              | 60 |

|    | 4.5  | Compa    |             | Boolean Matching                             | 61 |

|    | 4.6  | -        |             | ults                                         | 62 |

|    | 4.7  |          |             | Future Work                                  | 64 |

|    |      |          |             |                                              |    |

| _  |      |          |             |                                              |    |

| 5  |      |          |             | tion Using SAT                               | (7 |

|    |      |          |             |                                              | 6/ |

|    |      |          |             | Roland Jiang, and Ruei-Rung Lee              |    |

|    | 5.1  |          |             | ••••••                                       | 67 |

|    | 5.2  |          |             | ••••••                                       | 69 |

|    | 5.3  |          |             |                                              | 69 |

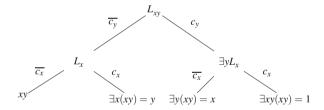

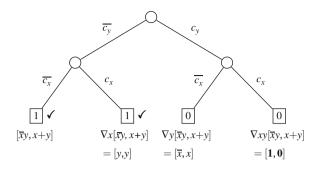

|    |      | 5.3.1    |             | al Decomposition                             | 70 |

|    |      | 5.3.2    |             | al Dependency                                | 71 |

|    |      | 5.3.3    |             | onal Satisfiability and Interpolation        | 71 |

|    |      |          | 5.3.3.1     | Refutation Proof and Craig Interpolation     | 71 |

|   |       |         | 5.3.3.2     | Circuit-to-CNF Conversion                    | 72 |

|---|-------|---------|-------------|----------------------------------------------|----|

|   | 5.4   | Main A  | lgorithms   |                                              | 72 |

|   |       | 5.4.1   | Single-O    | utput Ashenhurst Decomposition               | 72 |

|   |       |         | 5.4.1.1     | Decomposition with Known Variable Partition. | 72 |

|   |       |         | 5.4.1.2     | Decomposition with Unknown Variable          |    |

|   |       |         |             | Partition                                    | 75 |

|   |       | 5.4.2   | Multiple    | -Output Ashenhurst Decomposition             | 79 |

|   |       | 5.4.3   | Beyond A    | Ashenhurst Decomposition                     | 80 |

|   | 5.5   | Experir | nental Res  | ults                                         | 80 |

|   | 5.6   | Chapter | r Summary   | ·                                            | 84 |

|   | Refer | ences   |             |                                              | 84 |

|   |       |         |             |                                              |    |

| 6 | Ri-de | composi | ition Using | g SAT and Interpolation                      | 87 |

| v |       |         |             | g Roland Jiang, and Wei-Lun Hung             | 07 |

|   | 6.1   | -       |             |                                              | 87 |

|   | 6.2   |         |             |                                              | 88 |

|   | 6.3   |         |             |                                              | 89 |

|   | 0.5   | 6.3.1   |             | mposition                                    | 89 |

|   |       | 6.3.2   |             | onal Satisfiability                          | 90 |

|   |       | 0.5.2   | 6.3.2.1     | Refutation Proof and Craig Interpolation     | 90 |

|   |       | 6.3.3   |             | CNF Conversion                               | 91 |

|   | 6.4   |         |             |                                              | 91 |

|   | 0.1   | 6.4.1   |             | ecomposition                                 | 91 |

|   |       | 0.1.1   | 6.4.1.1     | Decomposition of Completely Specified        | 1  |

|   |       |         |             | Functions                                    | 91 |

|   |       |         | 6.4.1.2     | Decomposition of Incompletely Specified      |    |

|   |       |         |             | Functions                                    | 97 |

|   |       | 6.4.2   | AND Bi-     | decomposition                                | 97 |

|   |       | 6.4.3   |             | decomposition                                | 98 |

|   |       | 01110   | 6.4.3.1     | Decomposition of Completely Specified        | 10 |

|   |       |         | 0111011     | Functions                                    | 98 |

|   |       | 6.4.4   | Impleme     | ntation Issues                               |    |

|   | 6.5   |         | · ·         | ults                                         |    |

|   | 6.6   | -       |             |                                              |    |

|   |       |         | •           |                                              |    |

|   |       |         |             |                                              |    |

## Part II Boolean Satisfiability

| 7 | Boundary Points and Resolution |                                     |   |  |  |

|---|--------------------------------|-------------------------------------|---|--|--|

|   | Euger                          | ne Goldberg and Panagiotis Manolios |   |  |  |

|   | 7.1                            | Introduction                        | 9 |  |  |

|   | 7.2                            | Basic Definitions                   | 1 |  |  |

|   | 7.3                            | Properties                          | 2 |  |  |

|   |      | 7.3.1   | Basic Propositions                                   | 112   |

|---|------|---------|------------------------------------------------------|-------|

|   |      | 7.3.2   | Elimination of Boundary Points by Adding Resolvents. | 113   |

|   |      | 7.3.3   | Boundary Points and Redundant Formulas               | 115   |

|   | 7.4  | Resolu  | tion Proofs and Boundary Points                      | 115   |

|   |      | 7.4.1   | Resolution Proof as Boundary Point Elimination       | 116   |

|   |      | 7.4.2   | SMR Metric and Proof Quality                         |       |

|   | 7.5  | Equiva  | lence Checking Formulas                              |       |

|   |      | 7.5.1   | Building Equivalence Checking Formulas               |       |

|   |      | 7.5.2   | Short Proofs for Equivalence Checking Formulas       |       |

|   | 7.6  | Experii | mental Results                                       |       |

|   | 7.7  | -       | Background                                           |       |

|   | 7.8  |         | eteness of Resolution Restricted to Boundary Point   |       |

|   |      |         | ation                                                | 123   |

|   |      | 7.8.1   | Cut Boundary Points                                  |       |

|   |      | 7.8.2   | The Completeness Result                              |       |

|   |      | 7.8.3   | Boundary Points as Complexity Measure                |       |

|   | 7.9  |         | sions and Directions for Future Research             |       |

|   |      |         |                                                      |       |

|   | Refe | iences  |                                                      | 120   |

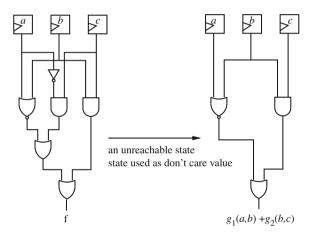

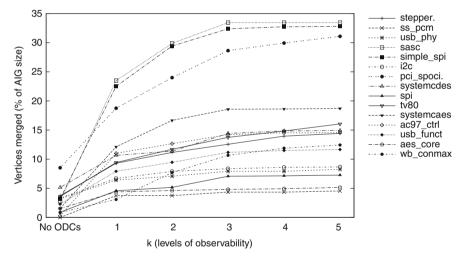

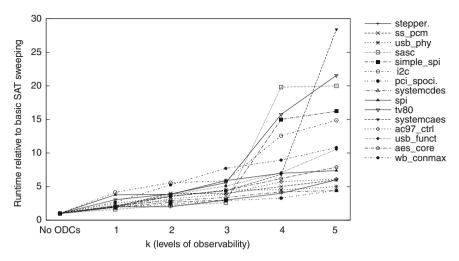

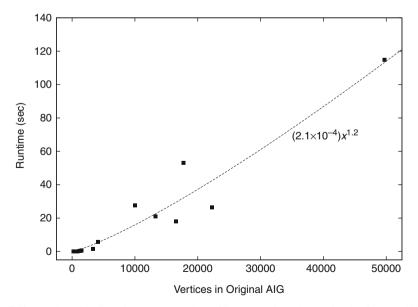

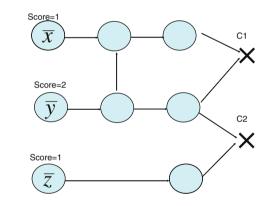

| 8 | SAT  | Sweepin | ng with Local Observability Don't-Cares              | . 129 |

|   |      |         | an B. Kitchen, Andreas Kuehlmann, and Alberto        |       |

|   | _    |         | Vincentelli                                          |       |

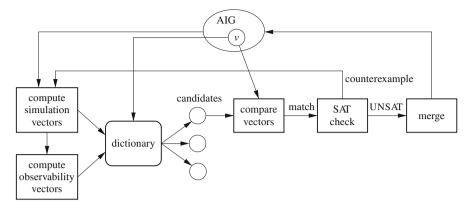

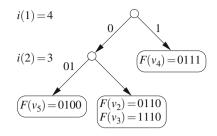

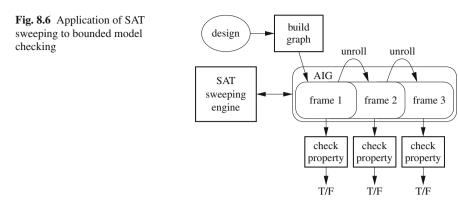

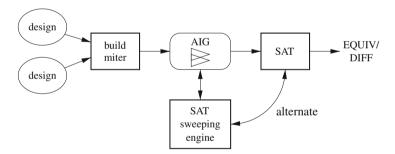

|   | 8.1  |         | iction                                               | 129   |

|   | 8.2  |         | us Work                                              |       |

|   | 8.3  |         | inaries                                              |       |

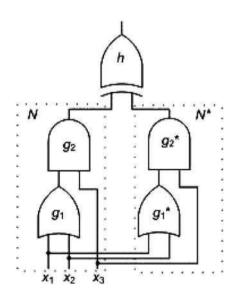

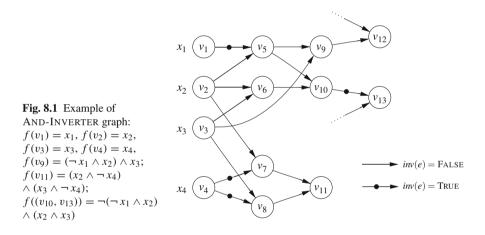

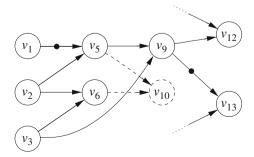

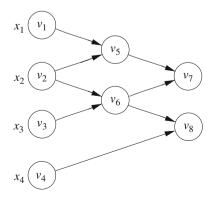

|   |      | 8.3.1   | AND-INVERTER Graphs                                  |       |

|   |      | 8.3.2   | SAT Sweeping                                         |       |

|   | 8.4  |         | weeping with Observability Don't Cares               |       |

|   |      | 8.4.1   | Motivating Example                                   |       |

|   |      | 8.4.2   | Observability Don't Cares                            |       |

|   |      | 8.4.3   | Algorithm                                            |       |

|   |      | 8.4.4   | Implementation                                       |       |

|   |      | 8.4.5   | Applications                                         |       |

|   | 8.5  |         | 6                                                    |       |

|   | 8.6  |         | isions                                               |       |

|   |      |         |                                                      |       |

|   | nere | iences  |                                                      |       |

| 9 | A Fa | st Appr | oximation Algorithm for MIN-ONE SAT and Its          |       |

|   |      |         | on MAX-SAT Solving                                   | 149   |

|   |      |         | Michael S. Hsiao                                     |       |

|   | 9.1  |         | iction                                               | 149   |

|   | 9.2  |         | inaries                                              |       |

|   | 9.3  |         | pproach                                              |       |

|   |      | 9.3.1   | RelaxSAT                                             |       |

|   |      | 9.3.2   | Relaxation Heuristic                                 |       |

|   |      |         |                                                      |       |

|    |       | 9.3.3 Discussion on Computation Complexity                      |

|----|-------|-----------------------------------------------------------------|

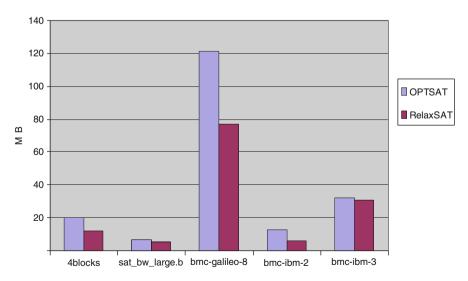

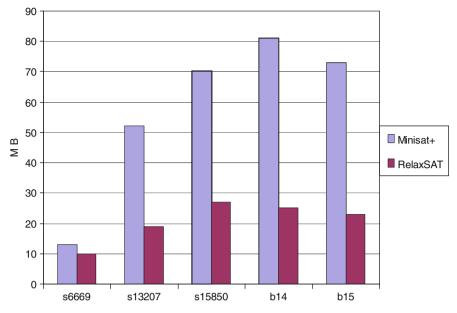

|    | 9.4   | Experimental Results                                            |

|    | 9.5   | Application Discussion: A RelaxSAT-Based MAX-SAT Solver 161     |

|    |       | 9.5.1 The New MAX-SAT Solver: RMAXSAT                           |

|    |       | 9.5.2 Evaluation of MAX-SAT Solver                              |

|    | 9.6   | Conclusions and Future Works                                    |

|    | Refer | ences                                                           |

|    |       |                                                                 |

| 10 | Algo  | rithms for Maximum Satisfiability Using Unsatisfiable Cores 171 |

|    | Joao  | Marques-Sila and Jordi Planes                                   |

|    | 10.1  | Introduction                                                    |

|    | 10.2  | Background                                                      |

|    |       | 10.2.1 The MaxSAT Problem                                       |

|    |       | 10.2.2 Solving MaxSAT with PBO 173                              |

|    |       | 10.2.3 Relating MaxSAT with Unsatisfiable Cores                 |

|    | 10.3  | A New MaxSAT Algorithm                                          |

|    |       | 10.3.1 Overview                                                 |

|    |       | 10.3.2 The Algorithm                                            |

|    |       | 10.3.3 A Complete Example                                       |

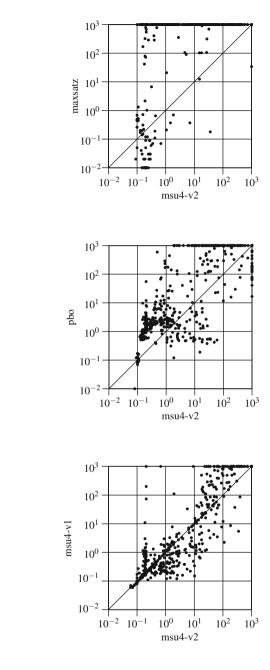

|    | 10.4  | Experimental Results                                            |

|    | 10.5  | Related Work                                                    |

10.6

Conclusions

180

References

181

## Part III Boolean Matching

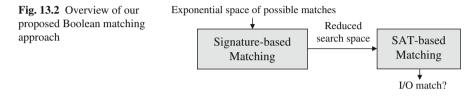

| 11 |       |          | d SAT-Based Boolean Matching for Large Boolear |     |

|----|-------|----------|------------------------------------------------|-----|

|    | Netw  | orks     |                                                | 185 |

|    | Kuo-l | Hua Wan  | g, Chung-Ming Chan, and Jung-Chang Liu         |     |

|    | 11.1  | Introduc | ction                                          | 185 |

|    | 11.2  | Backgro  | ound                                           | 186 |

|    |       | 11.2.1   | Boolean Matching                               | 186 |

|    |       | 11.2.2   | Boolean Satisfiability                         |     |

|    |       | 11.2.3   | And-Inverter Graph                             | 187 |

|    | 11.3  |          | on of Functional Property Using S&S Approach   |     |

|    | 11.4  | Definiti | ons and Notations                              | 189 |

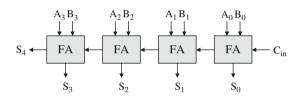

|    | 11.5  | Simulat  | ion Approach for Distinguishing Inputs         | 190 |

|    |       | 11.5.1   | Туре-1                                         | 191 |

|    |       |          | Туре-2                                         |     |

|    |       | 11.5.3   | Type-3                                         |     |

|    | 11.6  | S&S-Ba   | sed Boolean Matching Algorithm                 |     |

|    |       | 11.6.1   | Our Matching Algorithm                         |     |

|    |       | 11.6.2   | Recursive-Matching Algorithm                   |     |

|    |       |          |                                                |     |

|       | 11.6.3  | Implementation Issues |                                          |     |  |

|-------|---------|-----------------------|------------------------------------------|-----|--|

|       |         | 11.6.3.1              | Control of Random Vector Generation      | 196 |  |

|       |         | 11.6.3.2              | Reduction of Simulation Time             | 196 |  |

|       |         | 11.6.3.3              | Analysis of Space Complexity and Runtime | 196 |  |

| 11.7  | Experin | nental Resu           | ılts                                     | 197 |  |

| 11.8  | Chapter | Summary               |                                          | 200 |  |

| Refer | ences   |                       |                                          | 200 |  |

| Smita | a Krishnaswamy, Haoxing Ren, Nilesh Modi, and Ruchir Puri |     |

|-------|-----------------------------------------------------------|-----|

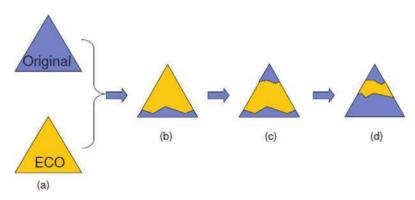

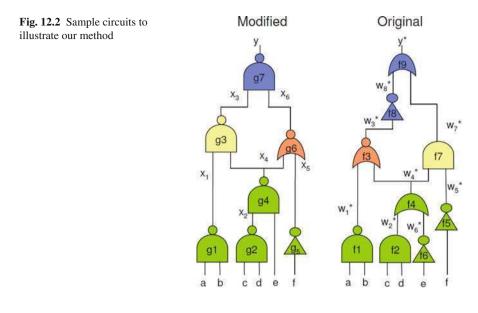

| 12.1  | Introduction and Background                               | 203 |

| 12.2  | Previous Work                                             |     |

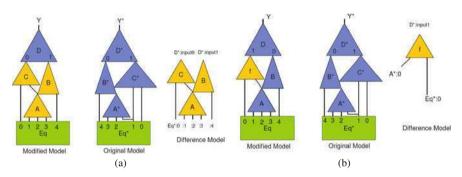

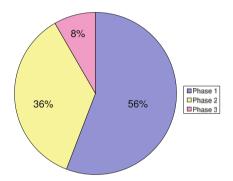

| 12.3  | DeltaSyn                                                  | 206 |

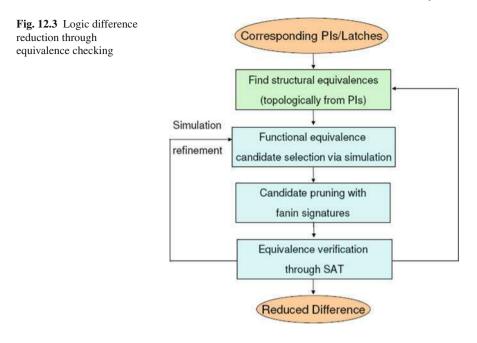

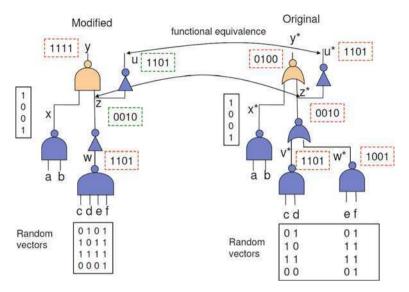

|       | 12.3.1 Phase I: Equivalence-Based Reduction               |     |

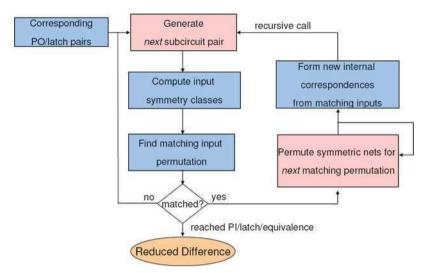

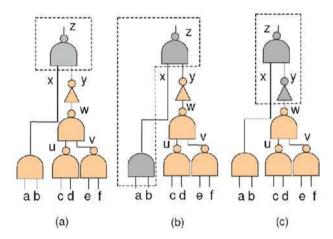

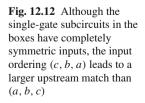

|       | 12.3.2 Phase II: Matching-Based Reduction                 | 209 |

|       | 12.3.2.1 Subcircuit Enumeration                           | 210 |

|       | 12.3.2.2 Subcircuit Matching                              | 213 |

|       | 12.3.2.3 Subcircuit Covering                              |     |

|       | 12.3.3 Phase III: Functional Hashing-Based Reduction      |     |

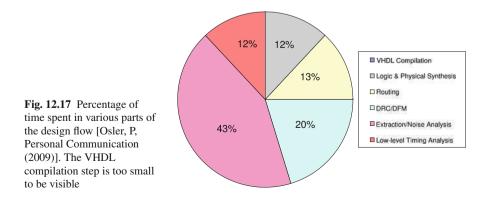

| 12.4  | Empirical Validation                                      | 220 |

| 12.5  | Chapter Summary                                           | 224 |

| Refe  | rences                                                    |     |

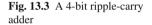

| 13 | Larg | e-Scale H      | Boolean Matching                                | 227 |

|----|------|----------------|-------------------------------------------------|-----|

|    | Hadi | nd Igor Markov |                                                 |     |

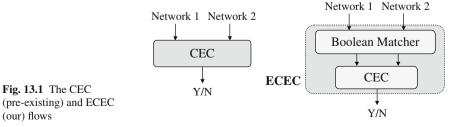

|    | 13.1 | Introdu        | ction                                           | 227 |

|    | 13.2 | Backgro        | ound and Previous Work                          | 229 |

|    |      | 13.2.1         | Definitions and Notation                        |     |

|    |      | 13.2.2         | And-Inverter Graphs (AIGs)                      | 230 |

|    |      | 13.2.3         | Boolean Satisfiability and Equivalence Checking | 231 |

|    |      | 13.2.4         | Previous Work                                   | 231 |

|    | 13.3 | Signatu        | re-Based Matching Techniques                    | 232 |

|    |      | 13.3.1         | Computing I/O Support Variables                 | 232 |

|    |      | 13.3.2         | Initial refinement of I/O clusters              |     |

|    |      | 13.3.3         | Refining Outputs by Minterm Count               | 234 |

|    |      | 13.3.4         | Refining I/O by Unateness                       |     |

|    |      | 13.3.5         | Scalable I/O Refinement by Dependency Analysis  |     |

|    |      | 13.3.6         | Scalable I/O Refinement by Random Simulation    | 235 |

|    |      |                | 13.3.6.1 Simulation Type 1                      |     |

|    |      |                | 13.3.6.2 Simulation Type 2                      |     |

|    |      |                | 13.3.6.3 Simulation Type 3                      | 237 |

|    | 13.4 | SAT-Ba         | ised Search                                     |     |

|    |      | 13.4.1         | SAT-Based Input Matching                        | 238 |

|    |      |                | · · ·                                           |     |

|       | 13.4.2  | Pruning Invalid Input Matches by SAT                   |     |

|-------|---------|--------------------------------------------------------|-----|

|       |         | Counterexamples                                        | 239 |

|       | 13.4.3  | SAT-Based Output Matching                              | 240 |

|       | 13.4.4  | Pruning Invalid Output Matches by SAT Counterexamples  | 241 |

|       | 13.4.5  | Pruning Invalid I/O Matches Using Support Signatures 2 | 241 |

|       | 13.4.6  | Pruning Invalid Input Matches Using Symmetries         | 241 |

|       | 13.4.7  | A Heuristic for Matching Candidates                    | 242 |

| 13.5  | Empiric | al Validation                                          | 242 |

| 13.6  | Chapter | Summary                                                | 246 |

| Refer | ences   |                                                        | 246 |

## Part IV Logic Optimization

| 14 | Algel                           | Algebraic Techniques to Enhance Common Sub-expression                                                                                                                                                                                                                                                                                                                                                      |                                              |  |  |  |

|----|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|

|    | Extra                           | ction for Polynomial System Synthesis                                                                                                                                                                                                                                                                                                                                                                      | 251                                          |  |  |  |

|    | Sivar                           | Sivaram Gopalakrishnan and Priyank Kalla                                                                                                                                                                                                                                                                                                                                                                   |                                              |  |  |  |

|    | 14.1                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                               | 251                                          |  |  |  |

|    |                                 | 14.1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                          | 252                                          |  |  |  |

|    |                                 | 14.1.2 Contributions                                                                                                                                                                                                                                                                                                                                                                                       | 253                                          |  |  |  |

|    |                                 | 14.1.3 Paper Organization                                                                                                                                                                                                                                                                                                                                                                                  | 253                                          |  |  |  |

|    | 14.2                            | Previous Work                                                                                                                                                                                                                                                                                                                                                                                              |                                              |  |  |  |

|    |                                 | 14.2.1 Kernel/Co-kernel Extraction                                                                                                                                                                                                                                                                                                                                                                         | 254                                          |  |  |  |

|    | 14.3                            | Preliminary Concepts                                                                                                                                                                                                                                                                                                                                                                                       | 255                                          |  |  |  |

|    |                                 | 14.3.1 Polynomial Functions and Their Canonical                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    |                                 | Representations                                                                                                                                                                                                                                                                                                                                                                                            | 255                                          |  |  |  |

|    |                                 | 14.3.2 Factorization                                                                                                                                                                                                                                                                                                                                                                                       |                                              |  |  |  |

|    | 14.4                            | Optimization Methods                                                                                                                                                                                                                                                                                                                                                                                       | 257                                          |  |  |  |

|    |                                 | 14.4.1 Common Coefficient Extraction                                                                                                                                                                                                                                                                                                                                                                       |                                              |  |  |  |

|    |                                 | 14.4.2 Common Cube Extraction                                                                                                                                                                                                                                                                                                                                                                              | 259                                          |  |  |  |

|    |                                 | 14.4.3 Algebraic Division                                                                                                                                                                                                                                                                                                                                                                                  |                                              |  |  |  |

|    | 14.5                            |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    | 14.6                            |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    | 14.7                            | 1                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |  |  |  |

|    | Refer                           |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    |                                 |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

| 15 | Auto                            | mated Logic Restructuring with aSPFDs                                                                                                                                                                                                                                                                                                                                                                      | 267                                          |  |  |  |

| 10 |                                 |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    |                                 |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    |                                 |                                                                                                                                                                                                                                                                                                                                                                                                            | 267                                          |  |  |  |

|    |                                 |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    | 15.2                            |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    |                                 |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    | 153                             |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

|    | 15.5                            |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |  |  |  |

| 15 | Refer<br>Auto<br>Yu-Sl<br>and D | ences         mated Logic Restructuring with aSPFDs         nen Yang, Subarna Sinha, Andreas Veneris, Robert Brayton,         ouncan Smith         Introduction         Background         15.2.1       Prior Work on Logic Restructuring         15.2.2       Sets of Pairs of Functions to Be Distinguished         Approximating SPFDs         15.3.1       Computing aSPFDs for Combinational Circuits | 26<br>26<br>26<br>26<br>26<br>26<br>26<br>26 |  |  |  |

|    |       | 15.3.2   | Computing <i>a</i> SPFDs for Sequential Circuits27     |   |

|----|-------|----------|--------------------------------------------------------|---|

|    |       | 15.3.3   | Optimizing <i>a</i> SPFDs with Don't Cares             |   |

|    |       |          | 15.3.3.1 Conflicts in Multiple Expected Traces 27      |   |

|    | 15.4  | •        | ransformations with <i>a</i> SPFDs27                   |   |

|    |       | 15.4.1   | SAT-Based Searching Algorithm                          |   |

|    |       | 15.4.2   | Greedy Searching Algorithm                             |   |

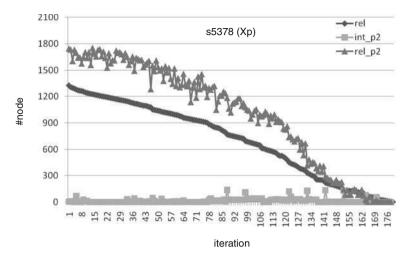

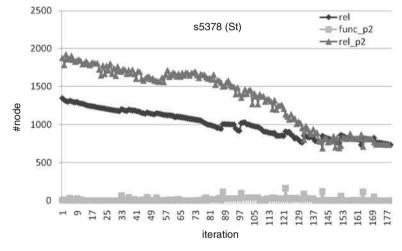

|    | 15.5  |          | nental Results                                         |   |

|    |       | 15.5.1   | Logic Restructuring of Combinational Designs           |   |

|    |       | 15.5.2   |                                                        |   |

|    | 15.6  |          | ry                                                     |   |

|    | Refer | ences    |                                                        | 5 |

|    |       |          |                                                        |   |

| 16 |       |          | inctions from Boolean Relations Using SAT              |   |

|    |       |          | tion                                                   | 7 |

|    |       | <u> </u> | nd Jiang, Hsuan-Po Lin, and Wei-Lun Hung               | _ |

|    | 16.1  |          | 28                                                     |   |

|    | 16.2  |          | s Work                                                 |   |

|    | 16.3  |          | naries                                                 |   |

|    |       | 16.3.1   |                                                        |   |

|    |       | 16.3.2   | Satisfiability and Interpolation                       |   |

|    | 16.4  |          | proach                                                 |   |

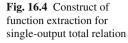

|    |       | 16.4.1   | Single-Output Relation                                 |   |

|    |       |          | 16.4.1.1 Total Relation                                |   |

|    |       |          | 16.4.1.2 Partial Relation                              |   |

|    |       | 16.4.2   | Multiple Output Relation                               |   |

|    |       |          | 16.4.2.1 Determinization via Expansion Reduction 29    |   |

|    |       |          | 16.4.2.2 Determinization via Substitution Reduction 29 |   |

|    |       | 16.4.3   | Deterministic Relation                                 |   |

|    |       | 16.4.4   | Function Simplification                                |   |

|    |       |          | 16.4.4.1 Support Minimization                          |   |

|    |       |          | 16.4.4.2 Determinization Scheduling                    |   |

|    | 16.5  |          | nental Results                                         |   |

|    | 16.6  | -        | Summary                                                |   |

|    | Refer | rences   |                                                        | 6 |

|    |       |          |                                                        |   |

| 17 | A Ro  | bust Wi  | ndow-Based Multi-node Minimization Technique           |   |

|    |       |          | n Relations                                            | 9 |

|    |       |          | Kanupriya Gulati, and Sunil P. Khatri                  |   |

|    | 17.1  |          | ction                                                  | 9 |

| 17.2 | Problem Definition                     | 311 |

|------|----------------------------------------|-----|

| 17.3 | Previous Work                          | 312 |

| 17.4 | Preliminaries and Definitions          | 314 |

|      | 17.4.1 BREL Boolean Relation Minimizer | 316 |

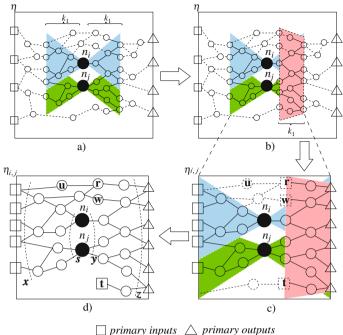

| 17.5  | Approa  | ch          |                                                   |

|-------|---------|-------------|---------------------------------------------------|

|       | 17.5.1  | Algorithm   | n Details                                         |

|       |         | 17.5.1.1    | Selecting Node Pairs                              |

|       |         | 17.5.1.2    | Building the Subnetwork                           |

|       |         | 17.5.1.3    | Computing the Boolean Relation $\mathcal{R}^Y$    |

|       |         | 17.5.1.4    | Quantification Scheduling 322                     |

|       |         | 17.5.1.5    | Endgame                                           |

| 17.6  | Experin | nental Resu | ılts                                              |

|       | 17.6.1  | Preproces   | sing Steps 325                                    |

|       | 17.6.2  | Parameter   | selection                                         |

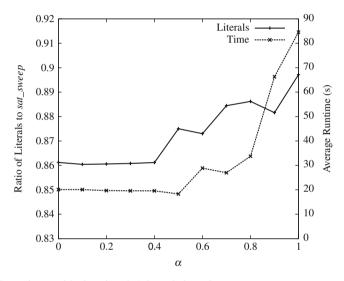

|       |         | 17.6.2.1    | Selecting $\alpha$                                |

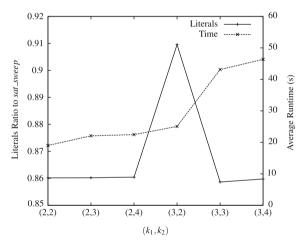

|       |         | 17.6.2.2    | Selecting $k_1$ and $k_2$                         |

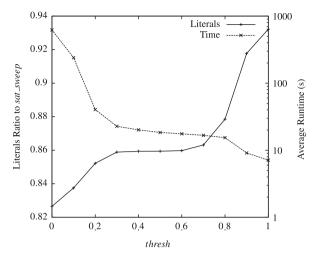

|       |         | 17.6.2.3    | Selecting thresh                                  |

|       | 17.6.3  | Comparis    | on of the Proposed Technique with <i>mfsw</i> 328 |

|       | 17.6.4  | Additiona   | ll Experiments                                    |

|       |         | 17.6.4.1    | Running relation After mfsw                       |

|       |         | 17.6.4.2    | Running relation Twice                            |

|       |         | 17.6.4.3    | Minimizing Single Nodes 331                       |

|       |         | 17.6.4.4    | Effects of Early Quantification                   |

| 17.7  |         |             |                                                   |

| Refer | ences   |             |                                                   |

## Part V Applications to Specialized Design Scenarios

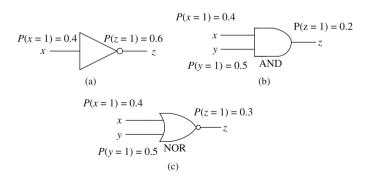

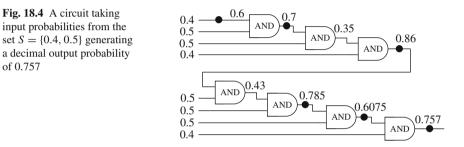

| Synthesizing Combinational Logic to Generate Probabilities:<br>Theories and Algorithms |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                        |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 18.1                                                                                   |                                                                                | ;7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 18.2                                                                                   | e                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 18.3                                                                                   |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                        |                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

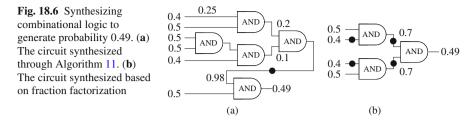

|                                                                                        | 18.3.1 Generating Decimal Probabilities from the Input                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                        | Probability Set $S = \{0.4, 0.5\}$                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                                                                        | 18.3.2 Generating Decimal Probabilities from the Input                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                        | Probability Set $S = \{0.5, 0.8\}$                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 18.4                                                                                   |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                        | Probabilities                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 18.5                                                                                   | Implementation                                                                 | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

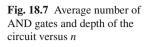

| 18.6                                                                                   | * · · · · · · · · · · · · · · · · · · ·                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 18.7                                                                                   | •                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Refer                                                                                  |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                        | Theor<br>Weika<br>18.1<br>18.2<br>18.3<br>18.4<br>18.4<br>18.5<br>18.6<br>18.7 | Theories and Algorithms33Weikang Qian, Marc D. Riedel, Kia Bazargan, and David J. Lilja3318.1Introduction and Background3318.2Related Work3418.3Sets with Two Elements that Can Generate Arbitrary Decimal<br>Probabilities3418.3.1Generating Decimal Probabilities from the Input<br>Probability Set $S = \{0.4, 0.5\}$ 3418.3.2Generating Decimal Probabilities from the Input<br>Probability Set $S = \{0.5, 0.8\}$ 3418.4Sets with a Single Element that Can Generate Arbitrary Decimal<br>Probabilities3418.5Implementation3518.6Empirical Validation35 |  |

| 19 | <b>Probabilistic Error Propagation in a Logic Circuit Using</b><br><b>the Boolean Difference Calculus</b> |          |              |                                       |     |  |

|----|-----------------------------------------------------------------------------------------------------------|----------|--------------|---------------------------------------|-----|--|

|    | Nasir                                                                                                     |          |              | Pakbaznia, and Massoud Pedram         |     |  |

|    | 19.1                                                                                                      |          | 359          |                                       |     |  |

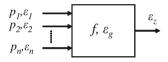

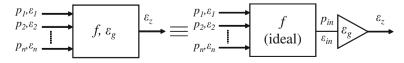

|    | 19.2                                                                                                      | Error Pr | ropagation   | Using Boolean Difference Calculus     | 361 |  |

|    |                                                                                                           | 19.2.1   | Partial Bo   | oolean Difference                     | 361 |  |

|    |                                                                                                           | 19.2.2   | Total Boo    | blean Difference                      | 362 |  |

|    |                                                                                                           | 19.2.3   | Signal and   | d Error Probabilities                 | 363 |  |

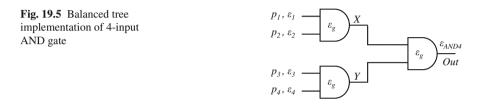

|    | 19.3                                                                                                      | Propose  | ed Error Pro | opagation Model                       | 364 |  |

|    |                                                                                                           | 19.3.1   | Gate Erro    | or Model                              | 364 |  |

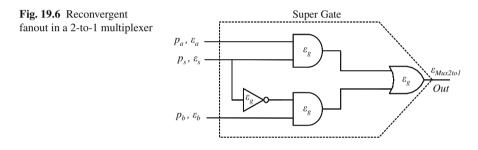

|    |                                                                                                           | 19.3.2   | Error Pro    | pagation in 2-to-1 Mux Using BDEC     | 367 |  |

|    |                                                                                                           | 19.3.3   | Circuit Er   | rror Model                            | 369 |  |

|    | 19.4                                                                                                      | Practica | l Consider   | ations                                | 370 |  |

|    |                                                                                                           | 19.4.1   | Output En    | rror Expression                       | 370 |  |

|    |                                                                                                           | 19.4.2   | Reconver     | gent Fanout                           | 371 |  |

|    | 19.5                                                                                                      | Simulat  | ion Results  | -<br>5                                | 373 |  |

|    | 19.6                                                                                                      | Extensi  | ons to BDE   | EC                                    | 377 |  |

|    |                                                                                                           | 19.6.1   | Soft Error   | r Rate (SER) Estimation Using BDEC    | 377 |  |

|    |                                                                                                           | 19.6.2   | BDEC fo      | or Asymmetric Erroneous Transition    |     |  |

|    |                                                                                                           |          | Probabilit   | ties                                  | 379 |  |

|    |                                                                                                           | 19.6.3   | BDEC A       | pplied to Emerging Nanotechnologies   | 379 |  |

|    | 19.7                                                                                                      | Conclus  | sions        |                                       | 379 |  |

|    | Refer                                                                                                     | ences    |              |                                       | 380 |  |

|    |                                                                                                           |          |              |                                       |     |  |

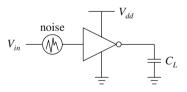

| 20 | Digit                                                                                                     | al Logic | Using Non    | I-DC Signals                          | 383 |  |

|    |                                                                                                           |          |              | inil P. Khatri, and Laszlo B. Kish    |     |  |

|    | 20.1                                                                                                      |          |              | · · · · · · · · · · · · · · · · · · · | 383 |  |

|    | 20.2                                                                                                      |          |              |                                       |     |  |

|    | 20.3                                                                                                      |          |              |                                       |     |  |

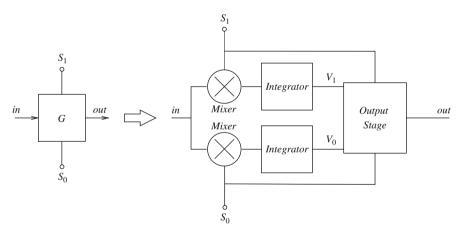

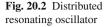

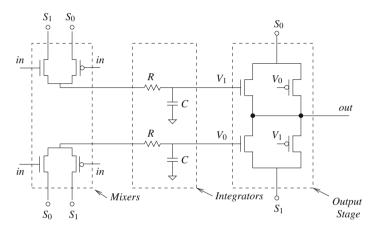

|    |                                                                                                           | 20.3.1   |              | Wave Oscillator                       |     |  |

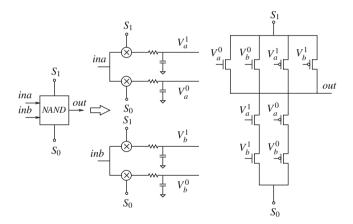

|    |                                                                                                           | 20.3.2   |              | Gate                                  |     |  |

|    |                                                                                                           |          | 20.3.2.1     |                                       |     |  |

|    |                                                                                                           |          | 20.3.2.2     | Low-Pass Filter                       |     |  |

|    |                                                                                                           |          |              | Output Stage                          |     |  |

|    |                                                                                                           |          | 20.3.2.4     | Complex Gates                         |     |  |

|    |                                                                                                           | 20.3.3   |              | ects                                  |     |  |

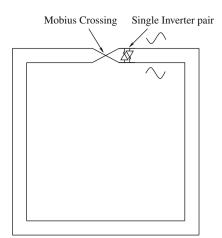

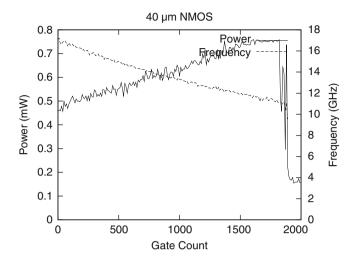

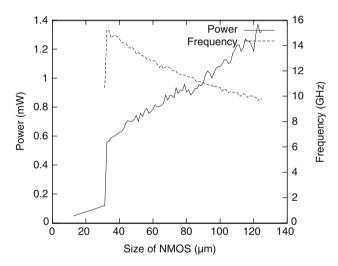

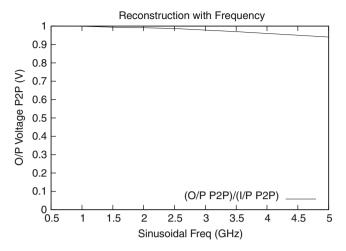

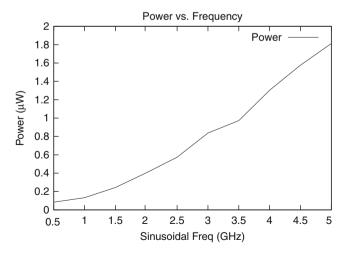

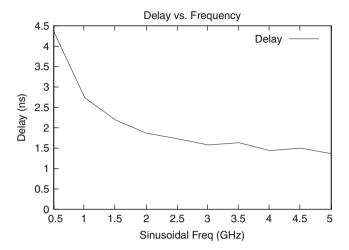

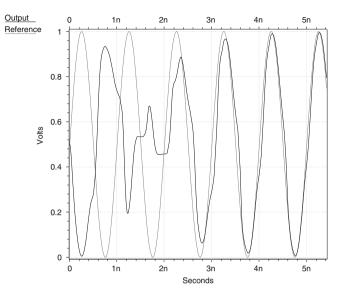

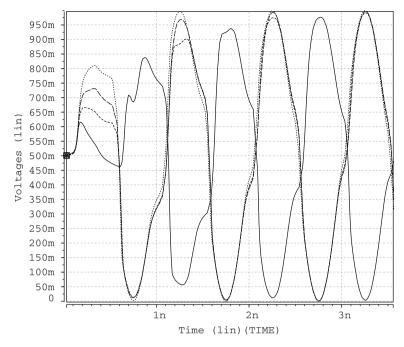

|    | 20.4                                                                                                      |          |              | ılts                                  |     |  |

|    |                                                                                                           | 20.4.1   |              | Generator                             |     |  |

|    |                                                                                                           | 20.4.1   |              | imization                             |     |  |

|    |                                                                                                           | 20.4.2   |              | ration                                |     |  |

|    | 20.5                                                                                                      |          | -            |                                       |     |  |

|    |                                                                                                           |          |              |                                       |     |  |

| Contents |

|----------|

|----------|

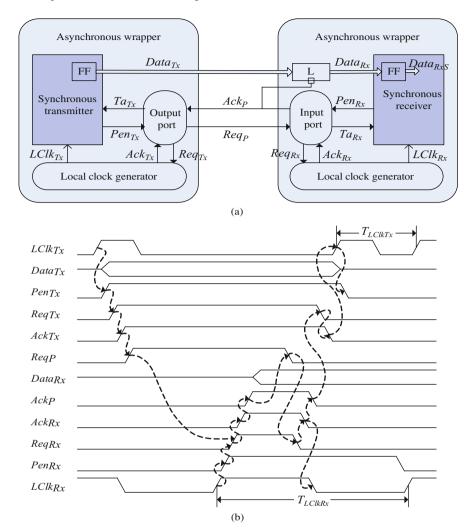

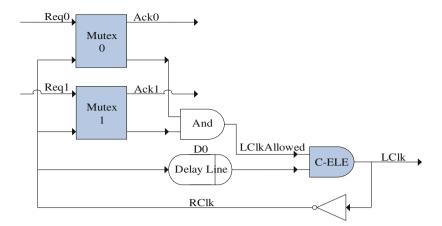

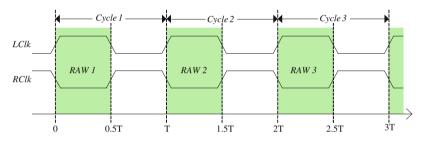

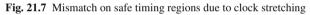

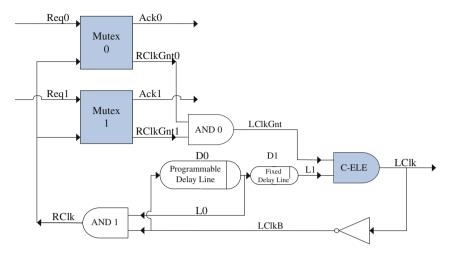

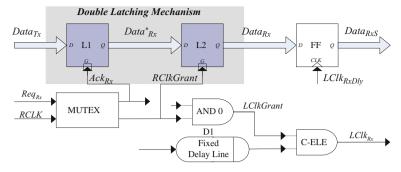

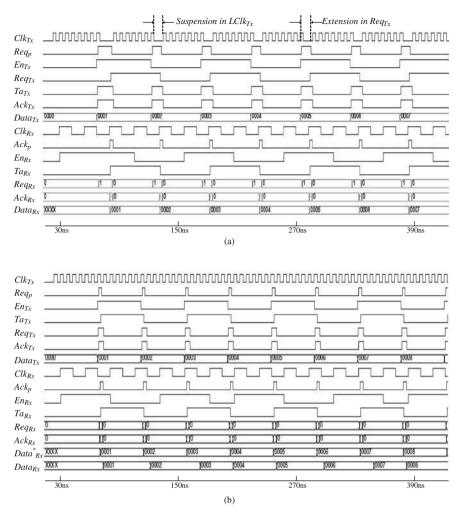

| 21  | Improvements of Pausible Clocking Scheme for High-Throughput |         |                                 |                                                                                                                                                    |  |

|-----|--------------------------------------------------------------|---------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     |                                                              | -       | -                               | ALS Systems Design                                                                                                                                 |  |

|     | Xin F                                                        |         |                                 | d Eckhard Grass                                                                                                                                    |  |

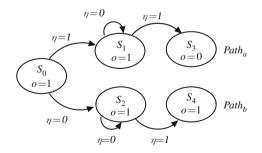

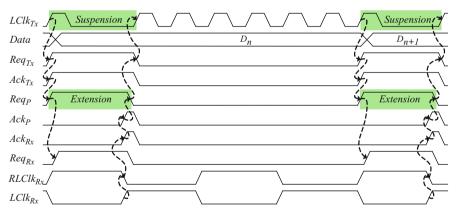

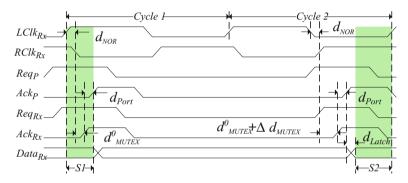

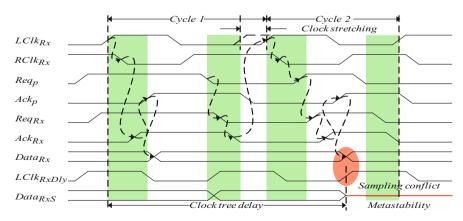

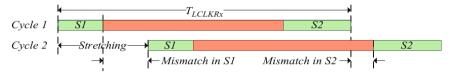

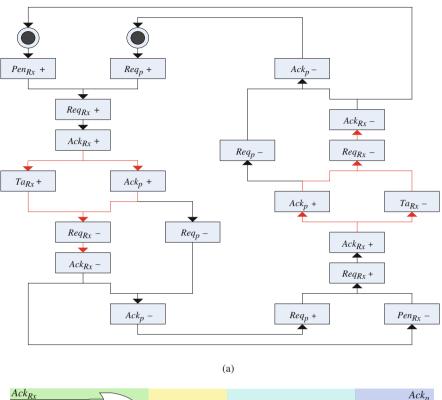

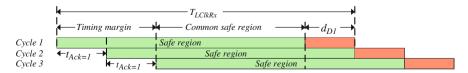

|     | 21.1                                                         | Introdu | ction                           |                                                                                                                                                    |  |

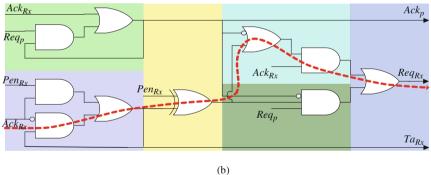

|     | 21.2                                                         | Analysi | sis of Pausible Clocking Scheme |                                                                                                                                                    |  |

|     |                                                              | 21.2.1  | Local Clo                       | ock Generators                                                                                                                                     |  |

|     |                                                              | 21.2.2  | Clock Ac                        | knowledge Latency                                                                                                                                  |  |

|     |                                                              | 21.2.3  | Throughp                        | out Reduction                                                                                                                                      |  |

|     |                                                              |         | 21.2.3.1                        | Demand-Output (D-OUT) Port to Poll-Input                                                                                                           |  |

|     |                                                              |         |                                 | (P-IN) Port Channel                                                                                                                                |  |