# Kenichi Okada · Shouhei Kousai Editors

# Digitally-Assisted Analog and RF CMOS Circuit Design for Software-Defined Radio

Digitally-Assisted Analog and RF CMOS Circuit Design for Software-Defined Radio

Kenichi Okada • Shouhei Kousai Editors

# Digitally-Assisted Analog and RF CMOS Circuit Design for Software-Defined Radio

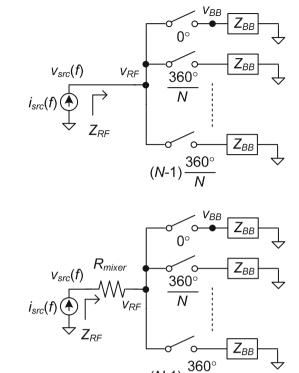

*Editors* Kenichi Okada Department of Physical Electronics Graduate School of Science and Engineering Tokyo Institute of Technology Tokyo, Japan okada@ssc.pe.titech.ac.jp

Shouhei Kousai Advanced Circuit Design Department Center for Semiconductor Research and Development Toshiba Corporation Kawasaki, Japan shouhei.kousai@toshiba.co.jp

ISBN 978-1-4419-8513-2 e-ISBN 978-1-4419-8514-9 DOI 10.1007/978-1-4419-8514-9 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011935146

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

Software-defined radios (SDRs) that are capable of transmitting and receiving modulated signals in any frequency band have long been desired. They are very attractive, especially as mobile devices, since mobile devices need to be compact even if they are compliant with many different wireless standards. In fact, recent mobile devices are required to offer an enormous range of wireless standards (e.g., 2G/3G/3.5G/3.9G/4G cellular, WLAN/WPAN, GPS, broadcasting).

For many years, various aspects of SDRs have been investigated and many technologies for realizing SDRs have been developed. However, it is still difficult to realize a practical SDR device. This is mainly because conventional RF front ends are not sufficiently flexible to satisfy the requirements for all modulation schemes and frequency bands. SDR transceivers must satisfy quite a diverse range of requirements depending on the wireless standard. For example, the frequency bands required are widely spread between 400 MHz and 6 GHz. On the other hand, SDR transceivers are also required to have competitive performances (in terms of power consumption, sensitivity, etc.) with those of other single-band transceivers.

A key idea for realizing SDR transceivers has recently been proposed: digitally assisted analog and RF circuits. Many circuit applications that use this concept have been reported and they are highly flexible. Thus, SDR transceivers are fairly close to becoming a reality. This book introduces potential circuits for SDRs, including RF, analog, and mixed-signal circuits.

This book is based on recent research conducted by the authors. It discusses approaches for realizing SDR transceivers using recently developed advanced CMOS technology, which use millions of fast transistors. One of the most important technologies for realizing SDR transceivers is a design technique of *digitally assisted analog and RF circuits* since SDR transceivers require high flexibility and programmability. This book covers every circuit block available for SDR transceivers to illustrate the various applications of digitally assisted circuits.

The book is aimed at graduate students who are designing CMOS wireless transceivers as well as professional circuit designers and researchers of wireless systems, antenna, and other wireless components. It assumes a basic knowledge of analog and RF circuit design and covers the entire transceiver, including the receiver,

transmitter, local oscillator, analog baseband, ADC, and DAC. Each chapter stands alone so that readers can select topics that interest them. Chapter 1 provides a brief overview and describes the relationships between the other chapters. The subsequent chapters are organized as follows:

Chapter 2 was written by Jan Craninckx of IMEC in Belgium. It describes a transceiver front-end for a SDR, which contains a quadrature local synthesizer and a 25%-duty sampling mixer. This transceiver is even capable of SAW-less FDD operation. It is one of the most promising SDR front-ends, and it should be considered by every SDR researcher.

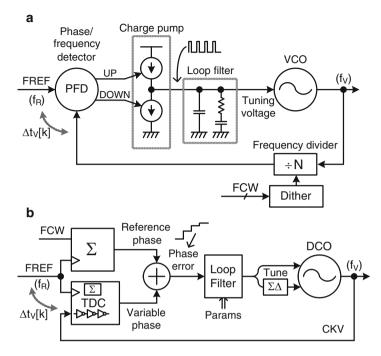

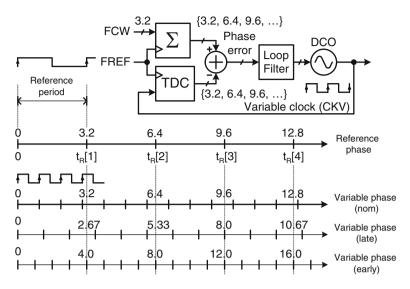

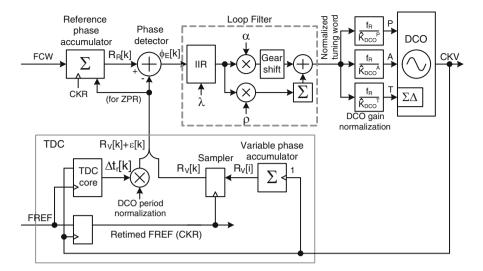

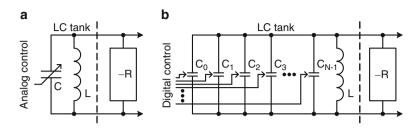

Chapter 3 was written by Robert Bogdan Staszewski of Delft University of Technology in the Netherlands. It describes the key concepts of digital RF and digitally assisted RF circuits, including an all-digital PLL and a direct-sampling mixer, which are now essential components for highly integrated CMOS transceivers.

Chapter 4 was written by Rahim Bagheri of Wilinx Corp., Ahmad Mirzaei and Saeed Chehrazi of Broadcom Corp., and Asad A. Abidi of the University of California in Los Angeles, California. It describes the first practical SDR receiver, which represents a historic achievement and indicates the direction of future SDR research.

Chapter 5 was written by Eric Klumperink, Zhiyu Ru, Niels Moseley, and Bram Nauta from the University of Twente in the Netherlands. It describes a practical SDR receiver that uses digitally enhanced harmonic rejection for robustness against interference.

Chapter 6 is written by Masaki Kitsunezuka, NEC Corp.; Shinichi Hori, NEC Corp.; and Tadashi Maeda, Renesas Electronics Corp., Japan. This chapter describes a tunable LPF that uses duty-cycle control of an analog baseband.

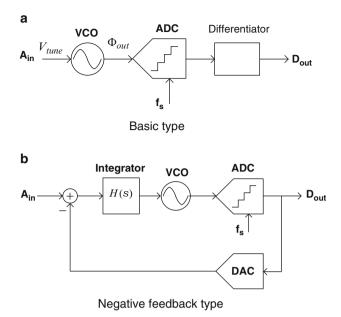

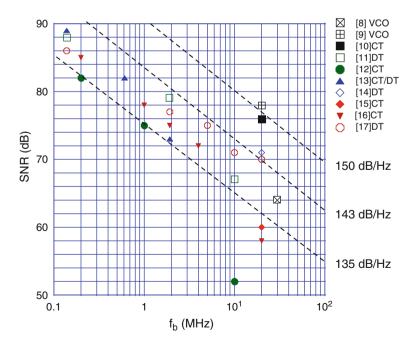

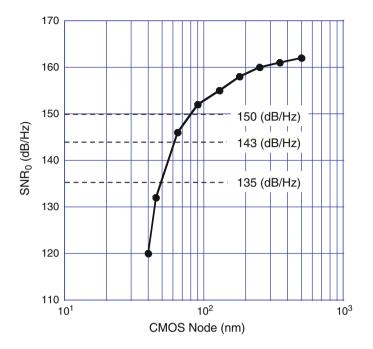

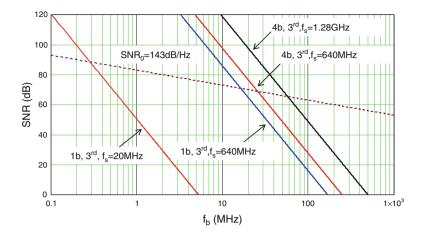

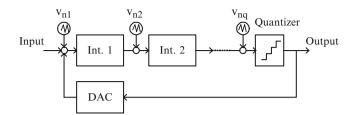

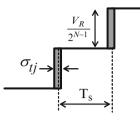

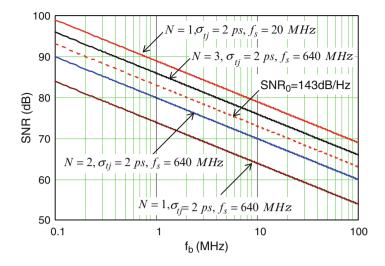

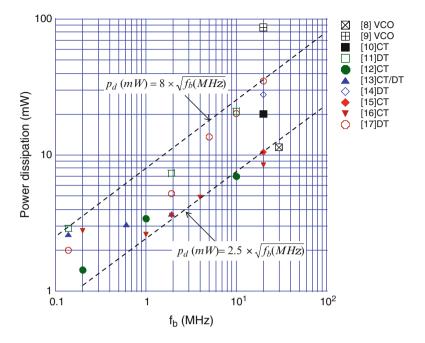

Chapter 7 is written by Akira Matsuzawa of the Tokyo Institute of Technology in Japan. It discusses reconfigurable data converters, focusing especially on a delta-sigma analog-to-digital converter that can be used to realize both a tunable resolution and a tunable conversion speed.

Chapter 8 is written by Shouhei Kousai of Toshiba Corp. This chapter describes a flexible, highly efficient, watt-level transmitter. This work was conducted by the Caltech High-Speed Integrated Circuits Group (CHIC).

We would like to acknowledge the chapter authors for their enormous effort in helping to prepare this book. They devoted considerable time to this book, even during their precious holidays. It would have been impossible to publish this book without their full cooperation.

Each chapter was subjected to a rigorous review process. We would like to thank the many volunteer reviewers for their insightful and constructive comments including Yohei Morishita (Panasonic Corp.), Masaki Kanemaru (Panasonic Corp.), Jun Deguchi (Toshiba Corp.), and some anonymous reviewers.

Finally, we would like to thank Charles Glaser and Elizabeth Dougherty of Springer for their generous and ongoing support and guidance.

Tokyo Institute of Technology, Japan Toshiba Corporation, Japan Kenichi Okada Shouhei Kousai

# Contents

| 1  | Introduction<br>Shouhei Kousai                                                                                                                                                                    | 1   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Nanoscale CMOS Transceiver Implementation<br>for a Software-Defined Radio Platform<br>Jan Craninckx                                                                                               | 3   |

| 3  | Digital RF and Digitally-Assisted RF<br>Robert Bogdan Staszewski                                                                                                                                  | 35  |

| 4  | Software-Defined Radio Receiver Architecture<br>and RF-Analog Front-End Circuits<br>Rahim Bagheri, Ahmad Mirzaei, Saeed Chehrazi,<br>and Asad A. Abidi                                            | 85  |

| 5  | Interference Rejection in Receivers by Frequency<br>Translated Low-Pass Filtering and Digitally Enhanced<br>Harmonic-Rejection Mixing<br>Eric Klumperink, Zhiyu Ru, Niels Moseley, and Bram Nauta | 113 |

| 6  | Reconfigurable Analog Baseband Filter<br>Masaki Kitsunezuka, Shinichi Hori, and Tadashi Maeda                                                                                                     | 151 |

| 7  | <b>Multi-Standard Data Converters</b><br>Akira Matsuzawa                                                                                                                                          | 171 |

| 8  | Highly Linear and Efficient Watt-Level SDR Transmitter<br>with Power Mixer Array<br>Shouhei Kousai                                                                                                | 191 |

| In | dex                                                                                                                                                                                               | 217 |

### Chapter 1 Introduction

Shouhei Kousai

The aim of this book is to assist with developing software-defined radio (SDR) transceivers and their related circuit techniques in CMOS. The book is structured as follows.

Chapter 2 describes a practical CMOS implementation of an SDR transceiver. It can transmit and receive signals of commonly used wireless communication standards in a frequency range of 0.1–6.0 GHz. It contains several low-noise amplifiers, driver amplifiers, and local oscillators to cover this frequency range and their performance is critical to the transceiver. The class-C VCO described in this chapter has a trade-off between noise and power consumption, offering the flexibility required for an SDR transceiver. The other circuit blocks (i.e., IQ up-conversion and down-conversion mixers and an analog baseband (ABB)) are highly tunable, enabling them to accommodate multiple standards in a single circuit block. The performance of the SDR transceiver is competitive with or even better than that of a transceiver designed for a single wireless standard.

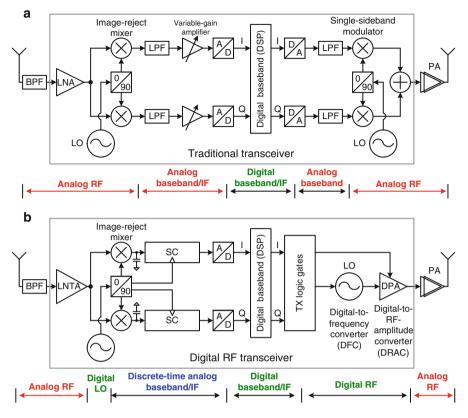

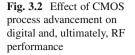

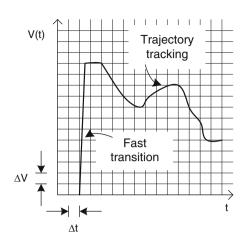

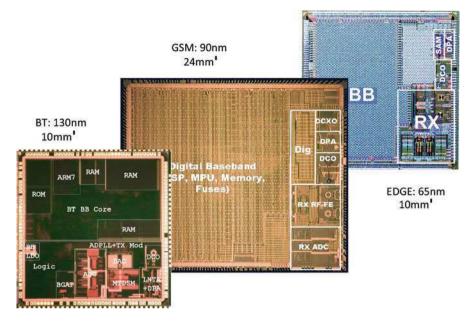

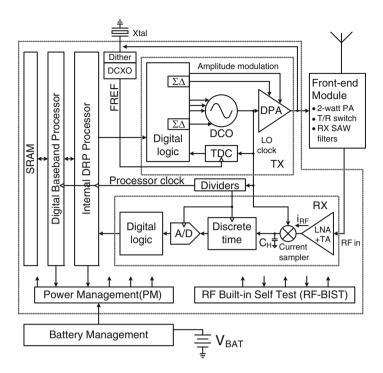

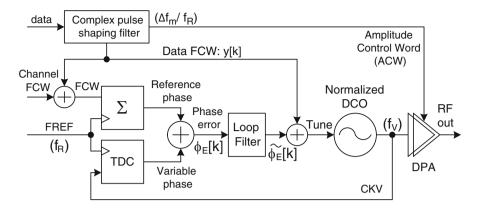

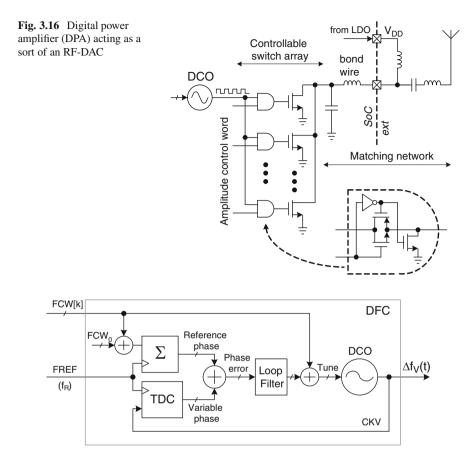

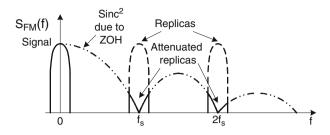

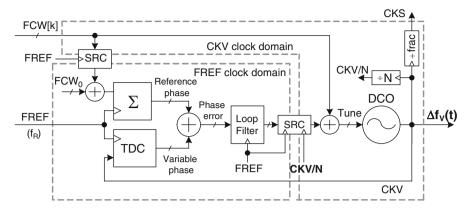

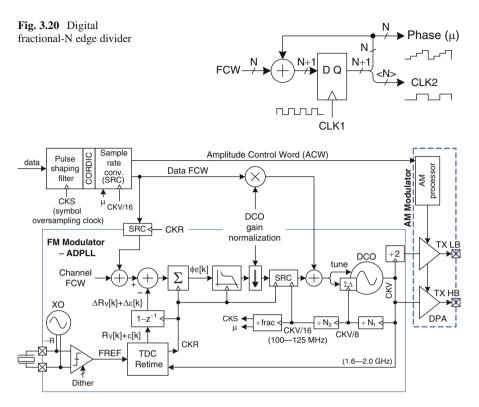

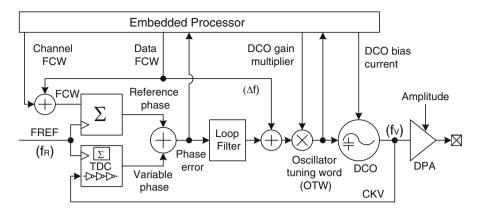

Chapter 3 describes a digital RF transceiver that has the most important characteristics for an SDR transceiver: programmability and flexibility. The key concepts of digital RF transceivers, such as all-digital PLL (ADPLL), discrete-time analog signal processing, digital-to-frequency converter (DFC), and digital-to-RF amplitude converter (DRAC), are explained in detail. This chapter emphasizes the advantages of time-domain signal processing over conventional voltage or current-domain signal processing in scaled CMOS technology in terms technical, historical, and commercial aspects.

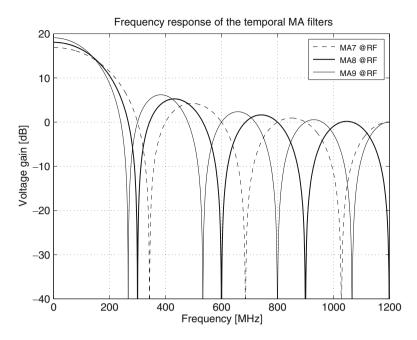

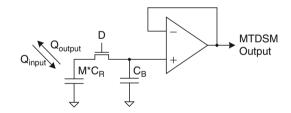

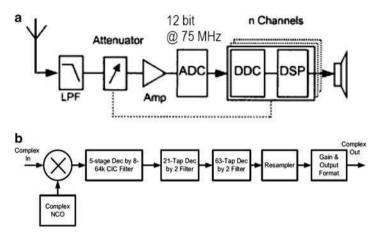

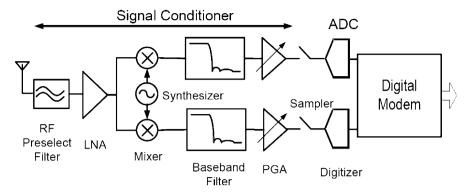

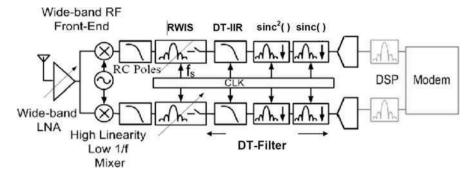

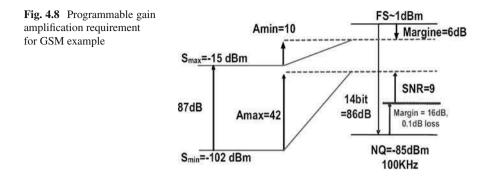

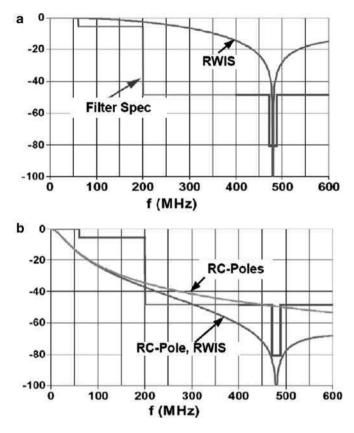

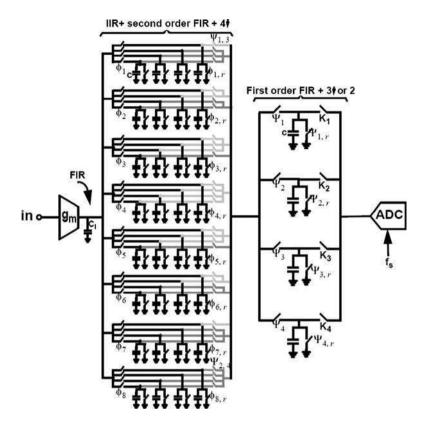

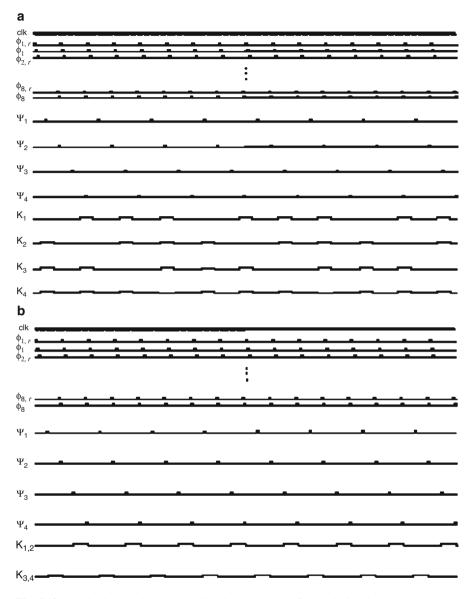

An advanced SDR receiver is discussed in Chap. 4. The basic concept is to remove the RF-front-end filters (i.e., SAW filters) and to increase its flexibility so that it can accommodate future wireless standards. Strong out-of-band blockers can be rejected by employing the combination of a rectangular window integration

1

S. Kousai (🖂)

Toshiba Corp., Tokyo, Japan

e-mail: shouhei.kousai@toshiba.co.jp

K. Okada and S. Kousai (eds.), *Digitally-Assisted Analog and RF CMOS Circuit Design for Software-Defined Radio*, DOI 10.1007/978-1-4419-8514-9\_1, © Springer Science+Business Media, LLC 2011

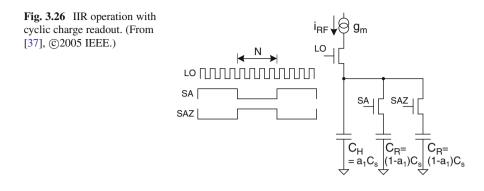

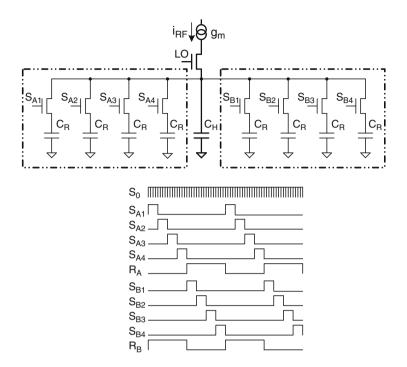

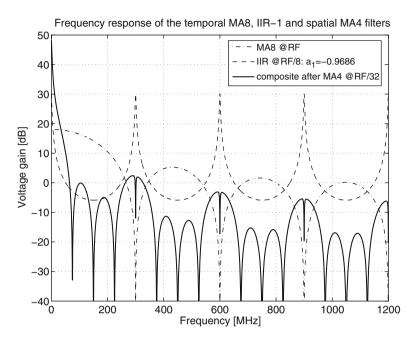

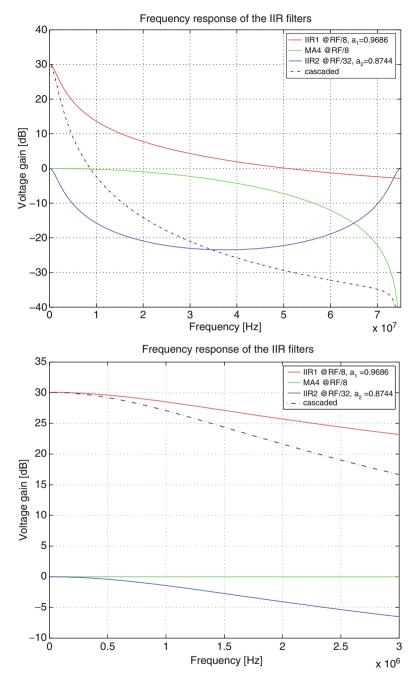

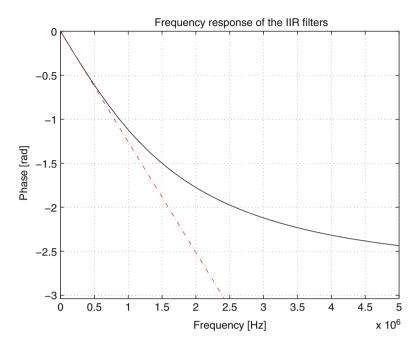

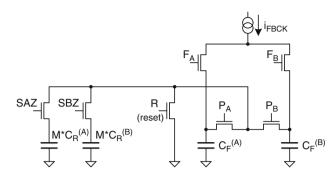

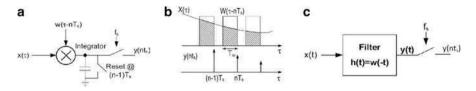

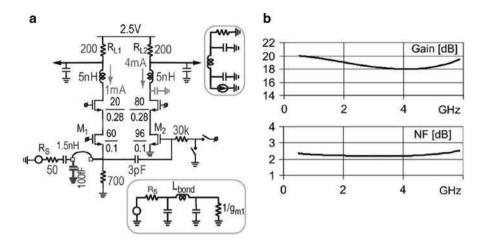

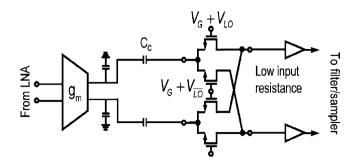

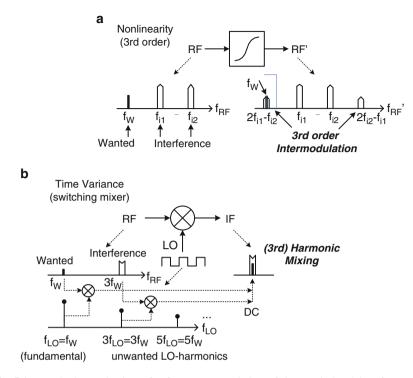

sampler, a discrete-time analog infinite impulse response (IIR) filter, and a discretetime analog decimation filter (DTDec); this configuration exploits the highly flexible and programmable discrete time analog signal processing introduced in Chap. 3. Wideband noise cancelling LNA operating from 800 MHz to 6.0 GHz with a noise figure (NF) of less than 2.5 dB is demonstrated. It employs a common-gate (CG) and common-source (CS) amplifier and can provide a balanced output without an offchip balun. An harmonic rejection (HR) mixer is also described for rejecting third and fifth harmonic mixing, which is a major challenge in wideband transceivers.

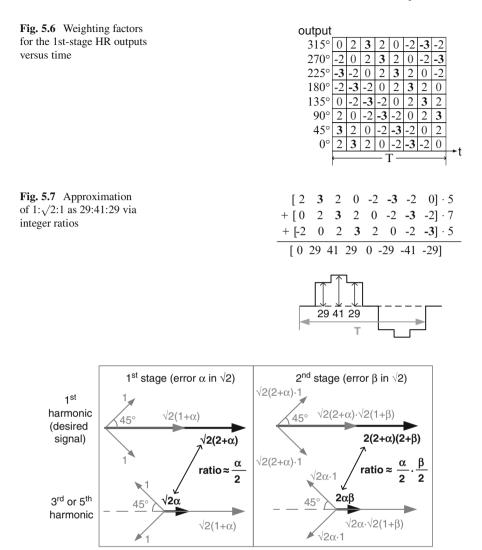

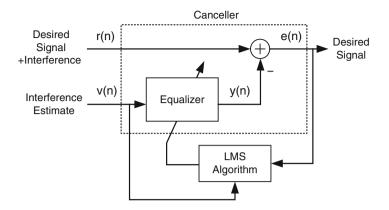

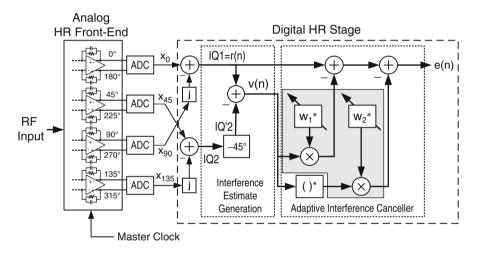

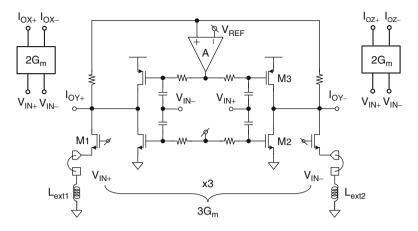

The above-mentioned challenges of harmonic mixing and out-of-band blocker rejection are further discussed in Chap. 5. In a wideband SDR receiver, an out-of band blocker can be much stronger than in-band blockers, since the RF-front end does not provide blocker rejection (unlike in conventional receivers). This chapter explains a receiver front-end architecture for maximizing the blocker immunity while maintaining a high sensitivity. The blocker is rejected before the first high-impedance node, thus preventing intermodulation. This chapter also describes two harmonic rejection (HR) techniques: an analog two-stage polyphase HR and digitally enhanced HR. Without any calibration, the analog HR achieves a rejection of more than 60 dB and mismatch robustness. The digitally enhanced HR achieves an even better rejection of over 80 dB.

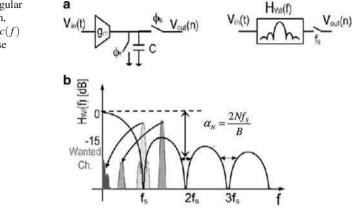

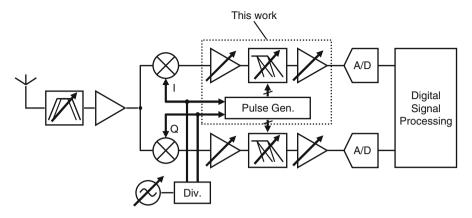

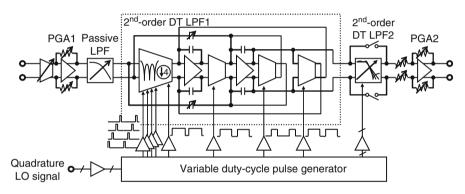

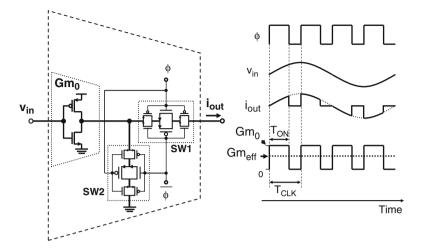

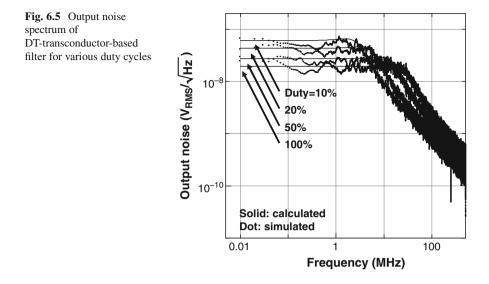

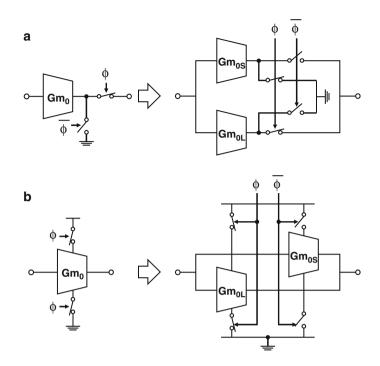

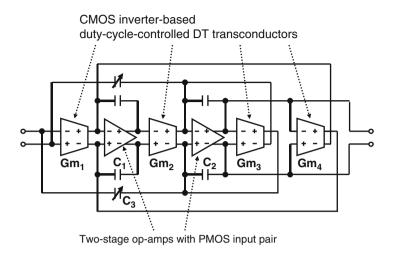

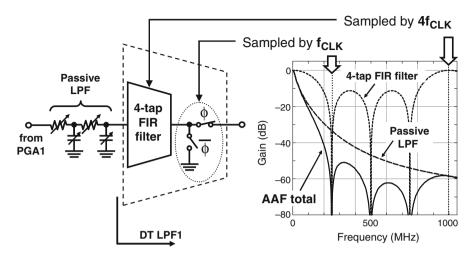

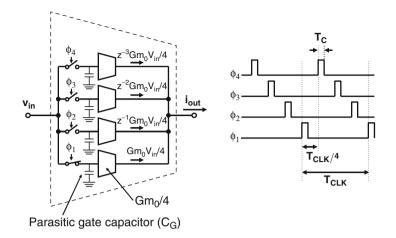

The major advantages of the discrete-time filtering discussed in Chaps. 3 and 4 are its high rejection obtained by zero insertion and frequency tunability. These advantages are fully exploited to realize a reconfigurable analog baseband (ABB), which is described in Chap. 6. A duty-cycle-controlled discrete-time transconductor combined with an op-amp integrator is introduced. It allows the poles and Q of a second-order LPF to be tuned almost arbitrarily. Passive LPF and four-tap FIR filter, which can be buried in the second-order LPF, can solve the problem of *aliasing*. Tunability of the cut-off frequency from 400 kHz to 30 MHz and Butterworth, Chebyshev, and elliptic filter transfer functions are demonstrated.

Chapter 7 reviews data converters for SDR transceivers, focusing especially on delta-sigma analog-to-digital converters (ADCs). Their high resolutions permit channel selection in the digital domain and thus enable high programmability and flexibility. They also offer a trade-off between power consumption and bandwidth, which can realize a comparable performance with ADCs designed for a single standard. Previously published ADCs are analyzed and are compared in terms of bandwidth, signal-to-noise ratio (SNR), technology node, topology, and power dissipation. This reveals the design requirements and limitations for a multimode ADC.

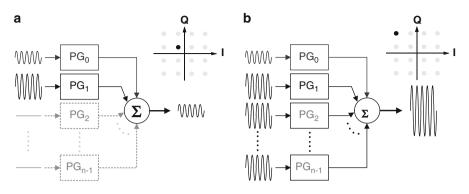

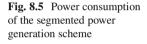

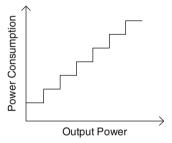

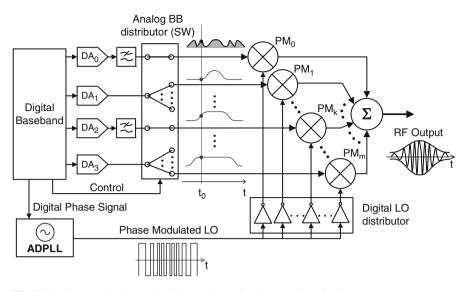

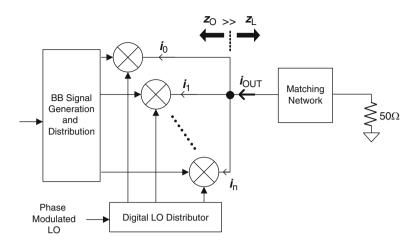

Chapter 8 describes a power mixer array as an efficient and flexible power generation approach for CMOS. The concept of digital power amplifier (DPA) described in Chap. 3 is expanded to transmit a watt-level modulated signal and to reject an aliasing signal, while maintaining the programmability of DPA. It comprises several power mixer units that are dynamically turned on and off to enhance the linearity and back-off efficiency. At the circuit level, the power mixer unit can operate as a switching amplifier to achieve a high peak power efficiency.

## **Chapter 2 Nanoscale CMOS Transceiver Implementation for a Software-Defined Radio Platform**

Jan Craninckx

A Software-Defined Radio (SDR) should theoretically receive and transmit any modulated frequency channel in the (un)licensed spectrum, targeting all modern communication standards relevant for a modern handheld mobile device (2G/3G/4G cellular, Wireless Local Area Networks (WLAN), Bluetooth, Global Positioning System (GPS), broadcasting, etc.). Moreover, it should guarantee top performance with energy savings, while still being integrated in a digital CMOS technology. In this chapter, a practical front-end implementation for such an SDR concept is demonstrated, including local oscillator, transmitter and receiver in the frequency range 0.1–6 GHz. Circuits and architectures are optimized for minimal area occupation in a standard digital 40 nm low-power (LP) CMOS technology. The radio front-end compares favorably with state-of-the-art dedicated radios while enabling, for the first time, wideband reconfigurable performance and energy scalability.

#### 2.1 Introduction

Driven by increasingly sophisticated user demands, wireless communication systems are moving towards an era where ubiquitous connectivity and growing levels of integration will be essential for most applications. This wireless revolution will not slow down in its penetration of society for the foreseeable future. There is on the one hand a market pull by an increasingly connected world population asking for vast information resources through the internet and/or mobile phones. On the other hand, there is a market push from a hundreds of billions dollar industry delivering all kinds of communication products and applications. In this context, mobile handsets can

J. Craninckx (🖂)

IMEC, Kapeldreef 75, 3000 Leuven, Belgium e-mail: jan.craninckx@imec.be

K. Okada and S. Kousai (eds.), *Digitally-Assisted Analog and RF CMOS Circuit Design for Software-Defined Radio*, DOI 10.1007/978-1-4419-8514-9\_2, © Springer Science+Business Media, LLC 2011

represent a real bottleneck as they incorporate several concurrent constraints (e.g., in battery duration, cost, performance, size, weight) that compromise the flexibility of future networks.

Although the most advanced smart phones already support an increasing number of radios, convergence of standards is currently achieved by simply assembling dedicated ICs on ultradense printed circuit boards (PCBs), which can finally turn into a significant increase in component count and Bill of Materials (BoM). System-on-Chip (SoC) solutions have also appeared, which integrate multiple RF front-ends and modems on the same chip, mostly relying on digitally assisted design techniques. However, current focus is still on the selection of a few limited standards having very similar requirements. Moreover, most of these transceivers provide state-of-the-art performance at fixed power levels whereas in many scenarios, tens of mWs could still be saved by tuning the radio at run-time, based on actual communication conditions [1].

We believe that the road to a *universal radio* lies in all-CMOS designs based on agile analog front-ends and a Software-Defined Radio (SDR) platform. Clearly enough, the original Software Radio (SR) concept [2], featuring a high dynamic range ADC able to *concurrently* receive any possible frequency channel directly at the antenna, remains still unrealistic for battery-powered devices. On the other side, an SDR device, whose key performances are configurable by software and which supports the reception/transmission of several standards (one-at-a-time) proves to be a pragmatic approach, which can bring significant advantages, ranging from lower BoM to universal RX/TX capabilities and considerable energy savings [3–5].

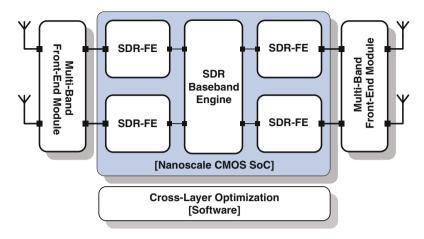

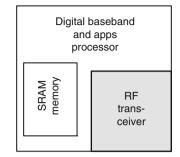

The mobile terminal that delivers the ultimate user experience will require a Software-Defined Radio (SDR) platform as the one depicted in Fig. 2.1. It consists of multiple front-end modules, possibly leveraging heterogeneous and 3-D integration technologies, a digitally assisted analog front-end and a reconfigurable base-band engine [6], both integrated in a digital nanometer CMOS technology. It is capable of transforming itself satisfying the requirements of any desired communication protocol while still providing competitive power consumption. A software *brain* is also present to guarantee advanced quality of service (QoS) and best power/performance trade-offs at any time via a cross-layer approach, since measuring performance requires taking into account the characteristics of the protocol stack, whereas optimizing energy expenditure assumes detailed knowledge of the low-level radio hardware [1].

The need for a reconfigurable radio front-end is already visible with the advent of Long Term Evolution (LTE) [7], where one of the key technical aspects is the large flexibility that is required from the radio front-end. Indeed, LTE combines variable baseband bandwidths with variable RF frequencies. As a result, a Software Defined Radio platform is the perfect base for an LTE front-end, as it provides the needed flexibility while offering tunable power/performance trade-offs.

As data rate requirements continue to increase, several communication standards will extensively use multiple transceiver branches (like multiple-input and multiple-output (MIMO)) in order to fit the required data rate (Mbit/s) in the pricy and thus limited available spectral bandwidths (MHz). Again, multiplying dedicated

Fig. 2.1 The possible instantiation of the ultimate SDR platform includes 4+ coexistent Software-Defined radio front-ends and a powerful baseband engine all integrated in a nano-scale digital CMOS technology. Energy and spectrum awareness is guaranteed by cross-layer optimizer whereas initial band selection and power amplification is provided by multi-band front-end modules

hardware for this increases cost and size, whereas a mobile terminal that consists of a few SDR hardware instantiations, as shown in Fig. 2.1 could be the ideal solution for this. In the usual operating mode, the radios can keep the user connected to a few systems, e.g. one cellular system, one for connectivity and one for broadcasting reception. At data rate peaks, these SDRs could all be programmed into a highcapacity MIMO mode for e.g. an 802.11n or an LTE-Advanced system for a limited amount of time, thus implementing all desired user functionality at minimal hardware cost. Note that in the proposed scheme, functionality and complexity of the system are not correlated. A commercial range of handheld devices could be differentiated by the number of SDR front-ends in the device. High-end devices would contain many front-ends and would be able to provide many services concurrently (e.g. broadband *and* cellular *and*...). The lowest end devices could have only one SDR front-end, which would limit the connection to one at a time, still to be chosen out of many standards (e.g. broadband *or* cellular *or*...).

Another 'powerful' aspect of an SDR platform is its energy awareness. The user's data does not have to be transmitted over the single protocol a dedicated terminal might be equipped with. Instead, the most optimal link can be chosen that enables the smallest required energy per bit, or maybe the one where the subscription cost is the lowest. Also within a certain communication link, the channel conditions may be such that the power budget can be optimized by reprogramming the hardware in the best trade-off for noise, filter order, linearity, etc. while still meeting all regulations for that standard. These trade-offs that are traditionally done only during the design phase of the radio, are now also possible at run-time, allowing for the best compromise possible between user experience and battery life.

A final example of the use of SDR would be the ability of the terminal to 'upgrade' itself by downloading a new configuration that allows it to be reconfigured into a new operating mode compatible with a new upcoming standard.

This chapter describes the implementation of a prototype radio front-end transceiver that follows this SDR concept [4,5], targeting all modern communication standards relevant for a modern handheld mobile device. In order to be accepted by the market as a possible solution, all the required flexibility should come at (almost) no cost, and performance should be similar to dedicated implementations. For a cost-effective implementation as part of the radio System-on-Chip (SoC) that will be dominated by a complex digital processor, the chosen technology is the most advanced one available today, i.e. 40 nm LP digital CMOS without any analog/RF option. The rest of this chapter is organized as follows. Section 2.2 describes the choices made on the architecture of the transceiver front-end. More details on the frequency synthesis, the receiver and the transmitter are given in Sects. 2.3, 2.4 and 2.5, respectively. Section 2.6 reports the measurement results and finally in the last section some conclusions are drawn.

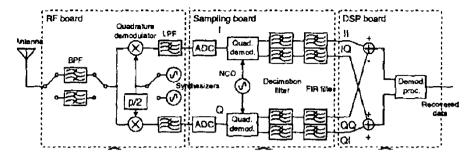

#### 2.2 SDR Architecture

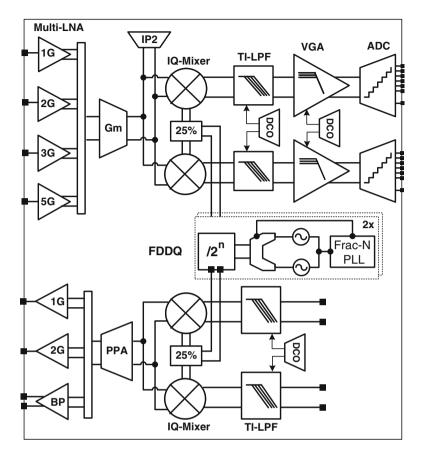

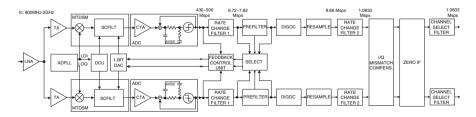

As shown in Fig. 2.2, we leverage a reconfigurable Zero-IF architecture, which has shown the highest potential to reduce costs, size and power, even under flexibility constraints [8,9]. Only modes with a very low bandwidth (such as e.g. GSM) will use a low (half-channel) IF frequency in receive mode to limit the impact of flicker noise. Although concurrently handling a few wireless standards may be a desirable feature in the future, we reasonably assume that this is a very unlikely scenario for the majority of mobile users at the moment, and hence are able to limit the major constraints and challenges in the design of the radio budget and the associated circuit blocks to those also present in single-mode radios.

As this SDR front-end needs several hundreds of control bits, a scalable Networkon-Chip (NoC) [10] is implemented to allow configuring each analog block, monitor the front-end performance, and dynamically control its behavior. To obtain stateof-the-art performance over a wide range of carrier frequencies and bandwidths, we rely on the advantages of a scaled technology together with adequate circuit design techniques and extensive calibration [11, 12]. To further reduce silicon area we limit the use of bulky passive components such as high-Q inductors, and adopt a proper distribution of gain stages. For example, increasing the gain (and the gain steps) as early as possible in the RX chain can relax the noise specifications of the baseband section and consequently yield a decrease in capacitors sizes and power consumption. However, this also implies tougher linearity requirements.

To allow frequency-division duplex (FDD) operation, the transceiver contains two high-frequency fractional-N phase-locked loops (PLLs). Both RX and TX PLLs leverage a high-band (HB) and low-band (LB) voltage-controlled oscillators (VCOs) that cover an uninterrupted range from 6 to 12 GHz, with adjustable VCO

Fig. 2.2 SDR Block diagram

gain. The high frequency of operation lowers pulling effects, and yields low area consumption for the VCOs. Local oscillator (LO) synthesis for all RF frequency bands below 6 GHz can therefore be provided by plain division-by- $2^{N}$ , which is implemented with a chain of full-swing CMOS dynamic dividers.

On the receiver side, a difficult choice to make is the number of low-noise amplifiers (LNA) to be used. While adding a separate LNA for each targeted frequency band can bring too much area overhead, having one single wideband LNA that covers the full 0.1–6 GHz RF input range is also not optimal. Although such an LNA has already been demonstrated [13], it might show some noise/gain limitations at the edge of the RF band, it will not provide any attenuation of far-away blockers so increasing the system's linearity requirements. Also, the total system will also suffer some extra losses due to interfacing issues with an array of fixed antenna filters (that will still be needed to block heavy out-of-band blockers). Therefore, the compromise of using four LNAs has been chosen here, targeting each a sufficiently wide frequency band to cover the full range up to 6 GHz.

The rest of the receive chain is constructed out of a 25% duty cycle passive mixer, a fifth order baseband trans-impedance low-pass filter (TI-LPF), a variable-gain amplifier (VGA) and a low-power 10-bit 60 MS/s successive approximation (SAR) analog-to-digital converter (ADC). Mixed-mode calibration is used for second order intermodulation and DC offset. This will be further detailed in Sect. 2.4.

The transmitter chain starts with a programmable third order reconstruction filter that removes digital-to-analog converter (DAC) aliases. For low out-of-band noise, which is a crucial performance requirement in most FDD standards, a 25% duty cycle passive voltage sampling mixer is used [14]. The RF section consists of a triple-band pre-power amplifier (PPA) with integrated transformer baluns.

#### 2.3 Frequency Synthesis

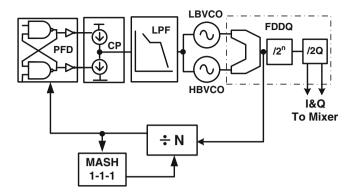

While still adopting a "classical" analog architecture, the frequency synthesizer couples multi-mode programmability with design techniques exploiting the speed capabilities of the scaled digital technology and limiting the area overhead due to passive devices. Indeed, many wideband frequency synthesis architectures must rely on poly-phase filters, multiplication, or single-side band (SSB) mixing [7] to achieve the required range of carrier frequencies desired in an SDR. However, all these techniques may easily become power-hungry and yield undesired spurious tones. In 40-nm CMOS, a fundamental VCO frequency up to 12 GHz is possible because of the intrinsically higher speed of the technology, and hence we propose to generate the LO quadrature signals by starting from a high-frequency LC-VCO signal and cascading divide-by-2 circuits [15].

A full octave tuning range (6–12 GHz) is needed to generate quadrature LO at all frequencies below 6 GHz. This is not possible with a single VCO, but two parallel VCOs centered at different frequencies can cover this range. Since at these high frequencies only small inductors are used, the area overhead is also limited. Therefore, a dual-VCO, fourth order, type-2  $\Sigma\Delta$  fractional-N PLL is implemented at the heart of our frequency synthesizer. The two VCOs cover the 6–12 GHz bandwidth while low-complexity cascaded divide-by-2 cells are used to generate quadrature frequencies. All building blocks can be programmed to achieve different carrier frequencies, VCO sensitivities, loop bandwidths, phase noise values and power consumptions.

#### 2.3.1 Reconfigurable PLL

The simplified block-diagram of the reconfigurable PLL is represented in. The phase-and-frequency detector (PFD), which is robust to crossover distortion, implements a programmable dead-zone delay between 0.86 ns and 1.55 ns to allow fine tuning for different charge pump current settings. The charge pump (CP) leverages

Fig. 2.3 Simplified block diagram of the  $\Sigma\Delta$  frequency synthesizer

eight parallel replica-biased current units and allows for up to 1.5% mismatch compensation. The CP current, programmable between 45 and 360µA, is fed into the low impedance input of a third order reconfigurable active-RC filter. While keeping the total amount of capacitance constant (approximately 200 pF), the filter configures its resistors to allow for cross-over frequency tuning between 110 and 320 kHz.

Based on the targeted frequency, either the 6–9 GHz low-band (LB) or the 9–12 GHz high-band (HB) VCO is active, whose output signal is selected by a high-speed CMOS multiplexer that drives the PLL frequency divider and the frequency distribution and division-in-quadrature circuit (FDDQ), which generates LO signals in the 0.1–6 GHz band. With a reference crystal of a few tens of MHz, a divider with a wide programmable range, e.g. from 128 to 511, is needed to close the loop of the PLL (Fig. 2.3).

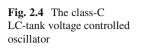

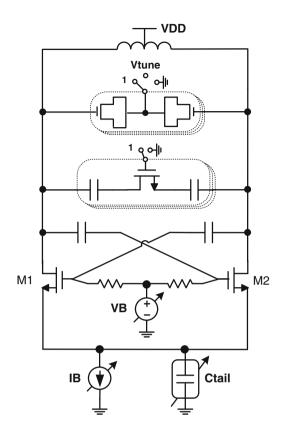

#### 2.3.2 LC Voltage Controlled Oscillators

Both VCOs adopt the class-C single-NMOS differential-pair topology [16] represented in Fig. 2.4 With respect to a standard LC-VCO, this topology produces a larger oscillation amplitude for a given bias current, potentially leading to improved phase noise performance for a given power budget. In fact, rather than operating as switches, the NMOS transistors in this topology either act (prevalently) in the active (saturation) region or they are off. As a consequence, the contribution of the core transistors to phase noise is basically as low as in the standard LC-VCO, but the amplitude of the fundamental current harmonic is maximized, as in a Colpitts oscillator, finally producing a net improvement of 3.9 dB for the same power consumption, and of 6 dB for the same oscillation amplitude. Additional advantages include built-in filtering of noise from the tail current source and lower sensitivity to stray capacitances at the common source node.

However, to guarantee class-C operation in the current limited regime, the maximum oscillation amplitude offered by a class-C VCO is always lower than the one of a standard LC-VCO. In fact, to operate the transistors in saturation, the output amplitude will be limited by  $A_{max} = V_{DD} - V_B + V_{Tn}$  where  $V_B$  is the transistor gate bias voltage and  $V_{Tn}$  is the threshold voltage. To achieve higher oscillation swings and overcome this limitation, we program  $V_B$  and  $I_B$  to allow the MOS devices to operate in moderate inversion (as far as the oscillation startup condition is met) and even moderately enter the triode region when needed. Proper device biasing is crucial to optimize noise performance, since variations of 100–200 mV in  $V_B$  may cause a sensible increase in phase noise. In our implementation, a 4-bit DAC, ac-coupled with the gates of the transistor pair, generates a gate voltage value in 50-mV steps.

In both VCOs, the tank inductor is a center-tapped single turn horseshoe coil, drawn in the topmost metal, shunted with the superficial aluminum redistribution layer. In fact, low phase noise values, for a given tank amplitude, call for larger tank capacitance and smaller inductance (0.4 nH in our case) based on analysis in [16]. A small inductance value is also preferred to increase the tuning range.

We use coarse frequency tuning to split a large tuning range into smaller bands. This allows covering our range of interest without increasing the VCO sensitivity

Fig. 2.5 Enhanced range divider supporting seamless  $\Sigma\Delta$  divide modulus dithering

$K_{VCO}$ , which would increase the level of the PLL spurs and phase noise. Coarse frequency band selection is done with a 6-bit low-cost MoM capacitor array. Within each band, the tank capacitance is then finely tuned through an array of 15 differential NMOS varactors. These varactors can be switched on or off for fine band selection, or connected to the tuning voltage  $V_{TUNE}$  to control the VCO gain for optimal PLL design [17]. For instance,  $K_{VCO}$  can be programmed to linearly scale with the PLL frequency to provide constant bandwidth.

Each VCO can further trade performance for power consumption, by also adjusting the bias current, the gate bias voltage, as well as the tail capacitance  $C_{tail}$  regulating transistors' operation region. In particular, the VCO active core negative resistance is also tuned through the bias current and the gate voltage  $V_B$ . However, differently than in [17], the active core is never switched, since changing transistor dimensions does not help improve noise [16]. On the other hand, it can increase circuit complexity or even compromise performance due to the addition of the switches.

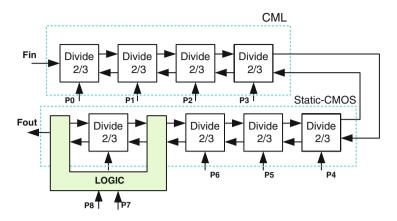

#### 2.3.3 Programmable Divider

To support seamless dithering on a wide-range divide modulus we implement a modular PLL divider architecture based on [18]. The divider consists of a cascade of divide-by-2/3 cells (Fig. 2.5) and exploits a hybrid CMOS/CML style to trade speed with phase noise and power consumption. Since *M* cells provide division ratios from  $2^{M}$  to  $2^{M+1} - 1$  (controlled by inputs P), we need eight cells to cover a 256–511 range. Moreover, by shunting out cell C7 (using an additional control bit P8) we can use the first seven cells to cover ratios between 128 and 255. The four highest frequency cells adopt differential CML whereas the remaining ones leverage full-swing single-ended static-CMOS.

While the above structure is enough for integer division, additional logic is needed for correct fractional-N mode operation. In fact, with a third order modulator, we expect the modulus to vary in the [N - 3N + 4] interval because of dithering. Therefore, for N in [252–258], smooth swapping between 7-cell and 8-cell configuration is needed with no violations. To support seamless switching, we employ bit P8 to control a multiplexer that mutually selects the divider output F8 (output of cell 8) or F7 (output of cell 7). At the same time, we take care that F8 is always preset to a known value, before its selection, to avoid glitches. Finally, we re-time the divider output via a higher frequency signal (e.g. the output of cell 5) to clear out modulus dependent jitter.

The sigma-delta modulator driving the divider modulus is MASH 1-1-1 with 24-16-8 bit accumulators [19], but can also be configured as a MASH 1-1. A 22-bit linear feedback shift register (LFSR) is included for dither addition to the LSB.

#### 2.4 Receiver

In the following pages, all circuit blocks of the receive chain, from the RF LNA down to the integrated SAR ADC, will be discussed.

#### 2.4.1 Low-Noise Amplifiers

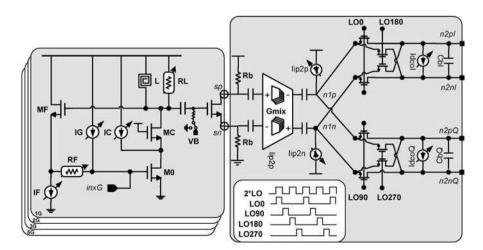

As shown in Fig. 2.6, in the receiver, four parallel LNAs (1-2-3-5 GHz) amplify the wide frequency range (100 MHz-6 GHz) of the input signal with NF down to 1.5 dB. They provide some selectivity against far out-of-band interference and reduce loss

Fig. 2.6 Receiver RF circuit details

and cost of the multi-band antenna interface. Each LNA uses shunt-shunt feedback to provide input matching, and a low-area stacked inductor for gain shunt peaking, keeping the LNA area below  $0.02 \,\mathrm{mm^2}$  [13]. The input matching condition and the noise factor (F) of the LNA are given by

$$g_{mf} = \frac{1}{R_s \cdot (1 + g_{m0} \cdot Z_L) - R_F}, [Z_L = R_L || j \omega L]$$

$$F \approx 1 + \frac{\gamma_0}{g_{m0} \cdot R_s} + \frac{R_F}{R_s (1 + A_v)^2}, [A_v = g_{m0} \cdot Z_L]$$

(2.1)

where  $g_{m0}$  and  $g_{mf}$  are the transconductances of the transistors M0 and MF respectively,  $\gamma_0$  is the (drain current) noise coefficient of the transistor M0 and  $R_s$  is the source resistance to which the input impedance of the LNA should be matched to. As can be seen from the equations, the NF can be lowered by increasing the transconductance of the input transistor at the cost of increased power consumption. This topology offers design freedom in setting NF, gain and input impedance orthogonally. Load ( $R_L$ ) and feedback resistors ( $R_F$ ) are made tunable to achieve a minimal gain step of 3 dB, and to find optimum gain setting for achieving certain linearity and NF over different standards. Current bleeding through  $I_C$  lowers the voltage drop over the tunable load resistor improving linearity and noise.

Every LNA output is AC coupled and drives one of the four inputs of a multiplexing linear active balun. This is implemented by linear NMOS transistors  $(M_B)$  which convert the voltage output of an LNA into a current which flows through  $R_B$  creating differential voltage across nodes *sp* and *sn*. At peak gain (and lowest noise) setting, the LNA together with balun consumes a maximum of 20–38 mA from the 1.1 V supply, depending on the desired operating frequency band.

#### 2.4.2 Passive Mixer and IIP2 Calibration

The RF down-conversion to zero-IF is performed by a current-driven doublebalanced passive mixer. The passive mixer topology is chosen for its good linearity performance while keeping low 1/f noise and easy operation over a wide RF frequency range.

As shown in Fig. 2.6, at the RF input of the mixer, the received voltage (the output of the balun) is converted into current by an array of binary-scaled transconductors (*Gmix*), based on self-biased CMOS inverters. This array provides supplemental gain control of the receiver's RF front end. It consumes a maximum of 17 mA from the 1.1 V supply.

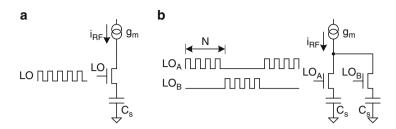

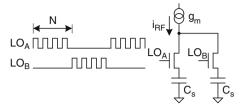

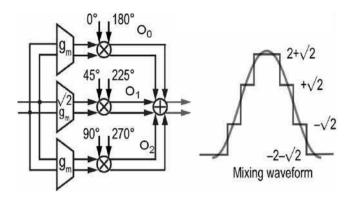

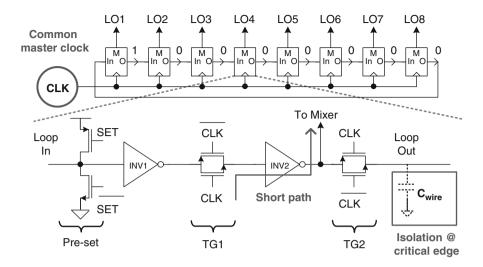

The resulting current is injected into the two switching quads for in-phase (I) and quadrature-phase (Q) down-conversion. The sources of the NMOS mixer switches are biased at half of the supply voltage by the baseband amplifiers. A 25% duty cycle LO provides 3 dB improvement in the gain of the mixer and hence improvement in the mixer's noise figure compared to the counterpart driven by LO with 50% duty cycle [20].

The 25% duty cycle LO signal is generated from the double-frequency signal coming out of the PLL. A rail-to-rail CMOS dynamic divider is placed closely to the mixer to limit LO-to-RF coupling. An AND-gate uses this to window the original 2LO signal, such that only one out of every two 2LO pulses passes, which results in a clean 25% duty cycle LO signal with minimal phase noise.

Finally, the baseband differential I and Q signals are obtained across the nodes n2pI, n2nI and n2nQ, n2pQ respectively. The baseband capacitor *CbI/CbQ* gives some initial out-of-band blocker selectivity before the output current is converted into a voltage by means of a trans-impedance amplifier (see Sect. 2.4.3).

As in all direct-conversion receivers, particular care must be paid to the minimization and/or calibration of second-order distortion components. In order to stop the leakage of second order distortion components from the RF blocks, the mixer transconductor is AC-coupled at both the input and the output. RF-to-LO or LO-to-RF coupling are limited by proper isolation and careful layout. The remaining source of second order input interception point (IIP2) degradation is the mismatch between the mixer switches [21]. Since sizing for intrinsic matching is impossible, we propose here a current injection into the positive/negative inputs of the switching quads, in contrast with [20] and [22] where a more conventional gate voltage fine tunability was proposed. The current injection has the advantage that it can be directly applied to an existing mixer core, without the need to split and reroute the LO distribution to the switch gates. Two bidirectional 6b current-steering DACs (Iip2p and Iip2n) inject small dc currents at nodes n1p and n1n. This IP2 compensating current will marginally modify the differential bias of the switches, compensating for either threshold voltage and mobility differential mismatches and therefore improving the receiver's second order distortion performance. The injected DC current also flows into the baseband and generates DC offset there, but this is easily corrected by the baseband DC offset compensating DACs IdcoI and IdcoQ. The IIP2 tuning is implemented directly after the RF transconductor and therefore impacts both quadrature paths. As a consequence, the second order distortion on both quadrature paths cannot be considered independently and therefore the IP2 performance should be evaluated from the complex receiver output, i.e. taking into account the amplitude and phase of the tones at the intermodulation frequency of both quadrature outputs. Analysis and measurements have shown that tuning *lip2p* and *lip2n* offers to minimize the complex second order intermodulation distortion measured from the receiver's quadrature outputs with a non-negligible but small impact on the receiver's DC offset. The impact of the compensation currents to suppress the residual DC offset (*Idcol* and *IdcoQ*) on the overall second order intermodulation distortion is however marginal. Automatic calibration can be performed in the receiver warm-up process or idle-time by generating calibration tones on-chip using the transmit path and exploiting a bilinear search algorithm in the receiver's digital baseband that is able to converge in a few steps, resulting in a complex RX IIP2 performance better than 50 dBm in all operating modes. Once this is fixed, the DC offset can be tuned on-line, together with other calibrations like quadrate accuracy as described in [23].

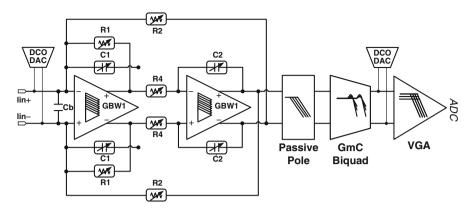

Fig. 2.7 Receiver analog baseband section

#### 2.4.3 Analog Baseband Chain

Based on a Tow-Thomas biquad topology, the transimpedance amplifier (TIA) converts the mixer's current output into a voltage signal by guaranteeing very low input impedance over frequency for improved out-of-band linearity. The TIA input impedance is given by:

$$Z_{in} = \frac{R_1}{(1 + sC_1R_1) \cdot [1 + A_1(s)] \cdot [1 + LG(s)]}$$

(2.2)

where  $R_I$  and  $C_I$  are shown in Fig. 2.7,  $A_I(s)$  is the open loop gain of the first amplifier, with gain-bandwidth product  $GBW_I$ , and LG(s) is the open loop gain of the Tow-Thomas biquad derived as:

$$LG(s) = -\frac{R_1}{sR_2R_4C_2 \cdot (1 + sC_1R_1)}$$

(2.3)

$Z_{in}$  is very close to zero at low frequencies, while it may increase at high frequencies, depending on the GBW of the first opamp. A maximum simulated out-of-band third order input interception point (IIP3) of 14 dBm can be achieved with a GBW of 400 MHz. To further reduce the out-of-band  $Z_{in}$  and boost out-of-band linearity, a capacitor  $C_b$  is placed across the virtual ground nodes.

Two complex conjugated poles (hence a 40 dB/decade attenuation) are generated with pole frequency  $\omega_p$  and quality factor Q given by:

$$\omega_p = \frac{1}{\sqrt{R_1 R_4 C_1 C_2}} \qquad \qquad Q = \frac{R_1}{\sqrt{R_2 R_4} \cdot \sqrt{\frac{C_1}{C_2}}}$$

(2.4)

To achieve flexible frequency discrimination and gain control, we employed binary-scaled arrays of analog components connected in parallel, as in [24]. Special care was placed in reducing silicon area and in sizing the array switches carrying useful signals. The switches are implemented as NMOS-PMOS transmission gates, and connected, whenever possible, to low impedance nodes.

Differently than in a simple integrator, biquad parameters in our topology can be independently tuned. For instance,  $R_1$  can be adjusted to achieve the specified Q, as suggested by (4), without changing the cut-off frequency;  $R_2$  and  $R_4$  can be tuned to configure the trans-resistance gain (from 1 to  $8k\Omega$ ) while keeping the bandwidth constant. By using this approach, Q can be tuned from 0.53 to 1.5, the cut-off frequency covers the range between 0.5 MHz and 20 MHz (or higher). Moreover, the switchable opamps approach [24] helps trade power consumption for bandwidth whenever lower out-of-band blockers are detected or lower cut-off frequencies are required.

After the TIA, many standards require further attenuation as the interferer power might be still quite high. As an active filtering block at this point would still need high out-of-band linearity, we decided to further attenuate interferers by using a flexible passive pole. Consequently, the final filter stage is a cheap Gm-C inverterbased biquad, as in [25], whose noise/linearity performance is not critical. Together with the TIA poles, the overall baseband provides flexible fifth order selectivity, but it can be conveniently switched to a third order if the Gm-C filter is bypassed. A VGA further maximizes the dynamic range with 24 dB gain in 16 logarithmic gain steps. As shown in Fig. 2.7, the DC offset is compensated at the virtual ground of the TIA and the VGA by injecting current in discrete steps through 6-bit current steering DACs.

#### 2.4.4 SAR ADC

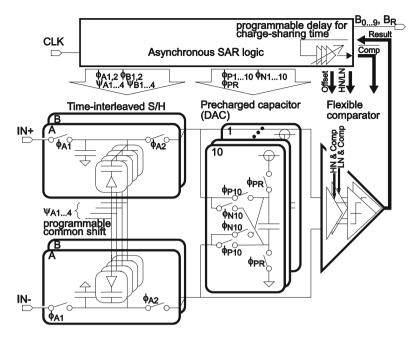

The ADC used in the receiver is based on the low-power charge-sharing SAR ADC architecture proposed in [26, 27]. This architecture offers sufficient speed for the intended applications, and lends itself very easily to integration in a nanoscale CMOS process, as the only active element is a comparator combined with capacitors, switches and a digital controller.

The ADC block diagram is shown in Fig. 2.8. It includes a time-interleaved bootstrapped S/H, a passive charge-sharing DAC, a redundant comparator topology and an asynchronous controller. As capacitor matching performance improves with technology, the resolution of the original 9 bit design in 90 nm [26, 27] could easily be extended to 10 bits without the need to increase the total capacitance value by a factor 4. The unit cap is chosen to be 30 fF. The least significant bits are constructed not by binary scaling the capacitance value but by pre-charging them to a lower voltage as in [26]. The flexible comparator scheme as in [27] uses a high-noise (HN) comparator in the first nine decisions and a low-noise (LN) comparator in the last one, and an extra decision for redundancy check to achieve almost 1-ENOB

Fig. 2.8 10 bit SAR ADC block diagram

improvement with low extra power. The comparator itself is based on [28]. It uses a dynamic pre-amp for low noise, and achieves an excellent noise/power trade-off.

The common-mode level (CM) at the comparator's inputs involves two important trade-offs. The settling speed of the charge-sharing is mainly determined by the NMOS sharing switches on-conductance, which is limited by the rather high threshold voltage combined with the low supply voltage of this low-power 40 nm process. To boost the conversion speed, the CM must be kept as low as possible. Hereto, the CM is shifted down right after the sampling operation. This has however also a significant impact on the thermal noise of the comparator and hence on the overall effective ADC resolution. This is even more important considering the increase of noise excess factor ( $\gamma$ ) in our 40 nm process and the strong dependence of the comparator pre-amplifier gain on the overdrive voltage of input-stage. As a compromise between noise and speed, a CM voltage around 0.33 V was chosen.

The total ADC achieves >9 effective bits resolution at a power budget of less than 1 mW, which is negligible in the total power budget. This is exploited in the receiver system budget by keeping the sampling frequency rather high, even for low-bandwidth standards. This oversampling allows to reduce the channel select filter's order, as there is no need to suppress interferers that would otherwise be aliased down to baseband by the sampling [4].

#### 2.5 Transmitter

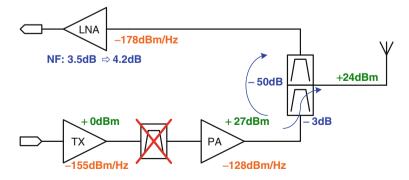

The SDR transmitter must support multiple standards at various transmit frequencies. These standards include FDD standards, in which the transmitter is active while receiving. The transmitter emits, besides the wanted output signal, unwanted outof-band noise as well. This noise is then further amplified by the external power amplifier before being fed to the duplexer, which connects the receive/transmit input/output with the antenna (Fig. 2.9). As the isolation between RX and TX is not infinite, part of the transmit out-of-band noise ends up at the input of the receiver and adds effectively to the receiver system noise. Traditionally, this transmitter noise is filtered by adding an interstage surface acoustic wave (SAW) filter between the integrated pre-power amplifier and the external power amplifier. As this adds up to the system BoM cost and reduces the flexibility, it is commercially attractive to avoid this interstage filter, which puts very though requirements on the out-of-band noise specifications of the transmitter.

The carrier-to-noise ratio (CNR) specifications for SAW-less FDD transmitters should be defined considering the complete system, including both receiver and transmitter and the external components. Figure 2.9 shows one example scenario. A receiver with a NF of 3.5 dB is considered and from system analysis, a maximal degradation up to a NF of 4.2 dB is acceptable. The transmitter noise power density which is acceptable at the receiver input for this condition is  $-178 \,dBm/Hz$ . For a duplexer isolation of 50 dB, the out-of-band noise at the output of the power amplifier is maximally  $-128 \,dBm/Hz$ . For a PA with a gain of 27 dB, the maximal noise at the output of the integrated pre-power amplifier is  $-155 \,dBm/Hz$  if the interstage SAW filter is omitted. For an output power of  $+24 \,dBm$  at the antenna, and an insertion loss of 3 dB in the duplexer, the RMS power at the output of the PPA is 0 dBm, and the required CNR is thus  $-155 \,dBc/Hz$ . From this analysis it is clear that the final CNR requirement for the transmitter has a certain variability that depends on external and system considerations, such as the isolation of the duplexer and the NF of the receiver and the degradation we can afford.

Fig. 2.9 SAW-less transmitter operation in FDD mode

Transmitter out-of-band noise has a significant contribution from upconverted baseband noise. To limit this contribution, the out-of-band noise at baseband has to be intrinsically low or filtered out before being upconverted. In a traditional current mode Gilbert active mixer, the baseband signal is a current and its noise component, which also includes the noise of the mixer's bias current, is very hard, if not impossible to be filtered, as it is a current as well. As the current-mode noise cannot be filtered at baseband and as we do not want to filter it with a SAW filter at RF, a current-mode upconverter requires an intrinsically low noise mixer design. This results however in a large power consumption, in the order of what is typically needed in a pre-power amplifier. As a result, in a current-mode design the mixer has to be combined with the PPA into a power mixer to maintain power efficiency [29].

If a voltage based design is considered, the baseband noise can be filtered easily in the voltage domain, which results in less stringent intrinsic noise requirements for the baseband, and in lower power consumption. For this reason, a voltage sampling mixer [14] was chosen for the presented SDR transmitter. The mixer is followed by a pre-power amplifier (PPA), whose noise contribution should be sufficiently low as it cannot be filtered at RF. This results in a non negligible current consumption, and as a result only a single stage is affordable in the PPA, as adding an extra stage would result in high power consumption.

Besides out-of-band noise, power control is another important aspect in the transmitter. The strategy adopted in the presented transmitter is to distribute the coarse gain control over the three main building blocks, while reserving one baseband DAC bit (6 dB) for digital fine tuning of the gain. From output to input, the PPA has a gain tuning range of 36 dB, the Mixer of 12 dB and the TI-LPF of 18 dB. By adding the 6 dB fine tune digital gain, a total control range of 72 dB is implemented.

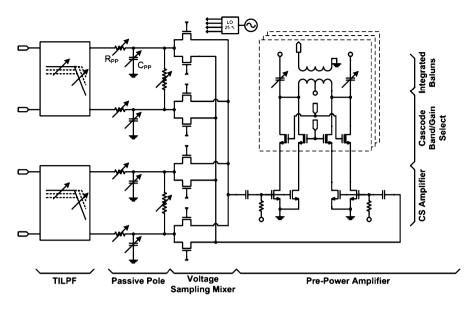

The total transmit chain architecture is depicted in Fig. 2.10, whose individual blocks are described in more detail in the next sections.

#### 2.5.1 The Transmit Baseband Section

The transmitter's baseband section is actually a copy of part of the receiver's channel select filter, where again the reconfigurability of the SDR philosophy is used that allows achieving the desired performance by simply reprogramming it into the corresponding mode. It consists of a Tow-Thomas transimpedance biquadratic low-pass section (TI-LPF) with programmable bandwidth (400 kHz up to more than 20 MHz) and a passive pole to filter out out-of-band noise.

Similarly to the receive baseband, scalable opamps are used of which the gainbandwidth product can be adjusted in eight steps from 60 to 480 MHz, exchanging filter's linearity for current consumption [24]. The DC offset can be compensated by injecting a small DC current at the input of the TI-LPF through integrated calibration current DACs.

Fig. 2.10 TX block diagram

#### 2.5.2 The Mixer

The mixer is the heart of the transmitter and the key component for low-noise operation. As discussed above a voltage-mode mixer was chosen, as it offers the possibility of baseband noise filtering before the upconversion. In this design, we adopt a differential direct voltage sampling mixer [14]. The baseband signals from the TI-LPF are first filtered by a passive RC low-pass filter (Fig. 2.10). This reduces the required noise performance of the preceding stage, which limits its power consumption. The baseband voltage is sampled alternatively from I and Q with a 25% duty cycle LO signal onto the load capacitance, which is actually the input capacitance of the subsequent PPA. The sampling behavior of the mixer results in charge and discharge currents from the baseband section that must flow through the passive pole's resistor. The resulting voltage drop reduces the overall mixer's conversion gain. As the charge currents are proportional to the LO frequency and the load capacitance, and the voltage drop over the LPF is proportional to its resistive component, the effective mixer's conversion gain (CG) is given by [30]:

$$CG = \frac{2\sqrt{2}}{\pi} \times \frac{Z_{mix}}{R_{PP} + Z_{mix}}$$

$$Z_{mix} = R_{sw,on} + \frac{1}{2 \cdot F_{IO} \cdot C_{load}}$$

(2.5)

where  $R_{PP}$  is the value of the passive pole resistor,  $Z_{mix}$  is the mixer input impedance,  $R_{sw,on}$  is the on-resistance of the LO switches and  $C_{load}$  is the input capacitance of the load, i.e. the PPA.

The mixer must therefore be carefully co-designed with the active LPF impedance and with the PPA load, considering the full system requirements, as the LO frequency and the input capacitance have an impact on the mixer's conversion gain when combined with the passive pole's resistor. The latter has an impact on the linearity and noise requirements of the active LPF and on the area (a small resistor requires more driving strength of the TI-LPF, and a bigger passive pole's capacitor for a given filtering). In our design, a nominal value of  $300\Omega$  was chosen as a compromise between noise filtering and gain roll-off at higher frequencies. Note that the resistor of the passive pole is tunable. In combination with a second tunable resistor, 12 dB of gain variability is obtained in the mixer.

As the voltage sampling mixer core is fully passive, the only contributor to the power consumption is the 25% duty cycle generator. Its design is based on CMOS-like rail-to-rail logic, with proper sizing to achieve sufficient low phase noise.

#### 2.5.3 The Pre-power Amplifier

The final stage in the transmitter is the pre-power amplifier (PPA). It takes the upconverted signal from the mixer, amplifies it and feeds it to the  $50\Omega$  input of an (off-chip) power amplifier. The PPA has to combine low noise for FDD operation with high linearity for EVM and ACPR performance. From a cascade analysis, the PPA has to achieve 10 dB differential to single-ended voltage gain. As discussed before, this gain has to be realized in a single stage to limit the current consumption. Furthermore, as the PPA's input capacitance is the sampling capacitor of the mixer, the PPA size is limited to avoid excessive mixer conversion gain degradation.

The PPA schematic is modular and is presented in Fig. 2.10. It consists of a set of parallel Common Source (CS) amplifiers, which can be turned on or off by thick oxide cascode transistors. The latter protect the 40 nm CS transistors from the 2.5 V supply, provide discrete 6 dB gain control steps and select one out of three possible outputs. As part of the PPA is turned off when gain and output power are reduced, the DC power consumption is proportional to the output power. This is especially beneficial, as in most practical situation (e.g. as described in DG09 [31]), operation at maximal output power is limited in time.

The PPA has been implemented pseudo differentially and fits with the differential mixer. Three on-chip baluns have been integrated to provide single ended outputs. The baluns consist of a transformer realized in the two top metal layers of the technology that are approximately  $0.8 \mu m$  thick. Their primary windings include a center tap to provide the DC bias current of the amplifier. The transformers were designed by combining two ASITIC [32] generated coils. This simulator was also used to derive a simplified transformer model, including the limited coupling, the limited Q-factor and the parasitics to ground and between both coils. This approach

using a simplified model speeds up the exploration phase of the design. When the final balun dimensions were defined, the simplified model was validated with a more precise finite-element generated model. Although the PPA core is intrinsically wide-band, the baluns introduce some bandwidth limitation. The center frequencies of the baluns are defined with a tunable parallel capacitor and spread over the frequencies from 700 MHz up to 3 GHz. In this prototype, the center frequency balun has been bypassed to provide a wide-band differential output for testing purposes. This can be combined with an external balun or differential amplifier as required. Measurements have been successfully performed both with internal and external baluns.

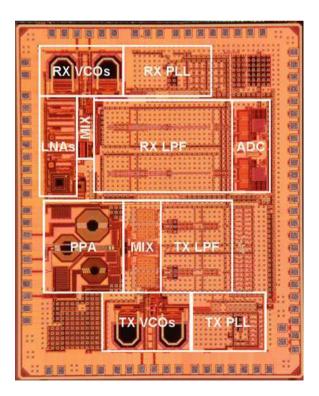

#### 2.6 Measurement Results

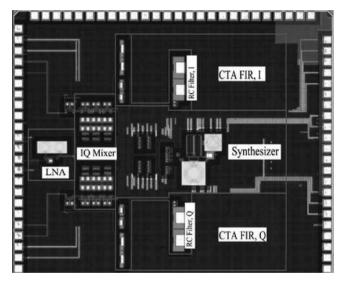

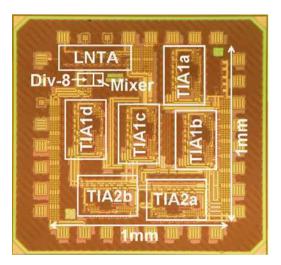

The microphotograph of the complete SDR prototype with the most important blocks annotated is shown in Fig. 2.11. It is implemented in a 1.1 V 40 nm LP CMOS technology and measures 2.0 by 2.5 mm<sup>2</sup>.

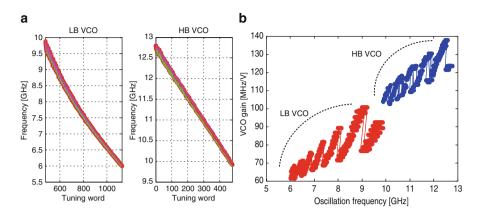

After an initial design in 45 nm technology that was slightly off-centered [15], the tuning range of the new dual VCO set in 40 nm CMOS covers the full range from 5.95 until 12.85 GHz as shown in Fig. 2.12. The VCO gain is calibrated to be

Fig. 2.11 Microphotograph of the complete transceiver

Fig. 2.12 (a) Total frequency range spanned by the two VCOs; (b) VCO gain programmed to be proportional to the center frequency

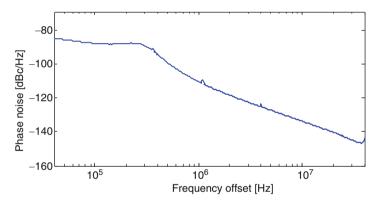

Fig. 2.13 PLL phase noise measurement at 7.2 GHz

proportional to the center frequency, using a procedure adapted from [17], as this results in a constant PLL BW for a fixed charge pump and loop filter.

The closed-loop PLL phase noise at 7.2 GHz shown in Fig. 2.13 yields  $-32 \, dBc$  in-band integrated phase noise. The measured phase noise value at 20 MHz offset frequency is  $-140 \, dBc/Hz$ , which could be extrapolated to  $-158 \, dBc/Hz$  at 900 MHz operation after division be 8. The 40 MHz reference spur sits at  $-80 \, dBc$ . The full synthesizer draws 30–40 mA from the 1.1 V supply

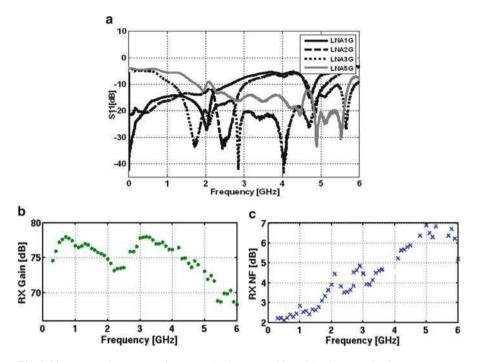

To evaluate the receiver's RF performance, it is measured at baseband at the output of the TI-LPF (which converts the mixer's output current to voltage). The input matching of the different LNAs is shown in Fig. 2.14a. In the frequency of interest, each of the LNAs provides S11 better than -10 dB. The measured maximal gain of the receiver (LNA, mixer and TI-LPF) is approximately 75 dB (with a peak of 77 dB) and gradually decreases at high frequency (around 5 GHz and

Fig. 2.14 Measured RX RF performance; (a) input matching; (b) gain; (c) noise figure

beyond) below 72 dB due to the combined effect of LNA and mixer's gain roll-off. The peaks and dips over the frequency range are due to fact that the gains of the various LNAs are not exactly matched and different LNAs are chosen to operate at different frequencies. The measured NF of the receiver at peak-gain settings is shown in Fig. 2.14c. The total NF ranges from 2.3 dB to 7 dB over the frequency range. The peaks and dips in the NF plot are due to the dependency of NF on RX gain.

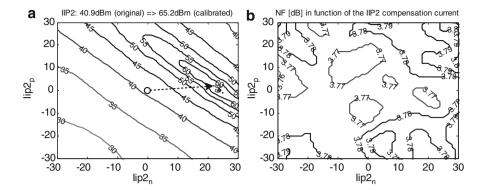

Figure 2.15a shows the measured IIP2 performance for the whole tuning range of both 6 bit IIP2 DACs on each differential line. The receiver operates at 5 GHz with a channel bandwidth of 20 MHz and at maximal gain. Two out-of-band CW blockers at arbitrary offset frequencies of 83 and 85 MHz are provided to the receiver input. The default IIP2 performance of 41 dBm (configuration 0/0 in Fig. 2.15a) can be improved in the measured area up to 65 dBm (configuration 23/1). Extensive measurements over different modes show a consistent improved IIP2 performance beyond 60 dBm, which is enough to cope with the toughest FDD cellular requirements. Figure 2.15b shows the (negligible) impact of IIP2 calibration on NF performance.

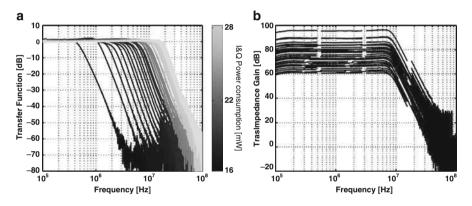

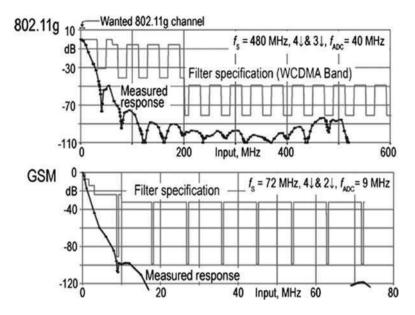

The RX analog baseband can be separately tested thanks to on-chip test circuitry that allows providing an external input signal to the TIA input. From a 2-port network analyzer measurement, the several transfer function settings are shown in Fig. 2.16a for 0 dB voltage gain. The low-pass filter's bandwidth ranges from

Fig. 2.15 (a) Measured IIP2 performance over the IP2 control tuning range; (b) impact of IP2 tuning on the receiver system NF

**Fig. 2.16** (a) Analog baseband transfer function, including VGA, for a constant 100 dB/dec selectivity and different bandwidth/power consumption levels; (b) possible AGC settings for the analog baseband section

0.5 up to more than 20 MHz, while the transition bandwidth is kept constant and allows up to 100 dB/dec Butterworth-like attenuation. Power consumption scales with the bandwidth from 16 to 28 mW: these numbers include TIA (50%), Gm-C filter (10%) and VGA (40%), for both I and Q channels. In addition to this coarse tuning capability, the cut-off frequency can be tuned with a maximum 5% error to compensate for  $\pm 40\%$  process deviation. Figure 2.16b shows all the possible transimpedance gain settings of the analog baseband; the gain range is about 36 dB while the minimum gain step is below 1 dB. The influence of baseband DC offset is negligible in both these tests.

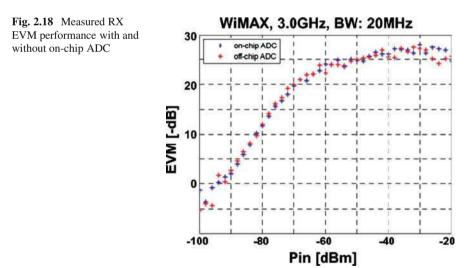

The ADC is measured separately, as reported in Fig. 2.17. The maximal sampling speed is 60 MS/s, with a power consumption of 1.2 mW. At lower speeds, the power decreases proportionally. An SNDR of 54 dB (9.3 ENOB) is obtained. Maximum DNL and INL are  $\pm 1.4$  and  $\pm 0.8$  LSB, respectively. Using the classical figure-

Fig. 2.17 Measured ADC performance: (a) near-Nyquist FFT; (b) SNDR vs input frequency

| Mode                  | Ref                              | CMOS<br>node    | Area<br>(mm <sup>2</sup> ) | NF<br>(dB)     | IIP3<br>(dBm)       | IIP2<br>(dBm) | PDC<br>(mW)  |

|-----------------------|----------------------------------|-----------------|----------------------------|----------------|---------------------|---------------|--------------|

| DVB-H<br>0.2–0.7 GHz  | This work [33]                   | 40 nm<br>65 nm  | 5<br>7                     | 2.6<br>2.2     | -4.6/+9<br>-6/-3    | 53<br>40      | 55–83<br>138 |

| GSM/EDGE<br>0.9 GHz   | This work<br>[34]                | 40 nm<br>90 nm  | 5<br>7.4                   | 2.4<br>2       | -17/-4.7<br>-25/-20 | 64<br>46      | 54–77<br>84  |

| WCDMA<br>0.85/2.1 GHz | This work [35]                   | 40 nm<br>130 nm | 5<br>8.7                   | 2.4/4<br>2.5/3 | -9/-6<br>-5         | 68<br>55      | 55–84<br>48  |

| GPS<br>1.5 GHz        | This work<br>[ <mark>36</mark> ] | 40 nm<br>130 nm | 5<br>6.6                   | 2.6<br>2.5/3   | -3/-4 25/-23        | 56<br>43      | 54–77<br>49  |

| MIMO<br>WiMAX         | This work                        | 40 nm           | 10                         | 3.8            | -12/-1              | 61            | 112–214      |

| 2.5 GHz               | [37]                             | 90 nm           | 12                         | 3.5            | -11/12              | N/A           | 300          |

| MIMO<br>WLAN          | This work                        | 40 nm           | 10                         | 3.4/7          | -15/-8              | 59            | 112–270      |

| 2.4/4.8 GHz           | [38]                             | 180 nm          | 18                         | 4/4.5          | -12/6               | N/A           | 495          |

Table 2.1 RX+LO performance summary and comparison with CMOS state-of-the-art

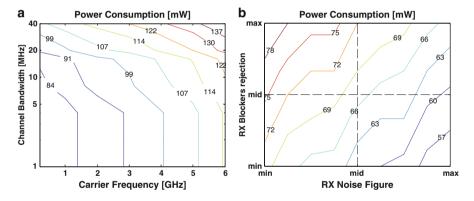

**Fig. 2.19** RX + LO Energy awareness: (a) Measured Receiver Power Consumption over all the RF frequency range and channel bandwidth. (b) Possible range of power consumption in GSM receiving mode by the required noise/selectivity and linearity requirements

of-merit formula, FoM =  $P_{DC}/(2^{ENOB}.F_S)$ , a value of 34 fJ per conversion step is obtained. Figure 2.18 reports the measured RX EVM performance in 3 GHz WiMAX mode (20 MHz BW), either using the analog output of the VGA or with the on-chip ADC, showing no significant difference

Table 2.1 compares the performance measured on the presented RX + LO circuits with state-of-the-art CMOS transceivers under different configuration modes showing in most cases comparable performance, area and power consumption. One of the unique features of an SDR transceiver is its energy awareness: Fig. 2.19a shows how the RX + LO measured power consumption changes according to the required

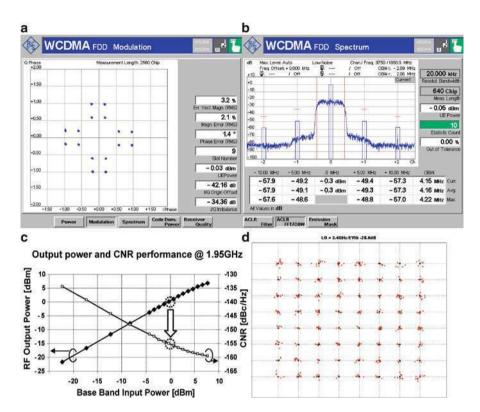

Fig. 2.20 TX performance: (a) WCDMA constellation diagram; (b) output spectrum; (c) output power and noise at 1.95 GHz; (d) EVM for 802.11 g 64QAM at 0 dbm output power

operational mode. While a GSM operation at 900 MHz and small bandwidth will require a maximal power consumption of about 80 mW, a Wi-Fi .11n at 5 GHz and 40 MHz channel bandwidth will require about 130 mW. On top of such standard-related trade-offs, it is also possible to provide run-time energy awareness by sensing the environmental conditions. Blockers could for example be sensed by adding power detectors at various filtering stages in the receive chain, SNR could for example be sensed to tune the receiver to a 'minimal margin' scenario. To exemplify this, Fig. 2.19b shows how a GSM mode power consumption can actually change based on the required noise/linearity performance of the receiver and an AGC algorithm that guarantees just a good-enough SNR rather than maximal SNR. Receiving a call in the centre of the city will not require 2dB RX noise figure (NF). Or receiving in the countryside is likely not to impose the toughest blocking conditions foreseen by the standards. Such trade-offs will allow to save energy where/when possible.

To measure the transmitter, the I/Q baseband signals are converted from the voltage of the measurement equipment into a current needed for the TI-LPF reconstruction filter input over an external  $5k\Omega$  resistor. The main transmitter

measurements are presented in Fig. 2.20 in for various modes of operation. An output 1 dB gain-conpression point (OP1dB) of around 7 dBm has been measured with the integrated baluns from 850 MHz up to 2 GHz and better than 4 dBm up to 2.5 GHz. A linear OFDM and WCDMA modulated signal with an EVM from 2.7 to 4% was measured up to 0 dBm output power. At 2.5 GHz, 2.5% EVM was achieved with an external LO for -2.5 dBm output power. An 8-PSK modulated signal up to 4.8 dBm was measured at 850 MHz with a spectral mask better than -61 dBc at 400 kHz offset. At 1.8 GHz, 1 dBm output power was measured.

The CNR was measured in two ways. First, a single tone was transmitted by applying a DC signal at baseband, and a phase-noise analyzer was used to determine the noise floor of the transmitter. This was then subtracted from the maximal linear RMS output power (that needs a certain back-off from OP1dB, depending on the modulation) to obtain the CNR. For the EDGE-mode of operation, a CNR of -156 dBc was measured at 20 MHz offset for a 900 MHz carrier with an external LO. The main noise contributor in this mode is baseband noise from the active filter, which is not filtered by the passive pole, due to its relatively high cut-off frequency. For WCDMA mode, a full linear WCDMA signal was transmitted. The TX band signal was filtered by a reversed duplexer (transmitter at output port), and the noise at the RX port in the receive band was measured, after de-embedding of the duplexer's insertion loss. These measurements result in -156 dBc/Hz at 45 MHzoffset for an 850 MHz LO and -153 dBc/Hz at 190 MHz offset for a 1,950 MHz LO. When using an external LO, -156 dBc/Hz was obtained for the 1,950 MHz case as well. At 1.95 GHz, the transmitter's CNR is mainly limited due to the phase-noise generated in the LO 25% duty cycle generator. It is caused by the jitter introduced by the limited relative speed of the LO signal's edges. When using the internal VCO, its phase noise and the noise of the first LO buffer at 7.8 GHz is added to this. At 850 MHz, the limitation comes from the baseband noise due to the smaller (45 MHz) offset between TX and RX band and the resulting reduced filtering from the passive pole and the active second order filter.

The power consumption of the transmitter varies with the required performance. Depending on the output power (TRA linearity/PPA Gain) and the frequency (LO25), the transmitter consumes from 20 up to 38 mA from the 1.1 V supply and 6–30 mA from the 2.5 V supply.

Table 2.2 summarizes the main TX measurement results and compares the performance achieved by this TX work with state-of-the-art WCDMA CMOS transmitters.

## 2.7 Conclusions

In this chapter, we have presented a full transceiver front-end for an SDR platform in a 40 nm LP CMOS process. Quadrature frequency synthesis is obtained with a set of two VCOs covering the 6–12 GHz range embedded in a fractional-N PLL, followed by a chain of rail-to-rail CMOS divide-by-2 circuits. Four parallel LNAs, a 25% duty

| Table 2.2 TX performance                                                            |               | l comparison w   | summary and comparison with CMOS state-of-the-art |                                             |                |                   |                |

|-------------------------------------------------------------------------------------|---------------|------------------|---------------------------------------------------|---------------------------------------------|----------------|-------------------|----------------|

|                                                                                     |               |                  | ACLR1/2                                           |                                             |                | LOFT <sup>b</sup> | IRR            |

| RF Freq<br>TX mode                                                                  | Pout<br>(dBm) | EVM (%)          | Spectrum<br>(dBc)                                 | CNR<br>(dBc/Hz)                             | OP1dB<br>(dBm) | @0dBm<br>(dBm)    | @0dBm<br>(dBm) |

| 850 MHz WCDMA Band<br>V                                                             | -0.3          | 2.7              | -47/-58                                           | -156@45 MHz                                 | 6.7            | -66               | 45             |

| 900MHz EDGE Mode <sup>a</sup>                                                       | 4.8           |                  | Spectrum: -61dBc@400kHz<br>-74dBc@600kHz          | -156@20 MHz<br>-153@10 MHz                  | 6.7            |                   |                |

| 1.8 GHz EDGE Mode <sup>a</sup>                                                      | 1             |                  | Spectrum: -65dBc@400kHz<br>-70dBc@600kHz          | -152@20 MHz<br>-150@10 MHz                  | 7.5            |                   |                |

| 1.95 GHz WCDMA Band I                                                               | 0             | 3.2              | -49/-57                                           | $-153/-156^{\mathrm{a}} @ 190 \mathrm{MHz}$ | 7.5            | -58               | 48             |

| 2.4 GHz                                                                             | -0.5          | 4.2              | -47/-60                                           |                                             | 4.2            | -59               | 45             |

| (64QAM/20 MHz) on-chip<br>balun WLAN Mode                                           |               |                  |                                                   |                                             |                |                   |                |

| 2.4 GHz                                                                             | 0             | 4                | -46/-62                                           |                                             | 4.7            | -59               | 46             |

| (64QAM/20 MHz) ext.<br>Balun WLAN Mode                                              |               |                  |                                                   |                                             |                |                   |                |

| 2.5 GHz                                                                             | -2.5          | 2.5              | -46/-62                                           |                                             | 4.6            | -53               | 43             |

| (64QAM/20 MHz) int<br>Balun/ext VCO WiMAX<br>mode <sup>a</sup>                      |               |                  |                                                   |                                             |                |                   |                |

|                                                                                     | CMOS          | Area             | ACLR                                              | @Pout                                       | CNR            | PDC               | @Pout          |

|                                                                                     | node          | $(mm^2)$         | (dB)                                              | (dBm)                                       | (dBc/Hz)       | (mW)              | (dBm)          |

| [39]/[40]                                                                           | 180 nm        | 5                | -42.6                                             | +5                                          | 160–3°         | 120               | +5             |

|                                                                                     |               |                  |                                                   |                                             |                | 06                | -8             |

| [29]/[41]                                                                           | 180 nm        | 4.5 <sup>c</sup> | -46                                               | +3.8                                        | 163            | 236               | 3.8            |

|                                                                                     |               |                  |                                                   |                                             |                | 75                | min            |

| [42]                                                                                | 130           | 7.5°             | -43                                               | L                                           | 161            | 100               | avg            |

| This work                                                                           | 40 nm         | 1.3              | -49                                               | 0                                           | 156            | 90                | $^+1$          |

| <sup>a</sup> External VCO<br><sup>b</sup> LO feed through<br><sup>c</sup> Estimated |               |                  |                                                   |                                             |                |                   |                |

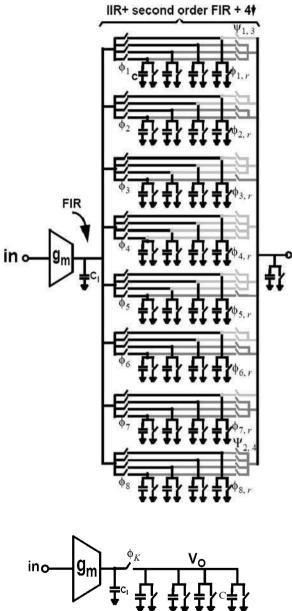

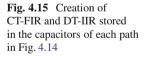

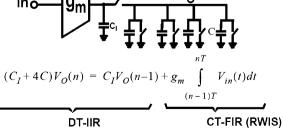

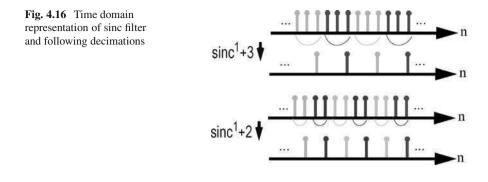

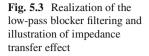

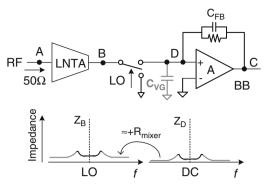

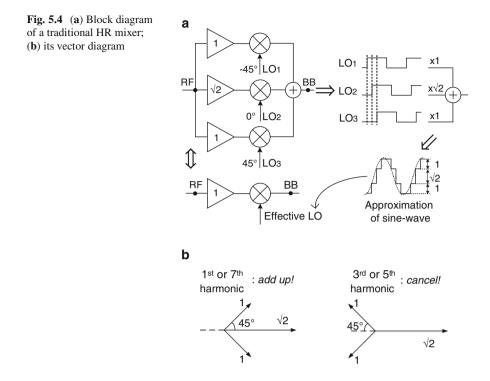

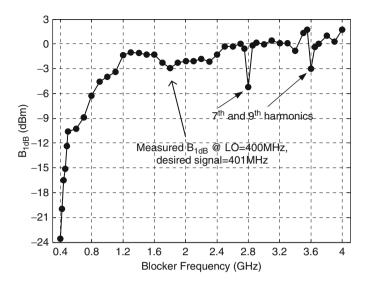

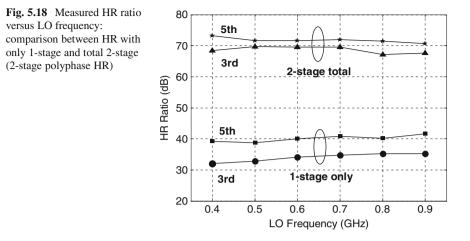

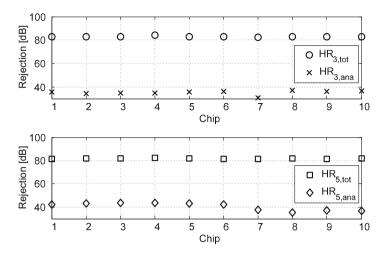

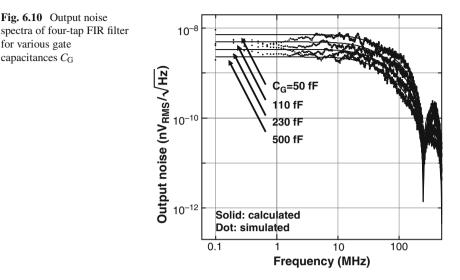

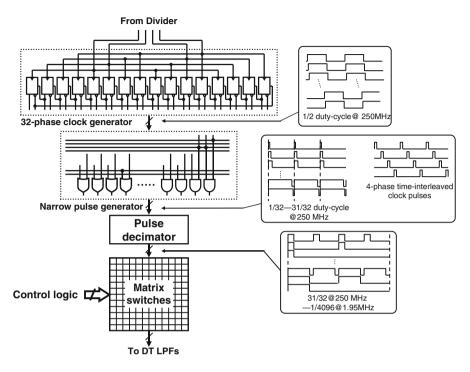

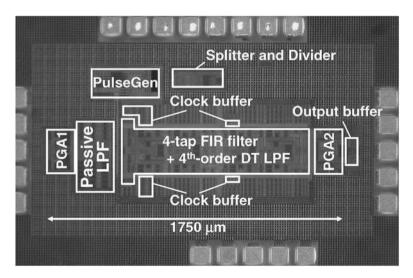

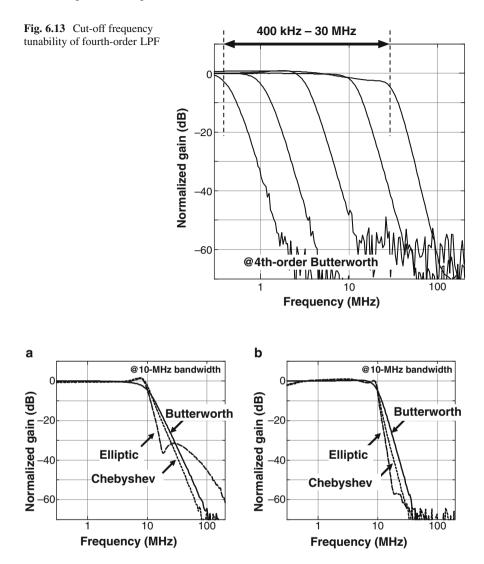

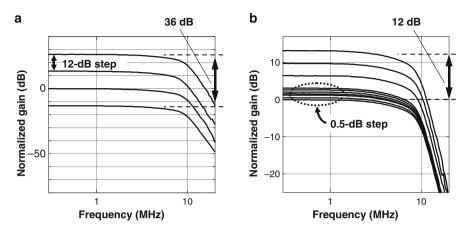

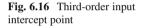

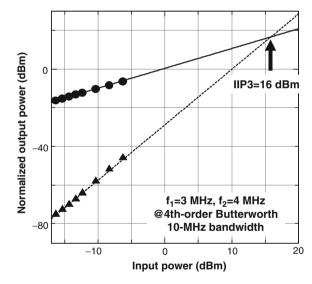

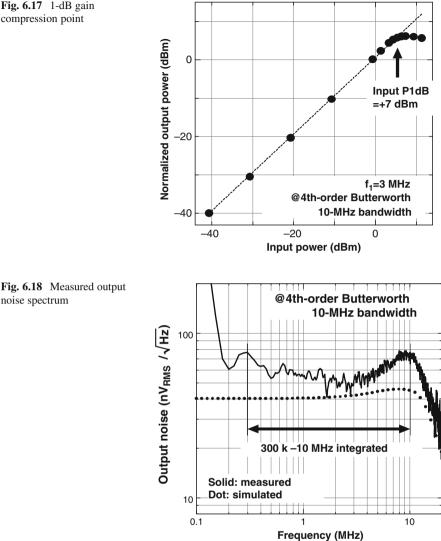

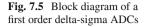

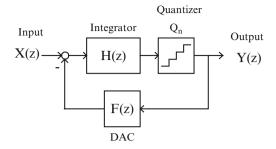

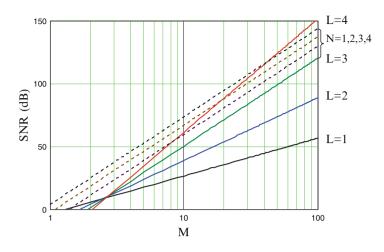

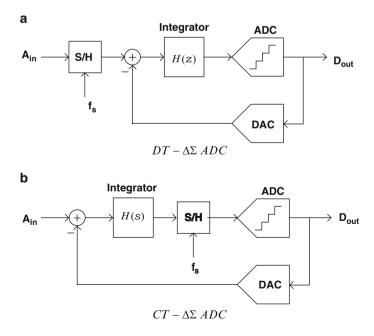

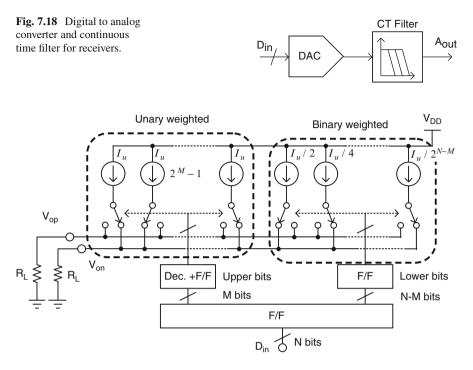

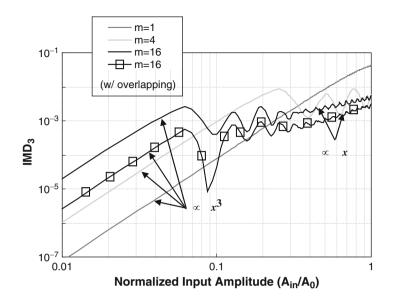

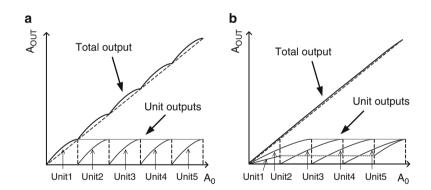

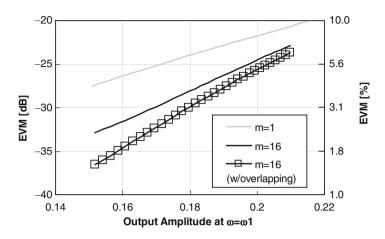

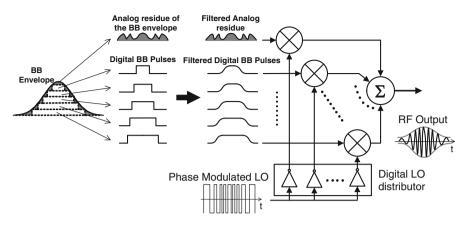

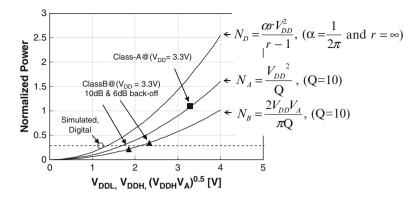

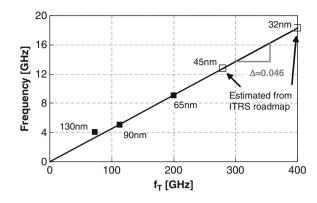

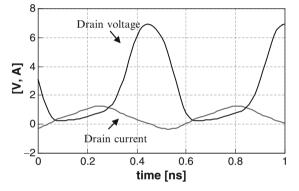

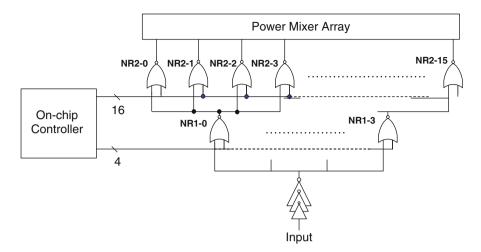

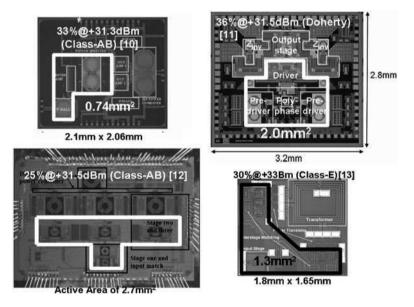

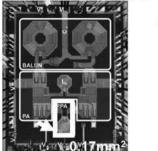

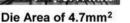

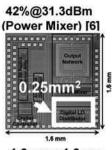

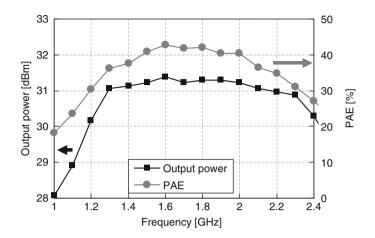

30