Lecture Notes in Electrical Engineering 82

# M. Haykel Ben Jamaa

# Regular Nanofabrics in Emerging Technologies

Design and Fabrication Methods for Nanoscale Digital Circuits

## Lecture Notes in Electrical Engineering

Volume 82

For further volumes: http://www.springer.com/series/7818 M. Haykel Ben Jamaa

# Regular Nanofabrics in Emerging Technologies

Design and Fabrication Methods for Nanoscale Digital Circuits

M. Haykel Ben Jamaa Commissariat à l'Energie Atomique (CEA-DRT-LETI-DACLE-LISAN) Rue des Martyrs 17 38054 Grenoble France e-mail: haykel.ben\_jamaa@a3.epfl.ch

ISSN 1876-1100

e-ISSN 1876-1119

ISBN 978-94-007-0649-1

e-ISBN 978-94-007-0650-7

DOI 10.1007/978-94-007-0650-7

Springer Dordrecht Heidelberg London New York

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: eStudio Calamar, Berlin/Figueres

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Acknowledgments

I am thankful to Prof. Giovanni De Micheli and Prof. Yusuf Leblebici for their support of this work. I would like to dedicate this book to my family, especially to my parents.

## Contents

| 1 | Intr | oductio  | )n                                        | 1  |  |  |  |

|---|------|----------|-------------------------------------------|----|--|--|--|

|   | 1.1  | The L    | inear Scaling                             | 4  |  |  |  |

|   | 1.2  |          | atest Milestones                          | 6  |  |  |  |

|   |      | 1.2.1    | Fabrication Technology                    | 6  |  |  |  |

|   |      | 1.2.2    | Device Design                             | 8  |  |  |  |

|   |      | 1.2.3    | System Design                             | 11 |  |  |  |

|   |      | 1.2.4    | Design Tools                              | 12 |  |  |  |

|   | 1.3  | Emerg    | ging Technologies                         | 13 |  |  |  |

|   |      | 1.3.1    | Selecting Emerging Technologies           | 14 |  |  |  |

|   |      | 1.3.2    | CMOS Extensions                           | 14 |  |  |  |

|   |      | 1.3.3    | Novel Information Processing Technologies | 16 |  |  |  |

|   | 1.4  | Regul    | ar Architectures and Fabrics              | 18 |  |  |  |

|   |      | 1.4.1    | The Need for Regularity                   | 19 |  |  |  |

|   |      | 1.4.2    | CMOS Many-Core Architectures              | 20 |  |  |  |

|   |      | 1.4.3    | Via Patterned Gate Arrays                 | 21 |  |  |  |

|   |      | 1.4.4    | Crossbar Architecture                     | 21 |  |  |  |

|   |      | 1.4.5    | NanoPLA                                   | 22 |  |  |  |

|   |      | 1.4.6    | CMOS/Molecular Hybrid Systems             | 23 |  |  |  |

|   | 1.5  |          |                                           |    |  |  |  |

|   |      | 1.5.1    | SiNW Technology.                          | 24 |  |  |  |

|   |      | 1.5.2    | CNT Technology                            | 26 |  |  |  |

|   | 1.6  | Organ    | ization of the Book                       | 27 |  |  |  |

|   | Refe | erences  |                                           | 28 |  |  |  |

| 2 | Fab  | ricatior | n of Nanowire Crossbars                   | 33 |  |  |  |

|   | 2.1  | Nanov    | wire Fabrication Techniques               | 34 |  |  |  |

|   |      | 2.1.1    | Bottom-up Techniques                      | 34 |  |  |  |

|   |      | 2.1.2    | Top-Down Techniques.                      | 37 |  |  |  |

|   | 2.2  | Crossl   | bar Technologies                          | 41 |  |  |  |

|   |      | 2.2.1    | Fluid-Directed Assembly                   | 41 |  |  |  |

|   |      | 2.2.2    | Electric-Field-Assisted Assembly          | 42 |  |  |  |

|   |      | 2.2.3   | Nanomold-Based Nanowire Crossbars         | 42  |

|---|------|---------|-------------------------------------------|-----|

|   |      | 2.2.4   | Crossbar Switches                         | 43  |

|   |      | 2.2.5   | Comparison Between Crossbar Technologies  | 43  |

|   | 2.3  | Fabric  | ation Facilities at EPFL                  | 44  |

|   |      | 2.3.1   | Photolithography                          | 45  |

|   |      | 2.3.2   | Etching                                   | 46  |

|   |      | 2.3.3   | Thin Films                                | 47  |

|   |      | 2.3.4   | Wafer Cleaning.                           | 48  |

|   |      | 2.3.5   | Process Control.                          | 48  |

|   | 2.4  | Proces  | ss Flow                                   | 49  |

|   | 2.5  | Proces  | ss Optimization                           | 52  |

|   |      | 2.5.1   | Etch of Sacrificial Layers.               | 52  |

|   |      | 2.5.2   | Spacer Definition                         | 55  |

|   |      | 2.5.3   | Gate Stack                                | 57  |

|   | 2.6  | Devic   | e Characterization                        | 58  |

|   |      | 2.6.1   | Structural Characterization               | 58  |

|   |      | 2.6.2   | Electrical Characterization               | 61  |

|   | 2.7  | Potent  | tial Applications                         | 65  |

|   |      | 2.7.1   | Crossbar Structures                       | 65  |

|   |      | 2.7.2   | Single Poly-Si Nanowire Memory            | 65  |

|   |      | 2.7.3   | Memristors                                | 66  |

|   |      | 2.7.4   | Nanowire Decoders                         | 67  |

|   | 2.8  | Discus  | ssions                                    | 68  |

|   | 2.9  |         | er Contributions and Summary              | 69  |

|   | Refe | -       | ·····                                     | 70  |

| 3 | Deco | oder Lo | ogic Design                               | 75  |

|   | 3.1  | Crossl  | bar Architecture                          | 76  |

|   | 3.2  | Decod   | ler and Encoding Types                    | 77  |

|   |      | 3.2.1   | Decoder Design and Fabrication            | 78  |

|   |      | 3.2.2   | Encoding Schemes                          | 80  |

|   | 3.3  | Multi-  | Valued Logic Encoding                     | 80  |

|   |      | 3.3.1   | Circuit Design with Multi-Valued Logic    | 81  |

|   |      | 3.3.2   | Semantic of Multi-Valued Logic Addressing | 81  |

|   |      | 3.3.3   | Code Construction.                        | 84  |

|   |      | 3.3.4   | Defect Models                             | 86  |

|   |      | 3.3.5   | Errors in the k-Hot Code Space            | 90  |

|   |      | 3.3.6   | Errors in the NRC Space                   | 98  |

|   |      | 3.3.7   | Assumptions of the Simulations            | 104 |

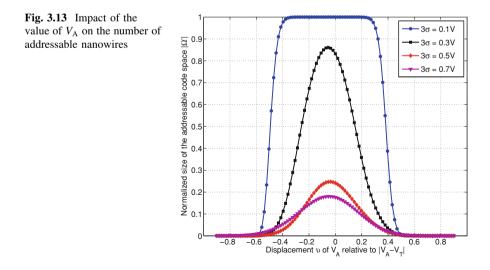

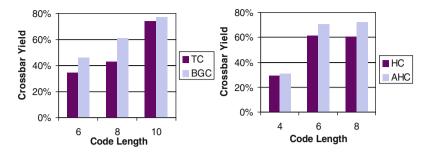

|   |      | 3.3.8   | Simulations of the Addressable Code Space | 106 |

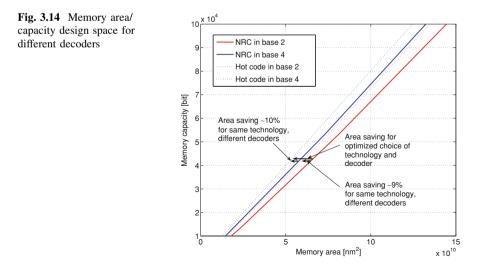

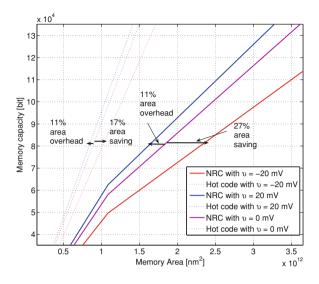

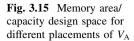

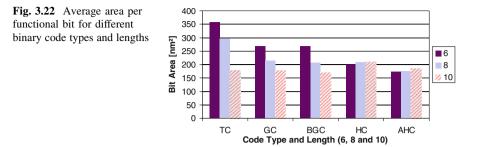

|   |      | 3.3.9   | Simulations of the Effective Memory Area  | 109 |

|   | 3.4  | The M   | ISPT Decoder                              | 113 |

|   |      | 3.4.1   | Design of the Decoder                     | 113 |

|   |      | 3.4.2   | Problem Formulation of MSPT-Based         |     |

|   |      |         | Nanowire Decoder                          | 114 |

|   |      | 3.4.3    | Optimizing Nanowire Codes.                      | 117 |

|---|------|----------|-------------------------------------------------|-----|

|   |      | 3.4.4    | Simulations of the Decoder                      | 119 |

|   | 3.5  | Discu    | ssions                                          | 123 |

|   | 3.6  | Chapt    | er Contributions and Summary                    | 125 |

|   | Refe | erences  | ·····                                           | 125 |

| 4 | Dece | oder To  | est                                             | 129 |

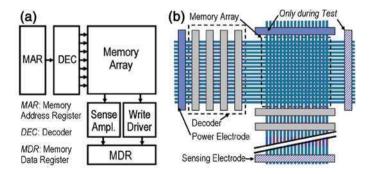

| - | 4.1  |          | sity of Testing Crossbar Circuits               | 130 |

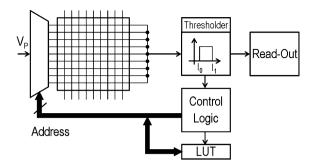

|   |      | 4.1.1    | Operation of Crossbar Memories.                 | 130 |

|   |      | 4.1.2    | Testing Complexity.                             | 131 |

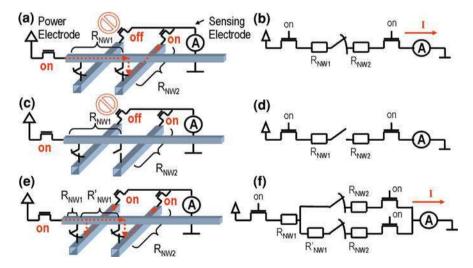

|   | 4.2  |          | g Crossbar Circuits                             | 132 |

|   |      | 4.2.1    | Test Method.                                    | 132 |

|   |      | 4.2.2    | Test Requirements.                              | 134 |

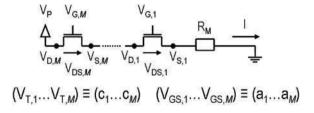

|   | 4.3  |          | bative Current Model.                           | 136 |

|   | 4.4  |          | astic Current Model                             | 138 |

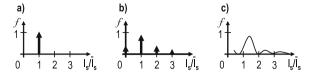

|   |      | 4.4.1    | Components of the Sensed Signal                 | 139 |

|   |      | 4.4.2    | Distribution of the Useful Signal               | 139 |

|   |      | 4.4.3    | Distribution of the Defect-Induced Noise        | 140 |

|   |      | 4.4.4    | Distribution of the Intrinsic Noise.            | 142 |

|   |      | 4.4.5    | Model of the Test Requirements                  | 142 |

|   | 4.5  |          | I Implementation                                | 143 |

|   | 4.6  |          | ation Results.                                  | 146 |

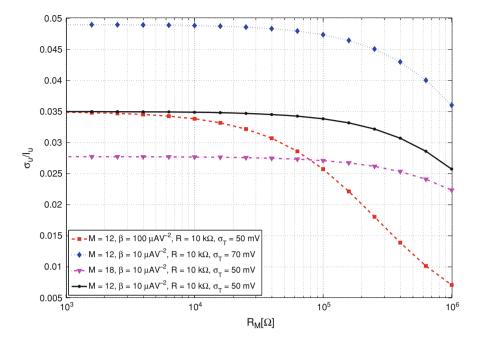

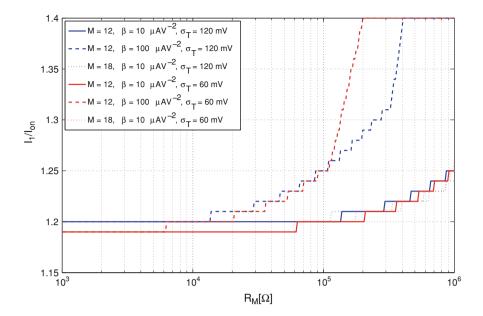

|   |      | 4.6.1    | General Signal Variation                        | 147 |

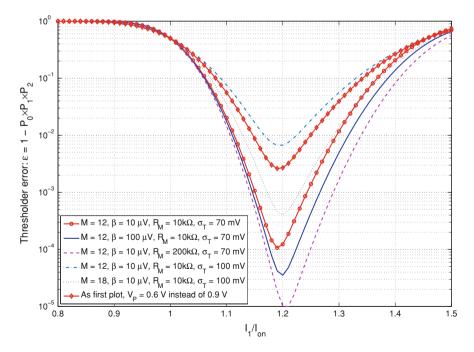

|   |      | 4.6.2    | Optimization of the Thresholder Parameters      | 147 |

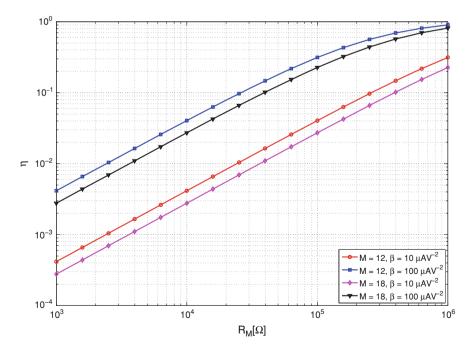

|   |      | 4.6.3    | Analysis of Test Quality                        | 149 |

|   |      | 4.6.4    | Exploration of Linearization Error              | 150 |

|   | 4.7  | Discu    | ssions                                          | 152 |

|   | 4.8  |          | er Contributions and Summary                    | 153 |

|   | Refe | erences  | ·····                                           | 154 |

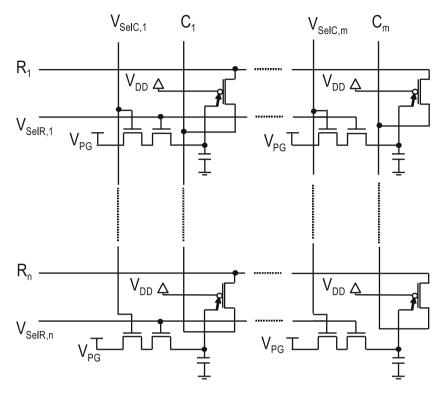

| 5 | Log  | ic Desis | gn with Ambipolar Devices                       | 155 |

|   | 5.1  |          | Circuits with Carbon Nanotubes.                 | 156 |

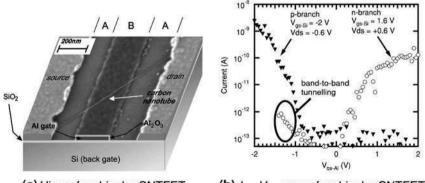

|   | 5.2  |          | polar CNTFETs                                   | 157 |

|   | 5.3  |          | mic Logic with Ambipolar CNTFETs                | 160 |

|   | 5.4  |          | Logic with Ambipolar CNTFETs                    | 161 |

|   |      | 5.4.1    | Transmission-Gate Static Logic Family           | 162 |

|   |      | 5.4.2    | Alternate CNTFET Families                       | 165 |

|   | 5.5  | Multi-   | -Level Logic Synthesis with Static CNTFET Gates | 166 |

|   |      | 5.5.1    | Transmission-Gate Static Design.                | 166 |

|   |      | 5.5.2    | Design of Alternative CNTFET Families           | 167 |

|   |      | 5.5.3    | Library Characterization                        | 167 |

|   |      | 5.5.4    | Logic Synthesis Results                         | 168 |

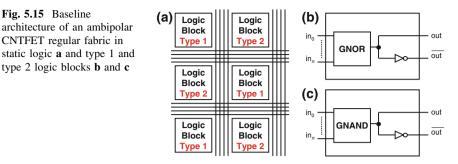

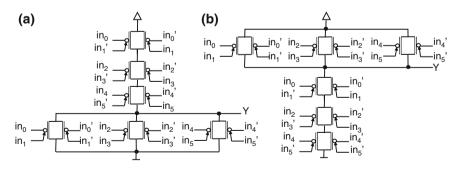

|   | 5.6  |          | n of Regular Fabrics                            | 174 |

|   |      | 5.6.1    | Dynamic PLA Architecture                        | 174 |

|   |      | 5.6.2    | Static Regular Fabrics                          | 177 |

|     | 5.7   | Dicussions                        | 179 |

|-----|-------|-----------------------------------|-----|

|     | 5.8   | Chapter Contributions and Summary | 180 |

|     | Refe  | rences                            | 181 |

| 6   | Con   | clusions and Future Work          | 185 |

|     | 6.1   | Book Summary and Contributions    | 185 |

|     | 6.2   | Future Work                       | 187 |

| Ine | dex . |                                   | 189 |

## List of Acronyms

| 1D     | One-dimensional                            |

|--------|--------------------------------------------|

| 2D     | Two-dimensional                            |

| 3D     | Three-dimensional                          |

| AFM    | Atomic force microscope                    |

| AHC    | Arranged hot code                          |

| Al     | Aluminum                                   |

| ALD    | Atomic layer deposition                    |

| As     | Arsenic                                    |

| ASIC   | Application specific integrated circuits   |

| Au     | Gold                                       |

| BGC    | Balanced gray code                         |

| BHF    | Buffered HF                                |

| BRC    | Binary reflexive code                      |

| BTB    | Band-to-band                               |

| CAD    | Computer-aided design                      |

| Ce     | Cerium                                     |

| CF     | Coupling fault                             |

| CG     | Control gate                               |

| Cl     | Chlorine                                   |

| CLB    | Complex logic block                        |

| CNT    | Carbon nanotube                            |

| CNTFET | Carbon nanotube field effect transistor    |

| Cr     | Chromium                                   |

| CMI    | Center of micro- and nano-technologies [1] |

| CMOL   | CMOS/molecular hybrid                      |

| CMOS   | Complementary metal oxide semiconductor    |

| CMP    | Mechanical-chemical planarization or       |

|        | mechanical-chemical polishing              |

| CVD    | Chemical vapor deposition                  |

|        |                                            |

| DIBL   | Drain induced barrier lowering                          |

|--------|---------------------------------------------------------|

| DRIE   | Deep reactive Ion etching                               |

| E-beam | Electron beam                                           |

| EDA    | Electronic design automation                            |

| EDP    | Energy-delay-product                                    |

| EOT    | Equivalent oxide thickness                              |

| EPFL   | Ecole Polytechnique Fédérale de Lausanne, Swiss Federal |

|        | Institute of Technology at Lausanne                     |

| EUV    | Extreme ultraviolet                                     |

| EUV-IL | Extreme ultraviolet interference lithography            |

| F      | Fluorine                                                |

| FET    | Field effect transistor                                 |

| FIB    | Focused ion beam                                        |

| FO4    | Fan-out-of-4                                            |

| FPGA   | Field programmable gate array                           |

| Ga     | Gallium                                                 |

| GAOI   | Generalized AOI, generalized AND-OR-Inverter            |

| GC     | Gray code                                               |

| Ge     | Germanium                                               |

| GIDL   | Gate-induced drain leakage                              |

| GNAND  | Generalized NAND                                        |

| GNOR   | Generalized NOR                                         |

| HC     | Hot code                                                |

| HMDS   | Hexamethyldisilazane ( $C_6H_{19}Si_2N$ )               |

| IC     | Integrated circuit                                      |

| In     | Indium                                                  |

| IST    | Iterative spacer technique                              |

| ITRS   | International technology roadmap for semiconductors     |

| Kr     | Krypton                                                 |

| LB     | Langmuir–Blodgett                                       |

| LPCVD  | Low pressure chemical vapor deposition                  |

| LTO    | Low temperature oxide                                   |

| LUT    | Look-up table                                           |

| MEMS   | Microelectromechanical system                           |

| MOS    | Metal oxide semiconductor                               |

| MOSFET | Metal oxide semiconductor field effect transistor       |

| MSPT   | Multi-spacer patterning technique                       |

| MVL    | Multi-valued logic                                      |

| MW     | Mesowire                                                |

| N      | Nitrogen                                                |

| Ni     | Nickel                                                  |

| NIL    | Nanoimprint lithography                                 |

| NoC                | Network-on-chip                                                       |

|--------------------|-----------------------------------------------------------------------|

| NRC                | <i>n</i> -Ary reflexive code                                          |

| NW                 | Nanowire                                                              |

| 0                  | Oxygen                                                                |

| OP                 | Operating point                                                       |

| OPC                | Optical proximity correction                                          |

| PANI               | Polyanilin                                                            |

| PD                 | Pull-down                                                             |

| PDMS               | Polydimethylsiloxane $[(C_2H_6OSi)_n]$                                |

| PEDAL              | Planar edge defined alternate layer                                   |

| PEO                | Polyethylene oxide, polyethylene glycol ( $C_{2n+2}H_{4n+6}O_{n+2}$ ) |

| PG                 | Polarity gate Polarity for $(C_{2n+2} \Pi_{4n+6} O_{n+2})$            |

| PLA                | Programmable logic array                                              |

| PMMA               | Polymethylmethacrylate $[(C_5O_2H_8)_n]$                              |

|                    | Poly-crystalline silicon                                              |

| Poly-Si            |                                                                       |

| Poly-SiNWFET<br>PR | Poly-crystalline silicon field effect transistor<br>Photoresist       |

| PSF                |                                                                       |

| PSF<br>Pt          | Pattern sensitivity fault<br>Platinum                                 |

| PU                 |                                                                       |

|                    | Pull-up                                                               |

| Q-bit              | Quantum bit                                                           |

| QCA                | Quantum cellular automata                                             |

| QWFET              | Quantum well field effect transistor                                  |

| RAM                | Random access memory                                                  |

| RDR                | Restrictive design rules                                              |

| RET                | Resolution enhancement techniques                                     |

| RIE                | Reactive ion etching                                                  |

| RTD                | Resonant tunneling diode                                              |

| S                  | Sulfur                                                                |

| Sb                 | Antimony                                                              |

| SB                 | Schottky barrier                                                      |

| SCE                | Short channel effect                                                  |

| SEM                | Scanning electron microscopy                                          |

| SET                | Single-electron transistors                                           |

| Si                 | Silicon                                                               |

| SiNW               | Silicon nanowire                                                      |

| SiNWFET            | Silicon nanowire field effect transistor                              |

| SNAP               | Superlattice nanowire pattern transfer                                |

| SoC                | Systems-on-chip                                                       |

| SOI                | Silicon-on-insulator                                                  |

| SRAM               | Static random access memory                                           |

| TC                 | Tree code                                                             |

| TEM                | Transmission electron microscopy                                      |

| Ti   | Titanium                                          |

|------|---------------------------------------------------|

| ULSI | Ultra large scale integration                     |

| VLS  | Vapor-liquid-solid                                |

| VLSI | Very large scale integration                      |

| VPGA | Via patterned gate array                          |

| WPLA | Whirlpool PLA, Whirlpool programmable logic array |

|      |                                                   |

### Reference

1. Center for Micro- and Nanotechnologies (CMI) at EPFL. http://cmi.epfl.ch

## List of Symbols

| Symbol                    | Definition                                                                                           | Unit       |

|---------------------------|------------------------------------------------------------------------------------------------------|------------|

| α                         | (i) Half-spacing between successive threshold voltages normalized to $V_0$                           | 1          |

|                           | (ii) Counter variable                                                                                | 1          |

| β                         | Transistor gain factor $\mu C_{\rm ox} W/L$                                                          | $AV^{-2}$  |

| $\beta_i$                 | $\beta$ at transistor <i>i</i>                                                                       |            |

| δ                         | Shift of any $V_{X,i}$ from $V_{A,i}$ normalized to $V_0$                                            | 1          |

| $\Delta V_{\mathrm{T}}$   | Distance between two successive $V_{T,i}$ 's                                                         | V          |

| $\delta(x)$               | (i) Dirac distribution around $x = 0$                                                                | Ø          |

|                           | (ii) Kronecker delta function                                                                        | Ø          |

| $\delta I$                | Small signal of I                                                                                    | А          |

| $\delta I_{\mathrm{d},i}$ | Small signal of $I_{d,i}$                                                                            | А          |

| $\delta I_{\mathrm{u}}$   | Small signal of $I_{\rm u}$                                                                          | А          |

| $\delta V_{ m DS}$        | Small signal of $V_{\rm DS}$                                                                         | V          |

| $\delta V_{{ m DS},i}$    | $\delta V_{\rm DS}$ at transistor <i>i</i>                                                           | V          |

| $\delta V_{\rm DS}$       | Vector of $\delta V_{\text{DS},i}$                                                                   | V (vector) |

| $\delta V_{\rm GS}$       | Small signal of $V_{GS}$                                                                             | V          |

| $\delta V_{{ m GS},i}$    | $\delta V_{\rm GS}$ at transistor <i>i</i>                                                           | V          |

| $\delta V_{\mathrm{T}}$   | Small signal of $V_{\rm T}$                                                                          | V          |

| $\delta V_{\mathrm{T},i}$ | $\delta V_{\rm T}$ at transistor <i>i</i>                                                            | V          |

| $\delta V_{\mathrm{T}}$   | Vector of $\delta V_{\mathrm{T},i}$                                                                  | V (vector) |

| $\epsilon$                | Test error probability                                                                               | 1          |

| η                         | (i) Statistical factor $\eta = P_{\rm nbr} \times P_{\rm unq} \times P_{\rm cnt} \times P_{\rm int}$ | 1          |

|                           | (ii) Sensitivity of $V_{\rm DS}$ to $V_{\rm T}$ in a decoder under test                              | 1          |

| $\eta^{\rm BU}$           | Statistical $\eta$ for bottom-up technologies                                                        | 1          |

| $\eta^{\text{TD}}$        | Statistical $\eta$ for top-down technologies                                                         | 1          |

| Φ                         | Fabrication complexity $\Phi = \sum \phi_i$                                                          | 1          |

| $\phi_i$                  | Number of photolithography/doping steps at MSPT step i                                               | 1          |

| $\mu_{\alpha}$            | Average number of code words having $\alpha$ identical digits                                        | 1          |

| v                         | Average number of patterns covered by a code word<br>under defects                                   | 1          |

| (co) | ntinu | ied) |

|------|-------|------|

| (00) | nunu  | icu, |

| Symbol                           | Definition                                                                 | Unit               |

|----------------------------------|----------------------------------------------------------------------------|--------------------|

| Ω                                | Code space                                                                 | Ø                  |

| $\Omega'$                        | Addressable code space under defects                                       | Ø                  |

| $ \Omega _{\mathrm{un}}$         | Size of uniquely addressed code space                                      | Ø                  |

| $ \Omega _{im}$                  | Size of immune code space                                                  | Ø                  |

| Σ                                | Variability matrix                                                         | $V^2$ (matrix)     |

| $\sigma(x)$                      | Sigmoid function of x                                                      | Ø                  |

| σ                                | Threshold voltage standard deviation $(=\sigma_T)$                         | V                  |

| $\sigma_{\delta \mathrm{d},i}$   | Standard deviation of $\delta I_{d,i}$                                     | А                  |

| $\sigma_{\delta \mathrm{u}}$     | Standard deviation of $\delta I_{\rm u}$                                   | А                  |

| $\sigma_{\mathrm{d},i}$          | Standard deviation of $I_{d,i}$                                            | А                  |

| $\sigma_{ m d}^{N_{ m def}}$     | Standard deviation of $I_d^{N_{def}}$                                      | А                  |

| σ <sub>T</sub>                   | Standard deviation of $V_{\rm T}$                                          | V                  |

| $\sigma_{\rm u}$                 | Standard deviation of $I_{\mu}$                                            | А                  |

| τ                                | (i) Number of digits that flip in order to generate                        | 1                  |

|                                  | defect-induced noise (context of decoder design)                           |                    |

|                                  | (ii) Intrinsic delay of fan-out-of-1 inverter                              | S                  |

|                                  | (context of ambipolar CNTFET)                                              |                    |

| τ                                | Mean value of number of digits $\tau$                                      | 1                  |

| )                                | (i) Normalized shift of $V_A$ from middle of two                           | 1                  |

|                                  | successive threshold voltages normalized to $V_0$                          |                    |

|                                  | (ii) counter variable                                                      | 1                  |

| 4                                | (i) Pattern space                                                          | Ø                  |

|                                  | (ii) Event of having $I_1 \leq I_s$                                        | Ø                  |

| A                                | First linearization matrix of the decoder                                  | 1 (matrix)         |

| В                                | Event of having defect-induced noise, $B = \bigcup B_i$                    | Ø                  |

| $B_i$                            | Event of having exactly <i>i</i> nanowires generating defect-induced noise | Ø                  |

| В                                | Second linearization matrix of the decoder                                 | 1 (matrix)         |

| a                                | Pattern                                                                    | 1 (vector)         |

| b                                | Pattern                                                                    | 1 (vector)         |

| b*                               | Defective pattern                                                          | 1 (vector)         |

| $C_{\rm eff}$                    | Effective crossbar (or memory) density                                     | $\mathrm{cm}^{-2}$ |

| $C_{ m eff}^{ m BU}$             | Effective crossbar (or memory) density in bottom-up technologies           | $\mathrm{cm}^{-2}$ |

| $C_{\mathrm{eff}}^{\mathrm{TD}}$ | Effective crossbar (or memory) density in top-down technologies            | $\mathrm{cm}^{-2}$ |

| c                                | Code word                                                                  | 1 (vector)         |

| <b>e</b> *                       | Defective code word                                                        | 1 (vector)         |

| $\mathfrak{e}^a$                 | Code word to the pattern a                                                 | 1 (vector)         |

| $e^b$                            | Code word to the pattern b                                                 | 1 (vector)         |

| d                                | Multi-digit error vector                                                   | 1 (vector)         |

| D                                | (i) Crosspoint density, memory density                                     | $\mathrm{cm}^{-2}$ |

|                                  | (ii) Elements of error subtree                                             | Ø                  |

| D <sub>RAW</sub>                 | Raw crosspoint (memory) density                                            | $cm^{-2}$          |

| D <sub>EFF</sub>                 | Effective crosspoint (memory) density                                      | $\mathrm{cm}^{-2}$ |

| (continued) |

|-------------|

| (continucu) |

| Symbol                                                        | Definition                                                                               | Unit                     |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------|

| f                                                             | (i) Probability distribution function                                                    | Ø                        |

|                                                               | (ii) Photolithography half-pitch                                                         | nm                       |

|                                                               | (iii) Non-linear bijective application between $N_{\rm D}$ and $V_{\rm T}$               | Ø                        |

| f <sub>u</sub>                                                | Probability distribution function of useful signal                                       | Ø                        |

| $f_{\rm d}^i$                                                 | Probability distribution function of defect-induced noise generated by nanowire <i>i</i> | Ø                        |

| f <sub>d</sub>                                                | Probability distribution function of total defect-induced noise                          | Ø                        |

| g                                                             | Bijective application between pattern and $V_{\rm T}$                                    | Ø                        |

| sds                                                           | Output conductance of a FET                                                              | S                        |

| g <sub>m</sub>                                                | Transconductance of a FET                                                                | S                        |

| gт                                                            | Sensitivity of $I_{\rm DS}$ to $V_{\rm T}$ : $\partial I_{\rm DS}/\partial V_{\rm T}$    | S                        |

| h                                                             | Non-linear bijective application between elements of <b>D</b> and those of <b>P</b>      | Ø                        |

| D                                                             | Doping matrix                                                                            | cm <sup>-3</sup> (matrix |

| I                                                             | Unit $M \times M$ -matrix                                                                | 1 (matrix)               |

| I                                                             | Current through a nanowire under test                                                    | Α                        |

| i                                                             | Counter variable                                                                         | 1                        |

| $I_0$                                                         | First thresholder parameter                                                              | А                        |

| $I_1$                                                         | Second thresholder parameter                                                             | А                        |

| $\overline{I}_{\delta d,i}$                                   | Mean value of $\delta I_{d,i}$                                                           | А                        |

| $\overline{I}_{\delta u}$                                     | Mean value of $\delta I_{\rm u}$                                                         | А                        |

| I <sub>d</sub>                                                | Defect-induced noise in decoder under test                                               | А                        |

| $I_{d,i}$                                                     | Defect-induced noise generated by nanowire <i>i</i>                                      | А                        |

| $\overline{I}_{d,i}$                                          | Mean value of $I_{d,i}$                                                                  | А                        |

|                                                               | Total defect-induced noise: $\sum I_{d,i}$                                               | А                        |

| $I_{ m d}^{N_{ m def}}$<br>$\overline{I}_{ m d}^{N_{ m def}}$ | Mean value of $I_{d}^{N_{def}}$                                                          | A                        |

| I <sub>ds</sub>                                               | Drain-source current                                                                     | А                        |

| Ii<br>Ii                                                      | Intrinsic noise in decoder under test                                                    | А                        |

| /i,0                                                          | Intrinsic noise generated by a single nanowire in decoder under test                     | А                        |

| I <sub>off</sub>                                              | Transistor off-current                                                                   | А                        |

| Ion                                                           | Transistor on-current                                                                    | А                        |

| I <sup>OP</sup>                                               | Operating point of I                                                                     | А                        |

| I <sub>s</sub>                                                | Sensed signal in decoder under test $= I_u + I_d + I_i$                                  | А                        |

| Iu                                                            | Useful signal                                                                            | А                        |

| u<br>Īu                                                       | Mean value of $I_{\mu}$                                                                  | А                        |

| i                                                             | Counter variable                                                                         | 1                        |

| k                                                             | (i) Parameter of optimal-size multi-valued hot code                                      | 1                        |

| -                                                             | (ii) Counter variable                                                                    | 1                        |

| k                                                             | Parameter vector of multi-valued hot code                                                | 1 (vector)               |

| L                                                             | Transistor length                                                                        | nm                       |

| $L_1$                                                         | Photolithography pitch                                                                   | nm                       |

| $L_{\rm n}$                                                   | Sub-photolithographic pitch, nanoscale pitch                                             | nm                       |

(continued)

| Symbol                 | Definition                                                                                | Unit                      |

|------------------------|-------------------------------------------------------------------------------------------|---------------------------|

| М                      | Length of code word, number of doping sequences<br>in a nanowire (equivalent definitions) | 1                         |

| Ν                      | Number of nanowires in a contact groups                                                   | 1                         |

| ND                     | Doping level (donors or acceptors)                                                        | $\mathrm{cm}^{-3}$        |

| N <sub>def</sub>       | Number of nanowires generating defect-induced noise in a decoder under test               | А                         |

| $N_{ m off}$           | Number of non-activated nanowires in a decoder<br>under test                              | А                         |

| N <sub>use</sub>       | Number of useful nanowires in a decoder under test $(N_{use} = 0 \text{ or } 1)$          | А                         |

| п                      | Logic value                                                                               | 1                         |

| P                      | Pattern matrix                                                                            | 1 (matrix)                |

| $P_0$                  | Probability that no nanowire is addressed                                                 | 1                         |

| <b>P</b> <sub>1</sub>  | Probability that 1 nanowire is addressed                                                  | 1                         |

| P <sub>2</sub>         | Probability that $\geq 2$ nanowires are addressed                                         | 1                         |

| P <sub>cnt</sub>       | Probability of a good nanowire control                                                    | 1                         |

| Pcontact               | Probability of a good nanowire ohmic contact                                              | 1                         |

| P <sub>int</sub>       | Probability of no nanowire loss at the interface between contact groups                   | 1                         |

| P <sub>nbr</sub>       | Probability of a non-broken nanowire                                                      | 1                         |

| Punq                   | Probability of a unique nanowire                                                          | 1                         |

| P <sub>I</sub>         | Probability of a type-I error in a code space                                             | 1                         |

| ν <sub>II</sub>        | Probability of a type-II error in a code space                                            | 1                         |

| $\mathcal{D}_{\alpha}$ | Probability that $\mu_{\alpha}$ code words undergo error sequences that make them covered | 1                         |

| <i>p</i> <sub>d</sub>  | Probability of a flip-down error in a code word                                           | 1                         |

| $p_{\rm im}$           | Probability of an immune code space                                                       | 1                         |

| o <sub>u</sub>         | Probability of a flip-up error in a code word                                             | 1                         |

| $v_{\rm U}$            | Probability of a uniquely covered code space                                              | 1                         |

| 7                      | On/off current ratio to detect a digit                                                    | 1                         |

| r <sub>i</sub>         | $R_{ m M}  g_{{ m m},i} $                                                                 | Ω                         |

| R <sub>M</sub>         | Resistance of the nanowire memory part                                                    | Ω                         |

| S                      | (i) Set of all $(p_{\alpha}, \mu_{\alpha})$                                               | Ø                         |

|                        | (ii) Set of indexes of digits that undergo flip-ups                                       | Ø                         |

| 5                      | Step doping matrix                                                                        | cm <sup>-3</sup> (matrix) |

| 5                      | Sequence digit shifts to generate defect-induced noise                                    | 1 (vector)                |

| Т                      | Error transformation matrix                                                               | Ø                         |

| t <sup>i</sup>         | Error transformation affecting digit level i                                              | Ø                         |

| V                      | Threshold voltage matrix                                                                  | V (matrix)                |

| v                      | Vector with all entries set to 1                                                          | 1 (vector)                |

| $V_+$                  | $V_{\rm PG}$ for n-type device                                                            | V                         |

| $V_{-}$                | $V_{\rm PG}$ for p-type device                                                            | V                         |

| $V_0$                  | (i) Decoder normalization voltage, set to $V_{DD}$ (context of decoder test)              | V                         |

(continued)

| Symbol                                  | Definition                                              | Unit       |

|-----------------------------------------|---------------------------------------------------------|------------|

|                                         | (ii) $V_{PG}$ for a low-conductivity transistor         | V          |

|                                         | (context of ambipolar CNTFET)                           |            |

| $V_{\rm A}$                             | Applied voltage at the decoder (gate-to-ground voltage) | V          |

| $V_{\mathrm{A},i}$                      | $V_{\rm A}$ at transistor <i>i</i>                      | V          |

| $V_{CG}$                                | Control gate voltage (ambipolar CNTFET)                 | V          |

| $V_{\rm DD}$                            | Supply voltage                                          | V          |

| $V_{\rm ds}$                            | Drain-source voltage (context of measurement)           | V          |

| V <sub>DS</sub>                         | Drain-source voltage (context of testing)               | V          |

| $V_{\mathrm{DS},i}$                     | $V_{\rm DS}$ at transistor <i>i</i>                     | V          |

| $V_{\rm gs}$                            | Gate-source voltage (contest of measurement)            | V          |

| V <sub>GS</sub>                         | Gate-source voltage (context of testing)                | V          |

| $V_{\text{GS},i}$                       | $V_{\rm GS}$ at transistor i                            | V          |

| $V_{\rm P}$                             | Power supply of decoder under test                      | V          |

| $V_{\rm PG}$                            | Polarity gate voltage (ambipolar CNTFET)                | V          |

| V <sub>SS</sub>                         | Ground, reference voltage                               | V          |

| $V_{\mathrm{T}}$                        | Threshold voltage                                       | V          |

| $\overline{V}_{\mathrm{T}}$             | Mean value of $V_{\rm T}$                               | V          |

| $\overline{\mathbf{V}}_{\mathrm{T}}$    | vector of $\overline{V}_{\mathrm{T},i}$                 | V (vector) |

| $\overline{V}_{\mathrm{T},i}$           | $\overline{V}_{\rm T}$ at transistor <i>i</i>           | V          |

| VT                                      | Vector of $V_{\mathrm{T},i}$                            | V (vector) |

| $\mathbf{V}_{\mathrm{T}}^{\mathrm{OP}}$ | $\mathbf{V}_{\mathrm{T}}$ at operating point            | V (vector) |

| $V_{\mathrm{T},i}$                      | $V_{\rm T}$ at transistor <i>i</i>                      | V          |

| $V_{\mathrm{X},i}$                      | Threshold voltage to detect digit <i>i</i>              | V          |

| V <sub>Tn</sub>                         | Threshold voltage of n-type device                      | V          |

| $V_{\mathrm{Tp}}$                       | Threshold voltage of p-type device                      | V          |

| Ŵ                                       | Transistor width                                        | nm         |

| Y                                       | Statistical yield                                       | 1          |

## Chapter 1 Introduction

Modern societies have been deeply reshaped by a sequence of industrial revolutions. Some of them were completed and they represent today a chapter of history, while some others are still evolving and generating more changes in the societies. One fundamental aspect that characterizes modern societies is the increasing level of usage of electronic systems that are partly becoming indispensable for some daily activities. Conversely, the daily activities are reshaped according to the new systems uninterruptedly coming to the market. This tight link between the needs of modern societies and the electronics system represents one of the latest revolutions.

Electronic systems are complex systems generally conceived around a physical core, the *hardware*, which can be customized and programmed by adding soft modules called *software*. The hardware of electronic systems is versatile. This diversity concerns the way it is fabricated, the *manufacturing* or *fabrication technology*, and the way the available manufacturing technology is utilized to design the full system, i.e., the *design technology*. Moreover, the electronic systems are segmented in terms of usage or *application*: while some systems are used for communication, transportation or office applications, some others are utilized for entertainment purposes, or in more vital fields such as health care, energy, security and defense.

It is interesting to notice that the hardware of all these diverse and numerous systems is ultimately a complex *integrated circuit (IC)*, whose manufacturing and design make the difference. An integrated circuit is a set of basic elements that control the flow of electrical current in a defined way in order to perform a certain set of operations. These basic elements are called *transistors*. The invention of such devices goes back to the first half of the twentieth century. But their assembly into integrated systems is just less than half a century old.

After the transistor was invented, the scientific community rapidly became aware of the potential benefits of this novel technology. As a matter of fact, transistors are made of commonly available materials: namely germanium (Ge), and especially silicon (Si). In addition, they are able to maintain the ability to control the current switching on and off despite the scaling down of their size. Then, by scaling the device and using a larger number of transistors, the integrated circuits had the potential of becoming more complex and performing more functions. The industrial community did not overlook this unique opportunity, and it initiated the era of *semiconductor industry*.

The growth of the semiconductor industry in the last half-century has not been as sensitive to the cyclicity of the world economy as other markets have, leading to a continuous growth of the developed systems from small integrated circuits made of a few transistors to a *very large scale integration (VLSI)* and *ultra large scale integration (ULSI)* levels with millions and billions of transistors. Many novel techniques are being investigated today in order to keep this growth. These techniques are the results of a wide range of research efforts in different fields, including both the manufacturing technologies (processing and device engineering) and the design technologies (at the circuit and system levels). The previous decades of research have been mostly focusing on the scaling down of the device features in order to further increase the integration level, while roughly keeping the same underlying transistor physics and the related system paradigms unchanged.

The *international technology roadmap for semiconductors (ITRS)* [1] is a consortium of leaders in the fields of semiconductor research and industry, whose goal is to survey the trends of the semiconductor technology and predict its future evolution. Today, the ITRS recognizes the existence of physical limits to this growth: the electronics-based technologies cannot be scaled down beyond certain dimensions that are defined by some physical limits [2].

The semiconductor technology that dominates the electronics market today is the *complementary metal-oxide-semiconductor (CMOS)* technology, which is based on the utilization of complementary transistors, designated by n- and p-types, which carry, respectively, electrons and holes. The challenging task of the ITRS today is to find a way to continue the scaling of CMOS technology or its fundamental replacement by other technologies promising more scaling opportunities. The efforts undertaken in this sense are reflected by the variety of processing techniques, device architectures and system designs that have been investigated in the last decade.

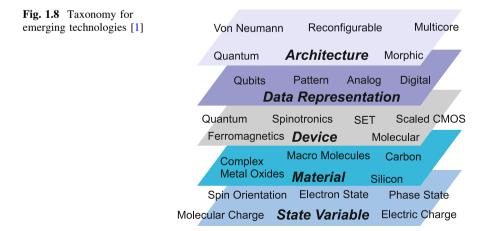

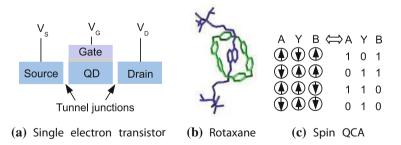

The candidates that are viable for a possible replacement of CMOS technology are commonly called *emerging technologies*. These tentative solutions are based on novel materials, device physics, circuit designs etc. They share some common aspects: for instance, the dimension scaling is pushed so far, that typical device dimensions are in the range of an average-size molecule. At this scale, the uncertainty becomes high and the variability increases at the single device level, so that a reliable operation of the system cannot be guaranteed anymore. On the other hand, the accurate placement of devices with the size of single molecules is challenging the manufacturing and increasing the overall variability.

The increasing variability and limited manufacturing abilities set a limit on the success of the industrial exploitation of electronic systems. It is therefore necessary to find technological solutions that enable a large scale implementation of

emerging technologies. One possible way to survive with an unreliable technology is to increase the redundancy, i.e., to use more instances of the same device or unit, in such a way that any failing part of the circuit can be replaced. Another way is to arrange devices and units in a regular way in order to increase the determinism of the circuit. Regularity is often compatible and desirable in redundant systems.

Regular architectures in emerging technologies are the driver of this research work. The global objective of this work is, first, to assess a set of emerging technologies, then to address some challenges arising from the manufacturing level at the design level. Consequently, the work is presented across different design fields and manufacturing technologies.

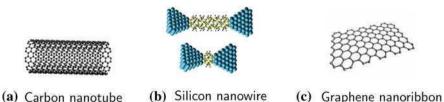

This work is organized across different technologies defined by two types of devices and it focuses on their integration into large systems. The considered technologies are defined by *one-dimensional* (*1-D*) devices: *silicon nanowires* (*SiNWs*) and *carbon nanotubes* (*CNTs*), both of which are promising a better performance compared to CMOS and more opportunities to further scale down the dimensions. The system integration starts from the fabrication and goes to the system level: for every one of the two types of devices, this research work will demonstrate the possibility of addressing a complex issue related to the fabrication by applying relatively simple solutions on the design level.

Both SiNW and CNT technologies are preferably locally arranged into regular and parallel layers, even though the global circuit can be defined in a custom design way. But their intrinsically different operation, physics and fabrication techniques are the reasons for the different challenges facing their integration into large scale systems.

When it comes to SiNW technology, the regular arrangement of devices into arrays, called *crossbars*, embodied within a surrounding CMOS part, is the most promising architecture. However the link between the crossbars and the CMOS part is a challenging task. In this work, a demonstration of a crossbar fabrication technique that can be potentially integrated in an easy way into a CMOS process is performed. Then, solutions are given in order to link the crossbar to the CMOS part. These solutions include the choice of the nanowire codes, the design of the decoder that links both parts and performing a reliable decoder testing operation.

On the other hand, among the most important challenge that CNT technology is facing is the doping of *CNT field effect transistors* (*CNTFETs*). As explained before, both n- and p-type devices may be needed in the most common circuit device approaches. However, for CNT technology, n-type devices are difficult to obtain through usual technique, called chemical doping in CMOS technology. Recently, it has been demonstrated that the polarity of CNT devices, i.e., whether they are n- or p-type devices, can be controlled during the operation of the device. The device is called in this case *ambipolar*, i.e., operating as n- and p-device at the same time. This represents an opportunity for new design methodologies for *ambipolar circuits*, which will be introduced in this work and their benefit will be assessed.

The novelty and contributions of this work consists in its multidisciplinary approach, in which the system design is enhanced by leveraging some opportunities offered by the versatile fabrication technologies. The complementary point of view is also a novel contribution of this work: i.e., some challenges of the fabrication technology are addressed at the system level.

This chapter is an introduction organized the following way. First, the past decades of linear scaling and the difficulties facing CMOS technology at the latest milestones are surveyed. Then, promising emerging technologies that may either sustain CMOS technology or create technological discontinuities are presented. Thereafter, some promising regular architectures are surveyed and the challenges that they are facing are explained. This chapter is concluded with the contributions and limitations of this work, and by explaining its outline.

#### 1.1 The Linear Scaling

The evolution of the semiconductor industry is among the most fascinating industry stories in the twentieth century. It is one of the latest industrial revolutions, whose impact can be seen in most of the details of our life today. Our basic needs have been reshaped in the last fifty years or more in such a way that electronic elements performing computation, storage, sensing, connectivity, entertainment, security, health care, and much more, are hardly separable from our daily activities. The range of applications in which microelectronics products are present is becoming even larger everyday. It is remarkable that most of the semiconductor systems are built out of the same fundamental element, which is the transistor.

The history of the transistor, driving the whole semiconductor industry and reshaping the needs of modern societies, does not go more than 60 years back in time. The exact date of birth of the transistor is not uncontroversial, since a non-advertised patent for the *field effect transistor (FET)* was filed in the twenties [3], but never used for any practical implementation by its inventor, until it became the basis of the first transistor fabricated in 1947 by researchers from Bell Labs [4] and then the first device that became known as the bipolar junction transistor was invented [5]. The first fabrication of a FET was successfully performed in 1959 [6], which evolved into the *metal-oxide-semiconductor field effect transistor (MOSFET)* we know today.

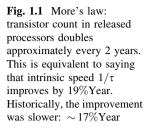

The evolution of integrated circuits is captured by Moore's law [7], which was stated in 1965, predicting an exponential growth of the number of transistors per die every year. Even though the growth rate was not constant during the last decades, still it was about a factor of 2 every 2 years, in the same range as predicted by Moore's law initially Fig. 1.1. This roughly constant growth is unique among all industries and raised the question about the origins and the reasons of this sustained growth. A naïve answer that has been continuously reported states the cost reduction. This used to be true in early ages of the semiconductor industry. Today, the silicon costs are marginal, and the *electronic design automation (EDA)* tools, mask fabrication and circuit design costs are

becoming tremendous compared to material costs. The emotional answer is tightly linked to the enthusiasm driving the research in the semiconductor field: it is always challenging and curious to assess the limits and see how far research can go with the available knowledge and come up with novel solutions. The most pragmatic answer comes from the fact that Moore's law represents a roadmap for future achievements, which is practically a non-binding agreement about the future between the actors of the semiconductor industry. Having a universal agreement between competitors is a highly desirable situation for semiconductor leaders because it decreases the uncertainty about the future of the semiconductor market. Such an agreement may be considered as a collusion though, which is a forbidden marketing practice in an economy with a perfect competition. Nevertheless, the semiconductor market has the unique chance of having its roadmap established and purposefully sustained by the competitors without any unlawful agreement. The second marketing-related answer is the continuous need for new products in a consumer-driven world economy. Since packaging makes the ICs morphologically identical, new semiconductor products have generally been differentiated by the device integration level. Recently, marketing experts have discovered that besides the hardware level, the application level is a strategic way to differentiate products as well [8].

The last decades, in which sustaining Moore's law was straightforward, are commonly called the happy-scaling period. During this period, the device dimensions and voltages have been scaled by a factor of  $\alpha$  periodically, which results in a global improvement of the device density and reduction of the device power consumption by a factor of  $\alpha^2$ , and a speed-up of the intrinsic device by a factor of  $\alpha$ , as shown in Table 1.1 [9]. In order to sustain this trend, the ITRS [1] was founded as a consortium representing the leading actors in the field of semiconductors, which periodically publishes predictions for the evolution of the semiconductor industry, including device research, process integration, semiconductor materials, circuit design, interconnect issues, packaging, EDA tools...

| Table 1.1         Linear scaling | Parameter                                                | Scaling factor |

|----------------------------------|----------------------------------------------------------|----------------|

| rules                            | Transistor length and width $(L, W)$                     | $1/\alpha$     |

|                                  | Junction depth $(x_i)$                                   | $1/\alpha$     |

|                                  | Oxide thickness $(t_{ox})$                               | $1/\alpha$     |

|                                  | Doping concentration $(N_d, N_a)$                        | α              |

|                                  | Supply voltage $(V_D)$                                   | $1/\alpha$     |

|                                  | Drive current $(I_{\rm D})$                              | $1/\alpha$     |

|                                  | Electric field (E)                                       | 1              |

|                                  | Capacitance $(\epsilon \cdot A/t_{ox})$                  | $1/\alpha$     |

|                                  | Delay time $(\tau = C \cdot V_D / I_D)$                  | $1/\alpha$     |

|                                  | Power dissipation (roughly $V_{\rm D} \cdot I_{\rm D}$ ) | $1/\alpha^2$   |

|                                  | Device density $(\sim 1/A)$                              | $\alpha^2$     |

#### **1.2 The Latest Milestones**

The linear scaling is expected to reach the 22-nm technology node. However, it is facing many challenges today, and the vision beyond this point is not a matter of a common consensus. This section surveys the most important issues that need to be addressed with the latest milestones at different research levels.

#### 1.2.1 Fabrication Technology

Until approximately the 90-nm technology node, the overall IC design flow was relying on the linear scaling of devices that was requiring a corresponding scaling of the design rules in order to insure the feasibility of the fabrication. Today, the design rules do not scale in a similar way, and even the simplest layout geometries may tend to create patterns that cannot be reliably printed with the available photolithographic techniques. The manufacturing is becoming more challenging, and it makes the design more difficult as well.

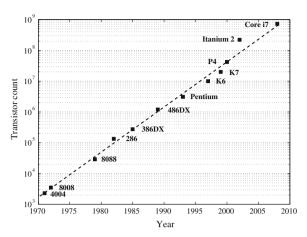

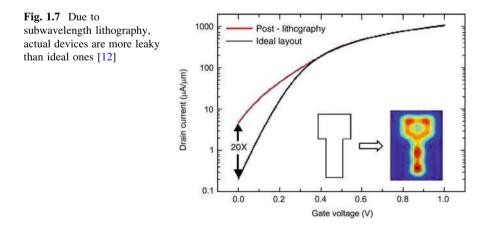

In the past, photolithographers applied an aggressive scaling of the wavelength of light in order to achieve the required scaled features. The difficulty in developing fabrication equipments that are compatible with shrinking wavelengths of light, obliged the manufacturing community to use larger wavelengths than the feature size Fig. 1.2. Thus, it became necessary to introduce aggressive techniques that sustained the scaling of the dimensions, while using the same light source [10]. Most of these alternative approaches use post-tapeout manufacturability enhancement techniques. One of the available options is a set of strong *resolution enhancement techniques* (*RETs*), such as phase-shifting masks [11]. These techniques use the properties of the optical projection process to reduce the resolution features and the sensitivity of the printed shapes to process variation during the photolithography steps. Another set of tools is the *optical proximity correction*

(*OPC*) [11], which attempts to compensate for systematic shape distortions of fabricated devices by applying the inverse distortions when converting the design shape (tapeout) to mask shapes.

The OPC technique is a data processing step with a tremendous cost in terms of time resulting from the complicated computation required in order to calculate the inverse distortions. On the other hand, although RETs can be used in order to improve the image quality of some patterns in the layout, they tend to compromise the quality of other patterns. There is a set of non-RET compliant patterns that need to be identified and avoided by the designer during the mask drawing steps. However, it is difficult to assess all non-RET compliant patterns because of the large possible combination of layout patterns that exist in an average library of hundreds of standard-cells.

The link between the design and manufacturing communities is becoming more critical than it used to be in the past [12]. This link can be summarized in a set of design rules that designers have to respect when they create an IC; such design rules insure the manufacturability of the layout. Their number is highly increasing with each technology node, making the task of the designer more difficult and time-consuming. On the other hand, the definition of the design rules becomes a difficult, sometime impossible task for the manufacturing team, since these rules, that used to reflect the mechanical, optical and chemical processes controlling the photolithography, are becoming design-dependent. It is therefore impossible to validate a process through a universal set of design rules, because of the geometry pattern explosion. Since design rules can be only validated for a given design, or more precisely for a given set of patterns, designs with non validated patterns are fault-prone and they dramatically impact yield; thus, representing a major concern of the semiconductor industry.

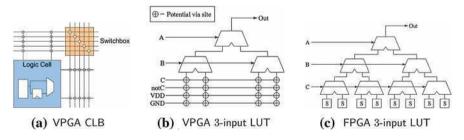

The need for limiting the pattern explosion sets new methodologies when it comes to defining the design rules. The general tendency is towards more regularity of the permitted patterns [12], corresponding to the set of patterns that were tested by the manufacturing team and validated as RET-compliant. A set of *restrictive design rules* (*RDR*), which can be also seen as radical design rules, has been recently proposed by different semiconductor manufacturers [11, 13] with

two goals: first, to ensure an RET-compliance of the design, and second, to reduce the computational complexity of the OPC processing step. The main concepts introduced by RDRs are: the use of smaller-and possibly discretized-range of line widths for critical patterns, the unidirectionality of critical features, such as gates, the placement of critical features on a discretized grid, and the limitation of the combinations of proximities for critical features.

#### 1.2.2 Device Design

#### **1.2.2.1 Electrostatic Channel Control**

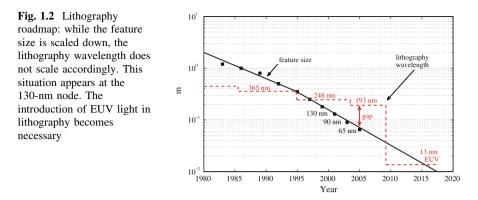

With the channel scaling, short channel effects are becoming more severe Fig. 1.3. The *short channel effect (SCE)*, measured at  $V_{ds} = 0$  V, reflects the lowering of the threshold voltage  $V_T$  with a decreasing channel length, due to a *two-dimensional* (2-*D*) distribution of the surface potential in the channel. Moreover, in short channel devices, the *drain-induced barrier lowering (DIBL)* consists in making the threshold voltage dependant on the drain bias  $V_{ds}$  due to the penetration of the drain depletion zone deep into the short channel. Both CSE and DIBL induce a lowering of  $V_T$  (for n-type transistors), which makes the devices more vulnerable to variability. DIBL has in addition critical consequences on the circuit design, due to the fact that the saturation of the  $I_{ds}$ - $V_{ds}$  curve does not occur any more, and the device on- and off-states (i.e.,  $V_{gs} > V_T$  or  $V_{gs} \leq V_T$ ) can be unintentionally set by  $V_{ds}$ .

#### 1.2.2.2 Carrier Mobility

Setting the threshold voltage properly and providing a better control of the short channel effects necessitate the channel doping level to be increased to extremely

higher values than the theoretical scaled values given by the linear scaling theory (Table 1.1). As a result of the high channel doping level, the carrier mobility in the channel deteriorates [14], causing a lower drive current and a slower device. The bulk mobility values for holes ( $\sim 500 \text{ cm}^2/\text{V}$ s) and electrons ( $\sim 1,400 \text{ cm}^2/\text{V}$ s) are therefore rarely measured in the silicon channel because of the presence of dopants; and the situation worsens with the applied electrical field, due to phonon scattering [15], and by the scattering at the Si/SiO<sub>2</sub> interface between the channel and the gate oxide [16].

#### 1.2.2.3 Leakage

The need for an extremely high valued of channel doping causes the increase of the junction leakage due to *band-to-band (BTB)* tunneling and *gate-induced drain leakage* (*GIDL*), both kinds of leakage leading to higher power consumption [17, 18].

On the other hand, the scaling of the oxide thickness along with the other device dimensions provokes an exponential increase of the gate leakage, occurring as a tunnel current through the gate oxide, with the linear decrease of the gate thickness [19].

#### 1.2.2.4 Gate Stack

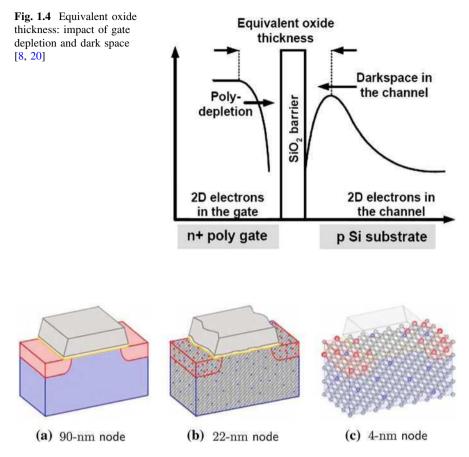

Historically, poly-Si was used for the gate stack because of its easy integration into CMOS processes. However, several issues are arising today due to the use of poly-Si gates. As a matter of fact, by applying the gate voltage, the current carriers are depleted at the gate to gate oxide interface. On the other side of the gate oxide barrier, namely at the channel to gate oxide interface, a dark space is created and is due to charge quantization effects in the inversion layer. Both dark space and poly-depletion thickness act as additional insulators between the channel and the gate, by virtually increasing the *equivalent oxide thickness (EOT)*, as depicted in Fig. 1.4.

This problem is today addressed by using a metal gate, since in metals no carrier depletion occurs. On the other hand, metal gates have the other advantage of being suitable for high- $\kappa$  materials used as gate insulators in order to reduce the gate leakage.

#### 1.2.2.5 Access Resistance

In addition to the channel resistance, a certain number of access resistances control the device performance. These include the contact resistance, drain/source resistance and the overlap resistance defined by the path underneath the gate and its spacers. It is very difficult to keep the access resistances constant with the decreasing

**Fig. 1.5** Evolution of device modeling from continuous to discretized concepts [22]: **a** Dopant fluctuation canceled by continuum at 90-nm node. **b** At 22-nm node: only 50 Si atoms along the channel. **c** At 4-nm node: discretized distribution of dopants is source of high variability

device dimensions, mainly because of limited doping control in the drain and source implantation regions [21].

#### 1.2.2.6 Variability

Shrinking the channel dimensions results in a lower total number of dopants in the channel, which in turns amplifies the variability of the number and location of doping species inside the channel. Under these condition, statistical averaging over the whole set of doping species becomes impractical, and the threshold voltage consequently suffers from a higher variability. The Fig. 1.5 from [22] illustrates the impact of the shrinking dimensions on the fluctuation of dopant distribution along the channel.

#### 1.2.3 System Design

Many device parameters do not scale according to the linear scaling theory [9] as previously explained. As a result, many device parameters that used to be fixed by the technology node are becoming design parameters, such as the supply and the threshold voltage. The designer can optimize these parameters in order to obtain the best trade-off in terms of area, power and delay.

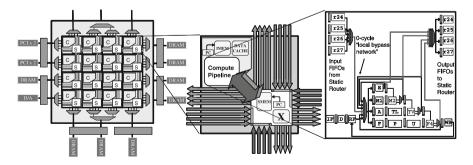

While the improvement in circuit density and performance has been achieved in the last decades by scaling down the transistors, latency of on-chip wires does not follow the same trend. The latencies of local interconnects scale accordingly; but global signals represent the big challenge. Their relative length to the device size does not scale down nor does is remain constant, because the chip size does not decrease while moving towards future technology nodes, given the fact that the number of transistors per chip continuously increases, and the die area roughly remains constant. The delay of global signals increases quadratically with their length, and their bandwidth accordingly degrades [12]. Wider interconnect wires may improve the overall latency, however they have a high cost in terms of energy-per-bit and bandwidth density (bits per second per unit routing width). Therefore, buses are becoming a less attractive option for on-chip connectivity; and they have to progressively be replaced by on-chip networks and other on-chip communication systems [23].

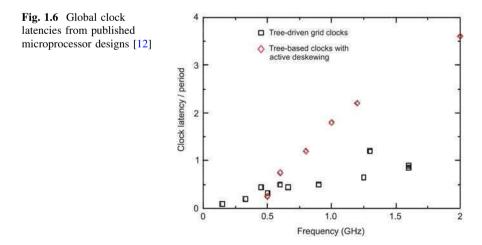

The clock distribution remains an important challenge in the design of digital systems. Most of modern clock systems are based on a single clock phase that is distributed globally, while local clock phases may be generated locally using different clock conditioning circuits. With the increasing relative length of global signals to the critical dimensions, the task of distributing the clock signal simultaneously (i.e., no skew) and periodically (i.e., no jitter) everywhere is becoming increasingly challenging. The relative non-scaling of wire delay and the increasing amount of capacitance per unit area worsen the clock latency (Fig. 1.6 from [12])

and increase the clock gain (measured as the ratio of the clock load capacitance to the capacitance driven from the phase-lock-loop reference) to extremely high values (more than  $10^5$ ). Moreover, skew and jitter become difficult to control when the temperature, process and supply voltage variation temporally and spatially increase.

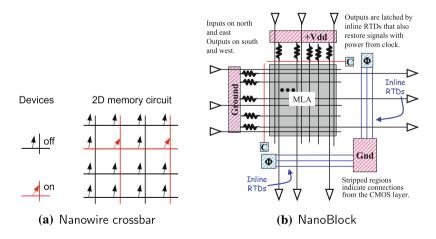

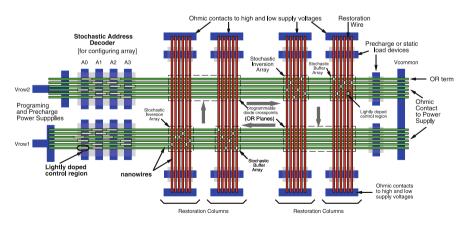

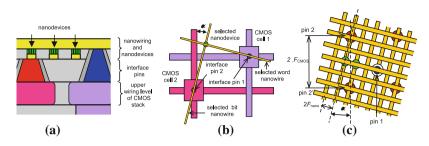

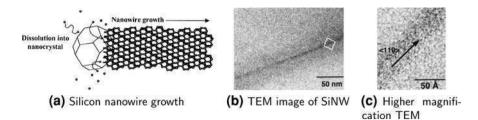

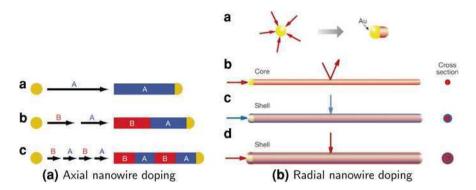

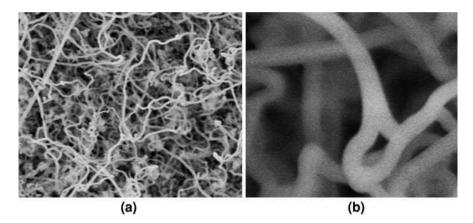

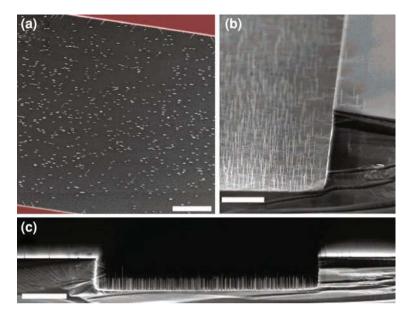

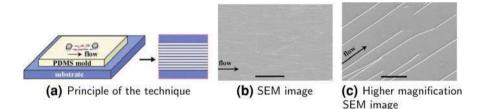

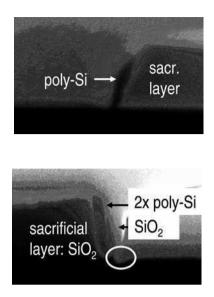

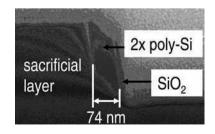

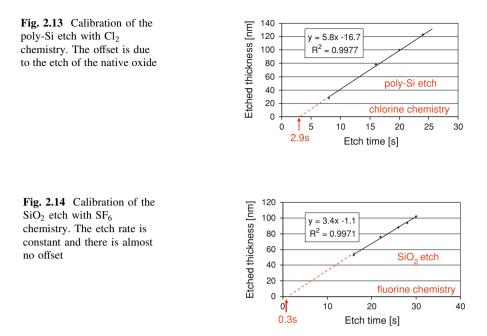

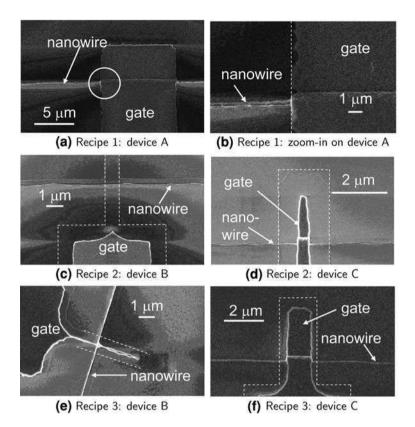

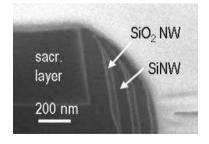

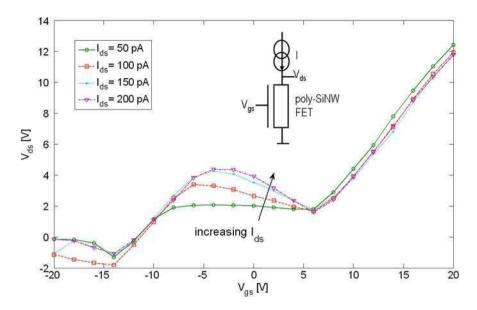

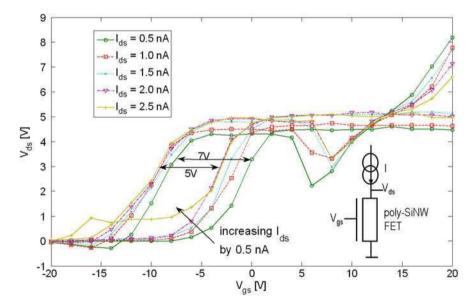

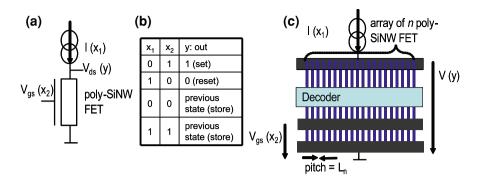

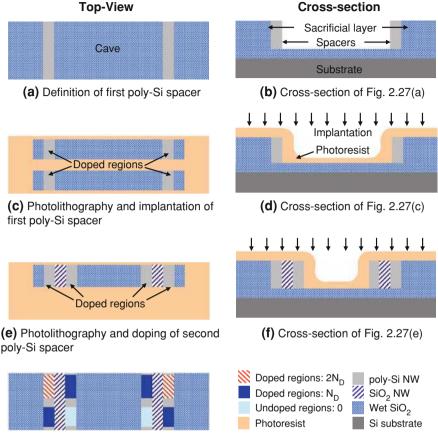

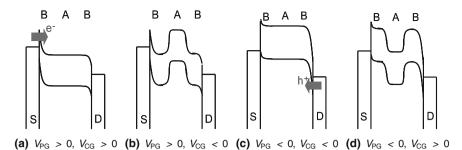

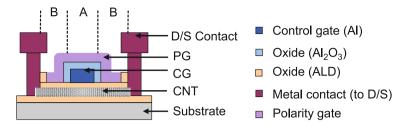

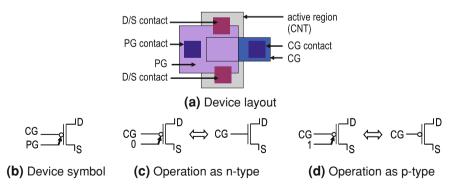

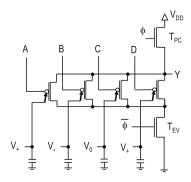

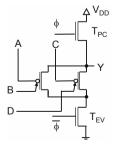

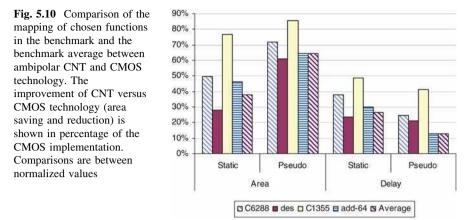

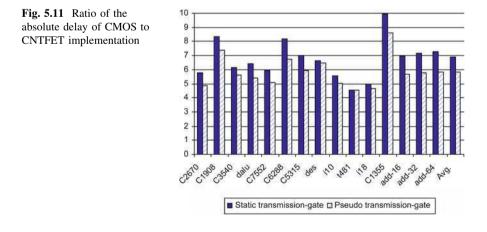

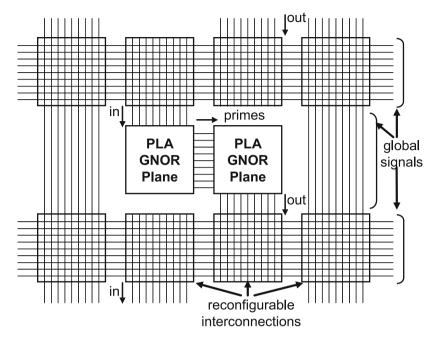

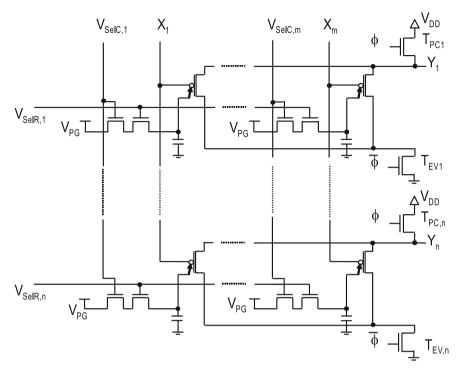

#### 1.2.4 Design Tools