Integrated Circuits and Systems

# Masashi Horiguchi Kiyoo Itoh Nanoscale Memory Repair

# Integrated Circuits and Systems

Series Editor Anantha Chandrakasan Massachusetts Institute of Technology Cambridge, Massachusetts

For further volumes, go to http://www.springer.com/series/7236

Masashi Horiguchi · Kiyoo Itoh

# Nanoscale Memory Repair

Dr. Masashi Horiguchi Renesas Electronics Corporation 5-20-1, Josuihon-cho Kodaira-shi, Tokyo, 187-8588 Japan masashi.horiguchi.kc@renesas.com Dr. Kiyoo Itoh Hitachi Ltd. Central Research Laboratory 1-280, Higashi-Koigakubo Kokubunji-shi, Tokyo, 185-8601 Japan kiyoo.itoh.pt@hitachi.com

ISSN 1558-9412 ISBN 978-1-4419-7957-5 e-ISBN 978-1-4419-7958-2 DOI 10.1007/978-1-4419-7958-2 Springer New York Dordrecht Heidelberg London

© Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the New York, written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

Repair techniques for nanoscale memories are becoming more important to cope with ever-increasing "errors" causing degraded yield and reliability. In fact, without repair techniques, even modern CMOS LSIs, such as MPUs/SoCs, in which memories have dominated the area and performances, could not have been successfully designed. Indeed, various kinds of errors have been prominent with larger capacity, smaller feature size, and lower voltage operations of such LSIs. The errors are categorized as hard/soft errors, timing/voltage margin errors, and speed-relevant errors. Hard/soft errors and timing/voltage margin errors, which occur in a chip, are prominent in a memory array because the array comprises memory cells having the smallest size and largest circuit count in the chip. In particular, coping with the margin errors is vital for low-voltage nanoscale LSIs, since the errors rapidly increase with device and voltage scaling. Increase in operating voltage is one of the best ways to tackle the issue. However, this approach is unacceptable due to intolerably increased power dissipation, calling for other solutions by means of devices and circuits. Speed-relevant errors, which are prominent at a lower voltage operation, comprise speed-degradation errors of the chip itself and intolerably wide chip-to-chip speed-variation errors caused by the ever-larger interdie designparameter variation. They must also be solved with innovative devices and circuits. For the LSI industry, in order to flourish and proliferate, the problems must be solved based on in-depth investigation of the errors.

Despite the importance, there are few authoritative books on repair techniques because the solutions to the problems lie across different fields, e.g., mathematics and engineering, logic and memories, and circuits and devices. This book systematically describes the issues, based on the authors' long careers in developing memories and low-voltage CMOS circuits. This book is intended for both students and engineers who are interested in the yield, reliability, and low-voltage operation of nanoscale memories. Moreover, it is instructive not only to memory designers, but also to all digital and mixed-signal LSI designers who are at the leading edge of such LSI developments.

Chapter 1 describes the basics of repair techniques. First, after categorizing sources of hard/soft errors, the reductions by means of redundancy, error checking

and correction (ECC), and their combination are comprehensively described. Second, after defining the minimum operating voltage  $V_{\min}$ , reductions of timing/ voltage margin errors are described in terms of  $V_{\min}$ . Finally, reduction techniques for speed-relevant errors are briefly discussed.

Chapter 2 deals with a detailed explanation of the redundancy techniques for repairing hard errors (faults), where faulty memory cells are replaced by spare memory cells provided on the chip in advance. Various yield models and calculations are introduced and various practical circuits and architectures that the authors regard as important for higher yield and reliability are discussed. The chapter also describes the devices for memorizing the addresses of faults and testing techniques for redundancy.

Chapter 3 describes the details of the ECC techniques to cope with both hard and soft errors, where extra bits (check bits) are added to original data bits, thereby enabling error detection and/or correction. After mathematical preparations, various error-correcting codes used for the techniques and their practical implementations in various memory LSIs are discussed. This is followed by the estimation of the reduction in hard-error and soft-error rates using ECC. Testing techniques for ECC are also described.

Chapter 4 deals with the combination of the redundancy and ECC. Combining both the techniques generates a synergistic effect and dramatically enhances the repair capability. It is especially effective for random-bit errors. After quantitative estimation of the synergistic effect, the application to the repair of faults due to device mismatch is discussed as a promising application of the effect.

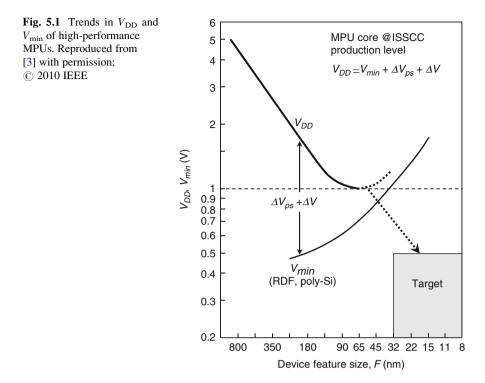

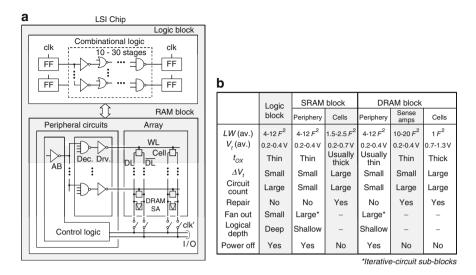

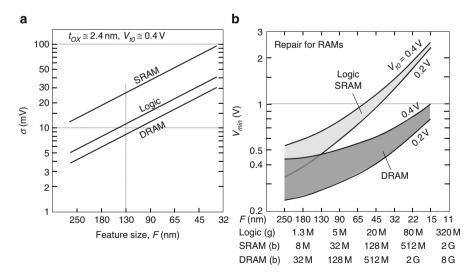

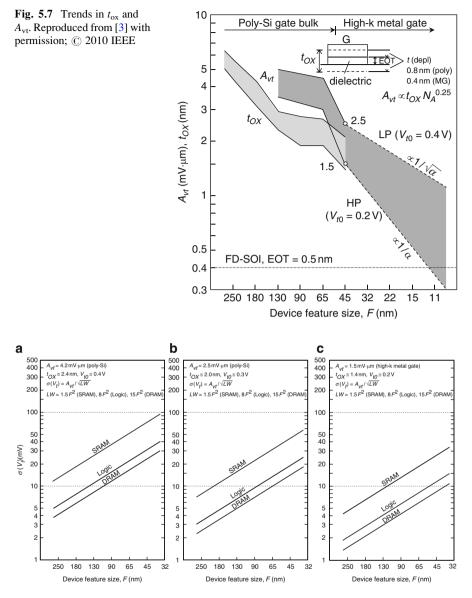

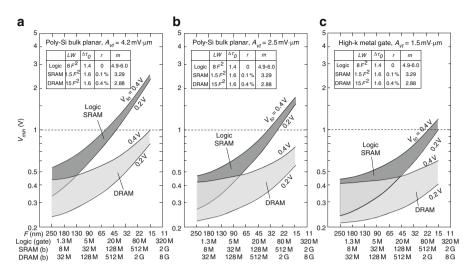

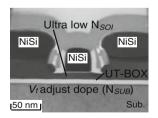

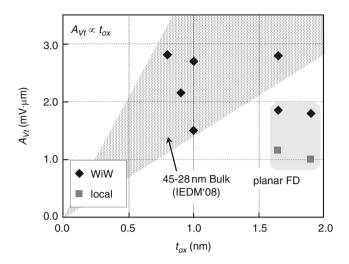

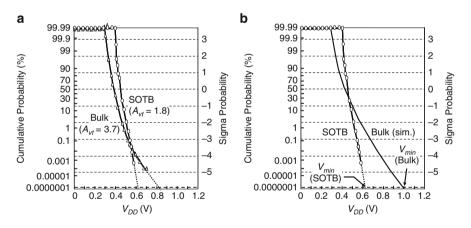

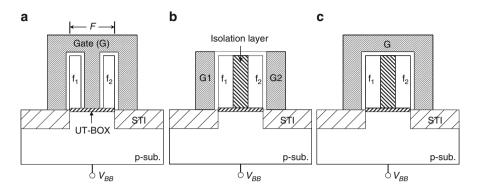

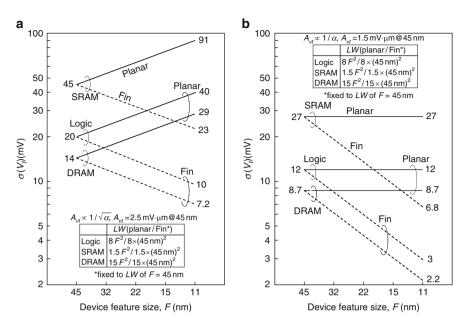

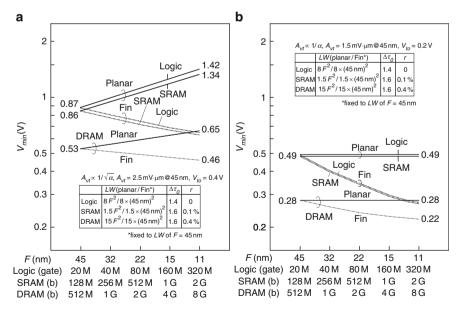

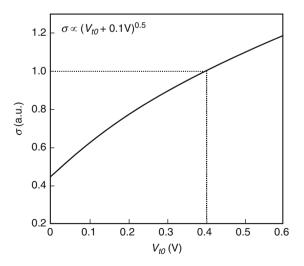

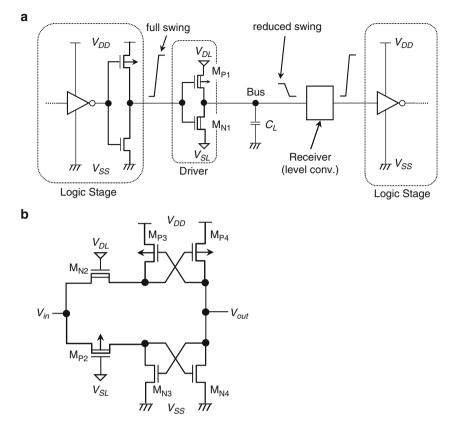

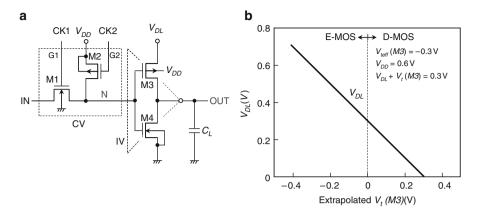

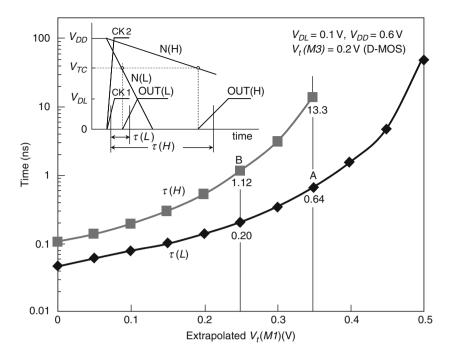

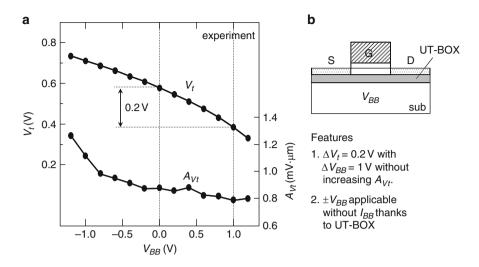

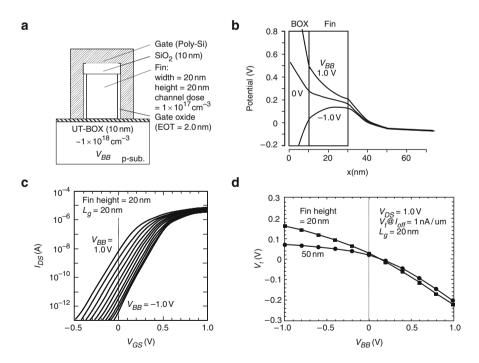

Chapter 5 systematically describes challenges to ultra-low-voltage nanoscale memories and the repair techniques to accomplish the issues. After clarifying that reduction in the minimum operating voltage  $V_{DD}$  (i.e.,  $V_{min}$ ) is the key to reducing the voltage and timing margin error, adaptive circuits and relevant technologies to reduce  $V_{min}$  are proposed, and the general features are described. Then, the  $V_{min}$ s of logic gates, SRAMs, and DRAMs are compared. After that, devices (e.g., fully depleted planar SOI and FinFET structures), circuits (e.g., gate-source reverse biasing schemes accepting low threshold voltage ( $V_t$ ) MOSFETs), and subsystems to widen the margins through reducing  $V_{min}$  are described.

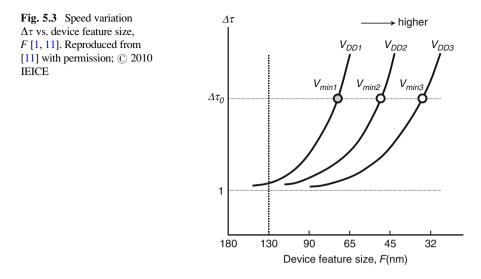

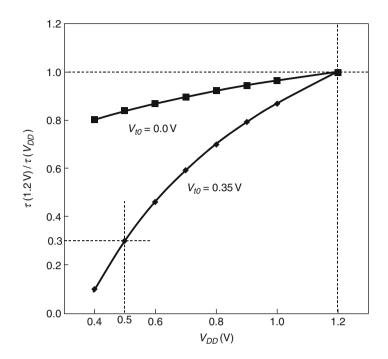

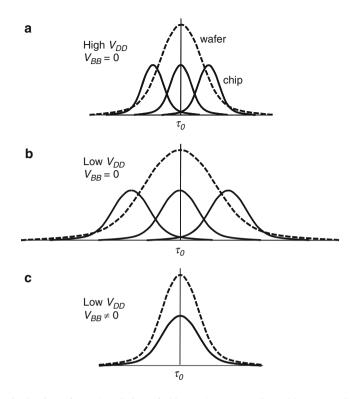

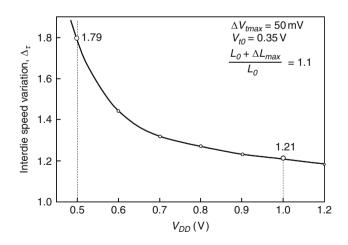

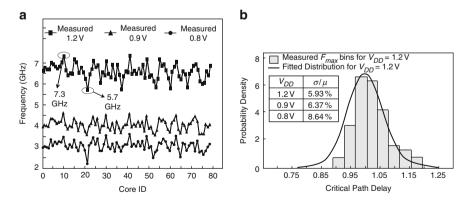

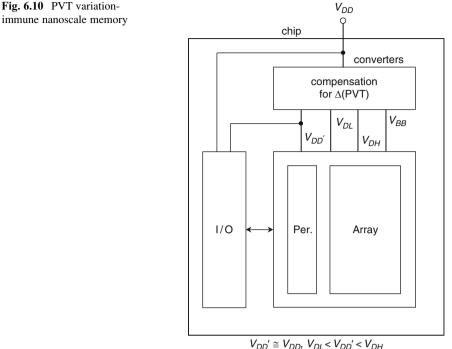

Chapter 6 briefly describes device/circuit techniques to cope with two kinds of speed-relevant errors, namely, the speed degradation error and the interdie speed variation error. After specifying reduced gate-over-drive voltage of MOSFETs as the source of the speed degradation error, some solutions (e.g., using low- $V_{t0}$  circuits and dynamic  $V_t$  circuits utilizing double-gate FD-SOI structures) are exemplified. Moreover, after specifying the so-called global variation of design parameters in the wafer as the source of the interdie speed variation error, some solutions such as power management for compensating for the variation with static or quasi-static controls of internal supply voltages are presented.

Tokyo, Japan

Masashi Horiguchi Kiyoo Itoh

# Contents

| 1 | An Introduction to Repair Techniques            | 1   |

|---|-------------------------------------------------|-----|

|   | 1.1 Introduction                                | . 1 |

|   | 1.2 Hard and Soft Errors and Repair Techniques  |     |

|   | 1.2.1 Hard and Soft Errors.                     |     |

|   | 1.2.2 Redundancy                                |     |

|   | 1.2.3 ECC                                       | .5  |

|   | 1.2.4 Combination of Redundancy and ECC         |     |

|   | 1.2.5 Others                                    |     |

|   | 1.3 Margin Errors and Repair Techniques         |     |

|   | 1.3.1 Device and Process Variations             |     |

|   | 1.3.2 Timing and Voltage Margin Errors          | 11  |

|   | 1.3.3 Reductions of Margin Errors               |     |

|   | 1.4 Speed-Relevant Errors and Repair Techniques |     |

|   | References                                      |     |

|   |                                                 |     |

| 2 | Redundancy                                      | 19  |

|   | 2.1 Introduction                                | 19  |

|   | 2.2 Models of Fault Distribution                | 20  |

|   | 2.2.1 Poisson Distribution Model                | 20  |

|   | 2.2.2 Negative-Binomial Distribution Model      | 22  |

|   | 2.3 Yield Improvement Through Redundancy        |     |

|   | 2.4 Replacement Schemes                         |     |

|   | 2.4.1 Principle of Replacement                  |     |

|   | 2.4.2 Circuit Implementations                   | 30  |

|   | 2.5 Intrasubarray Replacement.                  |     |

|   | 2.5.1 Simultaneous and Individual Replacement   |     |

|   | 2.5.2 Flexible Replacement                      |     |

|   | 2.5.3 Variations of Intrasubarray Replacement   |     |

|   | 2.6 Intersubarray Replacement.                  |     |

|   | 2.7 Subarray Replacement                        |     |

|   |                                                 |     |

|   | 2.8 Devices for Storing Addresses                            | 56  |

|---|--------------------------------------------------------------|-----|

|   | 2.8.1 Fuses                                                  | 56  |

|   | 2.8.2 Antifuses                                              |     |

|   | 2.8.3 Nonvolatile Memory Cells                               | 60  |

|   | 2.9 Testing for Redundancy                                   |     |

|   | References                                                   | 64  |

| 3 | Error Checking and Correction (ECC)                          | 69  |

|   | 3.1 Introduction                                             | 69  |

|   | 3.2 Linear Algebra and Linear Codes                          | 70  |

|   | 3.2.1 Coding Procedure                                       |     |

|   | 3.2.2 Decoding Procedure                                     |     |

|   | 3.3 Galois Field                                             |     |

|   | 3.4 Error-Correcting Codes                                   |     |

|   | 3.4.1 Minimum Distance                                       | 78  |

|   | 3.4.2 Number of Check Bits                                   |     |

|   | 3.4.3 Single Parity Check Code                               | 82  |

|   | 3.4.4 Hamming Code                                           | 82  |

|   | 3.4.5 Extended Hamming Code and Hsiao Code                   | 84  |

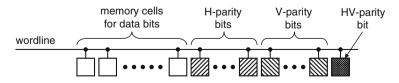

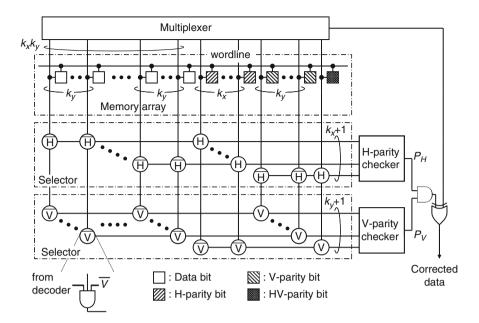

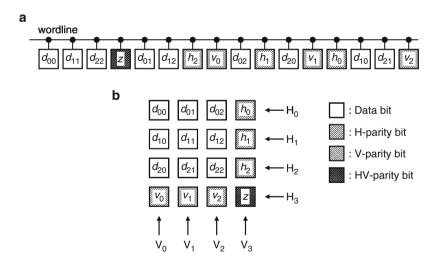

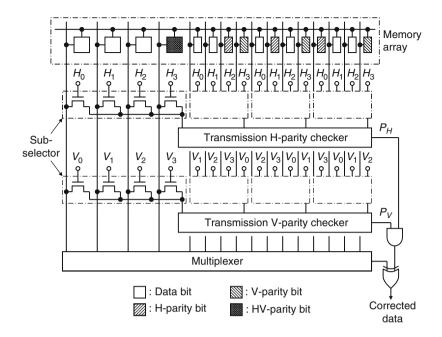

|   | 3.4.6 Bidirectional Parity Code                              | 85  |

|   | 3.4.7 Cyclic Code                                            |     |

|   | 3.4.8 Nonbinary Code                                         | 89  |

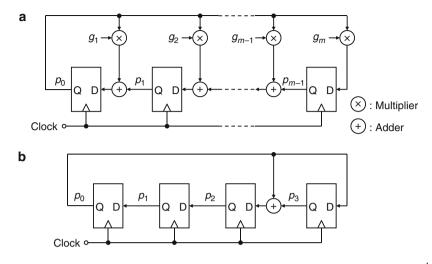

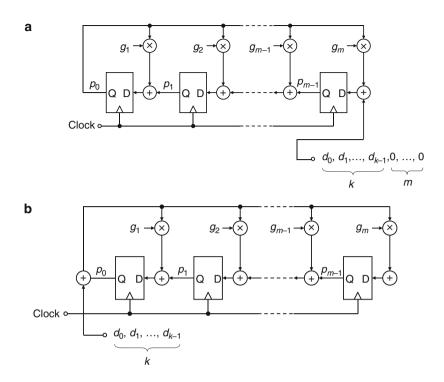

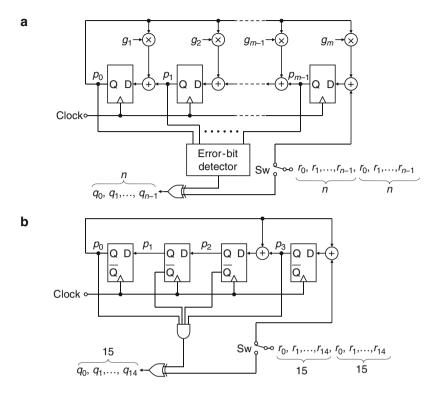

|   | 3.5 Coding and Decoding Circuits                             |     |

|   | 3.5.1 Coding and Decoding Circuits for Hamming Code          |     |

|   | 3.5.2 Coding and Decoding Circuits for Cyclic Hamming Code   |     |

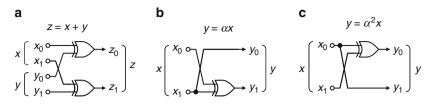

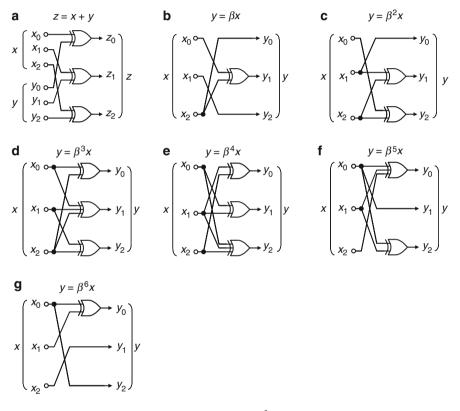

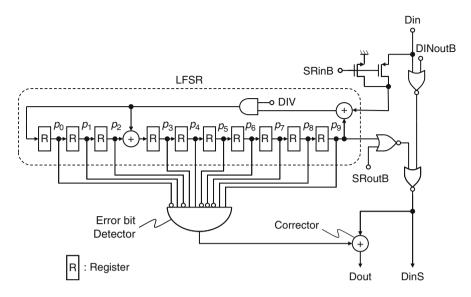

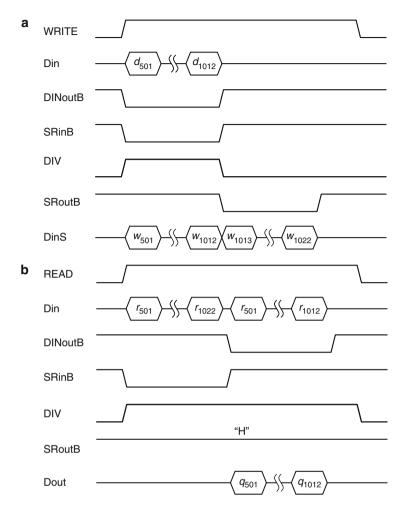

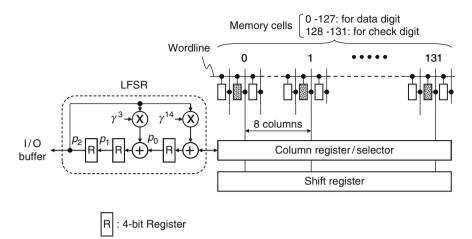

|   | 3.5.3 Coding and Decoding Circuits for Nonbinary Code        |     |

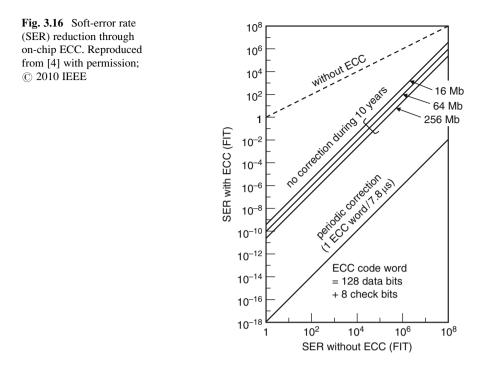

|   | 3.6 Theoretical Reduction in Soft-Error and Hard-Error Rates |     |

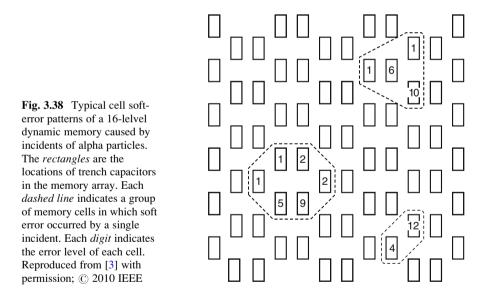

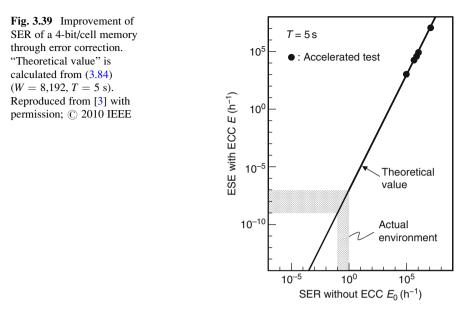

|   | 3.6.1 Reduction in Soft-Error Rate                           |     |

|   | 3.6.2 Reduction in Hard-Error Rate                           | 108 |

|   | 3.7 Application of ECC                                       |     |

|   | 3.7.1 Application to Random-Access Memories                  |     |

|   | 3.7.2 Application to Serial-Access Memories                  | 126 |

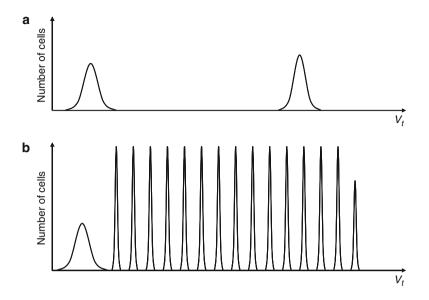

|   | 3.7.3 Application to Multilevel-Storage Memories             |     |

|   | 3.7.4 Application to Other Memories                          |     |

|   | 3.8 Testing for ECC                                          |     |

|   | References                                                   | 136 |

| 4 | Combination of Redundancy and Error Correction               | 139 |

|   | 4.1 Introduction                                             |     |

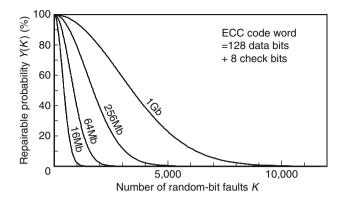

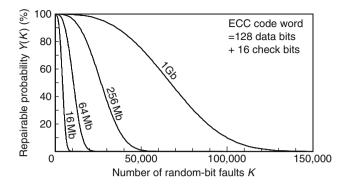

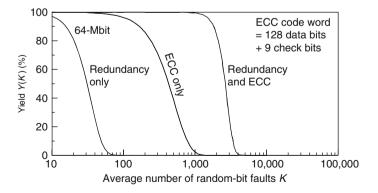

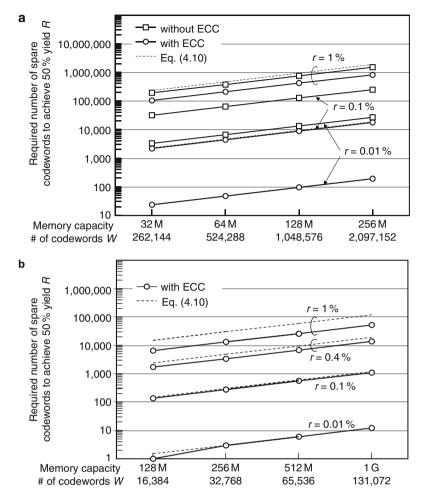

|   | 4.2 Repair of Bit Faults Using Synergistic Effect            |     |

|   | 4.2.1 Principle of Synergistic Effect                        |     |

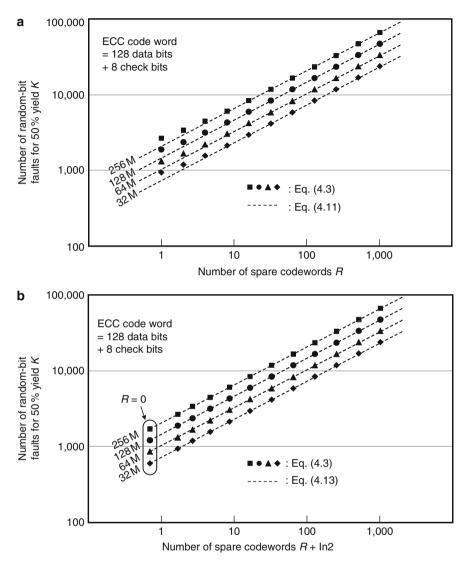

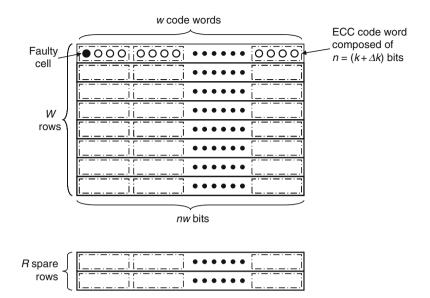

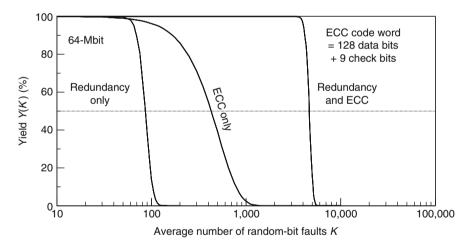

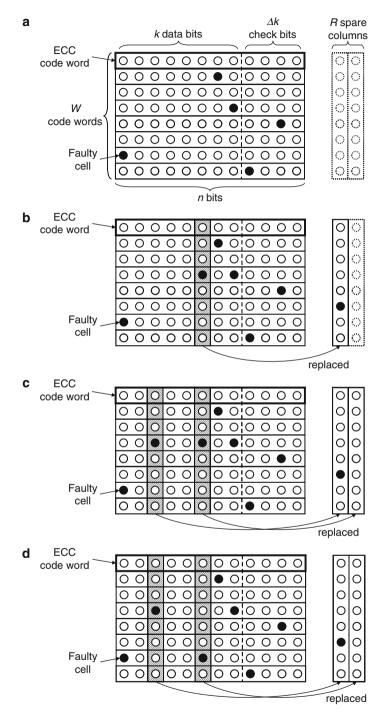

|   | 4.2.2 Yield Estimation                                       |     |

|   | 4.3 Application of Synergistic Effect                        | 149 |

|   | 4.3.1 Threshold-Voltage Variations                           | 149 |

|   | 4.3.2 Estimated Effect                                       | 151 |

|   | References                                                   | 155 |

|   |                                                              |     |

| 5  | Reduction Techniques for Margin Errors of Nanoscale Memories     | 157   |

|----|------------------------------------------------------------------|-------|

|    | 5.1 Introduction                                                 |       |

|    | 5.2 Definition of $V_{\min}$                                     |       |

|    | 5.3 Reduction of $V_{\min}$ for Wider Margins                    |       |

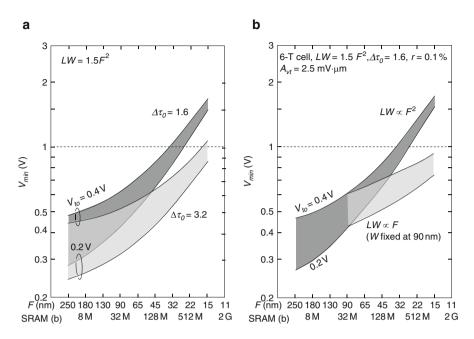

|    | 5.3.1 General Features of $V_{\min}$                             |       |

|    | 5.3.2 Comparison of $V_{\min}$ for Logic Block, SRAMs, and DRAMs |       |

|    | 5.4 Advanced MOSFETs for Wider Margins                           |       |

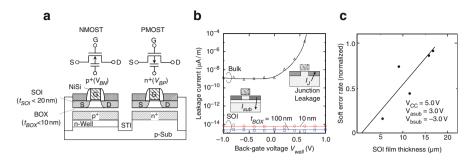

|    | 5.4.1 Planar FD-SOI MOSFETs                                      |       |

|    | 5.4.2 FinFETs                                                    |       |

|    | 5.5 Logic Circuits for Wider Margins                             |       |

|    | 5.5.1 Gate-Source Offset Driving                                 |       |

|    | 5.5.2 Gate-Source Differential Driving.                          |       |

|    | 5.5.3 Combined Driving                                           |       |

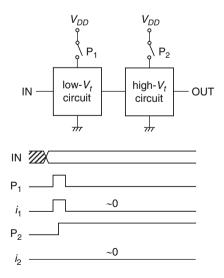

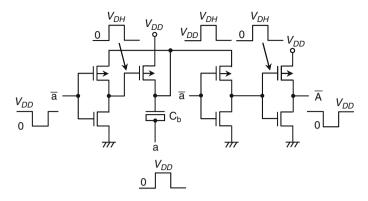

|    | 5.5.4 Instantaneous Activation of Low- $V_{t0}$ MOSFETs          |       |

|    | 5.5.5 Gate Boosting of High- $V_{t0}$ MOSFETs                    |       |

|    | 5.6 SRAMs for Wider Margins                                      |       |

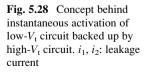

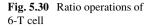

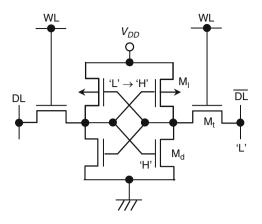

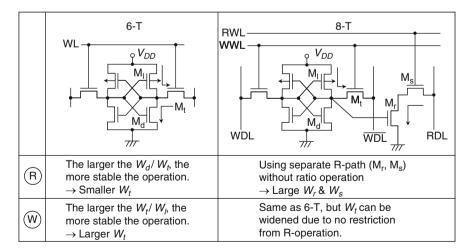

|    | 5.6.1 Ratio Operations of the 6-T Cell                           |       |

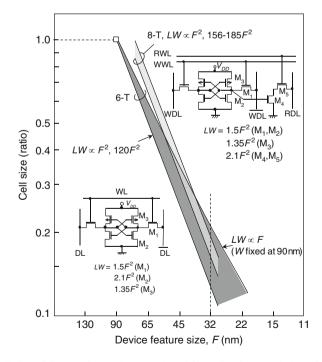

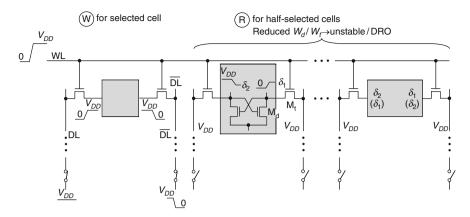

|    | 5.6.2 Shortening of Datalines and Up-Sizing of the 6-T Cell      |       |

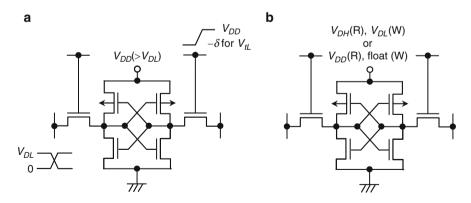

|    | 5.6.3 Power Managements of the 6-T Cell                          |       |

|    | 5.6.4 The 8-T Cell                                               |       |

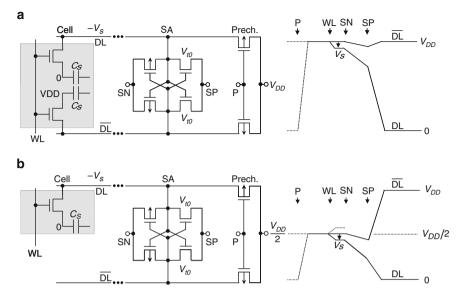

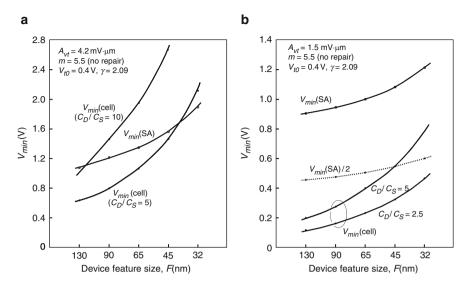

|    | 5.7 DRAMs for Wider Margins                                      |       |

|    | 5.7.1 Sensing Schemes.                                           |       |

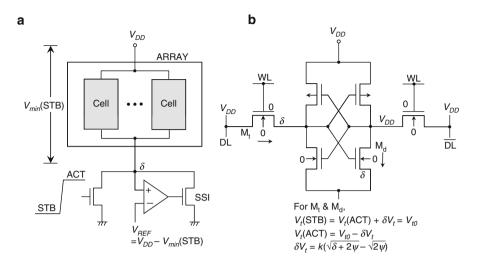

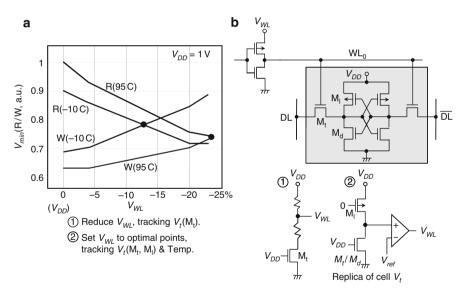

|    | 5.7.2 $V_{\min}(SA)$ of Sense Amplifier                          |       |

|    |                                                                  |       |

|    | 5.7.4 Comparison Between $V_{\min}(SA)$ and $V_{\min}(Cell)$     | . 190 |

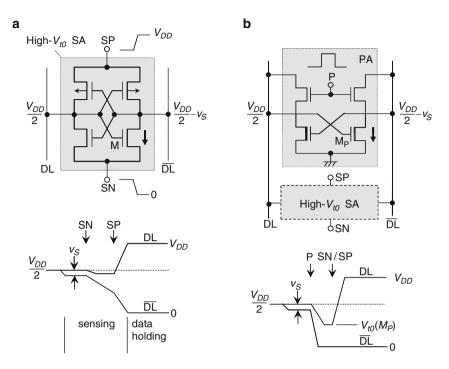

|    | $5.7.5$ Low- $v_{t0}$ sense Ampliner                             |       |

|    | 5.8 Subsystems for Wider Margins                                 |       |

|    | 5.8.1 Improvement of Power Supply Integrity                      |       |

|    | 5.8.2 Reduction in $V_{t0}$ at Subsystem Level                   |       |

|    | 5.8.2 Low- $V_{t0}$ Power Switches.                              |       |

|    | References                                                       |       |

|    |                                                                  | . 190 |

| 6  | Reduction Techniques for Speed-Relevant Errors                   |       |

| U  | of Nanoscale Memories                                            | 203   |

|    | 6.1 Introduction                                                 |       |

|    | 6.2 Reduction Techniques for Speed-Degradation Errors            |       |

|    | 6.3 Reduction Techniques for Interdie Speed-Variation Errors     |       |

|    | 6.3.1 On-Chip $V_{\rm BB}$ Compensation                          |       |

|    | 6.3.2 On-Chip $V_{DD}$ Compensation and Others                   |       |

|    | References .                                                     |       |

|    |                                                                  |       |

| In | ex                                                               | 213   |

|    |                                                                  |       |

### Chapter 1 An Introduction to Repair Techniques

#### 1.1 Introduction

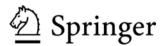

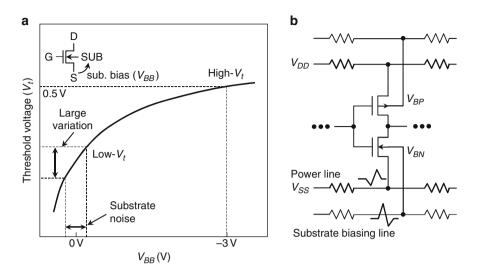

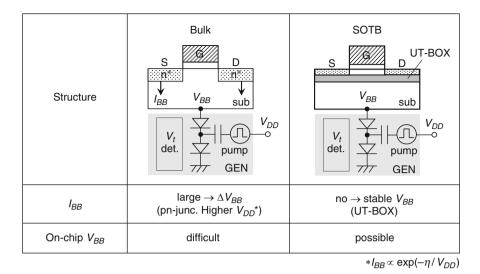

With larger capacity, smaller feature size, and lower voltage operations of memory-rich CMOS LSIs (Fig. 1.1), various kinds of "errors (faults)" have been prominent and the repair techniques for them have become more important. The "errors" are categorized as hard/soft errors, timing/voltage margin errors, and speed-relevant errors. Hard/soft errors and timing/voltage margin errors, which occur in a chip, are prominent in a memory array because the array comprises memory cells having the smallest size and largest circuit count in the chip. In particular, coping with the margin errors is becoming increasingly important, and thus an emerging issue for low-voltage nanoscale LSIs, since the errors rapidly increase with device and voltage scaling. Increase in operating voltage is one of the best ways to tackle the issue. However, this approach is not acceptable due to intolerably increased power dissipation. Speed-relevant errors, which are prominent at a lower voltage operation, include speed-degradation errors of the chip itself and intolerably wide chip-to-chip speed-variation errors caused by the ever-larger interdie design-parameter variation. For the LSI industry in order to flourish and proliferate, solutions based on in-depth investigation of the errors are crucial.

In this chapter, first, after categorizing sources of hard/soft errors, reductions of hard/soft errors by means of redundancy, error checking and correction (ECC), and their combination are comprehensively described. Second, after defining the minimum operating voltage  $V_{\rm min}$ , reductions of timing/voltage margin errors are described in terms of  $V_{\rm min}$ . Finally, reduction techniques for speed-relevant errors are briefly discussed.

#### 1.2 Hard and Soft Errors and Repair Techniques

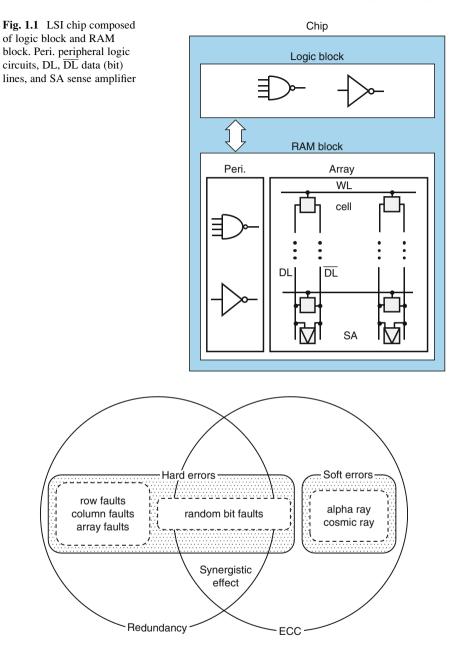

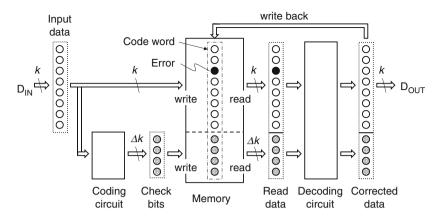

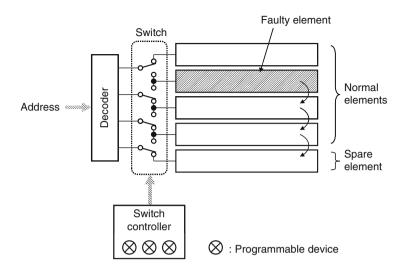

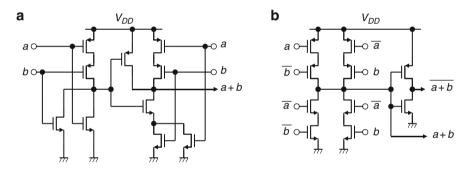

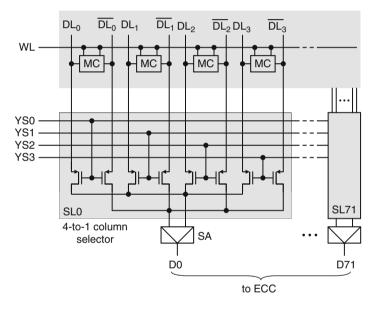

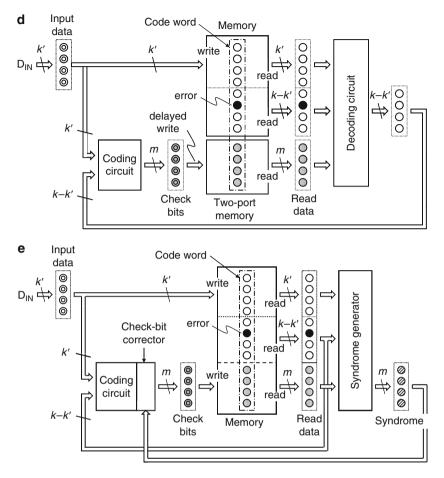

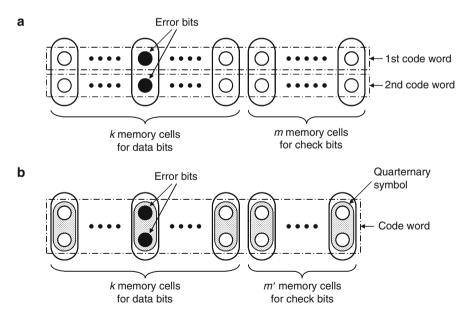

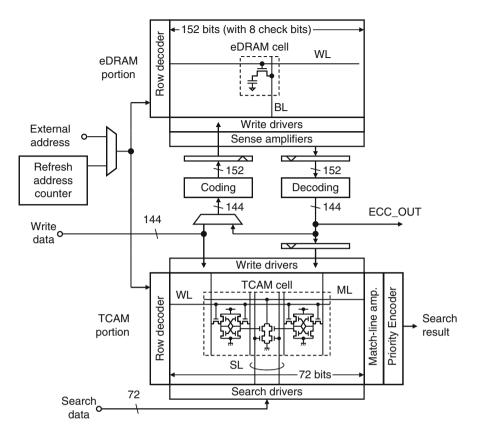

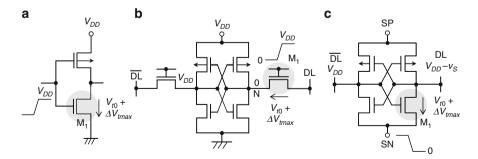

There are many sources of hard and soft errors. To repair the errors, redundancy and on-chip ECC, as shown in Fig. 1.2, and the combination are effective.

Fig. 1.2 Repair techniques for memories: redundancy and error checking and correction (ECC)

#### 1.2.1 Hard and Soft Errors

The hard errors, which are mainly caused by various fabrication-process defects, permanently cause incorrect operations of a part of an LSI chip or an entire chip.

They are classified into single-bit faults (only a memory cell is faulty), row/column faults (all the memory cells on a row/column are faulty), array faults (all the memory cells in a memory array are faulty), etc., according to the number of faulty cells and their distribution. The hard errors increase with device scaling due to need for more complicated process and device technologies.

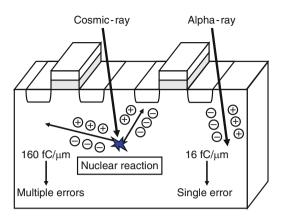

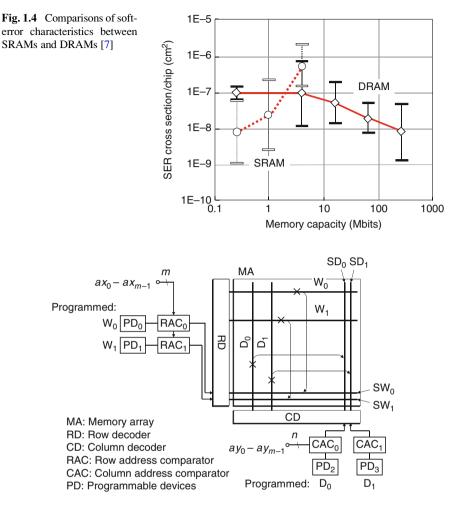

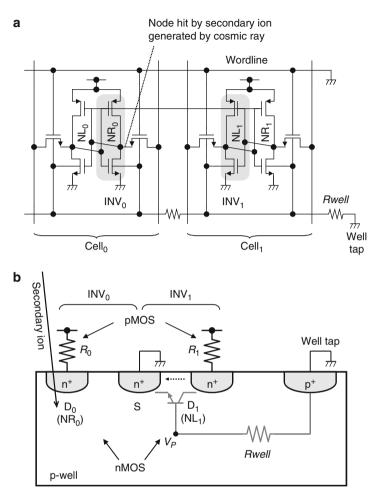

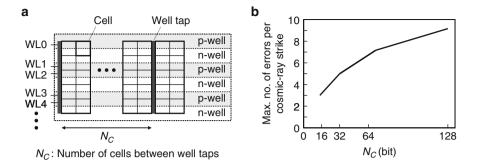

The soft errors are phenomena that the information stored in memory cell nodes and other circuit nodes is lost. They are caused by noises, especially by the incidents of alpha ray or cosmic ray. If the charge generated by the incidents is collected at the node that retains information, an upset of the node voltage may occur (Fig. 1.3) [1–4]. Since devices are not broken by soft errors, correct operations are possible after rewriting the lost information. The smaller the signal charge of the node (i.e., product of the voltage and capacitance), the larger the soft error rate (SER). Hence, SER increases with device and voltage scaling because signal charge is reduced, and the SER of memory cells usually having the smallest signal charge are thus larger than that of logic gates. In particular, the soft-error problem is problematic for SRAMs with device scaling, as seen in Fig. 1.4. The rapidly reduced signal charge of the cell is responsible for the increase because a capacitor is not added intentionally at stored nodes, unlike dynamic random-access memory (DRAM) cells. Even for logic circuits, alpha ray or cosmic ray causes soft errors.

#### 1.2.2 Redundancy

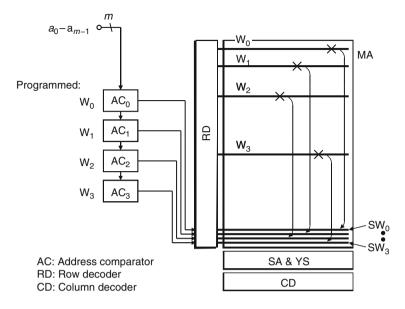

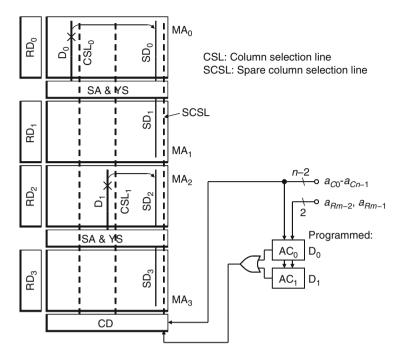

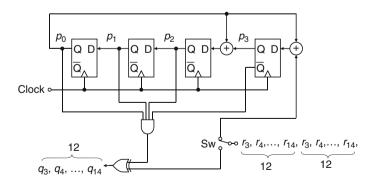

The redundancy technique is used for repairing hard errors. The idea was proposed in the 1960s [5, 6] and was applied to actual 64–256-kb RAMs in the late 1970s [7–9]. Since then, it has been widely used as effective methods of enhancing production yield and reducing cost per bit of DRAMs. In this scheme, faulty memory cells are replaced by spare memory cells, which are provided on the chip in advance. The replacement is controlled by programmable devices, in which the addresses of faulty memory cells are programmed before shipping. Usually, a row/column of memory

Fig. 1.5 Principle of redundancy for a RAM [7]

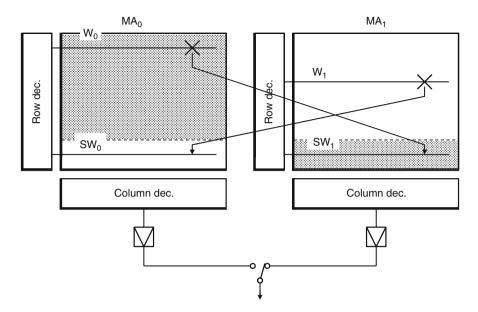

cells (usually wordlines and/or datalines), including faulty ones is replaced by a spare row/column because the memory cells are arranged in a matrix. Figure 1.5 shows a well-known redundancy technique [7] applied to a RAM. Here, the memory has two spare wordlines SW<sub>0</sub>, SW<sub>1</sub> and the same number of row-address comparators RAC<sub>0</sub>, RAC<sub>1</sub>, and programmable devices PD<sub>0</sub>, PD<sub>1</sub>. If the addresses of the faulty wordlines (W<sub>0</sub>, W<sub>1</sub>) have been programmed into the devices during wafer testing, the address comparators allow one of the spare wordlines (SW<sub>0</sub>, SW<sub>1</sub>) to be activated whenever a set of input row-address signals ( $ax_0 - ax_{m-1}$ ) during actual operations matches one of the faulty addresses. Thus, W<sub>0</sub> and W<sub>1</sub> are replaced by SW<sub>0</sub> and SW<sub>1</sub> (SW<sub>0</sub> and SW<sub>1</sub> are used instead of W<sub>0</sub> and W<sub>1</sub>), respectively. Similarly, faulty data lines D<sub>0</sub> and D<sub>1</sub> are replaced by spare datalines SD<sub>0</sub> and SD<sub>1</sub>, respectively. In modern RAMs, as many as over 100 faulty elements could be replaced by spare elements in the early stage of production, with an additional chip area of less than 5%. The programmable devices are usually poly-Si fuses, which are blown by means of a laser beam or a pulsed current, although they do accept antifuses or nonvolatile memory cells [7]. Laser programming occupies a smaller chip area and does not normally affect circuit performance, but it does require special test equipment and increases wafer handling and testing time. Also, the laser spot size and beam-positioning requirements become more stringent for ever finer line widths. On the other hand, electrical programming by a pulsed current is carried out using standard test equipment. Usually, a hole is cut in the passivation glass over such fuses to reduce the amount of programming current needed. The possibility of mobile-ion contamination of active circuit areas can be eliminated by using guard-ring structures surrounding the fuse area, or other techniques [7]. The area and performance penalties of electrical programming can be minimized by careful circuit design. Electrical programming is used when the number of fuses required is not large enough to offset the negative aspects of laser programming. In any event, laser programming has been widely accepted due to the small area and performance penalties, simplicity, assurance of cutting, and the ease of laying out fuses.

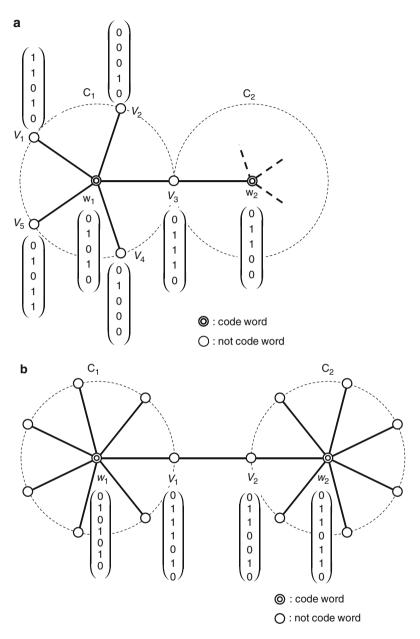

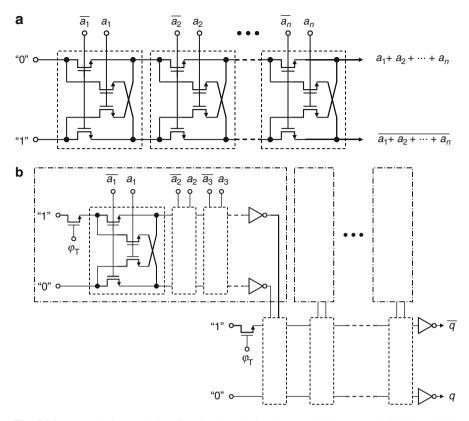

#### 1.2.3 ECC

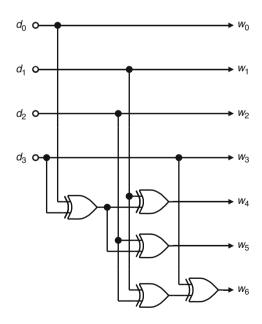

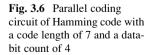

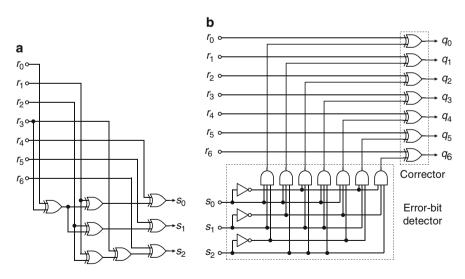

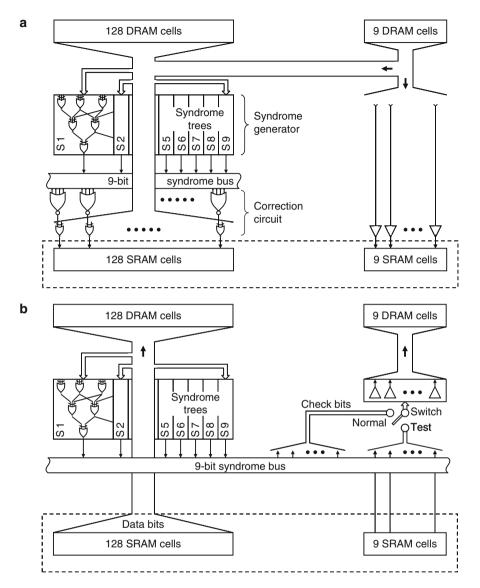

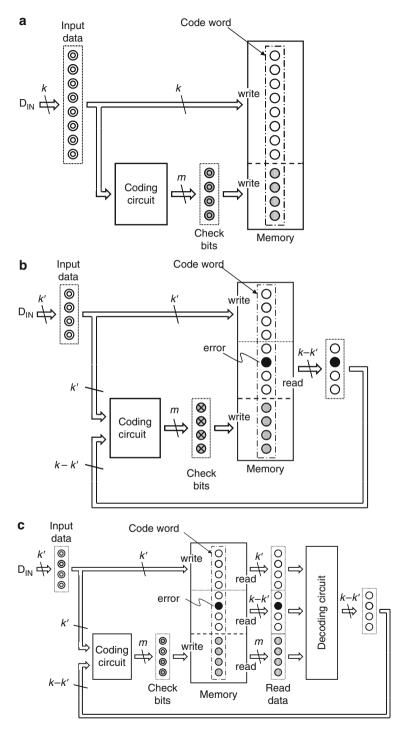

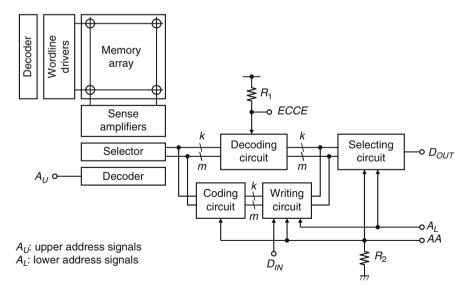

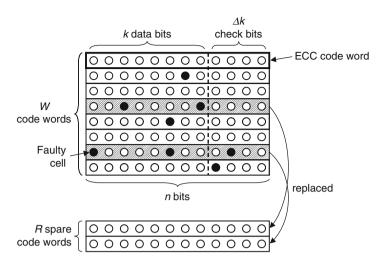

In the past, off-chip ECC technique was used for enhancing the reliability of main storages of computer systems. Nowadays, on-chip ECC technique has been widely used in various memory LSIs, since the importance was recognized by the discovery of soft error caused by alpha ray [1]. On-chip ECC is effective for correcting both soft errors and hard errors (faults) of RAMs [10-12]. The ECC technique provides extra memory cells on a chip to enable ECC using the information stored in the cells (check bits). Unlike the redundancy, programmable devices to store faulty addresses are not necessary. The principle of ECC is shown in Fig. 1.6. During write operation, the coding circuit generates check bits from the input data bits. The generation rule is determined by the error-correcting code used. The set composed of the data bits and the check bits generated according to the rule is called a *code word*. The code word is written into the memory array so that the stored information has a certain amount of redundancy. If there is a fault in the memory array or a soft error occurs before reading, the read data contain one or more errors. However, the error(s) can be detected and corrected by the decoding circuit if the number of errors does not exceed the correction capability of the error-correcting code. The operation of the decoding circuit is as follows. First, check bits are generated from the read data bits just like the coding circuit and are compared with the read check bits. If no error exists, both are the same. If they are not the same, the position(s) of erroneous bit(s) are detected by analyzing the comparison results and the errors are corrected before outputting. The corrected data are usually written back to the memory array to prevent the accumulation of soft errors. In DRAMs, checking and correcting are performed during every refresh operation [10] as well as during read operation.

Fig. 1.6 Principle of on-chip ECC for a RAM [7]

| Table 1.1 Number of requi       | red check | bits for s | single-erro | r correctio | n (SEC) c | ode |     |

|---------------------------------|-----------|------------|-------------|-------------|-----------|-----|-----|

| Number of data bits $k$         | 4         | 8          | 16          | 32          | 64        | 128 | 256 |

| Number of check bits $\Delta k$ | 3         | 4          | 5           | 6           | 7         | 8   | 9   |

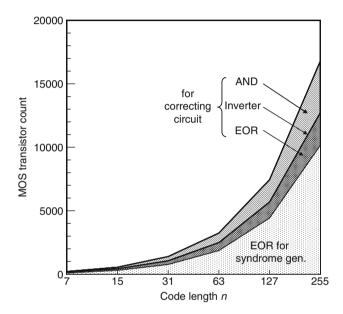

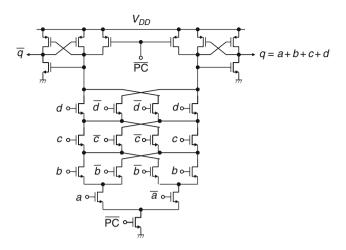

The key to designing an on-chip ECC circuit is the selection of a suitable errorcorrecting code. Error-correcting codes are classified into single-error correction (SEC) codes, single-error correction and double-error detection (SEC-DED) codes, double-error correction (DEC) codes, etc., according to the error-detection/correction capability. Table 1.1 shows the number of required check bits of a SEC code,  $\Delta k$ , for k data bits. It should be noted that the ratio  $\Delta k/k$  decreases as k increases. Although a large k reduces the memory-area penalty, it results in both large circuitarea and access-time penalties. This is because the number of logic gates for the encoding and decoding circuits is approximately proportional to  $k \log_2 k$  and the number of stages of the circuits is proportional to  $\log_2 k$ . Therefore, the design of an ECC circuit requires a compromise among the memory area, circuit area, and access time. The error-correcting codes that have been applied to RAMs until now include Hamming codes [12], extended Hamming codes [11], and bidirectional parity codes [10]. The former one is an SEC code, while the latter two are SEC-DED codes. DEC codes were not realistic for on-chip ECC because of considerable enlargement of the encoding/decoding circuits. For nanoscale memories, however, a DEC (or more) code might be necessary because of the increase in error rates, while the circuit-area penalty is reduced due to device scaling [13]. The correcting efficiency is closely related to array architectures as well as device structures immune to soft errors, as explained in Chaps. 3 and 5.

*Comparison Between Redundancy and ECC*: Both the redundancy and the ECC have their own advantages and disadvantages. Therefore, they are used for repairing different types of errors as shown in Fig. 1.2. The differences are summarized as follows.

- (1) The addresses of faults are programmed on chip and the programmable devices to store the addresses are needed in the redundancy. On the other hand, no addresses are programmed in the ECC. The ECC can repair errors at any addresses as long as the number of errors does not exceed the correcting capability, while the redundancy can repair only the programmed addresses. In addition, the ECC can repair both soft errors and hard errors, while the redundancy can repair only hard errors.

- (2) The chip-size and access-time penalties due to ECC are usually larger than those due to redundancy. The chip-size penalty includes memory cells for check bits and coding/decoding circuits, and the access-time penalty is the coding/decoding times. In addition, the number of extra cells for the ECC is determined by the error-correcting code, while that for the redundancy can be determined more freely according to the error rate and desired yield.

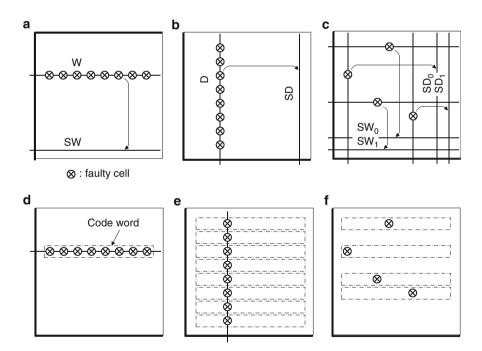

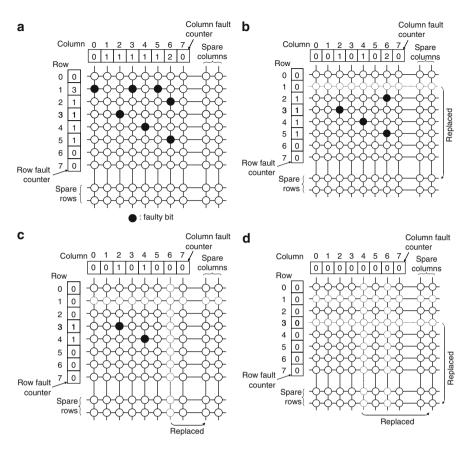

- (3) The redundancy and the ECC are suitable for different types of hard errors (faults) as shown in Fig. 1.7. Among various types of faults in memory LSIs, row faults and column faults are effectively repaired by the redundancy (Fig. 1.7a, b). However, repairing efficiency of random-bit faults by the redundancy is not high (Fig. 1.7c). For example, random-bit faults include insufficient voltage margin (e.g., static noise margin) due to device mismatch in

**Fig. 1.7** Hard-error repair using redundancy and ECC: (a) a faulty row is replaced by a spare row, (b) a faulty column is replaced by a spare column, (c) the repairing efficiency of random-bit faults by redundancy is not high, (d) a row fault cannot be repaired by ECC, (e) a column fault can be theoretically repaired by ECC, and (f) random-bit faults can be effectively repaired by ECC

SRAM cells [14, 15], and insufficient data-retention time in DRAM cells. Even if there is only one faulty cell in a row (column), an entire row (column) of spare cells are required. Generally, random-bit faults require as many spare lines (rows or columns) as the number of faulty cells unless two or more faulty cells are located on a row (column). The ECC can effectively repair these faults if the distribution of faulty cells is random as shown in Fig. 1.7f. On the other hand, the ECC is not suitable for repairing row and column faults. Row faults cannot be repaired by ECC. A code word of ECC is usually composed of memory cells in a row because they must be simultaneously read out. Therefore a row fault causes all the bits in a code word to be faulty, making it uncorrectable (Fig. 1.7d). Column faults can be theoretically repaired by the ECC because each code word along the faulty column contains only one faulty bit. However, another faulty bit in these code words cannot be repaired (Fig. 1.7e). Therefore, the redundancy is more suitable for repairing row and column faults.

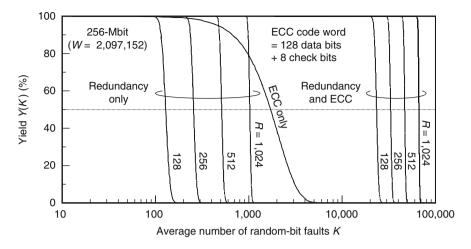

#### 1.2.4 Combination of Redundancy and ECC

Combination of the redundancy and the ECC maximizes the repair efficiency, as described in Chap. 4. It was found that the number of repairable errors dramatically increases by combining the redundancy and ECC techniques together [11]. This is because, for example, code words with only one defect cell are corrected by the ECC, and code words with two or more defect cells can be replaced by redundant words. This synergistic effect is especially effective for random-bit faults. Here, the random-bit faults include refresh faults of DRAMs.

#### 1.2.5 Others

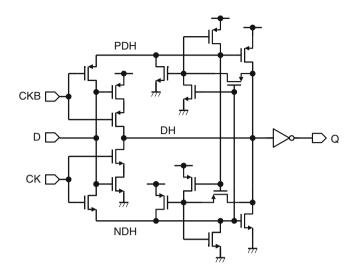

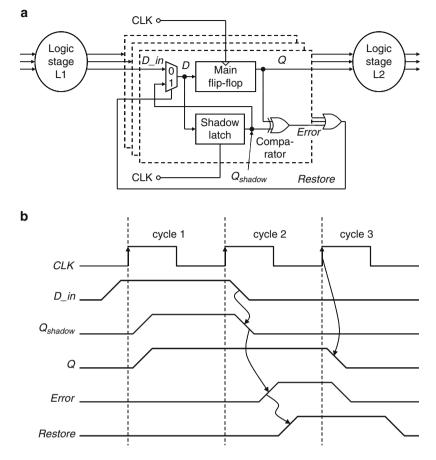

Hard errors and soft errors may occur even in logic circuits. An example is the soft error that the data in a latch is lost by the charge generated in Si substrate by cosmic-ray incident [16]. Another example is the timing error caused by the increase in variations of delay time of combinatorial circuits caused by device variations, particularly enhanced under low supply voltage. This is especially important for the so-called dynamic voltage scaling (DVS) techniques where supply voltage is dynamically changed for power reduction. The repair of errors of logic circuits, however, is more difficult because the circuit structure is not so regular as memories. A solution to cope with the soft error is a soft-error hardened latch shown in Fig. 1.8 [17]. The latch has three nodes for storing data, DH, PDH, and NDH. The latter two are redundant nodes. Even if data in one of the nodes is lost by soft error, it can be recovered by using the data in other two nodes. This is a kind of ECC technique. A solution to cope with the timing error is to add another latch for capturing a delayed output of the combinatorial circuit [18–20], as shown

Fig. 1.8 Soft-error hardened latch. Reproduced from [17] with permission; © 2010 IEEE

in Fig. 1.9a. The main data stream is the path from logic stage 1 to logic stage 2 through the main flip-flop. The shadow latch is provided for capturing the output D of logic stage 1. Since the latch captures D after the main flip-flop, a timing error is detected by comparing the outputs of the main flip-flop and the shadow latch, Q and  $Q_{\text{shadow}}$ . Figure 1.9b shows the operating waveforms. During cycle 1, the data input  $D_in$  arrives before the rising edge of the clock CLK and both the main flip-flop and the shadow latch can capture the correct data. During cycle 2, however,  $D_in$  arrives after the rising edge of CLK and the main flip-flop cannot capture it. On the other hand, since the shadow latch is "through" state when CLK is at high level, its output  $Q_{\text{shadow}}$  alters as soon as the arrival of  $D_in$ . Since the outputs Q and  $Q_{\text{shadow}}$  do not match, the error signal is asserted. The content of the shadow latch is transferred to the main flip-flop during the next cycle and Q is corrected. Thus, correct operations can be resumed. This is a kind of ECC technique using duplicate circuits.

#### **1.3 Margin Errors and Repair Techniques**

The margin error of nanoscale LSIs results from reduced timing and voltage margins. It is closely related to operating voltage  $V_{\rm DD}$ , variations of process, voltage, and temperature (i.e., PVT variations), and the speed target. Operating voltage  $V_{\rm DD}$  must be higher than the sum of the minimum operating voltage  $V_{\rm DD}$  ( $V_{\rm min}$ ) determined by intrinsic  $V_{\rm t}$ -variation ( $\Delta V_{\rm t}$ ) of MOSFETs, other PVT variations, and an additional voltage  $\Delta V_{\tau}$  necessary to meet the speed target. Here, other PVT variations include the power supply droop and noise  $\Delta V_{\rm ps}$  that depends on power supply integrity, and

Fig. 1.9 Principle of timing-error correction of logic circuit: (a) circuit diagram and (b) timing diagrams. Reproduced from [18] with permission;  $\bigcirc$  2010 IEEE

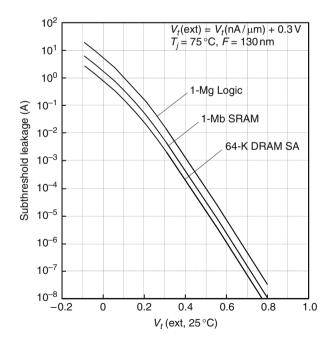

a necessary voltage  $\Delta V_{\text{ext}}$  to offset the effect imposed mainly by extrinsic  $V_{\text{t}}$ -variation of MOSFETs. The larger the difference between  $V_{\text{DD}}$  and the sum, the wider the margins. Since  $\Delta V_{\tau}$  cannot be specified here, reducing  $V_{\min}$ ,  $\Delta V_{\text{ps}}$ , and  $\Delta V_{\text{ext}}$  as much as possible is essential to widen the margins under a given  $V_{\text{DD}}$ . In particular, reducing  $V_{\min}$  is the key because  $V_{\min}$  rapidly increases with device scaling due to the ever-increasing  $\Delta V_{\text{t}}$ , so it eventually dominates  $V_{\text{DD}}$  (see Fig. 5.1). Even so,  $\Delta V_{\text{ps}}$  and  $\Delta V_{\text{ext}}$  must also be reduced because they start to govern the margins when  $V_{\min}$  dominates  $V_{\text{DD}}$ .  $\Delta V_{\text{ps}}$  is reduced with small cores and chips, new architectures such as multicore MPUs, and the compact 3-D integration of small chips with high density through silicon vias (TSVs). A drastic reduction in the memory array area is also vital to further reduce  $\Delta V_{\text{ps}}$  since the array dominates the core or chip. They ensure excellent power supply integrity and low noise in signal lines throughout the subsystem.

In the following, the  $V_{\min}$  issue is mainly discussed because it is closely related to the timing and voltage margin error. Then, the interdie speed variation issue caused by  $\Delta V_{ext}$  is briefly discussed.

#### **1.3.1** Device and Process Variations

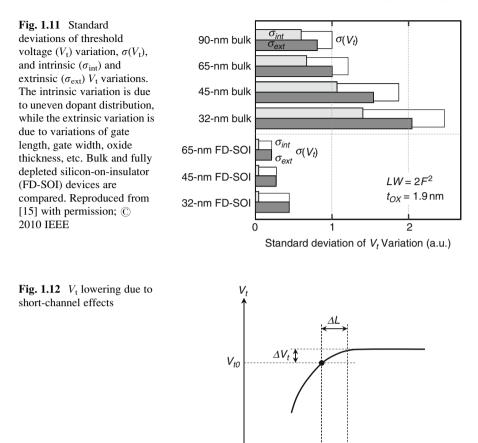

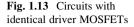

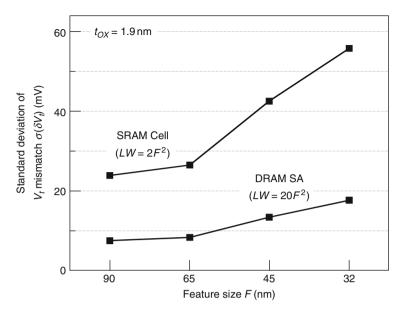

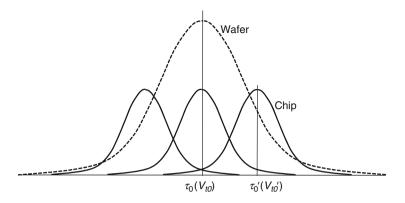

There are some process and device parameter variations [21] (Figs. 1.10 and 1.11) as sources of margin errors, which are prominent in the nanoscale era. The  $V_{t}$ -variation in a chip is dominated by random dopant fluctuations (RDFs) in the number and location of dopant atoms in the channel region of MOSFETs. It is called the local  $V_{t}$ -variation due to the chip-level variation. The local  $V_t$ -variation narrows the timing and voltage margin of circuits in a chip, and increases  $V_t$ -mismatch between a pair of MOSFETs in differential circuits such as sense amplifiers and latch circuits. On the other hand, even in the absence of RDF, there are other sources of the variations, that is, variations of the channel length (L) and its edge roughness, gate-oxide thickness, and implant uniformities of MOSFETs. They are called global or systematic variations because they are the wafer-level variations. Of the global variations, the short-channel effect (SCE) is a major concern. It presents the  $V_t$  lowering (Fig. 1.12), in which  $V_t$  decreases as the channel length L decreases, and thus giving a significant impact on the speed variation. For example, a MOSFET is slowest when having the longest L and thus the highest  $V_t$ , while fastest when having the shortest L and thus the lowest  $V_t$ . This increases speed variations between chips (i.e., causing interdie speed variations), and any chip that does not meet speed specifications is rejected as a faulty chip.

#### **1.3.2** Timing and Voltage Margin Errors

The timing and voltage margins can comprehensively be explained on the assumption that a chip comprises many identical circuit sets. Then, characteristics of the chip

| <ul> <li>Highly random effects</li> </ul> |

|-------------------------------------------|

| Random dopant fluctuation (RDF)           |

| Line-edge roughness                       |

| Local oxide thickness variations          |

| Interface charge nonuniformities          |

|                                           |

•Patterning proximity effects Optical proximity correction (OPC)

Proximity effects associated with stress, polish, and anneals

Overlayers, STI-induced, RTA-generated •Device-related Channel length Pocket implants poly grains Oxide thickness

•Design-related Hot spots, Droop

Fig. 1.10 Variation components in nanoscale LSIs [21]

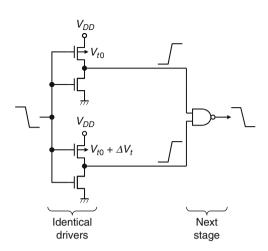

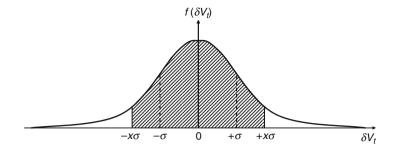

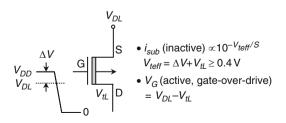

are explained by those of the circuit. Figure 1.13 illustrates a simple model of timing skew, where two identical circuits each composed of MOSFETs drive identical loads connected to the next stage. When the statistical variations in  $V_t$  in a chip are not negligible any more, the two MOSFETs in a certain set in the chip can statistically have two different  $V_t$ s as the difference of  $\Delta V_t$ . Here, the discharging or charging speed  $\tau(V_t)$  of a nanoscale MOSFET having a  $V_t$  is expressed as follows. The drain current of the conventional MOSFET is proportional to  $(V_{DD} - V_t)^{\eta}$ . The speed  $\tau(V_t)$  is thus given by the charge  $(\propto V_{DD})$  at the output divided by the drain current as

0

$$\tau(V_{\rm t}) \propto \frac{V_{\rm DD}}{W(V_{\rm DD} - V_{\rm t})^{\eta}},\tag{1.1}$$

L<sub>0</sub>

where W is the channel width of MOSFET, and the value of  $\eta$  varies between 2 and 1, depending on the MOSFET operation either in saturation or linear region during switching [22]. The value  $\eta$  becomes less than 2 for the saturation drain current of

short-channel MOSFET under velocity saturation conditions. Since the value  $\eta$  was 1.5 for 0.5-µm MOSFETs and 1.25 for 65-nm MOSFETs, it is assumed to be 1.2 for nanoscale MOSFETs. In any event, the two MOSFETs can have different speeds, causing a timing difference  $\Delta \tau$  between the two inputs of the next stage. If the average  $V_t$  is equal to the lowest necessary average  $V_t$  ( $V_{t0}$ ) that is determined by leakage specifications (see Fig. 5.5), the timing difference is given as

$$\Delta \tau = \frac{\tau (V_{t0} + \Delta V_t)}{\tau (V_{t0})} = \left(1 - \frac{\Delta V_t}{V_{DD} - V_{t0}}\right)^{-1.2}.$$

(1.2)

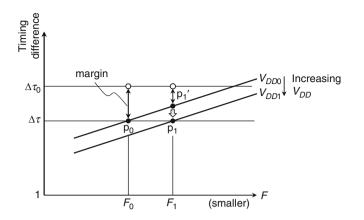

If the tolerable maximum  $\Delta \tau_0$  is defined as the  $\Delta \tau$  necessary for reliable timing designs, the timing margin in the fixed device generation  $(F_0)$  is given as  $\Delta \tau_0 - \Delta \tau$  (Fig. 1.14). Here,  $\Delta \tau_0$  is almost constant, which is determined by the design targets and circuit configurations, as discussed in Chap. 5. The margin narrows at each successive device generation since  $\Delta \tau$  increases as a result of increasing  $\Delta V_t$  (see a line  $p_0p'_1$  in the figure). Errors occur whenever  $\Delta \tau$  exceeds  $\Delta \tau_0$ . To maintain the margin to the same,  $\Delta \tau$  must be reduced to point  $p_1$  with increasing  $(V_{DD} - V_{t0})$  at each generation, so increased  $\Delta V_t$  is offset by increasing  $(V_{DD} - V_{t0})$  (see a line  $p_0p_1$ ). Since  $V_{t0}$  is usually constant to maintain the subthreshold leakage current to the same, increase in  $V_{DD}$  is eventually the key to maintain the margin in the subsequent generations.

As for the voltage margin, it is closely related to  $\Delta \tau_0$ . If the minimum operating (functional)  $V_{\text{DD}}$  (i.e.,  $V_{\text{min}}$ ) is defined as the  $V_{\text{DD}}$  necessary for  $\Delta \tau_0$ , it is given by solving (1.2) for  $V_{\text{DD}}$  as

$$V_{\min} = V_{t0} + (1+\gamma)\Delta V_t, \quad \gamma = 1/(\Delta \tau_0^{-1/1.2} - 1).$$

(1.3)

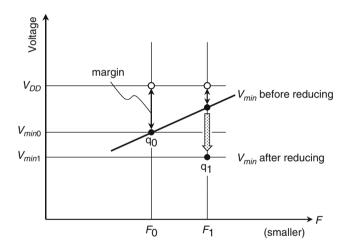

Obviously,  $V_{\min}$  increases with device scaling due to increased  $\Delta V_t$  for a given  $\Delta \tau_0$ , as shown in Fig. 1.15 and expected from Fig. 1.14. The voltage margin at a

Fig. 1.14 Timing margin vs. device generation

Fig. 1.15  $V_{\min}$  vs. device generation

fixed  $V_{\rm DD}$ , given as  $V_{\rm DD} - V_{\rm min}$ , thus narrows at each successive device generation. Voltage margin errors occur whenever  $V_{\rm min}$  exceeds  $V_{\rm DD}$ . To maintain the margin to the same, another way different from increasing  $V_{\rm DD}$  is necessary, which is to reduce  $V_{\rm min}$  (point  $q_1$  in the figure). Hence, reducing  $\Delta V_{\rm t}$  is strongly needed. This also contributes to widening the timing margin.

#### 1.3.3 Reductions of Margin Errors

Repair techniques to drastically reduce margin errors are required. Using the redundancy and/or ECC techniques are effective for memories. In fact, they

have considerably reduced the errors of SRAMs inherently having a larger  $V_t$ -variation. Even so, they cannot manage to reduce ever-more errors caused by the ever-increasing  $V_t$ -variation with device scaling. In addition, the techniques are ineffective for logic gates, although a few different ways have been proposed, as discussed previously. Hence, other innovative device and circuit techniques are strongly needed. Useful techniques to reduce  $V_t$ -variations and thus  $V_{min}$  are summarized as follows. The details are described in Chap. 5.

Use of Largest MOSFET Possible: It is especially effective to reduce the  $V_t$ -variation of MOSFETs in SRAM cells having the narrowest margin in a chip, as described in Chap. 5 (see Fig. 5.31b).

*Dual-V*<sub>t0</sub> *and Dual-V*<sub>DD</sub> *Circuits*: Using low- $V_{t0}$  circuits as much as possible in a chip widen the margins because low- $V_{t0}$  MOSFETs reduce  $V_t$ -variations, as explained in Chap. 5. The resultant leakage path, however, must be cut with the help of high- $V_{t0}$  MOSFETs, and thus high  $V_{DD}$  to maintain a high speed. This inevitably necessitates dual- $V_{t0}$  and dual- $V_{DD}$  circuits. Instantaneously activated low- $V_{t0}$  circuits backed up by high- $V_{t0}$  circuits also reduce the variations. Increased leakage is reduced because the leakage flows only during a short period, while the output level is held in the back-up circuits without leakage, as seen in DRAM sense amplifier (see Fig. 5.40).

*New MOSFETs*: Advanced MOSFETs to reduce  $V_t$ -variation are needed. Good examples are using conventional MOSFETs with thinner  $t_{ox}$ , a high-*k* metal gate for even thinner  $t_{ox}$ , and fully depleted (FD) silicon-on-insulator (SOI) structures, such as planar ultrathin buried oxide (BOX) MOSFETs and FinFETs, for ultralow dose channel.

#### 1.4 Speed-Relevant Errors and Repair Techniques

Two kinds of errors are more prominent with voltage and device scaling. The first comes from an excessively slow speed of an average chip. If  $V_{\min}$  is reduced sufficiently, the resultant wide voltage margin enables  $V_{DD}$  to be reduced, giving a benefit of low-power dissipation. This reduction, however, is strictly limited by this kind of errors. If the resultant speed of the average chip is too slow to meet the requirement, many chips result in faults even if they correctly operate. This is due to reduced gate-over-drive of MOSFET caused by reducing  $V_{DD}$ . There are two ways to solve the problem. One is to reduce  $V_{t0}$ , even if it calls for leakage reduction circuits [7]. The other is to enlarge the channel width W to offset the degraded gate-over-drive. The second comes from the interdie speed variation. Due to an excessively wide speed variation of chips, some of the chips result in faults. Compensation for the variations with adaptive controls of internal power supply voltages is indispensable, as described in Chap. 6.

#### References

- T. C. May and M. H. Woods, "Alpha-particle-induced soft errors in dynamic memories," IEEE Trans. Electron Devices, vol. ED-26, pp. 2–9, Jan. 1979.

- K. Takeuchi, K. Shimohigashi, E. Takeda, E. Yamasaki, T. Toyabe and K. Itoh, "Alphaparticle-induced charge collection measurements for megabit DRAM cells," IEEE Trans. Electron Devices, vol. 36, pp. 1644–1650, Sep. 1989.

- J. F. Ziegler, H. W. Curtis, H. P. Muhlfeld, C. J. Montrose, B. Chin, M. Nicewicz, C. A. Russell, W. Y. Wang, L. B. Freeman, P. Hosier, L. E. LaFave, J. L. Walsh, J. M. Orro, G. J. Unger, J. M. Ross, T. J. O'Gorman, B. Messina, T. D. Sullivan, A. J. Sykes, H. Yourke, T. A. Enger, V. Tolat, T. S. Scott, A. H. Taber, R. J. Sussman, W. A. Klein and C. W. Wahaus, "IBM experiments in soft fails in computer electronics (1978–1994)," IBM J. Res. Dev., vol. 40, pp. 3–18, Jan. 1996.

- K. Osada, K. Yamaguchi, Y. Saitoh and T. Kawahara, "SRAM immunity to cosmic-rayinduced multierrors based on analysis of an induced parasitic bipolar effect," IEEE J. Solid-State Circuits, vol. 39, pp. 827–833, May 2004.

- 5. E. Tammaru and J. B. Angell, "Redundancy for LSI yield enhancement," IEEE J. Solid-State Circuits, vol. SC-2, pp. 172–182, Dec. 1967.

- A. Chen, "Redundancy in LSI memory array," IEEE J. Solid-State Circuits, vol. SC-4, pp. 291–293, Oct. 1969.

- 7. K. Itoh, M. Horiguchi, and H. Tanaka, *Ultra-low voltage nano-scale memories*, Springer, New York, 2007.

- R. P. Cenker, D. G. Clemons, W. R. Huber, J. B. Petrizzi, F. J. Procyk and G. M. Trout, "A fault-tolerant 64K dynamic RAM," ISSCC Dig. Tech. Papers, Feb. 1979, pp. 150–151.

- R. R. DeSimone, N. M. Donofrio, B. L. Flur, R. H. Kruggel and H. H. Leung, "FET RAMs," ISSCC Dig. Tech. Papers, Feb. 1979, pp. 154–155.

- T. Mano, J. Yamada, J. Inoue and S. Nakajima, "Circuit techniques for a VLSI memory," IEEE J. Solid-State Circuits, vol. SC-18, pp. 463–470, Oct. 1983.

- H. L. Kalter, C. H. Stapper, J. E. Barth Jr., J. DiLorenzo, C. E. Drake, J. A. Fifield, G. A. Kelley Jr., S. C. Lewis, W. B. van der Hoeven and J. A. Yankosky, "A 50-ns 16-Mb DRAM with a 10-ns data rate and on-chip ECC," IEEE J. Solid-State Circuits, vol. 25, pp. 1118–1128, Oct. 1990.

- K. Arimoto, K. Fujishima, Y. Matsuda, M. Tsukude, T. Oishi, W. Wakamiya, S. Satoh, M. Yamada and T. Nakano, "A 60-ns 3.3-V-only 16-Mbit DRAM with multipurpose register," IEEE J. Solid-State Circuits, vol. 24, pp. 1184–1190, Oct. 1989.

- 13. R. Naseer and J. Draper, "Parallel double error correcting code design to mitigate multi-bit upsets in SRAMs," Proc. ESSCIRC, Sep. 2008, pp. 222–225.

- M. J. M. Pelgrom, A. C. J. Duinmaijer and A. P. G. Welbers, "Matching properties of MOS transistors," IEEE J. Solid-State Circuits, vol. 24, pp. 1433–1440, Oct. 1989.

- M. Yamaoka, K. Osada, R. Tsuchiya, M. Horiuchi, S. Kimura and T. Kawahara, "Low power SRAM menu for SOC application using yin-yang-feedback memory cell technology," Symp. VLSI Circuits Dig. Tech. Papers, June 2004, pp. 288–291.

- Y. Tosaka, S. Satoh, T. Itakura, H. Ehara, T. Ueda, G. A. Woffinden and S. A. Wender, "Measurement and analysis of neutron-induced soft errors in sub-half-micron CMOS circuits," IEEE Trans. Electron Devices, vol. 45, pp. 1453–1458, July 1998.

- 17. Y. Komatsu, Y. Arima, T. Fujimoto, T. Yamashita and K. Ishibashi, "A soft-error hardened latch scheme for SoC in a 90nm technology and beyond," Proc. CICC, Oct. 2004, pp. 329–332.

- S. Das, D. Roberts, S. Lee, S. Pant, D. Blaauw, T. Austin, K. Flautner and T. Mudge, "A selftuning DVS processor using delay-error detection and correction," IEEE J. Solid-State Circuits, vol. 41, pp. 792–804, Apr. 2006.

- J. Tschanz, K. Bowman, S.-L. Lu, P. Aseron, M. Khellah, A. Raychowdhury, B. Geuskens, C. Tokunaga, C. Wilkerson, T. Karnik and V. De, "A 45nm resilient and adaptive

microprocessor core for dynamic variation tolerance," ISSCC Dig. Tech. Papers, Feb. 2010, pp. 282–283.

- 20. D. Bull, S. Das, K. Shivshankar, G. Dasika, K. Flautner and D. Blaauw, "A power-efficient 32b ARM ISA processor using timing-error detection and correction for transient-error tolerance and adaptation to PVT variation," ISSCC Dig. Tech. Papers, Feb. 2010, pp. 284-285.

- 21. Kelin J. Kuhn, "Reducing variation in advanced logic technologies: approaches to process and design for manufacturability of nanoscale CMOS," IEDM Proc., pp. 471–474, Dec. 2007.

22. Shih-Wei Sun and Paul G. Y. Tsui, "Limitation of CMOS supply-voltage scaling by MOSFET

- threshold-voltage variation," IEEE J. Solid-State Circuits, vol. 30, pp. 947-949, Aug. 1995.

# Chapter 2 Redundancy

#### 2.1 Introduction

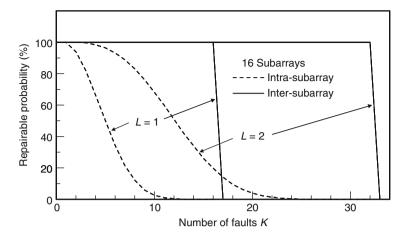

For designing redundancy circuit, the estimation of the advantages and disadvantages is indispensable. The introduction of redundancy in a memory chip results in yield improvement and fabrication-cost reduction. However, it also causes the following penalties. First, spare memory cells to replace faulty cells, programmable devices to memorize faulty addresses, and control circuitry to increase chip size. Second, the time required for the judgment whether the input address is faulty or not is added to the access time. Third, special process steps to fabricate the programmable devices and test time to store faulty addresses into the devices are required. Therefore, the design of redundancy circuit requires a trade-off between yield improvement and these penalties. The estimation of yield improvement requires a fault-distribution model. There are two representative models, Poisson distribution model and negative-binomial model, which are often used for the yield analysis of memory LSIs. The "replacement" of normal memory elements by spare elements requires checking whether the accessed address includes faulty elements, and if yes, inhibiting the faulty element from being activated and activating a spare element instead. These procedures should be realized with as small penalty as possible. One of the major issues for the replacement is memory-array division. Memory arrays are often divided into subarrays for the sake of access-time reduction, power reduction, and signal/noise ratio enhancement. There are two choices for memories with array division: (1) a faulty element in a subarray is replaced only by a spare element in the same subarray (intrasubarray replacement) and (2) a faulty element in a subarray may be replaced by a spare element in another subarray (intersubarray replacement). The former has smaller access penalty, while the latter realizes higher replacement efficiency. It is also possible that a subarray is replaced by a spare subarray. The devices for memorizing faulty addresses and test for finding out an effective replacement are also important issues for redundancy.

The fault distribution models are presented in Sect. 2.2. The yield improvement analysis using the models is described in Sect. 2.3. Section 2.4 describes the circuit techniques for realizing the replacement. The intrasubarray replacement, intersubarray replacement, and subarray replacement are described in Sects. 2.5, 2.6,

and 2.7, respectively. The programmable devices for storing faulty addresses are described in Sect. 2.8. Finally, testing techniques for redundancy are explained in Sect. 2.9.

#### 2.2 Models of Fault Distribution

#### 2.2.1 Poisson Distribution Model

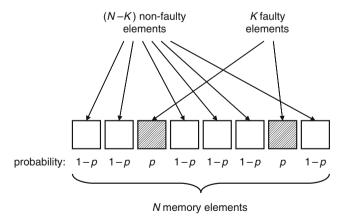

Let us consider a memory chip with N "elements" (Fig. 2.1). Here, an element may be a memory cell, a row of memory cells, a column of memory cells, a subarray, and so on. If faults are randomly distributed in the chip, the probability of an element being faulty, p, is independent of the probability of other elements being faulty or nonfaulty. Therefore, the probability that k elements are faulty and (N - K) elements are not faulty is expressed as the product of their probabilities,  $p^{K}(1 - p)^{N-K}$ . Since the number of cases of selecting K faulty elements out of Nelements is expressed by

$$\binom{N}{K} = {}_{N}C_{K} = \frac{N!}{(N-K)!K!} = \frac{N(N-1)\cdots(N-K+1)}{K!}, \quad (2.1)$$

the probability of existing K faulty elements in the chip is expressed as

$$P(K) = \binom{N}{K} p^{K} (1-p)^{N-K}.$$

(2.2)

Fig. 2.1 Probability of existing K faulty elements out of N elements when faulty probability of an element is p

#### 2.2 Models of Fault Distribution

This is called binomial distribution and the coefficient  $\binom{N}{K}$  is called binomial coefficient. Usually, N is very large and p is very small. When  $N \to \infty$ , keeping  $\lambda = Np$  constant, (2.2) becomes

$$P(K) = \frac{N(N-1)\cdots(N-K+1)}{K!} \cdot p^{K} \cdot (1-p)^{N-K}$$

=  $1 \cdot \left(1 - \frac{1}{N}\right) \cdots \left(1 - \frac{K+1}{N}\right) \cdot \frac{\lambda^{K}}{K!} \cdot \left(1 - \frac{\lambda}{N}\right)^{N} \left(1 - \frac{\lambda}{N}\right)^{-K}$  (2.3)

$\rightarrow \frac{\lambda^{K}}{K!} \left(1 - \frac{\lambda}{N}\right)^{N} = \frac{\lambda^{K} \exp(-\lambda)}{K!} \quad (N \to \infty).$

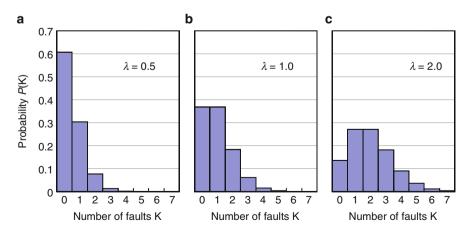

This is called *Poisson distribution*. Figure 2.2 shows examples of the distribution. The probability P(K) monotonously decreases with K for  $\lambda < 1$ , and has a peak around  $K \sim \lambda$  for  $\lambda > 1$ . Poisson distribution is characterized by only one parameter  $\lambda$ . The average  $\overline{K}$  and standard deviation  $\sigma(K)$  of the number of faulty elements are expressed as

$$\bar{K} = \sum_{K=0}^{\infty} KP(K) = \exp(-\lambda) \sum_{K=1}^{\infty} \frac{\lambda^K}{(K-1)!} = \lambda, \qquad (2.4)$$

$$\sigma(K) = \sqrt{\sum_{K=0}^{\infty} K^2 P(K) - \bar{K}^2} = \sqrt{\exp(-\lambda) \sum_{K=1}^{\infty} \frac{K \lambda^K}{(K-1)!} - \lambda^2}$$

$$= \sqrt{\exp(-\lambda) \left\{ \sum_{K=2}^{\infty} \frac{\lambda^K}{(K-2)!} + \sum_{K=1}^{\infty} \frac{\lambda^K}{(K-1)!} \right\} - \lambda^2}$$

$$= \sqrt{\exp(-\lambda) (\lambda^2 \exp \lambda + \lambda \exp \lambda) - \lambda^2} = \sqrt{\lambda}.$$

(2.5)

**Fig. 2.2** Examples of Poisson distribution: (a)  $\lambda = 0.5$ , (b)  $\lambda = 1.0$ , and (c)  $\lambda = 2.0$

Thus, the parameter  $\lambda$  is equal to the average number of faults and is expressed as:

$$\lambda = AD, \tag{2.6}$$

where A is the chip area and D is the fault density. The probability of a chip having no faulty elements (raw yield, i.e., yield without redundancy) is expressed as

$$P(0) = \exp(-\lambda) = \exp(-AD). \tag{2.7}$$

Poisson distribution model is often used for yield analysis because of its mathematical simplicity [1–5]. It is useful for rough yield estimation or the comparison of redundancy techniques. More precise yield estimation, however, requires a model that takes "fault clustering" into account described below.

#### 2.2.2 Negative-Binomial Distribution Model

It has been reported that actual faults are not randomly distributed but clustered and that the number of faulty elements does not match the Poisson distribution model [6, 7]. In this case, the parameter  $\lambda$  is no longer constant but does distribute. Compound Poisson distribution model

$$P(K) = \int_0^\infty \frac{\lambda^K \exp(-\lambda)}{K!} f(\lambda) d\lambda$$

(2.8)

was proposed [6] as a distribution model for nonconstant  $\lambda$ . The first factor in the integral is Poisson distribution and the second factor  $f(\lambda)$  is a function called "compounder" representing the distribution of  $\lambda$ . The average  $\overline{K}$  and standard deviation  $\sigma(K)$  of the number of faulty elements are given by the following equations:

$$\bar{K} = \sum_{K=0}^{\infty} KP(K) = \int_{0}^{\infty} \left\{ \exp(-\lambda)f(\lambda) \sum_{K=1}^{\infty} \frac{\lambda^{K}}{(K-1)!} \right\} d\lambda$$

=

$$\int_{0}^{\infty} \exp(-\lambda)f(\lambda) \cdot \lambda \exp(\lambda)d\lambda = \int_{0}^{\infty} f(\lambda) \cdot \lambda d\lambda = \bar{\lambda},$$

(2.9)

$$\sigma(K) = \sqrt{\sum_{K=0}^{\infty} K^2 P(K) - \bar{K}^2} = \sqrt{\int_0^{\infty} \left\{ \exp(-\lambda) f(\lambda) \sum_{K=1}^{\infty} \frac{\lambda^K \cdot K}{(K-1)!} \right\}} d\lambda - \bar{\lambda}^2$$

$$= \sqrt{\int_0^{\infty} \left[ \exp(-\lambda) f(\lambda) \left\{ \sum_{K=2}^{\infty} \frac{\lambda^K}{(K-2)!} + \sum_{K=1}^{\infty} \frac{\lambda^K}{(K-1)!} \right\} \right]} d\lambda - \bar{\lambda}^2$$

$$= \sqrt{\int_{0}^{\infty} \{\exp(-\lambda)f(\lambda)(\lambda^{2}\exp\lambda + \lambda\exp\lambda)\}} d\lambda - \bar{\lambda}^{2}$$

$$= \sqrt{\int_{0}^{\infty} f(\lambda) \cdot \lambda \, d\lambda} + \int_{0}^{\infty} f(\lambda) \cdot \lambda^{2} \, d\lambda - \bar{\lambda}^{2}$$

$$= \sqrt{\bar{\lambda} + \{\sigma(\lambda)\}^{2}}.$$

(2.10)

The candidates for  $f(\lambda)$  include uniform distribution and triangular distribution. However, Gamma distribution

$$f(\lambda) = \frac{\lambda^{\alpha - 1} \exp(-\lambda/\beta)}{\Gamma(\alpha)\beta^{\alpha}}$$

(2.11)

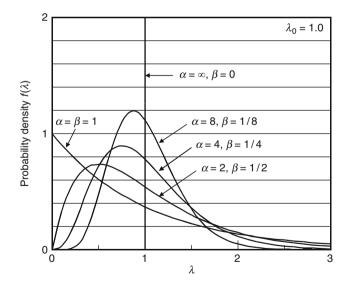

has been shown the most suitable for actual fault distribution<sup>1</sup> [6, 8]. The meanings of the parameters  $\alpha$  and  $\beta$  are as follows:  $\alpha$  corresponds to fault clustering (smaller  $\alpha$ means stronger clustering), and the product  $\alpha\beta$  is equal to the average of  $\lambda$ ,  $\lambda_0$ . The standard deviation of  $\lambda$  is equal to  $\beta\sqrt{\alpha}$ . Figure 2.3 shows examples of (2.11) for various parameters maintaining  $\lambda_0 = \alpha\beta = 1.0$ . When  $\alpha \to \infty$ , the distribution becomes the delta function, corresponding to no  $\lambda$  distribution.

Fig. 2.3 Probability density function of gamma distribution as a compounder (average of  $\lambda = 1.0$ )

$<sup>{}^{1}\</sup>Gamma(\alpha)$  is gamma function defined as  $\Gamma(\alpha) = \int_{0}^{\infty} t^{\alpha-1} \exp(-t) dt$ .  $\Gamma(\alpha) = (\alpha - 1)!$  for integer  $\alpha$ .

Substituting (2.11) and  $\beta = \lambda_0 / \alpha$  into (2.8) results in

$$P(K) = \int_{0}^{\infty} \frac{\lambda^{K} \exp(-\lambda)}{K!} \cdot \frac{\lambda^{\alpha-1} \exp(-\lambda/\beta)}{\Gamma(\alpha)\beta^{\alpha}} d\lambda$$

$$= \frac{1}{K!\Gamma(\alpha)\beta^{\alpha}} \int_{0}^{\infty} \lambda^{K+\alpha-1} \exp\left\{-\left(1+\frac{1}{\beta}\right)\lambda\right\} d\lambda$$

$$= \frac{1}{K!\Gamma(\alpha)\beta^{\alpha}} \left(\frac{\beta}{\beta+1}\right)^{K+\alpha} \int_{0}^{\infty} t^{k+\alpha-1} \exp(-t) dt \qquad (2.12)$$

$$= \frac{\Gamma(K+\alpha)\beta^{K}}{K!\Gamma(\alpha)(\beta+1)^{K+\alpha}}$$

$$= \frac{\alpha(\alpha+1)\cdots(\alpha+K-1)(\lambda_{0}/\alpha)^{K}}{K!(1+\lambda_{0}/\alpha)^{K+\alpha}}.$$

This is called *negative binomial distribution* [9]. The average and standard deviation of the number of faulty elements are calculated from (2.9) and (2.10):

$$\bar{K} = \bar{\lambda} = \lambda_0, \tag{2.13}$$

$$\sigma(K) = \sqrt{\overline{\lambda} + \{\sigma(\lambda)\}^2} = \sqrt{\lambda_0 + \beta^2 \alpha} = \sqrt{\lambda_0 (1 + \lambda_0 / \alpha)}.$$

(2.14)

Comparing (2.14) with (2.5), we can find that the standard deviation of the negative-binomial distribution is larger than that of Poisson distribution by a factor of  $\sqrt{1 + \lambda_0/\alpha}$ . The raw yield is expressed as

$$P(0) = \frac{1}{(1 + \lambda_0/\alpha)^{\alpha}} = \frac{1}{(1 + AD/\alpha)^{\alpha}}.$$

(2.15)

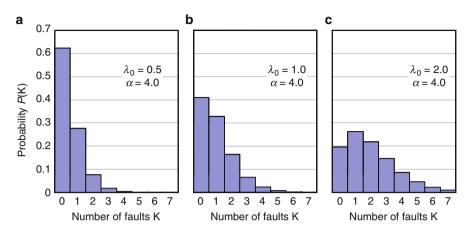

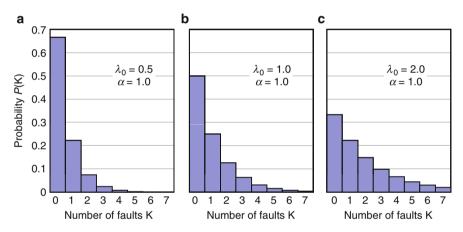

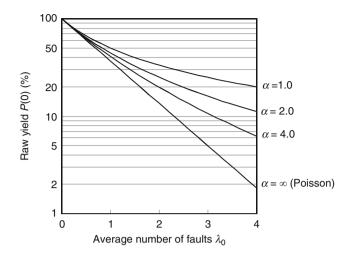

When  $\alpha \to \infty$ , (2.15) becomes identical to (2.7). Figures 2.4 and 2.5 show examples of the distribution with  $\alpha = 4.0$  (weaker fault clustering) and  $\alpha = 1.0$ (stronger fault clustering), respectively. Compared with Fig. 2.2 (corresponding to the case  $\alpha = \infty$ ), the probability for K = 0 and that for large K increase and the probability for medium K decreases as  $\alpha$  decreases. Equations (2.7) and (2.15) are plotted in Fig. 2.6. The raw yield using the Poisson distribution model is expressed by the straight line ( $\alpha = \infty$ ) in semilog scale. The raw yield using the negativebinomial distribution model is expressed by a concave-up line and is greater than that using the Poisson model.

The negative-binomial distribution model is often used for yield estimation of memory LSIs [10–12] because it gives good agreement with actual fault distribution. In order to use this model, however, we must determine two parameters  $\lambda_0$  (average number of faults) and  $\alpha$  (fault clustering factor) from experimental data. In addition, it should be noted that the parameter  $\alpha$  may depend on the kind of the memory element.

Fig. 2.4 Examples of negative binomial distribution with  $\alpha = 4.0$ : (a)  $\lambda_0 = 0.5$ , (b)  $\lambda_0 = 1.0$ , and (c)  $\lambda_0 = 2.0$

Fig. 2.5 Examples of negative binomial distribution with  $\alpha = 1.0$ : (a)  $\lambda_0 = 0.5$ , (b)  $\lambda_0 = 1.0$ , and (c)  $\lambda_0 = 2.0$

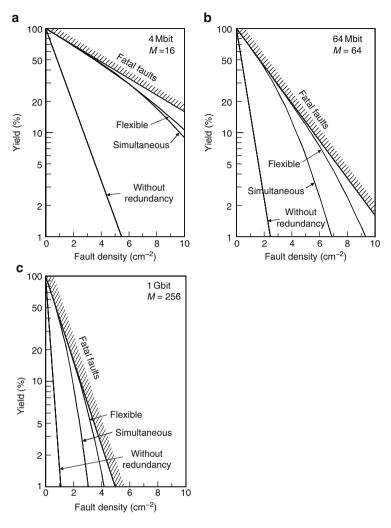

#### 2.3 Yield Improvement Through Redundancy

In this section, yield improvement through redundancy is analyzed using the models described above. We assume the followings for simplicity:

- 1. Faults on spare elements are neglected.

- 2. Fatal faults are neglected. A fatal fault is defined as a fault that makes the entire chip no good. For example, a defect on peripheral circuit of a memory LSI may cause a fatal fault.

Without redundancy, the yield  $Y_0$  is equal to P(0) as shown in Fig. 2.6 because only chips without faulty elements are accepted. If R spare elements

Fig. 2.6 Comparison of raw yield using Poisson and negative-binomial distribution models

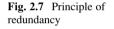

are added in the chip, chips with K faulty elements ( $K \le R$ ) become acceptable by replacing the faulty elements with spares as shown in Fig. 2.7. Therefore, the yield becomes

$$Y = \sum_{K=0}^{R} P(K).$$

(2.16)

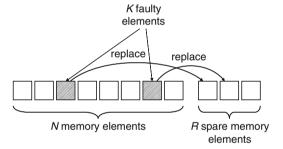

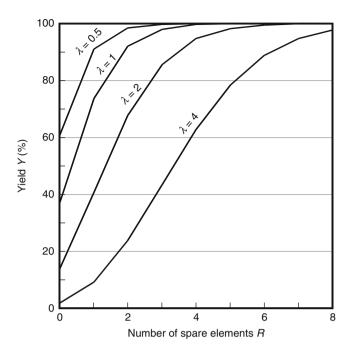

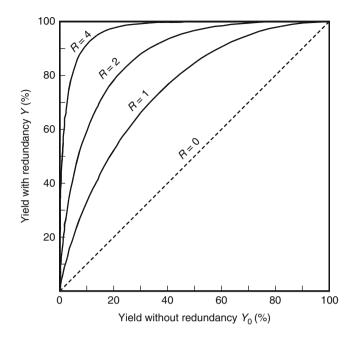

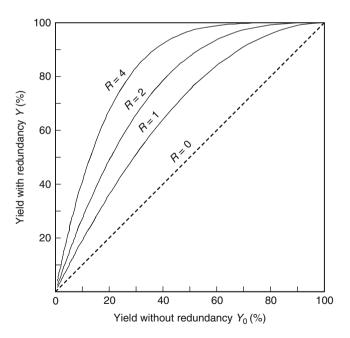

Figures 2.8 and 2.9 show the calculated yield using the Poisson distribution and the negative-binomial distribution models, respectively. The raw yield  $Y_0$  (R = 0) is lower but the yield improvement is larger with Poisson distribution model than with negative-binomial model. This is apparent in Figs. 2.10 and 2.11, where the relationships between yields with and without redundancy are plotted. Thus, it should be noted that using Poisson distribution model tends to underestimate  $Y_0$  and overestimate the yield improvement.

Fig. 2.8 Yield improvement through redundancy using Poisson distribution model

Fig. 2.9 Yield improvement through redundancy using negative-binomial distribution model ( $\alpha = 1.0$ )

Fig. 2.10 Yield improvement through redundancy using Poisson distribution model: number of spare elements as a parameter

Fig. 2.11 Yield improvement through redundancy using negative-binomial distribution model ( $\alpha = 1.0$ ): number of spare elements as a parameter

## 2.4 Replacement Schemes

# 2.4.1 Principle of Replacement

Since redundancy techniques repair memory LSIs by replacing faulty normal elements by spare elements and by hiding the faulty elements from users, the following steps are required.

- 1. Replacement information (which normal element is replaced by which spare element) is stored in on-chip programmable devices in advance.

- 2. When accessed, it is judged whether the demanded address is faulty ("hit") or not ("miss") using the information stored above.

- 3. In case of miss, the normal element is activated and no spare elements are activated.

- 4. In case of hit (a) the normal element is inhibited from being activated and (b) the spare element that replaces the normal element is instead activated.

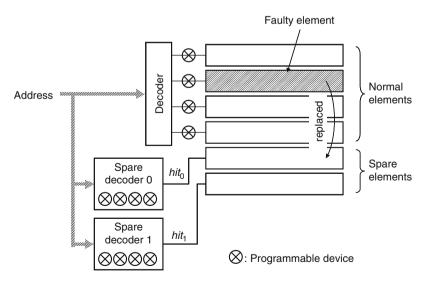

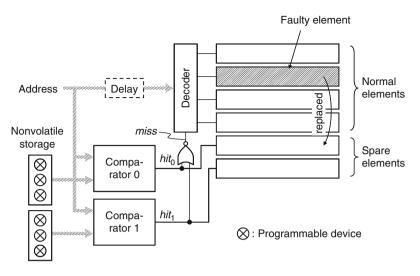

Step 1 requires programmable devices. In addition, they must be nonvolatile to retain the programmed replacement information during power-off. The devices used for this purpose include fuses, antifuses, and nonvolatile memory cells as is described in Sect. 2.8. There are two schemes for storing and reading the replacement information in the storage (steps 1 and 2): decoder programming and address comparison. The former utilizes spare decoders, which is the same as normal decoders except that the address is programmable (Fig. 2.12). The latter utilizes comparators for selecting spare elements (Fig. 2.13). In addition, there are two schemes for disabling the faulty normal element (step 4a): direct disabling and

Fig. 2.12 Replacement using decoder programming and direct disabling schemes

Fig. 2.13 Replacement using address comparison and indirect disabling schemes

indirect disabling. The former cuts off the signal path to the faulty element by blowing a fusible link (Fig. 2.12). The latter utilizes the spare-selection signals  $hit_i$  (Fig. 2.13). The activation of normal element is inhibited if one of the  $hit_i$  is asserted, and is allowed if none of the  $hit_i$  is asserted. Therefore, there are four  $(2 \times 2)$  possible combinations. Figure 2.12 shows a replacing scheme using decoder programming and direct disabling schemes, while Fig. 2.13 shows a scheme using address comparison and indirect disabling schemes. On the other hand, there is a quite different replacing scheme, shifting scheme, as shown in Fig. 2.14. The switches inserted between the decoder and the memory array are controlled by the programmable storage, in which the address of a faulty element is programmed. In case of no faulty elements, each output of the decoder is connected with the corresponding normal element and the spare element is not connected. If there is a faulty normal element, the connections are shifted so that the outputs of the decoder are connected with the spare element and the normal elements except for the faulty one.

#### 2.4.2 Circuit Implementations

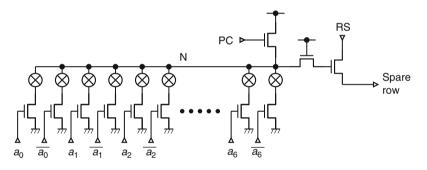

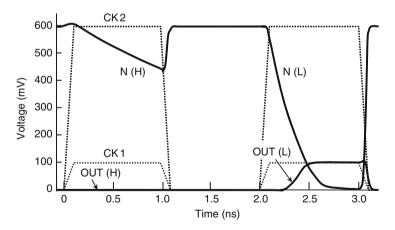

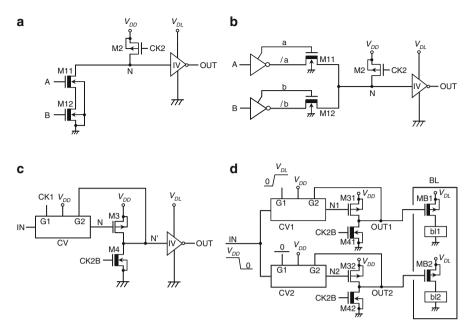

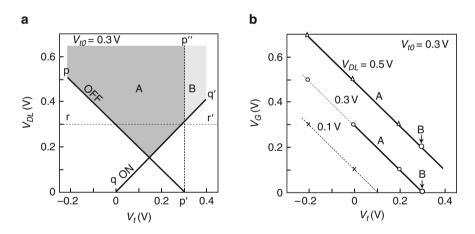

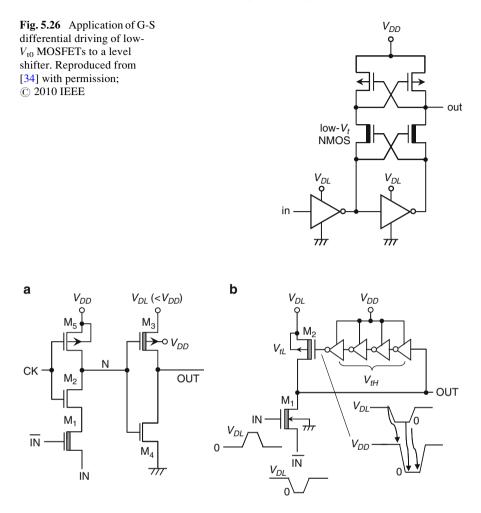

Next, circuit implementations of the replacement schemes are described. Figure 2.15 shows a spare row decoder using the decoder programming scheme [13]. The circuit has two fuses per an address bit, one for true signal  $a_i$  and the other for complement signal  $\bar{a}_i$ . One of the two fuses is blown by laser according to the faulty address. The node N is precharged to high level by signal PC before the input of address signals. If the input address coincides with the programmed address the node N remains high.

Fig. 2.14 Replacement using shifting scheme

Fig. 2.15 Spare row decoder using decoder programming scheme. Reproduced from [13] with permission; © 2010 IEEE

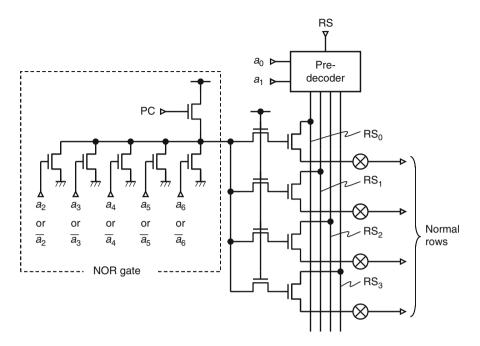

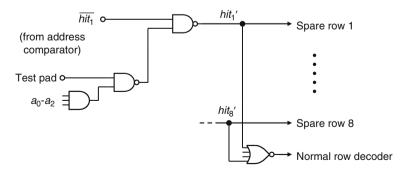

The spare row line is activated when row selection signal RS goes high. If the input address does not coincide with the programmed address, node N goes low and the spare line is not activated. If no faulty address, all the fuses are unblown. Since node N always goes low irrespective of the input address, the spare row line is never activated. Figure 2.16 shows a normal row decoder using the direct disabling scheme [13]. The output of the NOR gate is ANDed with the predecoder output signals  $RS_0$ – $RS_3$  to relax the circuit pitch. A normal row is disconnected to the output of the decoder by blowing the corresponding fuse by laser. Thus, this circuit requires as many fuses as the rows and the pitch of fuses is equal to row pitch. Figure 2.17 shows a row redundancy circuit using the address comparison and indirect disabling schemes [14]. Each address to generate the spare-selection signal *hit<sub>i</sub>*. If *hit<sub>i</sub>* is asserted, the corresponding spare row is activated at the timing

Fig. 2.16 Normal row decoder using direct disabling scheme [13]

Fig. 2.17 Row replacement using address comparison and indirect disabling schemes [14]

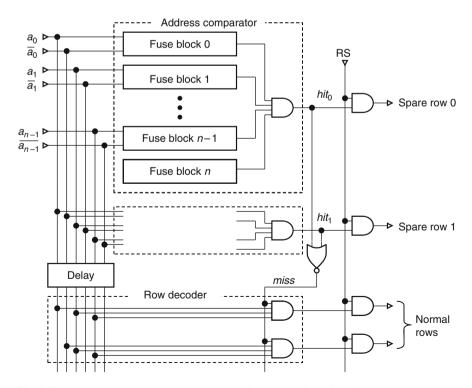

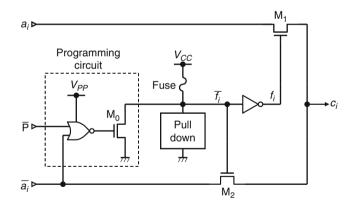

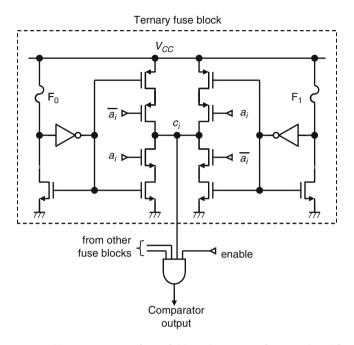

of RS and the row decoder is disabled through the NOR gate. Note that a delay circuit is inserted at the input of the row decoder. Without this delay, the arrival of the address signals at the row decoder precedes the generation of hit<sub>i</sub>, and a normal row may be wrongly activated. Therefore, this circuit has an access time penalty of the delay time. The detail of the fuse block included in the address comparator is shown in Fig. 2.18 [14, 15]. This circuit utilizes an electrically blown fuse. The blowing MOS transistor  $M_0$  is controlled by programming signal  $\bar{P}$ and address signal  $\bar{a}_i$ . If the fuse is blown, the signal  $\bar{f}_i$  is pulled down to low and  $f_i$  is high. Since  $M_1$  is on and  $M_2$  is off, the output signal  $c_i$  is equal to  $a_i$ . On the contrary, if the fuse is unblown,  $c_i$  is equal to  $\bar{a}_i$ . The programming and normal operations of the fuse block are summarized in Table 2.1. Note that  $c_i = 1$  if the address during programming is equal to the address during normal operation and otherwise  $c_i = 0$ . All the outputs of the fuse blocks are ANDed to generate the hit signal and to activate the corresponding spare row line. An extra fuse block is added to indicate whether the address comparator is valid or not. Without blowing the fuse in this extra block, the comparator is invalid and the corresponding spare row line is never activated.

The number of fuses required for each scheme is as follows. The decoder programming scheme require 2nR, while the address comparison requires (n + 1) R (including the fuses for extra blocks), where  $n = \log_2 N$  is the number of address bits, N is the number of normal lines, and R is the number of spare lines. The direct disabling scheme requires  $2^n$  because the number of normal lines is  $N = 2^n$  while the indirect disabling scheme requires none. Therefore, the combination of address

Fig. 2.18 Detail of fuse block [14, 15]

| Progra | mming $(\bar{P} =$ | = 0)    | Normal operation |             |       |             |                |

|--------|--------------------|---------|------------------|-------------|-------|-------------|----------------|

| $a_i$  | $\bar{a}_i$        | Fuse    | $f_i$            | $\bar{f_i}$ | $a_i$ | $\bar{a}_i$ | C <sub>i</sub> |

| 0      | 1                  | Unblown | 0                | 1           | 0     | 1           | 1              |

|        |                    |         |                  |             | 1     | 0           | 0              |

| 1      | 0                  | Blown   | 1                | 0           | 0     | 1           | 0              |

|        |                    |         |                  |             | 1     | 0           | 1              |

Table 2.1

Truth table of fuse block

Fig. 2.19 Column replacement using shifting scheme. Reproduced from [16] with permission; 2010 IEEE

comparison and indirect disabling schemes requires the fewest fuses. Since the size of fuses is not so scaled down according to design rules, the combination is the best choice for high-density memory LSIs with a large number of spare lines, despite the access penalty.

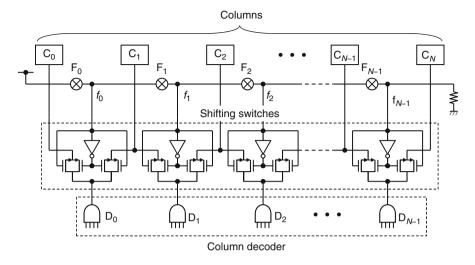

Figure 2.19 shows the shifting scheme applied to column redundancy of a highspeed SRAM [16]. Shifting switches are inserted between the outputs of the column decoder,  $D_0-D_{N-1}$ , and the columns,  $C_0-C_N$ , including a spare column  $C_N$ . The connections are changed by blowing one of the fuses,  $F_0-F_{N-1}$ . If no fuses are blown, all the control signals  $f_0-f_{N-1}$  are at high level. Column  $C_0$  is activated by  $D_0$ ,  $C_1$  is activated by  $D_1$ , and so on. The spare column  $C_N$  is never activated. If, for example, column  $C_1$  is found to be faulty, fuse  $F_1$  is blown. Since  $f_0$  is at high level and  $f_1-f_{N-1}$  are at low level,  $C_0$  is activated by  $D_0$ ,  $C_2$  is activated by  $D_1$ , and  $C_N$  is activated by  $D_{N-1}$ . Thus, the activation of the faulty column  $C_1$  is inhibited. This scheme requires N fuses. However, it features no access-time degradation because all the signal-path lengths, including the spare one are uniform.

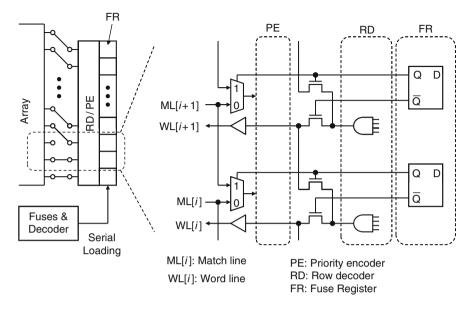

The shifting scheme is suitable for the row redundancy of a content addressable memory (CAM) because a CAM has a priority encoder (PE). If the search data matches the data stored in two or more rows, the PE outputs the address of the row having the highest priority. The order of priority is usually ascending or descending order of row address. If a faulty row is replaced by a spare row with the ordinary replacing scheme, the order of address is not maintained. With the shifting scheme, however, the order of row address is maintained even after shifting [17, 18]. Figure 2.20 shows a CAM with row redundancy using the shifting scheme. The information of faulty address stored in the fuses is decoded and is transferred to the register FR in advance and is used for switching both wordlines and matchlines.

Fig. 2.20 Row replacement of a CAM using shifting scheme. Reproduced from [17] with permission; © 2010 IEEE

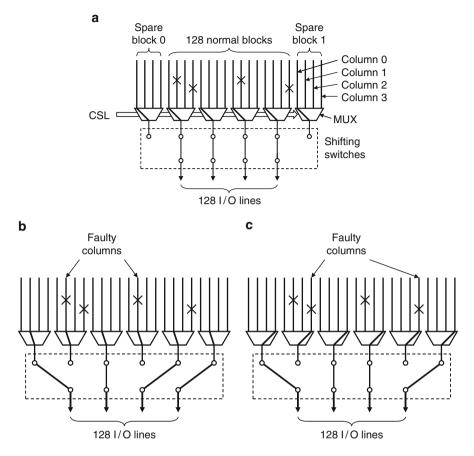

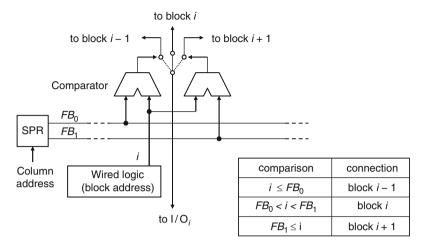

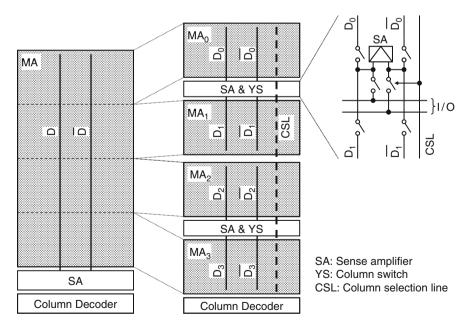

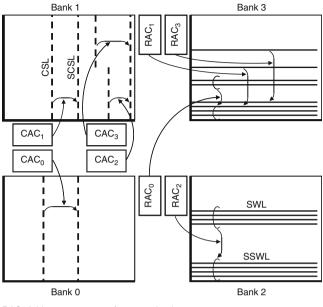

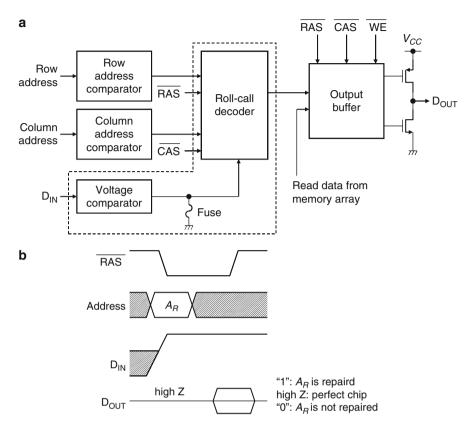

The shifting scheme is also suitable for wide I/O memories. Figure 2.21 shows the shifting scheme applied to a DRAM macro with 128 I/Os [19]. The macro has 128 normal blocks and two spare blocks on both sides. The redundancy scheme applied to this macro features that the connections of switches are variable according to column address (the connections of the switches in Figs. 2.19 and 2.20 are fixed after blowing fuses). A column of each block is selected by multiplexer MUX controlled by column selection lines CSL. When column 0 is selected (Fig. 2.21a), only normal blocks are connected to the I/O lines because column 0 of each block is not faulty. However, when another column is selected (Fig. 2.21b, c), the connections are changed so that the faulty columns are not connected to the I/O lines. The detail of the shifting switch is shown in Fig. 2.22. Faulty block addresses of each column are programmed in the shift point register SPR by blowing fuses. The faulty block addresses of the selected column, FB<sub>0</sub> and FB<sub>1</sub>, are read out and compared with each block address generated by a wired logic circuit. The connection of each switch is determined by the comparison results as shown in the table.

Although the circuit in Fig. 2.19 requires N fuses, the circuit in Fig. 2.20 requires only  $\log_2 N + 1$  because of decoding. The circuit in Fig. 2.21 requires  $2(\log_2 N + 1)$  because there are two spare columns. The number of programmable elements required for replacement schemes is summarized in Table 2.2.

A disadvantage of the shifting scheme is that the number of spares is limited. Since R sets of spares require (R + 1)-terminal shifting switches, a large R causes the complexity of switches and the control circuits. Therefore, R = 1 or 2 is practical.

**Fig. 2.21** Flexible DQ replacement of an embedded RAM using shifting scheme: (a) nonfaulty case, (b) two faulty columns are replaced, and (c) when another address is selected, other two faulty columns are replaced. Reproduced from [19] with permission;  $\bigcirc$  2010 IEEE

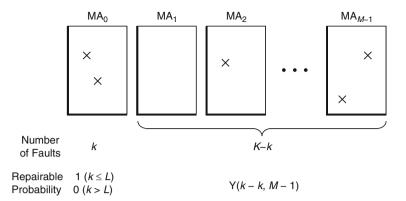

# 2.5 Intrasubarray Replacement

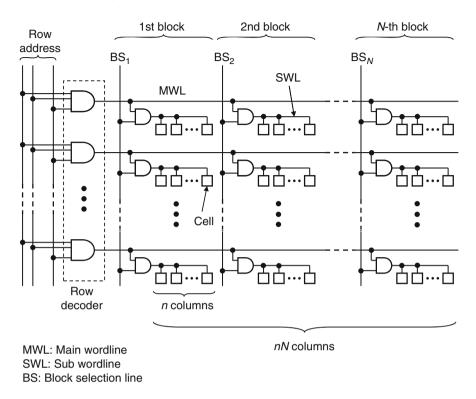

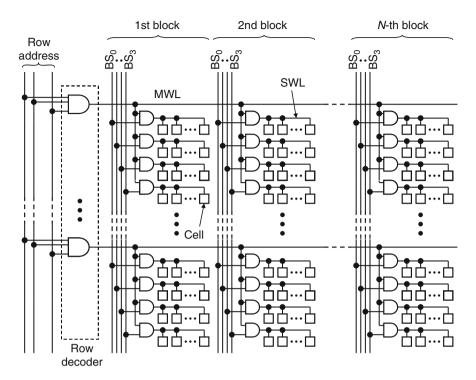

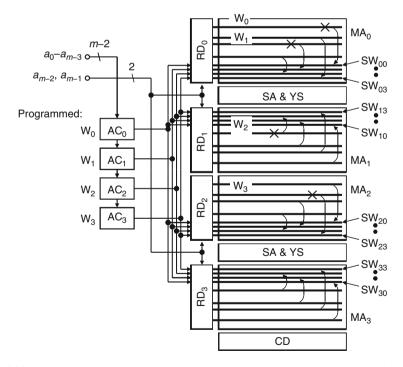

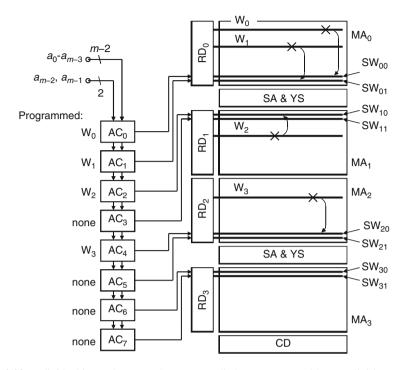

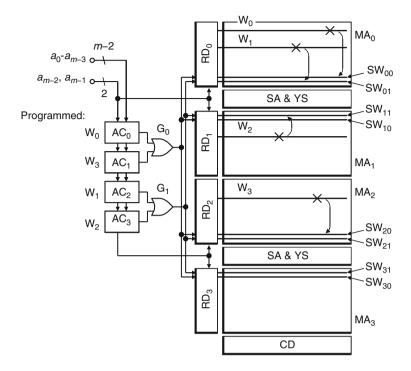

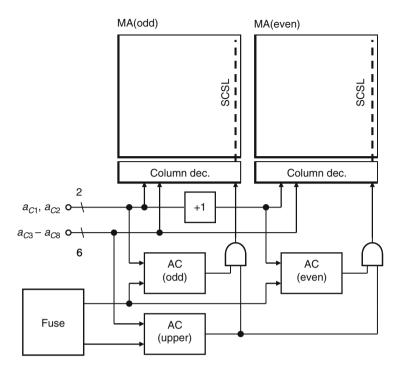

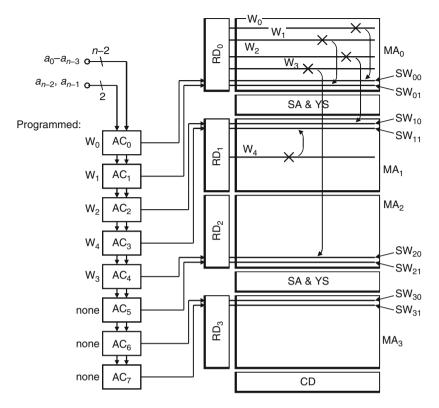

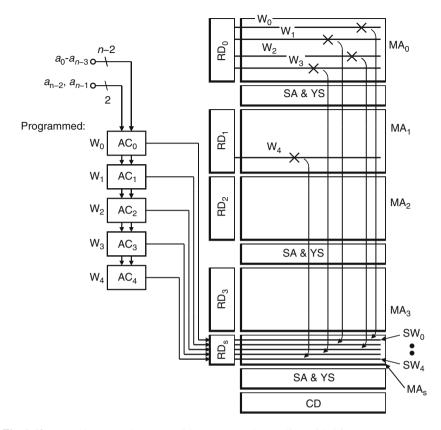

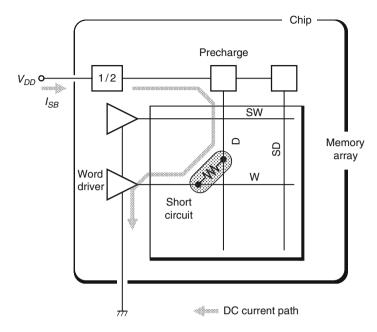

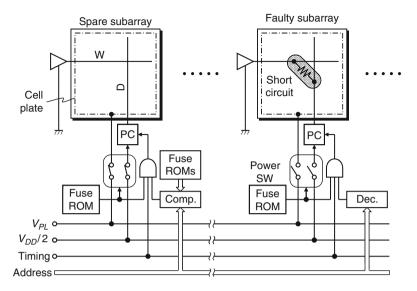

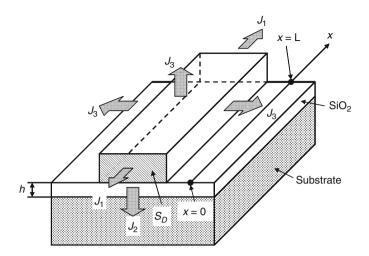

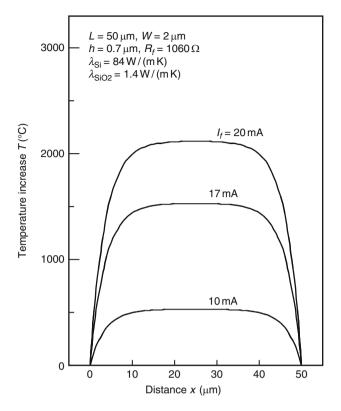

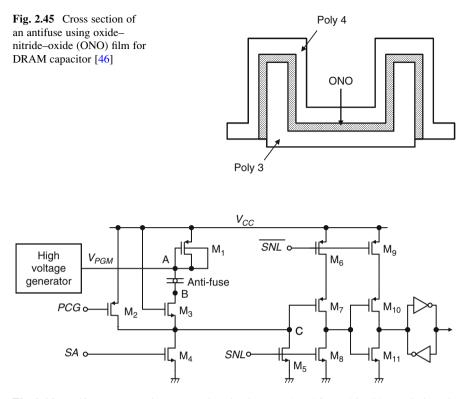

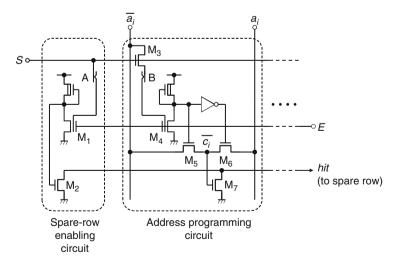

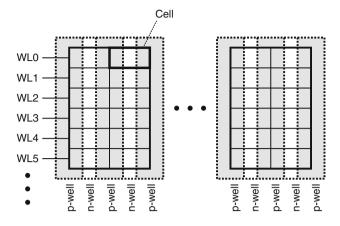

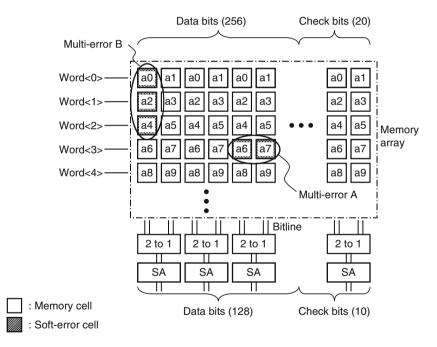

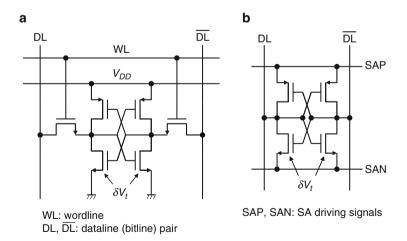

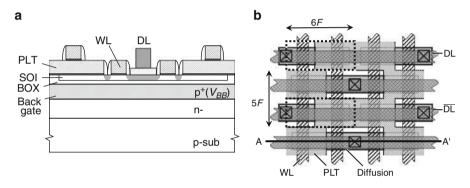

One of the problems for redundancy with the increase in memory capacity is memory-array division. Figure 2.23 shows the trend of memory-array division of DRAMs [20]. The number of subarrays doubled each generation before 64 Mbit. This is mainly due to the dataline (bitline) division shown in Fig. 2.24. The dataline D is divided into  $D_0$ – $D_3$  to reduce the parasitic capacitance for signal/ noise ratio enhancement and charging/discharging current reduction [21–24]. The number of divisions even quadrupled each generation after the introduction of hierarchical wordline structure as shown in Figs. 2.25 and 2.26 [25–27]. Here, a wordline is divided into a plurality of sub wordlines (SWLs), each of which is activated by the AND of a main wordline (MWL) and a block selection line BS.

SPR: Shift point register *FB*<sub>0</sub>, *FB*<sub>1</sub>: Faulty block addresses

| Fig. 2.22 | Detail of shifting switch and its control circuit [19 | 91 |

|-----------|-------------------------------------------------------|----|

|           |                                                       |    |

| Table 2.2 | Num | ber of | programmat | ole e | lements | required | for replacement | nt |

|-----------|-----|--------|------------|-------|---------|----------|-----------------|----|

|-----------|-----|--------|------------|-------|---------|----------|-----------------|----|

| Replacement scheme                       | Number of programmable elements | Figure     |

|------------------------------------------|---------------------------------|------------|

| Decoder programming + direct disabling   | $2R \log_2 N + N$               | 2.15, 2.16 |

| Decoder programming + indirect disabling | $2R \log_2 N$                   | _          |

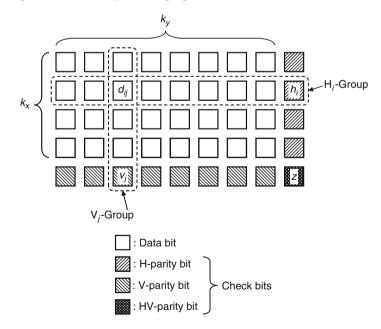

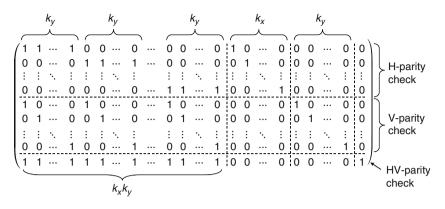

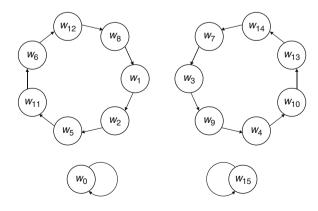

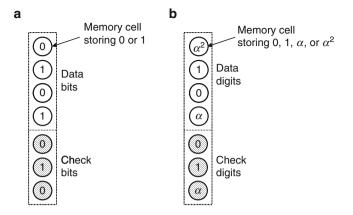

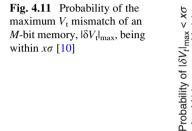

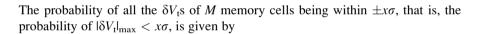

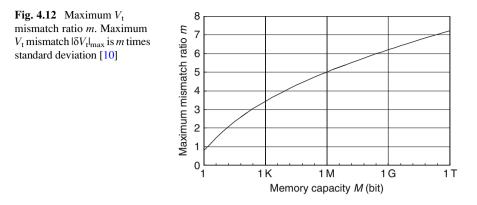

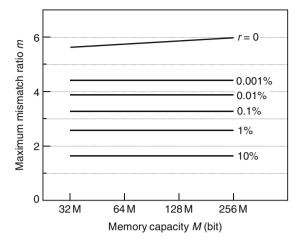

| Address comparison + direct disabling    | $R(\log_2 N + 1) + N$           | _          |