ACSP · Analog Circuits And Signal Processing

Mike Wens Michiel Steyaert

Design and Implementation of Fully-Integrated Inductive DC-DC Converters in Standard CMOS

## Design and Implementation of Fully-Integrated Inductive DC-DC Converters in Standard CMOS

#### ANALOG CIRCUITS AND SIGNAL PROCESSING

Series Editors: Mohammed Ismail. *The Ohio State University* Mohamad Sawan. *École Polytechnique de Montréal*

For other titles published in this series, go to www.springer.com/series/7381

# Design and Implementation of Fully-Integrated Inductive DC-DC Converters in Standard CMOS

Dr. Mike Wens ESAT-MICAS Dept. Elektrotechniek K.U. Leuven Room 91.22, Kasteelpark Arenberg 10 Leuven B-3001 Belgium Mike.Wens@esat.kuleuven.be

Series Editors: Mohammed Ismail 205 Dreese Laboratory Department of Electrical Engineering The Ohio State University 2015 Neil Avenue Columbus, OH 43210 USA Prof. Dr. Michiel Steyaert ESAT-MICAS Dept. Elektrotechniek K.U. Leuven Kardinaal Mercierlaan 94 Heverlee B-3001 Belgium michiel.steyaert@esat.kuleuven.ac.be

Mohamad Sawan Electrical Engineering Department École Polytechnique de Montréal Montréal, QC Canada

ISBN 978-94-007-1435-9 e-ISB DOI 10.1007/978-94-007-1436-6 Springer Dordrecht Heidelberg London New York

e-ISBN 978-94-007-1436-6

Library of Congress Control Number: 2011928697

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: VTeX UAB, Lithuania

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

To my wife Larissa and our daughter Anna

#### Preface

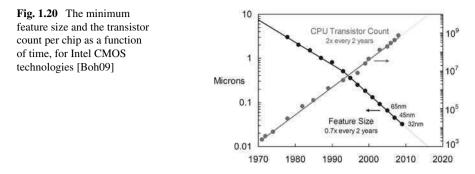

Technological progress in the semiconductor industry has led to a revolution towards new advanced, miniaturized, intelligent, battery-operated and wireless electronic applications. The base of this still ongoing revolution, commonly known as Moore's law, is the ability to manufacture ever decreasing transistor sizes onto a CMOS chip. In other words, the transistor density increases, leading to larger quantity of transistors which can be integrated onto the same single chip die area. As a consequence, more functionality can be integrated onto a single chip die, leading to Systems-on-Chip (SoC) and reducing the total system cost. Indeed, the cost of electronic applications depends in a inverse-proportional fashion on the degree of on-chip integration, which is the main drive for CMOS scaling.

A SoC requires both analog and digital circuitry to be combined in order for it to be able to interact with the analog world. Nevertheless, it is usually processed in a native digital CMOS technology. These CMOS technologies are optimized for the integration of large-scale digital circuits, using very small transistors and low power supply voltages to reduce the power consumption. Beside for the purpose of decreasing the (dynamic) power consumption, the power supply voltage of deep-submicron CMOS technologies is also limited due to the physically very thin gate-oxide of the transistors. This thin gate-oxide, of which the thickness may merely be a few atom layers, would otherwise suffer electrical breakdown. However, the analog circuitry generally needs higher power supply voltages, compared to the digital circuitry. For instance, a power amplifier needs a higher supply voltage to deliver sufficient power into the communication medium. Also, analog signal processing blocks require a higher supply voltage to achieve the desired Signal-to-Noise-Ratio (SNR).

Due to the trend towards electronic applications of portable and wireless nature, (rechargeable) batteries are mandatory to provide the required energy. Although also prone to innovation and improvement, the battery voltage does not scale with the CMOS technology power supply voltages. Obviously, this is due to their physical and chemical constraints. Moreover, their energy density remains limited, limiting the available power and/or the autonomy of the application. Therefore, it is clear that power-management on a SoC-scale is mandatory for ensuring the ongoing feasibility of these applications.

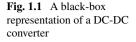

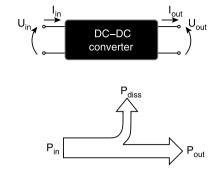

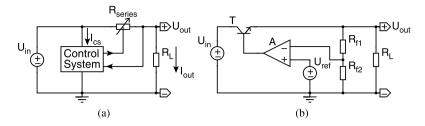

Matching the battery voltage to the required power supply voltage(s) of the SoC can essentially be done in two ways. The first method, which can only be used when the battery voltage is higher than the required power supply voltage(s), is the use of linear voltage converters. This method is very often applied in current state-of-the-art applications, due to the simplicity to integrated it onto the SoC and its low associated cost. However, the excess energy from the battery voltage is dissipated in the form of waste heat, negatively influencing the autonomy and/or physical size of the application. The second method, putting no constraints to the battery voltage in a power-efficient fashion, leading to potentially higher battery autonomies. As a drawback, these switched-mode DC-DC converters are more complex and difficult to integrate onto the SoC, which is why they still require off-chip electronic components, such as inductors and capacitors.

The focus of the presented work is to integrate the switched-mode DC-DC converters onto the SoC, thus reducing both the number of external components and the Printed Circuit Board (PCB) footprint area. However, the poor electrical properties (low Q-factors) of on-chip inductors and capacitors and their low associated values (nH, nF) poses many difficulties, potentially compromising the power conversion efficiency advantage. Combing both the concepts of monolithic SoC integration and achieving a maximal (overall) power conversion efficiency, is the key to success. Moreover, to minimize the costs, the power density of the fully-integrated DC-DC converter is to be maximized.

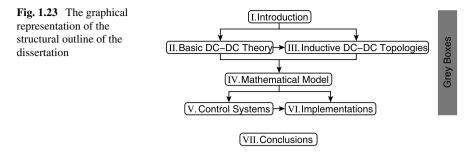

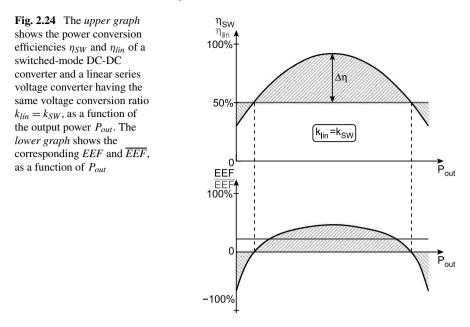

To achieve these goals a firm theoretical base on the matter of DC-DC conversion is provided, leading to the optimal inductive DC-DC converter topology choices. An extensive mathematical steady-state model is deduced, in order to accurately predict both the trade-offs and performance limits of the inductive DC-DC converters. A further increase the performance of DC-DC converters is achieved through the design of novel control techniques, which are particularly optimized for high-frequency monolithic inductive DC-DC converters. Finally, the theory and simulations are verified and validated through the realization of seven monolithic inductive CMOS DC-DC converters. As such, the highest power density and Efficiency Enhancement Factor (EEF) over a linear voltage converter are obtained, in addition to the feasibility proofing of various novel concepts.

The authors also wish to express their gratitude to all persons who have contributed to this scientific research and the resulting book. We would like to thank Prof. R. Puers and Prof. W. Dehaene for their useful comments. In addition we would like to thank the colleagues of the ESAT-MICAS laboratories of K.U. Leuven for both the direct and indirect contributions to the presented work. Finally, we thank our families for their unconditional support and patience.

Leuven

Mike Wens Michiel Steyaert

### Contents

| 1 | Intr | oduction                                                  |

|---|------|-----------------------------------------------------------|

|   | 1.1  | The Origin of DC-DC Converters                            |

|   |      | 1.1.1 Basic Considerations                                |

|   |      | 1.1.2 Historical Notes                                    |

|   | 1.2  | Low Power DC-DC Converter Applications                    |

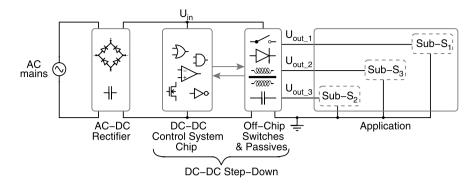

|   |      | 1.2.1 Mains-Operated                                      |

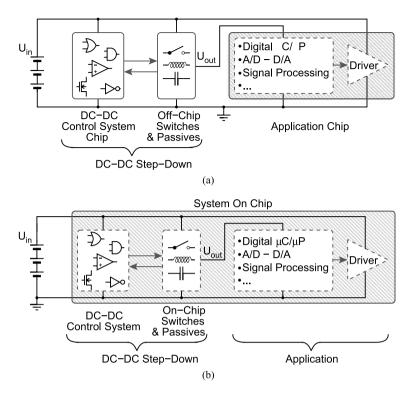

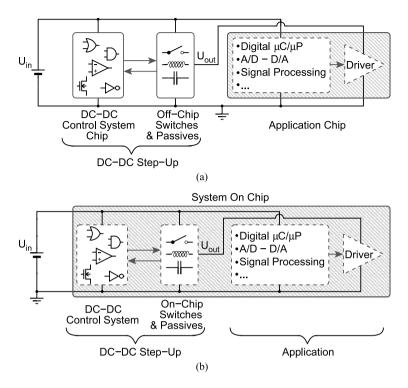

|   |      | 1.2.2 Battery-Operated                                    |

|   | 1.3  | Monolithic DC-DC Converters: A Glimpse into the Future 14 |

|   |      | 1.3.1 CMOS Technology                                     |

|   |      | 1.3.2 The Challenges                                      |

|   | 1.4  | Structural Outline                                        |

|   | 1.5  | Conclusions                                               |

| 2 | Basi | ic DC-DC Converter Theory                                 |

|   | 2.1  | Linear Voltage Converters                                 |

|   |      | 2.1.1 Series Converter                                    |

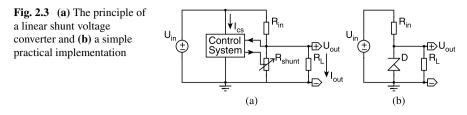

|   |      | 2.1.2 Shunt Converter                                     |

|   | 2.2  | Charge-Pump DC-DC Converters                              |

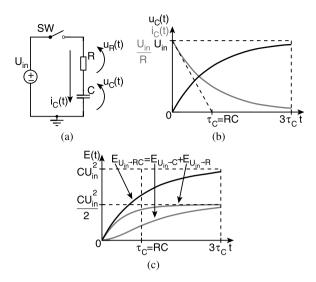

|   |      | 2.2.1 On Capacitors                                       |

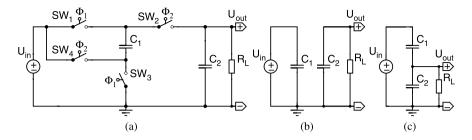

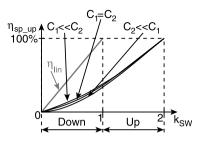

|   |      | 2.2.2 Series-Parallel Step-Down Converter                 |

|   |      | 2.2.3 Series-Parallel Step-Up Converter                   |

|   | 2.3  | Inductive Type DC-DC Converters                           |

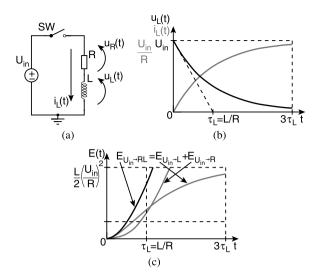

|   |      | 2.3.1 On Inductors                                        |

|   |      | 2.3.2 Inductors and Capacitors: The Combination           |

|   |      | 2.3.3 Reflections on Steady-State Calculation Methods 49  |

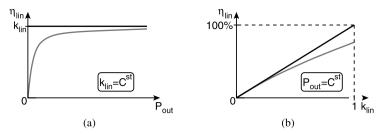

|   | 2.4  | INTERMEZZO: The Efficiency Enhancement Factor 59          |

|   |      | 2.4.1 The Concept                                         |

|   |      | 2.4.2 Interpretations                                     |

|   | 2.5  | Conclusions                                               |

| 3 | Indu | active DC-DC Converter Topologies                         |

|   | 3.1  | Step-Down Converters                                      |

|   |      |                                                           |

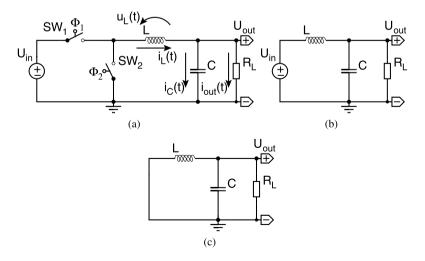

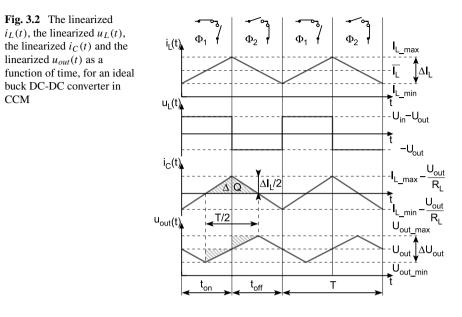

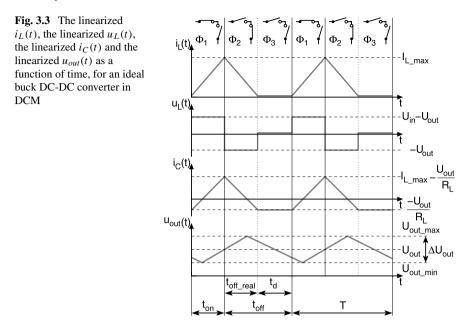

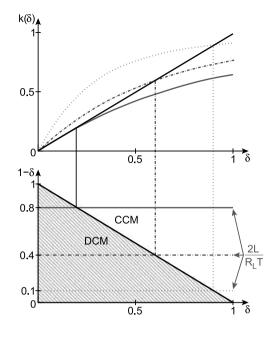

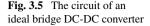

|   |     | 3.1.1           | Buck Converter                                       |

|---|-----|-----------------|------------------------------------------------------|

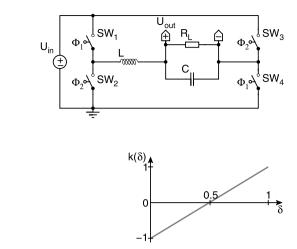

|   |     | 3.1.2           | Bridge Converter                                     |

|   |     | 3.1.3           | Three-Level Buck Converter                           |

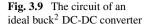

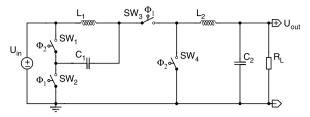

|   |     | 3.1.4           | $Buck2 Converter \dots 77$                           |

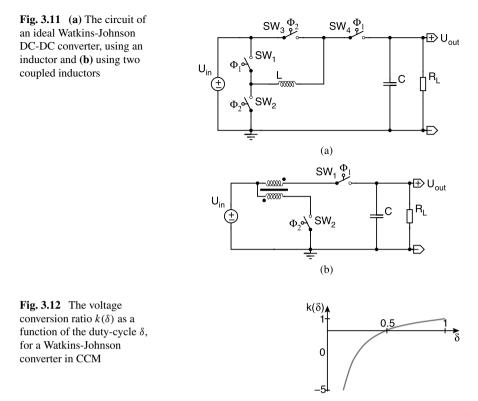

|   |     | 3.1.5           | Watkins-Johnson Converter                            |

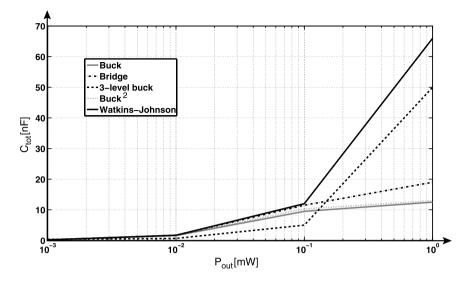

|   |     | 3.1.6           | Step-Down Converter Summary                          |

|   | 3.2 | Step-U          | Jp Converters                                        |

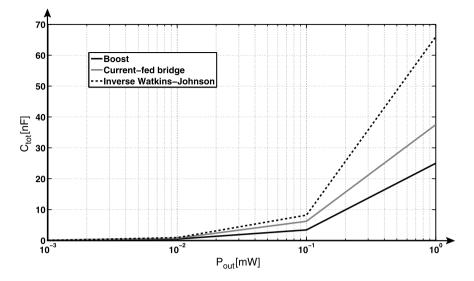

|   |     | 3.2.1           | Boost Converter                                      |

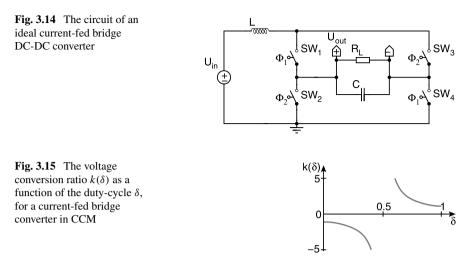

|   |     | 3.2.2           | Current-Fed Bridge Converter                         |

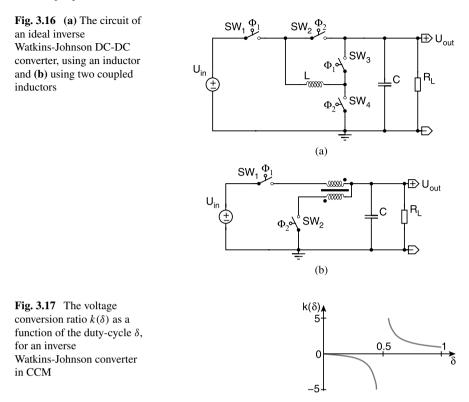

|   |     | 3.2.3           | Inverse Watkins-Johnson Converter                    |

|   |     | 3.2.4           | Step-Up Converter Summary                            |

|   | 3.3 | Step-U          | Jp/Down Converters                                   |

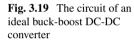

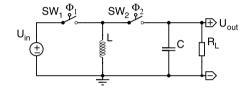

|   |     | 3.3.1           | Buck-Boost Converter                                 |

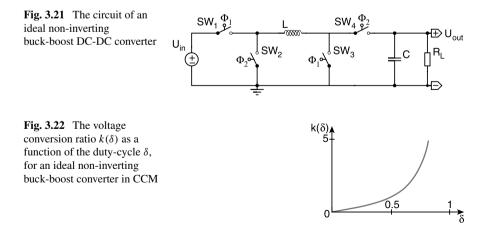

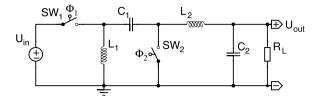

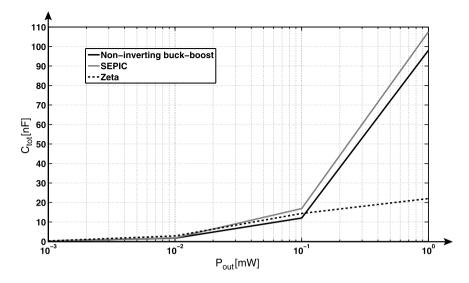

|   |     | 3.3.2           | Non-inverting Buck-Boost Converter                   |

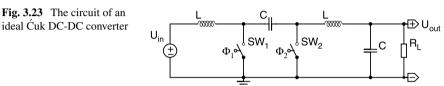

|   |     | 3.3.3           | Ćuk Converter                                        |

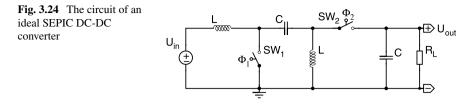

|   |     | 3.3.4           | SEPIC Converter                                      |

|   |     | 3.3.5           | Zeta Converter                                       |

|   |     | 3.3.6           | Step-Up/Down Converter Summary                       |

|   | 3.4 | Other           | Types of Inductive DC-DC Converters                  |

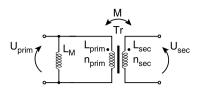

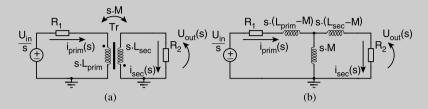

|   |     | 3.4.1           | Galvanic Separated Converters                        |

|   |     | 3.4.2           | Resonant DC-DC Converters                            |

|   | 3.5 | Topolo          | ogy Variations                                       |

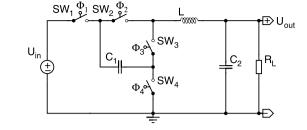

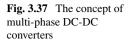

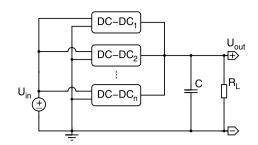

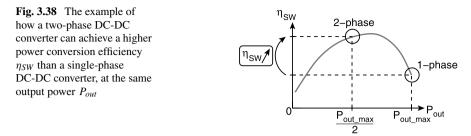

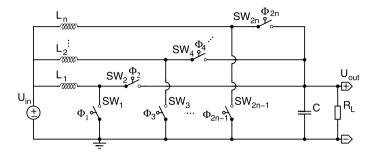

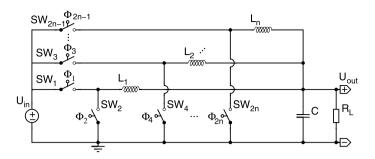

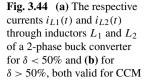

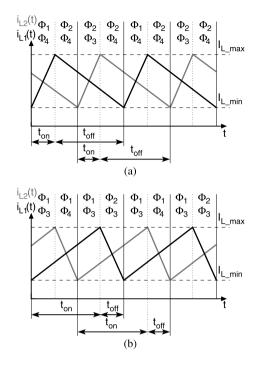

|   |     | 3.5.1           | Multi-phase DC-DC Converters                         |

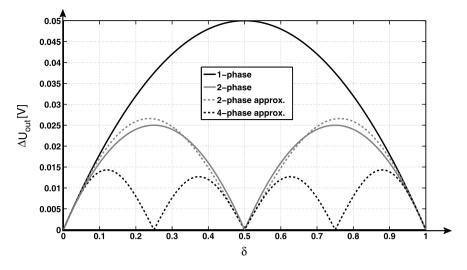

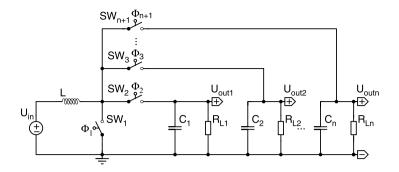

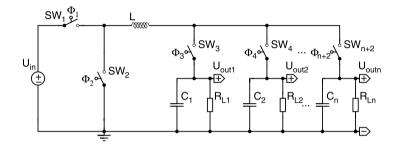

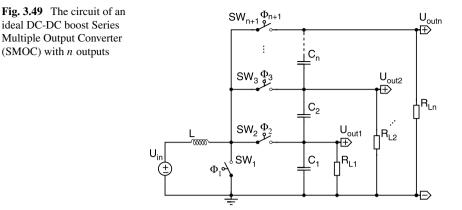

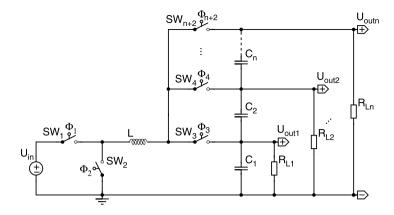

|   |     | 3.5.2           | Single-Inductor Multiple-Output DC-DC Converters 115 |

|   |     | 3.5.3           | On-Chip Topologies                                   |

|   | 3.6 | Concl           | usions                                               |

| 4 | ΔΜ  | athem           | atical Model: Boost and Buck Converter               |

| - | 4.1 |                 | d-Order Model: Boost and Buck Converter              |

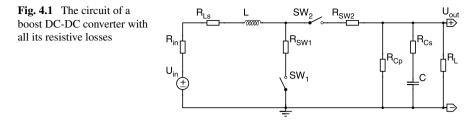

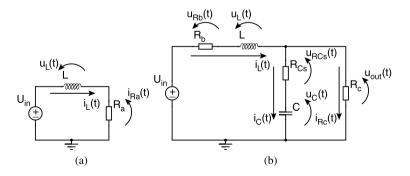

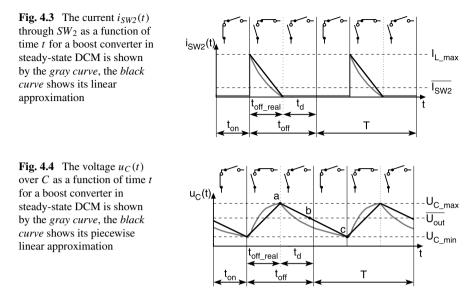

|   | 7.1 | 4.1.1           | Differential Equations: Boost Converter              |

|   |     | 4.1.2           | Calculating the Output Voltage: Boost Converter      |

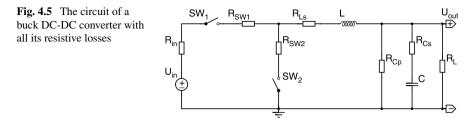

|   |     | 4.1.3           | Differential Equations: Buck Converter               |

|   |     | 4.1.4           | Calculating the Output Voltage: Buck Converter       |

|   | 4.2 |                 | deal Converter Components Models                     |

|   |     | 4.2.1           | Inductor                                             |

|   |     | 4.2.2           | Capacitor                                            |

|   |     | 4.2.3           | Switches                                             |

|   |     | 4.2.4           | Buffers                                              |

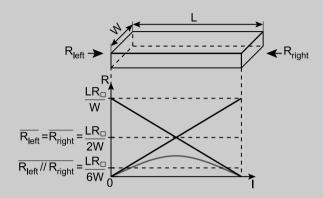

|   |     | 4.2.5           | Interconnect                                         |

|   | 4.3 |                 | erature Effects                                      |

|   |     | 4.3.1           | Inductor                                             |

|   |     |                 |                                                      |

|   |     | 4.3.2           | Switches                                             |

|   | 4.4 |                 |                                                      |

|   | 4.4 |                 | inal Model Flow                                      |

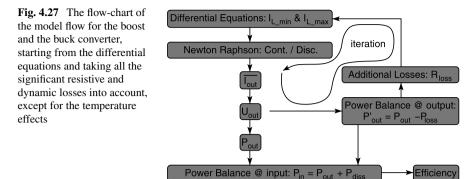

|   | 4.4 | The Fi          | inal Model Flow                                      |

|   | 4.4 | The Fi<br>4.4.1 | inal Model Flow                                      |

| 5 | Con | trol Systems                                                  | . 169 |

|---|-----|---------------------------------------------------------------|-------|

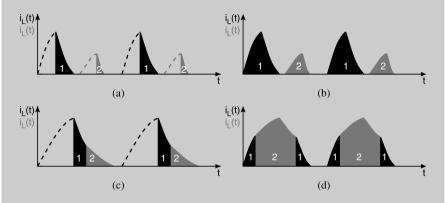

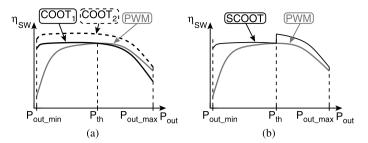

|   | 5.1 | Inductive Type Converter Control Strategies                   | . 170 |

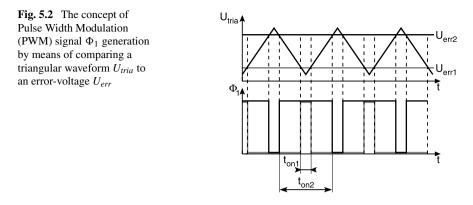

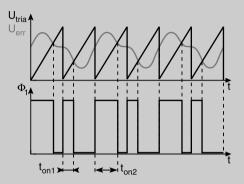

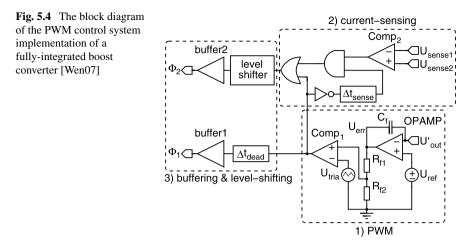

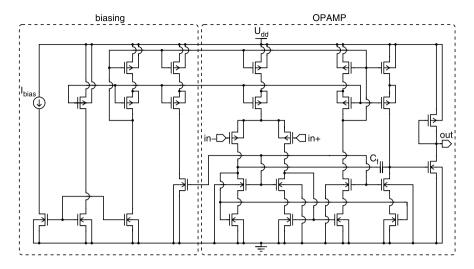

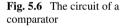

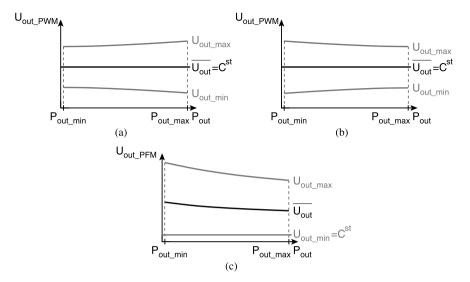

|   |     | 5.1.1 Pulse Width Modulation                                  | . 170 |

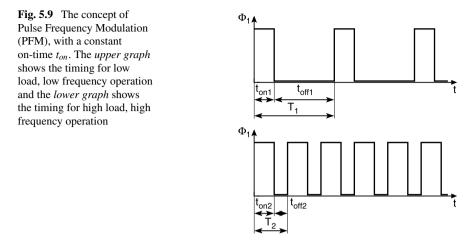

|   |     | 5.1.2 Pulse Frequency Modulation                              | . 175 |

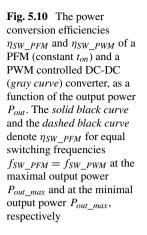

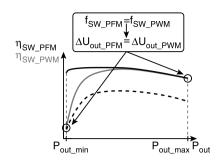

|   |     | 5.1.3 Pulse Width Modulation vs. Pulse Frequency Modulation   | . 176 |

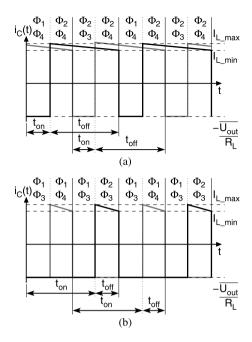

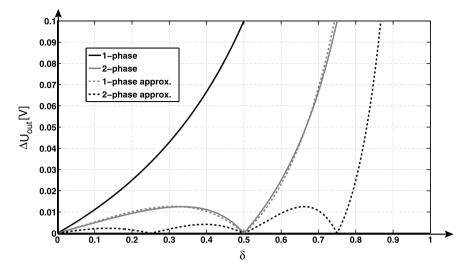

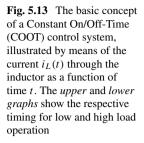

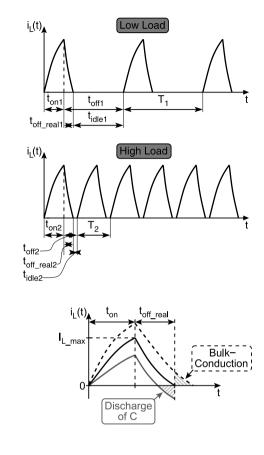

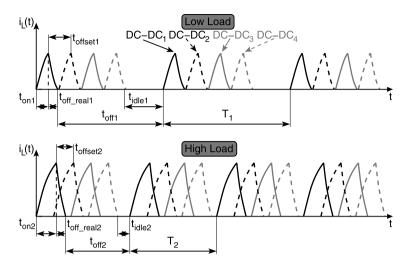

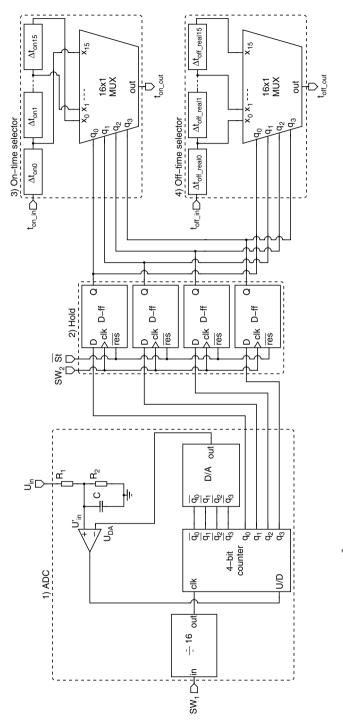

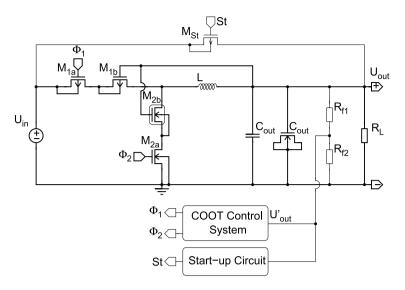

|   | 5.2 | Constant On/Off-Time: COOT                                    | . 181 |

|   |     | 5.2.1 The COOT Concept                                        | . 181 |

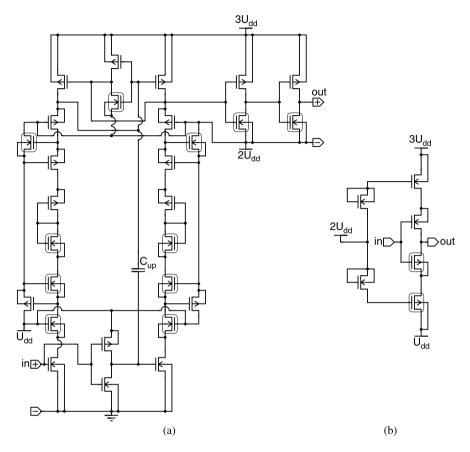

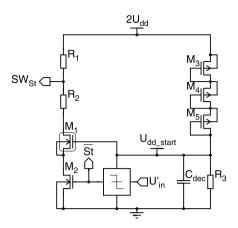

|   |     | 5.2.2 Single-Phase, Single-Output Implementations             | . 184 |

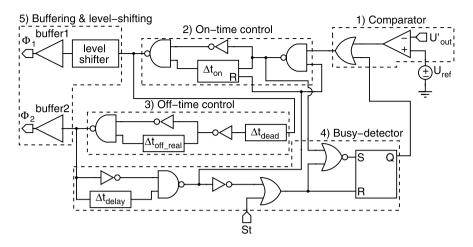

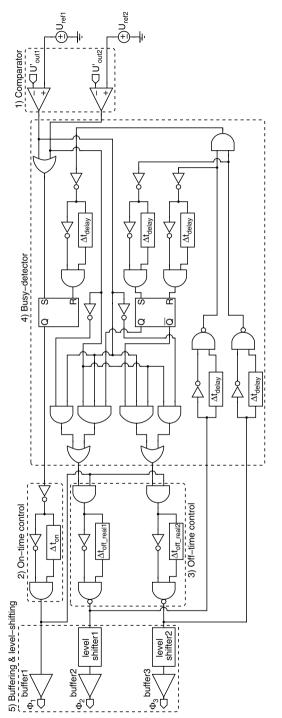

|   |     | 5.2.3 Single-Phase, Two-Output SIMO Implementation            | . 188 |

|   | 5.3 | Semi-Constant On/Off-Time: SCOOT                              | . 193 |

|   |     | 5.3.1 The SCOOT Concept                                       | . 193 |

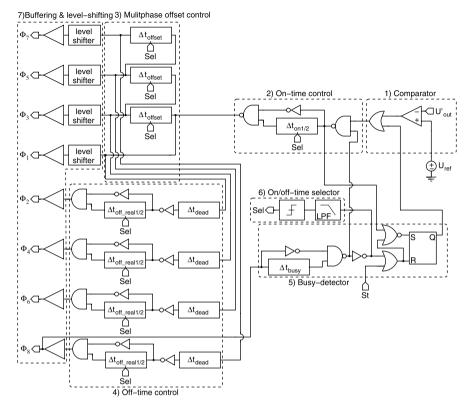

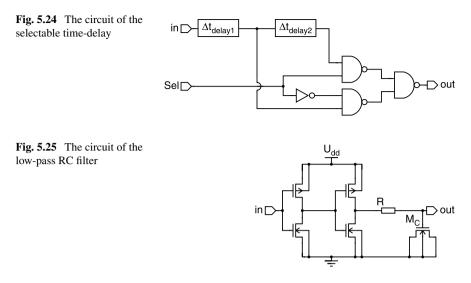

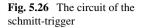

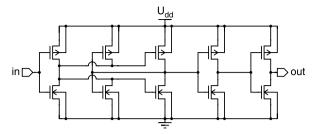

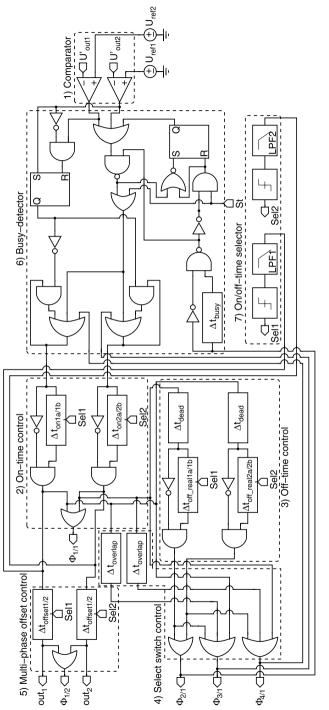

|   |     | 5.3.2 Multi-phase Implementations                             |       |

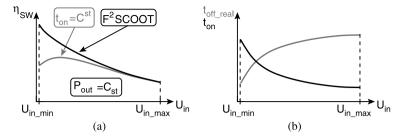

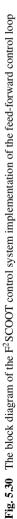

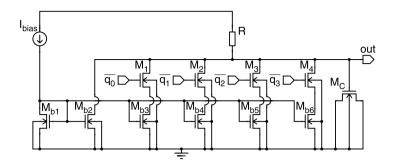

|   | 5.4 | Feed-Forward Semi-Constant On/Off-Time: F <sup>2</sup> -SCOOT | . 203 |

|   |     | 5.4.1 The $F^2$ -SCOOT Concept                                | . 203 |

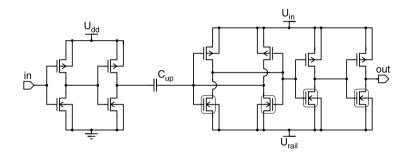

|   |     | 5.4.2 Single-Phase, Two-Output Implementation                 | . 205 |

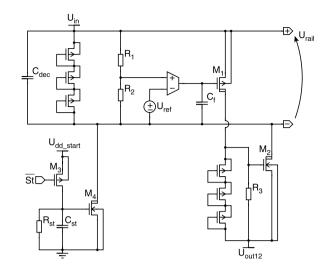

|   | 5.5 | Start-up                                                      | . 209 |

|   |     | 5.5.1 The Concept                                             | . 210 |

|   |     | 5.5.2 Implementations                                         | . 210 |

|   | 5.6 | Conclusions                                                   | . 211 |

| 6 | Imn | lementations                                                  | 213   |

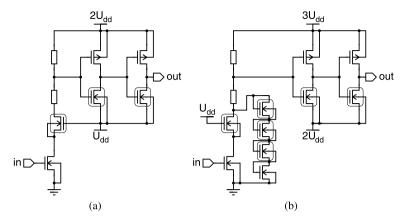

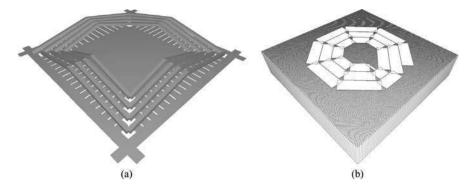

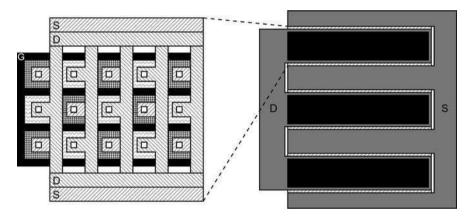

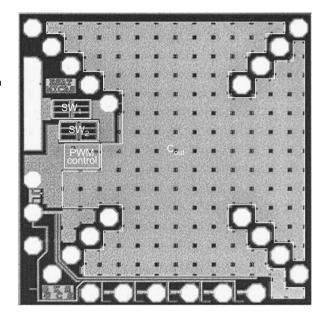

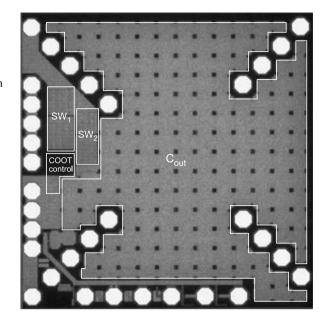

| v | 6.1 | Monolithic Converter Components                               |       |

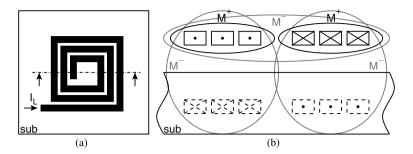

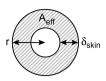

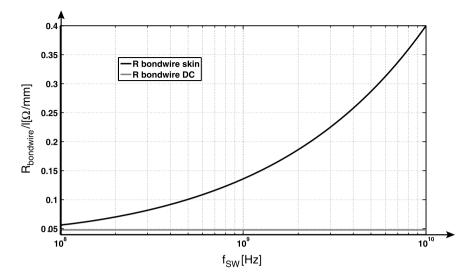

|   | 0.1 | 6.1.1 Inductor                                                |       |

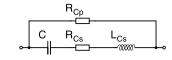

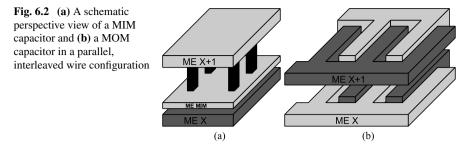

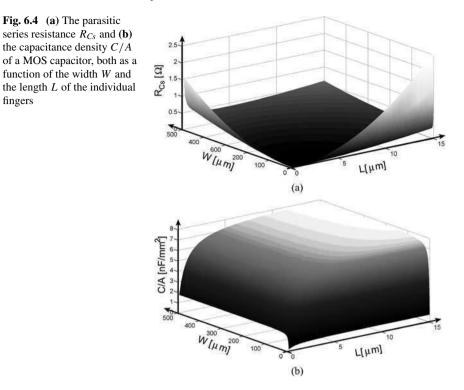

|   |     | 6.1.2 Capacitor                                               |       |

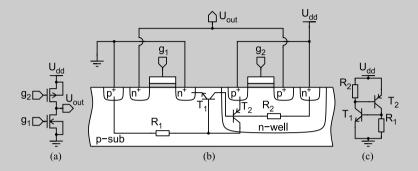

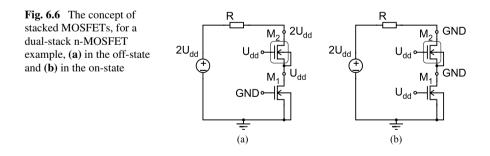

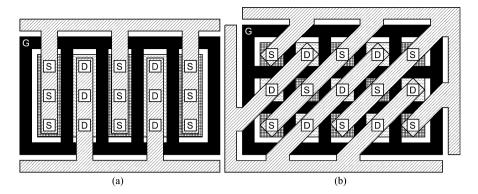

|   |     | 6.1.3 Switches                                                |       |

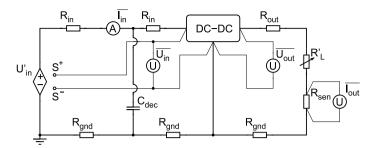

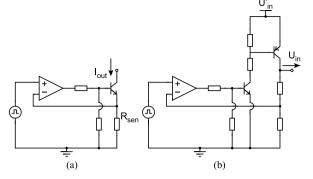

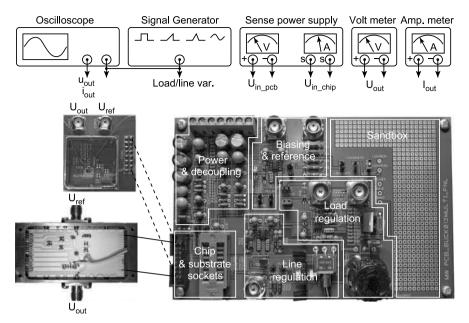

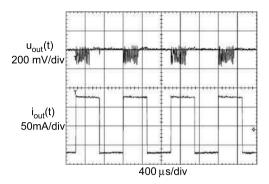

|   | 6.2 | On Measuring DC-DC Converters                                 |       |

|   |     | 6.2.1 Main Principles                                         |       |

|   |     | 6.2.2 Practical Example                                       |       |

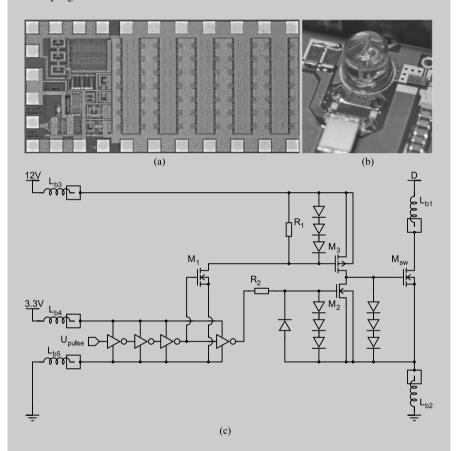

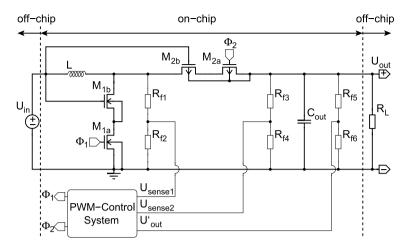

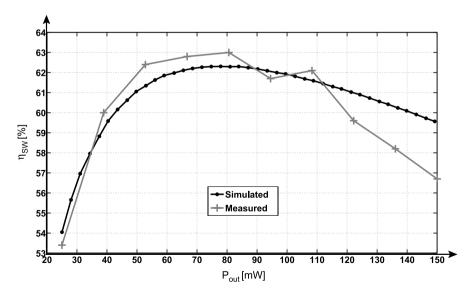

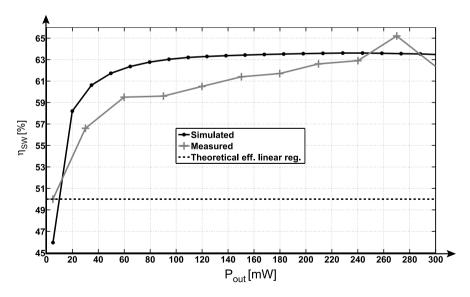

|   | 6.3 | Boost Converters                                              |       |

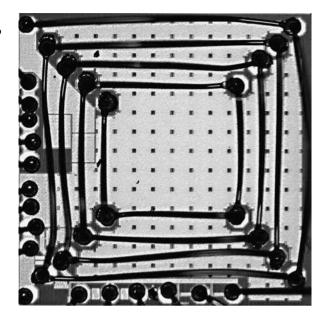

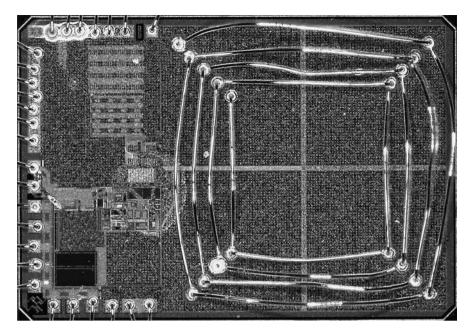

|   |     | 6.3.1 Bondwire, Single-Phase, Single-Output                   |       |

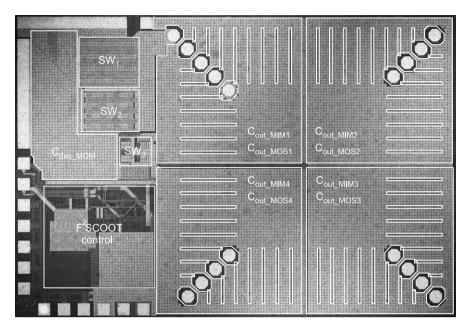

|   |     | 6.3.2 Metal-Track, Single-Phase, Two-Output SIMO              |       |

|   | 6.4 | Buck Converters                                               |       |

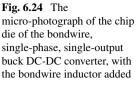

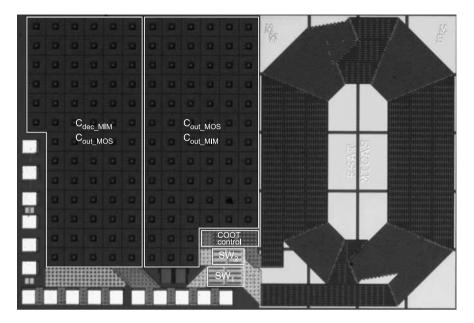

|   |     | 6.4.1 Bondwire, Single-Phase, Single-Output                   |       |

|   |     | 6.4.2 Metal-Track, Single-Phase, Single-Output                |       |

|   |     | 6.4.3 Metal-Track, Four-Phase, Single Output                  |       |

|   |     | 6.4.4 Metal-Track, Four-Phase, Two-Output SMOC                | . 248 |

|   |     | 6.4.5 Bondwire, Single-Phase, Two-Output SMOC                 |       |

|   | 6.5 | Comparison to Other Work                                      | . 254 |

|   |     | 6.5.1 Inductive Step-Up Converters                            | . 255 |

|   |     | 6.5.2 Inductive Step-Down Converters                          | . 256 |

|   | 6.6 | Conclusions                                                   |       |

| 7 | Gen | eral Conclusions                                              | 261   |

|   | 7.1 | Conclusions                                                   |       |

|   | 7.2 | Remaining Challenges                                          |       |

| References | • | • |  | • | • |  |   |  |  | • | • |  | • |  | • |  |  |  | • | • |  | 265 |

|------------|---|---|--|---|---|--|---|--|--|---|---|--|---|--|---|--|--|--|---|---|--|-----|

| Index      |   |   |  |   |   |  | • |  |  |   |   |  |   |  |   |  |  |  |   |   |  | 273 |

# **Abbreviations and Symbols**

#### Abbreviations

| Abbreviations        |                                                          |

|----------------------|----------------------------------------------------------|

| AC                   | Alternating-Current                                      |

| AC-AC                | Alternating-Current to Alternating-Current               |

| AC-DC                | Alternating-Current to Direct-Current                    |

| ADC                  | Analog-to-Digital Converter                              |

| BCM                  | Boundary Conduction Mode                                 |

| BiCMOS               | Bipolar Complementary Metal-Oxide Semiconductor          |

| BJT                  | Bipolar Junction Transistor                              |

| BW                   | BandWidth                                                |

| CB                   | Conduction Boundary                                      |

| CFL                  | Compact Fluorescent Lamps                                |

| СМ                   | Conduction Mode                                          |

| ССМ                  | Continuous Conduction Mode                               |

| CMOS                 | Complementary Metal-Oxide Semiconductor                  |

| COOT                 | Constant On/Off-Time                                     |

| CRT                  | Cathode Ray Tube                                         |

| DAC                  | Digital-to-Analog Converter                              |

| DC                   | Direct-Current                                           |

| DC-AC                | Direct-Current to Alternating-Current                    |

| DC-DC                | Direct-Current to Direct-Current                         |

| DCM                  | Discontinuous Conduction Mode                            |

| DIL                  | Dual In Line                                             |

| EEF                  | Efficiency Enhancement Factor                            |

| EMI                  | Electro Magnetic Interference                            |

| FAIMS                | High-Field Asymmetric waveform Ion Mobility Spectrometry |

| FET                  | Field-Effect Transistor                                  |

| ESI                  | Electro-Spray Ionization                                 |

| ESL                  | Electric Series inductance                               |

| ESR                  | Electric Series Resistance                               |

| FOX                  | Field Oxide                                              |

| F <sup>2</sup> SCOOT | Feed-Forward Semi-Constant On/Off-Time                   |

|                      |                                                          |

| GBW           | Gain BandWidth                                                                   |

|---------------|----------------------------------------------------------------------------------|

| GND           | GrouND                                                                           |

| HF            | High Frequency                                                                   |

| IC            | Integrated Circuit                                                               |

| IGBT          | Insulated Gate Bipolar Transistor                                                |

| LDO           | Low Drop-Out                                                                     |

| LIDAR         | Laser Imaging Detection And Ranging                                              |

| LIDAK         | Lithium-ION                                                                      |

| ME1           | Metal-1                                                                          |

| MIM           | Metal-Insulator-Metal                                                            |

| MOM           | Metal-Oxide-Metal                                                                |

|               | Metal-Oxide Semiconductor                                                        |

| MOS<br>MOSFET | Metal-Oxide Semiconductor Field-Effect Transistor                                |

|               | n-channel Metal-Oxide Semiconductor Field-Effect Transistor                      |

| n-MOSFET      |                                                                                  |

| MS            | Mass Spectrometry<br>Multi-PleXer                                                |

| MUX           |                                                                                  |

| NPN           | <i>n</i> -type <i>p</i> -type <i>n</i> -type transition<br>OPerational AMPlifier |

| OPAMP         |                                                                                  |

| OTA           | Operational Transconductance Amplifier<br>Oxide-1                                |

| ox1           |                                                                                  |

| PC            | Personal Computer                                                                |

| PCB           | Printed Circuit Board                                                            |

| PFC           | Power Factor Correction                                                          |

| PFM           | Pulse Frequency Modulation                                                       |

| p-mosfet      | p-channel Metal-Oxide Semiconductor Field-Effect Transistor                      |

| PNP           | <i>p</i> -type <i>n</i> -type <i>p</i> -type transition                          |

| PSRR          | Power Supply Rejection Ratio                                                     |

| PTC           | Positive temperature coefficient                                                 |

| PWM           | Pulse Width Modulation                                                           |

| Q.E.D.        | Quod Erat Demonstrandum                                                          |

| RC            | Resistor-Capacitor                                                               |

| RF            | Radio-Frequency                                                                  |

| RL            | Resistor-Inductor                                                                |

| RLC           | Resistor-Inductor-Capacitor                                                      |

| RMS           | Root-Mean-Square                                                                 |

| SCOOT         | Semi-Constant On/Off-Time                                                        |

| SEPIC         | Single-Ended Primary-Inductance Converter                                        |

| siGe          | Silicon-Germanium                                                                |

| SIMO          | Single-Inductor Multiple-Output                                                  |

| SMOC          | Series Multiple-Output Converter                                                 |

| SMOS          | Type of healthy sandwich                                                         |

| SMPS          | Switched-Mode Power Supply                                                       |

| SOC           | System-on-Chip                                                                   |

| SPICE         | Simulation Program with Integrated Circuit Emphasis                              |

|               |                                                                                  |

| SRR                                                             | Supply Rejection Ratio                                |

|-----------------------------------------------------------------|-------------------------------------------------------|

| SW                                                              | Switch                                                |

| Symbols and Q                                                   | Duantities                                            |

| Ă                                                               | Area                                                  |

| $A_C$                                                           | On-chip capacitor area                                |

| $A_{c}^{+}$                                                     | Positive charge balance area                          |

| $\begin{array}{c} A_C^+ \\ A_C^- \end{array}$                   | Negative charge balance area                          |

| $A_{L}$                                                         | Perpendicular projected area of the inductor windings |

| $ \begin{array}{c} A_L \\ A_L^+ \\ A_L^- \\ A_L^- \end{array} $ | Positive volt-second balance area                     |

| $A_{\perp}^{L}$                                                 | Negative volt-second balance area                     |

| arccos                                                          | Arc cosine                                            |

| $A_{oldsymbol{arphi}}$                                          | Perpendicular cross-sectional area                    |

| $A_{\varnothing\_eff}$                                          | Effective $A_{\varnothing}$                           |

| $C^{\sim}$                                                      | Capacitance                                           |

| $C_{eq}$                                                        | Equivalent capacitance                                |

| cos                                                             | Cosine                                                |

| $C_{db}$                                                        | Parasitic drain-bulk capacitance                      |

| $C_{dec}$                                                       | Input decouple capacitance                            |

| $C_{gb}$                                                        | Parasitic gate-bulk capacitance                       |

| $C_{gd}$                                                        | Parasitic gate-drain capacitance                      |

| $C_{gc}$                                                        | Parasitic gate-source capacitance                     |

| $C_{gg}$                                                        | Parasitic gate capacitance                            |

| $C_{g\_min}$                                                    | Parasitic gate of a minimal size inverter             |

| $C_{sb}$                                                        | Parasitic source-bulk capacitance                     |

| $C_{in}$                                                        | Input capacitance                                     |

| Cout                                                            | Output capacitance                                    |

| C <sub>tot</sub>                                                | Total capacitance                                     |

| C <sub>out_tot</sub>                                            | Total output capacitance                              |

| $C_{out\_1}$                                                    | Capacitance of output 1                               |

| $C_{pad}$                                                       | Parasitic substrate capacitance of a bonding pad      |

| $C_{par}$                                                       | Parasitic capacitance                                 |

| $C_{sub}$                                                       | Parasitic substrate winding capacitance               |

| $C_1$                                                           | Capacitance 1                                         |

| d<br>d                                                          | Thickness<br>Pitch between two conductors             |

|                                                                 | Thickness of the oxide                                |

| $d_{ox}$                                                        | Euler's constant: 2.718281828                         |

| e<br>E <sub>C_in</sub>                                          | Energy stored in <i>C</i>                             |

| $E_{C_{out}}$                                                   | Energy delivered by C                                 |

| $E_C_{out}$<br>$E_C(t)$                                         | Energy stored in $C$ as a function of $t$             |

| $E_{C_1}$                                                       | Energy stored in $C_1$                                |

| $E_{C_2}$                                                       | Energy stored in $C_2$                                |

| $E_{C_1C_2}$                                                    | Energy stored in $C_1$ and $C_2$                      |

| $E_{C_1 \to C_2}$                                               | Transferred energy from $C_1$ to $C_2$                |

| $E_{C_1 \to C_2}$ $E_{C_1 \to R}$                               | Transferred energy from $C_1$ to $R$                  |

| $C_1 \neq A$                                                    |                                                       |

| F                               | Transformed ensures from C to BC                                           |

|---------------------------------|----------------------------------------------------------------------------|

| $E_{C_1 \to RC}$                | Transferred energy from $C_1$ to $RC$                                      |

| EEF                             | Efficiency Enhancement Factor                                              |

| EEF                             | Mean Efficiency Enhancement Factor                                         |

| <i>EEF</i>                      | Weighted Efficiency Enhancement Factor                                     |

| $EEF(P_{out\_i})$               | <i>EEF</i> as a function of the <i>i</i> th $P_{out}$                      |

| $E_L$                           | Magnetic energy stored in L                                                |

| $E_{L\_in}$                     | Energy stored in L                                                         |

| $E_{L\_out}$                    | Energy delivered by L                                                      |

| $E_L(t)$                        | Magnetic energy stored in $L$ as a function of $t$                         |

| $E_L(t)$                        | Energy stored in $L$ as a function of $t$                                  |

| $E_R(t)$                        | Energy dissipated in $R$ as a function of $t$                              |

| $E_{R_2}$                       | Energy dissipated in $R_2$ in steady-state                                 |

| $E_{R_2}(t)$                    | Energy dissipated in $R_2$ as a function of $t$                            |

| $E_{U_{in}}(t)$                 | Energy delivered by $U_{in}$ as a function of t                            |

| $E_{U_{in} \to C_1}$            | Transferred energy from $U_{in}$ to $C_1$                                  |

| $E_{U_{in} \to C_1 C_2}$        | Transferred energy from $U_{in}$ to $C_1$ and $C_2$                        |

| $E_{U_{in}C_1 \rightarrow C_2}$ | Transferred energy from $U_{in}$ and $C_1$ to $C_2$                        |

| $E_{U_{in} \to C}(t)$           | Transferred energy from $U_{in}$ to C as a function of t                   |

| $E_{U_{in} \to L}(t)$           | Transferred energy from $U_{in}$ to L as a function of t                   |

| $E_{U_{in} \to R}(t)$           | Transferred energy from $U_{in}$ to R as a function of t                   |

| $E_{U_{in} \to RC}(t)$          | Transferred energy from $U_{in}$ to R and C as a function of t             |

| $E_{U_{in} \to RL}(t)$          | Transferred energy from $U_{in}$ to R and L as a function of t             |

| $E_{U_{in} \to RLC}(t)$         | Transferred energy from $U_{in}$ to $R$ , $L$ and $C$ as a function of $t$ |

| f                               | Frequency                                                                  |

| F                               | Global effective fan-out                                                   |

| $f_{scale}$                     | Scaling factor                                                             |

| $f_{SW}$                        | Switching frequency                                                        |

| $f_0$                           | Resonance frequency                                                        |

| $g_1\{\}$                       | Function $g_1$                                                             |

| $H(f_{SW})$                     | Transfer function as a function of $f_{SW}$                                |

| Ι                               | Current                                                                    |

| Iak                             | Anode-cathode current                                                      |

| $I_b$                           | Base current                                                               |

| $I_c$                           | Collector current                                                          |

| $i_{C\_charge}$                 | Charge current through C                                                   |

| $i_{C\_discharge}$              | Discharge current through C                                                |

| $I_{C\_leak}$                   | Leakage current through C                                                  |

| $I_{cs}$                        | Control system supply current                                              |

| $i_C(t)$                        | Current through $C$ as a function of $t$                                   |

| <i>iC</i> 1                     | Current 1 through C                                                        |

| $i_{C2}$                        | Current 2 through C                                                        |

| Ids                             | Drain-source current                                                       |

| $I_e$                           | Emitter current                                                            |

| I <sub>in</sub>                 | Input current                                                              |

| I' <sub>in_max</sub>            | Maximum input current                                                      |

| max                             | -                                                                          |

| I' <sub>in_min</sub>                   | Minimum input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In_min<br>Iin_RMS                      | RMS input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\frac{II}{I_L}$                       | Mean current through L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $I_{L_{max}}$                          | Maximal current through L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $I_{L_{min}}$                          | Minimal current through L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $i_L(t)$                               | Current through $L$ as a function of $t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $i_L(0)$<br>$i_L(0)$                   | Initial current through L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        | Output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\frac{I_{out}}{I_{out}}$              | Mean output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                        | RMS output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $I_{out\_RMS}$<br>$I_{out}(t)$         | Output current as a function of $t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $l_{prim}$                             | Current through primary winding in the Laplace domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $i_{prim}(s)$                          | Current through primary winding, in the Laplace-domain $C_{\text{through }} B_{\text{through }} a_{\text{through }} b_{\text{through }} a_{\text{through }} a_{$ |

| $i_{Rb}(t)$                            | Current through $R_b$ as a function of t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |