**Neal Stollon**

# On-Chip Instrumentation

Design and Debug for Systems on Chip

On-Chip Instrumentation

Neal Stollon

# **On-Chip Instrumentation**

Design and Debug for Systems on Chip

Neal Stollon HDL Dynamics, Dallas TX, USA neals@hdldynamics.com

ARM9, Coresight, ETM9, ETM9, MMD are trademarks or registered trademarks of ARM Holdings plc. All rights reserved.

EJTAG, HyperDebug, MIPS64, MIPS32, OCI, PDtrace, RRT are trademarks or registered trademarks of MIPS Technologies, Inc. All rights reserved.

OSCAN, CDX, BDX are trademarks or registered trademarks of IEEE 1149.7 Working Group. All rights reserved.

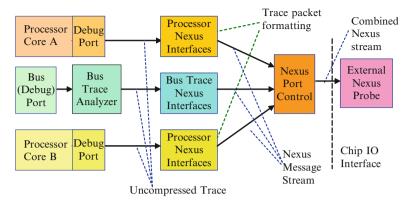

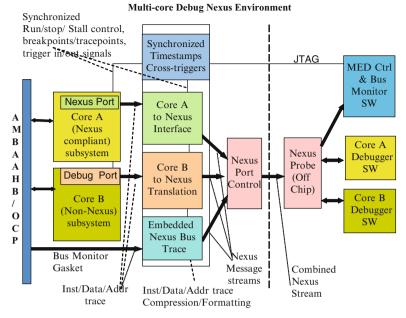

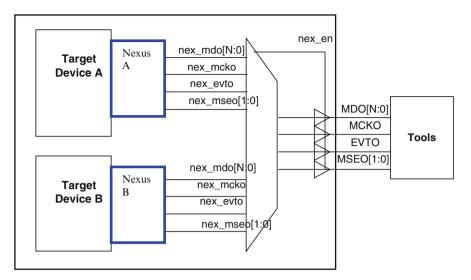

TCODE, NPC are trademarks or registered trademarks of IEEE 5001 and Nexus 5001 Forum. All rights reserved.

ONCE, mxC are trademarks or registered trademarks of Freescale Inc. All rights reserved.

OCDS, MCDS, Cerebus, PCP2 are trademarks or registered trademarks of Infineon Technologies AG. All rights reserved.

Any other third party trademarks remain the property of their respective owners

All copyrights on images, graphics, descriptions, products, and brands remain property of their respective owners. No infringement of rights is intended or implied.

ISBN 978-1-4419-7562-1 e-ISBN 978-1-4419-7563-8 DOI 10.1007/978-1-4419-7563-8 Springer New York Dordrecht Heidelberg London

© Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

When I started this book, I thought I understood the world of on-chip debug–after all, I had been part of one of the leading startups in the area for 5 years and had been a participant in a number of standard and industry organizations that were leading the world of on-chip debug and instrumentation into the next wave. As I gathered my materials, I grew more impressed by the day and by the month at the body of work that this topic has accumulated, in industry and in academia, in every nook and cranny of the embedded systems business, from embedded processor, to bus architecture, to FPGA, to IP development; engineers have developed and customized a truly impressive range of on-chip debug and instrumentation solutions to address and support their products and to enable an increasingly capable infrastructure that does much more than the prosaic word debug implies and starts to address the full potential of what on-chip instrumentation can truly provide for the electronics industry.

This book came about, in part, because of the lack of a comprehensive discussion of on-chip debug instrumentation. This seems to have been an area where the experts come about from on-the-job experience and in ad hoc methods. On-chip debug is an integral part of most modern processor and system on-chip (SoC) design, but in my experience it is not a topic given in-depth discussion in engineering school (universities take note). Most engineers' experience of on-chip debug is limited to plugging into the JTAG port and running the software, with little understanding of what goes on within. This text tries to provide a general overview of the different types of on-chip debug that goes into a design.

This book is structured into three main sections; the first, Chaps. 1–7, is an introduction to the variety of concepts that make up on-chip debug, in particular looking at some of the history and well-established infrastructure, including an overview of JTAG from a debug, rather than test, point of view. It also looks at aspects of processorand bus-level instrumentation and discusses multicore on-chip debug issues The second section, Chaps. 8–11, addresses a number of the standards and industry efforts that are ongoing in areas ranging from instrument interfaces to JTAG advances, some of which, like Nexus and OCP-IP, I have been involved in, and others that have been a learning experience for me over the last year, all of which I believe will form the core basis for the next generation of on-chip debug. The third section, Chaps. 12–15, is a survey of some of the wide variety of commercially supported solutions for on-chip debug, addressing a limited cross section of the types of on-chip instruments that are available for different processors and SoCs.

Some areas related to on-chip debug have been intentionally kept generic and out of the discussion to maintain the focus on the on-chip instrumentation. Notably, I have kept any detailed discussion of probes and host-based debugger software to a minimum, other than what is required to make the concepts of JTAG and trace understandable. This may seem unusual, but the reasons for this are two-fold. First, the topic of debug probe and software design is at least a book in itself. Second, the commercial business involved in probes and debug software is a significant business unit for most processor companies as well as the dozens of companies that provide probe and software solutions (many run by people I know) that address the range of debug options. To mention any one example in any detail would ignore the rest that are equally deserving of mention.

Few are of variety of instrumentation- and debug-related areas I cover are discussed exhaustively. This is due to both limitations on space and a large amount of supplemental detailed information available elsewhere for those who want to explore in more depth. Similarly, I have intentionally avoided discussion of some of the more advanced implementations, in order to keep the text accessible to a more general reader. For virtually all topics, I highly recommend the reader to directly contact the IP or chip vender or standards group for more detailed and updated information on the topics. Those interested in instrumentation products can find an amount of online resources that address specific instrumentation solutions in minute detail. The amount of documentation available on MIPS EJTAG or ARM ETM, for example, can put page length of *War and Peace* to shame.

The standards-related activities are somewhat less well documented, in some cases because they are work in progress. However, there is a lot of follow-on information out there for those who search. So I have tried to focus on what I think are the interesting or unique parts of different instrumentation solutions, with the assumption that readers interested in more detail can find it.

I want to acknowledge a number of people in the industry who have helped me along the way, especially Rick Leatherman and the on-chip instrumentation team of the First Silicon Solutions group at MIPS, who got me started in thinking about on-chip instrumentation and who taught me far more they realize about on-chip debug technologies and the businesses involved. I also thank the current and past members of the Nexus IEEE 5000 Forum and members of the OCP-IP Debug Working Group, with special recognition to Bob Uvacek, my longtime compatriot in the working group.

Last, but by far not least, I want to acknowledge my family, without whom I am nothing. My wife Marcy, my daughters Courtney and Naomi, my son Eric, and my mom Rita Bickel Stollon (of blessed memory) were patient and understanding of the time I spent working on this book. Finally, I dedicate this book to my family but especially to my father Arthur Stollon (of blessed memory), who proofread every-thing I wrote while I was in school and taught me "be prepared to trudge thru the wilderness to get a change at the limelight".

Dallas, TX

## Contents

| 1 | Intr | oduction                                                            | 1  |

|---|------|---------------------------------------------------------------------|----|

|   | 1.1  | The Need for On-Chip Debug                                          | 1  |

|   | 1.2  | Instrument- (**in-silicon) and EDA- (Presilicon) Based Verification | 3  |

|   | 1.3  | SoC Debug Requirements                                              | 7  |

|   | 1.4  | Instrumentation-Based Debug Infrastructure                          | 11 |

| 2 | On-  | Chip Instrumentation Components                                     | 17 |

|   | 2.1  | Trace and Event Triggering                                          | 17 |

|   | 2.2  | External Interfaces for On-Chip Instrumentation                     | 18 |

|   | 2.3  | Performance Analysis Using On-Chip Instrumentation                  | 19 |

|   | 2.4  | On-Chip Logic and Bus Analysis                                      | 20 |

|   | 2.5  | On-Chip Instrumentation Examples                                    | 22 |

|   |      | 2.5.1 Trace Monitoring and Interfaces                               | 22 |

|   |      | 2.5.2 Bus Logic Monitoring                                          | 23 |

|   |      | 2.5.3 Real-Time Data Exchange                                       | 25 |

|   | 2.6  | Multiprocessor Debug                                                | 26 |

| 3 | JTA  | G Use in Debug                                                      | 31 |

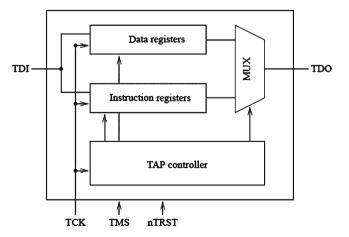

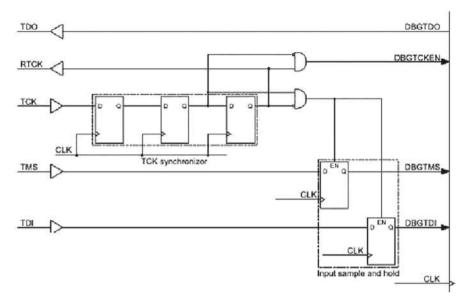

|   | 3.1  | JTAG Pins                                                           | 32 |

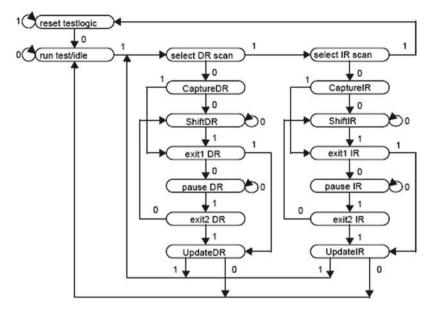

|   | 3.2  | Test Access Port                                                    | 35 |

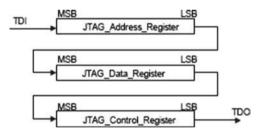

|   | 3.3  | JTAG Registers                                                      | 38 |

|   | 3.4  | JTAG Instructions                                                   | 39 |

|   | 3.5  | Boundary-Scan Description Language                                  | 40 |

|   | 3.6  | The Road to JTAG: Historical Debug Approaches                       | 44 |

|   |      | 3.6.1 Background Debug Mode                                         | 47 |

| 4 | Pro  | cessor System Debug                                                 | 49 |

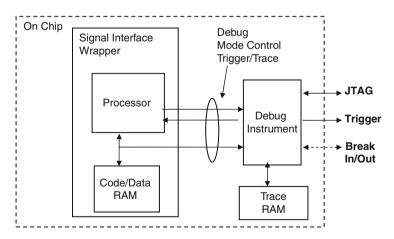

|   | 4.1  | A Processor Debug Instrument Implementation                         | 52 |

|   | 4.2  | Processor Trace Compression                                         | 55 |

|   | 4.3  | Hunting Code Errors with Self-Trace                                 | 59 |

| 5 | An ( | On-Chi         | p Debug System                                   |

|---|------|----------------|--------------------------------------------------|

|   | 5.1  |                | S Features                                       |

|   |      | 5.1.1          | Debug Events                                     |

|   |      | 5.1.2          | Debug Event Actions                              |

|   |      | 5.1.3          | Debug Registers                                  |

|   | 5.2  | Operat         | tion Modes                                       |

|   |      | 5.2.1          | Entering Communication Mode                      |

|   |      | 5.2.2          | Communication Mode Instructions                  |

|   |      | 5.2.3          | Monitor-to-Debugger Host Data Transfer (Receive) |

|   |      | 5.2.4          | Debugger Host-to-Monitor Data Transfer (Send)    |

|   |      | 5.2.5          | High-Level Synchronization                       |

|   | 5.3  |                | S Registers                                      |

|   |      | 5.3.1          | Debug Task ID Register                           |

|   |      | 5.3.2          | Instruction Pointer Register                     |

|   |      | 5.3.3          | Hardware Trigger Comparison Registers            |

|   |      | 5.3.4          |                                                  |

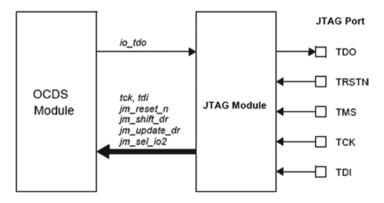

|   | 5.4  |                | S JTAG Access                                    |

|   | т    | 5.4.1          | Steps to Initialize the JTAG Module              |

|   | 5.5  |                | S Module Access                                  |

|   | 5.5  | 5.5.1          |                                                  |

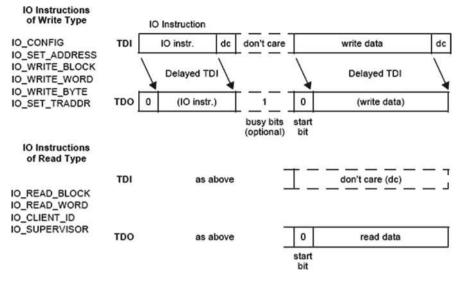

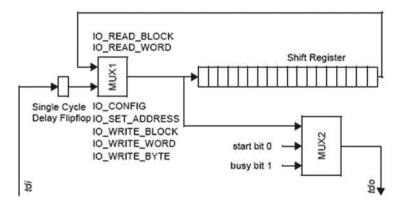

|   | 5.6  |                | S JTAG I/O Instructions                          |

|   | 5.7  |                | S JTAG Registers                                 |

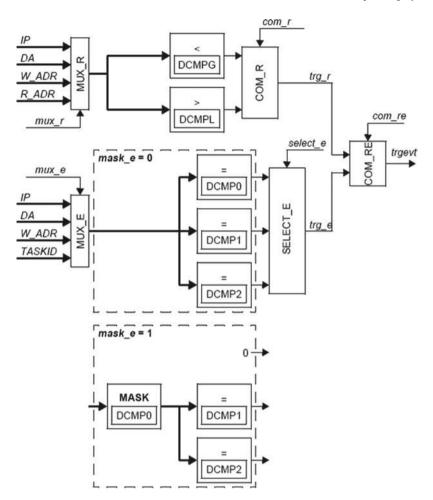

|   | 5.8  |                | vare Triggers                                    |

|   | 5.0  | 5.8.1          | Structure of a Noninterruptible Monitor Routine  |

|   |      | 5.8.2          | Structure of an Interruptible Monitor Routine    |

|   |      | 5.8.2          | Debug Event Control Registers                    |

|   | 5.9  |                | ional Features                                   |

|   | 5.9  | 5.9.1          |                                                  |

|   |      |                | System Security                                  |

|   |      | 5.9.2<br>5.9.3 | Reset from the JTAG Side                         |

|   |      | 5.9.5          | Reset from the Chip/Processor Side               |

| 6 | Buc  | System         | ı Debug                                          |

| U | 6.1  |                | nip Buses                                        |

|   | 6.2  |                | t-Based SoC Design                               |

|   | 0.2  | 6.2.1          |                                                  |

|   | 6.3  |                | evel Integration                                 |

|   | 0.5  | 6.3.1          | e                                                |

|   |      |                | $\partial$                                       |

|   |      |                | Peripheral Bus Monitoring                        |

|   | 6.4  | 6.3.3          | Slave Monitoring                                 |

|   | 6.4  |                | al and External Alternatives for Bus Trace       |

|   | 6.5  | -              | ammable Bus Performance Monitoring               |

|   | 6.6  |                | erformance Monitoring                            |

|   | 6.7  |                | nip and Off-Chip Analysis                        |

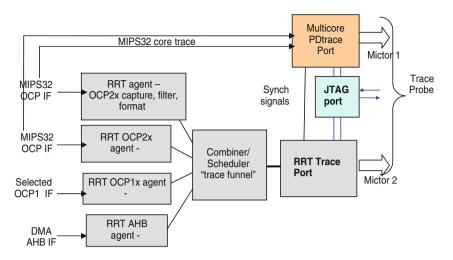

|   | 6.8  | -              | est Response Trace Bus Analysis                  |

|   |      | 6.8.1          | RRT Operations                                   |

|   |      | 6.8.2          | RRT Implementation                               |

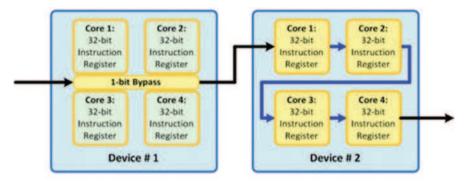

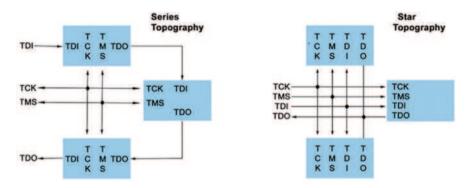

| 7  | Mult | tiprocessor Debugging                                   | 109 |

|----|------|---------------------------------------------------------|-----|

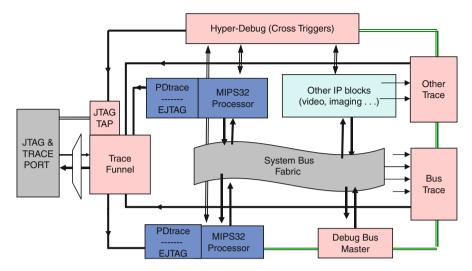

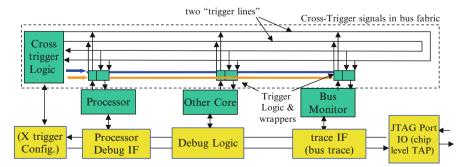

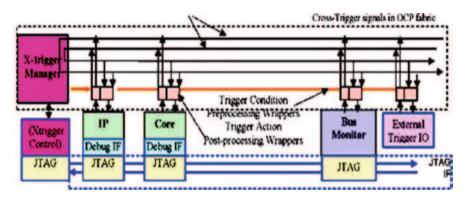

|    | 7.1  | Cross-Triggering and Global Breakpoint Control          | 110 |

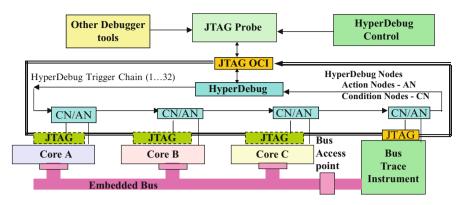

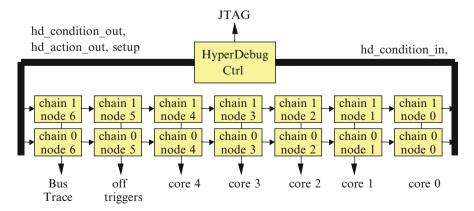

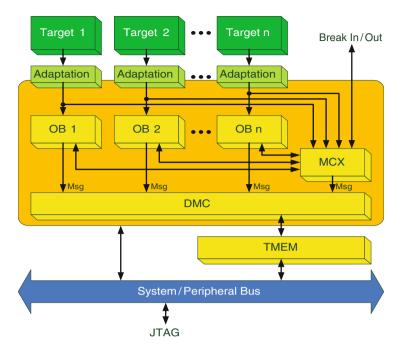

|    | 7.2  | HyperDebug Distributed Cross-Triggering                 | 110 |

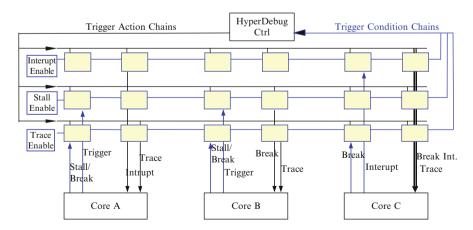

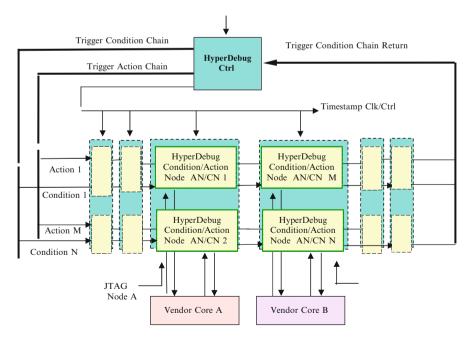

|    |      | 7.2.1 HyperDebug Controller                             | 112 |

|    |      | 7.2.2 Typical HyperDebug Implementation                 | 113 |

|    | 7.3  | Multicore Synchronization Triggering and Global Actions | 115 |

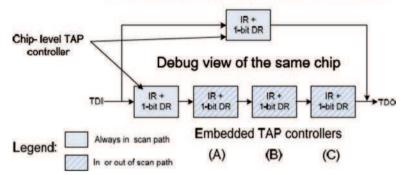

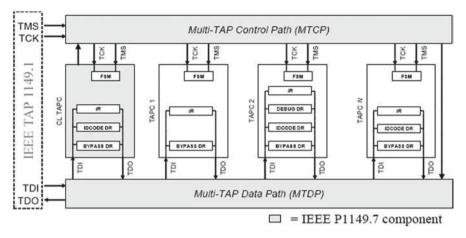

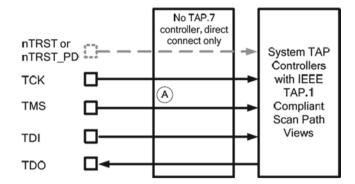

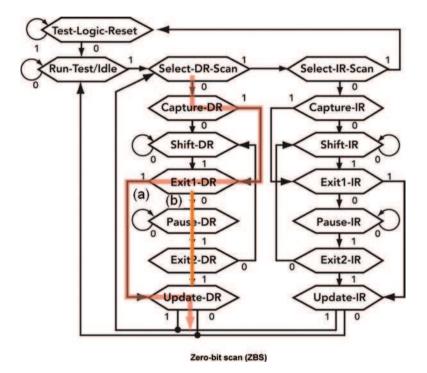

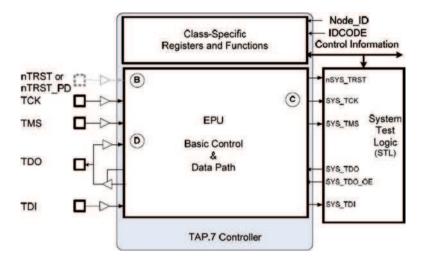

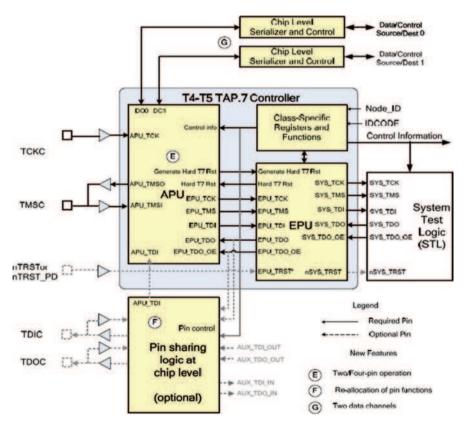

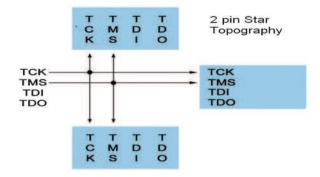

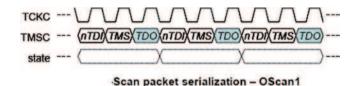

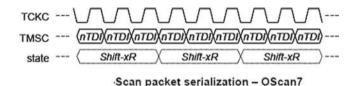

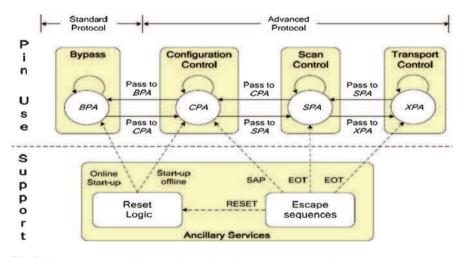

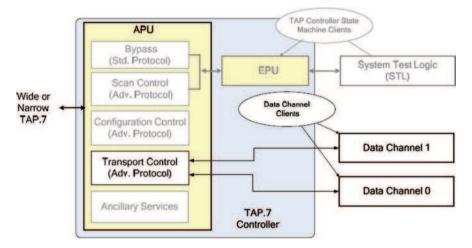

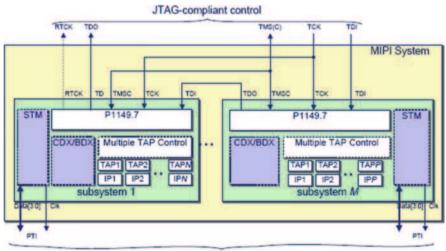

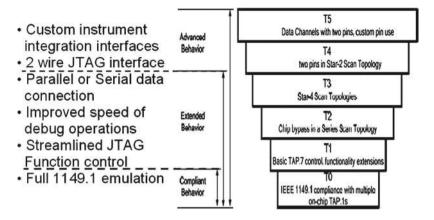

| 8  | IEEI | E 1149.7: cJTAG/aJTAG                                   | 117 |

|    | 8.1  | Test and Debug Views of 1149.7                          | 118 |

|    | 8.2  | Key T0–T5 Class Functions                               | 120 |

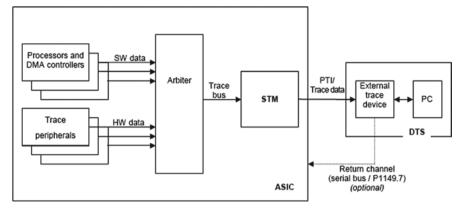

|    | 8.3  | MIPI Use of 1149.7                                      | 129 |

|    |      | 8.3.1 MIPI System Trace Module                          | 130 |

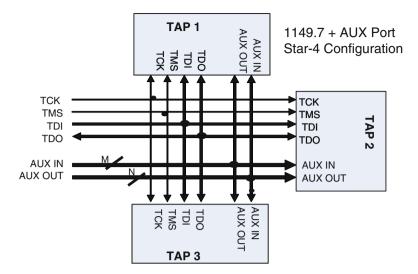

|    | 8.4  | Nexus Use of 1149.7                                     | 132 |

|    |      | 8.4.1 IEEE 1149.7/Nexus Integration                     | 134 |

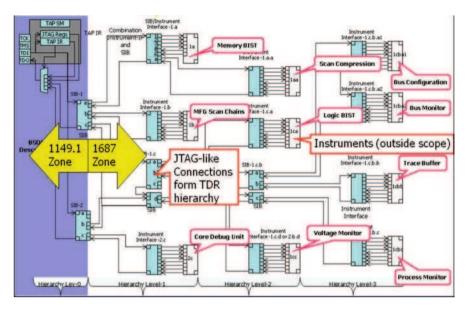

| 9  | IEEI | E P1687 – IJTAG                                         | 137 |

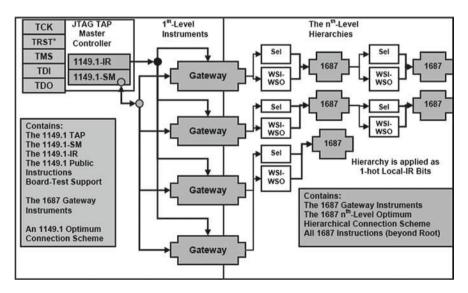

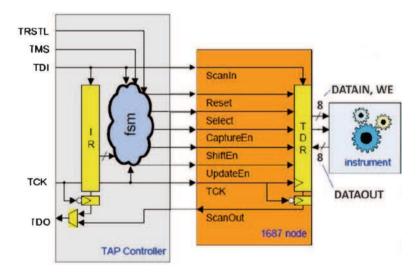

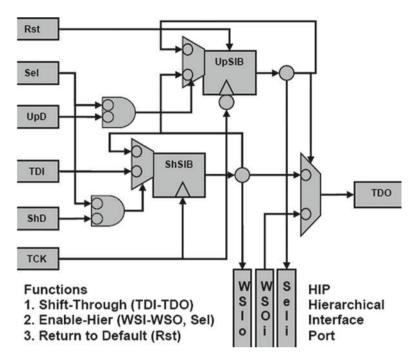

|    | 9.1  | Overlap Zones and Gateway Elements                      | 139 |

|    | 9.2  | Classes of P1687 Instruments                            | 141 |

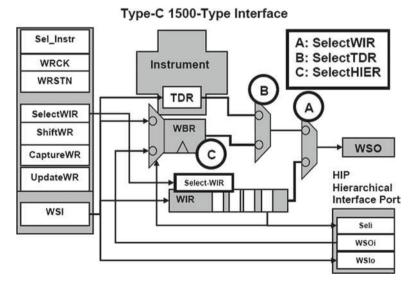

|    | 9.3  | IEEE 1500 Instruments                                   | 143 |

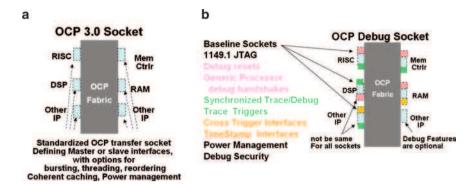

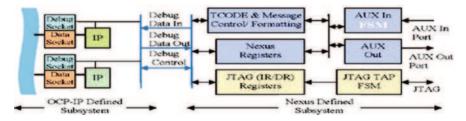

| 10 | OCF  | P IP Debug Interfaces                                   | 145 |

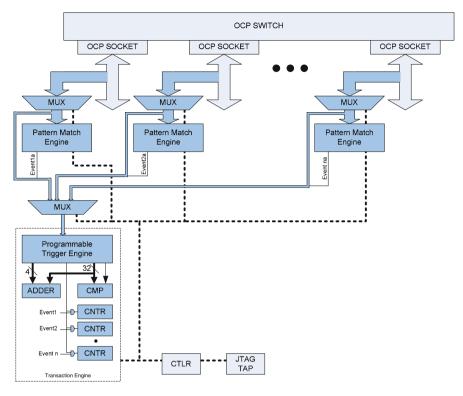

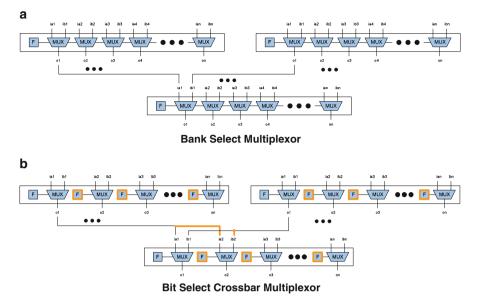

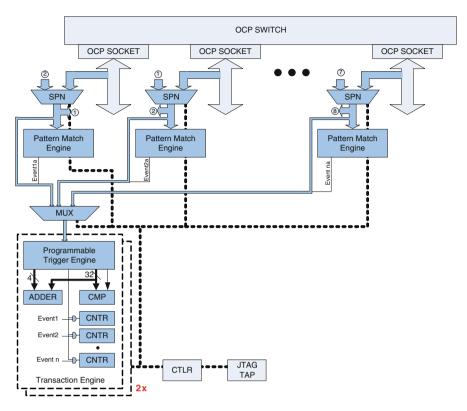

|    | 10.1 | OCP Multicore Debug                                     | 146 |

|    | 10.2 | OCP Debug Features                                      | 148 |

|    | 10.3 | Three Views of Debugging                                | 150 |

|    |      | 10.3.1 Pure Software Debugging                          | 150 |

|    |      | 10.3.2 Pure Hardware Debugging                          | 151 |

|    |      | 10.3.3 System-on-Chip Debugging                         | 151 |

|    | 10.4 |                                                         | 151 |

|    | 10.5 | Debug Socket Definitions                                | 152 |

|    |      | 10.5.1 Core Debug Socket Interfaces                     | 154 |

|    |      | 10.5.2 Cross-Triggering Socket Interfaces               | 157 |

|    |      | 10.5.3 OCP Synchronized Run Control                     | 163 |

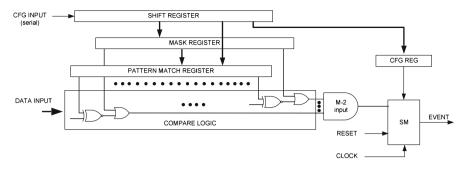

|    |      | 10.5.4 OCP Traffic-Monitoring and Trace Interfaces      | 163 |

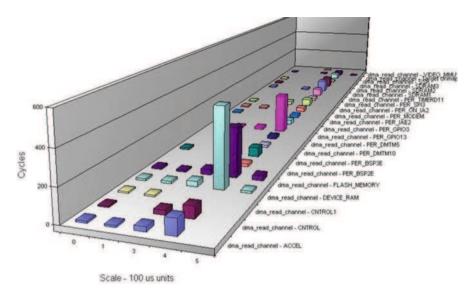

|    |      | 10.5.5 Performance Monitoring                           | 165 |

|    |      | 10.5.6 System Timestamping                              | 166 |

|    |      | 10.5.7 Power Management Monitoring                      | 166 |

|    |      | 10.5.8 Security Debug Interface                         | 167 |

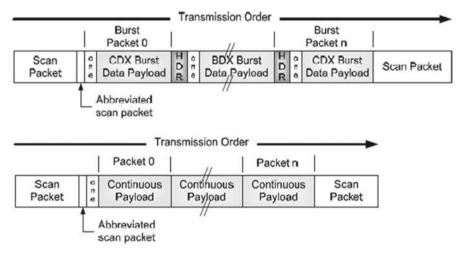

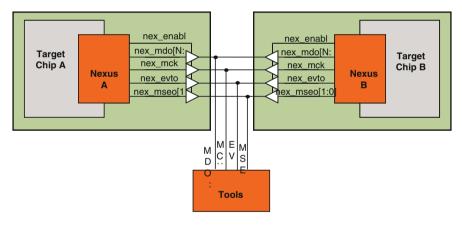

| 11 | Nexi | us IEEE 5001                                            | 169 |

|    | 11.1 | Nexus Implementation Classes                            | 171 |

|    | 11.2 | Nexus Message Architecture                              | 172 |

|    |      | 11.2.1 Nexus TCODEs                                     | 174 |

|    |      | 11.2.2 Nexus Registers                                  | 178 |

|    | 11.3 | NEXUS Interfaces                                        | 180 |

|    | 0    | 11.3.1 Nexus JTAG Access                                | 180 |

|    |      | 11.3.2 NEXUS AUX Interfaces                             | 181 |

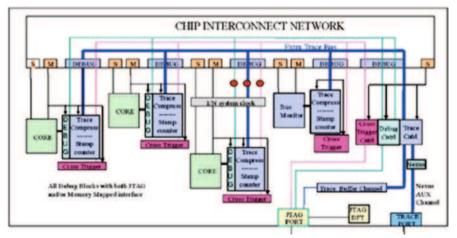

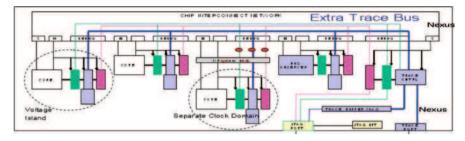

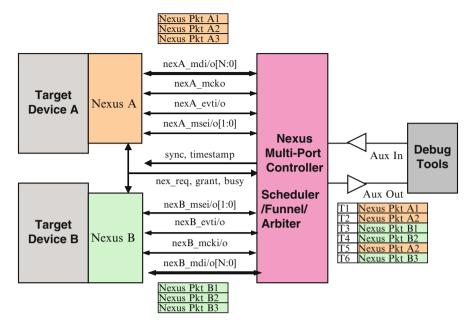

|     | 11.4   | Multicore Nexus Debug Approaches                         | 185 |

|-----|--------|----------------------------------------------------------|-----|

|     |        | 11.4.1 Input Tool-to-Target Messages                     | 187 |

|     |        | 11.4.2 Output Target-to-Tool Messages                    | 188 |

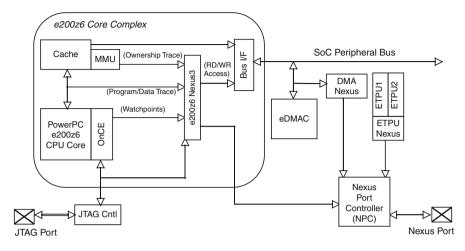

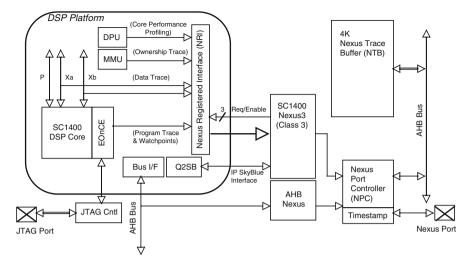

|     | 11.5   | Nexus Product Implementations                            | 189 |

|     | 11.6   | Summary                                                  | 193 |

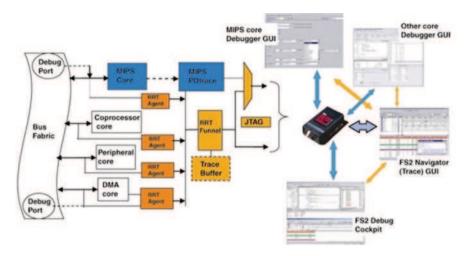

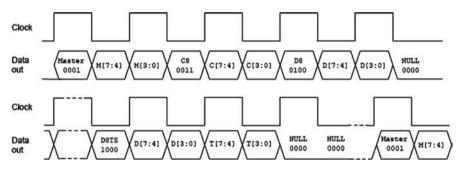

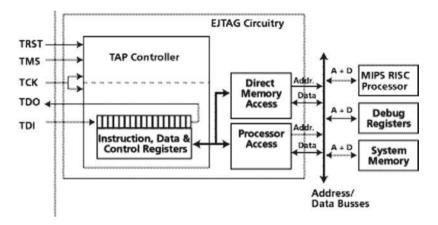

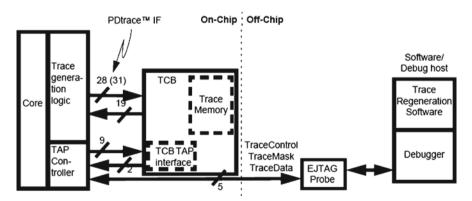

| 12  | MIPS   | S EJTAG                                                  | 195 |

|     | 12.1   | EJTAG Instructions and Registers                         | 197 |

|     | 12.2   | PC Sampling                                              | 199 |

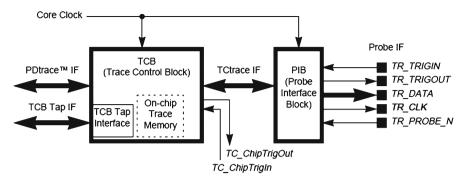

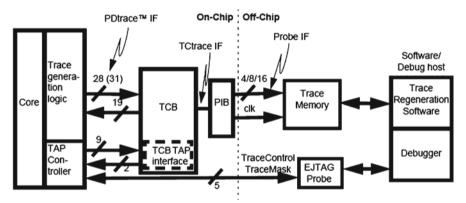

|     | 12.3   | MIPS PDtrace <sup>TM</sup>                               | 199 |

|     |        | 12.3.1 Trace Output Formats                              | 200 |

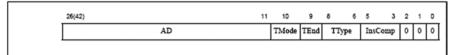

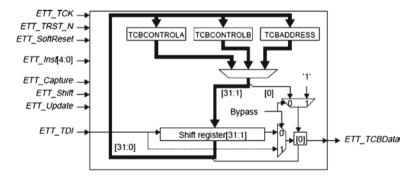

|     |        | 12.3.2 Trace Control Block Registers                     | 204 |

|     | 12.4   | TCB Trigger Logic Overview                               | 206 |

|     | 12.5   | PDtrace External Interface                               | 207 |

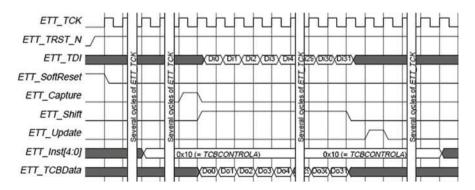

|     | 12.6   | TCtrace IF                                               | 209 |

|     | 12.7   | PDTRACE Operations                                       | 210 |

| 13  | ARM    | [ ETM                                                    | 213 |

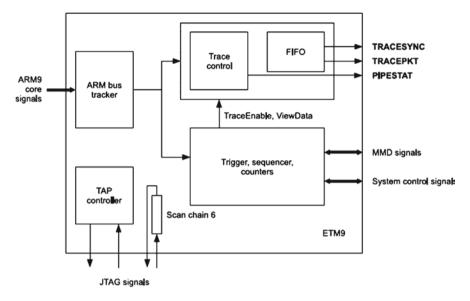

|     | 13.1   | ETM Signals                                              | 213 |

|     |        | 13.1.1 External Signals                                  | 214 |

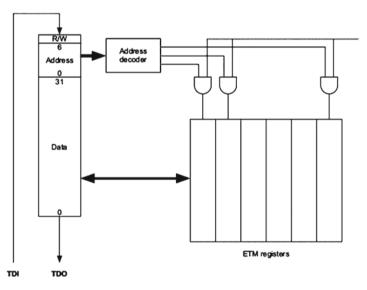

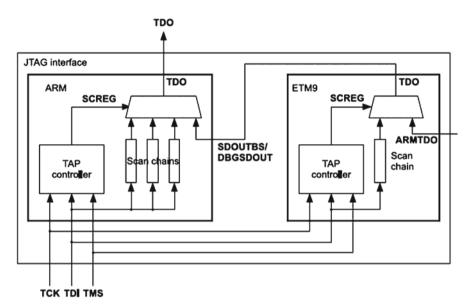

|     | 13.2   | ETM9 Registers                                           | 216 |

|     | 13.3   | Trace Interface                                          | 218 |

| 14  | Infine | on Multicore Debug Solution                              | 219 |

|     | 14.1   | MCDS Trace Protocol Definition                           | 221 |

|     |        | 14.1.1 Data Trace                                        | 223 |

|     | 14.2   | Debug Transactor: RUN Control Bus Master                 | 224 |

|     | 14.3   | MCDS Run Control: On-Chip Debug Support                  | 225 |

|     |        | 14.3.1 BCU Level 1 (Bus-Observer Unit on the System Bus) | 227 |

|     |        | 14.3.2 Concurrent Debugging in Level 3 MCDS              |     |

|     |        | (Two-Channel Tracing)                                    | 228 |

|     |        | 14.3.3 Debug Interface (Cerberus)                        |     |

|     |        | (Debug Bus-Transactor Module)                            | 228 |

|     | 14.4   | RW Mode and Communication Mode                           | 228 |

|     | 14.5   | Multicore Break Switch                                   | 229 |

| 15  | ЕЈТА   | G and Trace in Toshiba TX Cores                          | 231 |

|     | 15.1   | Processor Access Overview                                | 232 |

|     | 15.2   | Toshiba EJTAG Instructions and Registers                 | 233 |

|     | 15.3   | Debug Exceptions                                         | 235 |

|     | 15.4   | Processor Debug Instructions and CP0 Registers           | 235 |

|     | 15.5   | Break Functions                                          | 237 |

|     | 15.6   | Output by PC Trace                                       | 238 |

| Inc | lex    |                                                          | 241 |

## Chapter 1 Introduction

With each new generation of digital system-on-chip (SoC) technology, the level of integration, functionality, and complexity provided on a single chip has increased significantly. A problem that goes hand in hand with this increased amount of integration and functionality is that analysis tasks and difficulty associated with getting a design working and integrated increase at least proportionally to the size and complexity of the chip. Over a range of SoC types – ASIC, ASSP, system FPGAs, or a dozen other variants and platforms – there is a common need for better debug solutions. As more processing elements, features, and functions are simultaneously being embedded in the silicon, the emerging level of embedded complexity outstrips the capability of stand-alone logic analyzer-, debugger-, and emulator-based diagnostic tools for embedded designs. Although these tools allow the capture of data off the system data bus, they work only as long as every access (read and/or write) occurs over the external data bus. This issue points to a growing gap in terms of effectively being able to provide the necessary controllability and, in particular, the visibility of the internal operations of a complex system.

## 1.1 The Need for On-Chip Debug

The need for improved methods of observing and analyzing embedded processor and SoC operation has increased at a pace at least proportional to the explosive growth in electronic system designs and new intellectual property (IP) cores that populate them. The analysis side of the SoC world is then forced into a constant process of catching up to the designer's ability to add cores and integrate new resources on chips. With an ever-shortening development cycle, and often several generations of products produced in parallel or rapid succession, standardized embedded tools and capabilities that enable quick analysis and debug of the embedded IP are a critical factor in keeping SoC verification a manageable part of the process.

Most engineers involved in complex design will agree that verification and validation have become a critical stumbling blocks in the development and release of new devices. This is now equally true of the software components of those systems as well as the hardware. Better ways to address the verification and analysis of complex SoC designs, and corresponding new methodologies, tools, and capabilities, are needed to get the job done at different phases of the design and development cycle.

For brevity and convenience, we adopt some general definitions in this book. Analysis relating to pre-silicon design stages, in particular Electronic Design Automation (EDA) tools and methods and their use in RTL (register transfer level) and ESL (electronic system level), are collectively referred to as *verification*. Analysis relating to in-silicon analysis (sometimes referred to as post-silicon analysis), and in particular, tasks related to the use of on-chip instrumentation, are collectively referred to a *debug* (Fig. 1.1).

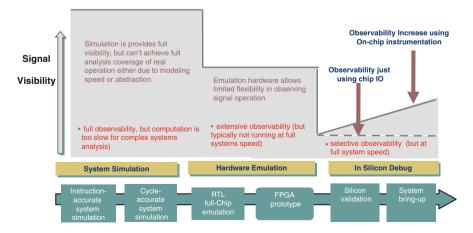

In-silicon debug provides complementary alternative methods to digital simulation as a means of viewing and analyzing embedded signals. Simulation, although a critical factor in verification, is not a total verification solution for embedded SoC. Simulation alone cannot address all the facets and nuances of physical hardware. In addition, it is not realistic to simulate large multiprocessor architectures for the extremely large numbers of cycles required to evaluate the software-specific aspects of system operation and real-world system performance. Although accelerated simulation, co-simulation, and emulation environments provide a stop-gap method of improving the simulation capability in observing system performance, these often introduce costs and complexities beyond the resources of many projects. On-chip instrumentation and debug approaches have evolved as a low-cost and efficient alternative of increasing system visibility which focus on the actual final hardware product rather than its model.

System-on-chip debug, like most verification philosophies, seeks to maximize test functionality and ease of verification while reducing the overall end-user cost. There is a constant trade-off that must be made on resources dedicated to system analysis and debug versus the system cost of including these features. The value of debug is mainly perceived during the development cycle (hardware or software), where operational questions and integration issues for the key processing blocks are unresolved. After the system is "fully debugged," the hardware investment in debug capabilities becomes much more application-focused. In the past, this often led to the removal of debug features (and associated gates and pins) in order to gain a small reduction in die size. These trade-offs have shifted in recent years by dramatic

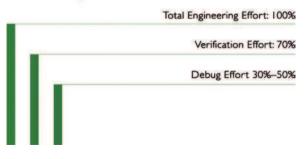

#### Cost of Debug

Fig. 1.1 The costs of debug

increases in complexity; gate availability and overall speed of system operation have changed the norm in chip design from a "core and gate-limited" to a "pin and IO-limited" focus. The debug question has migrated from how many gates can be spent on debug to an ease-of-use and bandwidth issue: How much of the system resources and IO is needed to debug the system successfully?

## **1.2** Instrument- (\*\*in-silicon) and EDA- (Presilicon) Based Verification

EDA (electronic design automation) flows that include the tools and methods for modeling, simulation, and analysis of SoC receive much attention and have evolved a variety of solutions to address verification needs for pre-silicon design, from diverse simulation-based methodologies to emerging formal and assertion-based methods and, increasingly, system-level abstraction. This verification flow largely works under the assumption that the verification effort is essentially completed when the design files are handed off to the foundry for fabrication. Anyone who has been involved in the in-silicon debug cycle, loosely defined as everything that must be verified and integrated from the time silicon is received back from the foundry to the point of being ready for a production release, knows that this is far from the case.

Although improved tools and rigor in pre-silicon verification are essential and play a important role in getting to working first-pass silicon, the use of in-silicon debug has received much less attention. However, as we discuss, in-silicon debug plays an essential role in addressing full-speed testing in real environments. It allows for more exacting analysis of interactions too subtle for models in simulation to address, such as unforeseen environmental variables, external constraints, etc. Analysis, and bug-fixing, including resolving hardware/software issues that cannot easily be addressed at speed other than by analysis of the in-silicon hardware platform itself.

A design team, in addition to having to address the issues of verification and model reuse at different stages of the design flow, typically must also develop debug flows to address both hardware prototypes and in-silicon verification of both the hardware and software in the system when getting chips to market.

With larger and more complex chip architectures and designs, supporting larger and more complex software applications, the penalties of discontinuities between pre-silicon verification and in-silicon debug are increasing. More consistent and common environments reduces costs and trade-offs of getting silicon not just designed but working and out the door to the end customers (Fig. 1.2).

The cost of debug in the development of complex SoC systems has not received the level of analysis that other parts of the methodology, such as EDA tools, have, but it is pragmatically known to be a significant portion of the overall cost of releasing new systems. EDA tools and flows have focused on evolving a variety of solutions to address pre-silicon verification, with diverse simulation-based methodologies that leverage high-level verification languages and formal and assertion-based

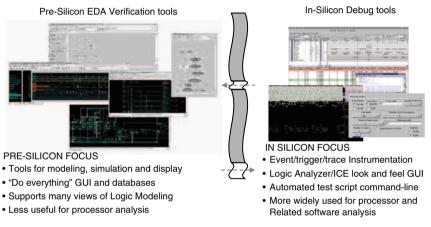

Fig. 1.2 Debug duration over a project

Fig. 1.3 Pre-silicon vs. in-silicon analysis

methods to verify at increasing levels of system-level abstraction. As we discuss, these are complementary to instrumentation-based debug (Fig. 1.3).

Debug typically relies on a toolbox of methods, instrumentation IP, and tools to support analysis of hardware-based systems and their software applications. Debug includes combinations of software tool methods (which can be thought of as "print" statements and breakpoints) and hardware methods (monitoring of events using Instrumentation IP to capture information for display and analysis).

Successful in-silicon analysis of next-generation systems will rely as much on system-level thinking in leveraging and reuse of verification efforts done during the pre-silicon verification cycle as on specific debug instrumentation approaches in providing closure to address the SoC verification and analysis problem (Fig. 1.4).

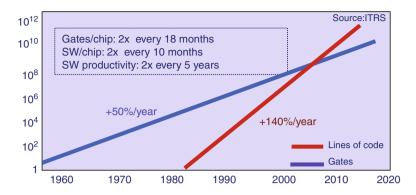

Complex architectures have spurred the requirement for new methodologies and capabilities to address the analysis and instrumentation needs of these architectures. We are arguably moving toward a new inflection point of requiring a sea change in debug assumptions, based on changing design methodologies that widely embrace

Fig. 1.4 Growth of hardware vs. software complexity

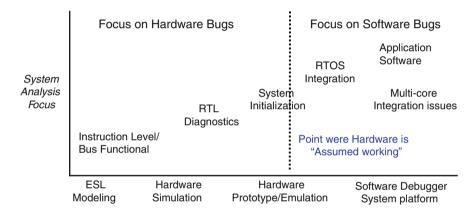

Fig. 1.5 Verification abstraction vs. debug tasks

multiprocessor architectures and their associated software development and integration issues, dramatically increased gate count availability, and increased complexity in all the diverse interfaces and peripherals making up a SoC device.

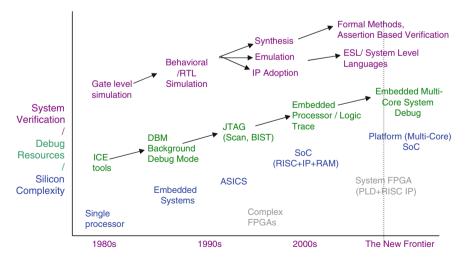

Looking historically at the major inflection points for EDA verification, debug tools, and silicon complexity in Fig. 1.5, it is interesting to note the interwoven relationship between these different but closely related technologies that are central to the progress of many aspects of the evolution of leading-edge electronics technology. The emergence of new EDA tools is both a driver and a result of new and increasingly complex levels of systems architectures. Similarly, complexities in architectures have spurred the requirement for new debug methodologies and capabilities to address the needs of these architectures. We are arguably in the middle or moving toward a new inflection point, based on changing design methodologies that widely embrace multiprocessor architectures, dramatically increased gate count availability, and increased complexity in all the diverse interfaces and peripherals making up an emerging SoC device.

This problem can be seen on several fronts, most notably the efficiency of the debug processes used for in-silicon validation. The need for new debug capabilities has evolved along with the state of embedded processor design. In Circuit Emulation (ICE) was developed to support debug of processor-based parts with minimal additional integration, but by emulating operations, rather than executing them normally. The adoption of IEEE 1149.1 aka JTAG (discussed in Chapter 3) popularized the use of a debug port that allows low overhead access and provides embedded developers with a range of potential capabilities for debugging, but with a limited bandwidth never designed to support any real-time analysis. Instrumentation adds to the debug port philosophy of JTAG by extending the bandwidth capabilities to address debug of one or multiple cores, internal buses, complex internal peripherals, and high-speed data traffic found at SoC levels of complexity (Fig. 1.6).

Looking at on-chip instrumentation in the proper context, it is useful to examine more traditional embedded systems debug. The ever-increasing trend in the embedded system development is the evolution of products that incorporate diverse processing resources. Over the last decade the embedded systems market has seen a proliferation of new processor architectures (8-bit MCUs, DSPs, RISC, application-specific co-processors, etc.) provided as IP and focused on SoC integration. Historically, development of each generation of processor IP is accompanied by supporting debug tools. Many currently available cores provide some form of JTAG interface for run control and debug functions. Rapidly emerging adjuncts to JTAG are supporting trace capabilities, usually in the form of a trace port such as the ARM's ETM (embedded trace module) and MIPS' EJTAG + TCB (trace control block) which allow the benefits of trace for more productive system debug.

Fig. 1.6 SoC verification, debug, and complexity

## **1.3 SoC Debug Requirements**

Analysis, at all levels of implementation, relies on methods of configuration, control, and data capture. Control refers to the manipulation of a system, outside of its normal execution, for the purpose of debug, analysis, and verification. Control can be influenced at any time during execution of the system, so it is a "real time" method in this respect. A simple control example might be to execute a single instruction, but more typically it may involve execution of a range or duration of operations tied to an initializing event and a concluding event. Configuration is actually nothing more than a special case of control, referring to the initial setup of a system to a known state. In some cases, this configuration may be part of the normal execution of a system (for instance, the default settings used after reset). Examples include setting of mode or configuration bits for cores, arbitration states for buses, and loading of data into specific locations in the system to (re)produce a system state for a particular operation or sequence of interest. Data capture refers to the export and storing of some system information occurring at a user-defined time. A simple example would be capture of a register value occurring at some triggering event in the system. Both ESL and instrumentation tools have similar requirements at a SoC level in how to address these tasks, and ideally would rely on standardized mechanisms for implementing them.

Most SoC include a programmable processor and in many cases, multiple processors as the core functionality. They also consist of infrastructure, either in terms of dedicated coprocessors or other logic and a communications infrastructure to allow both intercore and chip-to-outside world communications. The analysis of processors and the rest of a complex chip follow different paths and have traditionally relied on different approaches to verification and debug. Digital hardware design, on the contrary, typically relies on a synthesizable RTL model that assumes implicit clock-cycle timing during simulation. RTL has been the primary debug tool for configuration, control, and data capture of dedicated logic-based portions of the architecture, with hardware support based on either on- or off-chip logic analysis, although with the advent of synthesizable ESL language subsets and methodologies, these functions may be absorbed into the ESL of design flow. In either case, merging simulation and synthesis approaches have been proven in countless designs over the last 15 years, because logic-based functions can typically be analyzed over the range of fewer than a million clocks cycles, which is manageable for both simulation and logic analysis. Conversely, processor architectures, while relying on synthesis for implementation, are less successful in using RTL and logic analysis approaches due to the length of time required for execution of complex algorithms, and complexities of hardware and software interactions that are not amenable to RTL simulation and related approaches.

Simulation is always an important part of the development flow; just as important is the ability to analyze hardware during prototyping and system verification and, increasingly, on the final products themselves. Although the focus of much of the verification world has been on simulation-based verification technologies, instrumentation provides a counterpoint that focuses on the physical hardware. The problem in analyzing embedded information (on-chip processors and buses) in hardware in many cases devolves to a visibility problem – *it is difficult to fix problems that you cannot see.* The test community traditionally has referred to this problem in terms of levels of controllability and observability of a design. It is important to note that this analysis visibility cannot be adequately addressed by traditional on-chip test methods such as JTAG scan, and that the analysis and instrumentation problem, while overlapping with test issues and techniques in many cases, is fundamentally different.

One method of working around these analysis bottlenecks in simulation is to build hardware emulators or prototypes of (usually field-programmable) hardware implementations of the digital and possibly analog portions of a system. These hardware systems will run orders of magnitude faster than simulations, making running software applications feasible, but they are still typically at least an order of magnitude slower than the final silicon system, which results in both false positive (errors in the emulator that are not in silicon, due to differences in timing paths, synchronization of subsystems, etc.) and negative problems (found in the silicon that are not seen in the hardware, due to lower speed) and in many cases still not being able to run the system application at a speed compatible with the final system requirements.

Modern silicon system-level implementation typically proceeds through a design life cycle of increasing detail and refinement that must include modeling, verification, and analysis of hardware and software components. Software development has typically relied on analysis with a hardware target using ISS (instrument set simulation) models where timing is abstracted or nonexistent. These ISS models can vary significantly from vendor to vendor, which inhibits general methods for model compatibility between different core models and their integration with RTL simulation. RTL is synthesized into gate-level implementations that map into hardware and become a deliverable product, along with software that is either embedded as part of the product or added at a later stage by customers. More complex modeling is complicated in modern devices by several factors.

• Preferred software development environments may vary significantly for different processors. Although hardware development tools have developed in parallel but largely independent of different ways to implement a design (programmable logic, ASIC, ASSPs, and their related digital IPs), a limited number of common representations (gate-level, RTL, hardware itself) allow for straightforward integration; software development tools and models are developed by and in conjunction with processor and software IP vendors and have more limited commonality, for modeling and verification of multiple processors or even different processor targets running a common algorithm. The problem is even more acute for debug-related tasks, where different debuggers have different features. More commonality is found in use of GNU debuggers (GDB), versions of which have been developed by and for many processor architectures. GDB and variants are commonly used as a user interface for configuration, control, and data capture of software architectures during ISS, emulation, and in-silicon debug.

#### 1.3 SoC Debug Requirements

- For multicore devices, different suppliers often provide subsystems, in terms of hardware blocks, each developed with its own assumptions and incompatibilities in ISS modeling. Due to a lack of standardized sequential timing models in software languages used to develop ISS models (C, C++), new modeling approaches that include understanding of sequential and concurrent operations are needed to model systems that include multiple processors (running under different clocking and instruction flows) and processors and their supporting blocks (buses, peripherals, interfaces, etc.) that are typically modeled at RTL or other hardware methods.

- These may be in simulated SystemC, an ESL developed to support concurrent modeling of systems having processor architectures and software and supporting hardware blocks. SystemC combines compatibility with C++ as a class library with a set of corresponding modeling and simulation features similar to those used in RTL.

- Real device speeds are higher (typically by orders of magnitude) than that achievable by simulation. As a result, system modeling relies on abstractions and simplifications to increase simulation performance to a point where it is feasible to run software applications over the multimillion cycles needed to verify operation. Complexity and performance are further impacted if different subsystems are asynchronous or have other analysis-intensive incompatibilities. The lowest risk and often the simplest solution to real-time analysis is to use the actual hardware; however, even with added instrumentation, there are significant limitations in observability and controllability of a design as discussed earlier, so while hardware is a good verification platform, it is limited as an analysis platform. Simulation does not have the same limitations, because all signals are visible. One of the more important simulation efforts of SystemC is related to trade-offs between speed and visibility with TLMs (transaction-level models) that, by abstracting away noncritical functionality or timing, can simulate orders of magnitude faster than cycle-timed RTL models while being integrated with RTL models. Integration between TLM and RTL blocks in a simulation, while providing more resolution of signal analysis (at the expense of increased simulation timing), is still an area of active development.

- Complicating simulation analysis further is the modeling of the complex environments in which the device must operate. These can include the need for modeling a complex stimulus with both signal and noise characteristics, human interfaces, and analog subsystems that have their own modeling and analysis complexities, which are incompatible with large-system digital analysis and have their own traditional (frequency-domain-based) analysis methods. The effective integration of mixed analog and digital systems remains an open area of refinement in EDA analysis methods and in hardware-based debug and analysis; test features within ESL tools include the ability to model many analog and system characteristics as part of verification blocks (test benches) as well as the ability to integrate models from verification-level languages (Specman, Vera, Testbuilder, etc.) that have been developed and are being incorporated into new versions of RTL languages such as SystemVerilog.

Choosing among many design trade-off efforts is a tiered approach of modeling refinement and migration from ESL, to more detailed models, to hard platforms, to final silicon. As the modeling and analysis move from simulation to hardware, another factor to consider is an accompanying loss of visibility and access in the internal signal operation. In simulation, all signals, variables, and modeling parameters are available for viewing, and in most cases, for direct modification, providing a rich analysis environment, regardless of other limitations. Hardware, whether in emulation system or in final silicon, has limitations for debug purposes on the amount of visibility and control of embedded signals available at the system IO pins (Fig. 1.7). In this hardware environment, instrumentation significantly increases the amount of real-time visibility and control of the design at the cost of adding analysis blocks to a design. In many systems, instruments provide the most straightforward means for embedded trace or to directly configure, take direct control, or inject stimulus into a subsystem, as needed to resolve system level bugs.

A typical debug flow consists of several diverse tasks, both independent and interdependent, required to achieve a level of comfort in verifying an in-silicon product. With many devices consisting of both processor and fixed IP, along with related software and firmware, the verification concern is not only *operating as designed*, but also *performing as required* in its natural environment. For many products, this may include being exercised and verified in operational scenarios that were not foreseen or feasible to include during the pre-silicon verification cycle.

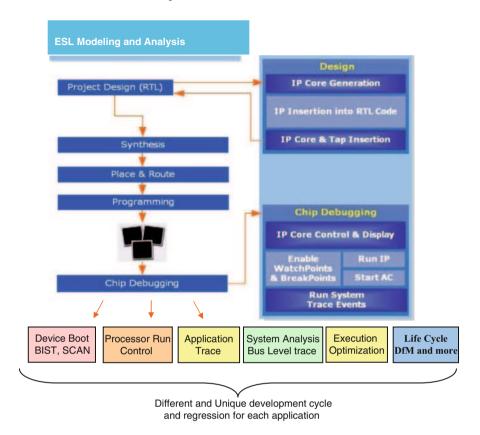

In recent years, in-system debug has taken on a specialization of its own, referred to in different contexts as on-chip instrumentation, design for debug (DfD), and the like. A flow of debug and analysis tasks that can be provided using instrumentation consists of several diverse independent and interdependent activities required to address different aspects of verifying an in-silicon product. DfD methodologies are still emerging areas of investigation. DfD differs from DFT and related approaches in the level of customization required to support specific debug requirements of an architecture or system (Fig. 1.8).

Fig. 1.7 Observability during design flow stages

Fig. 1.8 Debug activities in the in-silicon verification

The availability of gates and on-chip resources of modern SoC allows for more innovative approaches to systems debug and embedded logic analysis by allowing dedicated debug subsystems to be created, with minimal or even negligible impact on the overall chip size. Dedicated debug subsystems would effectively extract and analyze signals and operations within and between deeply embedded processor subsystems of a complex design.

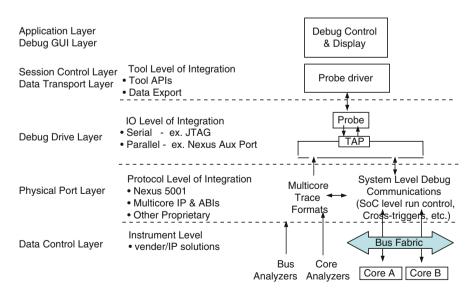

## 1.4 Instrumentation-Based Debug Infrastructure

A debug reference model shows a properly designed debug environment; different debug systems may be created in a modular fashion. Although a majority of the layers are software implemented in the debugger host, the two key instrumentation layers (1 and 2) in hardware address different instrument blocks that operate largely independently. Layer 1 I defines the port interface and its logic. Layer 2 defines the instrument function and operation. This separation allows the configuration of instrument related registers and decode of debug instructions can be treated largely independent of the physical layer, be it JTAG or any other interface (Table 1.1).

| Implementation layer                   | Typical tasks                                                                      | Location |

|----------------------------------------|------------------------------------------------------------------------------------|----------|

| 1. Physical port layer                 | Debug TAP IO, chain, and debug block wires                                         | Target   |

|                                        | Debug TAP FSM (schematic-level connection)                                         |          |

| 2. Data control layer                  | Low-level debug instructions<br>and registers                                      | Target   |

|                                        | Extended debug instructions,<br>optional debug block registers                     |          |

| 3. Debug driver layer                  | Debugger protocol, clocking<br>(probe-specific API)                                | Probe    |

| 4. Data transport layer                | APIs debug command sets,<br>run control API                                        | Host PC  |

| 5. Session control layer<br>(Optional) | Device connection setup and parameters<br>Remote debug server<br>(e.g., GDBserver) | Host/PC  |

| 6. Debug GUI layer                     | Debugger UI, GDB commands, trace viewers<br>(e.g., VCD)                            | Host/PC  |

|                                        | Set/observe breakpoints, watchpoints,<br>and event triggers                        |          |

|                                        | Run control go/halt/single step                                                    |          |

| 7. Application layer<br>(Optional)     | Eclipse, other IDE, global (Multi-tool) data management                            | Host/PC  |

Table 1.1

Open debug interconnect model

The integration of deeply embedded memory and embedded buses, along with limited IO for such embedded subsystems available for test purposes, limits the visibility of the embedded processors in SoC operation and dataflow.

In formal testability terms, multicore embedded systems present an asymmetrical functional test problem. Their controllability is high, because the systems are dominated by programmable processor cores. The observability is low, however, in terms of both critical signals that are directly available and the amount of embedded logic and internal signals as a ratio of the available IO in which to observe them. The addition of dedicated resources and structures that support functional analysis is needed to increase system observability. This requires a hierarchical focus to the issue of system analysis, starting at the individual core level of debug instrumentation and resources and increasing to a more system-centric diagnostic capability to facilitate increased observability. Although embedded debug instrumentation approaches are becoming increasingly common at the core level, system-level diagnostics and analysis at the multicore level has been a largely underaddressed and unresolved area of focus in complex embedded systems.

These "deep encapsulations" of key system functions, along with higher internal bus speeds, make traditional debug techniques, such as emulators, so limiting that they have forced the evolution to new logic analysis and debug approaches such as on-chip instrumentation.

Based on the shortfalls in applying current debug approaches to complex SoCs, the debug of structured SoC and related single-chip systems containing many embedded processor cores requires new system-level instrumentation approaches. The integration and debug of multiple cores, combined with an increasing ratio of overall gates versus package IO, makes an increasingly dominant portion of a system design "deeply embedded," so that only a minimal amount of data is needed for analysis to be made available in real time at the chips pins. These deeply embedded systems introduce new analysis problems, due to the interaction and communications of multiple cores, in addition to the more traditional debug issues associated with single-processor systems. The multicore debug requirement implicit for SoC requires new capabilities that exceed what can be addressed by traditional in-circuit emulation and logic analyzer capabilities, and by JTAG and BDM resources used in single-processor architectures. Whereas a JTAG or BDM can provide a snapshot of a piece of the system, the dynamics and interaction of multiple processors require a more dynamic and robust means of providing diagnostic information necessary to the designer and integrator (Fig. 1.9).

On-chip instrumentation is implemented as an embedded block that provides external visibility and access of the "inner workings" of processor and system architectures. When properly implemented, it provides a real-time "peephole" into the operations of key internal blocks that cannot otherwise be accessed in sufficient granularity on a real-time basis. The real-time visibility and monitoring of key interfaces and buses are increasingly crucial to understanding the dynamics of the operation of system architectures. As a general rule, debug visibility becomes

Fig. 1.9 Open debug model and components

increasingly problematic for highly integrated chips, which have extensive on-chip memory and caches, peripherals, and a range of on-chip buses. The key control and bus signals of interest in a deeply embedded system are often not externally addressable by the physical pins of the device and therefore are inaccessible to traditional instrumentation. This accessibility issue inhibits verifying silicon operation, introducing many hardware and software integration roadblocks, because the design team must address how traditional debug tools can be interfaced to work properly in SoC designs.

The value of instrumentation is, directly and indirectly, a function of several factors, including the instrument resources inserted on chip, the cost of the instrumented code and logic to the overall system, the overall applicability of the instrumentation, and the level of software and tool support available to make use of the instrumentation. In looking at the different types of on-chip instrumentation, they break out into roughly four major types of functions.

- Core Debug most processor IP includes some debug blocks that simplify run control (e.g., go, halt, single step,) and optionally provide instruction and data trace. The core-level integrated debug blocks and debugger features can differ significantly from processor to processor.

- Logic Debug providing more generic control and trace, logic debug IP essentially allows the embedding of a logic analyzer interface and part of a logic analyzer itself on the chip to provide visibility (and sometimes control) into the IP operation by allowing data capture of deeply embedded signals.

- Bus Debug embedded bus fabrics provide data movement between cores and present additional challenges for system debug due to complex interactions of on-chip bus fabrics and the sheer amount of data transferred over bus channels.

- System Cross Triggering for multicore systems, controlling and monitoring events from different cores is required to synchronize and manage the complexity of multicore debug. Cross-triggering instrumentation provides one flexible means of controlling and coordinating the concurrent operations of several cores and IP, even when running in different domains.

The number of specialized and customized instrumentation blocks to address analysis such as system or core performance analysis is even larger. As important as the instrumentation function is its integration and communication with other tools and user interfaces. Many instrumentation systems use JTAG as a primary debug interface. Others use more specialized and higher-performing debug access ports; both these types of interface are discussed in detail in subsequent chapters. The ability to seamlessly interface different instrumentation blocks to different debug tools requires a sophisticated hardware (probe) and instrumentation software environment that supports the requirement to service diverse and concurrent debug requests.

These tools, to a large extent, only address the specifics of the processor IP and do not address or facilitate the system application in which the IP is used. Although the processors become increasing deeply embedded, traditional development tools for system debug applications can not provide nonintrusive visibility into the highly integrated embedded processor. Applied to processor in-circuit emulators and their derivatives such as JTAG hardware debugging, the system must be placed in special debug modes or halted before being it can probe processor registers or read/write to the embedded memory. In many cases, this interruption of the steady-state performance of the system introduces (time) intrusive elements into the system operation that can complicate or invalidate the data or operations being observed. This problem grows proportionally to the ever-increasing frequency and complexity of high-performance embedded processors.

## Chapter 2 On-Chip Instrumentation Components

In this chapter we examine a typical on-chip instrumentation environment and discuss some of the individual instruments used for system debug, their typical features, and their integration, both with each other and the systems being analyzed.

## 2.1 Trace and Event Triggering

Concepts of the tracing of data as it moves through the application or system are central to most other instrumentation capabilities. To address different debug requirements, instrumentation blocks must support different implementations of trace collection. Typical requirements include the ability to trace in cycle, branch, and timer modes. Cycle mode collects all bus cycles generated by the core(s). Branch mode collects all execution path changes, sometimes called branch trace messages. Timer trace mode records a frame with a timestamp each time an event is satisfied, providing basic performance analysis measurements.

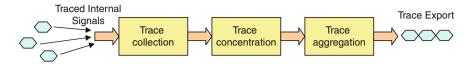

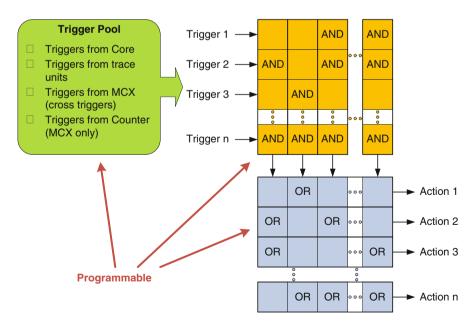

Event recognition is widely used in conjunction with trace to capture information on events and operations in the SoC. Trace data values can be monitored and compared to provide real-time triggers to control event actions such as breakpoints and trace collection. Event recognizers can simultaneously look for bus address, data, and control values and be programmed to trigger on specific values or sequences such as address regions and data read or write cycle types. The event recognizers can control enable or disable of breakpoints and trace collection (Fig. 2.1).

Data tracing based on recognizable events opens doors to new capabilities in real-time SoC analysis. The data trace mode provides real-time information about the status and data of a system's internal signals, including, for example, analysis of cache performance and internal memory and data transfer operations that cannot otherwise effectively be extracted from a system. In-line or postprocessing trace information allows for analysis of data flow performance or measurement of system characteristics such as bus availability or cache hit/misses, which require long-term steady-state (measured over many cycles) system information. Additional detection of events in traced data allows the development environment to flag specific features in the trace data as it flows through the application.

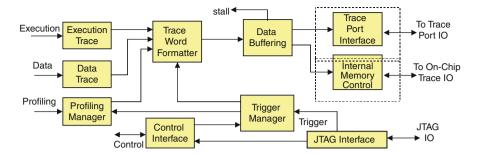

Fig. 2.1 On-chip trace formatting and export instrumentation

Fig. 2.2 Instrumented event recognition

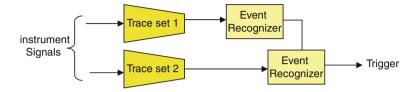

As an example of a complex instrument event recognizer feature, four event recognizers can be combined in a 1–2 and 3–4 arrangement to produce two complex events. In this arrangement, the complex events can be configured so that first event of the event pair must be satisfied before the second event is enabled (Fig. 2.2).

## 2.2 External Interfaces for On-Chip Instrumentation

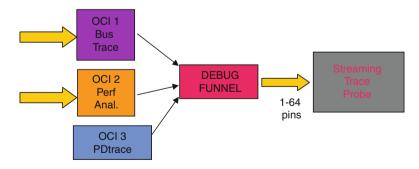

JTAG pin interfaces are the default interfaces of the most basic debug functions. Higher pin-out trace and probe ports are used with many on-chip instrumentation approaches. Even with these ports, however, the amount of debug information available can easily exceed the allocated debug interface of a SoC. To reduce the information being sent over the interface, approaches such as data compression increase the performance of the debug interface without significantly affecting system cost.

Obviously, the most useful approach to reducing the information from the debug port to the host development tool is to limit transmissions to new information and have inferred information derived by the development tools. For example, for required addresses to trace the instruction flow, it can be seen that not every instruction is required to construct an instruction trace. If the target processor does not have a change of flow, then the full address does not need to be transmitted. Only when a change of flow, such as an interrupt or branch, occurs would the system need to send the new beginning address. In addition, if the debugging session must be real time, then some information may be held in reserve. For instance, not all data values have to be visible at all times; only the data that the engineer is concerned with should be sent to the debug port during run time.

One of the major limiting factors on the use of instrumentation in SoC and multicore architectures is the ability to quickly export data as it is generated. On-chip instrumentation can address many of the operations associated with large amounts of on-chip debug, including triggering and performance monitoring. There is, however, almost always a need to be able to view the debug signals such as instruction/data trace from a processor, which means data must be exported off chip. The ability to transmit debug signals, most notably trace, is a hard limited function of two parameters:

- 1. The number of IO pins that can be dedicated to export of debug information at any given time.

- 2. The speed at which these signals can transmit the data.

This problem of exporting debug data is compounded for multiple-core SoC architectures, with monitoring of internal address, data, and control signals for each core, with the addition of inter-core and peripheral bus signals. One basic instrumentation approach is to rely on on-chip memory to buffer between traced data and the export bandwidth available. Trace buffer must consider the differences between data being generated on chip and the throughput of the debug interface. If buffers are modest in size, they can be overloaded by a large amount of trace data, as example, from multiple IP blocks or internal buses.

Despite the increasing number of IO signals available in leading-edge packages, system designers must limit the number of IO signals dedicated to trace and debug to reduce system cost (with packaging becoming an increasingly dominant factor in system cost). Most current approaches to increasing the IO bandwidth for debug rely on increasing the effective number of IO pins available (by multiplexing debug mode information into other system pins) and using higher-speed IO to increase the throughput of each pin. Each of these approaches to increase debug throughput has advantages and disadvantages. Increasing the effective pin count by statically multiplexing pins is a well-proven and low-risk approach. It does, however, involve coordination over the entire operation of the SoC, because pins that are dedicated to extended clock cycles to debug operations are unavailable for use in other modes of operation. To support SoC core and internal bus speeds, bigger pin bandwidth is increasingly required for instrumentation interfaces of a SoC.

## 2.3 Performance Analysis Using On-Chip Instrumentation

Customized instrumentation can integrate performance analysis of SoC architectures as part of a debug solution. Performance analysis (PA) is an all-encompassing term that refers to many types of measurements that provide information on how a particular core is being used, both in context of other parts of the system and with regard to specific algorithms. Integrating instruments to allow processor characterization, software performance, and system performance metrics provides valuable and concise information, which is more simply gathered locally to the processor because the lack of IO signal visibility in individual processor operations limits tracking of embedded processor performance. Performance metrics can be distorted or obscured by the layers of system buses, peripherals, and limited IO access between an embedded processor and the external test environment. Some common types of tests that are desirable in processor and SoC system performance analysis are:

- Find and profile hot spots in execution.

- Be able to measure loop times.

- Trace function calls, returns, and interrupts and measure the performance of this code.

- Measure the duration of ISR (interrupt service routine) and other events.

- Track interrupts and measure the maximum interrupt latency.

- Track RTOS context switches, measure task duration, and measure OS events such as semaphore waits.

- Measure the cache hit/miss ratio.

- Measure on-chip and off-chip memory access use.

- Count the number of processor stalls caused by (slow) bus accesses.

- Measure bus use and which master-slave transactions are using the bus the most.

- Count the number of processor stalls in a section of code.

- Count the number of instructions executed between two points in a program.

## 2.4 On-Chip Logic and Bus Analysis

Instrumentation-based logic trace allows analysis of bus architectures and related nonprocessor IP. Logic analysis instrumentation typically consists of debug blocks that are integrated into synthesizable logic files (typically VHLD or Verilog).

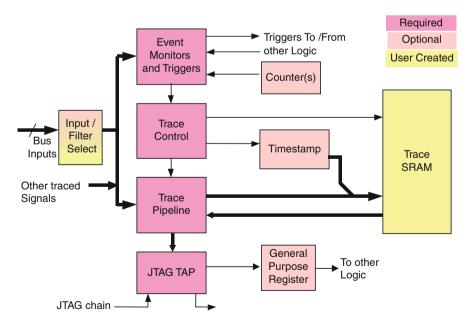

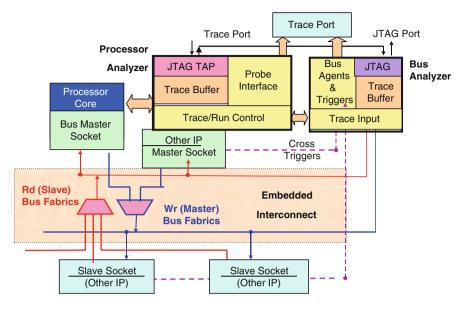

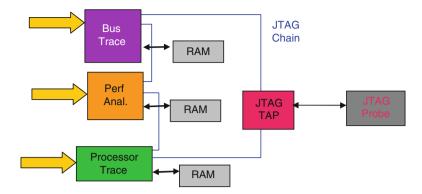

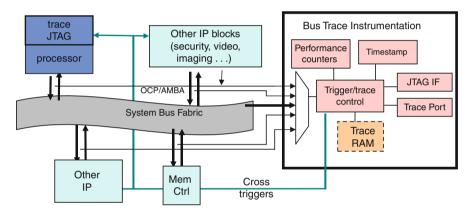

The bus analyzer collects a history of on-chip bus activity and exports it through the JTAG interface. Bus signal information is connected to the data inputs. A triggering system user starts and stops collection of data to an on-chip trace RAM. When collection stops, the most recent activity remains in the trace memory, from which it is unloaded through JTAG and displayed. The bus trace configuration includes a timestamp, which is stored with the data; to provide synchronization and interval information, on-chip counters for performance measurements; of the frequency of system events, and JTAG-controlled registers that hold parameters for input and output triggering of control operations that allow captured bus signals to interact on-chip with other debug components in the system.

- Bus fields include address bus, data bus, and user extension field and can track a number of bus masters in the system. More than one bus layer may be supported in a single instance. For more trace capability, or trace over different clock domains, more than one bus navigator instance can be implemented in a single JTAG chain.

- The trigger state (started, active, stopped, stalled) is recorded in the trace buffer. A multistate trigger allows triggering on sequential events. For example, a configuration that recognizes bus cycle A followed by bus cycle B is:

```

if (event A and state 0) then goto state 1

if (event B and state 1) then trigger

```

• Timestamps are used to indicate the distance between recorded samples when collecting trace using qualifications such as trace-on/trace-off, or collecting filtered trace that matches an event definition. Because bus measurements may be large numbers of cycles, the timestamp is set up to cover a large time range.

Being able to trigger from instrument data allows for both dynamic interactions with the target system and improved capture of the information of interest. Analyzers nominally support multiple triggers with multiple states per trigger (Fig. 2.3). Trigger conditions can be created as application-specific combinations of three components:

- Raw or processed data (filtered or aligned) compared to logic or edge events on each signal.

- Counter or times values matching a preprogrammed value.

- Trigger state (what trigger-related operations have occurred previously?).

When a trigger condition is satisfied, one or more actions can be taken, such as to mark the trigger frame, turn trace on or off, record a single frame, turn the counter on or off, increment or clear the counter, assert the external trigger out, or change the trigger state. The flexibility of this system under a wide variety of conditions and actions can improve visibility and monitor and tune system performance based on a range of operational parameters.

Fig. 2.3 Bus trace instrumentation block diagram

## 2.5 **On-Chip Instrumentation Examples**

In this section, we present several examples that illustrate the instrument features just discussed.

## 2.5.1 Trace Monitoring and Interfaces

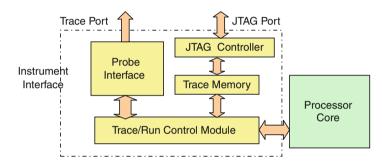

Embedded processor instrumentation addresses embedded processor debugging and system validation features such as run control, trace history, memory and register visibility, and complex breakpoints.

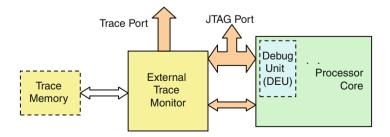

The external trace monitor is an instrumentation block integrated into and supporting of processor core monitoring. Trace monitoring allows capture of both execution history and other real-time information from the core and allows either on-chip or off-chip trace storage. Trace monitors can also be configured to collect profiling data for performance analysis. The specific instance of the instrument interfaces a debug unit interface for a processor architecture that provides debug functions such as start/stop execution, single-step, breakpoints, and register/ memory access (Fig. 2.4).

The trace monitor allows trace history to be captured in several modes (instruction and/or data full or compressed, etc.), depending on the available bandwidth and information desired. The block combines trace messages of various lengths into trace words of fixed width suitable for writing into memory, which are then sent to either on-chip memory or through a trace port to off-chip memory. Because the bandwidth of an external trace port is limited, the user must be selective about what information to collect. Typical choices include execution trace, data cycle trace, and profiling trace. The trace collection may also be enabled and disabled by hardware breakpoint registers set to generate trace actions (Fig. 2.5).

The trace monitor buffers trace words using a first-in-first-out (FIFO) memory, in order to compensate for the latency for outputting a trace word. The size of the FIFO is application dependent, and if the size is too modest, trace data can overflow

Fig. 2.4 Processor trace

Fig. 2.5 Trace monitor block architecture

Fig. 2.6 A processor-instrument interface

and become corrupted. The trace monitor control logic allows requests that the processor pipeline be stalled so that no trace information is lost (Fig. 2.6).

The trace monitor allows internal or external trace memory. When data is available from the data buffer, it is written to the internal memory. For external trace, the off-chip trace port logic multiplexes the trace words from the data buffer onto the trace port pins. As in the previous examples, control of the instrument block is handled by a JTAG interface and can be configured for on-chip or off-chip trace storage.

## 2.5.2 Bus Logic Monitoring

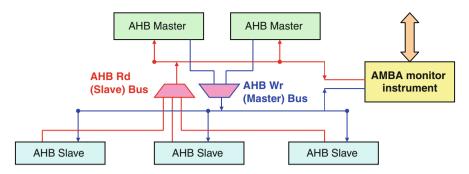

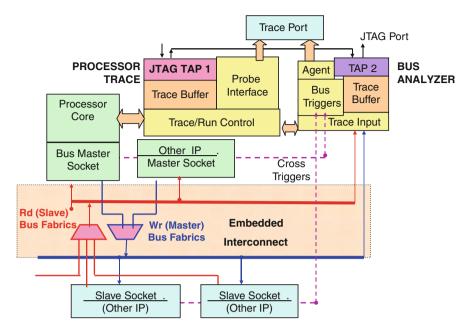

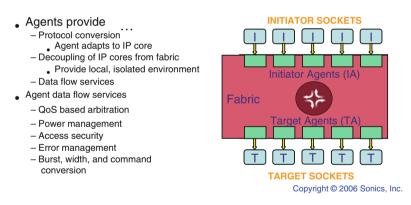

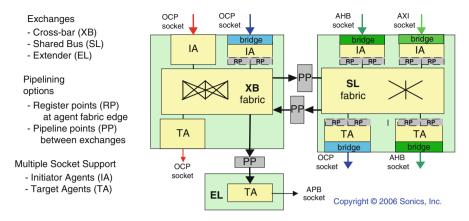

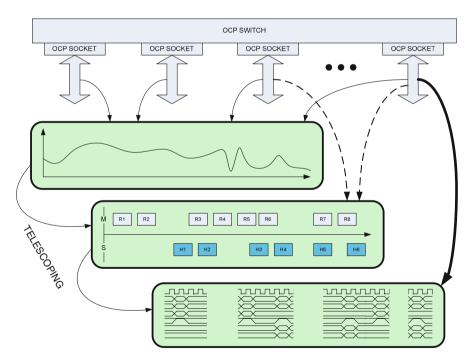

With increasing core density and interconnection of blocks in modern SoC design, monitoring internal bus operations is an important capability to debug the entire SoC. OCP and AMBA AHB are leading on-chip buses in use by many SoC design architectures to communicate between cores. On-chip instrumentation applied to the AHB captures bus activity and allows system diagnostics in real time.

In this case, the instrument connects to the AHB address bus, data buses, and various control signals at the bus multiplexed outputs. In AHB, signals are driven from each master and multiplexed onto a common address/data/control bus

Fig. 2.7 Instrument interface into an AMBA bus

by a multiplexer controlled by the arbiter. The multiplexed output is fanned out to all the AHB slaves. Similarly, data from each slave is multiplexed onto the common bus and sent to the SoC masters. The instrumentation interfaces are configured to receive address/control and data bus data from the currently granted master and addressed slave. The instrument passively collects bus activity and transfers the collected data through a trace port to the external probe interface (Fig. 2.7).

The bus instrument was developed to support a range of single-master and multiple-master systems. Additional signals can be hooked up to any nodes in the SoC, such as interrupt requests, additional AHB status, and processor control signals. The additional signals can also be used to compare and recognize specific on-chip activity outside the AHB bus, and then are transmitted to the probe for triggering purposes. As an example of real-time processing for debug that the instrument enables, the bus monitor allows probing of data in different modes. In the AHB case, data can be probed in two modes. Bus-cycle mode captures all address/control and data signals exactly as they occur per clock on the bus. Bus-transfer mode reduces the delays and latencies between address and data cycles on the bus, by aligning to the same clock cycle, operations that occur in different cycles. This reduces the number of trace cycles that are stored and allows for efficient combination of address-data-control event triggering for trace and monitoring operations. Bus transfer mode is especially effective for bus read operations in which the master transfer operation providing addresses and control and slave response providing data back to the master may be separated by a large number clock cycles of the bus waiting for the operation to complete. As an additional example of trace in-line processing, the trace hardware can be configured to filter out idle, busy, and not-ready cycles where no active data is being transferred. This allows each trace frame to record the critical AHB signals along with additional user-selectable signals and a timestamp to aid in performance analysis.

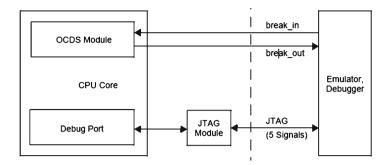

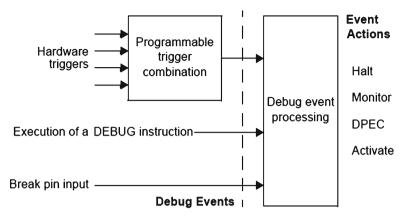

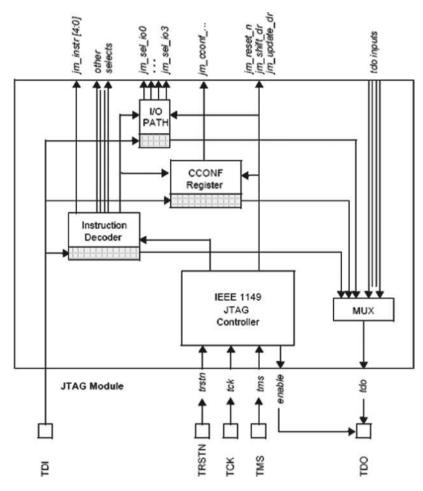

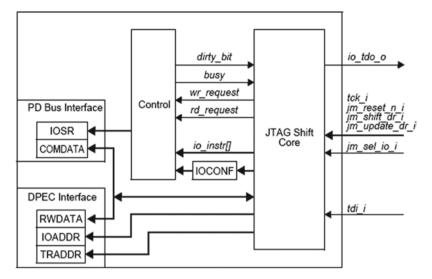

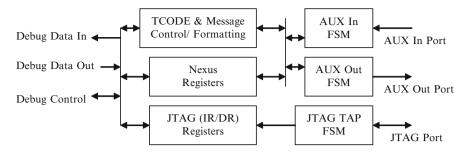

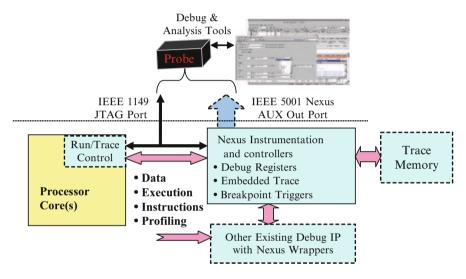

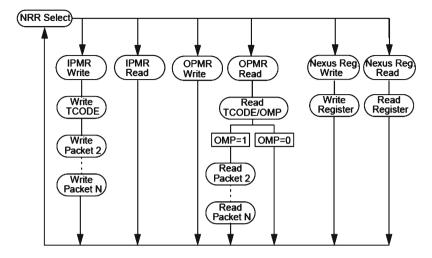

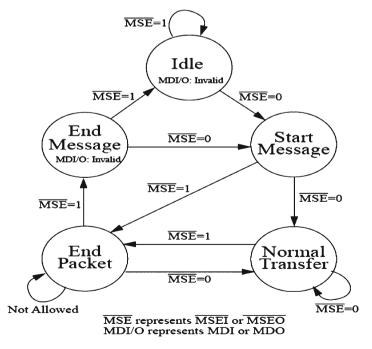

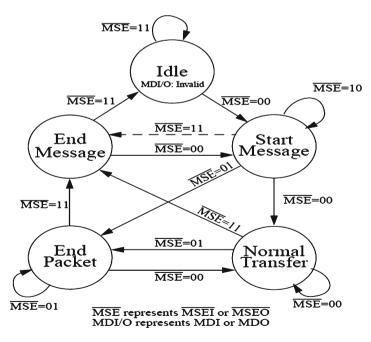

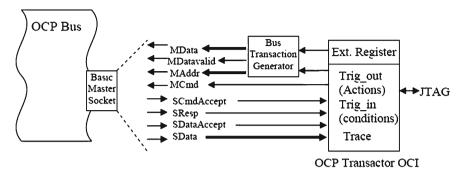

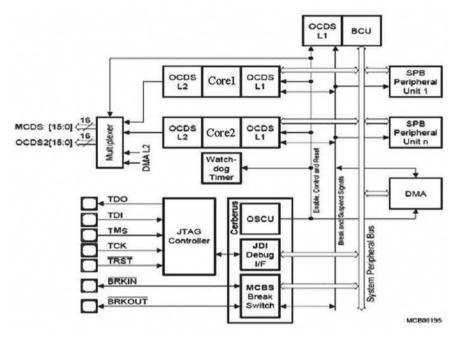

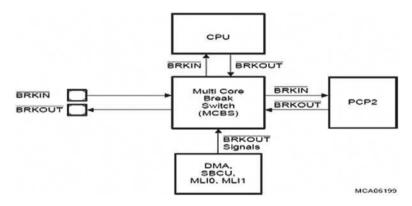

The host software for AMBA monitoring provides a good example of a specialized debug interface to support bus operations. Bus values can be viewed either numerically or symbolically. The symbolic representation increases the visibility and comprehension of complex bus operation (Fig. 2.8).