Lecture Notes in Electrical Engineering 95 Nikolaos Voros Amar Mukherjee Nicolas Sklavos Konstantinos Masselos Michael Huebner Editors

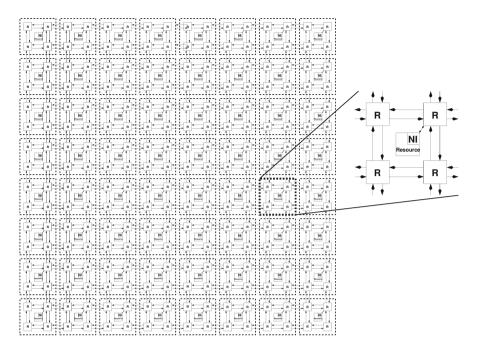

# VLSI 2010 Annual Symposium

# Lecture Notes in Electrical Engineering

Volume 105

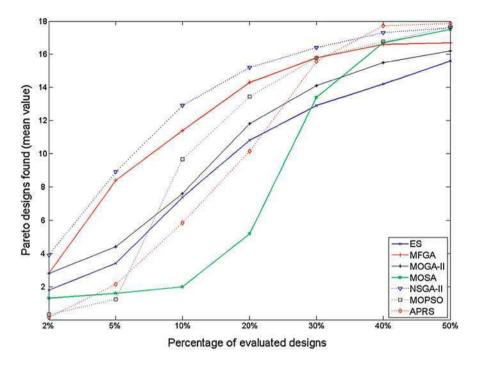

For further volumes: http://www.springer.com/series/7818 Nikolaos Voros · Amar Mukherjee Nicolas Sklavos · Konstantinos Masselos Michael Huebner Editors

# VLSI 2010 Annual Symposium

Selected papers

Nikolaos Voros Department of Telecommunication Systems and Networks Technological Educational Institute of Messolonghi National Road 303 00 Nafpaktos Nafpaktos-Antirrion (Varia) Greece e-mail: voros@teimes.gr

Amar Mukherjee School of Electrical Engineering and Computer Science University of Central Florida Central Florida Blvd. 4000 Orlando FL 32816-2362 USA e-mail: amar@eecs.ucf.edu

Nicolas Sklavos Informatics and MM Technological Educational Institute of Patras Rhga Feraiou 271 00 Pyrgos Ileias Region Greece e-mail: nsklavos@ieee.org Konstantinos Masselos Department of Computer Science and Technology University of Peloponnese 221 00 Tripolis Terma Karaiskaki Greece e-mail: kmas@uop.gr

Michael Huebner Institut für Technik der Informationsver Karlsruhe Institute of Technology Vinzenz-Priessnitzstr. 1 76131 Karlsruhe Germany e-mail: michael.huebner@kit.edu

ISSN 1876-1100 ISBN 978-94-007-1487-8 DOI 10.1007/978-94-007-1488-5 Springer Dordrecht Heidelberg London New York e-ISSN 1876-1119 e-ISBN 978-94-007-1488-5

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: eStudio Calamar, Berlin/Figueres

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### Preface

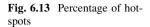

During the last years, significant changes have taken place in markets that traditionally had nothing in common. For example, markets like telecommunication, automotive, consumer electronics and medical equipment converge as far as the underlying systems of their products are concerned. The common needs come from the fact that modern devices contain, in most cases, complex parts relying on advanced hardware equipment. The increasing competition and the market pressure have created the need for hardware products of high reliability with short time-to-market.

The traditional development techniques, where the system development was relying on the experience of highly qualified engineers, are no longer adequate. The complexity of modern hardware systems calls for methodologies and tools supporting them to deal with the increasing market requirements.

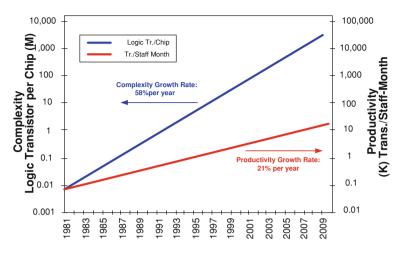

The existence of large number of computational intensive structures with diverse features leads also to hardware solutions that are no longer monolithic but able to adapt according to design needs. Moreover, energy aware systems and increased performance requirements are more and more important in an era where the size of most devices decreases while their complexity increases exponentially. Data intensive processing is also receiving renewed attention, due to rapid advancements in areas like multimedia computing and high-speed telecommunications. Many of these applications demand very high performance circuits for computationally intensive operations, often under real-time requirements. Furthermore, their computation power appetite tends to soar faster than Moore's law.

Moreover, the next generation of systems in most markets relies on the "computing everywhere" paradigm, which implies computing chips dedicated by market while at the same time development costs are exploding. This results in an increasing need of flexibility not only at the program level (by software) but also at the chip level (by hardware). So, combining flexibility and performance is now a key enabler for future hardware platforms. In that respect, current solutions are reaching their limits:

- Current computing solutions are out of breath: challenge of computing density and low power.

- Current development and programming tools do not provide the required productivity.

On one hand, the performance of most hardware architectures, in spite of the continuous increase in processors' speed, are, not surprisingly, lagging behind. Processors efficiency is more and more impaired by the memory bandwidth problem of traditional von Neumann architectures.

On the other hand, the conventional way to boost performance through Application Specific Integrated Circuits (ASIC) suffers from sky-rocketing manufacturing costs (requiring high volumes to be amortized) and long design development cycles. In the nanometre era, increasing non recurrent engineering costs could relegate system-on-chip to very few high volume products unless some standardization process is undertaken.

Modern Field Programmable Gate Arrays can implement an entire system-onchip, but at the cost of large silicon area and high power consumption. Moreover, a huge design productivity issue is raised by the difficulty of embedding algorithms on complex massively parallel architectures, while defining the processing architecture, under time to market pressure. Defining a programming paradigm for new hardware architectures is a difficult problem, where Computer Aided Design technologies call for new design paradigms. Current CAD tools have synthesis capabilities that don't reach the abstraction level required to handle complex hardware implementation.

Although the book *Designing Very Large Scale Integration Systems: Emerging Trends and Challenges* does not intend to provide answers to all the aforementioned open issues, it intends to identify and present in a comprehensive way the trends and research challenges of designing the next generation VLSI systems and systemson-chip. Throughout the chapters of the book, the reader will have the chance to get an insight to state-of-the-art technology and research results on areas like:

- Emerging devices and nanocomputing,

- Architecture level design of highly complex hardware systems and systemson-chip,

- Reconfigurable hardware technology, and

- Embedded systems.

All the book chapters are written by experts in the relevant domains and is envisaged to become the starting point for young scientists and practitioners to move science and technology one step further, in an attempt to deal with the ever increasing challenges of modern VLSI systems and systems-on-chip.

> N. Voros A. Mukherjee N. Sklavos K. Masselos M. Huebner

# Contents

#### Part I Architecture: Level Design Solutions

| 1 | Intelligent NOC Hotspot Prediction.                                                                                                                            | 3  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | Elena Kakoulli, Vassos Soteriou and Theocharis Theocharides                                                                                                    |    |

| 2 | Accurate Asynchronous Network-on-Chip Simulation Based<br>on a Delay-Aware Model<br>Naoya Onizawa, Tomoyoshi Funazaki, Atsushi Matsumoto<br>and Takahiro Hanyu | 17 |

| 3 | Trust Management Through Hardware Means: Design                                                                                                                |    |

|   | Concerns and Optimizations                                                                                                                                     | 31 |

|   | Apostolos P. Fournaris and Daniel M. Hein                                                                                                                      |    |

| 4 | MULTICUBE: Multi-Objective Design Space Exploration                                                                                                            |    |

|   | of Multi-Core Architectures                                                                                                                                    | 47 |

|   | Cristina Silvano, William Fornaciari, Gianluca Palermo,                                                                                                        |    |

|   | Vittorio Zaccaria, Fabrizio Castro, Marcos Martinez, Sara Bocchio,                                                                                             |    |

|   | Roberto Zafalon, Prabhat Avasare, Geert Vanmeerbeeck,                                                                                                          |    |

|   | Chantal Ykman-Couvreur, Maryse Wouters, Carlos Kavka,                                                                                                          |    |

|   | Luka Onesti, Alessandro Turco, Umberto Bondi,                                                                                                                  |    |

|   | Giovanni Mariani, Hector Posadas, Eugenio Villar,                                                                                                              |    |

|   | Chris Wu, Fan Dongrui, Zhang Hao and Tang Shibin                                                                                                               |    |

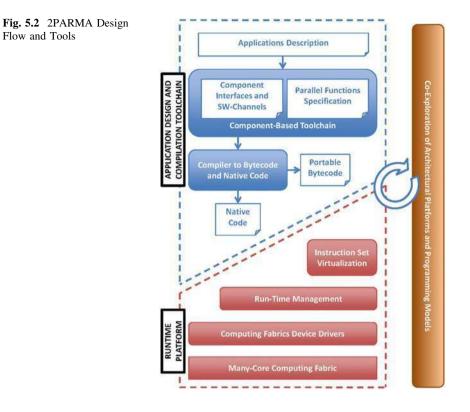

| 5 | 2PARMA: Parallel Paradigms and Run-time Management             |    |  |  |  |

|---|----------------------------------------------------------------|----|--|--|--|

|   | Techniques for Many-Core Architectures                         | 65 |  |  |  |

|   | C. Silvano, W. Fornaciari, S. Crespi Reghizzi, G. Agosta,      |    |  |  |  |

|   | G. Palermo, V. Zaccaria, P. Bellasi, F. Castro, S. Corbetta,   |    |  |  |  |

|   | A. Di Biagio, E. Speziale, M. Tartara, D. Melpignano,          |    |  |  |  |

|   | JM. Zins, D. Siorpaes, H. Hübert, B. Stabernack,               |    |  |  |  |

|   | J. Brandenburg, M. Palkovic, P. Raghavan, C. Ykman-Couvreur,   |    |  |  |  |

|   | A. Bartzas, S. Xydis, D. Soudris, T. Kempf, G. Ascheid,        |    |  |  |  |

|   | R. Leupers, H. Meyr, J. Ansari, P. Mähönen and B. Vanthournout |    |  |  |  |

|   |                                                                |    |  |  |  |

#### Part II Embedded System Design

| 6  | Adaptive Task Migration Policies for Thermal Controlin MPSoCsDavid Cuesta, Jose Ayala, Jose Hidalgo, David Atienza,Andrea Acquaviva and Enrico Macii                                                                                                                                                                              | 83  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7  | A High Level Synthesis Exploration Framework<br>with Iterative Design Space Partitioning                                                                                                                                                                                                                                          | 117 |

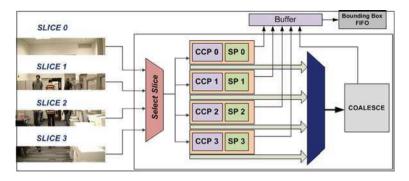

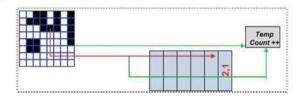

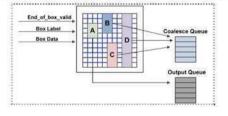

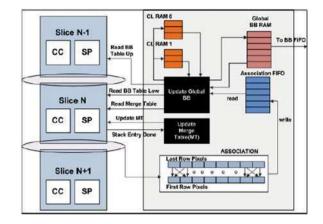

| 8  | A Scalable Bandwidth-Aware Architecture for Connected<br>Component Labeling<br>Vikram Sampath Kumar, Kevin Irick, Ahmed Al Maashri<br>and Vijaykrishnan Narayanan                                                                                                                                                                 | 133 |

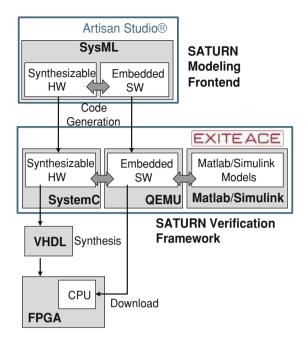

| 9  | <b>The SATURN Approach to SysML-Based HW/SW Codesign</b><br>Wolfgang Mueller, Da He, Fabian Mischkalla, Arthur Wegele,<br>Adrian Larkham, Paul Whiston, Pablo Peñil, Eugenio Villar,<br>Nikolaos Mitas, Dimitrios Kritharidis, Florent Azcarate<br>and Manuel Carballeda                                                          | 151 |

| 10 | Mapping Embedded Applications on MPSoCs:The MNEMEE ApproachChristos Baloukas, Lazaros Papadopoulos, Dimitrios Soudris,Sander Stuijk, Olivera Jovanovic, Florian Schmoll,Peter Marwedel, Daniel Cordes, Robert Pyka, Arindam Mallik,Stylianos Mamagkakis, François Capman, Séverin Collet,Nikolaos Mitas and Dimitrios Kritharidis | 165 |

| 11  | The MOSART Mapping Optimization for Multi-Core<br>ARchiTectures                                                                                                           | 181 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Bernard Candaele, Sylvain Aguirre, Michel Sarlotte,<br>Iraklis Anagnostopoulos, Sotirios Xydis, Alexandros Bartzas,<br>Dimitris Bekiaris, Dimitrios Soudris, Zhonghai Lu, |     |

|     | Xiaowen Chen, Jean-Michel Chabloz, Ahmed Hemani,                                                                                                                          |     |

|     | Axel Jantsch, Geert Vanmeerbeeck, Jari Kreku,<br>Kari Tianguria, Englishag Intermiting, Dimitriag Kritharidia                                                             |     |

|     | Kari Tiensyrja, Fragkiskos Ieromnimon, Dimitrios Kritharidis,<br>Andreas Wiefrink, Bart Vanthournout and Philippe Martin                                                  |     |

| Par | t III Emerging Devices and Nanocomputing                                                                                                                                  |     |

| 12  | XMSIM: Extensible Memory Simulator for Early                                                                                                                              |     |

|     | Memory Hierarchy Evaluation                                                                                                                                               | 199 |

| 13  | Self-Freeze Linear Decompressors: Test Pattern Generators                                                                                                                 |     |

|     | for Low Power Scan Testing<br>Vasileios Tenentes and Xrysovalantis Kavousianos                                                                                            | 217 |

| 14  | SUT-RNS Forward and Reverse Converters<br>E. Vassalos, D. Bakalis and H. T. Vergos                                                                                        | 231 |

| 15  | <b>Off-Chip SDRAM Access Through Spidergon STNoC</b><br>Khaldon Hassan and Marcello Coppola                                                                               | 245 |

| 16  | Digital Microfluidic Biochips: A Vision for Functional Diversity<br>and More than Moore<br>Krishnendu Chakrabarty and Yang Zhao                                           | 263 |

| Par | t IV Reconfurable System                                                                                                                                                  |     |

| 17  | FPGA Startup Through Sequential Partial and Dynamic<br>Reconfiguration                                                                                                    | 289 |

|     | Joachim Meyer, Michael Hübner, Lars Braun, Oliver Sander,<br>Juanjo Noguera, Rodney Stewart and Jürgen Becker                                                             |     |

| 18  | Two Dimensional Dynamic Multigrained Reconfigurable                                                                                                                       | 202 |

|    | Juanjo Noguera, Rodney Stewart and Jürgen Becker |     |

|----|--------------------------------------------------|-----|

| 18 | - ···                                            |     |

|    | Hardware.                                        | 303 |

|    | Lars Braun and Jürgen Becker                     |     |

| 19 | Design for Embedded Reconfigurable Systems Using<br>MORPHEUS Platform<br>Paul Brelet, Philippe Millet, Arnaud Grasset, Philippe Bonnot,<br>Frank Ieromnimon, Dimitrios Kritharidis and Nikolaos S. Voros | 319 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 20 | New Dimensions in Design Space and Runtime Adaptivity<br>for Multiprocessor Systems Through Dynamic<br>and Partial Reconfiguration: The RAMPSoC Approach<br>Diana Göhringer and Jürgen Becker            | 335 |

# Part I Architecture: Level Design Solutions

## Chapter 1 Intelligent NOC Hotspot Prediction

Elena Kakoulli, Vassos Soteriou and Theocharis Theocharides

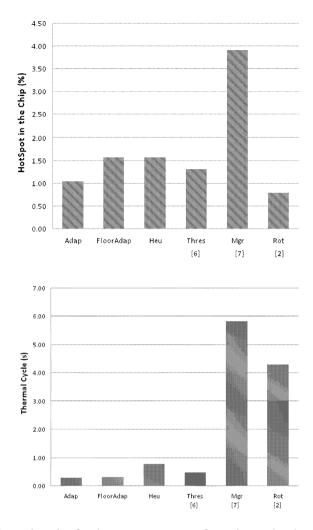

**Abstract** Hotspots are Network on-Chip (NoC) routers or modules which occasionally receive packetized traffic at a higher rate that they can process. This phenomenon reduces the performance of an NoC, especially in the case wormhole flow-control. Such situations may also lead to deadlocks, raising the need of a hotspot prevention mechanism. Such mechanism can potentially enable the system to adjust its behavior and prevent hotspot formation, subsequently sustaining performance and efficiency. This Chapter presents an Artificial Neural Network-based (ANN) hotspot prediction mechanism, potentially triggering a hotspot avoidance mechanism before the hotspot is formed. The ANN monitors buffer utilization and reactively predicts the location of an about to-be-formed hotspot, allowing enough time for the system to react to these potential hotspots. The neural network is trained using synthetic traffic models, and evaluated using both synthetic and real application traces. Results indicate that a relatively small neural network can predict hotspot formation with accuracy ranges between 76 and 92%.

**Keywords** Network on-Chip Hotspots • Artificial Neural Networks • VLSI Systems

E. Kakoulli · V. Soteriou

Department of Electrical Engineering and Information Technology, Cyprus University of Technology, Lemesos, Cyprus

T. Theocharides (🖂)

Department of Electrical and Computer Engineering KIOS Research Center for Intelligent Systems and Networks, University of Cyprus, Nicosia, Cyprus e-mail: ttheocharides@ucy.ac.cy

#### **1.1 Introduction**

The Network on-Chip paradigm, (NoC) [7] is a distributed, router-based interconnect architecture that is quickly becoming the preferred communication fabric in general purpose Chip Multi-Processors (CMPs) as well as in application-specific Systems-on-Chips (SoCs). NoCs facilitate high communication throughput demands among the various computational, memory and IP cores found in these parallel systems. With technology enabling billions of transistors on a single chip, time-and medium-shared interconnects, such as on-chip buses, are no longer adequate; NoCs on the other hand effectively scale and allow efficient reusability of computational resources. NoCs have already been demonstrated in the Tilera TILE64 CMP [2] and the Intel Teraflops chip [26], among other CMP implementations.

In wormhole flow-control (WFC) [8], commonly employed in NoCs ([3],[11]), communication is organized in the form of packetized messages of arbitrary length, which are broken down into further logical link-width chunks called flowcontrol units (flits). WFC allows parts of a packet to be forwarded to the next router towards a final destination or consumer node, without having to wait for the remaining flits of the same packet, unlike in store-and-forward flow control, allowing the efficient use of smaller intermediate buffering, that is suitable for power-, thermal-and area-constrained NoCs. The spreading of a packet in a pipelined fashion across several routers at a time, however, makes WFC susceptible to packet blocking and possible deadlocks, as an increased delay at an intermediate router quickly forms backpressure which can be propagated in the reverse direction of the packet's path traversal. Such adverse effect, as outlined later, can further lead to the creation of NoC hotspots. Loss in NoC performance is traditionally alleviated by utilizing several resource utilization-enhancing mechanisms, such as virtual channels [6], control packets that reserve resources in advance [20], specialty architectures or schemes that guarantee communication rates [5], or by purposely inefficiently operating high-performance NoCs at relatively low utilizations to avoid blocking [21].

Hotspots are NoC routers or modules which occasionally receive packetized traffic at a rate higher than their traffic consumption rate. Since interconnecting links and ports are bandwidth-limited, and as the load traffic distribution of real applications is inherently uneven, hotspots are common in popular NoC topologies such as at the diagonal of meshes [19]. Even a single heavily loaded router can cause a hotspot, and thus a hotspot can be created even with the use of infinite bandwidth links. Some factors which can cause hotspots are non-optimal application mapping, lack of traffic balancing with oblivious routing algorithms, application migration and specific application NoC resource demands [4]. Hotspots have a spatial component when a subset of the routers receives the majority of the traffic, and a temporal component as these router nodes receive traffic often. The adverse phenomenon of hotspot formation reduces the performance and the effective throughput of the NoC, and increases average packet

latency. This effect is particularly severe as backpressure can cause the buffers of neighboring routers to quickly fill-up in a domino-style effect, leading to a spatial spread in congestion that can cause the network to form a "saturation tree", and even worse, to deadlock. Hotspot formation is unpredictable in general-purpose parallel best-effort on-chip systems such as CMPs, as the application behavior is not exactly known a-priori so as to react accordingly by setting exact spatial-temporal hotspot reduction mechanisms.

This Chapter describes a first attempt towards utilizing artificial intelligence in predicting the formation of traffic hotspots. The Chapter presents a hardware-based artificial neural network (ANN), which is trained and used to detect the formation of hotspots, in an effort to notify the system. The Chapter focuses only on hotspot detection; plans to integrate avoidance and adjustment mechanisms are imminent. The proposed ANN is designed with manageable hardware overheads, implemented as a processing element in the NoC. The ANN monitors the NoC in an effort to detect runtime occurring hotspots, and reactively predicts the location of a potential hotspot that is about to be formed, allowing enough time for the system to adjust and potentially avoid the hotspot.

Section 1.2 presents some approaches in hotspot prevention and Sect. 1.3 presents the Artificial Neural Network-based (ANN) mechanism. Some details on the hotspot model considered, the data processed by the ANN, and the proposed ANN architecture are detailed in Sect. 1.3 as well, while Sect. 1.4 presents the experimental setup, ANN synthesis results and quantitative accuracy results in predicting NoC hotspots in CMPs using real application traces. Section 1.5 concludes this chapter.

#### 1.2 Background and Related work

Hotspot prevention has been explored significantly in the domain of large-scale interconnection networks found in off-chip parallel computer systems, but only recently, and to a much lesser extent, in the area of NoCs. In both domains, most of the work focuses on reducing the number of routed packets destined towards a hotspot, using various methodologies. All of these works assume that the hotspot spatial locations are (1) either known a-priory and pro-actively reduce the possibility of hotspot formation, or (2) spatially and temporarily react actively to reduce the possibility of a hotspot.

There are various hotspot prevention works in the domain of large-scale interconnected parallel computers. References [1, 10, 14, 15, 22] present methods that tackle hotspots in traditional, off-chip networks and multiprocessor systems. Most of the hotspot related work in the domain of off-chip networks however, is unsuitable for NoCs, as the resources are restricted (buffering, virtual channels and routing computation) and packet dropping and re-transmission is unacceptable due to the complexity of the mechanism and the need to attain ultra-high performance. Hotspot prevention is therefore mostly based on spatial techniques via the use of

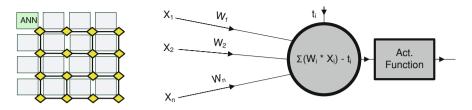

Fig. 1.1 An example placement of an ann prediction engine, as a dedicated pe (right) and the mathematical representation of a neuron (left)

adaptive routing which aims to route packets around hotspots, such as in [9]. Reference[27] uses a low-cost end-to-end credit-based allocation technique in NoCs to throttle and regulate hotspot-destined traffic, to allow fair sharing of the hotspot resource network and to mitigate the effects of non-hotspot traffic. All existing works however, are based on the premise that hotspots can be predicted due to application-specific behavior. This Chapter presents how an ANN can be used to predict hotspot occurrences in NoCs. ANNs have been used as prediction mechanisms successfully, in several application areas. In particular, they have been used as branch predictors in computer architecture [18, 23], yielding high accuracy, and as resource allocation mechanisms forecasting the computational demands. They have also been used in various other forecasting scenarios, such as weather and stock behavior [17].

An ANN is an information processing paradigm, consisting of computation nodes called neurons and the interconnections between them, called synapses. A neuron takes a set of inputs and multiplies each input by a weight value, accumulating the result until all inputs are received. Weights are determined during the training process. A threshold value (also determined in training) is then subtracted from the accumulated result, and this result is then used to compute the output of the neuron, via the so-called "activation function" (Fig. 1.1 (right)). Typical activation functions include complex mathematical functions such as the hyperbolic tangent function. The neuron output is then propagated to a number of destination neurons in another layer, which perform the same general operation with the newly received set of inputs and their own weight/threshold values, and this is repeated for other layers, depending on the complexity and accuracy required for the application. The activation function used, as well as the connectivity of the neurons, depends on the application as well. Neurons are typically used in multi-layer configurations, where they are trained to perform a desired operation in a similar manner to the way the human brain operates [16]. The ANN operates in two stages; the training stage and the computation stage. Each neuron receives training data that allows it to make necessary decisions based on the input data during execution of a desired operation. A small neural network can be easily implemented in hardware, as neurons can be designed using a Multiplier-Accumulator (MAC) unit, memory to hold the training weights, and a Look-Up Table (LUT) for the activation function. Optimizations, though, are necessary in interconnecting the neurons, however time-division multiplexing between neuron operations allows for resource sharing and minimal hardware needs.

#### **1.3 Artificial Neural Network Hotspot Predictor**

As already explained, hotspots are not single routing nodes, but rather a combination of increased utilization in a neighborhood of routers, usually involving two or more routers. Thus, the ANN is designed in such a way as to integrate information of neighboring routers, i.e. "reading" situations happening one and two routers away from the potential hotspot. Furthermore, the hardware needs must be taken into consideration when designing the ANN; this can be done by partitioning the on-chip network into smaller sub-regions, and using a base ANN for each region, in an effort to reduce the hardware resources necessary. Potentially the base ANN can be designed as a Processing Element (PE), as in Fig. 1.1 (left). This Section presents the base ANN mechanism.

#### 1.3.1 Hotspot Modeling

For training and evaluating the ANN-based hotspot prediction mechanism, and to test its effectiveness in forecasting hotspots, a hotspot model with well-defined spatially-located hotspot formations centered on randomly chosen routers in an  $8 \times 8$  mesh network, but of relatively short temporal duration so as to enable testing of the effectiveness of the prediction mechanism, has to be devised. This model enables synthetic generation of network traces that exhibit a range of throughput demands upon the NoC. The synthetic traces allow both training as well as evaluation. The idea is to compare un-even traffic flows (i.e. formed because of a hotspot) versus a base Uniform Random NoC Traffic (URT) pattern. Under URT, all router nodes in an NoC have an equal probability of receiving a packet per unit time, therefore the traffic is almost perfectly balanced and the attainable network throughput is the maximum that can be achieved both practically and theoretically [8]. The developed hotspot model uses the URT model as a base, for most of the time, except when for short pre-specified and periodically occurring time intervals just two arbitrarily selected nodes receive with equal probability all the network traffic from all the remaining sender nodes, with the remaining nodes receiving no traffic. Time Frame Windows (TFW) of 10,000 cycles are then defined, during any time which the two hotspots can occur simultaneously for a short duration of 200 cycles. No other hotspots can occur within a TFW, and during the rest of the duration of the TFW the traffic behaves purely as URT. This model test-stresses the prediction mechanism as hotspots occur both infrequently and for short durations.

| Normalized throughput | 20%   | 40%  | 60%  | 80%  | 100% |

|-----------------------|-------|------|------|------|------|

| 0.22*                 | 0.96  | 0.97 | 0.97 | 0.98 | 0.98 |

| 0.33                  | 0.84  | 0.87 | 0.88 | 0.88 | 0.88 |

| 0.44                  | 0.81  | 0.84 | 0.86 | 0.86 | 0.87 |

| 0.56                  | 0.85  | 0.88 | 0.89 | 0.89 | 0.91 |

| 0.67*                 | 0.098 | 0.98 | 0.98 | 0.98 | 0.99 |

| 0.78                  | 0.86  | 0.88 | 0.88 | 0.89 | 0.91 |

| 0.89                  | 0.85  | 0.86 | 0.88 | 0.90 | 0.92 |

| 0.98*                 | 0.95  | 0.96 | 0.96 | 0.96 | 0.96 |

**Table 1.1** Synthetic hotspot traffic results: prediction accuracy as a function of simulation time at various levels of normalized network throughput

Asterisks (\*) indicate training data

| * | 4 |

|---|---|

|   | 4 |

|   | 8 |

|   | 5 |

|   | 6 |

| * | 5 |

|   | 6 |

|   | 7 |

| * | 4 |

|   |   |

Asterisks (\*) indicate training data

#### 1.3.2 ANN Training

The ANN was trained using part of the synthetic traffic traces suite, consisting of buffer utilization data collected over half a million cycles. Three different traffic scenarios were targeted during this phase; moderate, average, and high hotspot temporal intensity, expressed in terms of the NoC's normalized saturation throughput (for hotspot traffic) at 0.22, 0.67 and 0.98 (asterisks in Tables 1.1 and 1.2), through the duration of the simulation. Moreover, training data includes multi-router hotspot scenarios. Using the synthetic traces, utilization rates of all buffers in all routers were collected by measuring the average utilization rate of each router during 50-cycle intervals. This data was fed as training input to the ANN.

The Matlab ANN toolbox and supervised learning algorithms [12, 13] were used for the training phase. The acceptable error rate was set to less than 10%, given the large data size and considerations in training memory for the ANN weights, as well as the large range variations and sparsity of the training set data. Error rates less than 5% cannot be obtained in realistic training time, thus are considered impractical for the purposes of the presented network; however,

potential optimization of the training set can probably improve the accuracy of the network and enable training for less than 5% acceptable error rate [25]. As the output of the hotspot prediction mechanism represents a probability that a hotspot will be formed in location (x, y) inside a 2D NoC, the acceptable error rate represents the probability that a hotspot is not created. If, for example, the ANN is trained with a resulting accuracy of 85%, this essentially represents that there is an 85% probability of a hotspot happening in location (x, y).

The training data obtained consists of 8-bit weight values, biased to yield positive integers for ease of hardware implementation. During the training stage, the bit-width precision of the weights has to be determined. By varying this in intervals of 4 bits, it was found that 4-bit weight values yield high error rates (>20%), whereas for 8-bit and 12-bit precision, the error rate is ~9.2 and ~8.4% respectively. This indicates that 8 bits are adequate for the weight data. The hyperbolic tangent can be used as the activation function, as its advantage lies in its function properties; it is an odd function with mirror symmetry:

$$tanh(-x) = -tanh(x) and tanh(\overline{z}) = tanh(z).$$

The function is also asymptotic, with the output of the function considered to be 1 (or-1) for input values above or below a certain threshold. A Look-Up Table (LUT) implementation requires only positive values ranging from zero to the threshold value that yields 1 (or-1). The activation function can be implemented as a multi-ported LUT, to parallelize accesses to it and enable parallel neuron computation.

The base ANN hotspot prediction mechanism consists of two perceptron layers which monitor  $2 \times 2$  and  $3 \times 3$  blocks of routers in the NoC, and fully connected hidden and output layers that combine the two perceptron layers and return the location of a potential hotspot router. The ANN operates by receiving buffer utilization statistical data from each router that it monitors, in discrete time intervals, and, using training weights, attempts to detect a pattern that can potentially lead to a hotspot located at one of the routers that the network monitors. The prediction time needs to be early enough for any adjustment mechanisms to interfere and potentially prevent the hotspot from forming. Therefore, the ANN must be accurate, and must also be fast as it needs to output a prediction early ahead of the next timing interval that it is about to receive new monitoring data.

The ANN can be scaled to monitor larger NoCs, by hierarchically connecting the base ANN together to an additional layer of neurons and training appropriately. Furthermore, more layers can be added as the network size grows. The hardware overheads necessary for larger ANNs will increase significantly, and the latency will also increase drastically, as the top ANN needs to receive data from each of the smaller ANNs and compute the final output; this adds significant delays in the overall operation of the ANN. However, the ANN idea can potentially be used in various network sizes and topologies, taking the hardware budgets into consideration.

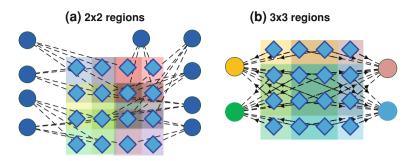

Fig. 1.2 Partitioning a  $4 \times 4$  mesh noc—the  $2 \times 2$  and  $3 \times 3$  partitions and the respective input layer neurons

#### 1.3.3 Neural Network Architecture

The base ANN is directed towards a 2-D Mesh architecture, and was trained and designed to support up to  $4 \times 4$  mesh NoC infrastructures. It consists of an input layer which partitions the routers being monitored into 9 segments of  $2 \times 2$  routers, and 4 segments of  $3 \times 3$  routers. The segmentations are shown in Fig. 1.2. The segmentation is done in such a way so as to detect hotspots not as single routers, but as a combination of events affecting routers one and two hops next to the probable hotspot location. The network receives the average buffer utilization from each router in the region that is responsible for monitoring, processes the information and returns as output a binary vector containing the location of a potential hotspot router, including hotspots where two or more routers become hotspots.

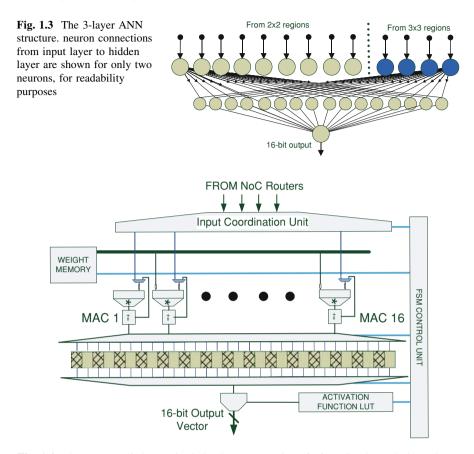

The first ANN (input) layer consists of 9 neurons responsible for monitoring regions of  $2 \times 2$  routers and 4 neurons responsible for monitoring regions of  $3 \times 3$  routers (Fig. 1.2). Each of the input layer neurons simply acts as a MAC, that multiplies the incoming utilization rate from each of the routers the neuron is responsible for. When the results are accumulated, they are passed through the activation function (hyperbolic tangent), and propagated to a hidden layer of 16 neurons, all fully connected. The hidden layer neurons similarly process the 13 inputs from each of the input layer neurons, and propagate their result to an output neuron which returns a 16-bit vector indicating whether or not a hotspot is predicted. If the output neuron predicts a hotspot, the location of a hotspot is encoded in the 16-bit output vector. The overall base ANN system is shown in Fig. 1.3.

The base ANN is designed with emphasis on hardware reuse and with the fact that results should be computed prior to the next timing interval that the NoC will re-transmit new utilization data. An overview of the base ANN architecture is shown in Fig. 1.4. The primary hardware component of the ANN is an 8-bit  $\times$  8-bit MAC unit; given however that the second layer of neurons could be computed in parallel, the network is designed with 16 MAC units, to boost the computation, reusing them on demand during the first layer of computation nodes.

**Fig. 1.4** The ANN prediction engine in hardware. It consists of 16 MAC units (only 2 are shown for readability purposes), a memory which holds the ANN weights, registers used to hold partial neuron sums, and the activation function LUT. The entire process is controlled through an FSM control unit and an input coordination unit

The neuron weights are stored in a RAM, with a 128-bit bus, transmitting at most sixteen 8-bit weight values in parallel during the multiplication stage. A FSM control unit synchronizes the entire ANN computation, where input values from each router arrive and are directed towards the appropriate MAC unit, depending on the neuron that they belong to. It is assumed that buffer utilization data for each router arrive as individual packets; using one packet per cycle as incoming data rate, the ANN receives 4 buffer utilization rates for a single router per cycle. Given the overlap of the  $2 \times 2$  and  $3 \times 3$  regions, the values are used at least twice, therefore, they are directed to the corresponding MAC unit. The MAC units are also interconnected to a set of accumulation registers, where each register holds the value of each neuron necessary for the computation. There are 30 registers; 13 for the input layer neurons, 16 for the output layer neurons and 1 for the output neuron. When the next input arrives at the ANN and is directed to a neuron already

being computed, its partial sum is fed back into a MAC unit using the stored value from the register. This enables data reuse, and reduces the overall hardware requirements. When a neuron finishes its computation cycle, its final sum of products is used as an input to the LUT, to return the activation function value, which in turn is reused as input to the MAC units for computing the second layer neuron values. The process is repeated for all second layer neurons. The last neuron receives as input all the outputs of the 16 s layer neurons, and its result is encoded as a 16-bit binary vector representing the location(s) of the routers with potential hotspot formation.

The computation starts when the first buffer utilization values arrive from one of the routers under monitoring. Data is collected within a 50-cycle TFW; if a router does not transmit monitoring data until the end of the TFW, its buffer utilization is set to maximum, as it is assumed to be part of a hotspot. By the time the ANN receives the last router information, the ANN requires 5 additional cycles to finalize computation of the first layer neurons (given that computation of the first layer of neurons happens as soon as utilization data arrive at the ANN). This is in part because each completed neuron output will have to pass through the activation function LUT. This can be reduced by parallelizing access to the LUT. Once the activation is complete, the second layer (16 neurons) is computed; there are a total of 13 MAC operations, hence the results for the last neuron will be available in 26 cycles (13 MAC operations and 13 LUT accesses). The last neuron performs 16 parallel MAC operations and a mapping of the result to the 16-bit output vector, needing an additional 3 cycles (1 for all MACs, 1 for the summation and 1 for the mapping). In total, the ANN requires 34 cycles from the time the last router utilization data is received until its output. If all routers are on time in transmitting the utilization data, then the network needs an extra 16 cycles to fill up the computation pipeline (1 cycle per router), bringing the total minimum number of cycles to 50, which is the targeted time interval between outputs.

#### **1.4 ANN Hotspot Prediction Results**

#### 1.4.1 Experimental Setup

The ANN was trained and modeled in two steps; training and evaluation. During the training stage, synthetic traffic utilization figures were used, as explained in Sect. 1.3.2. The evaluation stage consisted of two separate steps: (1) evaluation using synthetic traffic models with varied hotspot rates in an  $8 \times 8$  2D mesh network using 4 base ANN engines, with each such ANN monitoring a non-overlapping  $4 \times 4$  mesh sub-network, and (2) evaluation using the Raw CMP benchmarks [24], over the  $4 \times 4$  Raw network (see Sect. 1.4.3). The output of the ANN was compared to the actual trace, both for synthetic traffic and the Raw benchmarks, and the ANN accuracy is therefore evaluated. This accuracy was

measured during constant simulation intervals, to observe the behavior of the network as the amount of data increases.

A detailed cycle-accurate simulator is used to provide the buffer utilization data for training and evaluation of the ANN. The simulator supports k-ary 2-mesh topologies with 3 GHz 5-stage pipelined router cores, each with two virtual channels (VCs). Packets are composed of five 32-bit flits with each flit transported in 1 link cycle over links of 96Gbps bandwidth. Each router consists of eight unidirectional channels (four incoming and four outgoing).

#### 1.4.2 Synthetic Traffic Prediction Results

Various hotspot spatio-temporal intensities are used as input to the ANN. These intensities are modeled as a function of the normalized saturation throughput, defined as the throughput at which the latency value is three times the zero-load latency of the network. The output of the ANN is then compared with the actual behavior of each trace, in discrete intervals of 20% increments during the simulation process. A hotspot prediction is considered to be successful if it can be foreseen at least 50 cycles ahead of its occurrence in the NoC, and that its coordinate locality is correct. Table 1.1 shows the accuracy of the ANN for the synthetic traffic models. Each model exhibits different hotspot behavior; Table 1.1 also illustrates the training traces used for training (marked with asterisks (\*)); these traces were also used as evaluation benchmarks to validate the operation of the ANN. The accuracy ranges between 88% and 92%, values which are relatively good given the 10% acceptable error margin used during training. Table 1.2 shows the number of false positive predictions (i.e. predicted hotspots which never occurred in the actual trace). While false positives might seemingly not be a problem, their effect can only be studied when the overall cost of a hotspot correction/avoidance mechanism is implemented that utilizes the prediction information. The accuracy can be further improved, by improving the training set, and by potentially using more bits to represent the weights.

#### 1.4.3 Real-System Traffic Prediction Results

The Raw CMP [24] is a system for general-purpose and embedded computing, consisting of 16 identical tiles interconnected via a  $4 \times 4$  mesh array. Every tile contains its own pipelined RISC processor, computational resources, memory, and programmable routers. The Raw architecture contains four parallel networks: two dynamic networks to support unpredictable inter-communication requirements among the tiles (e.g. cache misses), and two static networks to allow implementation software-directed routing among tiles with ordered and flow-controlled transfer of operands and data streams between functional units. The switching of the routers in the two static networks is pre-programmed by the compiler,

| lation time |      |      |      |      |      |

|-------------|------|------|------|------|------|

| Benchmark   | 20%  | 40%  | 60%  | 80%  | 100% |

| 8b_encode   | 0.82 | 0.82 | 0.80 | 0.80 | 0.81 |

| 802.11a     | 0.88 | 0.89 | 0.88 | 0.88 | 0.89 |

| adpcmRAW    | 0.84 | 0.86 | 0.85 | 0.86 | 0.85 |

| Fft         | 0.76 | 0.78 | 0.78 | 0.80 | 0.80 |

| Mpeg2       | 0.91 | 0.90 | 0.91 | 0.91 | 0.92 |

| Streams     | 0.95 | 0.94 | 0.95 | 0.95 | 0.95 |

| vpr         | 0.92 | 0.90 | 0.91 | 0.91 | 0.90 |

Table 1.3 Results for the raw benchmarks: prediction accuracy results as a function of simulation time

| Benchmark | Percentage of predicted hotspots<br>at least 50 cycles in advance (%) |  |  |  |

|-----------|-----------------------------------------------------------------------|--|--|--|

| 8b_encode | 64                                                                    |  |  |  |

| 802.11a   | 69                                                                    |  |  |  |

| adpcmRAW  | 82                                                                    |  |  |  |

| Fft       | 80                                                                    |  |  |  |

| Mpeg2     | 72                                                                    |  |  |  |

| Streams   | 84                                                                    |  |  |  |

| vpr       | 68                                                                    |  |  |  |

collectively configuring the entire network on a cycle-by-cycle basis to enable predictable flow of data.

Seven traces extracted from the Raw's static network, through binaries compiled by the Raw compiler on the Raw cycle-accurate simulator were also used to evaluate the base ANN. The traces accurately match the hardware timing. The same methodology as with the synthetic benchmarks was followed; the ANN prediction accuracy for each of the seven Raw benchmark traces was obtained as before. Table 1.3 shows the accuracy rates obtained during discrete simulation intervals, until the simulation was completed at half a million cycles, while Table 1.4 shows the percentage of those identified hotspots that were detected at least 50 cycles in advance of their future occurrence. It is evident that the ANN remains accurate throughout the simulation, even if for the fast Fourier transform (fft) benchmark, the prediction accuracy is relatively low. The ANN does exceptionally well with three benchmark traces (mpeg2, streams and vpr). The streaming nature of the mpeg2 and stream applications follows a repetitive pattern, therefore if the ANN is properly trained, streaming applications could largely benefit from this.

#### 1.4.4 Hardware Synthesis Results

The ANN is evaluated also in terms of CMOS area requirements and hardware overheads. Hence, the ANN hardware architecture shown in Fig. 1.4 was implemented and synthesized using Synopsys Design Vision, targeting a 65 nm

Table 1.4 Results for the raw benchmarks: percentage of the correctly identified hotspots at least 50 system clock cycles in advance

commercial CMOS technology library. The targeted frequency was 500 MHz, operating at 1 V power supply voltage. Synthesis results indicate that an NoC router with 2 VCs, lookahead routing and speculative switch allocation requires  $\sim$  73,240 gates, while an estimated amount of 67,600 gates is required for the base ANN implementation that controls a  $4 \times 4$  region, making the ANN predictor smaller in area than the aforementioned pipelined router. Thus, the base ANN hardware overhead is 5.8% with respect to the base 16-router region it controls. These results indicate that the ANN predictor can be easily integrated as a PE in a typical NoC architecture. Synopsys' PrimePower is also used to provide an estimate of the power consumption. Using 50% switching activity probability, the ANN consumes an estimated 0.016 mW when computing one hotspot prediction. The estimated power requirements of the ANN predictor are considered negligible when compared to existing real architectures such as Teraflops [2]. Both these results show that the overall hardware and power overheads of the ANN predictor for hotspot management are very low, and thus allow for feasible hardware implementations in an NoC, given the benefits of performance hotspot prediction in on-chip interconnected systems.

#### **1.5 Conclusions and Future Work**

This Chapter presented an intelligent ANN hotspot prediction mechanism. The ANN uses buffer utilization data to dynamically monitor the interconnect fabric, and reactively predicts the location of an about to-be-formed hotspot. The ANN is trained using synthetic traffic models, and evaluated using both real and synthetic application traces. Results show that a relatively small neural network architecture can predict hotspot formation with accuracy ranges between 76 and 92%.

The promising results encourage further research in using intelligent mechanisms for managing NoCs. Further optimized ANNs can be explored in predicting hotspots in NoCs more accurately. Furthermore, the coupling of proactive ANN prediction mechanisms with reactive hotspot reduction mechanisms to avoid the formation of unforeseen hotspots occurring in NoCs can be very beneficial. Additionally, other system information such as link utilization and topology information can be used to enhance the training of the ANN, in order to improve the accuracy and efficiency of the predictor.

#### References

- Baydal E et al (2005) A Family of mechanisms for congestion control in wormhole networks. In IEEE TPDS 16(9):772–784 Sept 2005

- Bell S et al (2008) TILE64 Processor: A 64-Core SoC with mesh interconnect. In: ISSCC, pp 88–598 Feb 2008

- Bertozzi D, Benini L (2004) Xpipes: A Network-on-Chip architecture for gigascale Systemson-Chip. In: IEEE Circ Syst 4(2):18–31, Second Quarter

- Bjerregaard T, Mahadevan S (2006) A survey of research and practices of Network-on-Chip. In ACM CSUR 38(1):1–51 March 2006

- 5. Bolotin E et al (2004) QNoC: QoS architecture and design process for Network on Chip. In Elsevier JSA 50(2–3):105–128 Feb 2004

- 6. Dally WJ (1992) Virtual-channel flow control. In IEEE TPDS 3(2):94-205 March 1992

- Dally WJ, Towles B (2001) Route packets, not wires: on-Chip interconnection networks. In: DAC, pp 684–689 June 2001

- 8. Dally WJ, Towles B (2004) Principles and practices of interconnection networks. Morgan kaufmann publishers Inc. ISBN 9780122007514

- 9. Daneshtalab M et al (2006) NoC hot spot minimization using antNet dynamic routing algorithm. In: ASAP, pp 33–38 Dec 2006

- Duato J et al (2005) A new scalable and cost-effective congestion management strategy for lossless multistage interconnection networks. In: HPCA, pp 108–119 Feb 2005

- 11. Goossens K et al (2005) AEtherealn Network on chip: concepts, architectures, and implementations. In: IEEE DTC, pp 414–421 Sept-Oct 2005

- Hashem S et al (1999) A novel approach for training neural networks for long-term prediction. In IJCNN 3:1594–1599 July 1999

- 13. Hashemi KS et al (1991) On the number of training points needed for adequate training of feedforward neural networks. In: IFNNPS, pp 232–236 July 1991

- 14. Ho WS, Eager DL (1989) A novel strategy for controlling hot-spot congestion. In: IEEE ICPP, pp 14–18

- 15. Gaughan PT, Yalamanchili S (1993) Adaptive routing protocols for hypercube interconnection networks. In IEEE Computer 26(5):12–23 May 1993

- Jain AK et al (1996) Artificial neural networks: a tutorial. In IEEE Computer 29(29):31–44 March 1996

- 17. Maqsood I et al (2004) An ensemble of neural networks for weather forecasting. In Neural Computing & Applications 13(2):112–122 June 2004

- McCoy A et al (2007) Multistep-Ahead Neural-Network Predictors for Network Traffic Reduction in Distributed Interactive Applications. In: ACM TOMACS, 17(4):1–30

- 19. Nilsson E et al (2003) Load Distribution with the Proximity Congestion Awareness in a Network on Chip. In: DATE, pp 11126–11127 March 2003

- 20. Peh L-S, Dally WJ (2000) Flit-Reservation Flow Control. In: HPCA, pp 73-84 Jan 2000

- Pande PP et al (2005) Performance evaluation and design trade-offs for Network-on-Chip interconnect architectures. In IEEE TPDS 54(8):1025–1040 Aug 2005

- 22. Sarbazi-Azad H et al (2001) An analytical model of fully-adaptive wormhole-routed k-ary n-cubes in the presence of hot spot traffic. In IEEE TOC 50(7):623–634 July 2001

- 23. Steven G et al (2001) Dynamic branch prediction using neural networks. In: DSD, pp 178–185 Sept 2001

- 24. Taylor MB et al (2004) Evaluation of the raw microprocessor: an exposed-wire-delay architecture for ILP and streams. In: ISCA, pp 2–13

- Teixeira A et al (2000) A multi-objective optimization approach for training artificial neural networks. In: IEEE SBRN, pp 168–172 Jan 2000

- Vangal S et al (2007) An 80-tile 1.28TFLOPS Network-on-Chip in 65 nm CMOS. In: ISSCC, pp 98–99 Feb 2007

- 27. Walter I et al (2007) Access regulation to hot-modules in wormhole NoCs. In: NoCs, pp 137–148 May 2007

# Chapter 2 Accurate Asynchronous Network-on-Chip Simulation Based on a Delay-Aware Model

Naoya Onizawa, Tomoyoshi Funazaki, Atsushi Matsumoto and Takahiro Hanyu

Abstract A performance-evaluation simulator, such as a cycle-accurate simulator, is a key tool for exploring appropriate asynchronous Network-on-Chip (NoC) architectures in early stages of VLSI design, but its accuracy is insufficient in practical VLSI implementation. In this paper, a highly accurate performanceevaluation simulator based on a delay-aware model is proposed for implementing an appropriate asynchronous NoC system. While the unit delay between circuit blocks at every pipeline stage is constant in the conventional cycle-accurate simulator, which causes poor accuracy, the unit delay between circuit blocks in the proposed approach is determined independently by its desirable logic function. The use of this "delay-aware" model makes it accurate to simulate asynchronous NoC systems. As a design example, a 16-core asynchronous Spidergon NoC system is simulated by the conventional cycle-accurate and the proposed simulator whose results, such as latency and throughput, are validated with a highly precise transistor-level simulation result. As a result, the proposed simulator achieves almost the same accuracy as one of the transistor-level simulators with the simulation speed comparable to the cycle-accurate simulator.

N. Onizawa (🖂) · T. Funazaki · A. Matsumoto · T. Hanyu Research Institute of Electrical Communication, Tohoku University, Sendai, Japan e-mail: onizawa@ngc.riec.tohoku.ac.jp

T. Funazaki e-mail: funazaki@ngc.riec.tohoku.ac.jp

A. Matsumoto e-mail: matumoto@ngc.riec.tohoku.ac.jp

T. Hanyu e-mail: hanyu@ngc.riec.tohoku.ac.jp

#### 2.1 Introduction

With circuit size reaching billions of transistors, traditional shared-bus architectures become unusable for a complex System-on-Chip (SoC). Network-on-Chip (NoC) design paradigm [1] has been recently proposed to provide scalable on-chip global communication [2]. Especially, NoC based on Globally Asynchronous Locally Synchronous (GALS) system [3] takes advantage of the benefits of asynchronous circuits such as low power consumption and communication robustness [4].

On-chip communication performance, such as latency and throughput, in NoC is evaluated based on static performance analyses or system-level simulations for design space exploration of NoC architectures at early stages before implementation [5, 6]. To validate the fast evaluation techniques, a cycle-accurate simulator is useful for performance evaluation of synchronous NoC architectures because behavior of circuits within one clock cycle is precisely simulated [7, 8]. However, on-chip communication in the GALS-NoC is controlled by request-acknowledge based handshaking between modules without a global clock, the asynchronous operations are not performed at a constant period. Therefore, the GALS-NoC performance cannot be accurately evaluated by using the cycle-accurate simulator. For early design exploration of the GALS-NoC architectures, an accurate simulator supporting the asynchronous operation is required to validate the fast evaluation techniques.

This paper presents a highly accurate simulator based on a delay-aware model for evaluation of the on-chip communication performance, such as throughput and latency, in the asynchronous NoC architectures. In the proposed delay-aware model, each asynchronous operation between modules is modeled by a delay module. Since the delay information is selected dependent on conditions by a circuit-delay table, asynchronous on-chip communication operating at different speed can be simulated. The circuit delay is determined by transistor-level simulation results of post-layout asynchronous NoC routers and communication links, which improves the accuracy of the simulation. In addition, as the asynchronous operation is started when the acknowledge information of the previous operation is returned to the module, the delay module is scheduled to be active when inputs to the module satisfy the specific condition. The scheduling makes it possible to simulate local synchronization by the handshake operation between modules.

To evaluate the accuracy of simulations, the proposed and the cycle-accurate simulators are validated using a highly precise transistor-level simulation result in a 16-core asynchronous Spidergon [9] NoC architecture. As a result, the proposed simulator obtains the minimum latency with about 5% error with respect to that with about 35% error from the cycle-accurate simulator at comparable speed.

The rest of this paper is organized as follows. Section 2.2 describes related works and our motivation. Section 2.3 describes a delay-aware model for the asynchronous router. Section 2.4 describes the simulation accuracy of our simulator. Section 2.5 concludes this paper.

#### 2.2 Background and Motivation

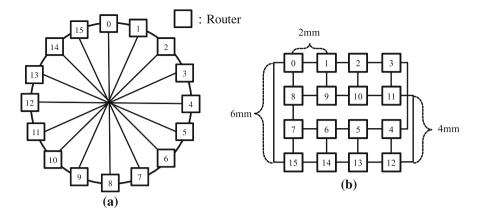

#### 2.2.1 GALS-NoC Architecture

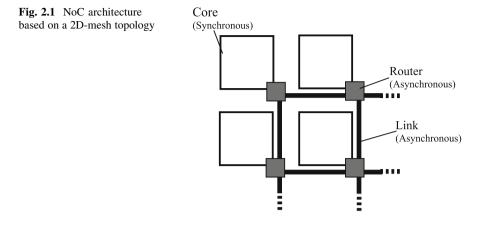

Figure 2.1 shows a typical NoC architecture based on a 2D-mesh topology, which consists of switching routers, communication links between the routers and processing cores. The processing cores transmit/receive data using the inter-core communication network. The switching routers compute where to transmit an incoming data and arbitration between potential concurrent data and finally transmit the selected data on the selected link.

The GALS-NoC architecture is that NoC is implemented based on a GALS system, where processing cores at different clock frequencies transmit/receive data through the asynchronous switching routers [10, 11] and communication links [12, 13]. In general, the asynchronous inter-core communication network is realized by using quasi delay-insensitive(QDI) circuits which are robust against a delay variation because of its timing assumption [14].

#### 2.2.2 Related Work and Contributions

NoC performance, such as throughput and latency are varied with topology, flow control, routing algorithm and flit size. In order to obtain an efficient NoC architecture for specific applications, performance evaluation techniques are extremely important at early stages before implementation. The performance evaluation techniques includes static performance analyses [5, 15] and simulations, where the simulations are done based on non-cycle accurate high-level modeling [16, 6] and cycle-accurate modeling [7, 8]. In general, the static analyses and the non-cycle accurate simulations are used to explore an optimum NoC architecture at early stages because of fast evaluation. To validate the fast

evaluation techniques, the cycle-accurate simulation is used. Since behavior of the circuit, such as routers, is precisely modeled within a clock cycle, on-chip communication performance in the synchronous NoC can be accurately evaluated.

In contrast, since on-chip communication is performed based on requestacknowledge based handshaking without a global clock in the GALS-NoC architecture, the asynchronous circuits are not operated at constant speed. The asynchronous on-chip communication cannot be accurately simulated by the cycle-accurate simulator, which causes inaccurate results of performance evaluation. To validate fast evaluation techniques using the static analyses and the noncycle simulation techniques for the asynchronous NoC design space exploration, an accurate simulation of the asynchronous NoC architecture is required.

In [17], a System C-based simulation technique for performance evaluation of the GALS-NoC architecture has been proposed. The simulator supports the asynchronous transfer delay which is independent of a clock cycle by using the circuit delay in packet switching. However, this is not normally used in the NoC because of hardware overhead, where a complete packet is stored in the router. The circuit delay is not accurate because the asynchronous routers and communication links are not implemented. In addition, the simulator does not support the acknowledge operation, which cannot accurately simulate the handshake operation.

This paper presents a highly accurate simulator to evaluate the on-chip communication performance, such as throughput and latency, in the GALS-NoC architectures. Our contributions of this work are: a) to model the acknowledge operation for the accurate simulation of the asynchronous circuit; b) to use highly precise delay information extracted from transistor-level simulation results of postlayout asynchronous NoC circuits for improving the accuracy; and c) to support wormhole switching which is normally used in NoC because of small hardware.

#### 2.3 Delay-Aware Model for an Asynchronous NoC Simulation

#### 2.3.1 Asynchronous Router

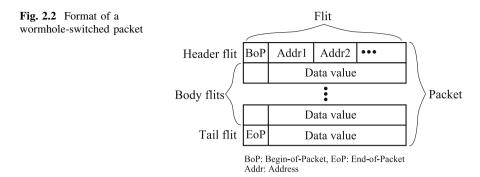

In the GALS-NoC architecture, every core communicates with each other by packet-based communication through asynchronous inter-core network whose elements are asynchronous switched routers and communication links. In wormhole switching, a packet is divided into several flow control digits (flits) which are transferred through the network. Figure 2.2 shows a format of wormhole-switched packets in a deterministic routing algorithm. The packet consists of three types of flits (*FlitType*): a header flit, a body flit and a tail flit. The header flit contains a static routing path in an address field in order to perform the packet routing from one processing core to a destination processing core. The address field contains some sub-addresses, such as Addr1, Addr2... and AddrN. Each router uses one sub-address (Addr1) in the address field and shifts the address field for the following routers.

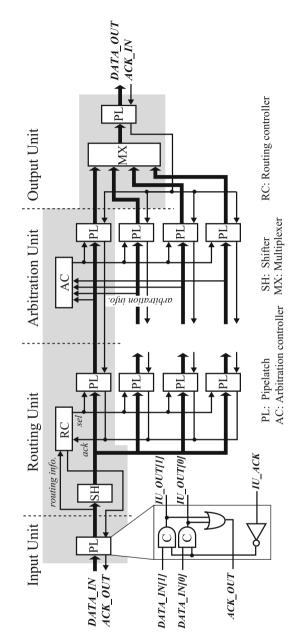

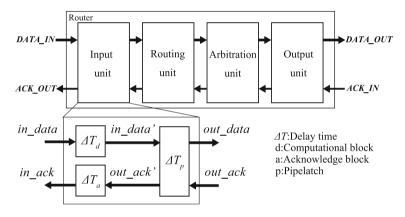

Figure 2.3 shows a block diagram of an asynchronous router which is divided into an input unit, a routing unit, an arbitration unit and an output unit by pipelatches (PLs). The input unit is first-in-first-out (FIFO) buffers for storing incoming flits from other switched routers via communication links or a processing core. The routing unit selects the link based on the address field of the header flit in routing controller (RC) and then transfers the flit to the selected arbitration unit using shifter (SH). The arbitration unit determines a flit which can be transferred to the output unit in arbitration controller (AC). When multiple flits simultaneously request the same output unit, a selected flit is transferred to the output unit, while the other flits remain in the routing unit. The output unit selects a flit from the arbitration unit in multiplexer (MX) and then transfers the flit to other switched routers via communication links or a processing core.

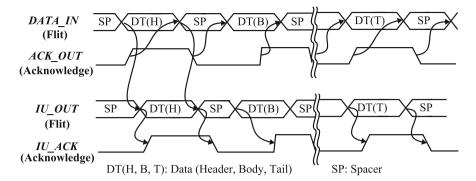

In the asynchronous router, a flit in each unit is asynchronously transferred by request-acknowledge based handshaking between PLs which are connected with the input and the output of its unit. In general, the asynchronous router is designed by using a QDI logic circuit based on a 4-phase protocol. A flit with the request information is encoded as data represented by a 1-of-N signal, while spacer is inserted into two time-consecutive data to distinguish them [14], where data and spacer are defined by *PhaseType* shown in Table 2.1. PL is implemented by C-elements [18] and an OR gate. The C-element is a standard asynchronous storage element, whose output is low (high) when all inputs are low (high), and which otherwise holds its value. When the 1-of-N signal (data) is stored in the C-elements, one of inputs to the OR gate becomes high, which asserts an output of the OR gate. In contrast, the output of the OR gate is deasserted when spacer is stored in the C-elements. The output signal of the OR gate means acknowledge information of the data or spacer. PhaseType of the acknowledge information is DataPhase when the output signal of the OR gate is high, and SpacerPhase when low shown in Table 2.1.

Figure 2.4 shows an example of an asynchronous router operation. Firstly, a header flit with the request information (data) is stored in PL of the input unit. Secondly, PL of the input unit asserts *ACK\_OUT* as acknowledge information of data whose *PhaseType* is DataPhase. This leads to changing *DATA\_IN* from data to spacer whose *PhaseType* is Spacer Phase. Thirdly, spacer is stored in PL of the

input unit when the acknowledge information of data is arrived to PL of the input unit from the next unit (router unit). This means that a flit (data or spacer) is stored in PL when the flit ( $DATA_IN$ ) and the acknowledge information ( $IU_ACK$ ) have different *PhaseType*. Finally, PL of the input unit deasserts *ACK\_OUT* as acknowledge information of spacer.

Fig. 2.3 Block diagram of an asynchronous router

Fig. 2.4 Example of an asynchronous router operation

Fig. 2.5 Asynchronous router based on the delay-aware model

This represents one cycle of the asynchronous operation based on the 4-phase protocol. Namely, the asynchronous unit is operated based on a one-cycle delay time which is varied with *FlitType* and *PhaseType*, since the operations are different on the conditions.

#### 2.3.2 Delay-Aware Model

To simulate accurately latency and throughput of a specific asynchronous NoC architecture, the proposed delay-aware model captures the functionality and timing information of each unit operating at different speed. Figure 2.5 shows the asynchronous router based on the delay-aware model. Each unit between PLs is modeled by a delay module based on the delay information of its desirable logic function. The delay module includes computation delay time ( $\Delta T_a$ ) and pipelatch delay time ( $\Delta T_p$ ).  $\Delta T_d$  is delay time that the flit is

| Table 2.1   PhaseType of the                                  |            |             |                 | PhaseType       |

|---------------------------------------------------------------|------------|-------------|-----------------|-----------------|

| asynchronous signal                                           | Flit       |             | Data            | DataPhase       |

|                                                               |            |             | Spacer          | SpacerPhase     |

|                                                               | Acknowledg | e           | High            | DataPhase       |

| Table 2.2         Delay time           dependent on PhaseType |            |             | Low             | SpacerPhase     |

|                                                               |            |             | PhaseType       |                 |

| and <i>FlitType</i>                                           |            |             | DataPhase       | SpacerPhase     |

|                                                               | FlitType   | Header flit | $\Delta T_{hd}$ | $\Delta T_{hs}$ |

|                                                               |            | Body flit   | $\Delta T_{bd}$ | $\Delta T_{bs}$ |

|                                                               |            | Tail flit   | $\Delta T_{td}$ | $\Delta T_{ts}$ |

transferred over computational blocks between PLs.  $\Delta T_p$  is delay time that the flit is stored in the C-elements of PL.  $\Delta T_a$  is delay time that the acknowledge information is transferred over the OR gate of PL and combinational blocks between PLs after the flit is stored in PL. Each delay time is determined by *FlitType* and *PhaseType* of an input in the delay module shown in Table 2.2

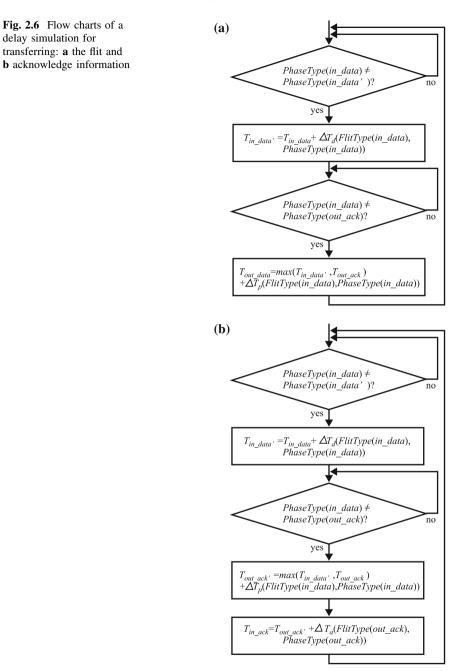

As the flit is transferred to the next unit while the acknowledge information is transferred to the previous unit in each unit, two kinds of delay time is simulated. Figure 2.6a shows a flow chart of a delay simulation for transferring the flit in the delay module.  $T_x$  is the arrival time of signal *x*. Firstly,  $T_{in\_data}$  is determined when *PhaseType* (*in\\_data*) and *PhaseType* (*in\\_data'*) are not the same, which means that a new flit is arrived to the unit. Secondly,  $\Delta T_d$  is selected based on *FlitType* and *PhaseType* of *in\_data* shown in Table 2.2. Then,  $T_{in\_data'}$  is calculated by adding the  $\Delta T_d$  to  $T_{in\_data}$ . Thirdly,  $T_{in\_data'}$  and  $T_{out\_ack}$  are compared and then the larger one is selected when *PhaseType* (*in\_data*) and *PhaseType* (*un\_data*) are not the same. Finally,  $T_{out\_data}$  is calculated by adding  $\Delta T_p$ .

Figure 2.6b shows a flow chart of a delay simulation for transferring the acknowledge information in the delay module. Two flow charts shown in Fig. 2.6 are almost the same.  $T_{out\_ack'}$  can be simulated as  $T_{out\_data}$  shown in Fig. 2.6a. Then,  $\Delta T_a$  is determined by *FlitType* and *PhaseType* of *out\\_ack* and is then added to  $T_{out\_ack'}$ .

#### 2.4 Evaluation

#### 2.4.1 Simulation Environment

Figure 2.7 shows simulation environment for performance evaluation of asynchronous NoC architectures. It is assumed that a target asynchronous NoC architecture is simulated by a testbench which calculates latency and throughput from the

simulation result. The target NoC architecture includes asynchronous routers (Rs) modeled as Sect. 2.3.2 and interconnect wires between routers. The interconnect wire is modeled as a delay element based on its wire length. Packet Transceivers (PTs) and

Fig. 2.8 Block diagram of a Packet Tranceiver (PT)

Controller are included in the testbench. The target asynchronous NoC architecture and the testbench are described using Verilog HDL.

In CT, packets are generated based on parameters, such as packet size, flit size and offered traffic. The packets are partitioned into flits, which are in turn encoded by 1-of-N signals, where information of a static routing path between source and destination PTs is embedded in the header flit. The encoded flits are transmitted to the source and the destination PTs based on the information of the static routing path.

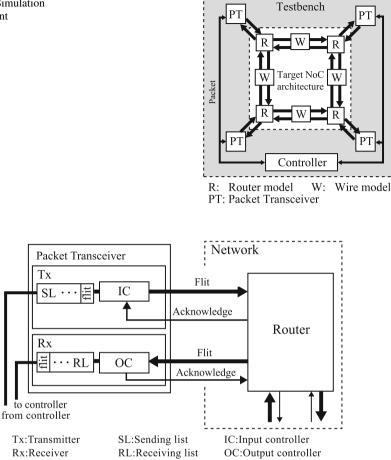

Figure 2.8 shows a block diagram of PT which is composed of transmitter (Tx) and receiver (Rx). Tx includes sending list (SL) and input controller (IC). Rx includes receiving list (RL) and output controller (OC). The encoded flits transmitted from CT are stored in SL when the header flit indicates that PT is the source of the routing path, or are stored in RL when the header flit indicates that PT is the destination of the routing path.

Fig. 2.9 16-core Spidergon NoC: a topology, b physical layout

In Tx, since the asynchronous operation based on the handshake protocol is not operated at constant speed, the flits should be transferred to a router in the target asynchronous NoC architecture when IC detects that the acknowledge signal from the router is changed. Time to transfer the flit is recorded in SL for calculation of latency and throughput. In Rx, the flits from other PTs are received. When the received flit is the same as the previously stored flit in RL, time to receive the flit is recorded in RL for calculation of latency and throughput. Then, OC changes the acknowledge signal of the flit from the router.

#### 2.4.2 Simulation Accuracy

To evaluate the accuracy of simulators, a 16-core asynchronous Spidergon [9] NoC architecture shown in Fig. 2.9 is simulated by the conventional cycle-accurate simulator and the proposed simulator whose results, such as latency, are validated with a highly precise transistor-level simulation result. Each node (router) has links to its clockwise and counter-clockwise neighboring nodes, and a direct link to its diagonally opposite neighbor shown in Fig. 2.9a. In the physical layout shown in Fig. 2.9b, the physical connections between routers only need to cross at one point. It is assumed that each processing core with its router is connected by three types of wires whose lengths are 2, 4 and 6 mm.

In the 16-core asynchronous Spidergon NoC architecture, asynchronous routers and the communication links are designed by the QDI logic circuit based on a 4-phase dual-rail encoding. The packet is partitioned into 12-bit flits. BoP and EoP are represented respectively by 1 bit, while data value or address is represented by 10 bits depicted in Fig. 2.2. The transistor-level simulation results are obtained by NanoSim under a ROHM 0.18  $\mu$ m CMOS technology. The conventional cycle-accurate and the proposed simulators are described by Verilog HDL.

| Tuble 2.5 Router latency versus the number of packet consisting |      |      |       |       |  |  |

|-----------------------------------------------------------------|------|------|-------|-------|--|--|

| # of packet collisions                                          | 0    | 1    | 2     | 3     |  |  |

| Proposed [ns]                                                   | 55.2 | 83.5 | 111.7 | 139.9 |  |  |

| Cycle-accurate [ns]                                             | 62.8 | 94.3 | 125.8 | 157.2 |  |  |

| Transistor-level [ns]                                           | 57.6 | 86.9 | 115.6 | 145   |  |  |

Table 2.3 Router latency versus the number of packet collisions

Fig. 2.10 Minimum latency in the 16-core asynchronous Spidergon NoC architecture

Table 2.3 shows latencies of the asynchronous router versus the number of packet collisions where one packet consists of 15 flits. The latencies are  $D_t, D_c$  and  $D_p$  from the transistor-level, the cycle-accurate and the proposed simulators, respectively, where an error is defined as a ratio of an absolute difference  $|D_t-D_c|$  or  $|D_t-D_p|$  to  $D_t$ . The latencies in the cycle-accurate simulator differ from those in the transistor-level simulator by about a 10% error because all units are simulated at a constant period limited by the worst-case delay. In contrast, as the proposed simulator simulate each unit operating at different speed by using the delay-aware model, the latencies can be obtained within a 5% error in comparison with one of the transistor-level simulators.

Figure 2.10 shows the minimum latencies through the 16-core asynchronous Spidergon NoC architecture which is dependent on the number of flits in one packet. Actually, the flit transmission in the asynchronous NoC is performed at different speed determined by the routing path. However, in the cycle-accurate simulator, the flit transmission in every unit is simulated at low speed dependent on the longest (6 mm) wire, which causes about a 35% error. In contrast, the flit

transmission in each unit is simulated at different speed in the proposed simulator. Therefore, the minimum latencies can be obtained within 5% error in comparison with one of the transistor-level simulators.

The proposed and the cycle-accurate simulator run at almost the same time which is about 4 orders of magnitude faster than the transistor-level simulator.

# 2.5 Conclusion

In this paper, a highly accurate asynchronous NoC simulator has been proposed for validation of fast evaluation techniques, such as static performance analyses and system-level simulators which are used for early design space exploration of NoC architectures. Since the asynchronous operation is modeled by a delay module, where the delay time is changed based on a flit type, the non-periodic operation based on the handshake protocol can be accurately simulated. As a result, the proposed simulator achieves almost the same accuracy as the transistor-level simulator with the comparable speed to the cycle-accurate simulator.

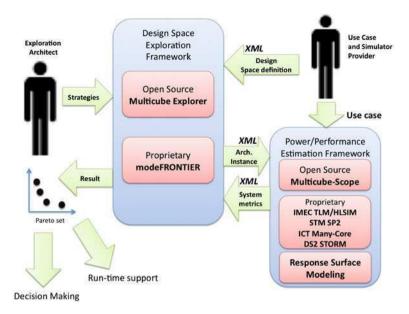

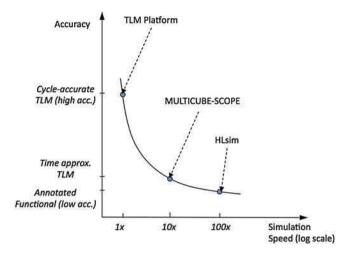

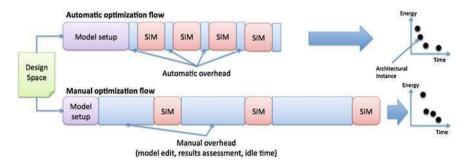

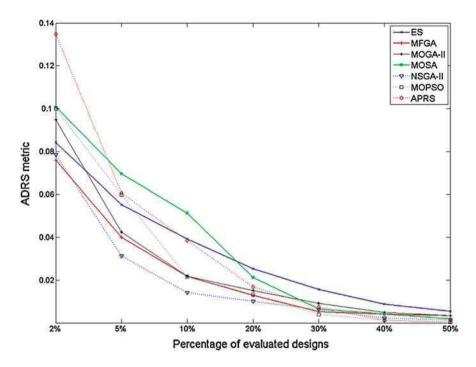

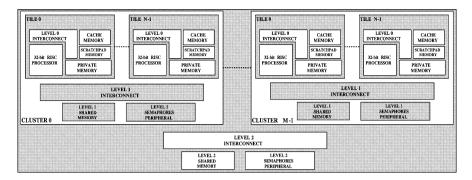

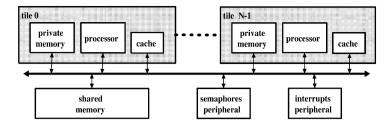

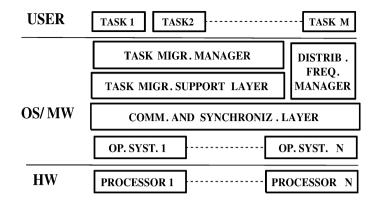

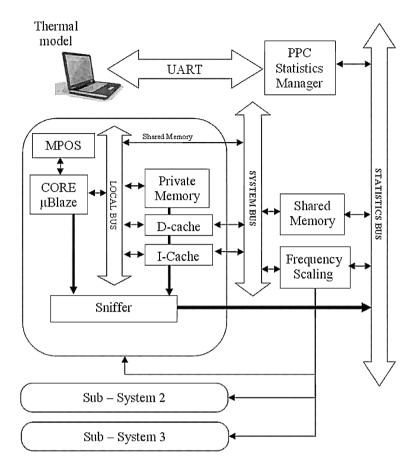

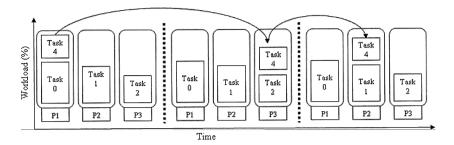

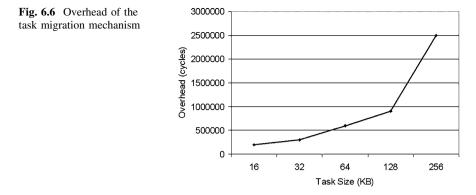

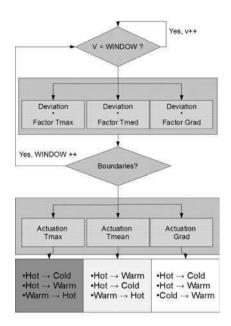

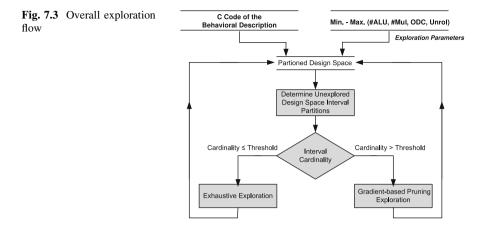

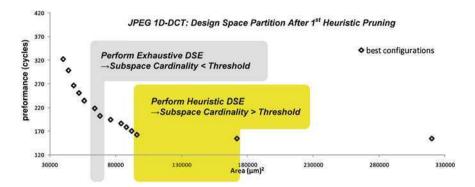

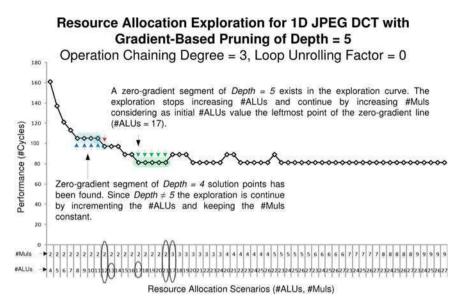

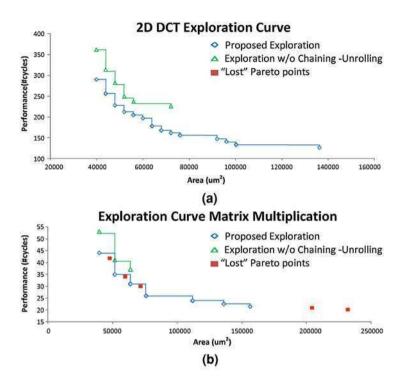

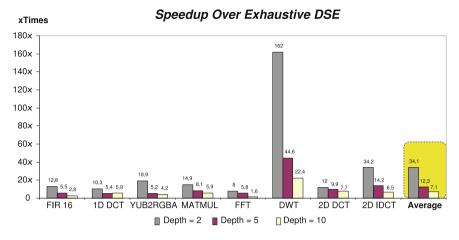

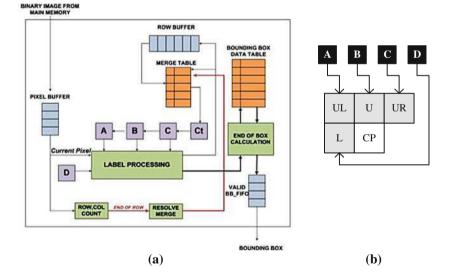

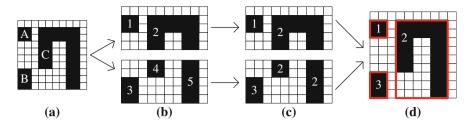

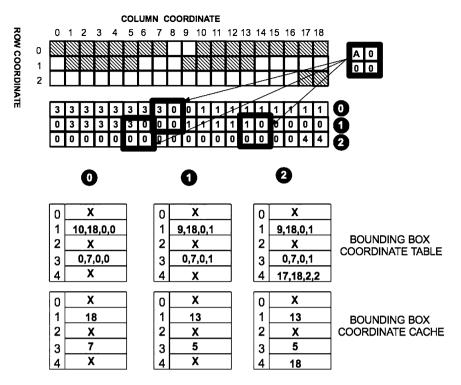

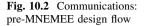

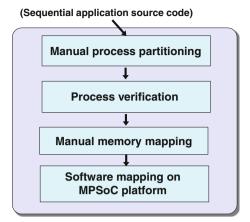

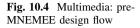

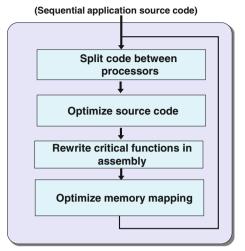

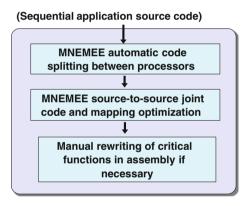

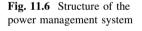

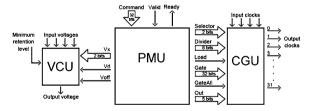

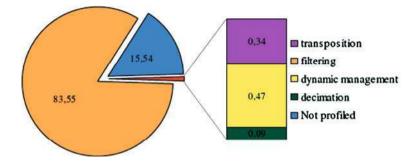

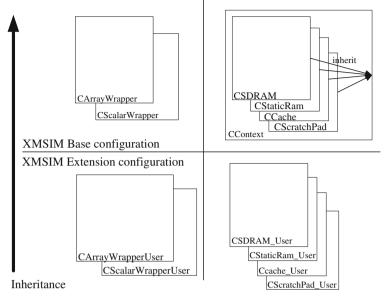

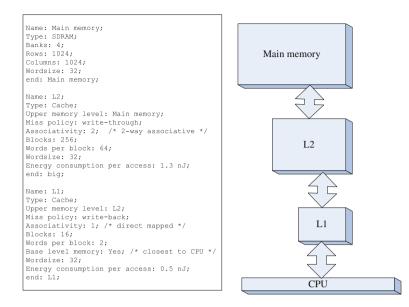

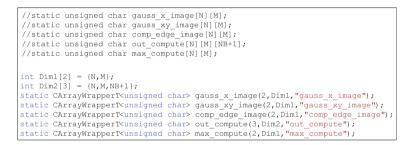

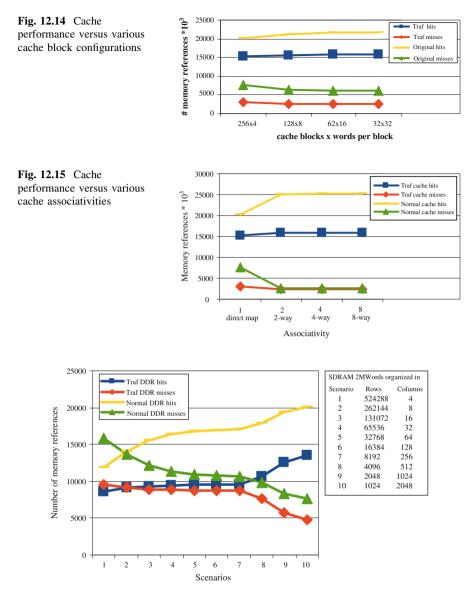

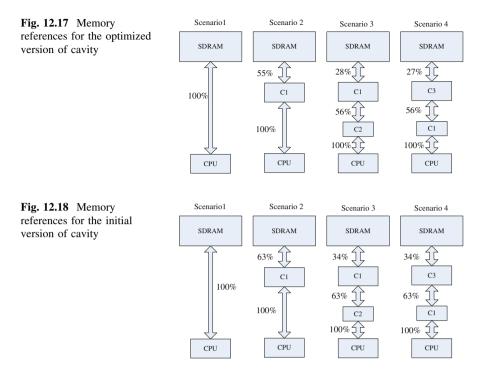

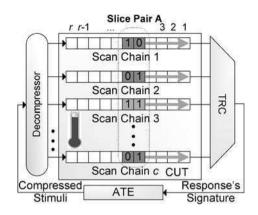

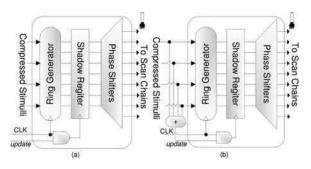

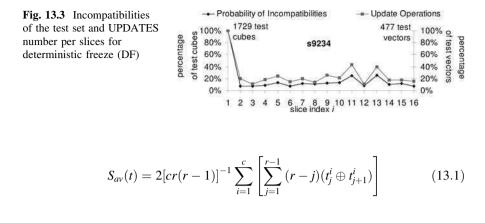

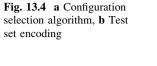

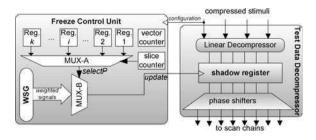

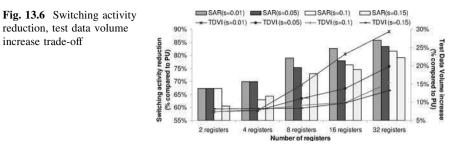

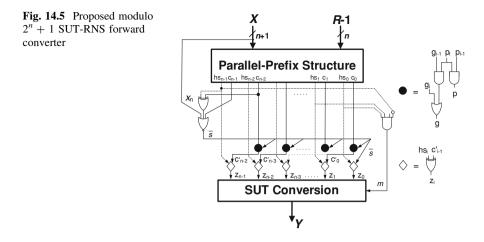

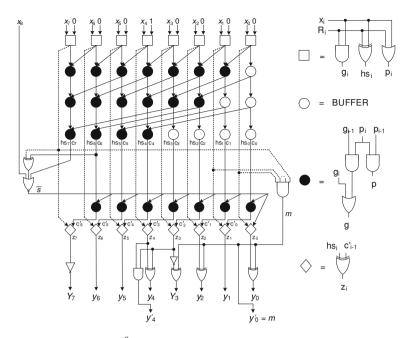

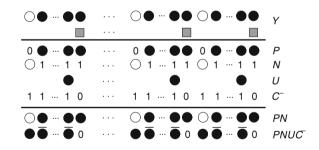

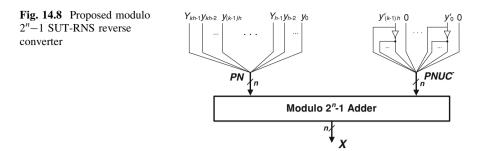

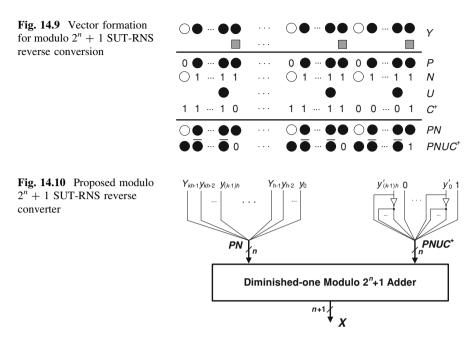

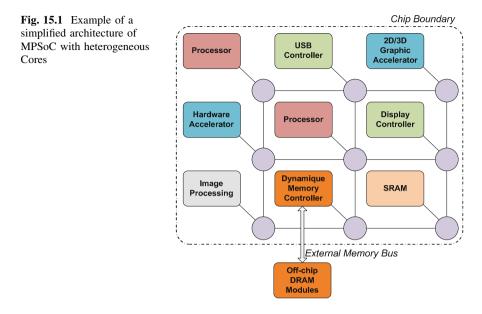

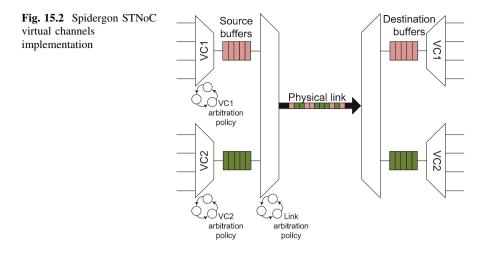

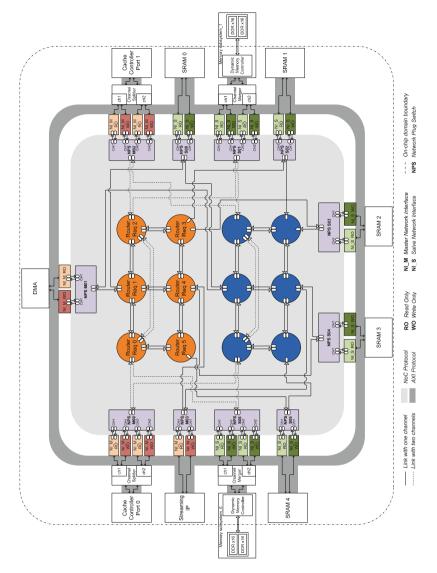

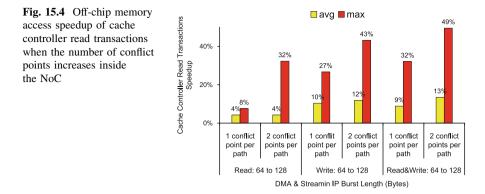

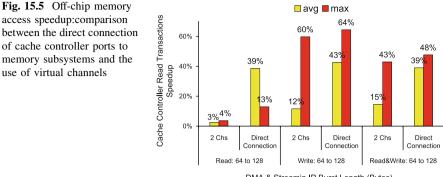

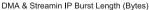

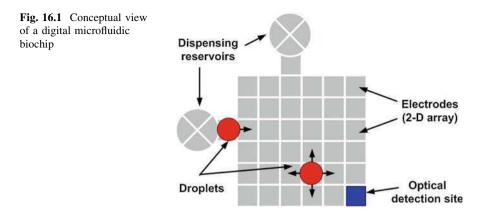

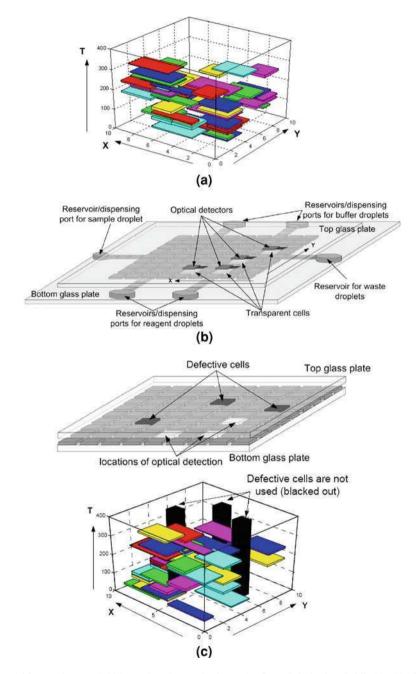

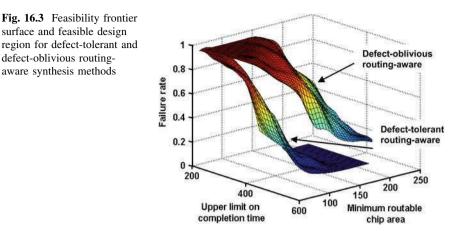

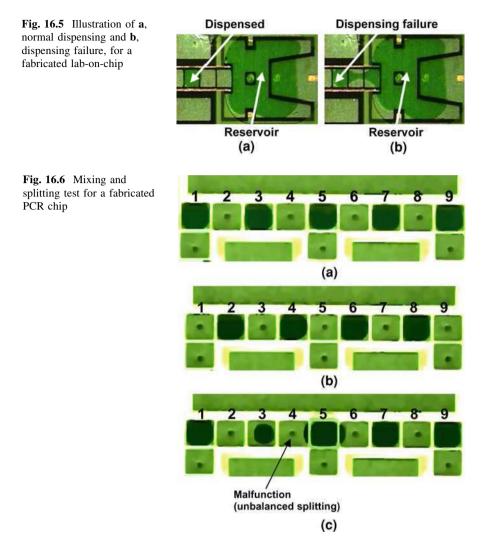

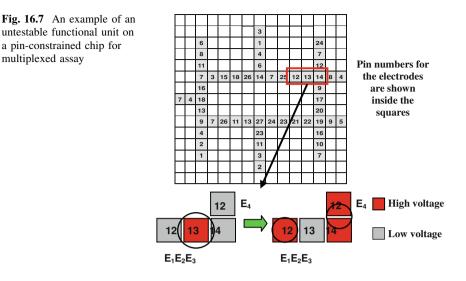

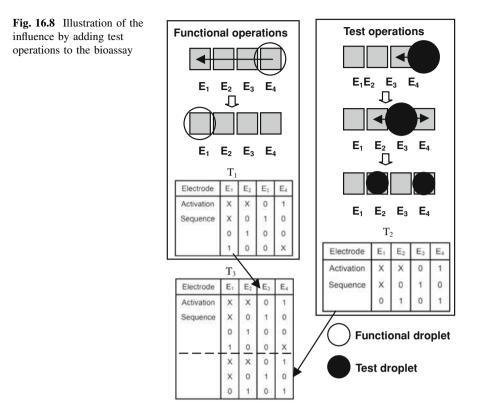

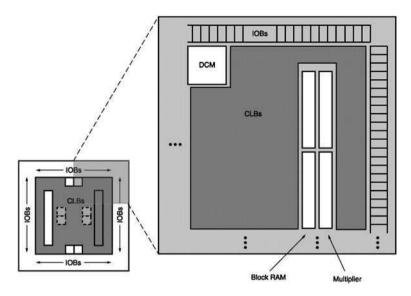

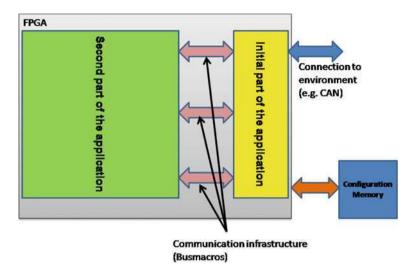

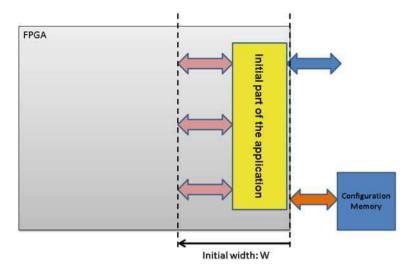

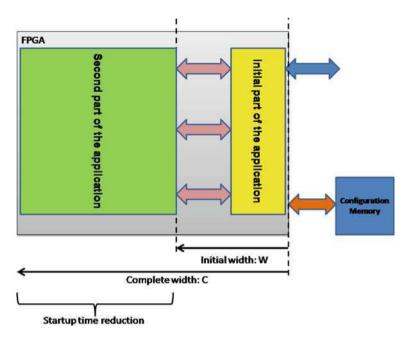

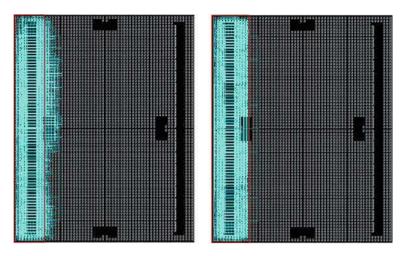

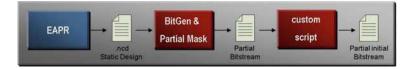

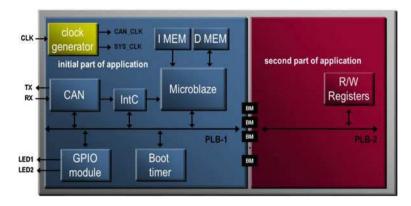

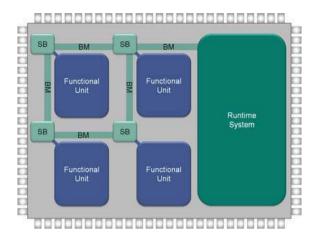

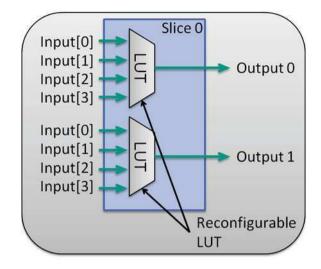

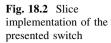

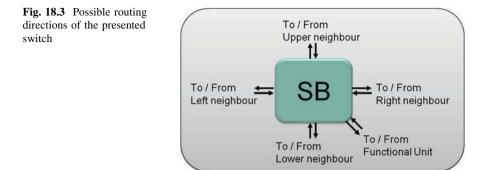

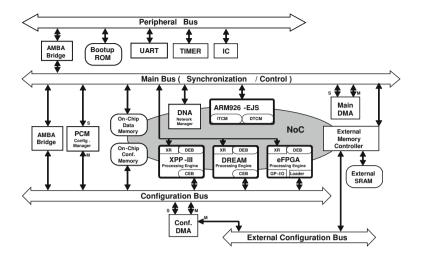

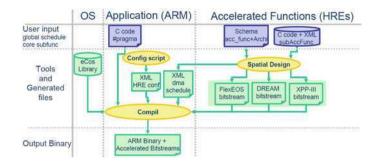

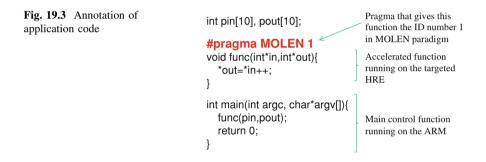

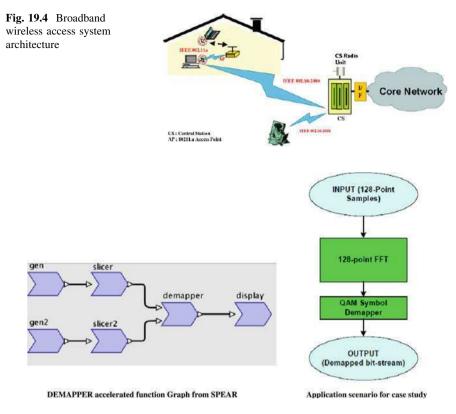

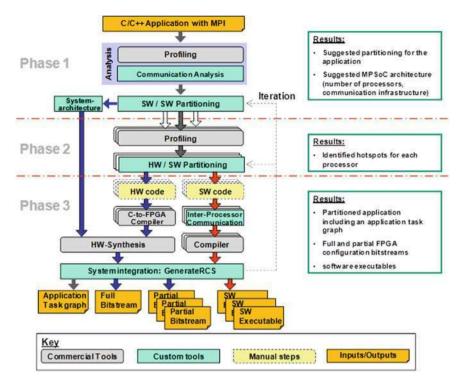

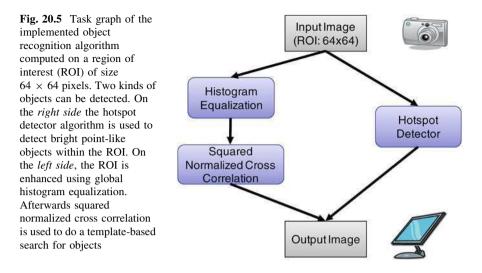

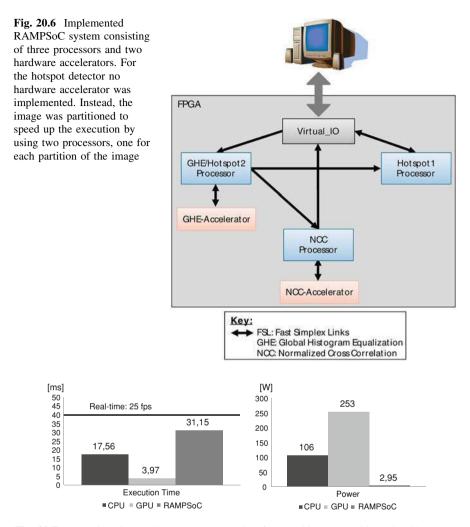

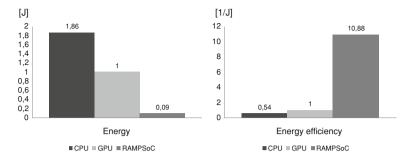

The future direction includes building a fast system-level asynchronous NoC simulator, whose accuracy is validated with the proposed simulator upon different topologies.