**ACSP** · Analog Circuits And Signal Processing

Robert H.M. van Veldhoven Arthur H.M. van Roermund

# Robust Sigma Delta Converters

And Their Application In Low-Power Highly-Digitized Flexible Receivers

### Robust Sigma Delta Converters

#### ANALOG CIRCUITS AND SIGNAL PROCESSING

Consulting Editor: Mohammed Ismail. Ohio State University

Robert H.M. van Veldhoven • Arthur H.M. van Roermund

# Robust Sigma Delta Converters

And Their Application in Low-Power Highly-Digitized Flexible Receivers

Dr. ir. Robert H.M. van Veldhoven NXP Semiconductor, Central R&D Mixed Signal Circuits & Systems High Tech Campus, Building 32, room 3.24 5656 AE Eindhoven The Netherlands Robert.van.Veldhoven@nxp.com

Series Editors:

Mohammed Ismail

205 Dreese Laboratory

Department of Electrical Engineering

The Ohio State University

2015 Neil Avenue

Columbus, OH 43210

USA

Prof. dr. ir. Arthur H.M. van Roermund Electrical Engineering Mixed-signal Microelectronics Group Technical University Eindhoven Den Dolech 2 5612 AZ Eindhoven The Netherlands A.H.M.v.Roermund@tue.nl

Mohamad Sawan Electrical Engineering Department École Polytechnique de Montréal Montréal, QC Canada

ISBN 978-94-007-0643-9 e-ISBN 978-94-007-0644-6 DOI 10.1007/978-94-007-0644-6 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: 2011920957

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: eStudio Calamar S.L.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### **Preface**

The foundation of this book is based on my very exciting time at Philips Research Laboratories and later at NXP Research. After 14 years of research on Sigma Delta Converters and other IP blocks, I have learned that IC design and in particular the design of Sigma Delta Converters is not only a very interesting and multi-dimensional research topic, but is also a religion interpreted differently by each and every individual. In the book, I have tried to include my work, view and experience in the field of Sigma Delta Converters to give the reader a head-start in the design of this intriguing type of analog to digital converter.

The book rests on the experience of designing, and coaching others to design tens of different Sigma Delta Converters for numerous applications, like instrumentation, hearing aids, mobile phones, battery management, car radio, etc. In this book the application area of Sigma Delta Converters is limited to cellular and connectivity terminals, to limit the scope.

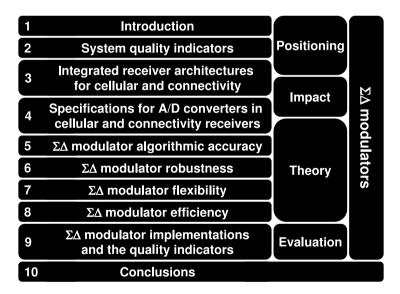

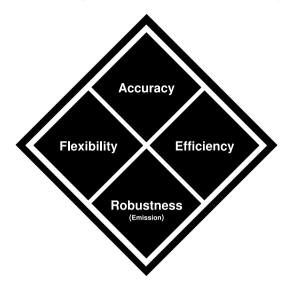

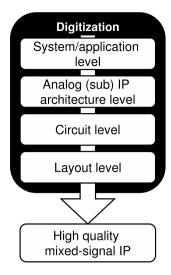

I partitioned the book systematically, by looking at what exactly determines the quality of a system. The found so-called quality indicators (Algorithmic accuracy, Robustness, Emission, Flexibility and Efficiency) are used as a framework throughout the book. The book shows all different aspects in the design of Sigma Delta Converters: system level specification and design, IP architecture, circuit implementation and layout are all subjects of this book. Also the verification of theory and silicon implementations by measurements is included. The book assumes some background on receiver architectures, Sigma Delta Converter theory, and IC design.

I very much hope you enjoy reading the book, and while reading, please do not forget: Analog design is beautiful, digital design is just a time discrete and quantized portion of it.

Valkenswaard January 2011 Robert H.M. van Veldhoven

### **Contents**

| 1 | Intr | Introduction                                                                |    |  |

|---|------|-----------------------------------------------------------------------------|----|--|

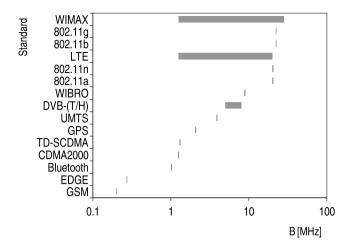

|   | 1.1  | Advanced, Multi-standard Cellular and Connectivity Terminals                |    |  |

|   |      | for the Mass Market                                                         | 2  |  |

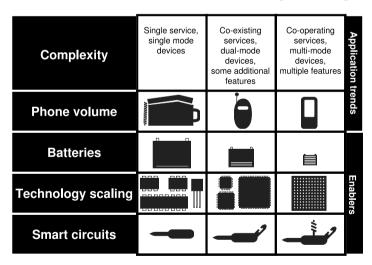

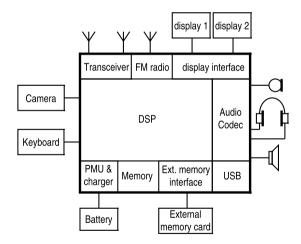

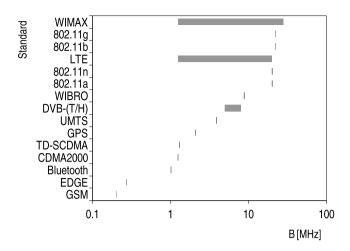

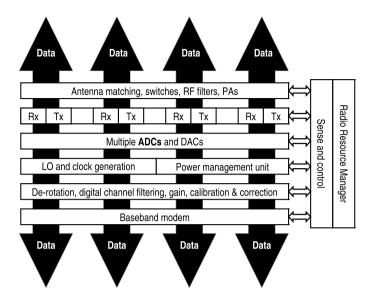

|   |      | 1.1.1 Complexity: Mobile Phone Trends, Its Impact on the                    |    |  |

|   |      | Transceiver and the Quest for Integration                                   | 3  |  |

|   |      | 1.1.2 Transistor Scaling: VLSI and Moore                                    | 7  |  |

|   |      | 1.1.3 Smarter Circuits: $\Sigma\Delta$ Modulators for Mobile Applications . | 9  |  |

|   | 1.2  | Book Aims                                                                   | 10 |  |

|   | 1.3  | Book Scope                                                                  | 11 |  |

|   | 1.4  | Outline                                                                     | 11 |  |

| 2 | Syst | tem Quality Indicators                                                      | 13 |  |

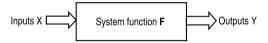

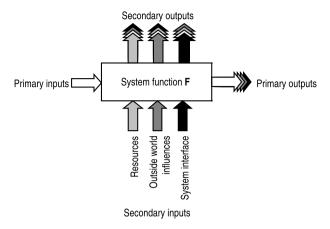

|   | 2.1  | The System Function and Its In- and Outputs                                 | 14 |  |

|   | 2.2  | System Quality                                                              | 15 |  |

|   |      | 2.2.1 Accuracy                                                              | 16 |  |

|   |      | 2.2.2 Robustness to Secondary Inputs                                        | 16 |  |

|   |      | 2.2.3 Flexibility                                                           | 16 |  |

|   |      | 2.2.4 Efficiency                                                            | 17 |  |

|   |      | 2.2.5 Emission of Secondary Outputs                                         | 17 |  |

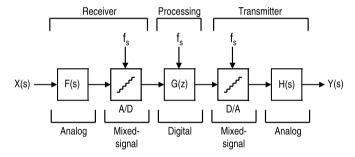

|   | 2.3  | The Digital Revolution                                                      | 18 |  |

|   |      | 2.3.1 The Analog-Digital Interface                                          | 19 |  |

|   |      | 2.3.2 Digital Systems and the Quality Indicators                            | 20 |  |

|   | 2.4  | Conclusions                                                                 | 23 |  |

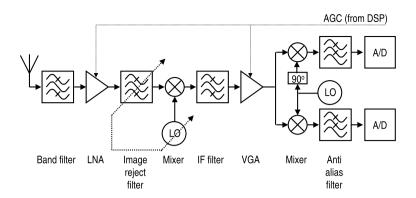

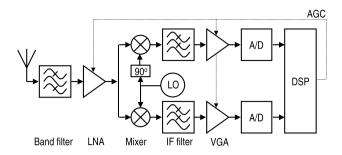

| 3 | Inte | grated Receiver Architectures for Cellular and Connectivity                 | 27 |  |

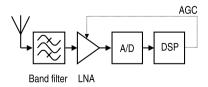

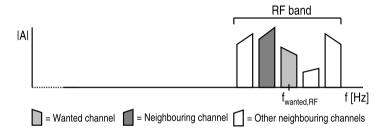

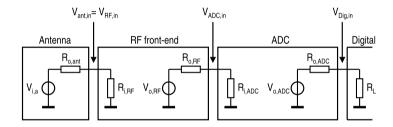

|   | 3.1  | Wireless Receiver Architectures for Digital Communication                   | 27 |  |

|   | 3.2  | Receiver Architecture and the Quality Indicators                            | 30 |  |

|   | 3.3  | Conclusions                                                                 | 31 |  |

viii Contents

| 4 | Spe             | Specifications for A/D Converters in Cellular and Connectivity |                                                                |    |

|---|-----------------|----------------------------------------------------------------|----------------------------------------------------------------|----|

|   | Rec             | eivers                                                         |                                                                | 33 |

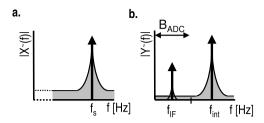

|   | 4.1             | IF Ch                                                          | oice                                                           | 34 |

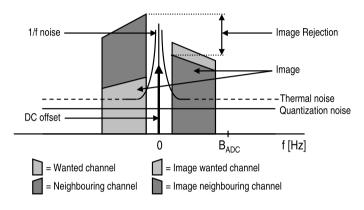

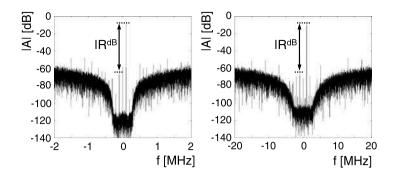

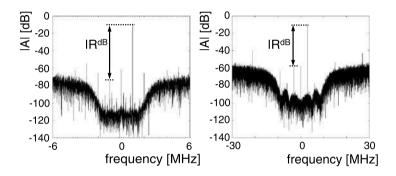

|   |                 | 4.1.1                                                          | Image Rejection                                                | 34 |

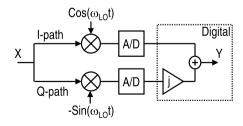

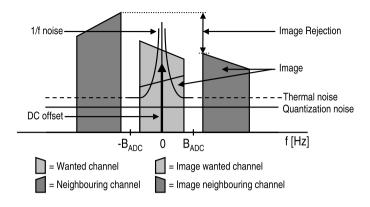

|   |                 | 4.1.2                                                          | Zero IF Architecture                                           | 35 |

|   |                 | 4.1.3                                                          | Near Zero and High IF Architecture                             | 37 |

|   |                 |                                                                | IF Assessment                                                  |    |

|   |                 |                                                                | DC Offset and 1/f Noise                                        | 38 |

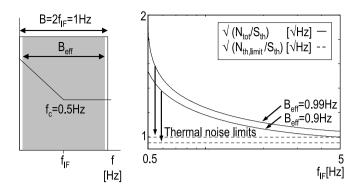

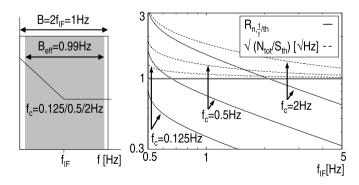

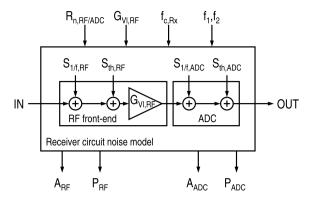

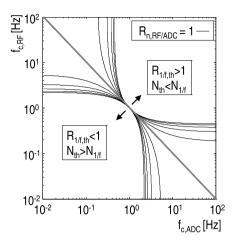

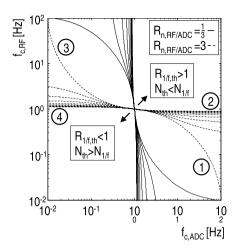

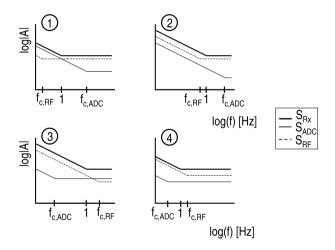

|   |                 | 4.1.6                                                          | RF Front-End and ADC 1/f-Thermal Noise Corner                  |    |

|   |                 |                                                                | Frequency                                                      | 41 |

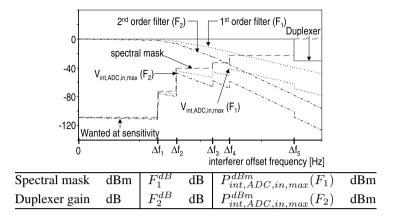

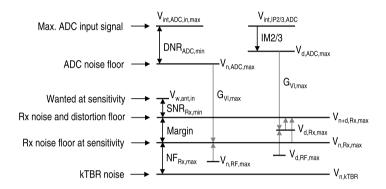

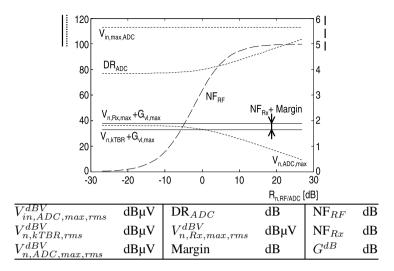

|   | 4.2             | Top-E                                                          | and of the ADC DR                                              | 45 |

|   |                 |                                                                | Signal Levels, Selectivity, and Maximum ADC Input Signal       | 46 |

|   |                 | 4.2.2                                                          | Crest Factor                                                   | 48 |

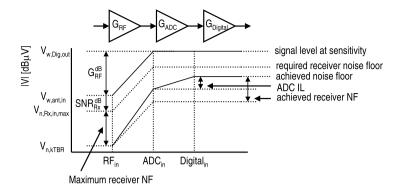

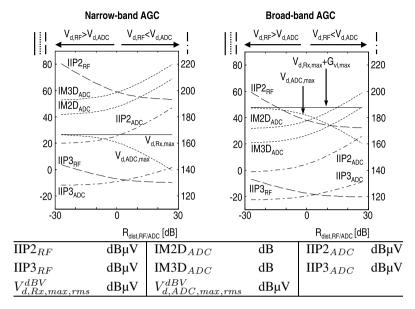

|   | 4.3             | Recei                                                          | ver Gain                                                       | 49 |

|   |                 |                                                                | Narrow vs. Broad Band AGC                                      | 50 |

|   | 4.4             |                                                                | m-End of the ADC DR                                            |    |

|   |                 |                                                                | Receiver SNR Requirement                                       |    |

|   |                 | 4.4.2                                                          | Receiver Noise Figure and ADC Noise Floor                      |    |

|   | 4.5             |                                                                | f the ADC                                                      |    |

|   |                 |                                                                | DR of a Quadrature ADC                                         |    |

|   | 4.6             |                                                                | ont-End and ADC Linearity Requirements                         |    |

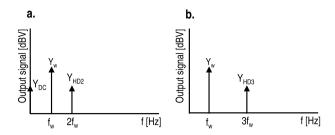

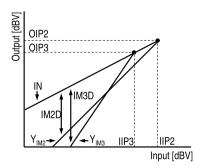

|   |                 | 4.6.1                                                          | Second and Third Order Harmonic Distortion                     |    |

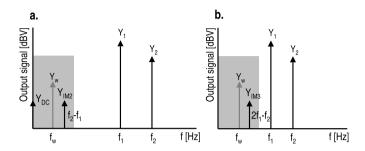

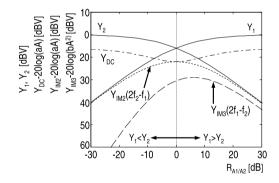

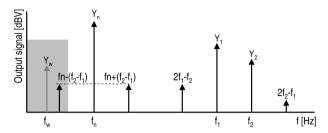

|   |                 |                                                                | Second and Third Order Intermodulation and IP2 and IP3 .       |    |

|   |                 |                                                                | Third Order Cross-Modulation                                   |    |

|   |                 |                                                                | Distortion in a Quadrature ADC                                 |    |

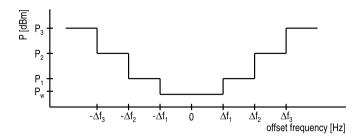

|   | 4.7             |                                                                | ple Receiver Partitioning: Receiver for a GSM Mobile Phone     | 61 |

|   |                 |                                                                | IF Choice and Image Rejection                                  | 62 |

|   |                 |                                                                | Top-End of the ADC Dynamic Range                               | 63 |

|   |                 | 4.7.3                                                          | Receiver Sensitivity Requirement and the Bottom-End            |    |

|   |                 |                                                                | of the ADC Dynamic Range                                       |    |

|   |                 |                                                                | Receiver Linearity Requirement and ADC Linearity               | 66 |

|   | 4.8             |                                                                | Requirements, the System Quality Indicators and $\Sigma\Delta$ |    |

|   |                 |                                                                | lators as the ADC Architecture                                 |    |

|   | 4.9             | Concl                                                          | usions                                                         | 70 |

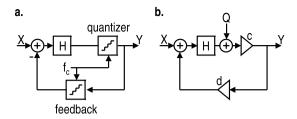

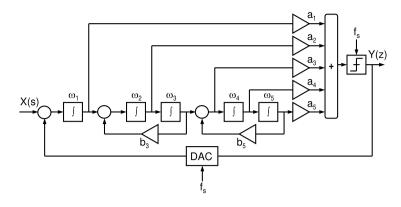

| 5 | $\Sigma \Delta$ |                                                                | llator Algorithmic Accuracy                                    | 71 |

|   | 5.1             |                                                                | Modulators with 1-bit Quantizer and 1-bit DAC                  | 73 |

|   | 5.2             |                                                                | Modulators with $b$ -bit Quantizer and $b$ -bit DAC            | 78 |

|   | 5.3             | $\Sigma\Delta$ N                                               | Modulators with 1.5-bit Quantizer and DAC                      | 79 |

|   | 5.4             | $\Sigma\Delta$ N                                               | Modulators with Multiple Quantizers and 1-bit DAC              | 80 |

Contents ix

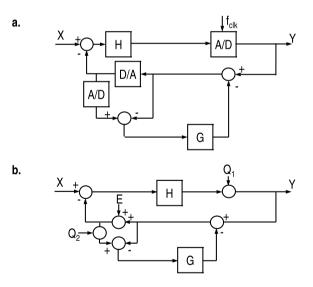

|   | 5.5             |        | Modulators with Additive Error-Feedback Loops 82                    |

|---|-----------------|--------|---------------------------------------------------------------------|

|   | 5.6             |        | $\operatorname{ded} \Sigma\Delta$ Modulators                        |

|   | 5.7             | Concl  | usions                                                              |

| 6 | $\Sigma \Delta$ |        | dator Robustness 91                                                 |

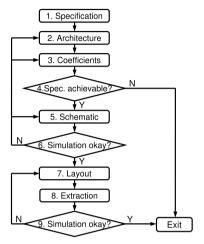

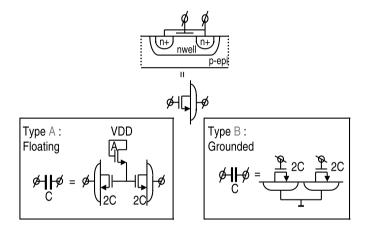

|   | 6.1             | Portab | ole, Technology Robust Analog IP and Time-to-Market 92              |

|   |                 | 6.1.1  |                                                                     |

|   |                 |        | Parameters                                                          |

|   |                 | 6.1.2  | A Design Methodology to Increase the Portability                    |

|   |                 |        | of Analog IP                                                        |

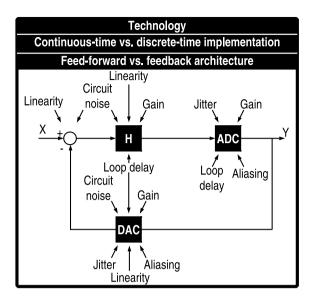

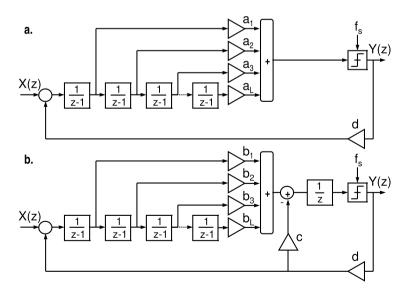

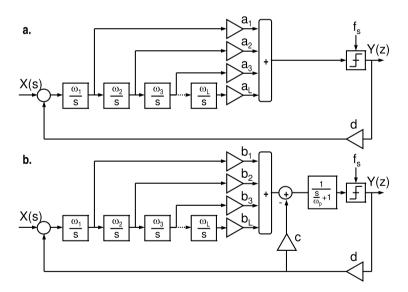

|   | 6.2             |        | nuous Time vs. Discrete Time Loop Filter 97                         |

|   | 6.3             |        | Forward vs. Feedback Loop Filter                                    |

|   | 6.4             |        | Accuracy                                                            |

|   |                 |        | $\Sigma\Delta$ Modulator with 1-bit Quantizer and 1-bit DAC 101     |

|   |                 |        | $\Sigma\Delta$ Modulator with b-bit Quantizer and b-bit DAC 101     |

|   |                 | 6.4.3  | $\Sigma\Delta$ Modulator with Multiple Quantizers and 1-bit DAC 101 |

|   |                 |        | $\Sigma\Delta$ Modulator with Additive Error Feedback Loops 102     |

|   |                 |        | Cascaded $\Sigma\Delta$ Modulators                                  |

|   | 6.5             | Circui | it Noise of the Modulator's Input Stage and DAC 105                 |

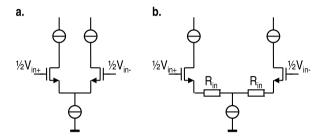

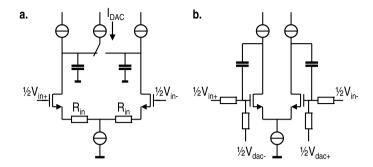

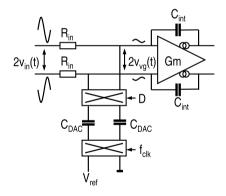

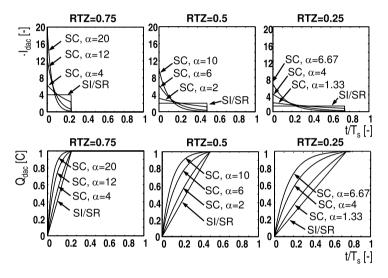

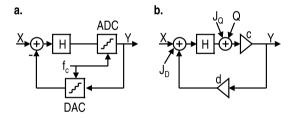

|   |                 | 6.5.1  | RC Integrator Input Stage and SI Feedback DAC 105                   |

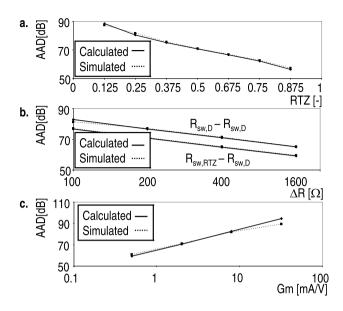

|   |                 | 6.5.2  | RC Integrator Input Stage and SR Feedback DAC 106                   |

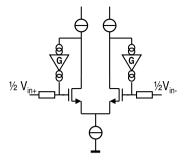

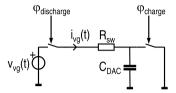

|   |                 | 6.5.3  | RC Integrator Input Stage and SC Feedback DAC 106                   |

|   |                 | 6.5.4  | 1 11 7 &                                                            |

|   |                 |        | Requirements                                                        |

|   | 6.6             | Non-l  | inearity                                                            |

|   |                 | 6.6.1  | Non-linearity in the Input Stage                                    |

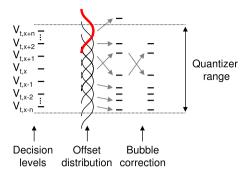

|   |                 | 6.6.2  | Non-linearity in the Quantizer Decision Levels 111                  |

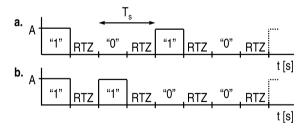

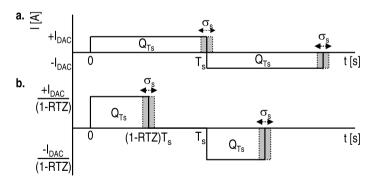

|   |                 | 6.6.3  | Inter-Symbol-Interference in the Feedback DAC 112                   |

|   |                 | 6.6.4  | Non-linearity in the Output Levels of the Feedback DAC 113          |

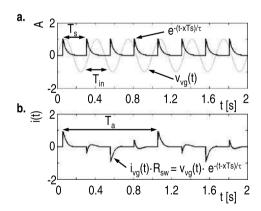

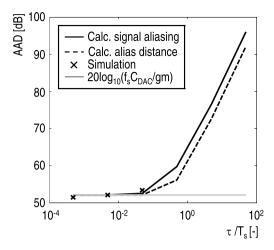

|   | 6.7             | Aliasi | ng in $\Sigma\Delta$ Modulators                                     |

|   |                 | 6.7.1  | Aliasing in the Quantizer                                           |

|   |                 | 6.7.2  | $\Sigma\Delta$ Modulator with an SI Feedback DAC 117                |

|   |                 | 6.7.3  |                                                                     |

|   |                 | 6.7.4  | $\Sigma\Delta$ Modulator with an SC Feedback DAC 122                |

|   | 6.8             | Exces  | s Loop Delay                                                        |

|   |                 | 6.8.1  | Excess Time Delay Compensation                                      |

|   |                 | 6.8.2  | Excess Phase Compensation                                           |

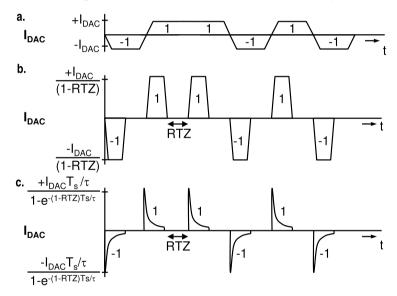

|   |                 | 6.8.3  | DAC Feedback Pulse Shape and Delay                                  |

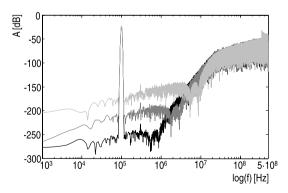

|   | 6.9             | Clock  | Jitter in CT $\Sigma\Delta$ Modulators                              |

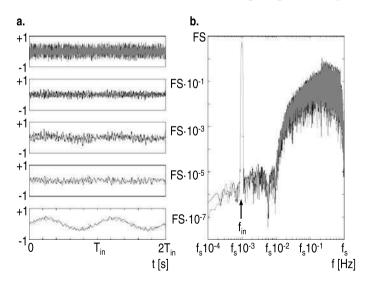

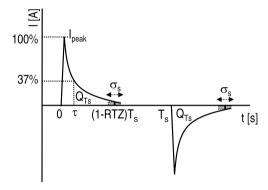

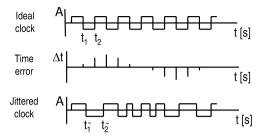

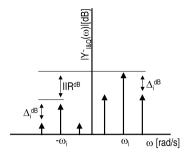

|   |                 | 6.9.1  | The TAJE Model                                                      |

x Contents

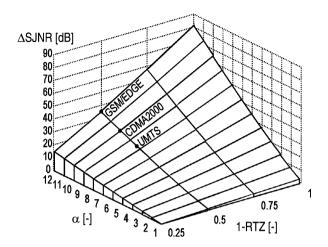

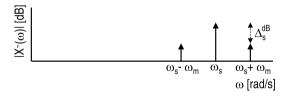

|   |                 | 6.9.2 The TPJE Model: Sine Wave Induced Jitter                      | 139 |

|---|-----------------|---------------------------------------------------------------------|-----|

|   |                 | 6.9.3 The TPJE Model: Substitution of White Noise Jitter            |     |

|   |                 | in the Sine Wave Induced Jitter Model                               |     |

|   |                 | 6.9.4 The TPJE Model: SI Versus SC Feedback DAC                     | 161 |

|   |                 | 6.9.5 The TPJE Model: An Application Driven Choice Between          |     |

|   |                 | SI Versus SC Feedback DAC                                           | 162 |

|   | 6.10            | Conclusions                                                         | 169 |

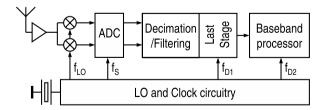

| 7 | $\Sigma \Delta$ | . Modulator Flexibility                                             | 175 |

|   | 7.1             | Receiver Dictated Flexibility Requirements                          | 175 |

|   | 7.2             | $\Sigma\Delta$ Modulator Clock Flexibility                          | 177 |

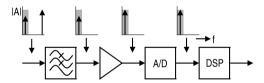

|   |                 | 7.2.1 Receiver Architecture with LO-Dependent ADC Clock             | 178 |

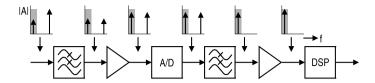

|   |                 | 7.2.2 Receiver Architecture with a Flexible and Independent Clock   |     |

|   |                 | for the ADC                                                         | 179 |

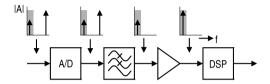

|   |                 | 7.2.3 Receiver Architecture with Fixed, Independent ADC Clock       | 180 |

|   |                 | 7.2.4 Choice of Clock Strategy                                      | 182 |

|   | 7.3             | Input Stage and DAC Flexibility                                     | 183 |

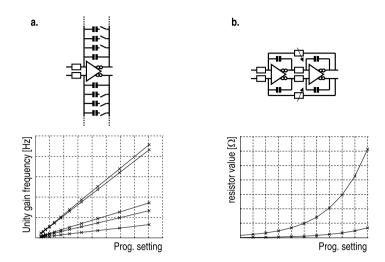

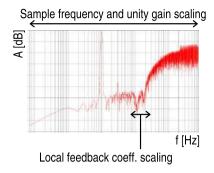

|   | 7.4             | Loop-Filter Flexibility                                             | 183 |

|   | 7.5             | Quantizer Flexibility                                               | 185 |

|   | 7.6             | Conclusions                                                         | 186 |

| 8 | $\Sigma \Delta$ | Modulator Efficiency                                                | 189 |

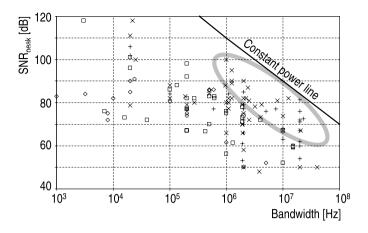

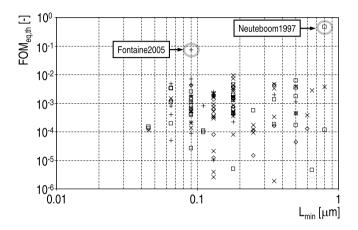

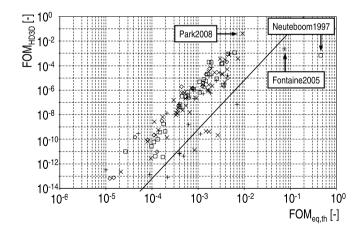

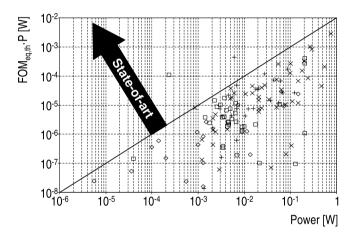

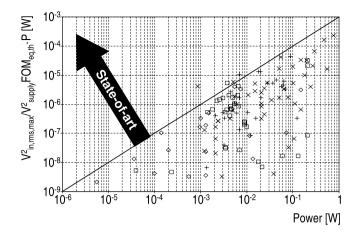

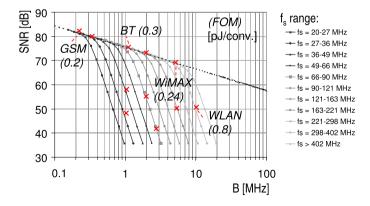

|   | 8.1             | Power Efficiency FOM: FOM $_{DR}$                                   | 191 |

|   |                 | 8.1.1 Benchmarking with $FOM_{DR}$                                  | 193 |

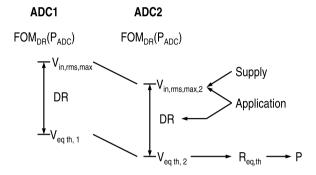

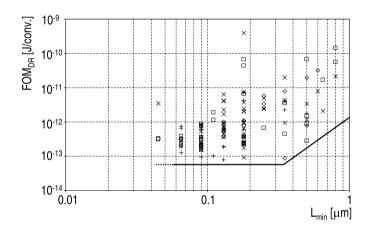

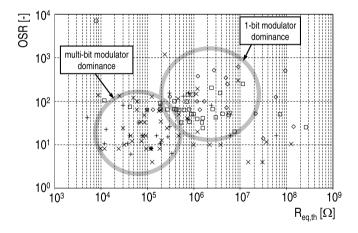

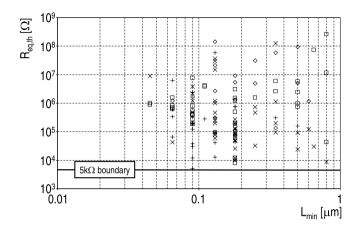

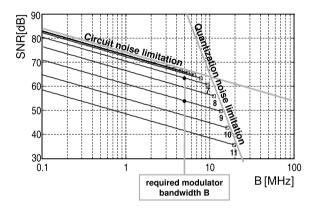

|   | 8.2             | Power Efficiency FOM: $FOM_{eq,th}$                                 | 194 |

|   |                 | 8.2.1 Benchmarking with $FOM_{eq,th}$                               | 197 |

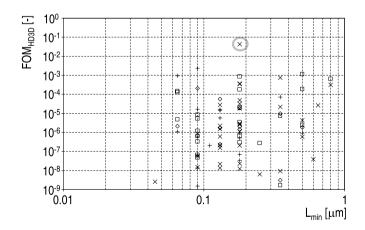

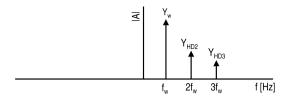

|   | 8.3             | Distortion FOM: FOM $_{HD3D}$                                       | 200 |

|   |                 | 8.3.1 Benchmarking with $FOM_{HD3D}$                                | 202 |

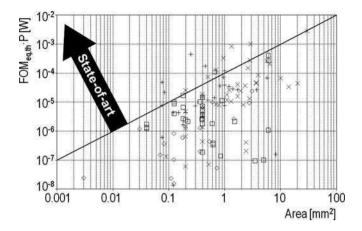

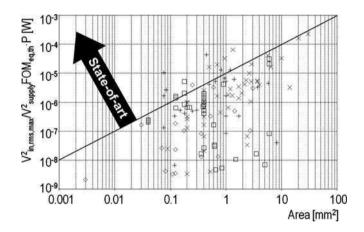

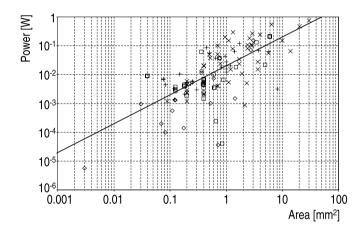

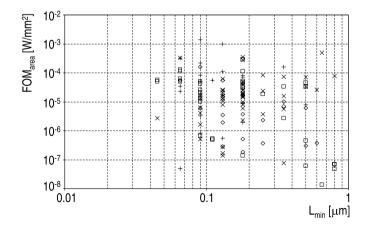

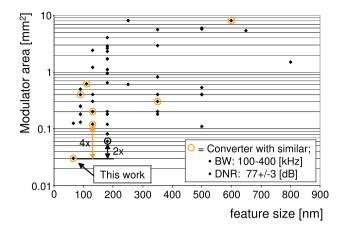

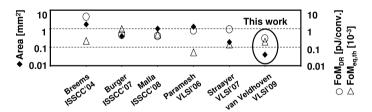

|   | 8.4             | Area FOM: $FOM_{area}$                                              | 205 |

|   |                 | 8.4.1 Benchmarking with $FOM_{area}$                                | 209 |

|   | 8.5             | Conclusions                                                         | 211 |

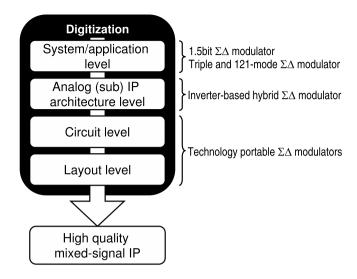

| 9 | $\Sigma \Delta$ | Modulator Implementations and the Quality Indicators                | 213 |

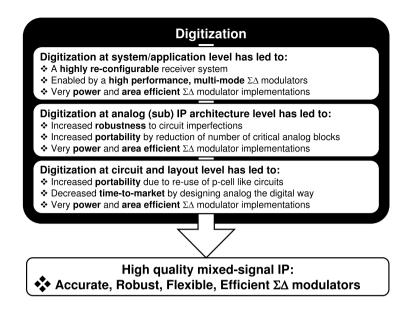

|   | 9.1             | Digitization at System/Application Level: $\Sigma\Delta$ Modulators |     |

|   |                 | for Highly Digitized Receivers                                      |     |

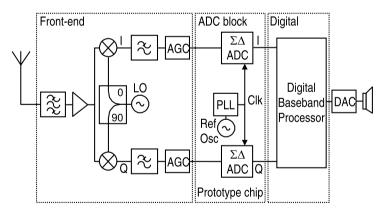

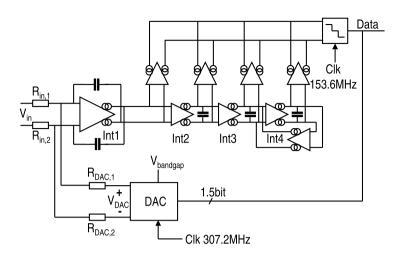

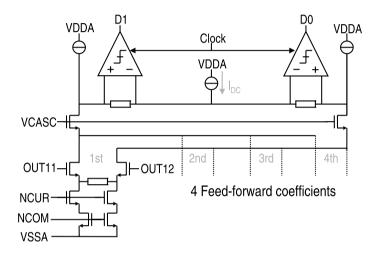

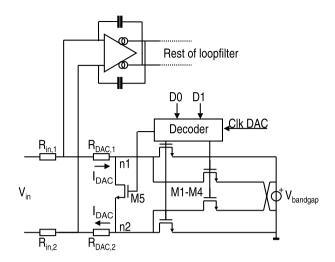

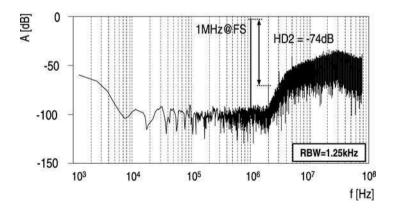

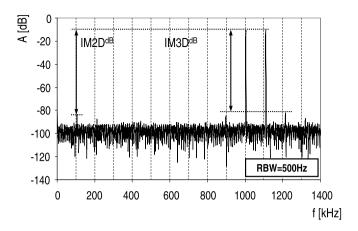

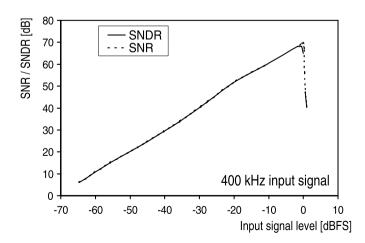

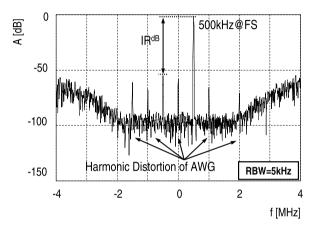

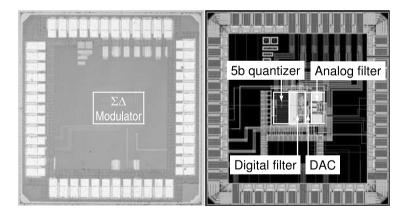

|   |                 | 9.1.1 A 1.5-bit $\Sigma\Delta$ Modulator for UMTS                   | 215 |

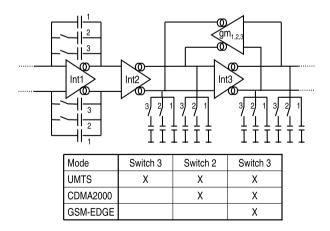

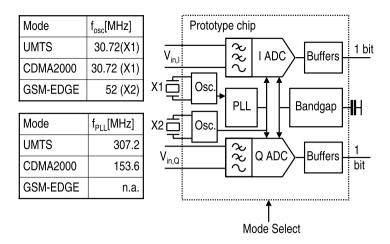

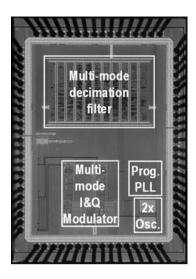

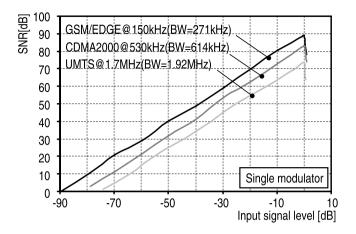

|   |                 | 9.1.2 A Triple-Mode $\Sigma\Delta$ Modulator for GSM-EDGE, CDMA2000 |     |

|   |                 | and UMTS                                                            | 222 |

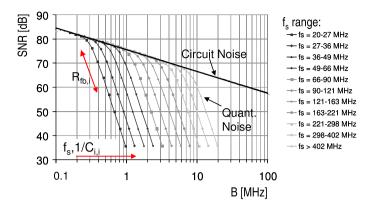

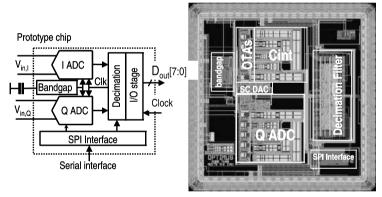

|   |                 | 9.1.3 An Extremely Scalable $\Sigma\Delta$ Modulator for Cellular   |     |

|   |                 | and Wireless Applications                                           | 232 |

Contents xi

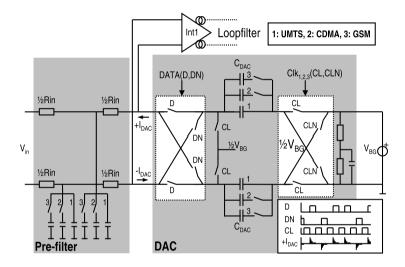

|             | 9.2               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Multi-mode Modulator Clock Strategy zation at Analog IP Architecture Level: A Hybrid, | 238                                                       |

|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------|

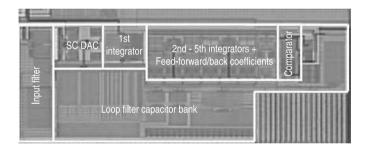

|             | <b>7.2</b>        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | er-Based $\Sigma\Delta$ Modulator                                                     | 240                                                       |

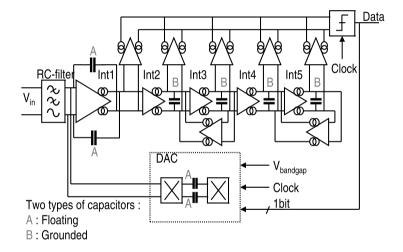

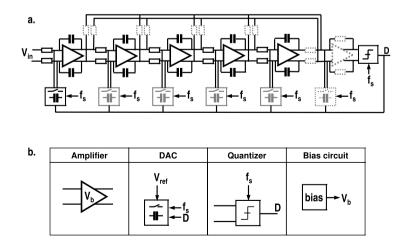

|             |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\Sigma\Delta$ Modulator Architecture                                                 |                                                           |

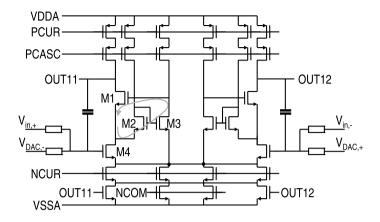

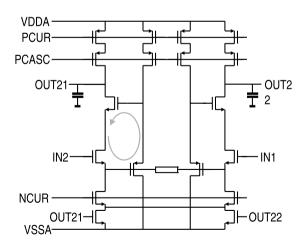

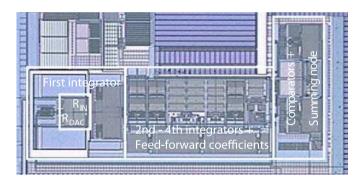

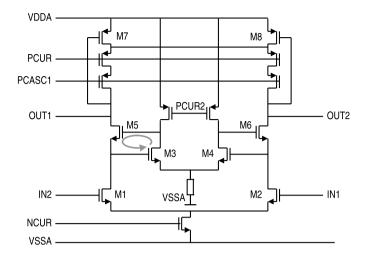

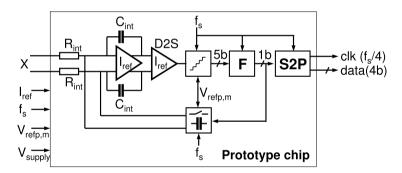

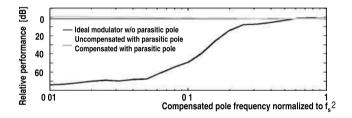

|             |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Circuit Design                                                                        |                                                           |

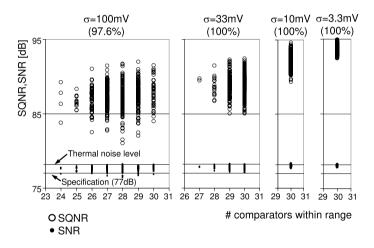

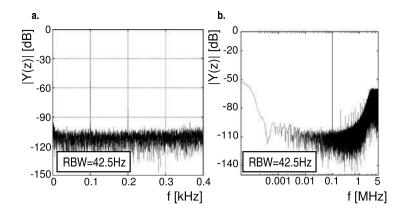

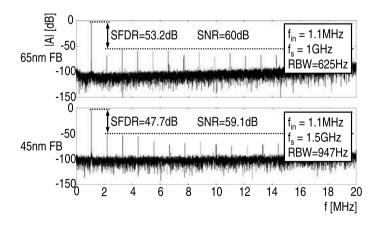

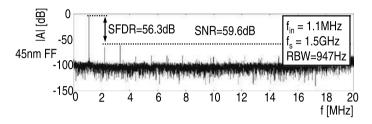

|             |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Experimental Results                                                                  |                                                           |

|             |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Conclusions                                                                           |                                                           |

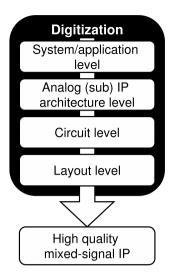

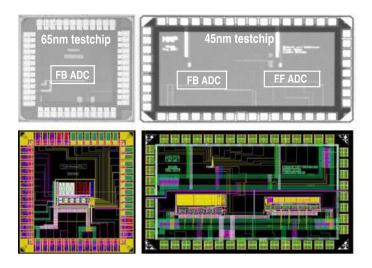

|             | 9.3               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | zation at Circuit and Layout Level: Technology Portable $\Sigma\Delta$                |                                                           |

|             |                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | lators                                                                                | 249                                                       |

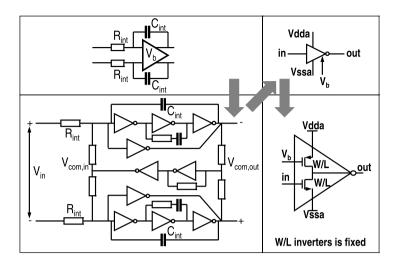

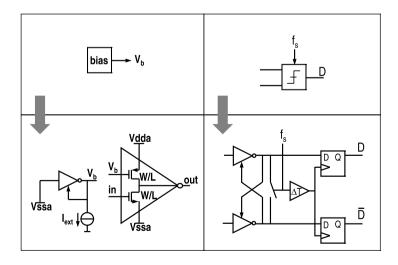

|             |                   | 9.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $\Sigma\Delta$ Modulator Architecure                                                  | 250                                                       |

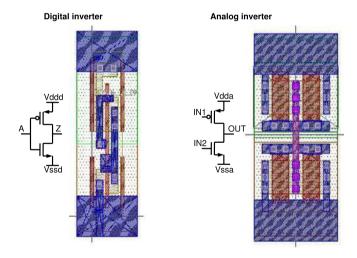

|             |                   | 9.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Circuit Design and Layout                                                             | 251                                                       |

|             |                   | 9.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Conclusions                                                                           | 256                                                       |

|             | 9.4               | Imple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | mentations Judged on the FOMs and Quality Indicators                                  | 257                                                       |

|             | 9.5               | Concl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | usions                                                                                | 260                                                       |

| 10          | Con               | clusio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ns                                                                                    | 263                                                       |

|             |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |                                                           |

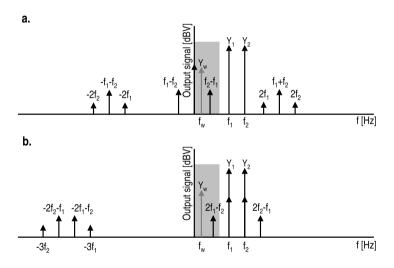

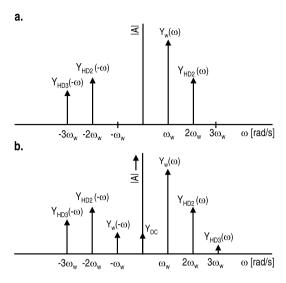

| A           | Har               | monic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | and Intermodulation Distortion in an I&Q System                                       | 265                                                       |

| A           |                   | Doub                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | le Sided Spectrum of Second and Third Order Distortion                                |                                                           |

| A           | A.1               | Double of a C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | le Sided Spectrum of Second and Third Order Distortion complex Signal                 |                                                           |

| A           | A.1               | Double of a Couble                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | le Sided Spectrum of Second and Third Order Distortion                                | 265                                                       |

|             | A.1<br>A.2        | Double of a Couble | le Sided Spectrum of Second and Third Order Distortion complex Signal                 | 265                                                       |

|             | A.1 A.2 Dist      | Double of a Couble | le Sided Spectrum of Second and Third Order Distortion complex Signal                 | 265                                                       |

|             | A.1 A.2 Dist      | Double of a Contion a Cortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | le Sided Spectrum of Second and Third Order Distortion complex Signal                 | <ul><li>265</li><li>266</li></ul>                         |

| В           | A.1 A.2 Dist Inve | Double of a C Double in a C cortion ersion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | le Sided Spectrum of Second and Third Order Distortion complex Signal                 | 265<br>266<br><b>269</b>                                  |

| B<br>C      | A.1 A.2 Dist Inve | Double of a C Double in a C cortion ersion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | le Sided Spectrum of Second and Third Order Distortion complex Signal                 | 265<br>266<br><b>269</b>                                  |

| B<br>C<br>D | A.1 A.2 Dist Inve | Double of a C Double in a C cortion ersion rier Seck Jitte er Mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | le Sided Spectrum of Second and Third Order Distortion complex Signal                 | <ul><li>265</li><li>266</li><li>269</li><li>271</li></ul> |

### **List of Abbreviations**

AA anti-alias

AAD anti-alias distance A/D analog-to-digital

ADC analog-to-digital converter

AGC automatic gain control

AWG arbitrary waveform generator

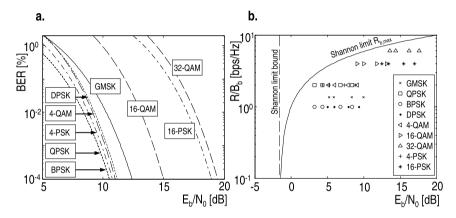

BER bit error rate

BPSK binary phase shift keying

BT bluetooth

CDMA code division multiple access

CM cross-modulation

CMOS complementary metal oxide semiconductor

CNR carrier-to-noise ratio

CT continuous-time

CW carrier wave

D/A digital-to-analog

DAC digital-to-analog converter

DC direct current

DEM dynamic element matching

DPSK differential phase shift keying

DR dynamic range

DSP digital signal processor

DT discrete-time

DUT device under test

DVB digital video broadcasting

DVB-H digital video broadcasting hand-held DVB-T digital video broadcasting terrestrial

DWA data weighted averaging

EDGE enhanced data rates for GSM evolution

xiv List of Abbreviations

EMC electro-magnetic compatibility

ENOB effective-number-of-bits FM frequency modulation

FOM figure-of-merit

GMSK Gaussian minimum shift keying

GPRS general packet radio service

GPS global positioning system

GSM global system for mobile communication

IC integrated circuit

IEEE802.X institute of electrical and electronics engineers

local area network standards

IF intermediate frequency

IL implementation loss

IM intermodulation

IIP input intercept point

IP intercept point *or* intellectual property

I&Q in phase and quadrature phase

IR image rejection

IRR image rejection ratio

ISI inter-symbol interference

ISSCC International Solid-State Circuits Conference

JSSC Journal of Solid-State Circuits

LCD liquid crystal display

LNA low noise amplifier

LO local oscillator

LSB least significant bit

LTE long term evolution

MIMO multi-input multi-output

MP3 MPEG-1 audio layer 3

MPEG moving pictures experts group

MSB most significant bit

NF noise figure NRTZ non-RTZ

NTF noise transfer function

NZIF near-zero intermediate frequency

OIP output intercept point OSR over-sampling ratio

OTA operational transconductance amplifier

PA power amplifier PC personal computer List of Abbreviations xv

PCB printed circuit board p-cell parameterized cell PDA personal digital assistant PLL phase locked loop

PMU power management unit POD performance on demand PSK phase shift keying

QAM quadrature amplitude modulation QPSK quadrature phase shift keying

RF radio frequency

RMS root mean square

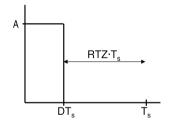

RTZ return-to-zero

Rx receiver

$\begin{array}{lll} \text{S2P} & \text{single-ended to parallel} \\ \text{SC} & \text{switched capacitor} \\ \text{SD} & \text{sigma-delta} \left( \Sigma \Delta \right) \\ \text{SI} & \text{switched current} \end{array}$

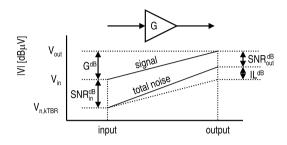

SDR signal-to-distortion ratio SNR signal-to-noise ratio

SNDR signal-to-noise-and-distortion ratio

SoC system-on-chip

SQNR signal-to-quantization-noise ratio

SR switched resistor

STF signal transfer function

TAJE time-to-amplitude-jitter-error

TD-SCDMA time division synchronous code division multiple

access

THD total harmonic distortion

TPJE time-to-phase-jitter-error

TV television

Tx transmitter

UMTS universal mobile telecommunications system

USB universal serial bus VGA variable gain amplifier

VHDL VHSIC hardware description language

VHSIC very high speed integrated circuit

VLSI very-large-scale integration

WIBRO wireless broadband

Wi-Fi wireless fidelity

WIMAX worldwide interoperability for microwave access

xvi List of Abbreviations

WLAN ZIF wireless local area network zero intermediate frequency

## **Terminology**

#### **Adaptability**