## Sandro Rigo · Rodolfo Azevedo Luiz Santos *Editors*

# Electronic System Level Design

An Open-Source Approach

Electronic System Level Design

Sandro Rigo • Rodolfo Azevedo • Luiz Santos Editors

# Electronic System Level Design

An Open-Source Approach

*Editors* Sandro Rigo Instituto de Computaçao Universidade Estadual de Campinas Av.Albert Einstein 1251 Campinas, São Paulo 13083-970 Brazil sandro@ic.unicamp.br

Rodolfo Azevedo Instituto de Computaçao Universidade Estadual de Campinas Av.Albert Einstein 1251 Campinas, São Paulo 13083-970 Brazil rodolfo@ic.unicamp.br Luiz Santos Depto. Informática e Estatística Universidade Federal de Santa Catarina UFSC Campus Florianópolis, Santa Catarina 88030-300 Brazil santos@inf.ufsc.br

ISBN 978-1-4020-9939-7 e-ISB DOI 10.1007/978-1-4020-9940-3 Springer Dordrecht Heidelberg London New York

e-ISBN 978-1-4020-9940-3

Library of Congress Control Number: 2011927759

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: VTeX UAB, Lithuania

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

Electronic System Level Design, or ESL Design, is generally understood as the set of tools, methodologies and design techniques applied to modern electronic systems design, from high-end chips and systems, to embedded devices, to integrated hardware and software systems. Given the complexity of current systems, advanced tools and methodologies have become absolutely essential to achieve the necessary productivity, quality, cost and performance expected in a design process. One of the important tenets in ESL Design is the need for early design analysis. This is done mainly through high-level modeling and simulation, performance and power analysis and functional verification, before committing the design to lower-levels of abstraction aimed at synthesis and optimization. This is especially true for complex systems involving different types of components such as processors, custom blocks and software. In fact, it may be totally impractical to simulate such systems at a lowlevel of representation such as register-transfer level, due to extremely long simulation times. High-level models are simpler to write, understand, optimize and debug than lower-level models, and they can simulate significantly faster. The more the design can be refined, optimized and verified at a high-level of abstraction, the higher the overall design productivity, the better the quality and consequently the lower the cost of the final result. However, high-level models and development environments are not without their own difficulties. It is not simple to write a high-level model at the appropriate abstraction level which will result in the best trade-off between architectural details and simulation speed. For this end, researchers have formalized different abstraction levels at different levels of architectural and timing accuracy. Depending on what types of design analysis need to be done, one abstraction level may be more suitable than another. This adds to the modeling complexity, and in the worst case, if multiple models need to be developed, it may start reducing the productivity advantage of a high-level modeling methodology. A high-level modeling and simulation framework is a complex software engineering challenge. Different types of models, such as a processor model, custom blocks and application software, need to be compiled, linked, executed and debugged together. This goes far beyond the correct individual modeling of a block using a high-level language. A successful high-level design methodology depends heavily on how well automated this framework is. SystemC is a system-level specification and design language (based on C++

classes) that has been widely adopted for high-levels of abstraction modeling. SystemC also emergence of transaction-level models (TLM) as an abstraction layer and modeling style capable of fully separating the computation part from the communication part of a model. Despite the widespread acceptance and use of SystemC and TLM, it is still very complex to create models which achieve a perfect balance between the required architectural detail for the desired types of analysis and simulation speed. This book addresses the very issues raised above. It presents a high-level design methodology, support tools and framework capable of full system modeling and design exploration, including components such as processors, custom blocks and application software. One of the main contributions of the book is the detailed description of ArchC. ArchC is an architectural description language (ADL) which allows designers to model instruction-set architectures and automatically map them into SystemC simulatable descriptions. ArchC is an ADL capable of detailed modeling of instructions and supporting processor architectures. Since ArchC generates an executable SystemC model, it can be fully integrated with other SystemC models using transaction-level interfaces, which allows the specification, modeling and simulation of complete systems. The book also explains in detail how the overall software environment works, including how the models are compiled, linked, executed together and debugged as a platform. Detailed examples using single and dual core platforms, coupled with custom accelerators and running real life applications are presented. Power modeling is also addressed in this book. Authors describe an interesting extension to SystemC called PowerSC, which allows switching and power information to be gathered and computed during and integrated with the functional simulation. Important to readers should the fact that the platform presented is Open-Source and available for download, whereas comparable systems available today are proprietary. This will certainly help researchers and developers alike to jumpstart their modeling efforts by using a readily available platform and development tools. Readers interested in a good overview of ESL methodologies as well as those interested in practical implementation details of architectural-description languages, platform modeling and support tools will be well served by this book.

> Visiting Professor Reinaldo A. Bergamaschi Odysci, Brazil/USA University of Campinas, Campinas, Brazil

## Contents

| Part | I System Design Representation                                                                       |          |

|------|------------------------------------------------------------------------------------------------------|----------|

| 1    | Electronic System Level Design                                                                       | 3        |

| 2    | <b>Open-Source Languages</b>                                                                         | 1        |

| 3    | Transaction Level Modeling       2         Sandro Rigo, Bruno Albertini, and Rodolfo Azevedo       2 | 25       |

| Part | II Open-Source Models and Tools                                                                      |          |

| 4    | ArchC Model Design Handbook                                                                          | <b>9</b> |

| 5    | <b>Building Platform Models with SystemC</b>                                                         | 1        |

| 6    | <b>Retargetable Binary Tools</b>                                                                     | 9        |

| Part | III Advanced Topics                                                                                  |          |

| 7    | <b>Debugging SystemC Platform Models</b>                                                             | 7        |

| 8    | <b>SystemC-Based Power Evaluation with PowerSC</b>                                                   | :9       |

| Inde | <b>x</b>                                                                                             | 5        |

## Contributors

**Bruno Albertini** Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil, balbertini@ic.unicamp.br

**Guido Araujo** Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil, guido@ic.unicamp.br

**Rodolfo Azevedo** Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil, rodolfo@ic.unicamp.br

Alexandro Baldassin Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil, alebal@ic.unicamp.br

**Paulo Centoducatte** Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil, ducatte@ic.unicamp.br

Felipe Klein Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil, klein@ic.unicamp.br

Sandro Rigo Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil, sandro@ic.unicamp.br

Luiz Santos System Design Automation Laboratory, Computer Science Department, Federal University of Santa Catarina, Florianópolis, Brazil, santos@inf.ufsc.br

## Part I System Design Representation

## Chapter 1 Electronic System Level Design

Luiz Santos, Sandro Rigo, Rodolfo Azevedo, and Guido Araujo

#### 1.1 The ESL Concept

Systems-on-chip (SoCs) became a reality in the mid-nineties, as a result of the long evolution of VLSI technology and the sheer growth of integrated circuit complexity. As it happens each time electronic design complexity impairs the expected time-to-market, the quest for higher productivity involves a combination of the following key notions:

- **Abstraction** At design entry, the level of representation is raised to cope with the increased design complexity. As a consequence, the design flow goes through several levels and styles of representation. Hardware design representation has been raised through physical, circuit, gate, register-transfer, and functional/behavioral levels.

- **Reuse** Pre-designed components are assembled within a new design. Reuse goes hand-in-hand with design paradigms, such as cell-based, IP-based, and platform-based.

S. Rigo e-mail: sandro@ic.unicamp.br

R. Azevedo e-mail: rodolfo@ic.unicamp.br

G. Araujo e-mail: guido@ic.unicamp.br

L. Santos (🖂)

System Design Automation Laboratory, Computer Science Department, Federal University of Santa Catarina, Florianópolis, Brazil e-mail: santos@inf.ufsc.br

S. Rigo · R. Azevedo · G. Araujo Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil

- Automation To overcome the error-prone and time-consuming nature of manual refinement, designers rely on Electronic Design Automation (EDA) tools. To refine the design representation from higher to lower abstraction levels, (layout, logic, register transfer, and behavioral) synthesis tools can be used. To check for equivalent functionality across successive levels of representation, a solid infrastructure of automatic verification tools is available.

- **Exploration** The analysis of alternative design solutions with respect to area, performance and power at a given abstraction level reduces the probability that, after refinement through lower levels, the design might turn out not to meet the specified requirements, leading to redesign.

Although integrated circuit design has already witnessed abstraction level raising from the circuit level to the gate level and then to the *Register-Transfer Level* (RTL), the so-called SoC Revolution [10] required a broader paradigm shift. Since the integrated circuit became an integrated *system*, the new abstraction should harmonize the representation of both hardware and software. Abstraction offers system-level design representations, such as executable hardware-software especifications [2], transaction-level modeling (TLM) [4] and UML modeling. The *platform-based design paradigm* [14] guides reuse from the perspective of a reference system architecture. Automation asks for software-toolkit generation [9], such as retargetable compilers and binary utilities (since the software embedded in the system may be run on possibly distinct multiple target processors). Exploration addresses the joint-evaluation of hardware and software components.

This leads to the concept of *Electronic System Level* (ESL) [1], a generic term for a set of abstractions (possibly at distinct levels), which are adequate for the design representation of SoCs. It complies with the need for hardware and software co-design, while building upon legacy hardware design representation.

#### **1.2 Requirements of an ESL Representation**

A representation suitable for ESL design should provide a unique representation of the platform architecture, capture parameters handled by hardware-dependent software, allow advance performance and power evaluation on the target platform, rely on encapsulation of processor models and non-programmable components, support platform debugging, and enable virtual prototyping. Let us consider each of such aspects individually:

- **Uniqueness of representation** Actual hardware-software co-design should rely on a unique abstraction of the hardware platform so that changes performed by either the hardware design or the software development teams could be agreed upon a same reference. It should also play the role of golden reference model for the hardware verification team.

- Hardware-dependent software The representation must provide a programmer's view of the platform that not only captures the *Instruction-Set Architecture* (ISA)

of each processor, but also includes bit-accurate descriptions of I/O device registers, memory maps for all devices with configurable registers and memory layout for data, application code, and initialization routines. This allows the early development of hardware-dependent software, such as drivers and boot code, enabling actual hardware-software co-design.

- Advance performance evaluation Although it is possible to obtain a rough performance estimate by running the application software on a stand-alone instructionset simulator, a much more accurate performance evaluation is obtained when not only the processors, but all the other platform components are captured in the design representation.

- Advance power evaluation In spite of the fact that power estimation is much more accurate at lower design levels, the ability to assess power earlier in the design flow helps in the identification of power bottlenecks, thereby allowing low-power design from the very beginning.

- **Encapsulation of processor models** Since processors are the most complex system components, the expected ESL productivity gain would be seriously impaired if processor models had to be developed from scratch. Therefore, the representation should encapsulate either reused processor models extracted from a library or automatically generated processor models.

- **Encapsulation of non-programmable components** From the perspective of hardware-dependent software development, the behavior of a component is what matters, regardless of how it will be implemented later, as far as a bit-accurate view of its I/O registers is available. Therefore, the representation should allow the functional modeling of hardware components.

- **Platform debugging** The software to be embedded into the system could be run on the host workstation and conventional debuggers could be used to pinpoint application code bugs. Besides, code inspection could be improved by porting a debugger so that it could run on an instruction-set simulator of a target processor of a platform. Although yet useful, this conventional approach is clearly limited to uncovering software bugs. Therefore, to expose architecture design bugs, the representation should support component I/O probing or even component inner probing.

- Virtual prototyping The representation should support the co-simulation of hardware and software in such a way that a virtual prototype could be used to evaluate the functionality, the performance, and the power/energy consumption of the final product. Such a prototype would contain application software, hardwaredependent software and platform architecture, elements allowing sufficiently accurate pre-evaluation without the need to dive into more time-consuming RTLbased prototyping or emulation.

#### **1.3 ESL Design Flow**

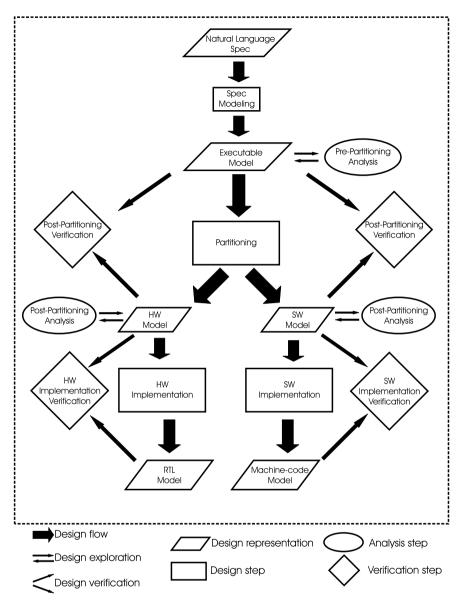

As a consequence of platform-based design, ESL flows are typically a combination of bottom-up and top-down approaches. In spite of that, Fig. 1.1 shows an idealized

Fig. 1.1 An idealized top-down ESL design flow

top-down ESL design flow, which is used here as a frame to illustrate the main design steps rather than to advocate a particular design flow. Figure 1.1 adopts the terminology introduced in [1].

From a *natural language specification*, i.e. a document capturing the product requirements and constraints, the first design step consists in obtaining a specification written in an executable or declarative language. (This book focuses on executable specifications, such as those obtained with SystemC [5]).

The resulting executable model, which captures the *functional specification* of a system, is submitted to a preliminary analysis step so as to provide grounds for future architectural decisions. By means of proper instrumentation, initial estimates for performance, storage space, power, and communication traffic can be obtained.

Based upon that preliminary analysis, the next design step leads to an *architectural specification* of a system, obtained from its functional specification through *hardware-software partitioning*, i.e. the mapping of algorithms to software running on target processors or to non-programmable hardware blocks. Although the resulting architecture specification captures hardware and software views, they should be built as interacting engines that execute cooperatively within a unified architectural model. To reach a threshold of simulation performance that enables hardwaresoftware codesign, such architectural model may rely on the TLM style. (In Chap. 5, this book proposes an open-source infrastructure to build executable architectural models that comply with TLM, which is reviewed in Chap. 3).

Once an architectural specification is available after partitioning, it has to be verified with respect to the original functional specification. Essentially, such *postpartitioning verification* aims at demonstrating that the design satisfies the specified requirements.

A few building blocks are required for the architectural specification, such as processors, non-programmable hardware components, memories, and buses. On the one hand, a building block representing a non-programmable hardware component is easily modeled by its (single) behavior (e.g. the C++ implementation of its underlying algorithm). On the other hand, since processors exibit many complex behaviors, their executable models are usually generated from declarative processor models written in an *Architecture Description Language* (ADL). (This book describes an open-source ADL in Chap. 2).

The resulting architectural model also enables a *post-partitioning analysis* step, where more accurate estimates can be obtained. For instance, performance, storage space, and power can be evaluated at the light of the chosen target processors; communication traffic can be correlated with the number of transactions. This analysis leads to the exploration of alternative architectural solutions, for instance by experimenting with distinct target processors. For such an exploration, cross compilers and binary tools must be available for the target processors. (This book describes open-source infrastructure for automatically retargeting binary utilities in Chap. 6).

Post partitioning analyses of the hardware and software models provide grounds for proper *hardware and software implementation*, giving rise to an RTL model for the hardware and application binaries for the software.

The resulting implementations have to be verified with respect to the architectural specification. The ultimate goal of such *implementation verification* is to demonstrate that the implementation has no flaws. For this, the observability of a device under verification has to be increased through white-box techniques allowing the inspection of a component's inner structure. (A suitable infrastructure for white-box verification is proposed in Chap. 7).

Although, at the first glance, executable models may seem able to track behavior only (and thereby performance), they have to be extended to simultaneously track other important issues, like power consumption, for instance. (Chapter 8 shows how SystemC descriptions can be instrumented to account for power).

This book addresses a few important aspects of the ESL design flow. It focuses on languages and artifacts used as infrastructure for executable specification, hardware-software modeling, and design tools (implementation, analysis, and verification).

#### 1.4 Target Audience, Scope and Organization

Although several ESL technologies are currently provided by EDA vendors, this book focuses on technologies available under open-source licenses, such as SystemC [5], OSCI TLM [12], ArchC [13], and PowerSC [8].

This book intends to provide grounds for further research on ESL, by means of open-source artifacts and tools, thereby stimulating the unconstrained deployment of new concepts, tools, and methodologies. It devises electronic system design from the pragmatic perspective of a SystemC-based ESL representation, by showing how to *build* and how to *use* ESL languages, models, and tools.

Other specification languages suitable for ESL design such as MATLAB [15], UML [11], SDL [7] and SystemVerilog [6] are outside the scope of this book. Proprietary ESL-compliant processor modeling, such as [3], are also beyond the intended scope.

Most of the requirements enumerated in Sect. 1.2 are covered in the next chapters, which are organized as follows:

- ESL Specification: SystemC is one of the most promising ESL languages. It is actually a class library that extends the C++ language in such a way that hardware and software components can be described within an executable specification. Some relevant aspects of SystemC are reviewed in Chap. 2 as a basis for the discussions in further chapters.

- ESL-Compliant Processor Modeling: Since describing processor models directly in SystemC would not be practical, most of processor modeling and software toolkit generation relies on ADLs. Since the ADLs designed in the midnineties preceded the rise of SystemC, the executable processor models generated by them were not thought to be encapsulated as SystemC modules. The ArchC language is an ADL born in the SystemC era. Instead of directly generating an executable processor model, a functional or cycle-accurate SystemC model is produced. The ArchC language is summarized in Chap. 2, while Chap. 4 and Chap. 5 explain how ArchC can be efficiently used to build ESL-compliant processor models. As an important complement, Chap. 6 shows how the ArchC ADL can be used as a starting point for the automatic generation of assemblers, linkers, and debuggers.

- TLM-Based ESL Design: A crucial concept to ESL is the separation between computation and communication of a system module. Since SystemC is already

built upon that concept, the definition of interfaces to encapsulate communication protocols within channels allows a convenient style of design representation: the system can be described as a set of modules (each exhibiting its concurrent behavior) that communicate by means of transactions through channels. The TLM style provides a programmer's view of the platform that allows early development of hardware-dependent software. Chapter 3 reviews the main assets of the TLM design representation.

- **ESL Design Verification**: Since the SystemC Verification Library is an already well-established verification infrastructure based on the conventional black-box approach, Chap. 7 focuses on a complementary verification aspect: the use of data introspection to enable white-box verification strategies.

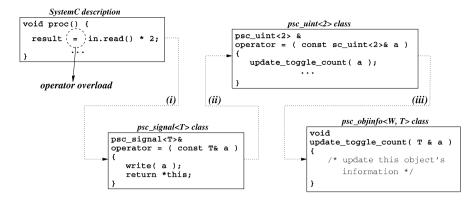

- ESL Power-Conscious Exploration: Although SystemC can model hardware and software functionalities, thereby allowing performance-based exploration, it does not come with support for modeling power consumption. Chapter 8 shows how SystemC can be extended to capture signal transitions, to correlate them with dynamic power consumption, to add up the static power contribution from technology libraries, and to accommodate distinct power macromodels.

#### References

- 1. B. Bailey, G. Martin, A. Piziali, *ESL Design and Verification: A Prescription for Electronic System Level Methodology* (Morgan Kaufmann, San Mateo, 2007)

- 2. D.C. Black, J. Donovan, SystemC: From the Ground Up (Springer, Berlin, 2004)

- 3. Coware Inc., CoWare® Processor Designer. Available at http://www.coware.com. Accessed in February 2009

- 4. F. Ghenassia, Transaction-Level Modeling with SystemC: TLM Concepts and Applications for Embedded Systems (Springer, New York, 2006)

- 5. IEEE Standards Association, IEEE 1666<sup>™</sup> Standard SystemC© Language Reference Manual. Available at http://standards.ieee.org, December 2005

- IEEE Standards Association, IEEE 1800-2005<sup>™</sup> Standard for SystemVerilog: Unified Hardware Design, Specification and Verification Language. Available at http://standards.ieee.org, 2005

- International Telecommunication Union, Specification and Description Language (SDL), ITU-T Recommendation Z.100. Available at http://www.itu.int, August 2002

- F. Klein, G. Araujo, R. Azevedo, R. Leao, L.C.V. dos Santos, An efficient framework for highlevel power exploration, in 50th Midwest Symposium on Circuits and Systems (MWSCAS) (2007), pp. 1046–1049

- 9. R. Leupers, P. Marwedel, *Retargetable Compiler Technology for Embedded Systems: Tools and Applications* (Kluwer Academic, Dordrecht, 2001)

- G. Martin, H. Chang, Winning the SoC Revolution: Experiences in Real Design (Kluwer Academic, Dordrecht, 2003)

- 11. Object Management Group, OMG Unified Modeling Language<sup>™</sup>, Superstructure, V2.1.2. Available at http://www.omg.org. Accessed in February 2009

- 12. Open SystemC Initiative, TLM Transaction Level Modeling Library, Release 2.0 Draft 2. Available at http://www.systemc.org. Accessed in February 2009

- 13. S. Rigo, G. Araujo, M. Bartholomeu, R. Azevedo, ArchC: A SystemC-based architecture description language, in 16th Symposium on Computer Architecture and High Performance Computing (SBAC-PAD) (2004), pp. 66-73

- 14. A. Sangiovanni-Vincentelli, G. Martin, Platform-based design and software design methodology for embedded systems. IEEE Des. Test Comput. 23–33 (2001) 15. The Mathworks Inc., MATLAB<sup>®</sup>. Available at http://www.mathworks.com. Accessed in

- February 2009

## Chapter 2 Open-Source Languages

Sandro Rigo, Luiz Santos, Rodolfo Azevedo, and Guido Araujo

As stated in Chap. 1, the main goal of this book is to enable ESL research based on an open-source infrastructure. In order to make it possible to readers that are not familiar with SystemC and/or ArchC to follow the model and platform descriptions presented in the remaining chapters of this book, this chapter briefly reviews the main concepts related to these two open-source languages. Moreover, ArchC will be put in practical use in Chap. 4. Nevertheless, we strongly encourage such readers to refer to the literature referenced in the following sections for a more complete specification of both languages.

#### 2.1 Basic SystemC Concepts

Since the launching of the Open SystemC Initiative (OSCI) in 1999, SystemC has evolved into one of the most important languages for ESL design. As a consequence, the SystemC literature comprises not only in-depth explanations on language constructs [5, 8], but also extensive overviews on how to put it to practical use [2–4, 7].

S. Rigo (🖂) · R. Azevedo · G. Araujo

R. Azevedo e-mail: rodolfo@ic.unicamp.br

G. Araujo e-mail: guido@ic.unicamp.br

#### L. Santos

Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil e-mail: sandro@ic.unicamp.br

System Design Automation Laboratory, Computer Science Department, Federal University of Santa Catarina, Florianópolis, Brazil e-mail: santos@inf.ufsc.br

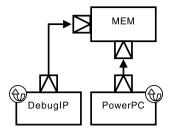

That is why this book focuses instead on how to generate and integrate processor models into SystemC platform descriptions. However, to pave the way towards platform descriptions, a few SystemC concepts and constructs will be reviewed by means of an illustrative example: a minimalist system consisting of a PowerPC processor tied to a generic read-write memory.

Figure 2.1 shows the description of such a system. The function  $sc_main$  is the starting point (its arguments have the same meaning as those in the C++ main function).

The actual description lies between Line 6 and Line 21. In Line 6 an instance PPC of a PowerPC processor of type ppc is declared. Line 8 describes an instance MEM of a memory of type mem. The name of an instance is passed as a parameter to the instance's constructor for inner storage (so that it could be used for debugging purposes).

Line 11 describes the connection between the processor's data memory port (DM\_port) and the memory's (target\_export).

Being essentially the source code for an executable representation, a SystemC description contains not only the actual instantiation of components and their connections, but also simulation control and post-simulation diagnosis.

That's why the code inside the sc\_main function executes in three phases. In Phase 1, which is called elaboration, data structures to hold the described components are created, initialized, and their connections are built. Since descriptions are typically hierarchical, creation and initialization are propagated through the subcomponents.

As it will be illustrated in a while, the functionality of each component is captured by means of one or several processes, which model concurrently executing behaviors. During the elaboration phase, all the processes attached to the described components are registered.

In Phase 2, the function sc\_start (Line 15) launches the simulation of the described (sub)system by invoking the attached behaviors. Upon its return, sc\_start marks the beginning of a new phase.

Phase 3 handles the outcome of simulation so that diagnosis reports can be issued. For instance, in Line 21 the inner state of processor PPC is printed (by invoking the method PrintStat() in Line 19). This phase ends by returning a status: zero meaning success; non-zero, failure. This example assumes that the processor has an attribute exit\_status, which is returned.

To describe the functionality of a system's component, SystemC employs the notion of **module**, which is essentially an encapsulation of the component's state and behavior. Therefore, a system is described as a set of interconnected modules. To grant modules concurrent behaviors, SystemC relies on the notion of **process**, which is a special class method of a module that is registered in SystemC's underlying simulation kernel. Processes are invoked by SystemC's event-triggered scheduler, thereby appearing as concurrent behaviors. Although SystemC has three basic process types, this chapter reviews only the notion of **thread**, since it is the predominant process type used throughout this book. Once initiated by the simulation kernel scheduler, a thread executes until it terminates, although it can be suspended

```

int sc_main(int ac, char *av[])

1

2

{

3

// Phase 1: ELABORATION

4

5

// An instance of a PowerPC processor

6

ppc PPC("PPC");

// An instance of a read-write memory

7

8

mem MEM("MEM");

9

// Connection between PPC's and MEM's data ports

10

PPC.DM_port(MEM.target_export);

11

12

// Phase 2: SIMULATION

13

14

15

sc start();

16

17

// PHASE 3: DIAGNOSIS

18

19

PPC. PrintStat();

20

return PPC.exit_status;

21

22

}

```

Fig. 2.1 SystemC top-description of a minimalist system

and resumed during its execution. For a given simulation, a thread is executed only once.

To illustrate those basic notions and review a few more concepts, let us show a sketch of a PowerPC description, which consists of two files, as depicted in Fig. 2.2 and Fig. 2.3.

Figure 2.2 describes the module encapsulating PowerPC's functionality. Observe the header files being included (Line 1 to Line 5) and note that the description assumes that the processor's architectural resources and instruction set were described elsewhere (ppc\_arch.H and ppc\_isa.H, respectively).

Although SystemC provides a macro (SC\_MODULE) to ease module description, the example shows an alternative style (Line 7) where the module inherits from two pre-defined classes: ac\_module (which itself implicitly inherits from SystemC's sc\_module class) and ppc\_arch (where architectural resources such as register file, endian, and wordsize are described).

Note that two main attributes of the processor are shown: its instruction pointer pc (Line 11) and its instruction-set architecture ISA (Line 13), which encapsulates the description of binary instruction formats and fields.

The class method in Line 16, represents the processor's global functionality (whose implementation will be shown later in terms of individual instruction behaviors). This method is turned into a process by a combination of SystemC constructs. First, the module ppc is registered as owner of a process (Line 18), then its method behavior is registered as a thread (Line 23).

```

#include "systemc.h"

1

#include "ac module.H"

2

3

4

#include "ppc_arch.H"

5

#include "ppc isa.H"

6

class ppc: public ac_module, public ppc_arch {

7

8

9

public :

10

unsigned pc;

11

12

ppc_parms::ppc_isa ISA;

13

14

//!Behavior execution method.

15

void behavior();

16

17

18

SC_HAS_PROCESS(ppc);

19

//! Constructor.

20

ppc(sc_module_name nm): ac_module(nm), ppc_arch(), ISA(*

21

this) {

22

SC_THREAD(behavior);

23

24

pc = 0;

}

25

26

virtual void PrintStat();

27

28

void load(char* program);

29

30

31

virtual~ppc() {};

32

};

```

Fig. 2.2 A sketch of the processor's description (ppc.h)

Thread registration is an essential part of a module's constructor, whose scope is illustrated between Line 21 and Line 25. Note that the processor's module inherits from predefined constructors (Line 21), registers its thread and initializes its pc. The corresponding destructor is shown in Line 31.

Two other class methods are shown in Line 27 and Line 29. The first prints statistics for post-simulation diagnosis purposes and the second loads in memory the program to be executed by the processor. Notice that, as opposed to behavior, those auxiliarly methods are not registered as processes. They are just ordinary C++ methods that do not represent concurrent behavior.

Let us now focus on Fig. 2.3, which describes the overall processor's behavior as a loop (between Line 7 and Line 24) where instructions are endlessly decoded and

```

#include

1

"ppc.H"

2

3

void ppc::behavior()

4

{

unsigned ins id;

5

6

for (;;)

7

8

{

9

// Instruction decoding

10

ins_id = decode(pc);

11

switch (ins_id)

12

13

14

. . .

15

case 10: // Decoding outcome for addi

16

17

// Instruction execution

18

19

ISA.behavior_addi( // Instruction fields ... );

20

break:

21

22

}

break :

23

24

}

25

}

```

Fig. 2.3 A sketch of the processor's description (ppc.cpp)

executed. Each instruction is assigned an identifier (declared in Line 5) to distinguish among instruction behaviors. For a given pc value, the respective instruction is decoded and its identifier is assigned (Line 11). As a result, one among the various instruction behaviors is selected (between Line 12 and Line 22). For simplicity, all behaviors are omitted, except the one corresponding to the addi instruction (Line 16), namely the method behavior\_addi from the processor's instructionset architecture (Line 20).

Although the most important concepts required throughout this book were briefly summarized in this example, the reader should refer to SystemC manuals [5, 8] and specialized books [2–4, 7] for an in-depth study of SystemC concepts, syntax, and usage.

For the example in Fig. 2.1, we assumed that a SystemC model of a processor (PPC) was available, as sketched in Fig. 2.2 and Fig. 2.3. Since such a model is too complex to be written directly in SystemC, it is instead automatically generated from the ISA description of the processor. The next section introduces an appropriate language for the generation of SystemC processor models.

#### 2.2 Introduction to ArchC

The rapidly increasing complexity of modern system architectures raised difficulties that end up delaying the whole design process and preventing designers from meeting their stringent time-to-market. Such difficulties have forced hardware architects and software engineers to reconsider how designs are specified, partitioned, and verified. As a consequence, designers are starting to move from *Register-Transfer Level* (RTL) design towards the so-called *Electronic System Level* (ESL) design and beyond the abstraction limitations of *Hardware Description Languages* (e.g. VHDL, Verilog) to ESL languages, which offer more levels and styles of abstraction (e.g. SystemC) and address not only the hardware view, but also its software counterpart. Therefore, when moving to ESL abstractions, designers have to face several new issues.

Among them, two issues are directly related to processor modeling at the ESL. The first is how to produce code for the *different* target processors under exploration. This issue is tackled through the automatic generation of a software toolkit (assembler, linker, compiler) for every distinct target processor. Such a generation tool is commonly based on an *Architecture Description Language* (ADL) [6]. The second issue is how to produce cooperative executable models for the *multiple* processors of a given platform. Although the generation of an *Instruction-Set Simulator* (ISS) has long been one of the goals of an ADL, the integration of multiple cooperating ISSs withing a platform is a recent aspect of ADL usage. This section introduces a SystemC-based architecture description language called ArchC, which addresses the above-mentioned issues.

Besides, their application and well-known suitability for designing and experimenting with new architectures in the industry, ADLs can be very useful for academic purposes, like teaching/researching computer architecture. On the one hand, at the undergraduate level, models of well-known architectures are the most appropriate to learn how a pipelined architecture works (e.g. interlocking, hazard detection and register forwarding). If allowed by the ADL, this model can be plugged to different memory hierarchies in order to illustrate how the performance of a given application can vary, depending on the choice made for cache size, update policy, associativity, etc. On the other hand, at the graduate level, researchers can use ADLs to model modern architectures and experiment with their *Instruction-Set Architectures* (ISAs) and internal organizations with all the flexibility demanded in research projects.

ArchC [1, 10] is a simple language that follows a SystemC syntax style. Its main goal is to provide enough information, at the right level of abstraction, in order to allow users to explore and verify a (new or legacy) processor's architecture by automatically generating not only software tools for code generation and inspection (like assemblers, linkers, and debuggers), but also executable processor models (integrated ISSs) for platform representation, such as the PPC model invoked in Fig. 2.1 (Line 6).

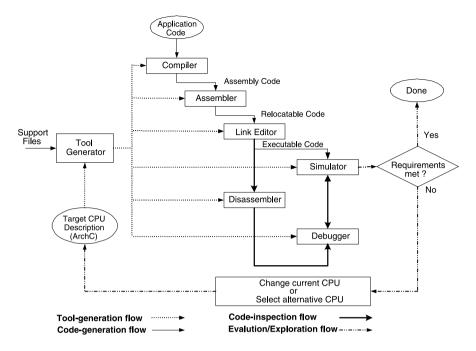

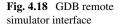

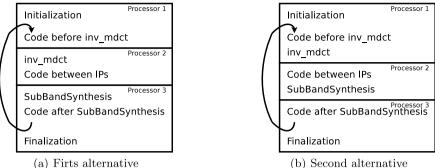

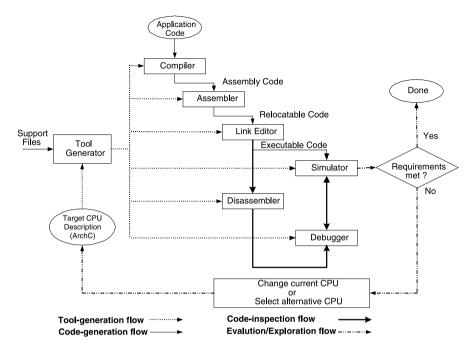

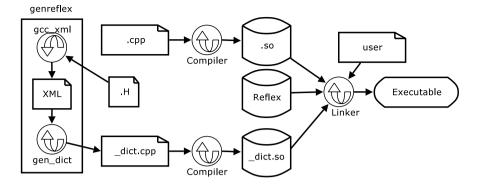

Figure 2.4 illustrates a simplified, ADL-based design exploration flow. From the ADL description of a target processor (and a few auxiliary files) the tool generator

Fig. 2.4 ADL-based exploration flow

synthesizes a compiler's backend, an ISS, and a set of binary utilities. The application's source code is compiled, assembled and linkedited, resulting in an executable code that is run on a processor model (ISS). After code inspection, which may require disassembly and debugging, the outcome of the simulation is evaluated in face of the requirements and design criteria. If a requirement or a criterion is not met, another candidate processor may be selected and the process is repeated until all constraints and criteria are satisfied. (Since Fig. 2.4 depicts a complete, ADLindependent flow, a given ADL may not support the generation of the whole toolkit; e.g. the automatic generation of compilers is not yet available for ArchC.)

The flexibility provided by such design exploration capabilities is mandatory in an ESL design environment, where multiple processors have to be considered in the composition of complex virtual platforms. For example, to quickly produce and evaluate different platform instances based upon distinct processors, all that is required is the ADL description of each candidate processor. Therefore, the decision on which processors are best suited to a given application is more accurate when a broader set of alternatives is explored through efficient ADL-based automatic generation.

In ArchC, an architecture is represented by two separate descriptions: *Instruction Set Architecture* (AC\_ISA) and *Architecture Resources* (AC\_ARCH). Within the AC\_ISA description, the designer provides information on instruction formats (lengths and fields), on instruction decoding and assembly (binary and symbolic encodings), along with the behavior of each instruction. In the AC\_ARCH description,

```

AC_ARCH(powerpc) {

1

2

ac wordsize 32;

3

ac_mem MEM:8M;

4

ac_regbank GPR:32;

5

ac req MSR;

ARCH_CTOR(powerpc) {

6

7

ac_isa("powerpc_isa.ac");

8

set endian("big");

9

};

10

};

```

Fig. 2.5 Excerpt of the PowerPC AC\_ARCH Description

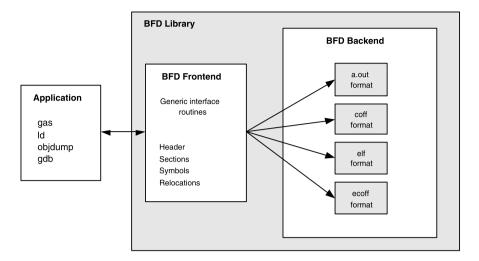

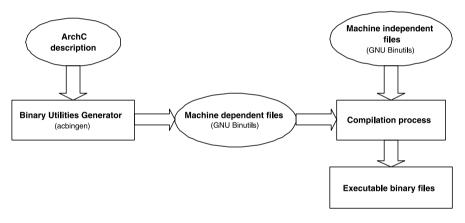

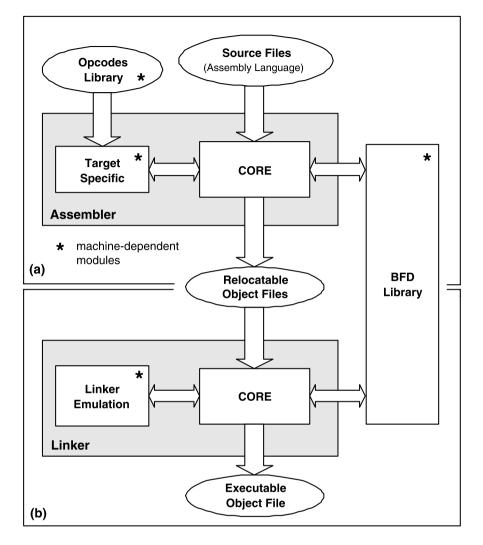

the designer declares how the processor is organized in terms of storage devices, pipeline structure, endian etc. Based on these two descriptions, ArchC can generate interpreted simulators (using SystemC) and compiled simulators (using C++), along with assemblers, linkers, and debuggers (using the GNU Binutils framework [9]).

Section 2.2.1 and Sect. 2.2.2 discuss the descriptions of architecture resources and ISA by means of examples, whereas Sect. 2.2.3 summarizes the evolution of ArchC towards platform modeling.

Throughout this book, our illustrative examples rely mainly on samples of ArchC descriptions for the PowerPC architecture. However, when this choice may limit our discussion of ADL features, we sometimes also include samples from MIPS, SPARC-V8, and Intel 8051 ArchC models, which can be downloaded from the ArchC website [12].

#### 2.2.1 Architecture Resources Description

The architecture resources represent the structural information about the target architecture, like register banks, memory, pipeline, special registers, endian, etc. ArchC collects such information from the so called AC\_ARCH description.

Obviously, the degree of detail adopted for this description depends on the level of abstraction required for the desired executable model. Although ArchC allows (in its version 1.6) the declaration of pipelines and multicycle instructions, in this book we focus on *functional models*, which are high-level descriptions suitable for the building of virtual platform models using TLM and SystemC. (For a complete ArchC specification, the reader should refer to the language reference manual [11].)

An architecture description at the functional level needs little structural information, as shown in Fig. 2.5. This example illustrates the minimum amount of architecture resource information required to build a PowerPC functional model.

Let us explain the main keywords in the example of Fig. 2.5.

AC\_ARCH: An architecture resource description always starts with this keyword. The designer should provide the model's name (e.g. powerpc).

ac\_wordsize: Declares the size of the processor's word in number of bits.

- ac\_regbank: Declares the register bank and its number of registers (e.g. the GPR bank has 32 registers).

- ac\_reg: Declares a single register (e.g. MSR).

- ac\_mem: Declares a memory of a given size (e.g. MEM has 8 megabytes). The size can be expressed in bytes (no unit abbreviation needed), in kilobytes (K or k), in megabytes (M or m), or in gigabytes (G or g).

- ac\_tlm\_port: Declares an external TLM communication port. It is followed by the name of that port object, a colon, and the size of its address space. This size, just like in ac\_mem, may be expressed either in bytes or its multiples. (Chapter 3 will explore TLM ports in detail).

- ac\_tlm\_intr\_port: Declares an interrupt TLM communication port, followed

by the port object name.

- ARCH\_CTOR: Initializes the AC\_ARCH constructor declaration.

- ac\_isa: Informs the name of the file containing the AC\_ISA description (e.g. powerpc\_isa.ac) attached to this architecture description.

- set\_endian: Defines the architecture's endianness as "big" or "little".

#### 2.2.2 Instruction Set Architecture Description

The AC\_ISA description provides the behavior of every instruction and all the information required to automatically synthesize a decoder for a given ISA. This description is divided in two files, one containing instruction and format declarations, another containing instruction behaviors.

#### **ISA Specification**

For simplicity, the main ArchC keywords appearing in an AC\_ISA description are addressed by means of an example. Figure 2.6 shows a fragment of AC\_ISA description extracted from a PowerPC model and Fig. 2.7 shows another from the SPARC model.

First, let us focus on the description of instructions, formats, and encodings by providing an overview of the main keywords. (Chapter 4 will explore their usage to build processor models).

- AC\_ISA: An ISA description always starts with this keyword. The designer should provide the model's name (e.g. powerpc in Fig. 2.6, Line 1; sparcv8 in Fig. 2.7, Line 1).

- ISA\_CTOR: It merely initializes the AC\_ISA constructor declaration.

- ac\_format: It declares an instruction format and its fields (e.g. in Fig. 2.6, Line 2, a format I1 is defined as the concatenation of four fields; the first, named opcd, consists of 6 bits). ArchC provides an additional construct that allows fields to overlap. It can be used to facilitate the description of complex instruction sets, as illustrated by the example in Fig. 2.7, Line 8. The declaration of alternative

```

AC_ISA(powerpc) {

1

ac format I1 = "%opcd:6 %li:24:s %aa:1 %lk:1";

2

3

ac_format B1 = "%opcd:6 %bo:5 %bi:5 %bd:14:s %aa:1

%lk:1";

ac format XO1 = "%opcd:6 %rt:5 %ra:5 %rb:5 %oe:1 %xos:9

4

%rc:1":

ac format SC1 = "%opcd:6 0x00:5 0x00:5 0x00:4 %lev:7 0

5

x00:3 0x01:1 0x00:1":

6

ac_instr <I1> b, ba, bl, bla;

7

ac_instr <B1> bc, bca, bcl, bcla;

8

ac_instr <XO1> add, add_, adc, mullw, divw, subf;

9

ac_instr <SC1> sc;

10

11

12

ac asm map reg {

13

/* default gas assembler uses numbers as register

names */

14

""[0..31] = [0..31];

15

}

16

17

ISA_CTOR(powerpc) {

18

19

add.set_asm("add %reg, %reg, %reg", rt, ra, rb);

add.set_decoder(opcd=31, oe=0, xos=266, rc=0);

20

21

bca.set_asm("bca %imm, %exp, %addr(pcrel)", bo, bi, bd

22

):

bca.set_decoder(opcd=16, aa=1, lk=0);

23

24

lmw.set_asm("lmw %reg, %imm (%reg)", rt, d, ra);

25

lmw.set asm("lmw %reg, %exp@l(%reg)", rt, d, ra);

26

27

lmw.set_decoder(opcd=46);

28

sth.set_asm("sth %reg, %imm (%reg)", rs, d, ra);

29

sth.set_asm("sth %reg, %exp@l(%reg)", rs, d, ra);

30

sth . set_decoder(opcd=44);

31

32

pseudo_instr("mr %reg, %reg") {

33

34

"or %0, %1, %1";

35

}

};

36

37

}

```

Fig. 2.6 Fragment of the PowerPC ac\_isa description

field choices starts with a square bracket ("["). Additional groups are given after a vertical bar ("|"). When all alternatives are declared, a closing square bracket ("]") ends the declaration. It should be noted that ArchC decodes all

overlapping fields. However, although they can be accessed independently, not all are simultaneously valid. The designer has to define which alternative group is valid according to the value of some other field. For the example at Line 8, the field "is" plays the role of a selector. When is=1, fields "r2a" and "rs2" are valid; otherwise "r2b" and "imm7" are the valid fields.

- ac\_instr<fmt>: It declares an instruction and ties it to a predefined format. Formats are assigned to instructions using a syntax similar to C++ *templates*. In Fig. 2.6, for instance, the instruction add at Line 9 is tied to the instruction format XO1 declared at Line 4.

- set\_decoder: It initializes the instruction decoding sequence, which is a key element to the automatic generation of an instruction decoder for the executable processor model. The sequence is composed of pairs <*field\_name* = value>. In Fig. 2.6 at Line 20, for instance, add.set\_decoder states that a bit stream coming from memory is an add instruction if, and only if, fields opcd, oe, xos, and rc contain the values 31, 0, 266, and 0, respectively.

Now, let us address the keywords that define symbolic names for instructions, registers and groups of instructions, since they are the key to the automatic generation of binary utilities (e.g. assemblers). Chapter 6 will explore such keywords and binary utilities generation in more depth.

- ac\_asm\_map: Specifies a mapping between assembly symbols and values (e.g. in Fig. 2.6, Lines 12–15) define the set of register names and their corresponding numbers in the register bank of the PowerPC architecture).

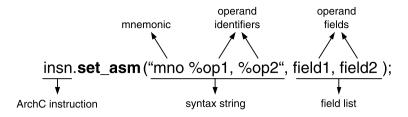

- set\_asm: Associates an assembly syntax string and operand encoding to an instruction. The syntax of this construct is similar to the printf family used in the C language. Literal characters must be matched as it appears in the assembly source program, while conversion specifiers (%) force the assembler to recognize ranges of values or symbols for operands. For each operand, there must be an associated instruction field, specifying the operand encoding (e.g. in Fig. 2.6, Line 19, the add instruction uses three operands of type reg with are associated, respectively, with the fields rt, ra, and rb of the format declared in Line 4).

- pseudo\_instr: Describes a pseudo instruction in terms of previously described instructions (e.g. in Fig. 2.6, Lines 33-35, the pseudo instruction mr is associated with the predeclared instruction or).

#### **Instruction Behavior Description**

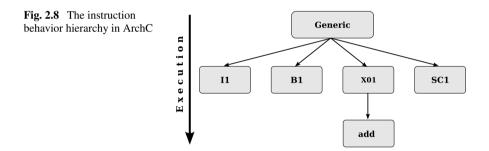

The designer must also provide the operations executed by each instruction. This is done by means of the so-called behavior methods. ArchC allows three hierarchical levels for instruction behavior description: the generic behavior, which contains actions that must be executed for every instruction, the instruction-type behavior, which describes actions to be executed by the subset of instructions tied to a given

```

AC_ISA(sparcv8) {

1

2

ac_format Type_F1="%op:2 %disp30:30";

ac_format Type_F2A="%op:2 %rd:5 %op2:3 %imm22:22";

3

4

ac_format Type_F3A="%op:2 %rd:5 %op3:6 %rs1:5 %is:1 %asi:8 %

rs2:5":

ac_format Type_F3B="%op:2 %rd:5 %op3:6 %rs1:5 %is:1 %simm13

5

:13:s";

6

/* format for trap instructions */

7

ac_format Type_FT="%op:2 %r1:1 %cond:4 %op2a:6 %rs1:5

8

%is:1 [%r2a:8 %rs2:5 | %r2b:6 %imm7:7]";

9

ac_instr <Type_F1> call;

10

ac_instr <Type_F2A> nop, sethi;

ac_instr <Type_F3A> add_reg, sub_reg;

11

12

ac_instr <Type_F3B> add_imm, sub_imm;

ac_instr <Type_FT> trap_reg, trap_imm;

13

14

. . .

15

}

```

Fig. 2.7 Fragment of the SPARC ac\_isa description

instruction format, and the instruction-specific behavior that distinguishes it from all other instructions. The idea behind this hierarchy is that designers can factorize the instruction behavior to minimize the code size of the model. The automatically generated processor model will rely on such hierarchical behavioral description: every time a new instruction is fetched, the execution always starts at the generic behavior method and then goes down through the type and specific behaviors. Figure 2.8 illustrates this sequence for the PowerPC's add instruction, which was declared in Fig. 2.6.

In ArchC descriptions, instruction behavior methods are actually written in pure SystemC/C++ code, thereby avoiding that users should learn additional keywords (beyond those described so far). The designer can even declare helper functions to perform special actions and use them inside their behavior descriptions. For more details on how to design a processor model using ArchC, the reader should refer to Chap. 4, which presents a step-by-step model development process, through a richer set of illustrative examples.

#### 2.2.3 The Evolution of ArchC Towards Platform Modeling

ArchC was first designed for processor architecture research, specially for experimenting with new instruction sets for application-specific architectures. The main goal was to generate simulators which were fast enough to run real software applications by means of a processor description that should be easy to write and maintain. From the very beginning, SystemC was the choice for the ArchC simulator generation tool.

The first open-source release of ArchC happened in February 2004. Its first versions evolved to support interpreted simulator generation in SystemC, compiled simulation generation and optimization using C++, and software tools like assemblers. But, as the number of ArchC users increased, it became clear that its most popular application was to generate processor models to be embedded into complex virtual platform models written in SystemC.

Since its 2.0 release in 2001, SystemC was gaining momentum as a language to enable design in higher abstraction levels. At that time, system-level design was attracting a lot of attention from the EDA community, and SystemC was one of the most suitable languages to support this new design paradigm (actually, the main goal of SystemC was to enable system-level modeling [4]).

In short, with the advent of System-on-Chip (SoC) designs, the whole design process where ADLs were applied changed. Processor models are not only used for processor architecture development anymore, but also became an important part of heterogenous platform models on a SoC design flow, aiding on the application of the new ESL design methodologies.

Aiming this new horizon for their languages, ADL designers have to increase not only the expression power of their languages, making them capable of modeling the modern complex architectures, but also the modularity and portability of their generated simulators, making them suitable for ESL-based design flows. The most important aspect on this matter is the communication capabilities of those simulators. An ADL will only be adopted by a platform designer if its simulators are easily integrated in their platform models, which implies in making them capable of communicating with other hardware modules.

Although it has always been possible to integrate ArchC models into SystemC platform models (since they were written in SystemC), this was not an easy task up to version 1.6. Users had to manually alter the automatically generated simulator to include a communication channel so as to connect the processor model to a wrapper or to another SystemC module directly.

As the demand from researchers interested in virtual platforms had grown substantially and since the so-called *Transaction Level Modeling* (TLM) style had risen as the most promising alternative for platform modeling in SystemC-based ESL environments, ArchC developers decided to add a feature to their automatically generated functional simulators from version 2.0 on: the capability of declaring TLM ports. As a result, it became pretty simple for platform designers to use those simulators as processor models within an ESL environment by modeling communication in the TLM style. Besides, the new feature also granted the capability of modeling an interrupt system.

Chapter 3 will introduce the TLM concept and its application in SystemC, and Chap. 5 will present an in-depth discussion on the platform integration capabilities of ArchC-generated simulators by means of a few platform design examples.

#### References

- R. Azevedo, S. Rigo, M. Bartholomeu, G. Arajo, C. Arajo, E. Barros, The arch carchitecture description language. Int. J. Parallel Program. 33(5), 453–484 (2005)

- 2. J. Bhasker, A SystemC Primer (Star Galaxy Publishing, Allentown, 2002)

- 3. D.C. Black, J. Donovan, SystemC: From the Ground Up (Springer, Berlin, 2004)

- 4. T. Grötker, S. Liao, G. Martin, S. Swan, *System Design with SystemC* (Kluwer Academic, Dordrecht, 2002)

- 5. IEEE Standards Association, IEEE 1666<sup>™</sup> Standard SystemC<sup>©</sup> Language Reference Manual. Available at http://standards.ieee.org, December 2005

- P. Mishra, N. Dutt (eds.), *Processor Description Languages* (Morgan Kaufmann, San Mateo, 2008)

- W. Müller, W. Rosenstiel, J. Ruf, SystemC: Methodologies and Applications (Springer, Berlin, 2003)

- 8. Open SystemC Initiative, SystemC® Language Reference Manual, Version 2.2. Available at http://www.systemc.org. Accessed in February 2009

- 9. R.H. Pesch, J.M. Osier, *The GNU Binary Utilities* (Free Software Foundation Inc, Boston, 1993)

- S. Rigo, G. Araujo, M. Bartholomeu, R. Azevedo, ArchC: A SystemC-based architecture description language, in 16th Symposium on Computer Architecture and High Performance Computing (SBAC-PAD) (2004), pp. 66–73

- 11. The ArchC Team, The ArchC Architecture Description Language v 2.0 Reference Manual. Available at http://www.archc.org, August 2007

- 12. The ArchC website (March 2008). http://www.archc.org

## Chapter 3 Transaction Level Modeling

Sandro Rigo, Bruno Albertini, and Rodolfo Azevedo

This chapter introduces the Transaction Level Modeling (TLM) design methodology. Its main goals are to explain the main concepts behind TLM and to show that it can work very well in SystemC-based designs. That is why we discuss the strong relation between SystemC and TLM and emphasize the main features in the SystemC TLM 2.0 standard. As in Chap. 2, the intention is not to serve as a substitute for the reference manual. Instead, our focus is to provide a good understanding on the underlying ideas and to show how to put TLM to work in SystemC-based platform designs. (For details, the interested reader should refer to the OSCI TLM 2.0 User Manual.) We finalize this chapter with a simple platform example using the SystemC TLM standard. Chapter 5 will present more elaborate platform examples by relying on the main concepts and elements introduced by Chaps. 2–4.

#### **3.1 Introduction**

As already discussed in Chap. 1, the rise of SoCs caused a paradigm shift on system design flow. The TLM methodology was created in the search for a new paradigm that could allow design representation at an intermediate level of abstraction be-

S. Rigo (🖂) · B. Albertini · R. Azevedo

Computer Systems Laboratory, Institute of Computing, University of Campinas, Campinas, Brazil e-mail: sandro@ic.unicamp.br

B. Albertini e-mail: balbertini@ic.unicamp.br

R. Azevedo e-mail: rodolfo@ic.unicamp.br

S. Rigo et al. (eds.), *Electronic System Level Design*, DOI 10.1007/978-1-4020-9940-3\_3, © Springer Science+Business Media B.V. 2011

tween paper specification and RTL models. That is why TLM plays nowadays an important role in ESL technologies.

The first key concept behind TLM is that unnecessary details should be avoided at the early phases of the design flow. By using a high-level of abstraction, TLM leads to a large gain of simulation speed and modeling productivity, which enables new design methodologies. The main goal of a TLM model is to be a common reference model for teams working on software, hardware, architecture analysis, and verification. For this reason, it should appear very early in the design flow, preferably right after HW-SW partitioning.

The second key concept is the separation between computation and communication. In a TLM representation, modules contain concurrent processes that execute their behaviors, whereas communication is performed through packet exchanging among these modules, which are called *transactions*. Communication is implemented inside channels, hiding the protocols from the modules, but exposing their interfaces.

Although TLM is language independent, SystemC fits perfectly its style of representation by allowing adequate levels of abstraction and by providing elements for supporting separate computation and communication. The connection between SystemC and TLM has grown so strong in the recent years that OSCI created a special TLM Working Group to define the SystemC TLM standard [7].

A TLM-based representation fits well in an ESL design flow. As discussed in Chap. 1, there are some requirements that a design representation should meet to be suitable for ESL design, which are:

- provide a unique representation of the platform architecture;

- capture parameters handled by hardware-dependent software;

- allow advance performance evaluation on the target platform;

- allow advance power evaluation on the target platform;

- rely on encapsulation of processor models;

- rely on encapsulation of non-programmable components;

- support platform debugging;

- enable virtual prototyping.

All these requirements were considered in the principles of TLM [2], as we are going to further discuss in the following sections.

The key to successful TLM usage is a good architecture planning. Designers should partition hardware into key pieces and model every piece as a SystemC module. TLM is then used to model communication between those modules by using high-level function calls to replace the expensive and slow RTL signal-based communication (which models every event on the system). For a full functional model of the whole system, software is then integrated into the TLM platform. After proper validation, the resulting TLM representation can become a golden reference model for further phases of the design flow (e.g. RTL model validation).

#### 3.2 The Evolution Towards the OSCI TLM 2.0 Standard

Since its version 2.0 was released in 2001, SystemC has been enabling a TLM approach for model development. At that time, all the key language constructs for enabling TLM, like channels, ports, and interfaces, were already available.

The basic hierarchical unit in SystemC is a *module*. Inside a module, the computation is implemented by *processes* (methods or threads). Communication is implemented through *channels*, which can appear in a variety of complexity levels. A channel can be as simple as a wire or be hierarchically designed to comprise sophisticated communication mechanisms. Modules are interconnected through channels. Channels implement *interfaces*, which expose to the modules the methods available to perform communication. *Ports* are the binding point between modules and channels. Therefore, every transaction between two modules can be reduced to the invocation of a function.

At certain point in the evolution of SystemC support for TLM, it became clear that a commonly accepted standard would be required for the whole SystemC community so that software, hardware, and verification engineers could be able to achieve the expected productivity levels. As a result, OSCI founded the so-called TLM Working group (TLMWG) [7], which became responsible for the definition of the envisaged standard. This group included representatives of several companies, such as STMicrolectronics, Mentor Graphics, Cadence, and ARM, among others. In 2005, the 1.0 version of the TLM Standard was approved by OSCI.

Interoperability is a key factor to ESL design because it improves the chances of in-house and third-party IP reuse for the building of virtual platform models. Unfortunately, the experience proved that TLM 1.0 was not able to strongly promote TLM model interoperability and did not offer a good balance between model development time, speed, and accuracy.

TLM 1.0 had a set of functions to standardize both blocking and non-blocking communication interfaces. However, there was no standard to define which data structures (or class), would carry the data on transactions. Each designer was responsible for defining his own data structures to compose the packets transmitted in each transaction. Each IP designer or provider ended-up creating its own data payload format, which had a clear impact on IP module reuse. The usual solution was to include a wrapper (or transactor) between two IPs in order to translate between the different payload formats, thereby establishing the communication. This makeshift not only increased the modeling effort, but also resulted in a penalty on simulation performance.

Although interoperability was the main missing point in TLM 1.0, two additional issues hampered its widespread adoption: there was no timing annotation mechanism and there were some performance limitators. Time delays had to be implemented by calls to the wait() method, which caused context switches and, as a consequence, slowed down the simulation. Every transaction needed to pass its data as value or const references, further increasing simulation times. To work around those issues, designers had to rely on non-standard solutions. Therefore, interoperability and model reuse were indirectly affected.

As virtual platforms and TLM continued to grow in importance, specially in performance analysis and design space exploration, the TLMWG kept working on developing the libraries for TLM in SystemC. Its main goal was to make interoperable TLM a reality for SystemC users. The 2.0 version of the SystemC TLM standard was finally released in June 2008. The next section introduces its main functionalities.

#### 3.3 Main Features in the TLM 2.0 Standard

TLM 2.0 was developed with memory-mapped bus applications as its main target. This type of application simulates communication and demands concurrent execution, which is achieved by means of several SystemC processes. Therefore, TLM 2.0 developers made clear that pure algorithmic models, those which can be simulated by a single thread and require no inter-process communication, were not a main concern on the definition of the standard [5]. Since designers could rely on TLM 1.0 core interfaces to model purely untimed systems, TLM 2.0 focused on providing proper interfaces for two different coding styles: *loosely-timed* (LT) and *approximately-timed* (AT) [4].

As clearly stated in the OSCI's TLM 2.0 User Guide, users could come up with other coding styles, but these two must be enough to model any use case to which the development of TLM 2.0 was targeted for. The choice between LT and AT styles depends on what is expected from the models, as we are soon going to discuss in detail; a good rule of thumb is that, for starting a new design from scratch, it is advisable to first build a LT model, and then refine it towards an AT model if necessary.

LT descriptions include enough details to model the communication, but without considering timing issues. On the one hand, this level of detail is sufficient to model interrupts and to allow the booting of an OS over a multicore platform. On the other hand, it is not suitable for bus development due to the lack of timing. LT platform models are capable of modeling functionalities for components, debug, and memory maps. This makes them suitable for functional verification, and early software development. LT models were usually referred as Programmer's View (PV) models in former SystemC and TLM literature [1–3]. The LT coding style is better supported by the blocking transport interface in the TLM 2.0 standard.

Approximately-timed (AT) models present every process running locked to the simulation time. These models are suitable for architecture exploration and performance analysis, since they can include resource contention and arbitration. In the AT coding style, transactions are broken into multiple phases, marked by timing points. The TLM 2.0 standard supports timing annotation and multiple timing points by means of its non-blocking transport interface. It is important to mention that, although user-defined protocols may have multiple timing points, to be fully compatible with the generic payload, the designer must be aware that the base protocol has four points marking the beginning and end of both the request and the response.

#### 3 Transaction Level Modeling

Since time penalties increase with timing accuracy, designers usually start from a full LT model (no timing at all). As the design evolves, modules with some time accuracy are added, either via decomposition (model partition) or through refinement (adding details to make it more precise). To keep the simulation speed benefits offered by LT abstraction, different teams use different platforms and load timeaccurate models only when and where needed. This generates an *hybrid model*, where parts with no notion of time are synchronized with accurate parts through the use of time wrappers or explicit synchronization.

Every SystemC model that uses TLM must assume the role of an initiator or a target. An *initiator* is responsible for assembling the payload and sending a request packet through a function call. A *target* receives the payload and acknowledges it, returning the call. After processing the data, the target sends a response packet, if applicable. Modules that are both an initiator and a target are modeled as they where one or another at a given time, even if the time between a send and a receive is null. An example of such a module is the so called interconnect modules, whose sole functionality is to transfer transactions packets from its initiator socket to its target socket, without modifying its contents.

To become an initiator or a target, a SystemC module only needs to supply a connection socket and implement one of the four interfaces, according to the type of communication desired. The four transport interfaces are the blocking and nonblocking versions for forward, initiator to target, and backward, target to initiator, communication. These interfaces may be specialized.

The blocking version is used with LT models. In this case, target modules receive a request packet and must return a response packet. Initiators stay blocked until the target returns from the call.

The non-blocking interface is more suitable to AT models. The protocol is divided into phases, where both initiator and target take actions. The initiator module begins a communication in the same way as it would do with a blocking transport interface, but the target module may return without a response, freeing the initiator to continue execution. The initiator should accept target packets, that should be the response to the initiator request. The modeling structure for both types are shared and unified. This allows the same model to be used as blocking or non-blocking without changes. Both methods allow timing annotation.

As stated before, all communication using TLM is composed by a payload that is transferred from one side to another by means of a function call. To promote full interoperability among IP modules, TLM 2.0 has a fixed guideline for payloads. It is called *generic payload*, and contains fields for a command, an address, data, byte enables, and response status. These attributes were intentionally chosen to suit memory-mapped bus models.

It could be argued that this packet structure is too restrictive. In practice, only a few transaction-level models are likely to need something different from a masked data/address request-response packet. Therefore, it is largely enough to model the use cases which the standard was targeted for. Nevertheless, it is still possible to design specific structures for protocols that demand specialized attributes, by extending the generic payload. However, the less specialized the structure, the higher the

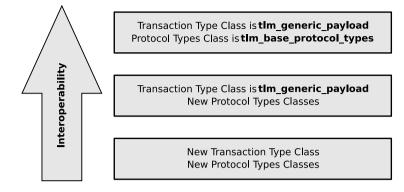

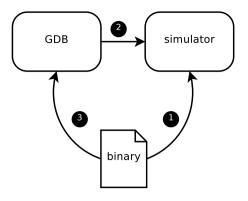

Fig. 3.1 Relation between interoperability and payload customization

amount of modules compatible with a given design, thereby promoting interoperability and reuse, as clearly stated in Chap. 6 of the OSCI TLM-2.0 User Manual [5]. This notion is illustrated in Fig. 3.1, which shows three alternatives recommended by OSCI (for designing transaction and protocol types classes for TLM models), and their increasing level of interoperability.

TLM 2.0 defines a generic payload and three kinds of interfaces: *transport*, *DMI*, and *debug*. Interfaces were developed to readily supply most, if not all, cases of communication. As discussed above, the *transport interface* consists of a request-reply protocol with blocking and non-blocking versions.

The *DMI interface* is also called by LT models. DMI returns a pointer to the requested memory location, thereby allowing a faster access, bypassing all communication stack, including function calls. Concurrency is solved by reserving memory chunks for exclusive access and invalidating those pointers after use.

The *debug interface* gives an initiator access to memory without delay or sideeffect. It passes a normal payload to memory, which is instantly processed. It is not intended for regular usage, since a memory access seems as if it never happened. This interface can be called from both LT and AT models.

In order to better understand the interoperability issues involving the three alternatives shown in Fig. 3.1, let us first take a look at the so-called combined interfaces [5] in TLM 2.0. Figure 3.2 shows an excerpt of the declaration code that may be found in the  $tlm_fw_bw_ifs$ . h file in the TLM 2.0 distribution released by OSCI in 2008. First, the protocol types' structure is declared (Line 1). Notice that it uses the standard generic payload for data transfer and also the standard phase type for controlling transaction phases. This protocol type classes are passed to the TYPES argument in the interfaces declaration (Line 8). The combined interfaces group the transport, DMI, and debug interfaces. Figure 3.2 shows the forward combined interface declaration using the types defined in the structure above. The backward interface declaration follows the same pattern.

Temporal decoupling is allowing SystemC processes to run ahead of the simulation time, which consists in controlled by the SystemC scheduler. The idea is to speed up simulation by allowing processes to run up to the point where one needs

```

struct tlm_base_protocol_types

1

2

{

3

typedef tlm_generic_payload tlm_payload_type;

typedef tlm_phase tlm_phase_type;

4

5

}:

6

// The forward interface:

7

template <typename TYPES = tlm_base_protocol_types >

8

9

class tlm_fw_transport_if :

public virtual tlm_fw_nonblocking_transport_if <typename</pre>

10

TYPES::tlm_payload_type, typename TYPES::

tlm_phase_type >,

public virtual tlm_blocking_transport_if <typename TYPES</pre>

11

::tlm_payload_type>,

public virtual tlm_fw_direct_mem_if <typename TYPES::</pre>

12

tlm_payload_type >,

public virtual tlm_transport_dbg_if <typename TYPES::</pre>

13

tlm_payload_type>

14

{};

```

Fig. 3.2 Combined interfaces declaration. (Extracted from OSCI TLM 2.0 distribution)

synchronization or interaction with another process, also reducing the scheduling overhead by decreasing the amount of context switches and events. Temporal decoupling only makes sense if associated to the LT coding style, since AT models have a much stronger dependency between timing and data.

A typical case that creates a synchronization barrier is a process reaching a point where there is a dependency on a value that comes from another process. This value may not have been updated yet. In a SystemC temporal decoupled implementation the process has two choices: accepting the current value or returning the control to the SystemC kernel. The first option allows the process to continue the simulation, but is up to the process to determine if no harm will be done to the correctness of the model.

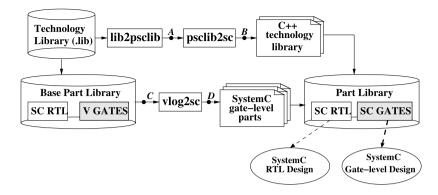

#### **3.4 A Small TLM Platform Example**