Sudipta Kundu Sorin Lerner Rajesh Gupta

# High-Level Verification

Methods and Tools for Verification of System-level Designs

High-Level Verification

Sudipta Kundu · Sorin Lerner · Rajesh K. Gupta

# High-Level Verification

Methods and Tools for Verification of System-Level Designs

With Chapter 6 contributed by Malay K. Ganai and Chapter 8 contributed by Zachary Tatlock

Sudipta Kundu Synopsys Inc. NW Thorncroft Dr. 2174 97124 Hillsboro USA sudiptakundu@gmail.com Rajesh K. Gupta Department of Computer Science and Engineering University of California, San Diego Gillman Drive 9500 92093-0404 La Jolla USA rgupta@ucsd.edu

Sorin Lerner Department of Computer Science and Engineering University of California, San Diego Gillman Drive 9500 92093-0404 La Jolla USA lerner@ucsd.edu

ISBN 978-1-4419-9358-8 e-ISBN 978-1-4419-9359-5 DOI 10.1007/978-1-4419-9359-5 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011928550

### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

Given the growing size and heterogeneity of Systems on Chip (SOC), the design process from initial specification to chip fabrication has become increasingly complex. The growing complexity provides incentive for designers to use high-level languages such as C, SystemC, and SystemVerilog for system-level design. While a major goal of these high-level languages is to enable verification at a higher level of abstraction, allowing early exploration of system-level designs, the focus so far has been on traditional testing techniques such as random testing and scenario-based testing.

This book focuses on the rapidly growing area of high-level verification. We envision a design methodology that relies upon advances in synthesis techniques as well as on incremental refinement of the design process. These refinements can be done manually or through elaboration tools. In this book, we discuss verification of specific properties in designs written using high-level languages as well as checking that the refined implementations are equivalent to their high-level specifications. The novelty of each of these techniques is that they use a combination of formal techniques to do scalable verification of system designs completely automatically.

The verification techniques fall into two categories: (a) methods for verifying properties of high-level designs and (b) methods for verifying that the translation from high-level design to a low-level Register Transfer Language (RTL) design preserves semantics. Taken together, these two parts guarantee that properties verified in the high-level design are preserved through the translation to low-level RTL. By performing verification on the high-level design, where the design description is smaller in size and the design intent information is easier to extract, and then checking that all refinement steps are correct, we describe a hardware development methodology that provides strong and expressive guarantees that are difficult to achieve by directly analyzing the low-level RTL code.

We expect the reader to gain appreciation and knowledge of the recent advances in raising the abstraction for design verification tasks. While the complexity of the problem is not lost on a typical reader, this book would ultimately present a positive outlook on the engineering solutions to the problem that the reader can use in practice.

# Acknowledgments

Acknowledgment is not a mere formality but a genuine opportunity to express the sincere thanks to all those; without whose active support and encouragement this book would not have been successful.

This book would not have been possible without contribution from Dr. Malay K. Ganai and Mr. Zachary Tatlock. Dr. Ganai shared his expertise on bounded model checking in Chap. 6 and Mr. Tatlock shared his knowledge on once-and-for-all verification techniques in Chap. 8.

Significant part of this book is based on Dr. Sudipta Kundu's doctoral dissertation work. To this end, we express our thanks to Prof. Ranjit Jhala, Prof. Ingolf Krueger, Prof. Bill Lin, Dr. Yuvraj Agarwal, Federic Doucet, Ross Tate, and Pat Rondon and to all the faculty members, staffs, and graduate students of the Department of Computer Science and Engineering for their continuous help and support.

Our sincere thanks to Chao Wang, Nishant Sinha, Aarti Gupta, and all other members of the System LSI and Software Verification group at NEC Laboratories America for uncountably many interesting discussion and explanation of key concepts in Verification.

We thank Prof. Alan J. Hu for his valuable insights and comments on the initial version of the translation validation part of this book.

We also thank the members of the MESL and Progsys group for their ceaseless effort, constant encouragement, and also for the endless good times during the making of this book.

We also agree that words are not enough to express our indebtedness and gratitude toward our families, to whom we owe every success and achievements of our life. Their constant support and encouragement under all odds has brought us where we stand today.

# Contents

| 1 | Intro        | oduction              |                                        |    | 1  |  |

|---|--------------|-----------------------|----------------------------------------|----|----|--|

|   | 1.1          | Overvi                | iew of High-Level Verification         |    | 2  |  |

|   | 1.2          | Overvi                | iew of Techniques Covered in this Book |    | 4  |  |

|   |              | 1.2.1                 | High-Level Property Checking           |    | 4  |  |

|   |              | 1.2.2                 | Translation Validation                 |    | 5  |  |

|   |              | 1.2.3                 | Synthesis Tool Verification            |    | 6  |  |

|   | 1.3          | Contri                | butions of the Book                    |    | 7  |  |

|   | 1.4          | Book (                | Organization                           |    | 8  |  |

| 2 | Back         | ground                |                                        |    | 11 |  |

|   | 2.1          |                       | Level Design                           |    |    |  |

|   | 2.2          |                       | Design                                 |    |    |  |

|   | 2.3          |                       | Level Synthesis                        |    |    |  |

|   | 2.4          | Model                 | Checking                               |    | 15 |  |

|   |              | 2.4.1                 | Simple Elevator Example                |    |    |  |

|   |              | 2.4.2                 | Property Specification                 |    | 18 |  |

|   |              | 2.4.3                 | Reachability Algorithm                 |    | 19 |  |

|   | 2.5          | 5 Concurrent Programs |                                        |    | 20 |  |

|   |              | 2.5.1                 | Representation of Concurrent Programs  |    | 20 |  |

|   |              | 2.5.2                 | Partial-Order Reduction                |    | 21 |  |

|   | 2.6          | Summary               |                                        | 23 |    |  |

| 3 | Related Work |                       |                                        |    |    |  |

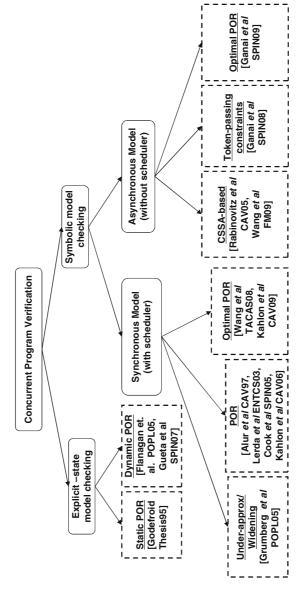

|   | 3.1          | High-I                | Level Property Checking                |    | 25 |  |

|   |              | 3.1.1                 | Explicit Model Checking                |    |    |  |

|   |              | 3.1.2                 | Symbolic Model Checking                |    | 27 |  |

|   | 3.2          | Transla               | ation Validation                       |    | 29 |  |

|   |              | 3.2.1                 | Relational Approach                    |    | 29 |  |

|   |              | 3.2.2                 | Model Checking                         |    |    |  |

|   |              | 3.2.3                 | Theorem Proving                        |    | 31 |  |

|   | 3.3   | Synthesis Tool Verification                        | 1 |  |  |

|---|-------|----------------------------------------------------|---|--|--|

|   |       | 3.3.1 Formal Assertions                            | 2 |  |  |

|   |       | 3.3.2 Transformational Synthesis Tools             | 3 |  |  |

|   |       | 3.3.3 Witness Generator                            | 3 |  |  |

|   | 3.4   | Summary 3:                                         | 5 |  |  |

| 4 | Vanie | action Using Automated Theorem Ductions            | 7 |  |  |

| 4 |       | cation Using Automated Theorem Provers             |   |  |  |

|   | 4.1   | Satisfiability Modulo Theories                     |   |  |  |

|   | 4.2   | Hoare Logic                                        |   |  |  |

|   | 4.3   | Weakest Preconditions                              |   |  |  |

|   | 4.4   | Additional Complexities for Realistic Programs     |   |  |  |

|   |       | 4.4.1 Path-Based Weakest Precondition              |   |  |  |

|   |       | 4.4.2 Pointers                                     |   |  |  |

|   |       | 4.4.3 Loops 49                                     | 9 |  |  |

| 5 | Execu | Ition-Based Model Checking for High-Level Designs  | 1 |  |  |

|   | 5.1   | Verification of Concurrent Programs                |   |  |  |

|   | 5.2   | Overview of SystemC                                |   |  |  |

|   | 5.3   | Problem Statement                                  | 2 |  |  |

|   | 5.4   | Overview of Execution-Based MC for SystemC Designs |   |  |  |

|   | 5.5   | SystemC Example                                    |   |  |  |

|   | 5.6   | SystemC Simulation Kernel                          |   |  |  |

|   |       | 5.6.1 Nondeterminism                               | 5 |  |  |

|   | 5.7   | State Transition System 50                         | 6 |  |  |

|   | 5.8   | The EMC-SC Approach                                |   |  |  |

|   |       | 5.8.1 Static Analysis                              |   |  |  |

|   |       | 5.8.2 The Explore Algorithm                        | 0 |  |  |

|   | 5.9   | The Satya Tool                                     |   |  |  |

|   | 5.10  | Experiments and Results                            | 4 |  |  |

|   |       | 5.10.1 FIFO Benchmark                              | 4 |  |  |

|   |       | 5.10.2 TAC Benchmark                               | 5 |  |  |

|   | 5.11  | Further Reading                                    | 5 |  |  |

|   | 5.12  | Summary                                            | 6 |  |  |

| 6 | Boun  | ded Model Checking for Concurrent Systems:         |   |  |  |

| U |       | aronous Vs. Asynchronous                           | 7 |  |  |

|   | 6.1   | Introduction                                       |   |  |  |

|   | 0.1   | 6.1.1   Synchronous Models   69                    |   |  |  |

|   |       | 6.1.2Asynchronous Models70                         |   |  |  |

|   |       | 6.1.3 Outline                                      |   |  |  |

|   | 6.2   | Concurrent System                                  |   |  |  |

|   | 0.2   | 6.2.1 Interleaving (Operational) Semantics         |   |  |  |

|   |       | 6.2.2 Axiomatic (Non-Operational) Semantics        |   |  |  |

|   |       | 6.2.3 Partial Order                                |   |  |  |

|   |       |                                                    | • |  |  |

|   | 6.3 Bounded Model Checking |                                                       | 75                                            |     |  |  |

|---|----------------------------|-------------------------------------------------------|-----------------------------------------------|-----|--|--|

|   | 6.4                        | Concur                                                | rent System: Model                            | 76  |  |  |

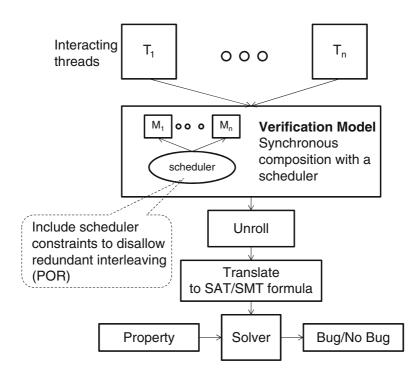

|   | 6.5                        | Synchr                                                | onous Modeling                                | 77  |  |  |

|   | 6.6                        | BMC on Synchronous Models                             |                                               |     |  |  |

|   |                            | 6.6.1                                                 | BMC Formula Sizes                             | 81  |  |  |

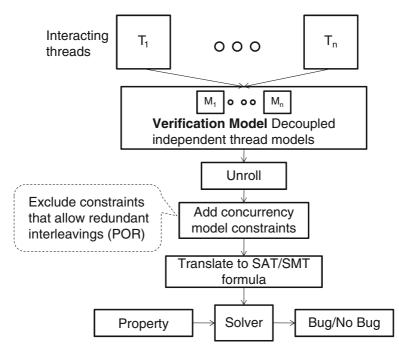

|   | 6.7                        | Asynch                                                | nronous Modeling                              | 81  |  |  |

|   | 6.8                        | BMC o                                                 | n Asynchronous Models: CSSA-Based Approach    | 83  |  |  |

|   |                            | 6.8.1                                                 | Thread Program Constraints: $\Omega_{TP}$     | 83  |  |  |

|   |                            | 6.8.2                                                 | Concurrency Constraints: $\Omega_{CC}$        |     |  |  |

|   |                            | 6.8.3                                                 | BMC Formula Sizes                             | 84  |  |  |

|   | 6.9                        | BMC o                                                 | n Asynchronous Models: Token-Based Approach   | 84  |  |  |

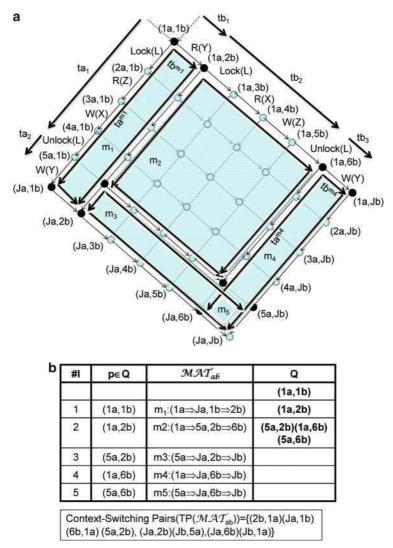

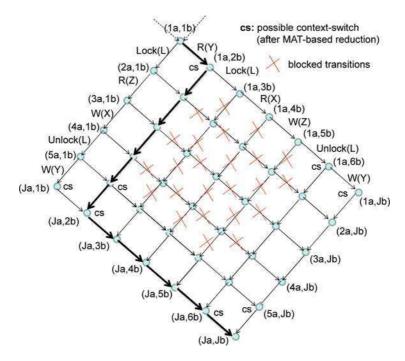

|   |                            | 6.9.1                                                 | MAT-Based Partial Order Reduction             | 86  |  |  |

|   |                            | 6.9.2                                                 | Independent Modeling                          | 89  |  |  |

|   |                            | 6.9.3                                                 | Concurrency Constraints                       | 90  |  |  |

|   |                            | 6.9.4                                                 | BMC Formula Sizes                             | 91  |  |  |

|   | 6.10                       | Compa                                                 | rison Summary                                 | 92  |  |  |

|   | 6.11                       |                                                       | Reading                                       |     |  |  |

|   | 6.12                       | Summa                                                 | ıry                                           | 93  |  |  |

| 7 | Trans                      | <b>Translation Validation of High-Level Synthesis</b> |                                               |     |  |  |

|   | 7.1                        | Overvie                                               | ew of Translation Validation                  | 97  |  |  |

|   | 7.2                        | Overvie                                               | ew of the TV-HLS Approach                     | 98  |  |  |

|   | 7.3                        | Illustra                                              | tive Example                                  | 99  |  |  |

|   |                            | 7.3.1                                                 | Translation Validation Approach               | 101 |  |  |

|   |                            | 7.3.2                                                 | Simulation Relation                           | 101 |  |  |

|   |                            | 7.3.3                                                 | Checking Algorithm                            |     |  |  |

|   |                            | 7.3.4                                                 | Inference Algorithm                           |     |  |  |

|   | 7.4                        |                                                       | ion of Refinement                             |     |  |  |

|   | 7.5                        |                                                       | tion Relation                                 |     |  |  |

|   | 7.6                        |                                                       | anslation Validation Algorithm                |     |  |  |

|   |                            | 7.6.1                                                 | Checking Algorithm                            |     |  |  |

|   |                            | 7.6.2                                                 | Inference Algorithm                           |     |  |  |

|   | 7.7                        |                                                       | lence of Transition Diagrams                  |     |  |  |

|   | 7.8                        |                                                       | ments and Results                             |     |  |  |

|   |                            | 7.8.1                                                 | Automatic Refinement Checking of CSP Programs |     |  |  |

|   |                            | 7.8.2                                                 | SPARK: High-Level Synthesis Framework         |     |  |  |

|   | 7.9                        |                                                       | Reading                                       |     |  |  |

|   | 7.10                       | Summa                                                 | ıry                                           | 121 |  |  |

| 8 | Parai                      | neterize                                              | d Program Equivalence Checking                | 123 |  |  |

|   | 8.1                        | Overvie                                               | ew of Synthesis Tool Verification             | 123 |  |  |

|   |                            | 8.1.1                                                 | Once-And-For-All Vs. Translation Validation   |     |  |  |

|   | 8.2                        | Overvie                                               | ew of the PEC Approach                        | 124 |  |  |

|   |                            |                                                       |                                               |     |  |  |

|    | 8.3     | Illustra | ative Example                          | 125 |

|----|---------|----------|----------------------------------------|-----|

|    |         | 8.3.1    | Expressing Loop Pipelining             |     |

|    |         | 8.3.2    | Parameterized Programs                 |     |

|    |         | 8.3.3    | Side Conditions                        |     |

|    |         | 8.3.4    | Executing Optimizations                |     |

|    |         | 8.3.5    | Proving Correctness of Loop Pipelining |     |

|    |         | 8.3.6    | Parameterized Equivalence Checking     |     |

|    |         | 8.3.7    | Bisimulation Relation                  |     |

|    |         | 8.3.8    | Generating Constraints                 | 130 |

|    |         | 8.3.9    | Solving Constraints                    |     |

|    | 8.4     | Param    | eterized Equivalence Checking          |     |

|    |         | 8.4.1    | Bisimulation Relation                  |     |

|    |         | 8.4.2    | Architectural Overview                 |     |

|    | 8.5     | Genera   | ateConstraints Module                  | 134 |

|    | 8.6     | Solve    | Constraints Module                     |     |

|    | 8.7     | Permu    | te Module                              |     |

|    | 8.8     | Experi   | ments and Results                      | 140 |

|    | 8.9     |          | tion Engine                            |     |

|    | 8.10    |          | r Reading                              |     |

|    | 8.11    | Summ     | ary                                    | 144 |

| 9  | Conc    | lusions  | and Future Work                        | 147 |

|    | 9.1     | High-I   | Level Property Checking                | 147 |

|    | 9.2     | Transl   | ation Validation                       | 148 |

|    | 9.3     | Synthe   | esis Tool Verification                 | 148 |

|    | 9.4     | -        | Work                                   |     |

| Re | eferenc | es       |                                        | 151 |

| In | dex     |          |                                        | 163 |

# Acronyms

| ATP   | Automated Theorem Prover                      |

|-------|-----------------------------------------------|

| BDD   | Binary Decision Diagram                       |

| BMC   | Bounded Model Checking                        |

| CCFG  | Concurrent Control Flow Graph                 |

| CDFG  | Control Data Flow Graph                       |

| CEGAR | Counter Example Guided Abstraction Refinement |

| CFG   | Control Flow Graph                            |

| CSG   | Conflict Sub-Graph                            |

| CSP   | Communicating Sequential Processes            |

| CSSA  | Concurrent Static Single Assignment           |

| CTL   | Computation Tree Logic                        |

| FIFO  | First In First Out                            |

| FSM   | Finite State Machine                          |

| FSMD  | Finite State Machine with Datapath            |

| GALS  | Globally Asynchronous Locally Synchronous     |

| HDL   | Hardware Description Language                 |

| HLD   | High-Level Design                             |

| HLS   | High-Level Synthesis                          |

| HLV   | High-Level Verification                       |

| HTG   | Hierarchical Task Graph                       |

| ICs   | Integrated Circuits                           |

| LLS   | Language of Labeled Segments                  |

| LTL   | Linear Temporal Logic                         |

| MAT   | Mutually Atomic Transaction                   |

| MC    | Model Checking                                |

| OSCI  | Open SystemC Initiative                       |

| PEC   | Parameterized Equivalence Checking            |

| POR   | Partial-Order Reduction                       |

| RTL   | Register Transfer Level                       |

| SAT   | SATisfiability                                |

| SMC   | Symbolic Model Checking                       |

| SMT   | Satisfiability Modulo Theory                  |

| TLM   | Transaction Level Modeling                    |

| TV    | Translation Validation                        |

|       |                                               |

# Chapter 1 Introduction

The quantitative changes brought about by Moore's law in design of integrated circuits (ICs) affect not only the scale of the designs, but also the scale of the process to design and validate such chips. While designer productivity has grown at an impressive rate over the past few decades, the rate of improvement has not kept pace with chip capacity growth leading to the well known design-productivity-gap [105]. The problem of reducing the *design-productivity-gap* is crucial in not only handling the complexity of the design, but also combating the increased fragility of the composed system consisting of heterogeneous components. Unlike software programs, integrated circuits are not repairable. The development costs are so high that multiple design spins are ruled out, a design must be correct in the one and often the only one design iteration to implementation.

High-Level Synthesis (HLS) [61, 62, 82, 84, 136, 147, 148, 203] is often seen as a solution to bridge the *design-productivity-gap*. HLS is the process of generating the Register Transfer Level (RTL) design consisting of a data path and a control unit from the behavioral description of a digital system, expressed in languages like C, C++ and Java. The synthesis process consists of several inter dependent subtasks such as: specification, compilation, scheduling, allocation, binding and control generation. HLS is an area that has been widely explored and relatively mature implementations of various HLS algorithm have started to emerge [82, 84, 136, 203]. This shift in design paradigm enables designers to avoid many low-level design issues early in the design process. It also enables early design space exploration, and faster functional verification time. However, for verification of high-level designs, the focus so far has been on traditional testing techniques such as random testing and scenario-based testing. Over the last few decades we have seen many unfortunate examples of hardware bugs (like Pentium FDIV bug, Killer poke, and Cyrix coma bug) that have eluded testing techniques. Recently, many techniques inspired from formal methods have emerged as an alternative to ensure the correctness of these high-level designs, overcoming some of the limitations of traditional testing techniques.

The new techniques and methodology for verification and validation at higher level of abstraction are collectively called *high-level verification* techniques. We divide the process of high-level verification into two parts. The first part deals with verifying properties of high-level designs. The methods for verifying high-level designs allow designers to check for certain properties such as functional behavior, absence of deadlocks and assertion violations in their designs. Once the properties are checked, the designers refine their design to low-level RTL manually or using a HLS tool.

HLS tools are large and complex software systems, and as such they are prone to logical and implementation errors. Errors in these tools may lead to the synthesis of RTL designs with bugs in them. As a result, the second part deals with verifying that the translation from high-level design to low-level RTL preserves semantics. Taken together, these two parts guarantee that properties satisfied by the high-level design are preserved through the translation to low-level RTL.

Unfortunately, despite significant amount of work in the area of formal verification we are far from being able to prove automatically that a given design always functions as intended, or a given synthesis tool always produces target programs that are semantically equivalent to their source versions. Yet, there have been recent advances: using practical applications of SAT solvers [74, 151], automated theorem proving [75, 164, 165], and model checking [23, 29, 196], where researchers are able to prove that the designs satisfy important properties. Also, in many cases they are able to guarantee the functional equivalence between the initial behavioral description and the RTL output of the HLS process.

We argue that despite these advances in verification, the potential for their impact on chip design largely remains unrealized. For the same reason, we argue that high-level synthesis has not made significant impact on practice, that is, they have not advanced together. Indeed, we view synthesis and verification as two sides of the design methodology coin, both equally important and need to advance together to make a practical impact on the design process. A chip design process is inherently one of elaboration, one of filling in design details to architectural and micro-architectural scaffolding. Thus, an effective design methodology incrementally refines a design as it moves through the design process. These refinements can be done manually or through elaboration tools. The chapters in this book address verification of specific properties in high-level languages as well as checking that the refined implementations are equivalent to their high-level specifications. While various literature and our experience shows that no single technique (including the ones developed specifically for high-level verification) can be universally useful, in general an intelligent combination of a number of these techniques driven by well considered heuristics is likely to prove parts of a design or tool correct, and also in many cases find bugs in them. The key contribution of this book is that it explores and describes a combination of formal techniques to do scalable verification of system designs completely automatically.

# 1.1 Overview of High-Level Verification

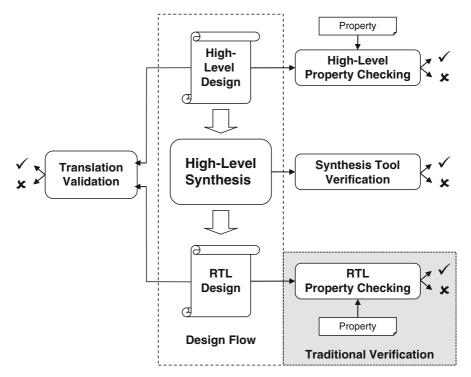

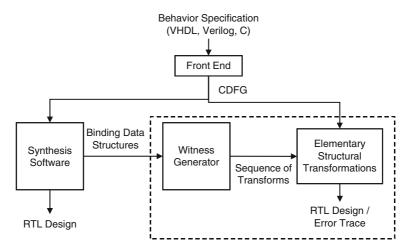

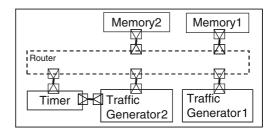

The HLS process consists of performing stepwise transformations from a behavioral specification into a structural implementation (RTL). The main benefit of HLS is that it provides faster time to RTL and faster verification time. Figure 1.1 shows

Fig. 1.1 Overview of high-level verification

the various components involved in high-level verification and how they interact. The design flow from high-level specification to RTL is shown along with various verification tasks. These tasks can be broadly classified as follows:

- 1. High-level property checking

- 2. Translation validation

- 3. Synthesis tool verification

- 4. RTL property checking

Traditionally, designers start their verification efforts directly for RTL designs. However, with the popularity of HLS, these efforts are moving more toward their high-level counterparts. This is particularly interesting because it allows faster (sometimes by three orders of magnitude [201]) functional verification time, when compared to a more detailed low-level RTL implementation. Furthermore, it enables more elaborate design space exploration, which in turn leads to better quality of design. Since RTL property checking techniques is a widely explored subject [81, 110, 142], here we focus only on the first three verification tasks.

The first category of methods, *high-level property checking*, allow various properties to be verified on the high-level designs. Once the important properties that the high-level components need to satisfy have been checked, various other

techniques are used in order to prove that the translation from high-level design to low-level RTL is correct, thereby also guaranteeing that the important properties of the components are preserved.

The second category *translation validation* include techniques that try to show, for each translation that the HLS tool performs, that the output program produced by the tool has the same behavior as the original program. Although this approach does not guarantee that the HLS tool is bug free, it does guarantee that any errors in translation will be caught when the tool runs, preventing such errors from propagating any further in the hardware fabrication process.

The third category *synthesis tool verification* consists of techniques whose goal is to prove automatically that a given optimizing HLS tool itself is correct. Although, these techniques have same goal as translation validation, i.e., to guarantee that a given HLS tool produces correct result, these techniques are different because they can prove the correctness of parts of the HLS tool *once and for all*, before they are ever run.

In this book, we have explored techniques for each one of the three areas outlined above, namely high-level property checking, translation validation, and synthesis tool verification. In the following section we briefly describe the various techniques from each of these areas that we will cover in details in the later chapters, thereby outlining the connections and trade-offs between them.

# 1.2 Overview of Techniques Covered in this Book

As mentioned in the previous section the approaches described in this book falls into three categories. The key insight behind these approaches is that by performing verification on the high-level design, where the design description is smaller in size and the design intent information is easier to extract, and then checking that all refinement steps are correct, these approaches expand current hardware development methodology to provide strong and expressive guarantees that are difficult to achieve by directly analyzing the low-level RTL code. In the following sections we briefly discuss each of these techniques that are developed specifically for high-level verification.

# 1.2.1 High-Level Property Checking

Starting with a high-level design, we will first discuss model checking techniques to verify that the design satisfies a given property such as the absence of deadlocks or assertion violations. Model checking in its pure form suffers from the well-known state explosion problem. To cope with this problem, some systems give up completeness of the search and focus on the bug finding capabilities of model checking. This line of thought lead to execution-based model checking approach, which for a given test input and depth, systematically explores all possible behaviors of the design (due to asynchronous concurrency). The most striking benefit of execution-based

model checking approach is that it can analyze feature-rich programming languages like C++, as it sidesteps the need to formally represent the semantics of the programming language as a transition relation. Another key aspect of this approach is the idea of *stateless* search, meaning it stores no state representations in memory but only information about which transitions have been executed so far. Although stateless search reduces the storage requirements, a significant challenge for this approach is how to handle the exponential number of paths in the program. To address this, one can use dynamic *partial-order-reduction* (POR) techniques to avoid generation of two paths that have the same effect on the design's behavior. Intuitively, POR techniques exploit the independence between parallel threads to search a reduced set of paths and still remain provably sufficient for detecting deadlocks and assertion violations.

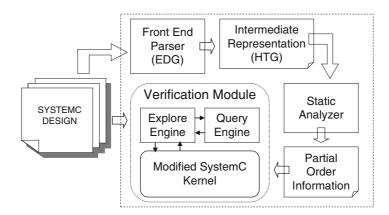

In Chap. 5 we describe an approach on execution-based model checking. This approach is implemented in Satya, a *query-based* model checking tool that combines static and dynamic POR techniques along with high-level semantics of SystemC to intelligently explore all possible behaviors of a SystemC design. During exploration the runtime overhead is reduced (without significant loss of precision) by computing the dependency information statically. To illustrate its value we describe an example, where Satya was able to automatically find an assertion violation in the FIFO benchmark (distributed as a part of the OSCI repository), which may not have been found by simulation.

Another approach for model checking is to use symbolic algorithms that manipulate sets of states instead of individual states. These algorithms avoid ever building the complete state graph for the system; instead, they represent the graph implicitly using a formula in propositional logic. *Bounded Model Checking* (BMC) is one such algorithm that unrolls the control flow graph (loop) for a fixed number of steps (say k) and checks whether a property violation can occur in k or fewer steps. This typically involves encoding the bounded model as an instance of Satisfiability (SAT) problem. This problem is then solved using a SAT or SMT (Satisfiability Modulo Theory) solver. A key challenge for BMC is to generate efficient verification conditions that can be easily solved using the appropriate solver.

Chapter 6 (contributed by Dr. Malay Ganai) discusses and compares the stateof-the-art BMC techniques for concurrent programs. In particular, it compares the synchronous and asynchronous modeling styles used in formulating the decision problems, and also the sizes of the corresponding formulas. For synchronous model it discusses the partial-order based BMC technique as presented in [205] and for asynchronous model it presents two approaches namely CSSA-based (Concurrent Static Single Assignment) [174, 204] approach and token-based [67] approach.

# 1.2.2 Translation Validation

Once the important properties of the high-level components have been verified, the translation from the high-level design to low-level RTL still needs to be proven correct, thereby guaranteeing that the important properties of the components are

preserved. One approach to prove that the translation from high-level design to lowlevel RTL is correct is to show – for each translation that the HLS tool performs – the output program produced by the tool has the same behavior as the original program.

In Chap. 7, we describe a translation validation algorithm that uses a *bisimulation relation* approach to automatically prove the equivalence between two concurrent systems. We discuss the implementation of the above algorithm in a system called **Surya**. Furthermore, we describe our experience to use it for validating the synthesis process of **Spark** [84], a parallelizing HLS framework. **Surya** validates all the code transformation phases (except for parsing, binding and code generation) of **Spark** against the initial behavioral description. The experiments with **Surya** showed that with only a fraction of the development cost of **Spark**, it can validate the translations performed by **Spark**, and it even uncovered two previously unknown bugs that eluded testing and long-term use.

### **1.2.3** Synthesis Tool Verification

In order to make a practical impact on improving the level at which designs are done it is important that both synthesis and verification methods are targeted at high-level design. Practically, this means verifying not only the design but also the process that produces such designs. While validation of manual parts of the design process is out of scope here, we focus on methods that guarantee that the (high-level) synthesis tool itself is correct. This approach to validation of both process and product are at the core of our incremental refinement methodology that builds upon advances in translation validation and synthesis tool verification. Chapter 8 (contributed by Zachary Tatlock) discuss an approach that verifies the correctness of critical parts of a synthesis tool. Because some of the most error prone parts of an HLS tool are its optimizations, this approach proves the correctness of optimizations using *Parameterized Equivalence Checking* (PEC) [120]. Moreover, the PEC approach is not limited to only HLS tools; it can be used for any domain that transforms an input program using semantics-preserving optimizations, such as optimizers, compilers, and assemblers.

The PEC technique is a generalization of translation validation that proves the equivalence of *parameterized programs*. A parameterized program is a partially specified program that can represent multiple concrete programs. For example, a parameterized program may contain a section of code whose only known property is that it does not modify certain variables. To highlight the power of PEC, a domain-specific language is designed for implementing complex optimizations using many-to-many rewrite rules. This language is used to implement a variety of optimizations including software pipelining, loop unrolling, and loop unswitching. The PEC implementation was able to automatically verify that all the optimizations implemented in this language preserve program behavior.

# **1.3** Contributions of the Book

The primary contribution of this book is to explore various formal techniques that can be used for high-level verification. We believe by performing verification on the high-level design, and then checking that all refinement steps are correct, the domain of high-level verification can provide strong and expressive guarantees that would have been difficult to achieve by directly analyzing the low-level RTL code. The goal is to move the functional verification tasks earlier in the design phase, thereby allowing faster verification time and possibly quicker time to market.

To systematically explore the domain of high-level verification, we classified the various verification tasks into three main parts, namely high-level property checking, translation validation, and synthesis tool verification. We describe approaches for each of the above mentioned verification tasks. The novelty of these approaches is that they combine a number of formal techniques along with well considered heuristics to do *scalable* verification of high-level designs completely *automatically*.

We discuss the implementation of some of these high-level verification approaches into prototype tools. We also describe the complemented methodology to use these tools. The tools are: Satya for high-level property checking, Surya for translation validation, and PEC for synthesis tool verification. These tools use state-of-the-art techniques from areas such as model checking, theorem proving, satisfiability modulo theories, static analysis and compiler correctness. Apart from these tools, this book also covers a comparison of recent BMC techniques for concurrent programs.

The techniques presented here exploits structures specific to high-level designs, thereby in many cases simplifying the algorithms and improving their performance. For example, Satya exploits SystemC specific semantics to efficiently explore a reduced set of possible executions, and Surya relies on structure preserving transformations that are predominantly used in HLS.

The prototype tools enables experimentation with large "real-world" designs and tools. The key characteristics of the high-level verification approaches covered are as follows:

*Scalable*: Most of the techniques discussed here are modular as they work on one entity at a time. For example, **Surya** works on one procedure at a time, and **PEC** works on one transformation at a time. Furthermore, in the cases where the entire design have to analyzed, various reduction techniques like partial-order reduction, context bounding, and program structure based reduction (e.g. lock-unlock, fork-join, wait-notify, etc.) is applied. While these software engineering decisions and reductions theoretically limits the scope of the verification tasks on a given design, it is rarely an issue in practice as it follows the designer's and tool developer's programming abstractions.

*Practical*: The prototype tools are practical enough to be applied to industrial strength designs and tools. For instance, **Satya** was used to check an industrial benchmark namely the TAC platform [149], and **Surya** is being used to validate the synthesis process of **Spark** [84], a state-of-the-art academic HLS framework.

*Useful*: The tools are able to automatically guarantee the correctness of various properties and transformations. Apart from correctness guarantee, these tools are also quite useful for finding bugs. For example, **Satya** was able to automatically find an assertion violation in the FIFO benchmark (distributed as a part of the OSCI repository), and **Surya** was able to uncover two previously unknown bugs in the **Spark HLS** framework.

### **1.4 Book Organization**

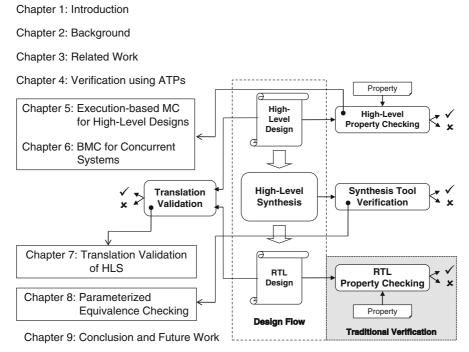

The organization of this book is shown in Fig. 1.2. Chapter 2 presents a brief overview of the three different parts of high-level verification on which the approaches are applied. More specifically, we present a brief introduction of high-level designs, RTL designs, and high-level synthesis. We also introduce in this chapter the concepts of model checking, partial-order reduction and a representation of concurrent programs, which we use in the rest of this book.

In Chap. 3, we present a detailed discussion of the related works in the area of high-level verification. In particular, we divide the related works in to three main areas, namely high-level property checking, translation validation, and synthesis tool

Fig. 1.2 Book organization

verification. We discuss the various tools and techniques explored in these areas. Apart from these related works, in each of the following chapters we again point the reader to further readings that are specific to the chapter.

The next chapter (Chap. 4) describes in details two core verification techniques that uses Automated Theorem Provers (ATP). It first provides a brief introduction to Satisfiability Modulo Theories (SMT) and then discusses two formal techniques, namely Hoare Logic and Weakest Preconditions, which are extensively used in high-level verification.

Chapters 5 and 6 discuss two high-level property checking techniques. In Chap. 5, we present an execution-based model checking approach for the high-level language SystemC. This approach starts with a design written in SystemC, and then intelligently explore a subset of the possible executions till a certain depth to verify that the design satisfies a given property such as absence of deadlocks or assertion violations. Chapter 6, on the other hand discuss symbolic analysis approaches for concurrent programs. It compares state-of-the-art synchronous and asynchronous BMC approaches for performance and scalability.

Chapter 7 discusses a translation validation approach that proves the translation from high-level design to the scheduled design is correct. We describe in detail an algorithm that uses a bisimulation relation approach to automatically prove the equivalence between two concurrent programs. In this chapter, we also report our efforts to validate the synthesis process of **Spark**, a parallelizing HLS framework.

In Chap. 8 we describe another approach that also proves the result of HLS process is correct. This approach called *Parameterized Equivalence Checking* falls in the synthesis tool verification category. This technique generalizes the translation validation technique of Chap. 7 to prove that the optimizations performed by a HLS tool is correct once and for all. We describe the details of the algorithm and experiments.

Finally, Chap. 9 wraps-up the book with a conclusion and a discussion of future work on high-level verification.

# Chapter 2 Background

We envision a design methodology that is built around advances in high-level design and verification to improve the quality and time to design microelectronic systems. In this chapter, we will present a brief overview of the three different parts of high-level verification as shown in Fig. 1.1 on which the verification algorithms are applied. We first present in Sect. 2.1 and in Sect. 2.2 a description of high-level designs and RTL designs respectively. We then in Sect. 2.3 give a brief introduction of high-level synthesis. In the next two sections we introduce the concept of model checking, and our program representation scheme that is used throughout the book.

# 2.1 High-Level Design

A high-level design is a behavioral or algorithmic specification of a system. This specification typically is written in a high-level language such as behavioral VHDL, C and C++ (and variants). The main reason to use a high-level language is to be able to describe both the hardware and software components of a design, and to allow large system designs to be modeled uniformly. The enormous flexibility in describing computations in a high-level language enables a designer to capture design description at multiple levels of abstraction from behavioral descriptions to transaction level modeling (TLM) [27, 78, 192]. Intuitively, high-level language, designers often use programming constructs such as conditionals and loops for programming convenience often with no notion of how these constructs may affect synthesis results. For example, SystemC [78] TLM supports new synchronization procedures such as wait-notify, which makes current techniques for synthesis in-applicable. One of the key aspects of high-level design is the ability to provide a golden reference of the system in an early phase of the development process.

In this book, we use various high-level languages as input for the verification techniques. In Chap. 5 we will discuss a property checking approach for the SystemC language. In Chap. 6 we describe various BMC techniques that work on concurrent C programs. Also, the translation validation approach described in Chap. 7 uses two high-level languages namely, C and CSP.

<sup>S. Kundu et al.,</sup> *High-Level Verification: Methods and Tools for Verification of System-Level Designs*, DOI 10.1007/978-1-4419-9359-5\_2,

© Springer Science+Business Media, LLC 2011

# 2.2 RTL Design

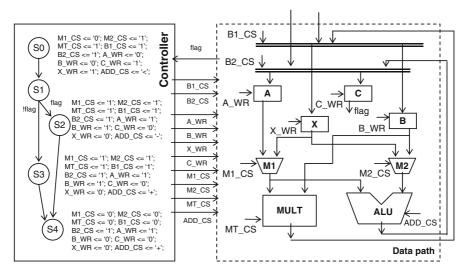

At the current state of practice, RTL designs are generally considered low-level designs consisting of structural implementation details. The RTL describes the exact behavior of the digital circuits on the chip, as well as the interconnections to inputs and outputs. The structural implementation usually consists of a data path, a controller and memory elements. Figure 2.2 shows the controller and data path for a RTL design. The data path consists of component instances such as ALU, multiplier, registers, and multiplexers selected from a RTL component library. The controller is a finite-state machine (FSM) describing an ordering of the operations in the data path. A tiny functional error in the RTL design are often tedious, complex, and error-prone as such it is desirable to have a good high level design and then use incremental refinement process to generate the final RTL.

In this book, we do not consider RTL property verification. However, for the purpose of translation validation we want to check the equivalence between a pair of high-level design and RTL design. Unfortunately, checking equivalence between the high-level design and RTL design is a hard problem. As such in Chap. 7 we describe an approach that validates the equivalence between a high-level design written in C and the scheduled design (described in the next section), which is an intermediate low-level design.

# 2.3 High-Level Synthesis

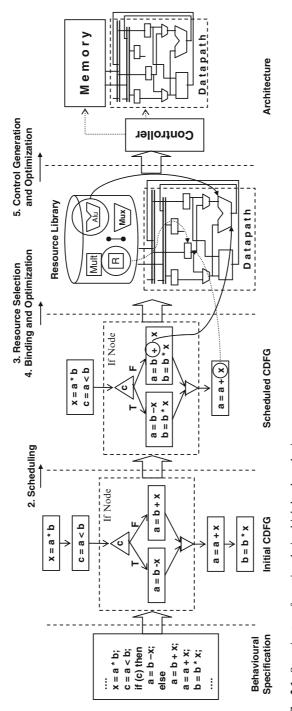

HLS can be seen as stepwise transformation of a high-level design into a RTL design as shown in Fig. 2.1. Figure 2.2 shows the RTL design for the example in Fig. 2.1. Different HLS tool produces different RTL design for the same high-level input as it minimizes various metrics like area, power and timing. HLS starts by capturing the behavioral description in an intermediate representation, usually a control data flow graph (CDFG). Thereafter the HLS problem has usually been solved by dividing the problem into several sub-tasks [84]. Typically the sub-tasks are:

Allocation: This task consists of determining the number of resources that need to be allocated to synthesize the hardware circuit (not shown in the figure). Typically, designers can specify an allocation in terms of the number of resources of each resource type. Resources consist of functional units (like adders and multipliers), registers and interconnection components (such as multiplexers and buses). The allocated resources constitute the *resource library* for the design.

In our example (Figs. 2.1 and 2.2), the resource library contains a multiplier, an ALU, 2 multiplexers, 4 registers, 2 buses and a memory component (not all components are shown in the figure). Usually, a designer chooses these components based on several design constraints like area, performance and power.

Fig. 2.2 The controller and the data path for the example in Fig. 2.1

2. *Scheduling*: This step determines the time step or the clock cycle in which each operation of the design executes. The ordering between the "scheduled" operations is constrained by the data (and possibly control) dependencies between the operations. Scheduling is often done under constraints on the number of resources.

Resource constraint scheduling algorithms are highly dependent on the resource allocation task. For example, since in the allocation step the designer chose a multiplier and an ALU, we were able to schedule both the statements (x = a \* b and c = a < b) in one cycle ( $C_1$ ). In contrast, if only an ALU is chosen then both the operations have to be scheduled in different cycles.

Schedulers also do code motions to enhance *concurrency* and hence improving resource utilization. In our example, the statement b = b \* x has been moved inside the 'if block' by the scheduler to schedule it in cycle  $C_2$  instead of cycle  $C_3$ .

3. *Resource selection*: This task determines the resource type from the resource library that an operation executes on. The need for this task arises because there are several resources of different types (and different area and timing) that an operation may execute on. For example, an addition may execute on an adder, an ALU, or a multiply-accumulate unit. Resource selection must make a judicious choice between different resources such that a metric like area or timing is minimized.

In the example, all multiplication operations are done using the multiplier and the addition and comparison operations are executed in the ALU (see Figs. 2.1 and 2.2).

4. *Binding and Optimization*: This task determines the mapping between the operations, variables and data (and control) transfers in the design graph and the specific resources in the resource library. Hence, operations are mapped

to functional units, variables to registers and data/control transfers to interconnection components. Optimizations deals with the minimization of the physical components in the synthesized design.

In our case, the variables a, b, c, and x in the behavioral description are bound to the registers A, B, C, and X respectively. Figure 2.1 shows the binding of the variable a to the register A and the operation + to the ALU. Notice that multiple operations can be bound to the same resource. The complete binding of the operations and the data/control transfers to functional units and interconnection components are shown in Fig. 2.2.

5. *Control Generation and Optimization*: Control synthesis generates a control unit (usually FSM) that implements the schedule. This control unit generates control signals that control the flow of data through the data path (i.e. through the multiplexers). Control optimization deals with minimizing metrics such as area and power.

Operations in the scheduled CDFG are replaced by the concrete values of control signals going to the data path. Thus, for example the concurrent operations (x = a \* b and c = a < b) are replaced by the following signals.

M1\_CS <= '0', M2\_CS <= '1', MT\_CS <= '1', B1\_CS <= '1', B2\_CS <= '1', A\_WR <= '0', B\_WR <= '0', C\_WR <= '1', X\_WR <= '1', ADD\_CS <= '<'

According to these control signals, the contents of the registers A and B are simultaneously fed as inputs to the MULT and the ALU units and then the result of MULT and ALU is saved in the registers X and C respectively.

HLS is an area that has been widely explored and relatively mature implementations of various HLS algorithm have started to emerge [84, 136, 203]. These tools are usually very large and complex piece of software, as such their implementation are prone to errors. In Chap. 7 we discuss an approach that validates parts of a parallelizing HLS tool called **Spark** [84]. Furthermore, in Chap. 8 we describe a technique that can once-and-for-all prove the correctness of important parts of a HLS tool.

# 2.4 Model Checking

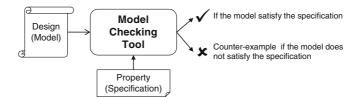

Does the design satisfy a given property (specification)? This is one of the key question that every hardware designer have to answer. Fortunately, in the last two decades, researchers have made tremendous progress in developing tools and techniques for verifying properties and design. Although, it is hard to prove if a design satisfy a given specification that is written in English, it is possible for specifications that are formulated using unambiguous formal language. Model Checking [101] is

the most successful approach in this direction. Given a model of a system, it tests *au-tomatically* whether this model satisfy a given specification (Fig. 2.3). Typically, the model of the (hardware) system is represented using a Finite State Machine (FSM) and the specification is formulated in temporal logic [169] formula. The FSM is a directed graph consisting of nodes (or vertices) and edges.

# 2.4.1 Simple Elevator Example

This section describes how we can use model checking to verify properties of a simple two floor elevator example, which is shown in Fig. 2.4 using a C-style language. The program has a main function Elevator (lines 5–11) and a helper function Move (lines 12–19). The global variables of the program are shown in lines 1–4. The program uses an *enum* variable *currFloor* to keep track in which floor the elevator is currently located. It also use a boolean array *doorOpen* to indicate if the door of the elevator is open in the corresponding floor and a boolean variable *moving* to represent if the elevator is currently moving or is stopped. The Elevator function in an infinite loop sets the *doorOpen* variable for the current floor to *false* and the *moving* variable to *true* and then calls the helper function Move. The Move function depending on the current floor where the elevator is present changes the *currFloor*.

Fig. 2.3 The model checking approach

- 1. enum  $Floor = \{1, 2\}$

- 2. Floor currFloor

- 3. bool doorOpen[2]

- 4. bool moving

```

12. function Move()

5. function Elevator()

if (currFloor == 1)

13.

while (true)

6.

14.

++currFloor

7.

wait 1 min

15.

elseif (currFloor == 2)

8

doorOpen[currFloor - 1] = false

--currFloor

16.

9.

moving = true

17.

moving = false

10.

Move()

18.

doorOpen[currFloor - 1] = true

11.

return

19.

return

```

Fig. 2.4 Simple elevator example

variable up or down and then sets the state of the *doorOpen* of that floor to open and the state of the elevator to stop. Although this example may appear trivial, it can be easily extended to one with many floors, fire emergency state, and priority of floors, thereby increasing the complexity of the elevator controller.

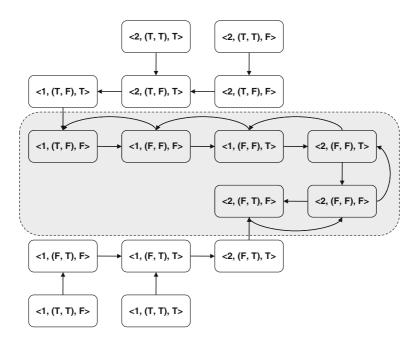

A *data state* for this example is defined by a tuple of values for each of the three global variables. For example, one particular data state is

$$\langle currFloor = 1, doorOpen[2] = (true, false), moving = false \rangle$$

For brevity we use the notation  $\langle 1, (T,F), F \rangle$  to represent the above data state. An assignment statement in Fig. 2.4 defines how the data state of the program changes. The data-state space of our example along with their possible transitions is shown in Fig. 2.5. Not all data states are valid initial data state. For example, let us assume that when the system starts the elevator is not moving and both the doors are closed. For this assumption, the possible reachable data states are shown within the dotted line in Fig. 2.5. A *program state* is defined as a data state along with the valuation of another variable the program counter (or program location) *pc*. The variable *pc* defines the possible locations of the program. Informally, the different values of *pc* is given in terms of the line number of the program. For our example, the variable *pc* can take values in the range [5–19] and it's initial value is 5.

An important concept in model checking is that of an *execution sequence* (also referred as execution path). Starting from a given initial program state an

Fig. 2.5 A FSM of the data-state space for the simple elevator example

execution sequence is informally defined as the possibly infinite sequence of states obtained by following the transitions in the FSM. Note that for concurrent programs this concept of execution sequence is generalized into an *execution tree* as from any state there are many possible next states. In general, there are many possible execution sequences for a given program. The goal of model checking is to check whether or not the execution sequences satisfies a user-given property specification.

# 2.4.2 Property Specification

A property is usually expressed using a formula specified using boolean propositional logic. For programs we also need to specify properties involving execution paths. Some form of temporal logic is usually suitable for specifying such properties. Computation Tree Logic (CTL) is a branching time temporal logic that has been extensively used by model checking tools for this purpose.

In CTL formulas are composed of *path quantifiers* and *temporal operators*. There are two path quantifiers – A (for all paths) and E (for some path) – for specifying properties of (all or some) paths beginning from a state. There are five temporal operators – X (next state), F (for some state), G (for all states), U (until), and R (release) – that describes properties of (all or some) states of a path. These quantifiers and operators are summarized as follows:

### Path Quantifiers:

- A  $\phi = \phi$  holds on *all* paths starting from the current state.

- **E**  $\phi$  There *exists* at least one path starting from the current state where  $\phi$  holds.

### Temporal Operators:

- $\mathbf{X} \phi \qquad \phi$  holds at the *next* state.

- **G**  $\phi$  **o** holds on *all* states for the entire subsequent path.

- **F**  $\phi$   $\phi$  *eventually* holds on some state on the subsequent path.

- $\phi \mathbf{U} \psi = \phi$  holds *until* at some state  $\psi$  holds and eventually  $\psi$  holds.

- $\phi \mathbf{R} \psi$   $\psi$  holds until and including the state where  $\phi$  holds, however,  $\phi$  is not required to hold eventually.

Some examples of properties are as follows:

- **EF**(*moving*  $\land$  *currFloor* == 1): It is possible to get to a state where the elevator is moving and it is at the first floor.

- AG(EF(¬*doorOpen*[0])): From any state it is possible to get to a state where the door of the first floor is closed.

- AG(*moving* ⇒ AF(¬*moving*)): If the elevator is moving then it will be eventually stopped.

# 2.4.3 Reachability Algorithm

Given a temporal logic formula  $\phi$  and a model of the program in some form of FSM  $\mathcal{M}$ , a simple model-checking algorithm essentially reduces to a graph reachability algorithm that examines every reachable node of  $\mathcal{M}$  to check if it satisfies the formula  $\phi$ .

For example, consider a property  $\mathbf{EF} f$  where f is a boolean propositional formula not involving any temporal quantifiers or operators. Let the FSM  $\mathscr{M}$  be a tuple  $\mathscr{M} = (\mathscr{N}, \mathscr{I}, \mathscr{E})$ , where  $\mathscr{N}$  is a set of nodes,  $\mathscr{I} \subseteq \mathscr{N}$  is a set of initial nodes, and  $\mathscr{E} \subseteq \mathscr{N} \times \mathscr{N}$  is a set of edges. The nodes represent program states, and the edges represent possible transitions which may alter the state. The property  $\mathbf{EF} f$  is satisfied in  $\mathscr{M}$  if there exists some state in  $\mathscr{M}$  that is reachable from the initial states and the formula f is true in that state.

Figure 2.6 shows the algorithm CheckEF, a procedure that traverses the graph to check if the formula f holds in any state of the graph. The algorithm maintains a set *reach* of reachable states and a set *worklist* of states that are found to be reachable but whose successors may not have been explored. Initially, the set *reach* is empty, and the set *worklist* contains all the initial states. The main loop of the algorithm starts by picking a state from the *worklist*. If the formula f holds in that state then we know that the property **EF** f is satisfied in  $\mathcal{M}$ , and the algorithm ends. Otherwise, if the state has not been visited before, the successors of the state are added to the *worklist*. The process is repeated until all reachable states have been explored, which happens when the *worklist* becomes empty. At this point, *reach* contains exactly the set of reachable states and the formula f does not hold in any of these states. Hence, the property **EF** f is not satisfied in  $\mathcal{M}$ . The loop in the algorithm terminates for all programs with finite reachable states.

In practice, model-checking algorithms are far more complex, they use intelligent heuristics and efficient data structures to prune the state space to avoid checking those parts where the property is guaranteed to be true. Recent model checkers are also able to verify properties of state spaces of size as large as 10<sup>20</sup> states [23]. Pioneering work on model checking was done by E.M. Clarke, E.A. Emerson and A.P. Sistla [32, 33, 52] and by J.P. Queille and J. Sifakis [173]. E.M. Clarke,

| 1.  | procedure $CheckEF(f)$                                                                         |

|-----|------------------------------------------------------------------------------------------------|

| 2.  | let $reach := \emptyset$                                                                       |

| 3.  | <b>let</b> <i>worklist</i> := $\{\iota \mid \iota \in \mathscr{I}\}$                           |

| 4.  | while worklist not empty do                                                                    |

| 5.  | let $\sigma := worklist$ .Remove                                                               |

| 6.  | if f holds in $\sigma$ then                                                                    |

| 7.  | " <b>EF</b> f is satisfied in $\mathcal{M}$ "                                                  |

| 8.  | return                                                                                         |

| 9.  | if $\pmb{\sigma}  otin reach$ then                                                             |

| 10. | $reach := reach \cup \{\sigma\}$                                                               |

| 11. | <i>worklist</i> := <i>worklist</i> $\cup$ { $\sigma' \mid (\sigma, \sigma') \in \mathscr{E}$ } |

| 12. | " <b>EF</b> $f$ is not satisfied in $\mathcal{M}$ "                                            |

| 13. | return                                                                                         |

| Fig. 2.6         | Algorithm for                      |

|------------------|------------------------------------|

| checking         | if <b>EF</b> <i>f</i> is satisfied |

| in $\mathcal{M}$ |                                    |

E.A. Emerson, and J. Sifakis shared the 2007 Turing Award for their work on model checking. In Chap. 3 we will cover some of the advances in model checking and provide pointers for them. In Chaps. 5 and 6 we present two model-checking algorithms that are related to high-level verification.

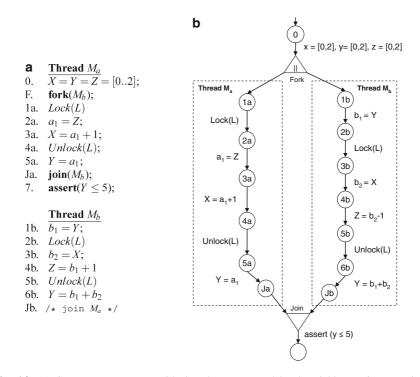

### 2.5 Concurrent Programs

A concurrent program usually consists of a set of processes or components that interact with each other. The execution semantics of a concurrent program can be broadly divided into two types: *asynchronous* and *synchronous*. In asynchronous (or interleaved) mode of execution only one atomic statement of a process is executed at any time. In synchronous mode of execution an atomic statement from each of the processes is execute at the same time. For example, consider a simple program of two processes  $P_1$  and  $P_2$  interacting with shared variables y and z. The processes have only one statement each as shown below.

| Process $P_1$ | Process $P_2$ |

|---------------|---------------|

| y := z        | z := y        |

In asynchronous mode of execution only one process is executed at any time. Therefore, at the end of the execution either both shared variables y and z will have the old value of z (if  $P_1$  is executed first) or both variables will have the old value of y(if  $P_2$  is executed first). On the other hand, in synchronous mode of execution the values of y and z will be swapped (exchanged).

Apart from the mode of execution, two concurrent programs can also differ based on their mode of communications. Concurrent programs can again be *synchronous* (blocking) or *asynchronous* (non-blocking) based on their mode of communication. In synchronous mode, communication between processes is unbuffered, and processes wait (or block) until the data between them has been transferred. In asynchronous mode, communication between processes is buffered and the processes do not wait after sending or before receiving data.

# 2.5.1 Representation of Concurrent Programs

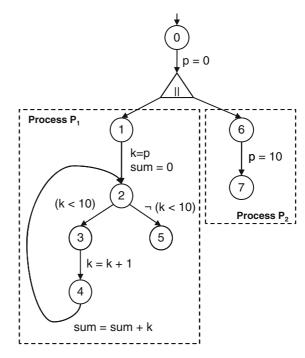

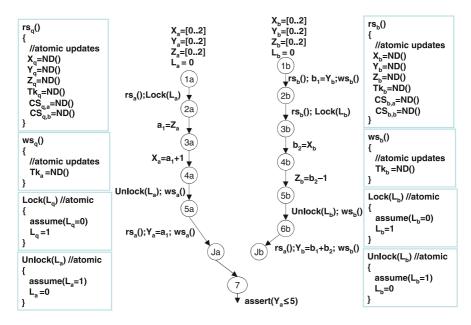

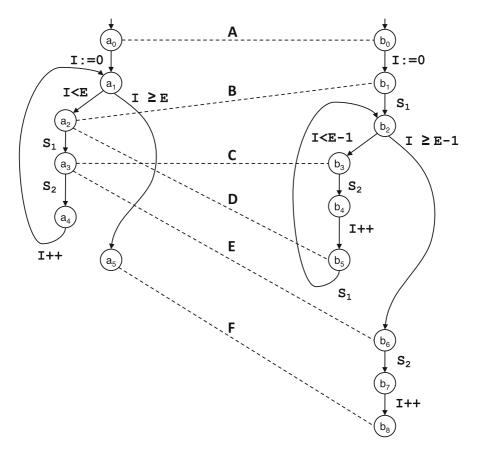

Unless otherwise specified all of the programs we consider are Globally Asynchronous Locally Synchronous (GALS). This means that the programs consists of components that are asynchronous (interleaved), however within a component there can be statements that are synchronous (i.e. multiple statements can be executed at the same time). We visually represent a concurrent program using an internal Concurrent Control Flow Graph (CCFG) representation. Concurrent behavior of programs can be modeled as synchronous or asynchronous. The CCFG of a simple Fig. 2.7 Our Concurrent Control Flow Graph (CCFG) representation

example is shown in Fig. 2.7. In general, we omit the details of the actual code, because the CCFG representation is complete. This example consist of two processes  $P_1$  and  $P_2$ . We use a node with the symbol | | to denote the asynchronous parallel composition of child processes (components). Statements on the same edge are executed at the same time (i.e. synchronously). The example computes the sum from 1 to 10 in the variable sum if the process  $P_1$  is executed before  $P_2$ , otherwise sum is 0.

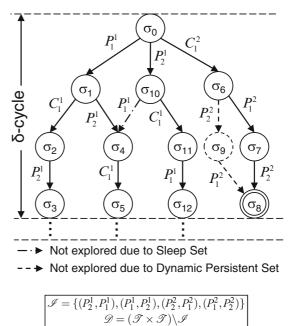

# 2.5.2 Partial-Order Reduction

In this section, we provide an overview of the partial-order reduction (POR) technique, which is used in almost all approaches discussed in this book. Verification of asynchronous concurrent programs is hard due to various possible interleavings between the processes. The verification model is typically obtained by composing individual process models using interleaving semantics. Thus, in the worst case, the global state space can be the product state space of the individual processes. To combat this state explosion problem, most methods employ POR techniques to restrict the state-traversal to only a representative subset of all interleavings, thereby, avoiding exploring the redundant interleaving among independent transitions [70].

POR in its most simple form exploit the commutativity of concurrently executed transitions, which result in the same state when executed in different orders.

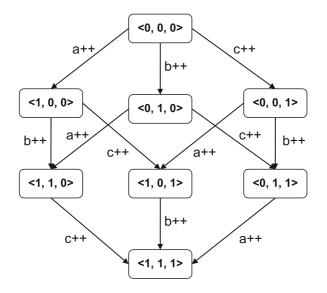

Fig. 2.8 Possible data states due to executing three concurrent statements

For example, consider a simple program of three processes  $P_1$ ,  $P_2$ , and  $P_3$ . The processes have only one statement each as shown here.

Process

$$P_1$$

Process  $P_2$ Process  $P_3$  $a++$  $b++$  $c++$

Let the initial data state of the program be  $\langle a = 0, b = 0, c = 0 \rangle$  (for brevity we use the notation  $\langle 0, 0, 0 \rangle$ ). Figure 2.8 shows the various possible data states that can be reached from the initial state due to interleavings. The three statements in this example are independent, i.e., their order of execution does not change the final state. Now, if the property we are considering is only dependent on the final state, then during exploration using POR we only need to traverse one of these interleavings.

POR techniques are extensively used by *software model checkers* for reducing the size of the state space of concurrent system [71,94]. Other state space reduction techniques, such as slicing [88, 184] and abstraction [9], are orthogonal and can be used in conjunction with POR. The POR techniques can be divided in two main categories: *static* [70] and *dynamic* [57].

The main static POR techniques are *persistent/stubborn* sets and *sleep* sets [70]. Intuitively, the persistent/stubborn set techniques compute a provably sufficient subset of the enabled transitions in each visited states such that if a selective search is done using only the transitions from these subsets the detection of all the deadlocks and safety property violations is guaranteed. All these algorithms infer the persistent sets from the static structure (code) of the system being verified. On the other hand, the sleep set techniques exploits independences between the transitions in the persistent sets to reduce interleavings. Both these techniques are orthogonal and can be

applied simultaneously [70]. In contrast, the dynamic POR technique evaluates the dependency relation dynamically between the enabled and executed transitions for a given execution. In particular, it starts by executing the program until completion, and then infers the persistent sets dynamically by collecting information about how threads have communicated during this specific execution trace. This technique is particularly important as we will see later that most of the approaches discussed in this book uses some form of POR.

#### 2.6 Summary

In this chapter, we presented a brief overview of the three main concepts related to our formulation of high-level verification namely, high-level design, RTL design, and HLS. We first presented a description of high-level design and RTL design in Sects. 2.1 and 2.2. We also mentioned the different high-level languages and RTL representation that we use in this book. We then briefly discussed in Sect. 2.3 the various steps of HLS using a simple example. We also provided a brief introduction to model checking in Sect. 2.4. Finally, in Sect. 2.5, we introduced the concurrent program representation and describe an important technique called partial-order reduction that we use throughout this book.

# Chapter 3 Related Work

Each one of the three areas of high-level verification outlined in Chap. 1, namely high-level property checking, translation validation, and synthesis tool verification, have been explored in a wide variety of research efforts. In this chapter, we discuss various techniques from each of these areas that are directly relevant to this book.

# 3.1 High-Level Property Checking

The high-level designs written using languages like C, SystemC, SystemVerilog are mostly software programs with support for specialized hardware data types and other hardware features like synchronous concurrency, synchronization, and timing [83]. Thus, many efforts to use software verification tools to verify these designs have been explored. Model checking is the most prevalent automatic verification technique for software and hardware. It is a technique for verifying that a hardware or software system satisfy a given property (specification). These properties, which are usually expressed in temporal logic, typically encode deadlock and safety properties (e.g. assertion violations). In this section, we survey several software model checking techniques grouped as *explicit* and *symbolic* techniques.

# 3.1.1 Explicit Model Checking

In explicit state enumeration model checking, the reachable states of a design are generated using an exhaustive search algorithm. This technique explicitly stores the entire state space in memory and checks if certain error states are reachable. For finite state system this technique is both sound (i.e. whenever model checking cannot reach a given error state, it is guaranteed to not reach that error state ever in real execution) and complete (i.e. whenever model checking finds an error, it is guaranteed to be an error in real execution). However, as the size of the finite state spaces grow larger and larger, this technique suffers from the well known *state explosion* problem. To address the state explosion problem, researchers use techniques

to construct the state space *on-the-fly* [94] during the search, rather than generating all the states and transitions before the search. In addition, they use *bit-state hash-ing* [94], in which the hash value of the reachable state is stored, instead of the state itself. Due to possible hash collision the bit-state hashing technique is unsound. Other techniques include *partial-order-reduction* [70], *symmetry reduction* [35, 53] and *compositional techniques* [34].

Intuitively, the partial-order reduction technique exploits the independence between parallel threads to compute a provably sufficient subset of the enabled transitions in each visited states such that if a selective search is done using only the transitions from these subsets the detection of all the deadlocks and safety property violations is guaranteed. Symmetry reduction on the other hand exploits symmetries in the program, and explores one element from each symmetry class. Compositional techniques decompose the original verification problem to related smaller problems such that the result of the original problem can be obtained by combining the smaller ones.

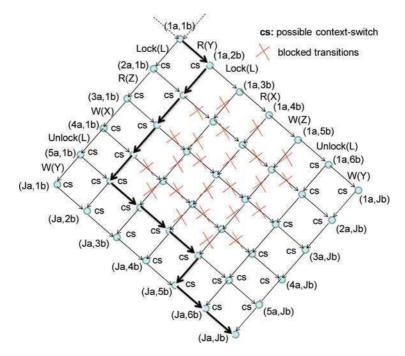

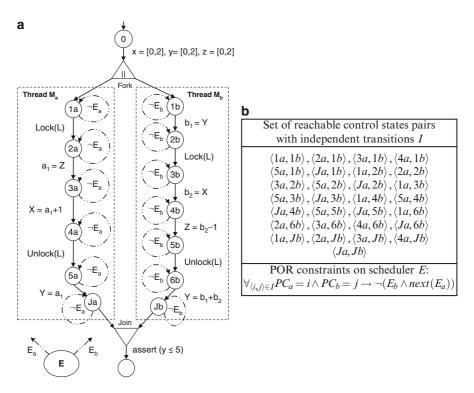

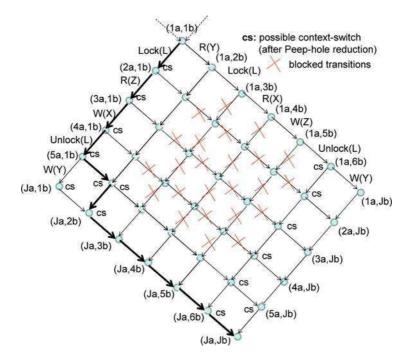

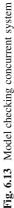

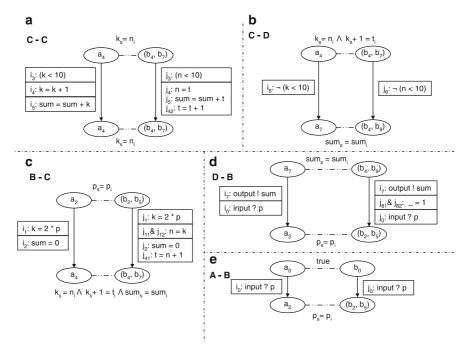

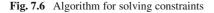

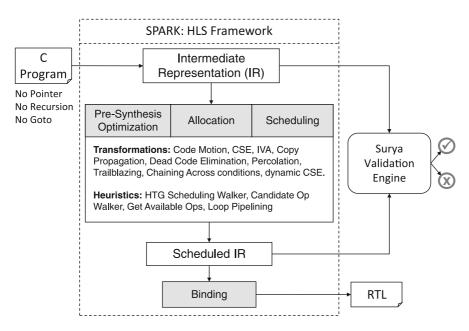

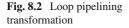

The most popular finite state explicit model checker for concurrent programs are SPIN [94] and MURPHI [46]. Both tools have been successfully used for verification of sequential circuits and protocols.