Torsten Kempf Gerd Ascheid Rainer Leupers

# Multiprocessor Systems on Chip

**Design Space Exploration**

Multiprocessor Systems on Chip

Torsten Kempf • Gerd Ascheid • Rainer Leupers

# Multiprocessor Systems on Chip

**Design Space Exploration**

Torsten Kempf RWTH Aachen University Institute for Integrated Signal Processing Systems (ISS) Sommerfeldstr. 24 52074 Aachen Germany torsten.kempf@iss.rwth-aachen.de

Gerd Ascheid RWTH Aachen University Institute for Integrated Signal Processing Systems (ISS) Walter-Schottky-Haus Room 24 A 207 Sommerfeldstr. 24 52074 Aachen Germany ascheid@iss.rwth-aachen.de Rainer Leupers RWTH Aachen University Software for Systems on Silicon Templergraben 55 52056 Aachen Germany leupers@iss.rwth-aachen.de

ISBN 978-1-4419-8152-3 e-ISBN 978-1-4419-8153-0 DOI 10.1007/978-1-4419-8153-0 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011921340

© Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

Dedicated to Meike and Flora, to my brother Tibor and to my parents Brigitte and Wolfgang.

### Preface

This book highlights the research conducted in the area of Multi-Processor Systemon-Chip design for more than five years. The work documented within was carried out during my time at the Institute of Integrated Signal Processing Systems (ISS) at the RWTH Aachen University.

More than putting forth a brilliant idea, the conducted work reflects a careful evolution of design methodologies and associated tooling. The original motivation dates back to the GRACE++ methodology. This early attempt of system level modeling with SystemC targeted the efficient and convenient exploration of complex architectures, with particular focus on communication architectures. The tight links to industry partners and the ongoing development turned this technology into a commercialized tool called Architects View Framework.

At the time I joined the ISS as a researcher, plenty of experience had been gained in modeling System-on-Chip platforms. By the investigation of several industrial platforms, we soon discovered that the detailed modeling of processing elements limited the capabilities of design space exploration. Accordingly, we extended the methodology to a more abstract modeling of processing elements and, furthermore, broadened it to capture the challenges of temporal and spatial task mapping. With the help of many partners from different research cooperations, we have evolved the methodology and were lucky to be able to validate our approach with relevant design problems. Finally, this innovative technology was brought to the market and became commercially available in 2009.

All the design issues to be found in the development of MPSoC platforms cannot be mastered by a single person. Therefore, I am grateful for the strong support of researchers with whom I had the pleasure to work.

First of all, I would like to thank my supervisor and Prof. Gerd Ascheid who is the co-author of this book. Apart from his valuable feedback and deep interest in my work, I enjoyed the creative working atmosphere of independent research while being guided by inspiring discussions. In the same way, I would like to thank my co-examiner and co-author Prof. Rainer Leupers for his support and valuable feedback.

As mentioned before, my work is based on the Architects View Framework developed by Tim Kogel. Not only for supervising my master's thesis, but also for the joined research projects, I would like to convey my gratitude to Tim. In addition, I would like to thank my former colleague and office-mate Andreas Wieferink who recruited me to the ISS when I was an undergraduate student. He was always helpful in solving critical debugging issues.

I am grateful to all my colleagues at ISS, who supported me in my research work. Among them I would like give my special thanks to Filippo Borlenghi, Jeronimo Castrillon, Anupam Chattopadhyay, Meik Dörpinghaus, Felix Engel, Lei Gao, Niels Hadaschik, Manuel Hohenauer, David Kammler, Kingshuk Karuri, Stefan Kraemer, Hanno Scharwächter, Stefan Schürmans, Martin Senst, Martin Witte and Diandian Zhang.

When performing research in the area of EDA tools, I personally consider tight interaction with semiconductor and EDA companies as essential to address the key design issues. Luckily, at ISS I had the unique opportunity to meet many helpful professionals over the years, which gave constant guidance and valuable feedback. My special thanks are due to Xavier Buisson, Andreas Hoffmann, Karl Van Rompaey, Bart Vanthournout from CoWare/Synopsys, and to all the professionals we met during the roadshow of the Virtual Processing Unit (VPU).

Converting my ideas into usable tools would have not been possible without the help of my postgraduate students. I would like to thank all of them for their efforts and hard work. Among them, I would like to give special thanks to Jens Reinecke and Stefan Wallentowitz. Furthermore, I would like to thank Filippo Borlenghi, Jeronimo Castrillon, and James Wood for reviewing this book.

I would like to thank my parents for all the constant love and support. I also thank my brother for his support and advice. My very special thanks go to Meike and my daughter Flora for their support, love, and patience.

July 2010

Torsten Kempf

## Contents

| 1 | Intro | oduction                                                 | 1  |  |  |  |

|---|-------|----------------------------------------------------------|----|--|--|--|

|   | 1.1   | Organization of the Book                                 | 4  |  |  |  |

| 2 | Syste | ems for Wireless Communication                           | 7  |  |  |  |

|   | 2.1   | Applications for Mobile Devices                          | 8  |  |  |  |

|   |       | 2.1.1 Wireless Communication Domain                      | 8  |  |  |  |

|   |       | 2.1.2 Multimedia Applications                            | 9  |  |  |  |

|   |       | 2.1.3 General Purpose and Other Applications             | 11 |  |  |  |

|   |       | 2.1.4 Application Impact on Design Methodology           | 12 |  |  |  |

|   | 2.2   | Hardware Platforms and Components                        | 13 |  |  |  |

|   |       | 2.2.1 Processing Elements                                | 16 |  |  |  |

|   |       | 2.2.2 Communication Architectures and Memory Subsystems  | 19 |  |  |  |

|   |       | 2.2.3 Hardware Architecture Impact on Design Methodology | 20 |  |  |  |

|   | 2.3   | Summary                                                  | 21 |  |  |  |

| 3 | Prin  | ciples of Design Space Exploration                       | 23 |  |  |  |

|   | 3.1   | Evaluation of a Single Design Point                      | 24 |  |  |  |

|   |       | 3.1.1 Simulation-Based Approaches                        | 26 |  |  |  |

|   |       | 3.1.2 Analytical Approaches                              | 38 |  |  |  |

|   |       | 3.1.3 Joint Analytical and Simulation-Based Approaches   | 40 |  |  |  |

|   |       | 3.1.4 Summary of Approaches                              | 40 |  |  |  |

|   | 3.2   | Exploring the Design Space                               | 42 |  |  |  |

|   |       | 3.2.1 Summary of Exploration Approaches                  | 45 |  |  |  |

|   | 3.3   | Requirements for Early Design Space Exploration          | 45 |  |  |  |

| 4 | Rela  | nted Work                                                | 49 |  |  |  |

|   | 4.1   | Simulation-Based Approaches                              | 49 |  |  |  |

|   | 4.2   | 2 Analytical Approaches                                  |    |  |  |  |

|   | 4.3   | Joint Analytical and Simulation-Based Approaches         | 53 |  |  |  |

|   | 4.4   | Summary                                                  | 53 |  |  |  |

| 5 | Met                   | hodolog   | y                                             | 55  |

|---|-----------------------|-----------|-----------------------------------------------|-----|

|   | 5.1                   |           | ve Design Process                             |     |

|   | 5.2                   | Analy     | tical Implementation Model                    | 58  |

|   | 5.3                   |           | act Simulation Implementation Model           |     |

|   | 5.4                   |           | ased Implementation Model                     |     |

| 6 | Ana                   | lytical I | mplementation Model                           | 67  |

|   | 6.1                   | Desig     | n Space Exploration as a Mathematical Problem | 67  |

|   |                       | 6.1.1     | Problem Statement and Elementary Definitions  |     |

|   |                       | 6.1.2     | Input Analysis and Evaluation Constraints     |     |

|   | 6.2                   |           | sis Algorithm                                 | 80  |

|   |                       | 6.2.1     | Analysis Graph Calculation                    | 81  |

|   |                       | 6.2.2     | Analysis Precalculation                       |     |

|   |                       | 6.2.3     | Critical Path Evaluation                      | 86  |

|   | 6.3                   | Simula    | ation Link and Back Annotation                | 86  |

| 7 | Abs                   |           | mulation Implementation Model                 |     |

|   | 7.1                   |           | iew and Key Components                        |     |

|   | 7.2                   |           | l Processing Unit Concept                     |     |

|   | 7.3                   | Annot     | ation Principle of Execution Characteristics  |     |

|   |                       | 7.3.1     | Statistical Annotation Model                  |     |

|   |                       | 7.3.2     | Source-Level Annotation Model                 |     |

|   |                       | 7.3.3     | Implementation-Based Annotation Model         | 99  |

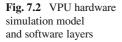

|   | 7.4                   | Softwa    | are Layers of the VPU                         | 103 |

|   |                       | 7.4.1     | Hardware Abstraction Layer                    | 103 |

|   |                       | 7.4.2     | Device Drivers                                | 105 |

|   |                       | 7.4.3     | Operating System Layer                        | 107 |

|   |                       | 7.4.4     | Middleware Layer                              |     |

|   | 7.5 Application Layer |           | 115                                           |     |

|   |                       | 7.5.1     | Textual Design Entry                          | 115 |

|   |                       | 7.5.2     | Graphical Design Entry                        | 119 |

|   | 7.6                   | Refine    | ement to Instruction Set Simulation           | 122 |

|   |                       | 7.6.1     | Hardware Simulation Model Refinement          | 123 |

|   |                       | 7.6.2     | Software Refinement                           | 123 |

|   |                       | 7.6.3     | Automatic Refinement Flow for the Graphical   |     |

|   |                       |           | Design Entry                                  | 126 |

|   | 7.7                   | Summ      | ary of the Abstract Simulation Model          | 129 |

| 8 | Case                  | e Study   |                                               | 131 |

|   | 8.1                   | Task L    | evel Annotation                               | 131 |

|   |                       | 8.1.1     | Task Level Analysis Scenario                  |     |

|   |                       | 8.1.2     | Task Level Analysis Results                   |     |

|   | 8.2                   | System    | n Level Case Study                            |     |

|   |                       | 8.2.1     | Wireless Communication Standards              |     |

|   |                       | 8.2.2     | Overview of Processing Element                | 141 |

|     |             | 8.2.3 Exploration                                      | 142    |

|-----|-------------|--------------------------------------------------------|--------|

|     | 8.3         | Summary of the Case Study                              |        |

| 9   | Sum         | nmary and Outlook                                      | 153    |

| A   | Adv         | vanced Features of the Analysis Framework              | 157    |

|     | A.1         | Analysis Graph Simplification                          | 157    |

|     |             | A.1.1 Task Merging                                     | 157    |

|     |             | A.1.2 Shortcut Elimination                             |        |

|     |             | A.1.3 Iterative Application                            | 158    |

|     | A.2         |                                                        |        |

|     |             | A.2.1 Scheduling Definition Within the Analysis Framew | ork160 |

|     | A.3         | · ·                                                    |        |

|     | A.4         | Practical Calculation and Stochastic Independence      | 161    |

| В   | Adv         | vanced VPU Features                                    | 163    |

|     | <b>B</b> .1 | Advanced Device Drivers                                | 163    |

| С   | Task        | k Modeling and Virtual Processing Unit                 | 165    |

|     | C.1         | Overview                                               | 165    |

|     | C.2         | Task Graph Assembly and Analysis                       | 167    |

|     | C.3         | VPU IP Component and Platform Modeling                 | 169    |

|     | C.4         |                                                        |        |

| Re  | feren       | ices                                                   | 173    |

| Ine | lex         |                                                        | 187    |

# **List of Figures**

| Fig. 1.1 | Wireless communication subscriptions (Source: Informa              |    |

|----------|--------------------------------------------------------------------|----|

|          | Telecoms & Media [1]). (a) Global Subscription Growth              |    |

|          | and Netadds. (b) Regional Subscription Growth                      | 2  |

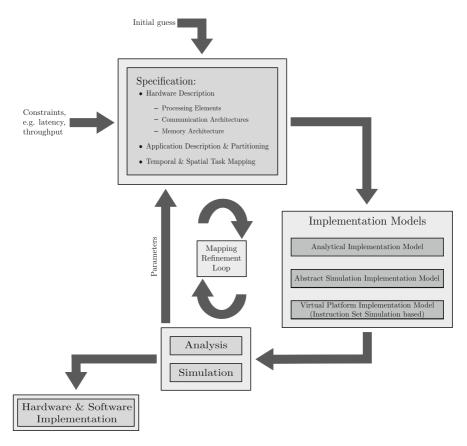

| Fig. 1.2 | Early design space exploration methodology                         | 3  |

| Fig. 2.1 | Wireless communication networks                                    | 8  |

| Fig. 2.2 | Wireless communication task graph example: WLAN                    |    |

|          | 802.11a receiver [17, 18]                                          | 10 |

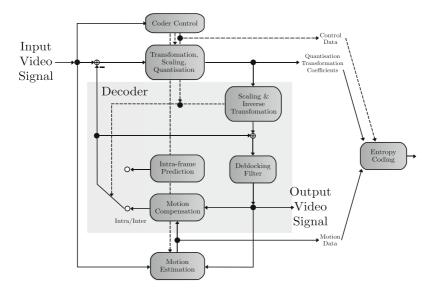

| Fig. 2.3 | Multimedia example H.264 task graph [23]                           | 11 |

| Fig. 2.4 | IP block structure of the TI OMAP44x platform [38]                 |    |

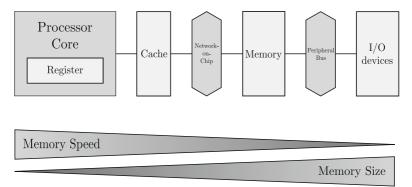

| Fig. 2.5 | Memory architectures of common processor cores [24]                | 20 |

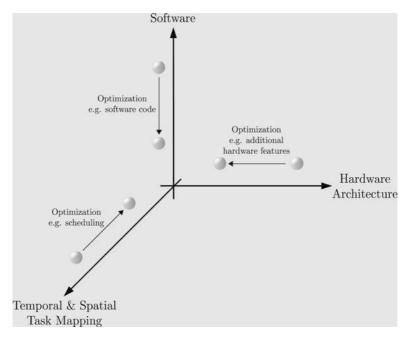

| Fig. 3.1 | Design space: software, hardware architecture, and task mapping    | 24 |

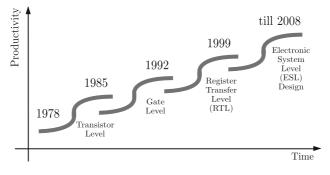

| Fig. 3.2 | S-Curves: abstraction levels of hardware design [75]               | 25 |

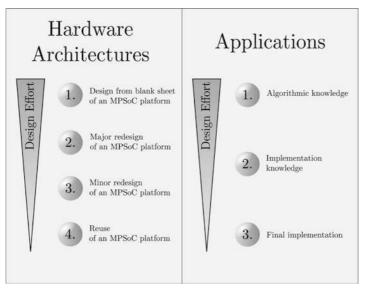

| Fig. 3.3 | Design entries: hardware architectures and applications            | 26 |

| Fig. 3.4 | Dimensions of the TLM-2 standard (based                            |    |

| C        | on [39, 100, 149])                                                 | 33 |

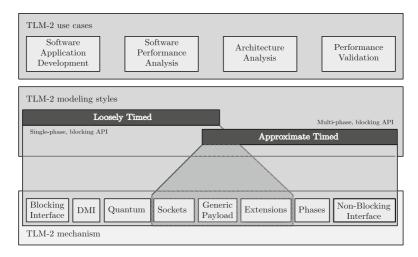

| Fig. 3.5 | Use cases, modeling styles and mechanisms [153]                    |    |

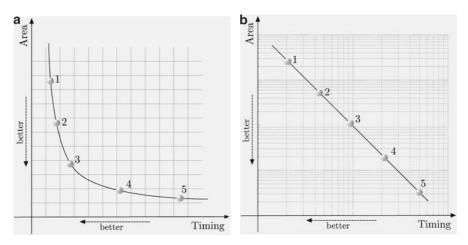

| Fig. 3.6 | Example for Pareto optimization: solutions for                     |    |

| C        | a minimal area-timing-product. (a) Linear scale.                   |    |

|          | ( <b>b</b> ) Double-logarithmic scale                              | 43 |

| Fig. 5.1 | Iterative design process with analysis/simulation-based evaluation | 57 |

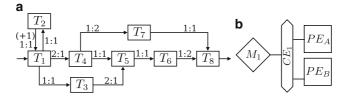

| Fig. 5.2 | Exemplary analysis components. (a) Task graph and                  |    |

| -        | critical paths. (b) Hardware architecture. (c) Temporal            |    |

|          | & spatial task mapping. (d) Task characteristic examples           |    |

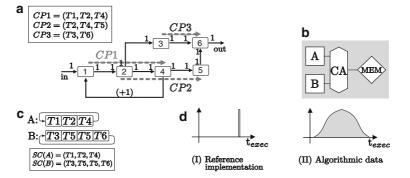

|          | <i>X</i> ( <i>Task</i> , <i>PE</i> )                               | 59 |

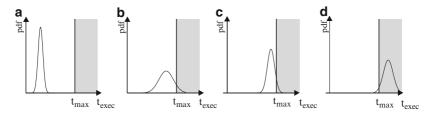

| Fig. 5.3 | Exemplary analysis results for latency constraints.                |    |

| U        | (a) Likely feasible. (b) Uncertainty dominated.                    |    |

|          | (c) Expected value dominated. (d) Unlikely feasible                | 60 |

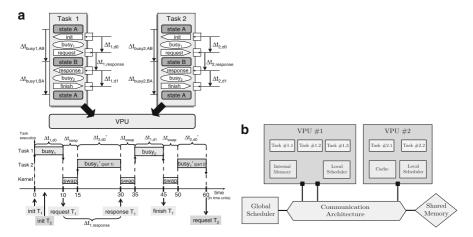

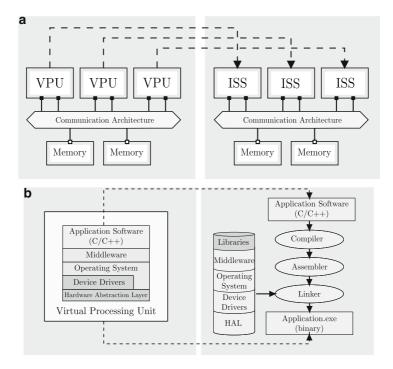

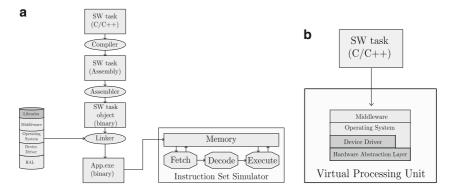

| Fig. 5.4 | Principle and usecase of the Virtual Processing Unit               |    |

| C        | (VPU). (a) VPU Performance Model. (b) System-level                 |    |

|          | design including VPUs                                              | 61 |

|          |                                                                    |    |

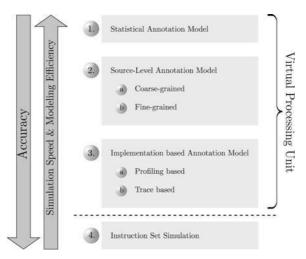

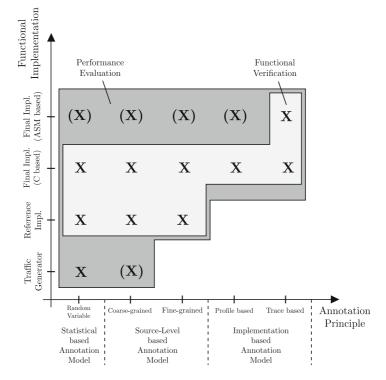

| Fig. 5.5  | Supported annotation models of the VPU                             |  |

|-----------|--------------------------------------------------------------------|--|

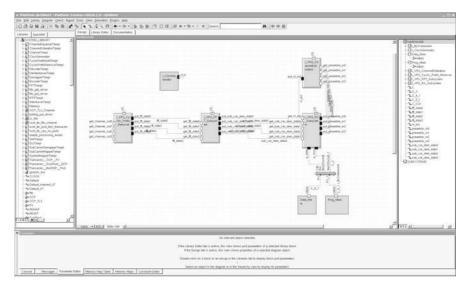

| Fig. 5.6  | Graphical design entry 64                                          |  |

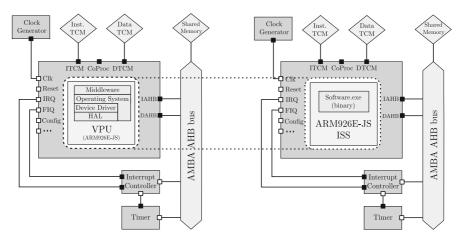

| Fig. 5.7  | (a) VPU to ISS refinement: hardware part. (b) VPU to               |  |

|           | ISS refinement: software part                                      |  |

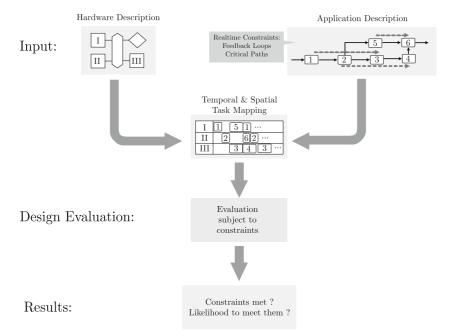

| Fig. 6.1  | Problem statement of design space exploration                      |  |

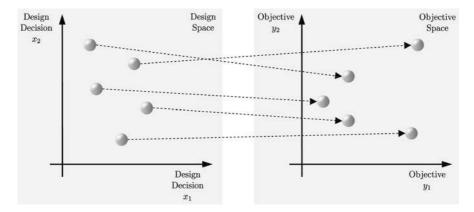

| Fig. 6.2  | Multiobjective optimization problem: decision                      |  |

|           | and objective space                                                |  |

| Fig. 6.3  | Examples of valid and invalid application task graphs              |  |

| •         | (TG). (a) Illegal task graph. (b) Inconsistent data rates.         |  |

|           | (c) Valid task graph                                               |  |

| Fig. 6.4  | From single to multiapplication scenario. (a) Two                  |  |

| U         | applications and task graphs. (b) Joint representation of          |  |

|           | two applications                                                   |  |

| Fig. 6.5  | Transformation of the general application task graph               |  |

| 8         | to a acyclic directed DFG. ( <b>a</b> ) Initial task graph (TG).   |  |

|           | (b) Respective Feedback Data Flow Graph (FDFG).                    |  |

|           | (c) Respective Data Flow Graph (DFG)                               |  |

| Fig. 6.6  | Examples of valid and invalid spatial mappings.                    |  |

| 1 ig. 0.0 | (a) Invalid Spatial Mapping. (b) Valid Spatial Mapping             |  |

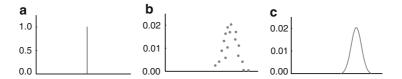

| Fig. 6.7  | Different types of stochastic parameter description                |  |

| 1 15. 0.7 | illustrated by their probability density functions.                |  |

|           | (a) Perfect Knowledge. (b) Simulation Results.                     |  |

|           | (c) Stochastic Description                                         |  |

| Fig. 6.8  | Example: application and hardware architecture.                    |  |

| 1 15. 0.0 | (a) Initial task graph (TG). (b) HW architecture                   |  |

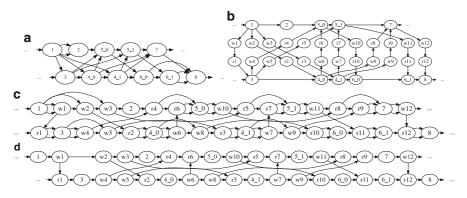

| Fig. 6.9  | Evaluation of the analysis graph. (a) The joint DFG                |  |

| 1 15. 0.7 | and CFG. ( <b>b</b> ) Adding read and write communication          |  |

|           | vertices and edge reduction. (c) Insert communication              |  |

|           | into schedules. (d) Edge reduction                                 |  |

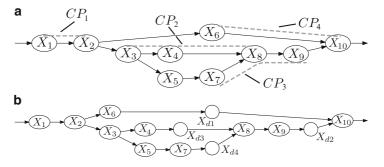

| Fig. 6.10 | Example: analysis graph with exemplary critical paths              |  |

| 115. 0.10 | and dependency delays. (a) Critical paths in an analysis           |  |

|           | graph. (b) Inserted dependency delays                              |  |

| Fig 611   | Mathematical to ISS refinement of the implementation model         |  |

| 115.0.11  | Wallemater to 155 remember of the implementation model             |  |

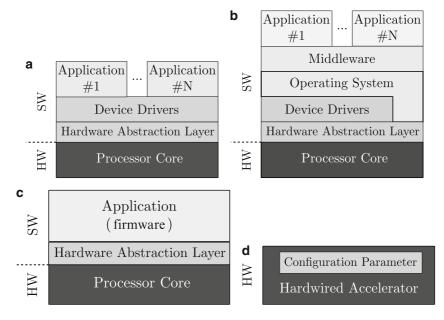

| Fig. 7.1  | Challenges for software and hardware modeling.                     |  |

|           | (a) Processor core with single-threaded application.               |  |

|           | (b) Processor core with multi-threaded application.                |  |

|           | (c) Programmable hardware accelerator. (d) Hardware accelerator 91 |  |

| Fig. 7.2  | VPU hardware simulation model and software layers                  |  |

| Fig. 7.3  | Techniques of functional implementation and execution              |  |

|           | characteristic annotation                                          |  |

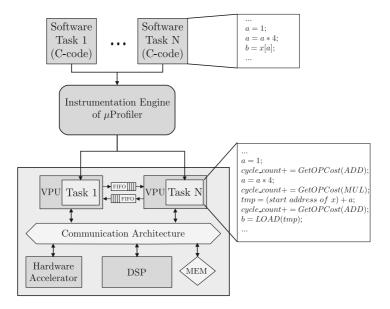

| Fig. 7.4  | Annotation of the execution characteristic: statistical model      |  |

| Fig. 7.5  | Task execution work flow    99                                     |  |

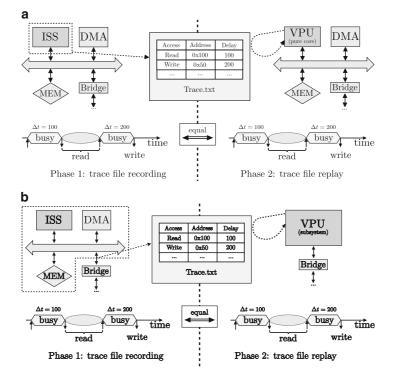

| Fig. 7.6  | Annotation of the execution characteristic: trace-based                  |     |

|-----------|--------------------------------------------------------------------------|-----|

|           | annotation. (a) Trace-based annotation for processor                     |     |

|           | core. (b) Trace-base annotation for subsystem                            | 102 |

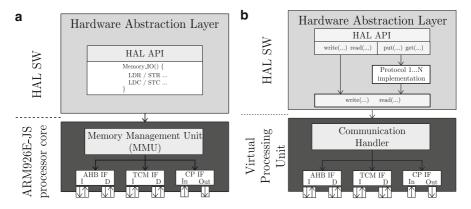

| Fig. 7.7  | Comparison between hardware abstraction layer                            |     |

|           | for ISS- and VPU-based simulation. (a) Hardware                          |     |

|           | Abstraction Layer for ARM926E-JS. (b) Hardware                           |     |

|           | Abstraction Layer on VPU                                                 | 104 |

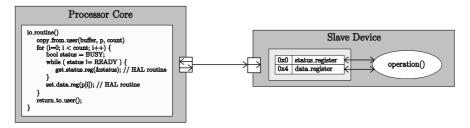

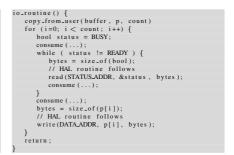

| Fig. 7.8  | Hardware device and device driver [273, p. 285] with                     |     |

| -         | pure slave behavior                                                      | 106 |

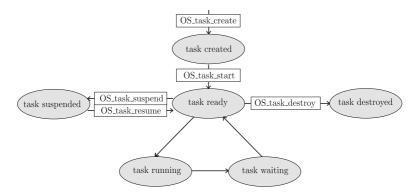

| Fig. 7.9  | Advanced task state control in the generic operating system              | 110 |

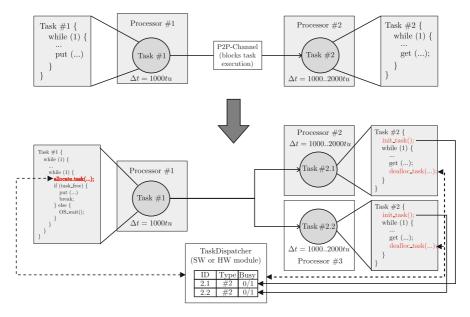

| Fig. 7.10 |                                                                          |     |

| Fig. 7.11 | Example of a middleware on top of the VPU                                |     |

| Fig. 7.12 | Comparison of modeling of software and hardware on                       |     |

| •         | ISS and VPU. (a) Modeling and usage of software on                       |     |

|           | an ISS. (b) Modeling and usage of software on a VPU                      | 117 |

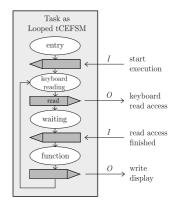

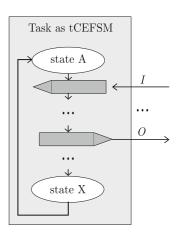

| Fig. 7.13 | Exemplary task model illustrated as tCEFSM                               | 118 |

| Fig. 7.14 | Principle of the graphical design entry                                  | 119 |

| Fig. 7.15 | Looped tCEFSM                                                            |     |

| Fig. 7.16 | Refinement example – from VPU to ISS                                     | 124 |

| Fig. 7.17 | Operating system specific refinement example                             | 126 |

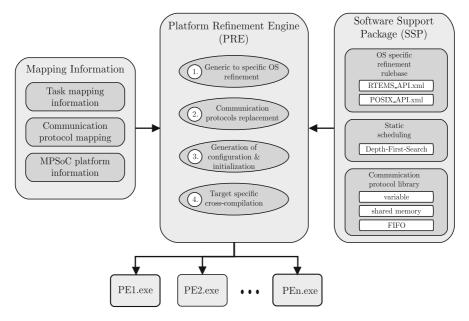

| Fig. 7.18 | Platform refinement engine (PRE)                                         | 127 |

| Fig. 8.1  | Evaluation principle of annotation techniques                            |     |

| U         | (ARM926EJ-S example)                                                     | 134 |

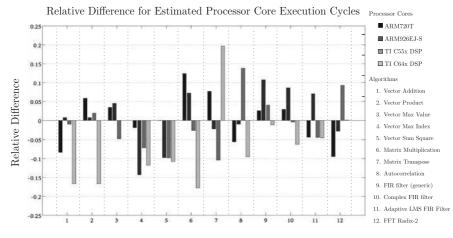

| Fig. 8.2  | Estimation error of execution core cycles                                |     |

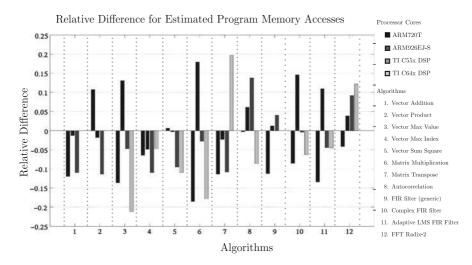

| Fig. 8.3  | Estimation error and accuracy of program memory accesses                 |     |

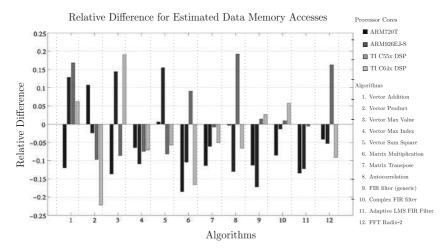

| Fig. 8.4  | Estimation error and accuracy of data memory accesses                    |     |

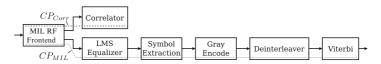

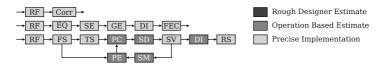

| Fig. 8.5  | The MIL-STD-188-110B algorithm                                           |     |

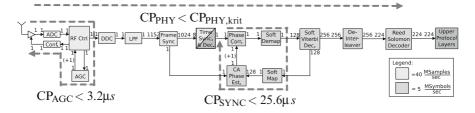

| Fig. 8.6  | Representative communication algorithm                                   |     |

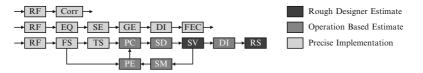

| Fig. 8.7  | Scenario at the initial design entry                                     |     |

| Fig. 8.8  | The explored design options of the hardware                              |     |

| U         | architecture during the case study                                       | 144 |

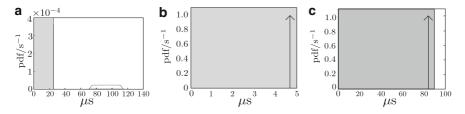

| Fig. 8.9  | Results for the initial setup [valid range – gray] (step 1).             |     |

| e         | (a) RCA sample processing time. (b) MIL correlation                      |     |

|           | mode sample processing time. (c) MIL normal mode                         |     |

|           | sample processing time                                                   | 144 |

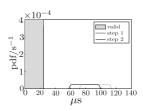

| Fig. 8.10 |                                                                          |     |

| U         | [valid range – gray] (step 2)                                            | 145 |

| Fig. 8.11 |                                                                          |     |

| C         | DSP (step 3)                                                             | 145 |

| Fig. 8.12 |                                                                          |     |

| -         | range – $gray$ ] (step 3). (a) RCA sample processing time.               |     |

|           | ( <b>b</b> ) RCA latency (not critical). ( <b>c</b> ) RCA feedback delay | 146 |

|           | $(\mathbf{U})$ KCA Interversion (IIOU CITICAL). (C) KCA IEEUUACK UEIAY   |     |

| Fig. 8.13 | Results for the architecture refinement: TI C55x DSP to C64x DSP [valid range $- gray$ ] (step 4). (a) RCA |

|-----------|------------------------------------------------------------------------------------------------------------|

|           | sample processing time. (b) RCA latency (not critical).                                                    |

|           | (c) RCA feedback delay146                                                                                  |

| Fig. 8.14 | RCA results for interleaved schedule and increased                                                         |

|           | clock frequency [valid range $- gray$ ] (step 5). (a) Sample                                               |

|           | processing time. (b) Agg. sample processing time147                                                        |

| Fig. 8.15 | Simulation results for the aggregated RCA sample                                                           |

|           | processing time [valid range $- gray$ ] (step 6). (a) Sample                                               |

|           | processing time. (b) Agg. sample processing time148                                                        |

| Fig. 8.16 | Results for system including VCP connected to a bus                                                        |

|           | architecture [valid range – gray] (step 7). (a) RCA                                                        |

|           | sample processing time per sample. (b) RCA aggregated                                                      |

|           | sample processing time. (c) MIL sample processing time149                                                  |

| Fig. 8.17 | Results for the tightly coupled VCP [valid range –                                                         |

|           | gray] (step 8.1). (a) RCA sample processing time per                                                       |

|           | sample. (b) RCA aggregated sample processing time.                                                         |

|           | (c) MIL sample processing time150                                                                          |

| Fig. 8.18 | Results for the bus connected VCP with unoptimized                                                         |

|           | scheduling [valid range – gray] (step 8.2). (a) RCA                                                        |

|           | sample processing time per sample. (b) RCA aggregated                                                      |

|           | sample processing time. (c) MIL sample processing time                                                     |

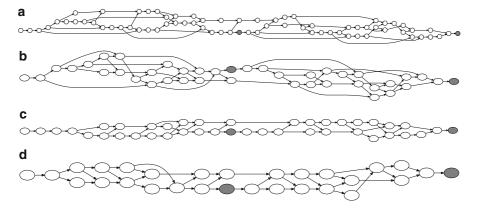

| Fig. A.1  | Exemplified analysis graph simplifications. (a) Original                                                   |

| 0         | Analysis Graph as constructed from DFG and CFG.                                                            |

|           | ( <b>b</b> ) Merging of nodes reduces the number of vertices.                                              |

|           | (c) Removal of redundant edges. (d) Further merging of                                                     |

|           | nodes reduces the number of vertices                                                                       |

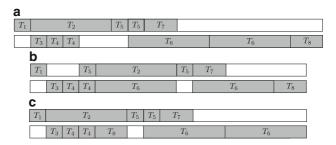

| Fig. A.2  | Exemplary schedules. The upper chart pictures $SC(PE_A)$                                                   |

|           | and the lower one $SC(PE_B)$ . (a) Initial schedule based                                                  |

|           | on the topological task sequence of the initial task                                                       |

|           | graph. (b) Schedule modification based on task $T_5$                                                       |

|           | instances. (c) Task scheduling with interleaved iterations                                                 |

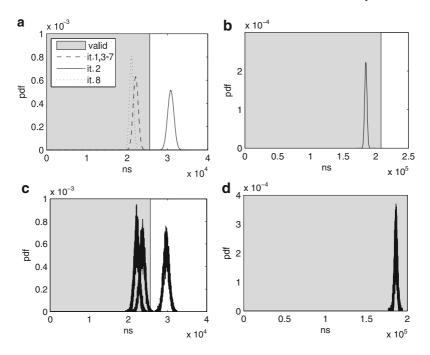

| Fig. A.3  | Stochastic analysis vs. Monte-Carlo                                                                        |

| 1.18.1.10 | results ( $N = 100,000$ ). (a) Stochastic Analysis:                                                        |

|           | RCA sample processing time per sample. (b) Stochastic                                                      |

|           | Analysis: RCA aggregated sample processing time.                                                           |

|           | (c) Monte-Carlo: RCA sample processing time per                                                            |

|           | sample. (d) Monte-Carlo: RCA aggregated sample                                                             |

|           | processing time                                                                                            |

| Fig. B.1  | Example of interrupt-driven memory mapped I/O device                                                       |

| 0         | driver on VPU                                                                                              |

| Fig. B.2  | Example of DMA based I/O device driver                                                                     |

|           |                                                                                                            |

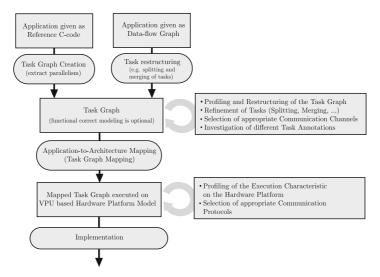

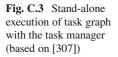

| Fig. C.1 | Overview of the design flow (based on [307])             | 166 |

|----------|----------------------------------------------------------|-----|

| Fig. C.2 | Exemplary task graph in synopsys PCT                     | 167 |

| Fig. C.3 | Stand-alone execution of task graph with the task        |     |

|          | manager (based on [307])                                 | 168 |

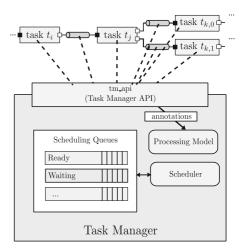

| Fig. C.4 | Task execution trace                                     | 168 |

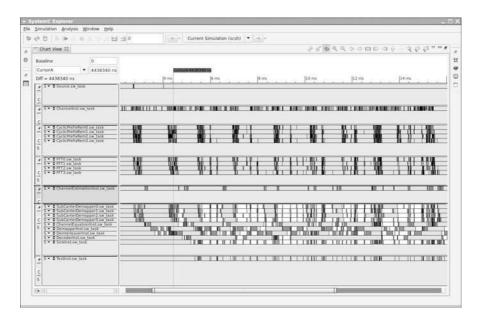

| Fig. C.5 | VPU IP component and task graph mapping (based on [307]) | 169 |

| Fig. C.6 | Hardware platform                                        | 170 |

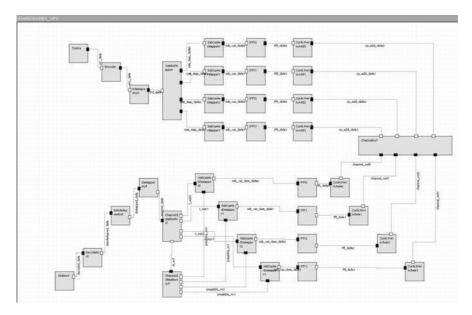

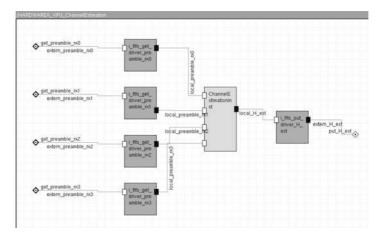

| Fig. C.7 | Mapped task graph (channel estimation subsystem)         | 171 |

|          |                                                          |     |

# **List of Tables**

| Table 2.1 | Computational and communication requirements<br>of multimedia applications [21] 10 |

|-----------|------------------------------------------------------------------------------------|

| Table 7.1 | Protocols of the VPU's hardware abstraction layer105                               |

| Table 7.2 | Basic functions of the generic operating system to                                 |

|           | support task management                                                            |

| Table 7.3 | Specific OS API refinement of important OS functions111                            |

| Table 7.4 | Replacement or implementation of explicit memory                                   |

|           | access functions                                                                   |

| Table 7.5 | Specific OS API refinement of important OS functions125                            |

| Table 8.1 | Considered task level analysis scenario implementation options 133                 |

| Table 8.2 | Compatibility matrix for annotation techniques                                     |

|           | of the execution characteristic                                                    |

|           |                                                                                    |

## Chapter 1 Introduction

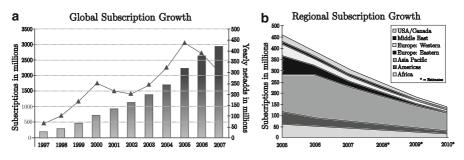

Over the past 20 years, advances in digital wireless communication technologies have modified everyone's day-to-day life. Predominantly utilized by business customers, the switch from analog to digital wireless communication networks has made them affordable and widely accepted within the consumer market. This trend is clearly reflected by the increase in the number of global cellular subscriptions over the last decade. Figure 1.1 illustrates the impressive growth from ~200 million to over 3,000 million subscriptions listed between the years 1997 and 2008 [1].

Parallel to the achievements in wireless communication, user devices have evolved at an incredible pace over the last years. The technology advances in the semiconductor industry have led to supercomputers in the form factor of a mobile terminal. Accordingly, latest-generation smartphones are no longer limited solely to pure voice communication, but support a wide range of applications from the domains of multimedia, entertainment, and infotainment. In turn, these applications have had a particularly strong impact on connectivity requirements, resulting in the need for the latest smartphones to support multiple wireless communication standards.

These requirements have created one of the most challenging assignments in engineering today. Looking purely at the necessary computational performance shows an approximate demand of 10–80 GOPS peak performance [2] for the execution of today's communication standards. In addition, upcoming standards will further increase the demands, e.g., the upcoming Long Term Evolution (LTE) standard extension. The demand to support the mobility of battery powered devices, makes high energy efficiency one of the key elements for business success within the anticipated market. This demand together with the requirements of low cost, short time-to-market, and the extremely short lifecycles put particular pressure on system architects when designing such terminals.

Today we are witnessing a complete change in the design philosophy of wireless communication devices. In the past, the main answer to the increasing requirements came from the semiconductor technology scaling the manufacturing process, leading to higher performance and energy efficiency gains. These gains were predicted by Moore's Law [3] and Dennard's Scaling Rules [4]. Unfortunately, having reached process manufacturing sizes below 65 nm, further downscaling is becoming more and more challenging, and pessimistic voices predict the end of Moore's Law.

Fig. 1.1 Wireless communication subscriptions (Source: Informa Telecoms & Media [1]). (a) Global Subscription Growth and Netadds. (b) Regional Subscription Growth

Whether true or not, a more severe design issue has arisen, commonly referred to as the *crisis of complexity* [5]. It is the limitation to fully exploit the advantages provided by process technology due to the lack of efficient design methodologies and tools.

More than ever before, system architects are being required to apply new and innovative designs to increase computational performance and to keep pace with consumer expectations. In a nutshell, the strong computational requirements are forcing system architects to incorporate parallel processing as it offers the capability of sharing the computation among the different resources. Besides this, the contradictory requirements of performance, energy efficiency, and flexibility can only be resolved by programmable processor cores. Starting from the well-known concepts of general purpose computing (GPPs) and digital signal processing (DSPs), the urgent demand for high energy efficiency has led to extensive research on processor cores. One result of this research are application-specific instruction-set processors (ASIPs), which are optimized for a specific application. Furthermore, reconfigurable ASIPs (rASIPs), including postfabrication reconfigurability, have been envisioned and first prototypes are available.

With processor cores being the heart of every wireless communication platform, heterogeneous Multi-Processor Systems-on-Chip (MPSoC) are widely considered to be the optimal choice for implementation. Experiments have shown that, when designed carefully, MPSoCs have the potential to achieve the best trade-off among computational performance, energy efficiency, and flexibility. Unfortunately, system architects are experiencing new and still unsolved challenges during design of such systems. These challenges cover engineering issues ranging from macro- to micro-scopic aspects in hardware and software development. In addition, earlier design strategies focussing on single components need to be reconsidered, because nowa-days only a joint analysis enables statements about the platform capabilities. These issues and challenges have created the research field of ESL design.

Evolving from the fundamental ideas of HW/SW codesign and later system level design, ESL design covers a large set of methodologies and tools surrounding MPSoC design in general. The centerpiece of nearly all ESL design techniques is a virtual platform that serves as an executable specification to evaluate particular design objectives. Virtual platform techniques have achieved a major break-through in the fields of software development and debugging, as well as platform analysis, optimization, and verification. These virtual platforms replace costly hardware prototypes and have the potential to significantly simplify and speed-up the design process. However, virtual platforms operating on instruction-set level can hardly be used directly at the start of the design cycle, when typically neither the hardware architecture nor the compiler tool chain and/or the software implementation are fixed. Therefore, innovative design methodologies to carry out early design space exploration are essential, as last minute design changes tend to be extremely costly and induce high risks of wasting development effort. Accordingly, these methodologies have to support system architects in identifying the optimal or suboptimal design options right from the outset. Moreover, for wide acceptance and practical use, a clear link to existing technologies is mandatory.

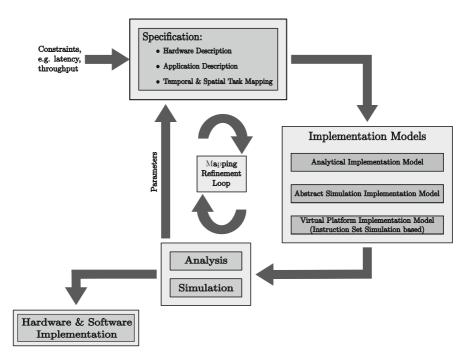

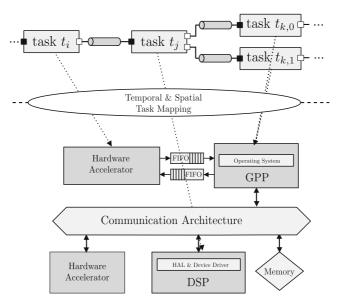

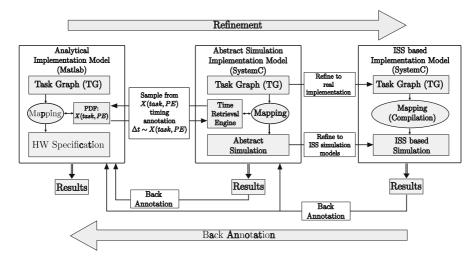

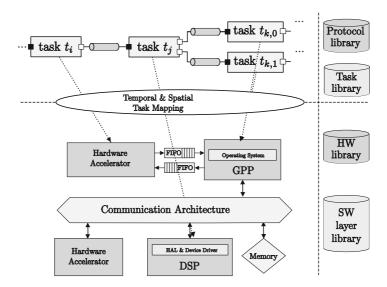

To address the design issues of future multi- and many-processor core architectures, with particular attention to platforms in the domain of wireless communication, this book outlines a unique early design space exploration framework. Its major contribution is a joint environment that covers several abstraction layers for the purpose of the exploration and evaluation of heterogeneous MPSoC platforms. The framework introduces the following main concepts and techniques and its overall structure is comprehensively described in Fig. 1.2.

Fig. 1.2 Early design space exploration methodology

- An *analytical implementation model* is built on the fundamentals of statistical processes and graph theory. This model targets early design stages, when the hardware architecture is undefined or only a few components are available. The key idea is to formally describe the anticipated hardware platform, the application specification and the temporal and spatial task mapping at a high abstraction level. Based on this solid foundation, a mathematical analysis allows the computation of the performance characteristics and helps to identify whether the system complies with the necessary constraints and also to highlight potential design difficulties.

- The second major implementation model is based on an *abstract simulation model*. The key principle is an annotation of the execution characteristics supporting the evaluation of arbitrary aspects without a detailed and time-consuming implementation. This paradigm has culminated in the Virtual Processing Unit (VPU) and several extensions for practical use and the investigation of common hardware features.

- Acceptance and usability not only require sophisticated implementation models but also an *effective design process* with the possibility of a smooth transition between the abstraction layers. In strict adherence to this paradigm, the proposed framework provides techniques to (semi-)automatically close the design gaps between the abstraction levels.

#### **1.1 Organization of the Book**

Various research activities dedicated to the field of multi- and many-core architectures have generated a considerable number of methodologies and techniques. For this reason, this book gives a rather detailed introduction into the overall ESL domain. Chapter 2 discusses the general application and architectural trends and also their implications on the design methodology. This includes applications from the domains of wireless communication, multimedia, and other general purpose ones. From the architectural perspective, utilized IP components are separately introduced based on their type, such as processing elements, communication architectures, and memories.

After this fundamental introduction, Chap. 3 identifies and highlights the foundation of any design space exploration. Central aspects that are discussed are the evaluation of a single design point and the strategy to navigate the design space. The chapter concludes with the identification of the requirements for an efficient design process and framework.

As the proposed framework is definitely not a single entity within the complex research space, Chap. 4 depicts the related work which can be found in academia and industry. The chapter is divided into two aspects, namely Electronic System Level (ESL) design and early design space exploration, covering both analytical and simulation-based approaches.

#### 1.1 Organization of the Book

The subsequent chapters introduce the proposed methodology and framework for early design space exploration. Chapter 5 highlights the overall principle and structure of the methodology which follows the paradigm of abstraction. The analytical implementation model is situated at the highest abstraction level, whereas the abstract simulation model bridges the design discontinuity to the well-known ESL design at the level of instruction set simulation. As a consequence, a continuous design process from a high- to low-level of abstraction is inherently ensured.

Chapter 6 discusses the analytical implementation model. Within the discussion, the problem of design space exploration and analysis is defined as a mathematical problem. Finally, the chapter concludes with the link to the abstract simulation-based environment.

The abstract simulation model is discussed from a practical point of view in Chap. 7, which highlights its practical usage and introduces the underlying concept, as well as the provided features. Subsequently, the refinement from the abstract to the instruction set simulation model is presented.

In Chap. 8 the usefulness and accuracy of the proposed framework and underlying concept are proved by a case study from the domain of wireless communication. This case study covers two main aspects. The first part captures the accuracy that can be achieved for various design decisions and the different modeling techniques, whereas the second part highlights the practical use based on a complex, yet typical design process.

Finally, the book concludes with a summary and an outlook on further research in the field of design space exploration.

### Chapter 2 Systems for Wireless Communication

The advent of second generation (2G), digital mobile communication networks for the mass markets had a significant impact on the use of mobile communication in the 1990s. Previously, the usage of mobile communication had been limited to business customers because of the high costs, whereas second (2G) and following (3G, LTE) wireless communication generations have been affordable for the masses. With the change of customers, the usage of mobile communication has broadened from pure mobile voice communication to infotainment and entertainment. This requires mobile handsets to support, in addition to the key components of voice and data communication, applications, like multimedia ones. The different structure and demands of these applications require different kinds of wireless communication protocols and standards which, in turn, has led to the incorporation of a hardware subsystem for each standard. This solution promises short-term success, however in the long term this principle is not expected to scale with a large number of supported communication standards. Finally, this has led to the vision of a Software Defined Radio (SDR) [6] which implements these standards in software to allow an easy upgrade and extension of the set of supported standards. It is commonly agreed that heterogeneous Multiprocessor System-on-Chip (MPSoCs) [7] are the best choice for the underlying platform to cope with the challenging demands of computational performance, energy efficiency, and flexibility, especially for wireless communication devices like SDRs.

This chapter first examines the applications executed on cellphones and smartphones separately for the three domains of wireless communication, multimedia, and general purpose. Based on them, the impact and constraints for the design methodology for wireless communication platforms are derived. The second part of the chapter discusses the underlying hardware platforms and components. Additionally, the specific influence of the platform and components on the design process is highlighted.

#### 2.1 Applications for Mobile Devices

Applications for mobile devices differ significantly in their characteristics according to their domain. Therefore, they are discussed separately. Applications for wireless communications, with particular focus on physical-layer processing, are treated in greatest detail as the case study discussed in Chap. 8 addresses this domain.

#### 2.1.1 Wireless Communication Domain

Within this area, targeted applications comprise all kinds of standards and protocols for voice and data communication. To achieve highest interoperability these are typically standardized by organizations like ITU [8], ETSI [9], and IEEE [10]. In addition, the application structure is defined according to the International Standard Organization Open Systems Interconnection Basic Reference Model (ISO/OSI Reference Model) [11] to simplify the design of wireless communication standards. However, modern standard implementations are not too strict about dividing the different layers, so that applied cross-layer optimizations soften the borders between adjacent layers.

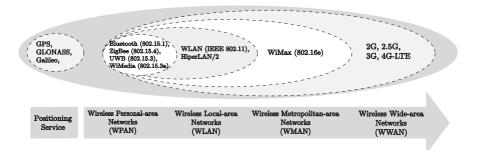

A large variety of wireless communication standards have emerged, each addressing a particular range of user-level applications. The traditional classification of standards differentiates among Wireless Personal Area Networks, Wireless Local Area Networks (WLAN), Wireless Metropolitan Area Networks (WMAN), and Wireless Wide Area Networks. Figure 2.1 illustrates these four classes including examples and use-cases. Additionally, localization services like the Global Positioning System (GPS) are considered as a part of wireless communication systems.

The multimedia and wireless communication domains are converging initiated by technology advances, e.g., high performance mobile processor cores, as well as high-resolution displays and touchscreens for mobile devices. The result of this convergence is a class of *smartphones* that combine the functionalities of

Fig. 2.1 Wireless communication networks

mobile phones and personal computers (PC) into a single mobile device. These devices support a wide range of different applications, each having individual connectivity demands. This requires the support of different wireless communication standards, e.g., Bluetooth [12] for wireless headsets, WLAN [13] for internet access, and 2G and 3G network connection for voice and data communication. Past and present designs cope with this challenge by incorporating one subsystem for each supported standard. For example, Apple's 3G iPhone [14] includes five subsystems for GSM/GPRS/EDGE (2G), WCDMA/HSDPA (3G), GPS, WLAN, and Bluetooth [15]. The addition of further subsystems to support additional wireless communication standards is not expected to scale in future. To cope with this issue, industry and research have opted for SDR [6], where different wireless communication standards are implemented in software allowing the reuse of hardware components. A case study [16] carried out by Infineon expects an SDR to outperform the traditional solution in terms of area and costs at five implemented standards. However, implementing even a single wireless communication standard is already a complex task, therefore the design of a complete SDR becomes quite challenging.

The development of wireless communication standards is dominated by the physical-layer processing, i.e., the lowest layer in the ISO/OSI reference model. This layer has a high computational demand (10–80 GOPS) and (mostly) hard real-time constraints have to be fulfilled. From the application perspective, the most severe constraints are *latency* and *throughput*. Failing to comply with these constraints will most likely lead to business failure.

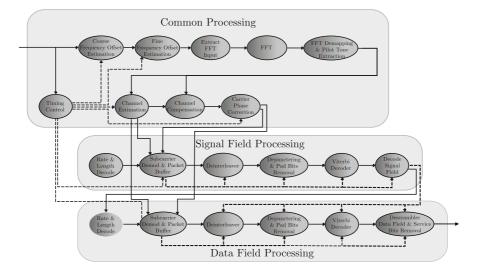

The key elements of physical-layer processing are digital signal processing algorithms. These algorithms are typically characterized by a computationally intensive data-plane processing at high data rates predominantly controlled through parametrization. These data flow dominated applications are rather well structured in terms of *task graphs* or block processing, allowing the utilization of static schedulers and making task-level parallelism rather clear. The known task structure and data communication between different tasks can be easily captured in task graphs, e.g., Kahn Process Networks (KPN) [19] or Synchronous Data Flow (SDF) [20] task graphs. For specific task graphs, especially for the latter mentioned SDFs, a static schedule can be derived prior to run-time. Thus, deterministic behavior is ensured and no dynamic overhead occurs. Figure 2.2 exemplifies a task graph structure of a WLAN 802.11a receiver [17] implementation.

#### 2.1.2 Multimedia Applications

The domain of multimedia covers a wide range of applications like audio, image, and video processing along with 2D and 3D graphic applications. Similar to the wireless communication domain, many standards coexist in the field, each having a particular optimization criterion like data compression or high quality.

Fig. 2.2 Wireless communication task graph example: WLAN 802.11a receiver [17, 18]

| Typical configur     | ation             | On-chip communication requirements |                            | Computational<br>requirements in |

|----------------------|-------------------|------------------------------------|----------------------------|----------------------------------|

| Resolution           | Frequency<br>(Hz) | Pixels per second<br>(Mpxl/s)      | Bytes per second<br>(MBps) | operations per<br>second (GOPS)  |

| $720 \times 480$     | 60                | 20.7                               | 82.8                       | 31.1                             |

| $1,280 \times 768$   | 60                | 59.0                               | 236.0                      | 123.9                            |

| $1,920 \times 1,080$ | 30                | 62.2                               | 248.8                      | 186.6                            |

| $1,920 \times 1,080$ | 60                | 124.4                              | 497.6                      | 373.2                            |

| $1,920 \times 1,200$ | 60                | 138.2                              | 552.8                      | 414.7                            |

Table 2.1 Computational and communication requirements of multimedia applications [21]

Multimedia applications are characterized by a *high computational* demand along with *high communication* requirements between processor and memory. The key application in this domain is video processing with requirements including stringent real-time constraints as exemplified in Table 2.1. This especially applies to high-quality video applications, which include high throughput demands with challenging latency requirements.

These challenging demands of the latest multimedia standards along with the need for energy efficiency, in particular for battery-powered mobile devices, has led to highly specialized hardware accelerators and graphic-processing units [22]. These hardware components are optimized for performing typical 2D and 3D graphic processing operations, e.g., texture mapping and rendering especially vertex, geometry, and pixel shader calculations. The key characteristic of these algorithms is the *massive parallelism* of vector and matrix operations. Similar to ASIPs, these hardware architectures are especially tailored for the needs of multimedia applications. The design principle is to restrict flexibility to a minimum to achieve highest

Fig. 2.3 Multimedia example H.264 task graph [23]

performance and energy efficiency. Despite the immense performance provided by such architectures, software development for them is extremely challenging. In addition, identifying the inherent parallelism within a particular algorithm is key and is mostly carried out by application experts and manual interaction.

Multimedia standards are mostly defined as task graphs (Fig. 2.3) like applications from the domain of wireless communication. The included control flow, e.g., the control overhead in H.264 decoding, leads to severe challenges in memory optimizations and data communication. Therefore, implementations commonly require special treatments to optimize the data communication.

#### 2.1.3 General Purpose and Other Applications

Various kinds of applications are categorized under the term of general-purpose applications. Typical examples are text processing and web-browsing applications. Traditionally developed for personal computers (PCs), these are becoming increasingly popular even on mobile devices like smartphones. These applications are software-centric and make heavy use of operating systems (OSs), middleware layers, and other forms of hardware abstraction layers (HAL) such as hardware dependent software (HdS). Contrary to performance-critical parts, like physical-layer processing in the domain of wireless communication, they have a less dominant data plane processing and their computational complexity is rather low. On the other hand, control plane processing is much more severe because applications have to react on *nondeterministic* user interactions.

This leads to a complex control flow execution, which requires techniques for efficient execution, such as efficient implementations of jump and branch instructions as well as function and procedure handling. To accelerate them, well-known personal computer techniques, such as like branch prediction and superscalar architectures [24], are being increasingly adopted. This architecture trend is constantly narrowing the gap between general purpose processors within the embedded system and the personal computer market. Naturally, this opens new market opportunities for IP vendors from the embedded domain like ARM, MIPS, and Tensilica while moving into the direction of GPC. However, companies originating from the domain of personal computing, e.g., Intel, AMD, and VIA, have announced or are already are moving toward embedded systems [25].

In contrast to the previously discussed application domains, several description and development techniques for general purpose applications exist. However, the most common method is the classical textual design based on a high-level programming language based on C/C++ or Java. Other approaches like component-based software design [26] or the unified modeling language (UML) [27] provide graphical design entries for improved implementation efficiency.

#### 2.1.4 Application Impact on Design Methodology

The rapidly increasing performance demands and limited available energy of battery powered devices, gives rise to an increasing energy-performance gap. Additionally, the need to jointly support various applications and their requirements is having a significant impact on the design methodology. *General purpose applications* demand flexible architectures to support a wide range of applications. Characterized by a dominant control path, software development relies on highlevel programming languages along with operating systems (OSs), middlewares, and libraries. In contrast, applications from the domain of *wireless communication* and *multimedia* are implemented by highly specialized architectures and low-level software development. Applications of these domains are characterized by high computational demands in the data plane processing with relatively low control overhead.

In general, these various application requirements have significant impact on the design methodology of the two major components *software* and *hardware*. From the hardware perspective, the complexity and computational demand of modern communication standards requires rapidly increasing performance while preserving energy efficiency for future wireless communication devices. As the current technology scaling cannot cope with these requirements by itself, new approaches have to be considered [5]. An obvious solution is to apply parallelism, in terms of processing the application on multiple processing elements in parallel. In addition, the contradictory requirements of high computational power and energy efficiency require highly specialized hardware architectures. This has led to the common agreement that *heterogeneous MPSoC* platforms are the best candidate for such devices [28].

Unfortunately, the selection of heterogeneous MPSoC platforms has a significant impact and induces design challenges like:

- Partitioning of tasks to optimally exploit the inherent parallelism within a given application.

- This partitioning is tightly linked to the selection of the type and number of hardware components, which is a key question for assembling the hardware architecture.

- Performance evaluation can no longer be performed on the basis of a single isolated component. Instead, the interacting behavior of all system components requires a system-wide performance evaluation.

- New programming techniques and models need to be considered since, due to the heterogeneous nature of the platform a simple adaptation of known multiprocessor programming is not feasible.

In addition, the first and most important design objective is to achieve the performance requirements, mostly given in regard to *latency* and *throughput* constraints. These requirements, particularly when implementing the physical layer of a wireless communication standard, are characterized by stringent (hard) real-time constraints that have to be fulfilled. Otherwise, devices will most likely fail standard compliance tests, leading to business failure. Hence, the design methodology must incorporate techniques to efficiently evaluate whether the application-induced constraints are met or not. As late design changes tend to be more costly than early ones, such techniques should be applied as early as possible in the design process.

After discussing the application needs and their coarse-grained impact on the design methodology, the discussion now turns to detailed design aspects and the corresponding influence of each possible hardware component. Along with this, the impact on the design methodology is highlighted.

#### 2.2 Hardware Platforms and Components

New design methodologies offering increased productivity in terms of design efficiency are indispensable for the development of future heterogeneous MPSoCs. For the comparison of different MPSoC platforms the following fundamental objectives and metrics can be defined.

*Performance*. Probably the most important design objective, the performance, is typically measured in terms of latency and throughput. Especially, meeting the performance constraints induced by applications is highly challenging but necessary for a successfully operating device.

*Energy and Power Efficiency*. Energy efficiency is one of the most severe design issues and platform differentiators. Especially, for mobile and battery powered devices energy efficiency is essential. Unfortunately, over the last years battery capacity has not been able to cope with the increasing performance demands, leading

to a growing performance-energy gap. This requires architectural innovations to increase the energy efficiency needed at present and definitely in the future. The metric *Millions of Instructions Per Second (MIPS) per Watt* typically defines energy efficiency [29]. Although this rather crude definition gives designers a first rough idea, it is unsuitable, as it is the required *energy per task* which matters. In the domain of wireless communication this metric can be expanded to the required *energy per decoded bit* or, within the domain of multimedia, to *energy per pixel*. The power efficiency classifies the power dissipation on the chip which influences the package and the layout of the final chip.

*Cost.* In general the total costs consist of the design costs and the initial manufacturing costs [30]. Whereas the design costs include the development of both software and hardware, the initial manufacturing costs comprise the mask and wafer costs as well as the initial packaging and testing. The dominating design costs are related to software and hardware development. These are reported for current design technologies (90 nm) to be in the region of 10–100 million USD with an expected increase of 50–100% per shrink in the process generation. Whereas in the past hardware-development costs claimed the major portion, the increasing use of programmable components has led to rapidly increasing software costs [30]. Latest market studies of MPSoC design report them to be at the same level. In addition, chip mask production has become increasingly expensive and is typically in the range of multiple million USD for each mask iteration.

*Flexibility*. In contrast to the previously discussed objectives and metrics, flexibility cannot be simply given as a single value. Flexibility defines the capability to execute a specific functionality on a particular processing element. This metric is of vital importance especially when designing SDRs [6]. Additionally, flexibility has the advantages of enabling short time-to-market and extending the lifetime by applying software updates and bugfixes. It is closely related to portability, which defines the ease of porting a certain functionality from one platform to another. Portability can be defined as the inverse of the porting effort [31] which, in turn, directly relates to flexibility.

These objectives help to guide system architects in their design decisions to find the optimal design. However, the complexity and short time-to-market along with the discussed requirements put a particular pressure on the development of such MPSoC platforms. Therefore, new design methodologies have to be considered to minimize the required development effort and costs. Here two fundamental design concepts, namely component-based design (CbD) [32] and platform-based design (PbD) [33], have been envisioned and found major acceptance.

*MPSoC design: Evolution rather than Revolution.* According to the componentbased approach, the complete platform is assembled from in-house or external IP components, e.g., processor cores, communication architectures, memories, and many other IP components. The key to the efficient use of this design principle is a unified interface definition to connect arbitrary IP components. These interfaces are mostly bus or Network-on-Chip (NoC) centric, like the interfaces of the

Fig. 2.4 IP block structure of the TI OMAP44x platform [38]

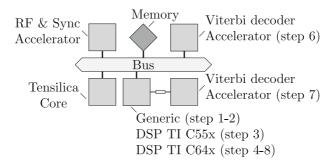

AMBA bus [34] or the IBM CoreConnect [35]. These have been standardized or evolved to a de facto standard by wide utilization. Based on this design methodology a large variety of companies have established a successful IP business, among them processor IP vendors like ARM, MIPS, and Tensilica as well as communication architecture IP providers like Arteris [36] as well as above-mentioned IP vendors like ARM and IBM. An example IP-component structure for TI's OMAP [37] platform is sketched in Fig. 2.4.

This CbD inherently ensures the high reuse of components over different platforms as they are separated by well-defined interfaces. Because of growing complexity, the average number of IP components an MPSoC platform consists of has increased from 25 in 2006 to 28 in 2007 and 33 in 2008 [39]. Further predictions expect an increase over the next years, already reaching 72 IP components in an average platform design by the year 2012.

With the aid of such IP components, PbD has proved to be highly suitable to quickly obtain modified platforms from a base one. The major element is the restriction of the design space by reducing flexibility, which simplifies and shortens the development cycle significantly. This design methodology has been successfully applied to especially address a specific market segment, e.g., the areas of wireless communication and multimedia. Prominent examples are TI's OMAP platforms for wireless communication devices and Philips Nexperia [40] platforms for multimedia applications.

The development of each platform is based on a construction kit. For each market segment a particular set of IP components is selected and connected. For example, the OMAP331 targeting the low-cost segment consists of an ARM926EJ-S processor core with a few surrounding peripheral devices. The high-cost segment is addressed by TI's OMAP3430 [37] platform that includes a more powerful ARM

Cortex-A8 processor, an IVA 2+ graphics accelerator, a POWERVR SGX graphics core [41], a dedicated image signal processor (ISP), and various other peripheral devices.

Apart from the business success of such platforms, this design methodology bears some hidden traps and risks [42, cf. 7.2]. The key risk is that system architects enter the design cycle biased and do not question design decisions related to the preexisting software or hardware IPs. In the end this can lead to false design decisions that decrease performance or increase energy consumption. In contrast, starting designs from scratch without reusing pieces of existing platforms is also no option when considering the tight time-to-market constraints. Therefore, a suitable design methodology requires a mixture of both extremes and demands strong design discipline. Hence, Bailey et al. [42] propose that all design options should be considered when developing a modified platform virtually starting with a blank sheet of paper, but characteristics, prior experiences and reuse of existing IP components can be incorporated to enhance the design process and the final platform.

As a large variety of different components exists, the rest of this section discusses each particular group of components separately and highlights the impact on the design methodology. However, it should be noted that the most essential issue in MPSoC design is the interwoven behavior of all the components and not that of a single isolated component. For example, a high performance processor core cannot fully exploit its capabilities if either the communication architecture or the memory subsystem is too slow to deliver the necessary data to be processed. Such issues cannot be evaluated in an isolated fashion because they only occur when investigating the system-wide performance.

#### 2.2.1 Processing Elements

The class of processing elements ranges from highly flexible general purpose processors (GPPs) to dedicated hardwired accelerators, optimized for a particular function. Lately, the demand for postfabrication flexibility has led system architects to increasingly use flexible and programmable components like general purpose processors, digital signal processors (DSPs), and application-specific instruction-set processors. Consequently, the amount and the importance of software are steadily increasing. Already today software has become one of the most critical pieces in system design [43], consuming a significant amount of the overall budget. With the increasing introduction of heterogeneous MPSoCs, various software design methodologies need to be considered jointly ranging from high-to low-level software constructs.

The class of the processing elements can roughly be classified into the following groups.

- General Purpose Processor (GPP)

- Digital Signal Processor (DSP)

- Application Specific Instruction Set Processor (ASIP)

- Reconfigurable Application Specific Instruction Set Processor (rASIP)

- Field Programmable Gate Array (FPGA)

- Application Specific Integrated Circuit (ASIC)

*General Purpose Processors* offer high flexibility and are hence utilized for arbitrary applications like control and user-level applications. Commonly, application development is conveniently carried out in high-level programming languages, e.g., C/C++ and Java. Often an operating system (OS) is supported and software development is abstracted by HAL or other middlewares from low-level hardware features. This shields software design from the underlying hardware by means of abstraction, permitting to concentrate on the pure application development.

*Digital Signal Processors* are especially tailored for the common characteristics and operations of digital signal processing algorithms. These processors exhibit special instructions to efficiently perform operations common to these algorithms, e.g., multiply accumulate, add-compare-select, and Galois field instructions [44]. The latest DSP architectures provide increased parallelism by means of Very Long Instruction Words [45], Single-Instruction Multiple-Data [46], and superscalar [47] hardware features. Because of the high-performance and low energy-consumption demands in the domain of wireless communication, fixed-point DSPs are still the first choice even after the introduction of floating-point DSPs [44].

Application Specific Instruction Set Processors are specially developed for a specific application. In general, the design of an ASIP follows the guideline of minimizing flexibility to maximize energy efficiency, area efficiency, and/or performance. Today, the class of ASIPs covers a wide range of different approaches and architectures. Tensilica's approach [48] enters the design process with the Xtensa processor core as a base architecture and allows further customization of this template with respect to the addressed application. Other approaches support ASIP development based on an Architecture Description Language (ADL), e.g., LISA 2.0 [49] or Expression [50]. These ADL-based approaches do not restrict designers in their decisions to support full architectural design space exploration. Contrary to GPPs, application-specific features cannot be easily addressed by compilers. Therefore, ASIPs typically require low-level software development to exploit the specific features. However, there are promising approaches to generate the software tool-chain including compiler, assembler, and linker for the ASIP [51, 52] with reasonable performance.

*Reconfigurable Application Specific Instruction Set Processors* extend the concept of ASIPs further by combining the base processor with a reconfigurable fabric based on FPGAs [53]. This combination of a fixed and a reconfigurable hardware architecture promises high performance with increased flexibility to adapt the designed processor to different applications. Compared with the previously discussed ASIPs, the reconfigurable part adds postfabrication flexibility. Already a few architectures [54] and design methodologies [55, 56] exist, highlighting the potential of such architectures. However, this research field is relatively new and is expected

to have high potential in the future. Besides the earlier-mentioned issues for ASIPs, additional hardware description language (HDL) programming needs to be included to program the embedded FPGA.

*Field Programmable Gate Arrays* are reconfigurable processing elements. Based on the capability to reconfigure the functionality after manufacturing, these components provide a particular postfabrication flexibility. The utilization of such devices has a strong impact on the design process, because FPGA devices are traditionally programmed in hardware description languages, e.g., VHDL [57] and Verilog [58]. Therefore, adding an FPGA to a platform changes the design process to a mixed software and hardware development. However, its flexibility compared to ASICs is achieved at the expense of decreased performance and increased energy consumption, but offers the possibility of reprogramming and bugfixing in the field.

*Application Specific Integrated Circuits* are specially tailored for a given algorithm or application. With the functionality fixed, only minor configuration can be applied after fabrication. Mostly this configuration is limited to the setting of algorithmic parameters, e.g., the filter coefficients of an FIR filter. In contrast to the restricted flexibility, energy efficiency and performance are relatively high. This leads to an integration of such processing elements in the performance-critical parts of a design. The traditional design focuses on known hardware design methodologies like Register Transfer Level (RTL), modeling with logic synthesis on standard-cell libraries, or full-custom design on transistor level.

Summarizing the common use of these processing elements, wireless communication and multimedia algorithms, as proved in the past, can be efficiently implemented on specialized hardware. Dedicated hardwired accelerators (ASICs) are especially tailored for a particular algorithm, whereas DSPs are optimized to the common characteristics of such algorithms, e.g., multiplications, multiply accumulate, and add-compare-select. Application Specific Instruction Set Processors (ASIPs), like those proposed by Wehn et al. [59] or SODA [2], are specialized processor cores which have been specially developed for a particular algorithm or multiple ones. The key principle of ASIPs is to minimize the provided flexibility to increase performance and to minimize overheads in terms of area, power and energy consumption. To incorporate such specialized architectures, software development cannot follow the general-purpose approach, as current high-level language compilers can hardly exploit such features optimally due to their highly irregular structure [31,60]. However, research focuses on this issue and promising approaches exist in literature [51,61–64].

In contrast to specialized processing elements, general purpose applications require a higher degree of flexibility. Hence, GPPs are typically utilized for their execution and the latest techniques and architectures from the personal-computer domain are increasingly being applied to mobile devices. For example, ARM Inc. has just recently announced the ARM Cortex-A8 processor core as their first superscalar processor core. Additionally, multicore processors like the ARM Cortex-A9 can already incorporate up to four cores within a single entity. So far only processing elements have been considered. However, with the increasing parallelism in future platforms, data exchange between the processing elements is becoming another key issue. In general, to transfer data from one element to another, a communication architecture and storage elements are necessary. Recently with the increasing number of interacting components, the principle of bus-based communication architectures has gradually tended to become the bottleneck of the complete system. Therefore, the latest research in this domain has proposed more complex communication networks subsumed under the term Network-on-Chip (NoC) [65].

#### 2.2.2 Communication Architectures and Memory Subsystems

Despite the vast research and many publications within this domain, a precise definition of NoCs is typically not given [66]. The OCP-IP consortium defines the term NoC in a rather generic fashion as *a communication network that is used on chip* [67]. This generic definition allows further differentiation of NoC architectures under the key aspects of:

- Switching policy: circuit-switching and packet-switching.

- *Topology*: point-to-point, bus, hierarchical bus, crossbar, 2D-mesh, 2D-torus, 3D-torus, customized for the addressed application, etc.

- Routing: deterministic fixed routing and dynamic adaptive routing.

- Quality-of-Service: best effort and guaranteed throughput.

- Testing and fault-tolerance.