**Integrated Circuits and Systems**

# Yu Cao Predictive Technology Model for Robust Nanoelectronic Design

# Integrated Circuits and Systems

Series Editor Anantha P. Chandrakasan Massachusetts Institute of Technology Cambridge, Massachusetts

For further volumes: http://www.springer.com/series/7236

Yu Cao

# Predictive Technology Model for Robust Nanoelectronic Design

Foreword by Chenming Calvin Hu

Yu Cao School of ECEE Arizona State University Tempe, AZ, USA ycao@asu.edu

ISSN 1558-9412 ISBN 978-1-4614-0444-6 e-ISBN 978-1-4614-0445-3 DOI 10.1007/978-1-4614-0445-3 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011931530

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

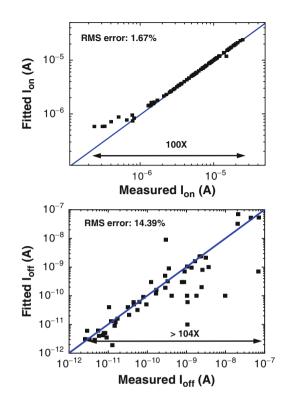

Springer is part of Springer Science+Business Media (www.springer.com)

To Xuejue, your dance of the water sings the pebbles of my life

## Foreword

The minimum feature size of CMOS technology will approach 10 nm in 10 years. Such aggressive scaling will lead to wonderful benefits to consumers, businesses and the global society. Unfortunately, it will also lead to increased power dissipation, process variations and device drift, posing tremendous new challenges to designing robust circuits. Already, the design complexity and time are increasing at accelerating rates. The lure of early market entry pushes advanced design research to begin much earlier than the completion of device technology development. The need is even clearer where new devices, e.g. FinFET and post-silicon devices are involved. The concept of technology/circuit co-development is no longer just a good idea, it is a necessity.

This new paradigm requires predictive SPICE transistor models for future technology generations, including both nanoscale CMOS and post-silicon devices. SPICE models used in circuit design are traditionally extracted from measurements taken on working transistors generated by the technology development process. In stark contrast, predictive SPICE model is created before the physical transistor has been fabricated, thus allowing design research to get an important early start. A predictive model is critical to identifying emergent problems and enable early search for solutions. While integrated semiconductor companies already make significant efforts to generate predictive models, fabless companies and university researchers usually do not have access to them.

PTM, a canonical *Predictive Technology Model* of both transistors and interconnect, offers a generic, open-source tool for early stage design research. Based on the standard BSIM model, PTM projects technology scaling down to the 12 nm node. It has been adopted for a broad range of research on low-power design, design robustness, system integration, design tools, and for university teaching, worldwide. As PTM becomes the de facto device model for advanced design benchmarking, this book timely reveals the "hidden secrets" behind PTM. I am proud to have worked with Prof. Cao to develop the early PTM (then called BPTM) at UC Berkeley in the late 1990s. Prof. Cao has expanded PTM from a simple predictive model of conventional MOSFETs into a suite of predictive models ranging from models of very small MOSFETs and promising alternative devices to process variability and reliability models embedded into the device models. These predictive models are further incorporated into the design environment, through predictive PDKs.

This is the first book to help university researchers and industry practitioners to understand predictive modeling principles and to gain insights into future technology trends. As evidenced by the thousands of research publications based on the use of PTM, the understanding and insights provided by this book will have a far-reaching impact on future circuit design research and IC development.

Berkeley, California

Chenming Calvin Hu

# Preface

The story of PTM, standing for Predictive Technology Model, is dated back to the year of 1999, when IC designers were hectically migrating from 0.25  $\mu$ m to 0.18  $\mu$ m CMOS technology. At that moment, many new problems were emerging from the physical level, such as short-channel effects and crosstalk noise, posing significant challenges that slowed down the product development. PTM was proposed to help bridge the technology and design groups, such that these issues can be brought to the attention as early as possible in the design process. Enabled by PTM, the new concept of concurrent process-design development is then widely practiced by university and industry groups. PTM effectively enhances design productivity and catalyzes the silicon evolution into the nanoscale regime.

Ten years after the start, PTM has successfully developed state-of-the-art CMOS models toward the 10 nm node. They are well disseminated through the web interface, and adopted into university curriculums. The demand of predictive modeling becomes even stronger today, as we are facing much more complicated and more diverse technological choices, as well as much larger scale of integration. This book covers both the essence of modeling principles and the application of PTM in nanoelectronic design. The chapters are intended primarily for IC designers and EDA tool developers, who have the background in transistor physics and circuit performance analysis. The discussion will especially benefit those with research interests in the areas of technology scaling and compact modeling.

The book starts with the background and overview of PTM. Chapter 1 reviews the important issues as CMOS technology is scaling toward the 10 nm node. It motivates the shift of IC design paradigm, in which PTM is the essential component. Current PTM provides standard compact model of bulk CMOS devices, BSIM4, down to the 12 nm node. Chapter 2 presents the systematic approach to scale device model parameters for future bulk devices, based on the solid understanding of device physics and silicon data as a reality check. Furthermore, Chap. 3 deals with recent extensions of conventional CMOS devices, including strained Si, high-k/metal gate, and the double-gate structure. Below the 90 nm node, these non-traditional materials and structures are vitally important to enhance the device

performance. Modeling solutions to them are compatible with standard CMOS model and circuit simulation tools.

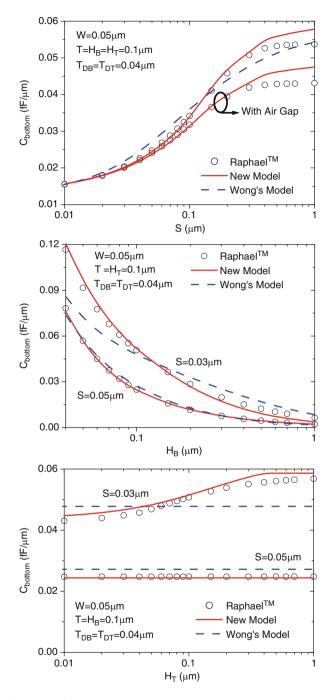

With CMOS scaling approaches fundamental physics and manufacturing limits, process variability and reliability degradation becomes the key limiting factors for future integrated system design. Chapters 4 and 5 address these concerns by developing statistical modeling, extraction and simulation techniques. New compact models are proposed for emerging variability and reliability effects, such as NBTI, in order to support design exploration for reliability. Besides these parasitic effects of transistor scaling, interconnect parasitics play an increasingly significant role in contemporary IC design. Chapter 6 presents modeling results of wire capacitance, capturing the latest advancement in interconnect technology.

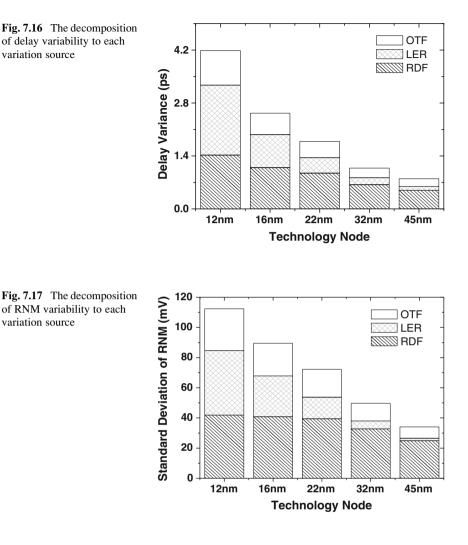

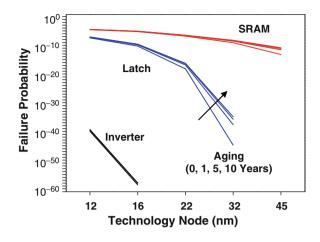

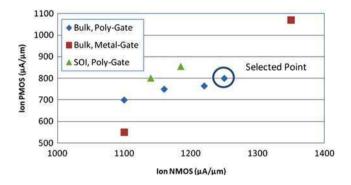

These device models provide the basis of design benchmarking and tool development. Using PTM, Chap. 7 quantitatively evaluates various technology factors in scaled CMOS design, helping shed light on the performance trend along the roadmap. Moreover, Chap. 8 describes a 45 nm predictive process design kits (PDK), which are the critical interface between circuit design and silicon fabrication. Under the increasing stress of the manufacturability, such a PDK facilitates designers assess layout dependent effects and manage their impact.

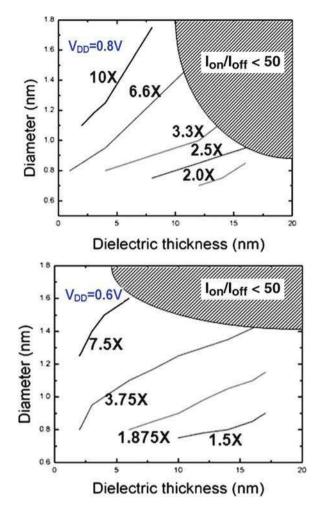

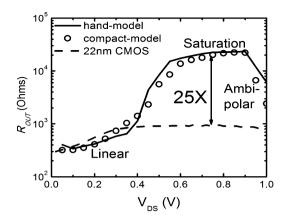

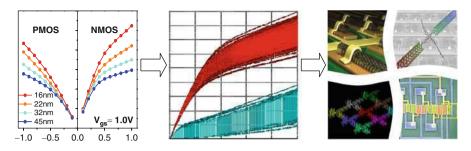

Beyond the 10 nm node, more radical solutions will be vital to meet the scaling criteria. While there have been significant accomplishments in scientific discovery, it is only the beginning of the engineering research that is required to transfer the science into device, circuit, and system integration. In Chap. 9, PTM outreaches the effort to the compact modeling of carbon nanotube devices, helping illustrate their enormous design potentials. Finally, Chap. 10 concludes the book with a brief outlook on future nanoelectronic modeling and design.

Tempe, AZ

Yu Cao

### Acknowledgements

I would like to thank many people who contribute to the PTM project. First and foremost, my grateful acknowledgement is made toward Professor Chenming Hu and the BSIM group at the University of California, Berkeley, for their insightful advices and guidance at the early stage. I also express my gratitude to Professor Dennis Sylvester, University of Michigan, Ann Arbor; Professor Michael Orshansky, University of Texas, Austin; and Professor Takashi Sato, Kyoto University, for their patient help to initialize this project. I am indebted to the visionary suggestions provided by Shekhar Borkar, Ram Krishnamurthy, and Jeff Parkhurst at Intel. Many students in my group have excellent contributions to PTM, including Wei Zhao, Wenping Wang, Chi-Chao Wang, Saurabh Sinha, Yun Ye, Asha Balijepalli, Min Chen, and Varsha Balakrishnan. The PTM project is made possible by the support from the Focus Center Research Program and Semiconductor Research Corporation.

Thanks are due to many university and industry researches who help improve PTM during its evolution. These people include: Judy An, Integrated Memory Logic; Dimitri Antoniadis, Massachusetts Institute of Technology; Robert Dutton and H.-S. Philip Wong, Stanford University; Nagib Hakim and Changhong Dai, Intel; Ali Icel, Global Foundries; Xia Li, Seung H. Kang, Matt Nowak, Qualcomm; Colin McAndrew, Freescale; Sani Nassif and Frank Liu, IBM; Jan Rabaey and Tsu-Jae King Liu, University of California, Berkeley; Vijay Reddy, Srikanth Krishnan, Keith Green, Texas Instruments; Kaushik Roy and Mark Lundstrom, Purdue University; Kishore Sinha, Synopsys; Yuan Xie and Vijay Narayanan, Pennsylvania State University; Yu Wang, Tsinghua University. I apologize in advance to anyone I overlooked. Their technical suggestions help lead PTM toward this stage.

Yu Cao

# Contents

| 1 |                                                  |                                  | on                                                        | 1<br>4 |  |  |  |  |  |

|---|--------------------------------------------------|----------------------------------|-----------------------------------------------------------|--------|--|--|--|--|--|

| 2 | Pree                                             | lictive                          | Technology Model of Conventional CMOS Devices             | 7      |  |  |  |  |  |

|   | 2.1 PTM in Light of CMOS Scaling                 |                                  |                                                           |        |  |  |  |  |  |

|   | 2.2                                              | Predic                           | ctive Methodology                                         | 10     |  |  |  |  |  |

|   |                                                  | 2.2.1                            | Parameter Taxonomy                                        | 10     |  |  |  |  |  |

|   |                                                  | 2.2.2                            | Prediction of Model Parameters                            | 11     |  |  |  |  |  |

|   | 2.3                                              | Evalu                            | ation of PTM                                              | 15     |  |  |  |  |  |

|   |                                                  | 2.3.1                            | Verification and Prediction of I-V Characteristics        | 15     |  |  |  |  |  |

|   |                                                  | 2.3.2                            | Impact of Process Variations                              | 17     |  |  |  |  |  |

|   | Refe                                             | erences                          |                                                           | 22     |  |  |  |  |  |

| 3 | Pre                                              | lictive                          | Technology Model of Enhanced CMOS Devices                 | 25     |  |  |  |  |  |

|   | 3.1                                              | Strain                           | Engineering in Scaled CMOS                                | 25     |  |  |  |  |  |

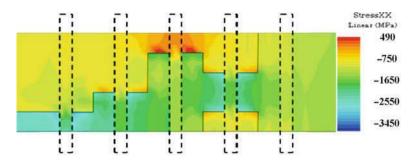

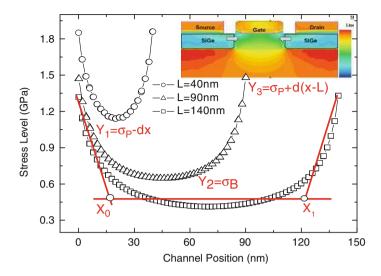

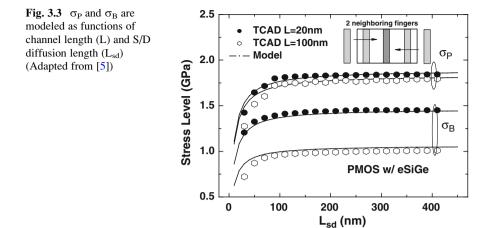

|   |                                                  | 3.1.1                            | Modeling of Stress Distribution in the Channel            | 27     |  |  |  |  |  |

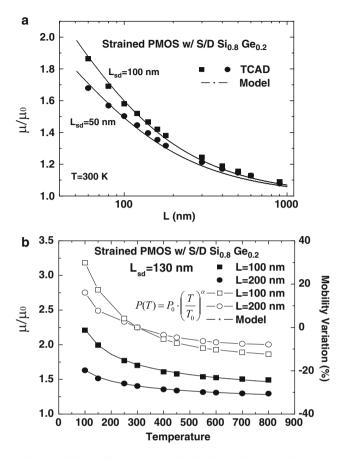

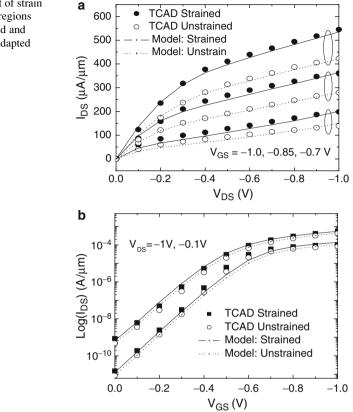

|   |                                                  | 3.1.2                            | Equivalent Mobility Model                                 | 28     |  |  |  |  |  |

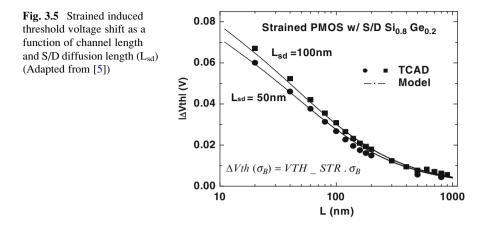

|   |                                                  | 3.1.3                            | Strain Induced Threshold Voltage Shift                    | 30     |  |  |  |  |  |

|   | 3.2                                              | High-                            | <i>k</i> /Metal Gate and Multiple-V <sub>th</sub> Devices | 32     |  |  |  |  |  |

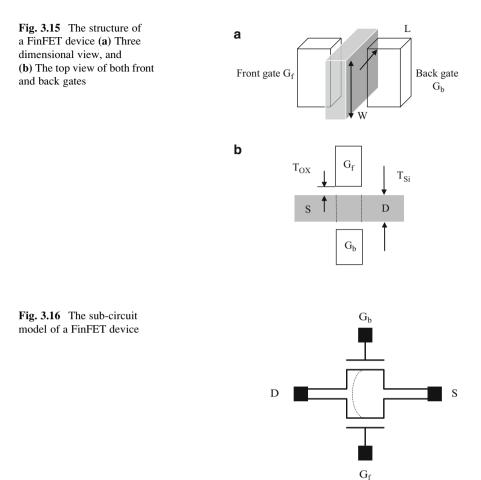

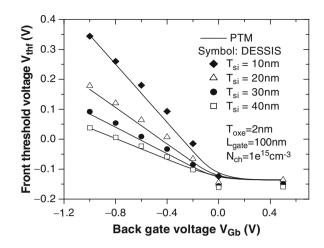

|   | 3.3                                              | Modeling of the FinFET Structure |                                                           |        |  |  |  |  |  |

|   | Refe                                             | erences                          |                                                           | 39     |  |  |  |  |  |

| 4 | Stat                                             | istical                          | Extraction and Modeling of CMOS Variability               | 43     |  |  |  |  |  |

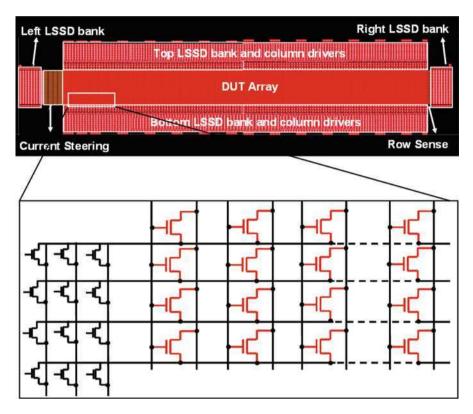

|   | 4.1                                              | Varia                            | bility Characterization and Extraction                    | 44     |  |  |  |  |  |

|   |                                                  | 4.1.1                            | Test Chip and In-Situ Measurement                         | 45     |  |  |  |  |  |

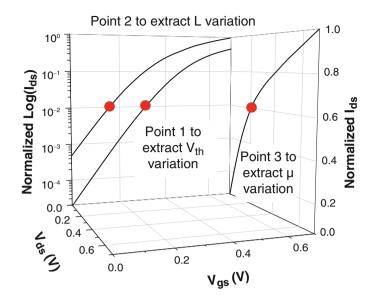

|   |                                                  | 4.1.2                            | Extraction and Decoupling of Variations                   | 46     |  |  |  |  |  |

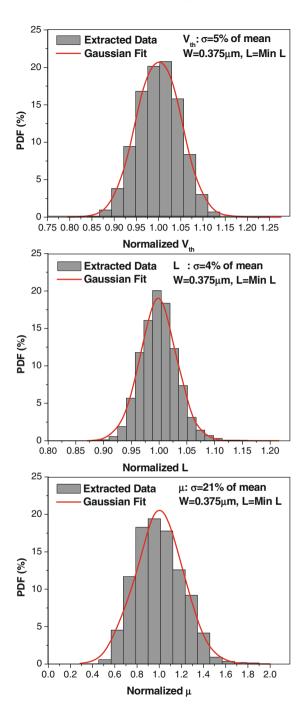

|   |                                                  | 4.1.3                            | Verification and Statistical Analysis                     | 49     |  |  |  |  |  |

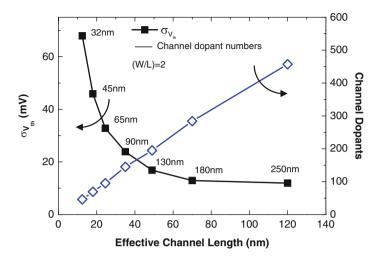

|   | 4.2 Predictive Modeling of Threshold Variability |                                  |                                                           |        |  |  |  |  |  |

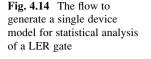

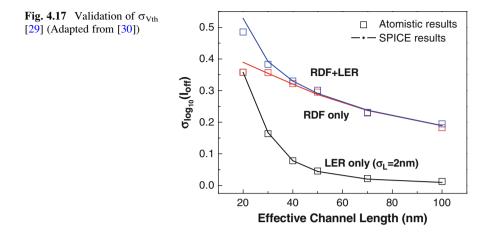

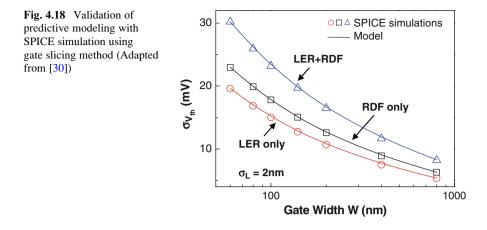

|   |                                                  | 4.2.1                            | Simulation with Gate Slicing Method                       | 55     |  |  |  |  |  |

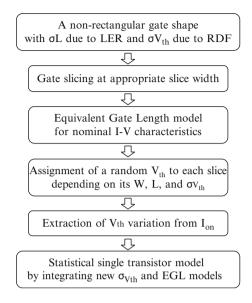

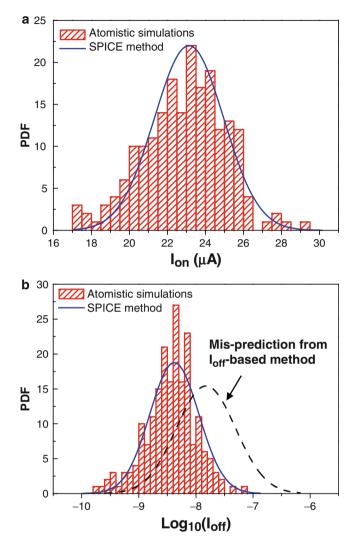

|   |                                                  | 4.2.2                            | Validation with Atomistic Simulations                     | 59     |  |  |  |  |  |

|   |                                                  | 4.2.3                            | Predictive V <sub>th</sub> Variability Modeling           | 61     |  |  |  |  |  |

|   | Refe                                             | erences                          |                                                           | 64     |  |  |  |  |  |

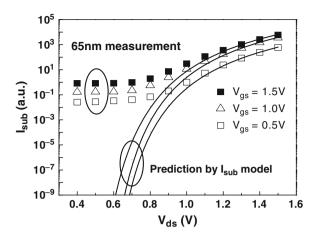

| 5 | Moo  | deling of Temporal Reliability Degradation       6' |  |  |  |  |  |  |  |

|---|------|-----------------------------------------------------|--|--|--|--|--|--|--|

|   | 5.1  | Static Aging Models                                 |  |  |  |  |  |  |  |

|   | 5.2  | Dynamic NBTI Models                                 |  |  |  |  |  |  |  |

|   |      | 5.2.1 Cycle-to-Cycle Degradation Model              |  |  |  |  |  |  |  |

|   |      | 5.2.2 Long-Term Degradation Model                   |  |  |  |  |  |  |  |

|   | 5.3  | Model Implementation and Prediction         74      |  |  |  |  |  |  |  |

|   |      | 5.3.1 Sub-circuit for SPICE Simulation              |  |  |  |  |  |  |  |

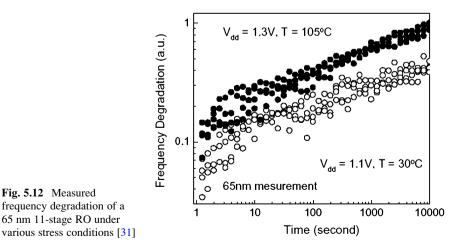

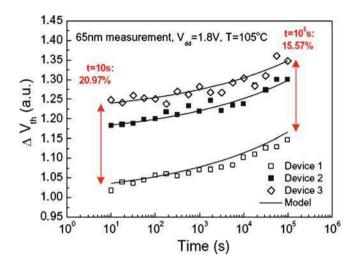

|   |      | 5.3.2 Device and Circuit Performance Degradation    |  |  |  |  |  |  |  |

|   | 5.4  | Interaction with Process Variations                 |  |  |  |  |  |  |  |

|   | Refe | erences                                             |  |  |  |  |  |  |  |

| 6 | Мо   | deling of Interconnect Parasitics                   |  |  |  |  |  |  |  |

| U | 6.1  | Background of Interconnect Models                   |  |  |  |  |  |  |  |

|   | 6.2  | Modeling Principles       8                         |  |  |  |  |  |  |  |

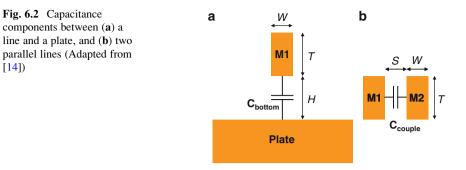

|   | 6.3  | Capacitance Modeling of the Basic Patterns          |  |  |  |  |  |  |  |

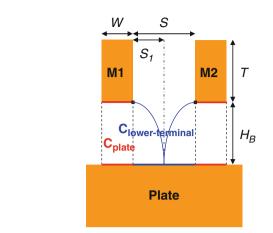

|   | 0.5  | 6.3.1Model of the Line-to-Plate Capacitance8'       |  |  |  |  |  |  |  |

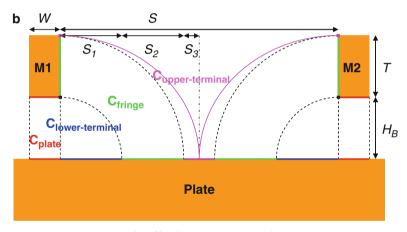

|   |      | 6.3.2Role of Terminal Capacitance88                 |  |  |  |  |  |  |  |

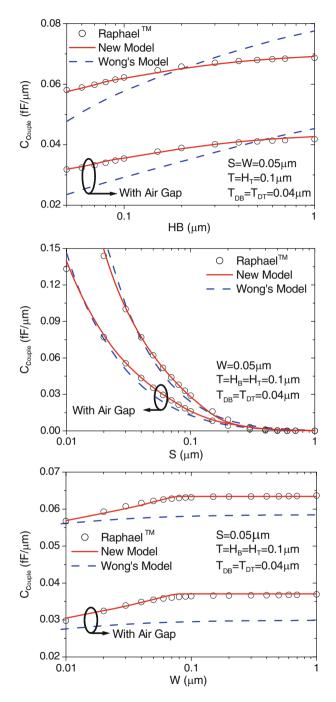

|   |      | 6.3.3Model Comparison and Discussions89             |  |  |  |  |  |  |  |

|   |      | 6.3.4 Coupling Capacitance between Parallel Lines   |  |  |  |  |  |  |  |

|   | 6.4  | Applications to General BEOL Structures             |  |  |  |  |  |  |  |

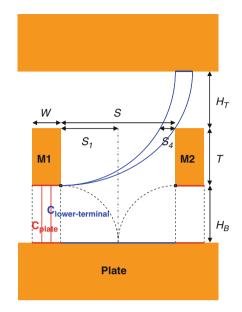

|   | 0.7  | 6.4.1 Physical Effects with Multiple Electrodes     |  |  |  |  |  |  |  |

|   |      | 6.4.2 Modeling of the Coupling Capacitance          |  |  |  |  |  |  |  |

|   |      | 6.4.3 Revisiting the Line-to-Plate Capacitance      |  |  |  |  |  |  |  |

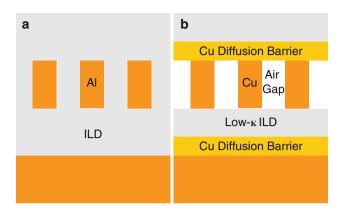

|   |      | 6.4.4Cu Diffusion Barrier96                         |  |  |  |  |  |  |  |

|   |      | 6.4.5 Air Gap                                       |  |  |  |  |  |  |  |

|   | 6.5  | Model Validation and Comparison                     |  |  |  |  |  |  |  |

|   |      | erences                                             |  |  |  |  |  |  |  |

| _ |      |                                                     |  |  |  |  |  |  |  |

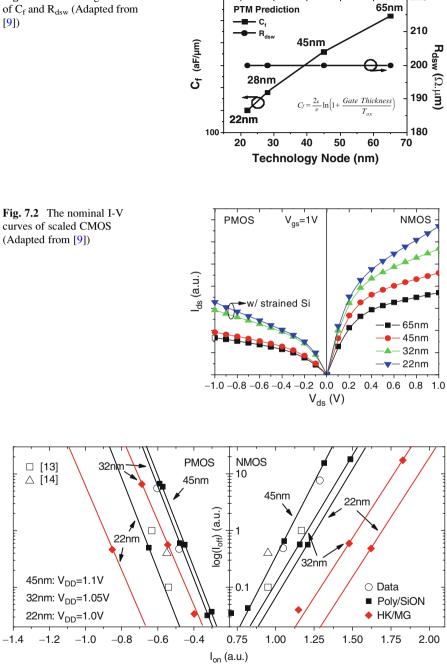

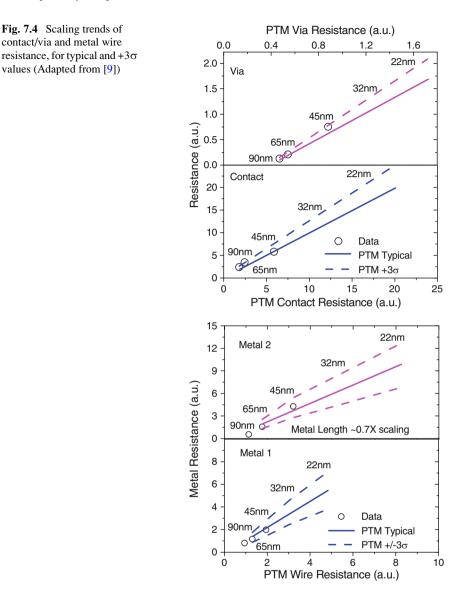

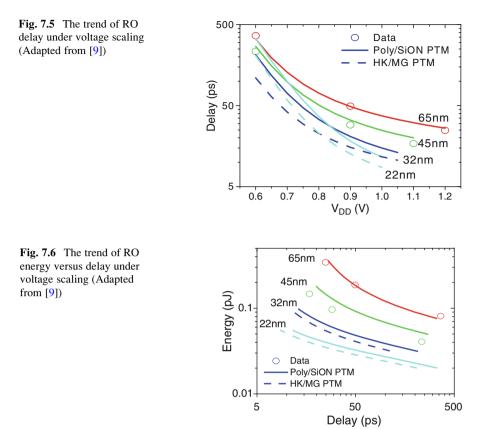

| 7 |      | ign Benchmark with Predictive Technology Model 103  |  |  |  |  |  |  |  |

|   | 7.1  | Customization of PTM                                |  |  |  |  |  |  |  |

|   | 7.2  | Exploratory Design of 22 nm CMOS Circuits 108       |  |  |  |  |  |  |  |

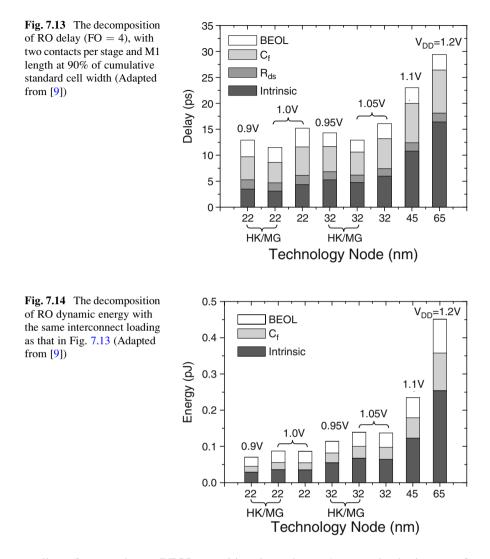

|   |      | 7.2.1 Ring Oscillator Delay and Energy 110          |  |  |  |  |  |  |  |

|   |      | 7.2.2 Performance of Sequential Elements            |  |  |  |  |  |  |  |

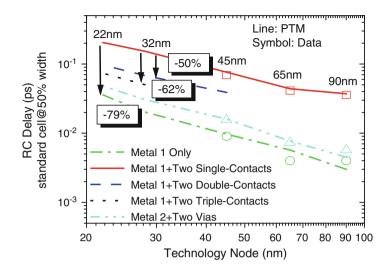

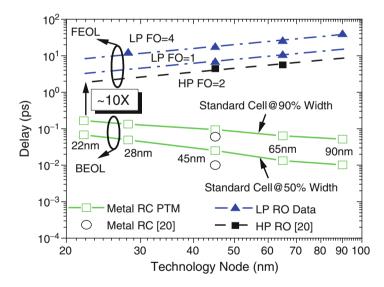

|   |      | 7.2.3 Impact of BEOL Scaling.                       |  |  |  |  |  |  |  |

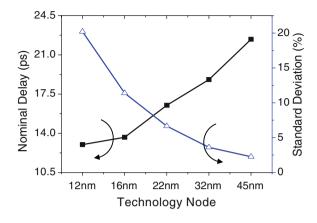

|   | 7.3  | Scaling Trend of Circuit Resilience 11:             |  |  |  |  |  |  |  |

|   | Refe | erences 118                                         |  |  |  |  |  |  |  |

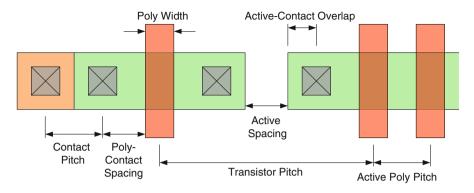

| 8 | Pre  | dictive Process Design Kits 12                      |  |  |  |  |  |  |  |

|   | W. 1 | Rhett Davis and Harun Demircioglu                   |  |  |  |  |  |  |  |

|   | 8.1  | 6                                                   |  |  |  |  |  |  |  |

|   | 8.2  |                                                     |  |  |  |  |  |  |  |

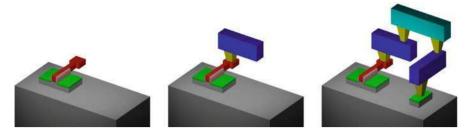

|   | 8.3  |                                                     |  |  |  |  |  |  |  |

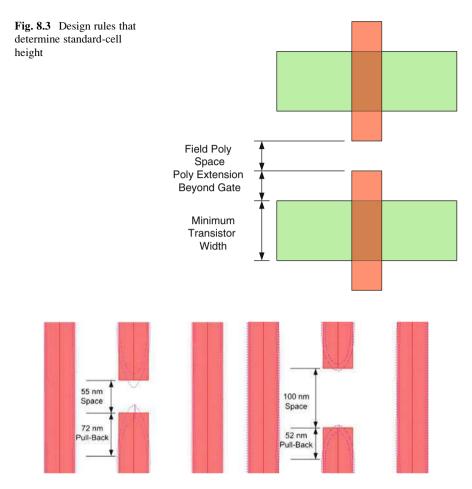

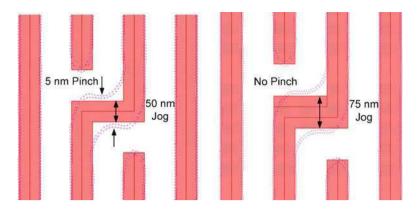

|   |      | 8.3.1 Width-Affecting Rules 12:                     |  |  |  |  |  |  |  |

|   |      | 8.3.2 Height-Affecting Rules 120                    |  |  |  |  |  |  |  |

|   |      | 8.3.3 Antenna Rules 123                             |  |  |  |  |  |  |  |

| 8.4  | Back-                                                                                                                                                                       | End Design Rules                                                                                                                                                                                                                                                                         | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

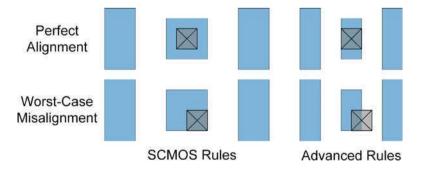

|      | 8.4.1                                                                                                                                                                       | Via Rules                                                                                                                                                                                                                                                                                | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

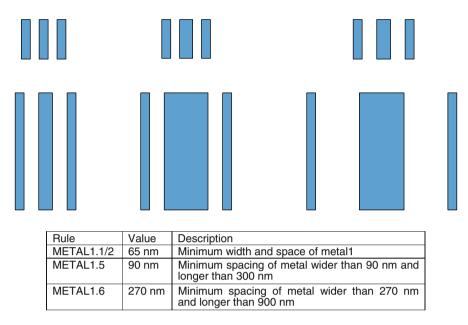

|      | 8.4.2                                                                                                                                                                       | Variable Spacing and Density Rules                                                                                                                                                                                                                                                       | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 8.4.3                                                                                                                                                                       |                                                                                                                                                                                                                                                                                          | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

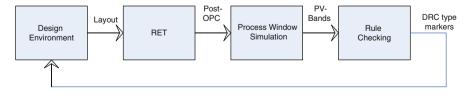

| 8.5  | Lithog                                                                                                                                                                      | graphy Simulation Model                                                                                                                                                                                                                                                                  | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8.6  | The F                                                                                                                                                                       | uture of Process Design Kits                                                                                                                                                                                                                                                             | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8.7  |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                          | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Refe | erences                                                                                                                                                                     |                                                                                                                                                                                                                                                                                          | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

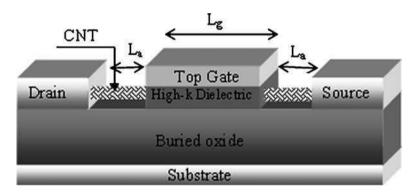

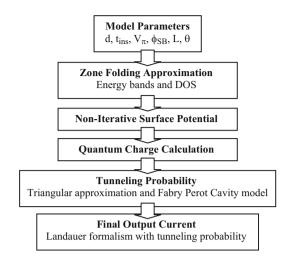

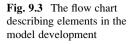

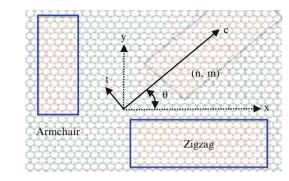

| Pre  | dictive                                                                                                                                                                     | Modeling of Carbon Nanotube Devices                                                                                                                                                                                                                                                      | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.1  |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                          | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 9.1.1                                                                                                                                                                       |                                                                                                                                                                                                                                                                                          | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 9.1.2                                                                                                                                                                       |                                                                                                                                                                                                                                                                                          | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 9.1.3                                                                                                                                                                       |                                                                                                                                                                                                                                                                                          | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 9.1.4                                                                                                                                                                       |                                                                                                                                                                                                                                                                                          | 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

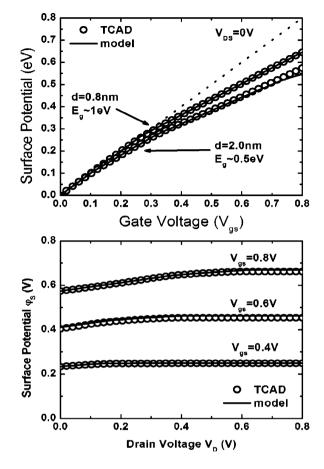

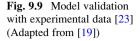

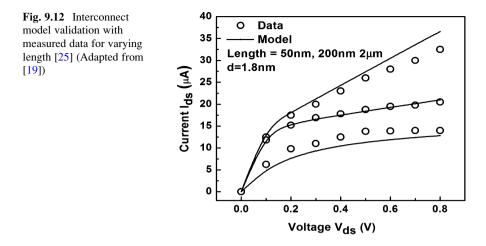

|      | 9.1.5                                                                                                                                                                       | Transistor Model Extraction and Validation                                                                                                                                                                                                                                               | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

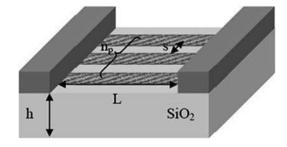

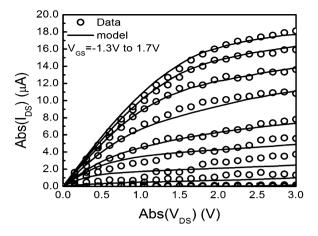

| 9.2  | Interco                                                                                                                                                                     | onnect Modeling                                                                                                                                                                                                                                                                          | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

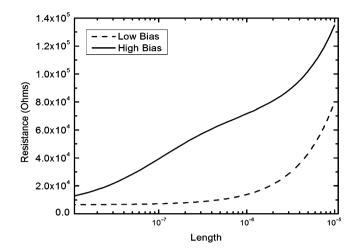

|      | 9.2.1                                                                                                                                                                       | CNT Interconnect Resistance                                                                                                                                                                                                                                                              | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 9.2.2                                                                                                                                                                       | Capacitance and Inductance of CNT Interconnect                                                                                                                                                                                                                                           | 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 9.2.3                                                                                                                                                                       | Interconnect Model Extraction and Validation                                                                                                                                                                                                                                             | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.3  | Statist                                                                                                                                                                     | ical Extraction of Process Variability                                                                                                                                                                                                                                                   | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

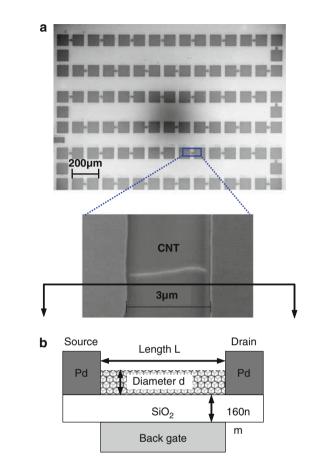

|      | 9.3.1                                                                                                                                                                       | Device Fabrication and Measurement                                                                                                                                                                                                                                                       | 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 9.3.2                                                                                                                                                                       | Model Based Extraction of Variations                                                                                                                                                                                                                                                     | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.4  | Desig                                                                                                                                                                       | n Insights with CNT Devices                                                                                                                                                                                                                                                              | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Refe | erences                                                                                                                                                                     |                                                                                                                                                                                                                                                                                          | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Prec | lictive                                                                                                                                                                     | Technology Model for Future Nanoelectronic Design                                                                                                                                                                                                                                        | 165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ex   |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                          | 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | <ul> <li>8.5</li> <li>8.6</li> <li>8.7</li> <li>Refe</li> <li><b>Preo</b></li> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>Refe</li> <li><b>Preo</b></li> </ul> | 8.4.1<br>8.4.2<br>8.4.3<br>8.5 Lithog<br>8.6 The F<br>8.7 Concl<br>References<br><b>Predictive</b><br>9.1 Predic<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.2 Interco<br>9.2.1<br>9.2.2<br>9.2.3<br>9.3 Statist<br>9.3.1<br>9.3.2<br>9.4 Desig<br>References<br><b>Predictive</b> | 8.4.1       Via Rules         8.4.2       Variable Spacing and Density Rules         8.4.3       Metal Stack.         8.5       Lithography Simulation Model         8.6       The Future of Process Design Kits         8.7       Conclusion         References       References         9.1       Predictive Modeling of Carbon Nanotube Devices         9.1       Predictive Transistor Model Development         9.1.1       Device Structure         9.1.2       Zone-folding Approximation         9.1.3       Surface-potential Based Modeling         9.1.4       Schottky Barrier Modeling         9.1.5       Transistor Model Extraction and Validation         9.2.1       CNT Interconnect Resistance         9.2.2       Capacitance and Inductance of CNT Interconnect         9.2.3       Interconnect Model Extraction and Validation         9.3       Statistical Extraction of Process Variability         9.3.1       Device Fabrication and Measurement         9.3.2       Model Based Extraction of Variations |

# Chapter 1 Introduction

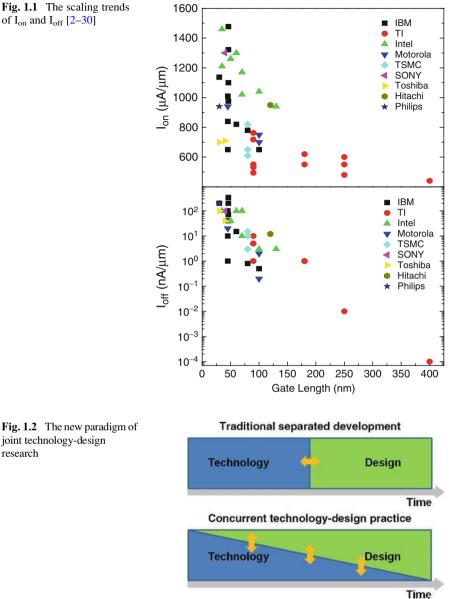

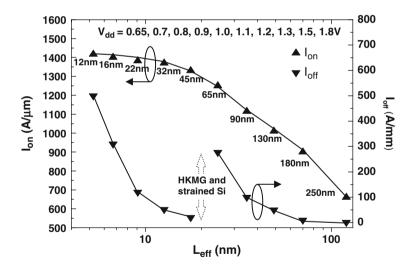

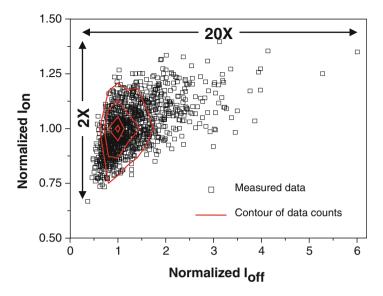

The scaling of CMOS technology has been the driving force of the semiconductor industry during past five decades, with the minimum feature size expected to reach 10 nm in 10 years [1]. Beyond that benchmark, the present scaling approach may have to take a different route, in order to overcome dramatic barriers in transistor performance degradation, power consumption, process and environmental variations, and reliability issues. For instance, Fig. 1.1 illustrates the scaling trends of the maximum on-state current (I<sub>on</sub>) and the off-state leakage current (I<sub>off</sub>), from a comprehensive set of published data [2–30]. From the 0.5  $\mu$ m node to the 32 nm node, the increase in I<sub>on</sub> is smaller than 3×; meanwhile, I<sub>off</sub> increases by more than six orders! Such a dramatic reduction in the ratio of I<sub>on</sub>/I<sub>off</sub> significantly affects the drivability of the device, and further influences all aspects of circuit performance, such as data stability of on-chip memory.

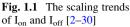

To continue the success of integrated circuit (IC) design, the grand challenge to IC community is to identify unconventional materials and structures, such as carbon-based electronics, integrate them into the large-scale circuit architecture, and enable continuous growth of chip scale and performance [1, 31]. Different from previous design paradigm, today's competitive circuit design and research must begin before a future generation of CMOS technology is fully developed, in order to successfully manage the development cost and guarantee the time to market. Figure 1.2 highlights the paradigm shift toward concurrent technology and design research [32].

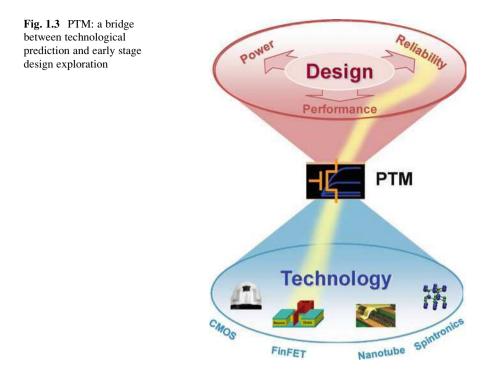

In this context, Predictive Technology Model (PTM), which bridges the process/ material development and circuit simulation through device modeling, is essential to assessing the potential and limits of new technology and to supporting early design prototyping. PTM is the critical interface between technology innovation and IC design exploration, as shown in Fig. 1.3. Coupled with circuit simulation tools, they significantly improve design productivity, providing the insight into the relationship between technology/design choices and circuit performance. In order to guarantee the quality of the prediction, PTM should be scalable with latest technology advances, accurate across a wide range of process uncertainties and operation conditions, and efficient for large-scale computation. As semiconductor

Y. Cao, Predictive Technology Model for Robust Nanoelectronic Design, Integrated Circuits and Systems, DOI 10.1007/978-1-4614-0445-3\_1, © Springer Science+Business Media, LLC 2011

joint technology-design

research

technology scales into the nanoscale regime, these modeling demands are tremendously challenged, especially by the introduction of alternative device materials and structures, as well as the ever-increasing amount of process variations.

This paper presents a comprehensive review on the development and latest results of Predictive Technology Model for nanoscale devices, covering end-ofthe-roadmap and post-silicon technologies. Driven by the increasingly complex and diverse nature of the underlying technology, the overarching goal of PTM is to

provide early comprehension of process choices and design opportunities, as well as to address key design needs, such as variability and reliability, for robust system integration. Specific topics include:

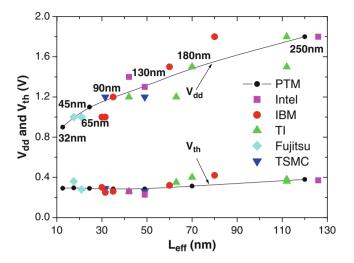

- Predictive modeling of end-of-the-roadmap CMOS technology: CMOS will arguably be the technology of choice for the next 15 years. To predict future technology characteristics, an intuitive approach would simply scale down the feature size and voltage parameters, such as supply voltage and threshold voltage ( $V_{th}$ ), from an existing technology. However, this approach is overly simplified and underestimates the overall device performance toward the end of the roadmap [33]. During technology scaling, process developers will optimize many other aspects of the device beyond sole geometry scaling. For instance, the scaling of  $V_{th}$  not only requires the change of channel doping concentration, but also impacts other physical parameters, such as mobility, saturation velocity, and the body effect. These intrinsic correlations among physical parameters need to be carefully considered for an accurate prediction.

- PTM for alternative materials and structures: The scaling of traditional bulk CMOS structure is slowing down in recent years as fundamental limits are rapidly approached. For instance, short-channel effects, such as drain-induced-barrierlowering (DIBL) and threshold voltage rolloff, severely increase leakage current and degrade the ratio of I<sub>on</sub>/I<sub>off</sub>. To overcome these difficulties and continue the path perceived by Moore's law, new materials (e.g., strained silicon, metal gate, high-k dielectrics, low-resistance source/drain) and structures (e.g., double-gate device)

need to be adopted into conventional CMOS technology. Therefore predictive models for bulk CMOS technology should be updated to capture the distinct electrical behavior of these advances, guaranteeing start-of-the-art predictions and design benchmarking toward the 10 nm regime.

- Modeling of CMOS variability and reliability: While technology scaling can be extended with alternative materials and structures, CMOS technology will eventually reach the ultimate limits that are defined by both physics and the fabrication process. One of the most profound physical effects will result from the vastly increased parameter variations and reliability degradation due to manufacturing and environmental factors. These parameter fluctuations exacerbate design margins, degrade the yield, and invalidate current deterministic design methodologies. To maintain design predictability with those extremely scaled devices, predictive models should incorporate both static process variations and temporal shift of device parameters. They should be extended from the traditional corner-based approach to a suite of modeling efforts, including extraction methods, the decoupling of variation sources, and highly efficient strategies for the statistical design paradigm.

- Process design kits (PDK) and design benchmark: As technological and design issues become more complicated with scaled CMOS devices, design productivity continues to be a major challenge for the semiconductor industry. Improved design flow automation and reuse methodologies are well known approaches to deal with this problem. But the lack of standards for archiving design data has prevented these techniques from having a significant impact. Recent trends towards open frameworks and open PDK promise to provide the very standards needed to enable greater levels of automation and reuse. Based on PTM, the development of predictive PDK and open library makes widespread adoption of these standards possible, and allows designers to perform more realistic assessment of the trends and challenges in future IC design.

- *Predictive modeling of post-silicon devices*: Beyond the far end of the CMOS technology roadmap, several emerging technologies have been actively researched as alternatives, such as nano-tubes, nano-wires, and molecular devices. As demonstrated in the success of PTM for CMOS, the outreach of PTM to these revolutionary technologies will help shed light on design opportunities and challenges with post-silicon technologies beyond the 10 nm regime.

In nanoelectronic design, predictive device modeling plays an essential role in joint technology-design exploration. Solutions to those modeling challenges will ensure a timely and smooth transition from CMOS-based design to robust integration with post-silicon technologies.

#### References

- 1. International Technology Roadmap of Semiconductors, 2007. (available at http://www.itrs.net).

- M. Khare, et al., "A high performance 90 nm SOI technology with 0.992µm<sup>2</sup> 6T-SRAM cell," *IEDM Tech. Dig.*, pp. 407–410, 2002.

- 3. R. A. Chapman, et al., "High performance sub-half micron CMOS using rapid thermal processing," *IEDM Tech. Dig.*, pp. 101–104, 1991.

- 4. Y. Taur, et al., "High performance 0.1 μm CMOS devices with 1.5 V power supply," *IEDM Tech. Dig.*, pp. 127–130, 1993.

- M. Rodder, Q. Z. Hong, M. Nandakumar, S. Aur, J. C. Hu, and I. C. Chen, "A sub-0.18 μm gate length CMOS technology for high performance (1.5 V) and low power (1.0 V)," *IEDM Tech. Dig.*, pp. 563–566, 1996.

- L. Su, et al., "A high-performance sub-0.25 μm CMOS technology with multiple thresholds and copper interconnects," VLSI Symp. Tech. Dig., pp. 18–19, 1998.

- 7. M. Hargrove, et al., "High-performance sub-0.08 µm CMOS with dual gate oxide and 9.7 ps inverter delay," *IEDM Tech. Dig.*, pp. 627–630, 1998.

- S. Yang, et al., "A high performance 180 nm generation logic technology," *IEDM Tech. Dig.*, pp. 197–200, 1998.

- 9. P. Gilbert, et al., "A high performance 1.5 V, 0.10 μm gate length CMOS technology with scaled copper metalization," *IEDM Tech. Dig.*, pp. 1013–1016, 1998.

- T. Ghani, et al., "100 nm gate length high performance/low power CMOS transistor structure," *IEDM Tech. Dig.*, pp. 415–418, 1999.

- K. K. Young, et al., "A 0.13 μm CMOS technology with 193 nm lithography and Cu/low-k for high performance applications," *IEDM Tech. Dig.*, pp. 563–566, 2000.

- S. Tyagi, et al., "A 130 nm generation logic technology featuring 70 nm transistors, dual V<sub>t</sub> transistors and 6 layers of Cu interconnects," *IEDM Tech. Dig.*, pp. 567–570, 2000.

- 13. K. Ichinose, et al., "A high performance 0.12 μm CMOS with manufacturable 0.18 μm technology," VLSI Symp. Tech. Dig., pp. 103–104, 2001.

- 14. S. Thompson, et al., "An enhanced 130 nm generation logic technology featuring 60 nm transistors optimized for high performance and low power at 0.7–1.4 V," *IEDM Tech. Dig.*, pp. 257–260, 2001.

- M. Celik, et al., "A 45 nm gate length high performance SOI transistor for 100 nm CMOS technology applications," VLSI Symp. Tech. Dig., pp. 166–167, 2002.

- 16. V. Chan, et al., "High speed 45 nm gate length CMOSFETs integrated into a 90 nm bulk technology incorporating strain engineering," *IEDM Tech. Dig.*, pp. 77–80, 2003.

- 17. K. Mistry, et al., "Delaying forever: Uniaxial strained silicon transistors in a 90 nm CMOS technology," *VLSI Symp. Tech. Dig.*, pp. 50–51, 2004.

- S. Mayuzumi, et al., "Extreme high-performance n- and p-MOSFETs boosted by dual-metal/ high-k gate damascene process using top-cut dual stress liners on (100) substrates," *IEDM Tech. Dig.*, pp. 293–296, 2007.

- 19. A. Pouydebasque, et al., "High density and high speed SRAM bit-cells and ring oscillators due to laser annealing for 45 nm bulk CMOS," *IEDM Tech. Dig.*, pp. 663–666, 2005.

- 20. W.-H. Lee, et al., "High performance 65 nm SOI technology with enhanced transistor strain and advanced-low-*k* BEOL," *IEDM Tech. Dig.*, pp. 56–59, 2005.

- S. Tyagi, et al., "An advanced low power, high performance, strained channel 65 nm technology," *IEDM Tech. Dig.*, pp. 1070–1072, 2005.

- 22. M. Rodder, et al., "Oxide thickness dependence of inverter delay and device reliability for 0.25 μm CMOS technology," *IEDM Tech. Dig.*, pp. 879–882, 1993.

- M. Rodder, A. Amerasekera, S. Aur, and I. C. Chen, "A study of design/process dependence of 0.25 μm gate length CMOS for improved performance and reliability," *IEDM Tech. Dig.*, pp. 71–74, 1994.

- M. Rodder, S. Aur, and I.-C. Chen, "A scaled 1.8 V, 0.18 μm gate length CMOS technology: Device design and reliability considerations," *IEDM Tech. Dig.*, pp. 415–418, 1995.

- M. Rodder, et al., "A 1.2 V, 0.1 μm gate length CMOS technology: Design and process issues," *IEDM Tech. Dig.*, pp. 623–626, 1998.

- M. Mehrotra, et al., "A 1.2 V, sub-0.09 μm gate length CMOS technology," *IEDM Tech. Dig.*, pp. 419–422, 1999.

- 27. A. H. Perera, et al., "A versatile 0.13 μm CMOS platform technology supporting high performance and low power applications," IEDM Tech. Dig., pp. 571–574, 2000.

- N. Yanagiya, et al., "65 nm CMOS technology (CMOS5) with high density embedded memories for broadband microprocessor applications," *IEDM Tech. Dig.*, pp. 57–60, 2002.

- 29. S. Thompson, et al., "A 90 nm logic technology featuring 50 nm strained silicon channel transistors, 7 layers of Cu interconnects, low-k ILD, and 1μm<sup>2</sup> SRAM cell," *IEDM Tech. Dig.*, pp. 61–64, 2002.

- 30. P. Bai, et al., "A 65 nm logic technology featuring 35 nm gate lengths, enhanced channel strain, 8 Cu interconnect layers, low-k ILD and 0.57 pmZ SRAM Cell," *IEDM Tech. Dig.*, pp. 657–660, 2004.

- 31. B. H. Calhoun, Y. Cao, X. Li, K. Mai, L. T. Pileggi, R. A. Rutenbar, and K. L. Shepard, "Digital circuit design challenges and opportunities in the era of nanoscale CMOS," *Proceedings of the IEEE*, vol. 96, no. 2, pp. 343–365, February 2008.

- 32. S. Jha, "Challenges on design complexities for advanced wireless silicon systems," *Design Automation Conference*, 2008.

- W. Zhao, Y. Cao, "New generation of predictive technology model for sub-45 nm early design exploration," *IEEE Transactions on Electron Devices*, vol. 53, no. 11, pp. 2816–2823, November 2006.

# Chapter 2 Predictive Technology Model of Conventional CMOS Devices

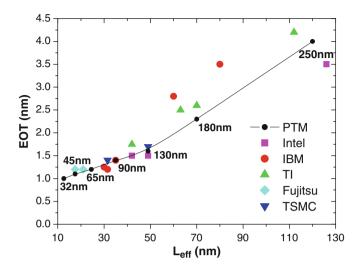

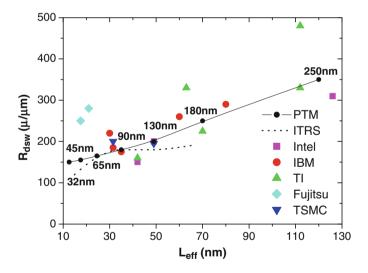

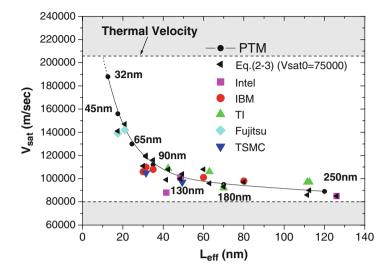

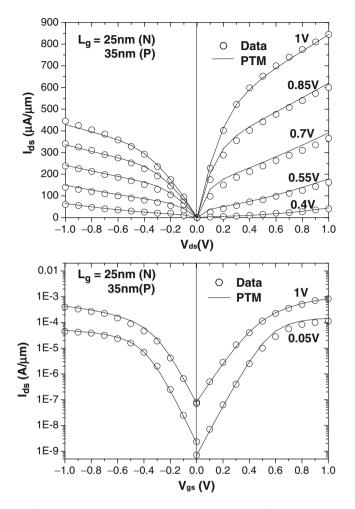

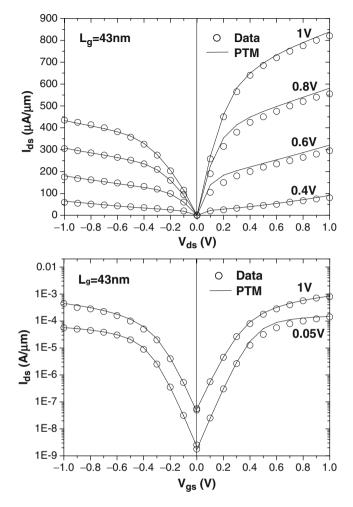

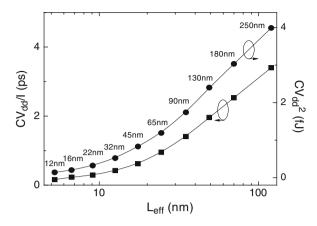

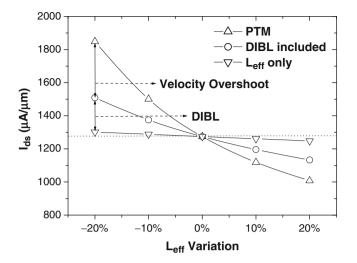

Bulk CMOS has been the dominant device structure for integrated circuit design during the past decades, because of its excellent scalability. It is expected that such a device type will continue toward the 10 nm regime. To efficiently predict the characteristics of future bulk CMOS, the scaling trends of primary model parameters, such as the threshold voltage and gate dielectric thickness, need to be identified; their association in determining major device characteristics should be well included for accurate model projection. In this chapter, a new generation of Predictive Technology Model (PTM) for conventional CMOS technology is presented to accomplish these goals. Based on a set of essential device models and early stage silicon data, PTM of bulk CMOS is successfully generated down to the 12 nm node. The accuracy of PTM predictions is comprehensively verified with published silicon data: the error of  $I_{on}$  is below 10% for both NMOS and PMOS devices. By tuning only ten primary model parameters, Furthermore, PTM correctly captures the sensitivity to process variations.

#### 2.1 PTM in Light of CMOS Scaling

The relentless scaling of CMOS technology has accelerated in recent years and will arguably continue toward the 10 nm regime [1]. In the nanometer era, physical factors that previously had little or no impact on circuit performance are now becoming increasingly significant. Particular examples include process variations, transistor mobility degradation, and power consumption. These new effects pose dramatic challenges to robust circuit design and system integration. To continue the design success and make an impact on leading products, advanced circuit design exploration must start in parallel with, or even earlier than silicon development. This new design paradigm demands predictive MOSFET models that are reasonably accurate, scalable with main process and design knobs, and correctly capture those emerging physical effects.

Fig. 2.1 A simple method fails the I-V prediction (Adapted from [8])

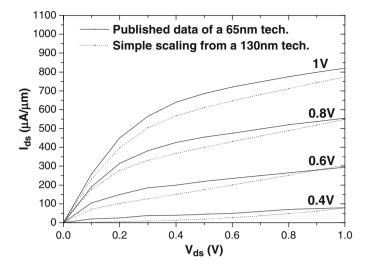

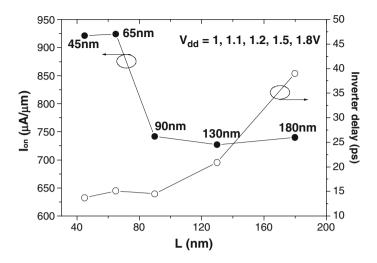

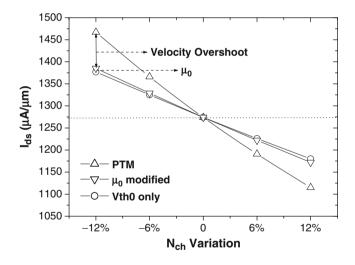

To predict future technology characteristics, an intuitive approach would simply scale down the geometry and voltages from an existing technology. For instance, based on the standard MOSFET model, BSIM4 [2], we can shrink the parameters of effective gate length ( $L_{eff}$ ), equivalent electrical oxide thickness ( $T_{oxe}$ ), threshold voltage ( $V_{th0}$ ), drain and source paratactic resistance ( $R_{dsw}$ ), and supply voltage ( $V_{dd}$ ) to the target values, while keeping all the other parameters unchanged. However, as shown in Fig. 2.1, this approach is too simple to capture the basic MOSFET behavior. In Fig. 2.1, the I-V characteristics of a preliminary 65 nm technology are predicted based on a well-characterized 130 nm technology by scaling  $L_{eff}$ ,  $T_{ox}$ ,  $V_{th0}$ ,  $R_{dsw}$  and  $V_{dd}$ . Compared to published measurement data, this simple prediction underestimates the overall performance. This observation matches the fact that during technology scaling, process developers will optimize many other aspects of the device beyond simple geometry scaling, in order to meet all performance criteria.

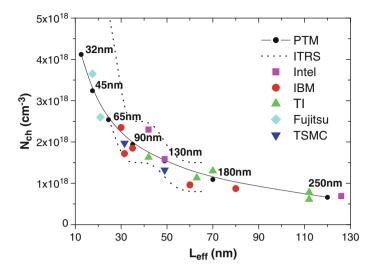

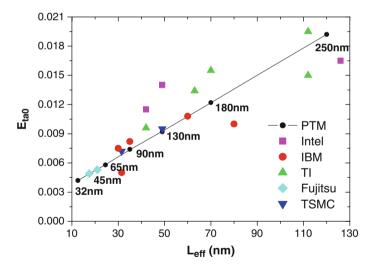

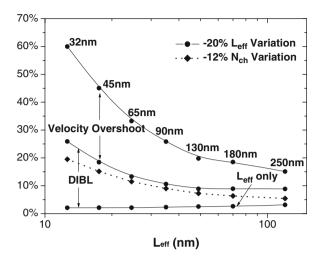

An improved predictive method was presented by Berkeley Predictive Technology Model (BPTM) [3]. Based on BSIM3 model, BPTM includes more physical parameters into the prediction. Their values are empirically extracted from published data during early stage technology development. Although BPTM provides reasonable models for technology nodes from 180 to 45 nm, its empirical nature constrains the physicality and scalability of the predictions. As the model file for each technology node is independently fitted, the overall scaling trend is not smooth from BPTM, as shown in Fig. 2.2. Furthermore, intrinsic correlations among physical parameters are not sufficiently considered. For instance, the scaling of V<sub>th0</sub> not only requires the change of channel doping (N<sub>ch</sub>), but further affects other physical parameters, such as mobility ( $\mu_0$ ), saturation velocity (V<sub>sat</sub>), the body effect, etc. Insufficient modeling of these correlations limits the prediction accuracy

Fig. 2.2 The prediction in BPTM is not smooth with scaling (Adapted from [8])

of process sensitivities. As process variations become increasingly significant in scaled CMOS technology, it is critical to include these parameter correlations into future predictive models, such that robust circuit design can be correctly guided [4].

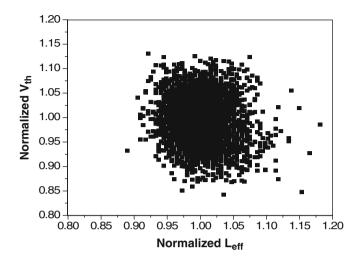

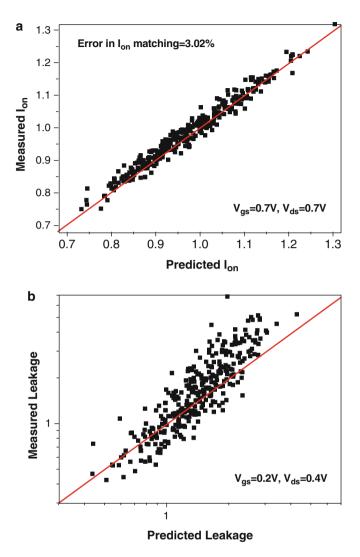

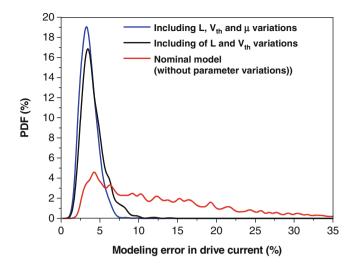

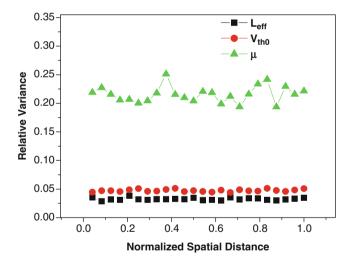

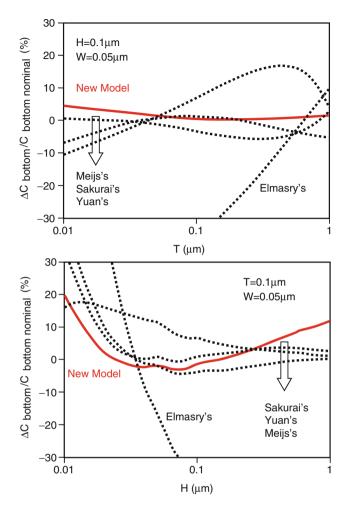

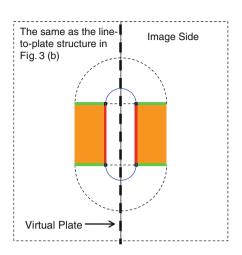

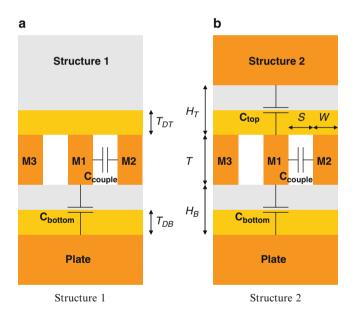

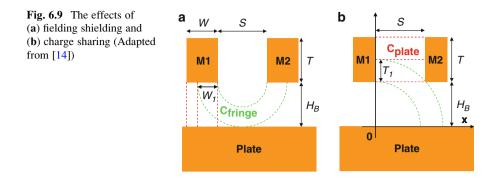

In this context, a new generation of PTM is developed to overcome these shortcomings. Two cornerstones ensure the accurate and smooth prediction: