**METRIC**

MIL-HDBK-62 13 September 1996

# DEPARTMENT OF DEFENSE HANDBOOK

# DOCUMENTATION OF DIGITAL ELECTRONIC SYSTEMS WITH VHDL

This handbook is for guidance only.

Do not cite this document as a requirement.

AMSC/NA FSC 5962

<u>DISTRIBUTION STATEMENT A.</u> Approved for public release; distribution is unlimited.

# **FOREWORD**

- 1. This handbook is approved for use by all Departments and Agencies of the Department of Defense (DoD).

- 2. This handbook is for guidance only. This handbook cannot be cited as a requirement. If it is, the contractor does not have to comply.

- 3. This handbook was developed to provide guidance to Department of Defense personnel who are writing requests for proposals for military digital electronic systems, DoD contractors who are developing very high-speed integrated circuit (VHSIC) hardware description language (VHDL) models for the Government, and DoD engineers, scientists, and management or independent validation and verification contractors who are evaluating or reviewing models delivered to the Government. It documents the state of the art and existing technologies for VHDL model development. Addressed in the handbook are which VHDL models are required to be delivered with a contract, which VHDL models should be developed during the different stages of the lifetime of a system, and how VHDL models can be structured to be consistent with modeling standards.

- 4. This handbook was developed under the auspices of the US Army Materiel Command's Engineering Design Handbook Program, which is under the direction of the US Army Industrial Engineering Activity. Research Triangle Institute (RTI) was the prime contractor for this handbook under Contract No. DAAA09-86-D-0009. The handbook was authored by Dr. Geoffrey A. Frank and edited by Ray C. Anderson of RTI. Development of this handbook was guided by a technical working group that included Mr. Gerald T. Michael, US Army Research Laboratory, chairman; Dr. John W. Hines, US Air Force Wright Laboratory; Mr. J. P. Letellier, US Naval Research Laboratory; and Mr. Michael A. Frye, US Department of Defense, Defense Logistics Agency.

- 5. Beneficial comments (recommendations, additions, deletions) and any pertinent data that may be of use in improving this document should be addressed to Defense Supply Center Columbus, ATTN: Director-VA, 3990 East Broad Street, Columbus, OH 43216-5000, by using the Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document or by letter.

The following is included at the request of IEEE:

"The Institute of Electrical and Electronics Engineers, Inc. (IEEE) disclaims any responsibility or liability resulting from the placement and use in this publication of material extracted from its publications. Information is reprinted with permission of the IEEE."

ii

# **CONTENTS**

| FOREWORD                                                        |      |

|-----------------------------------------------------------------|------|

| LIST OF ILLUSTRATIONS                                           | ix   |

| LIST OF TABLES                                                  |      |

| LIST OF ABBREVIATIONS AND ACRONYMS                              | xii  |

| CHAPTER 1                                                       |      |

| INTRODUCTION                                                    |      |

| 1-1 PURPOSE                                                     | 1-1  |

| 1-2 SCOPE                                                       | 1-1  |

| 1-3 INTENDED AUDIENCE                                           | 1-1  |

| 1-4 HISTORY, PURPOSE, AND SCOPE OF VHDL                         | 1-2  |

| 1-4.1 HISTORY OF VHDL                                           | 1-2  |

| 1-4.2 THE PURPOSE OF VHDL                                       | 1-2  |

| 1-4.3 THE SCOPE OF VHDL                                         | 1-3  |

| 1-5 RELATED INDUSTRY STANDARDS                                  | 1-3  |

| 1-6 OVERVIEW                                                    | 1-3  |

| REFERENCES                                                      | 1-4  |

| BIBLIOGRAPHY                                                    | 1-5  |

| CHADTED 2                                                       |      |

| CHAPTER 2 HARDWARE DESCRIPTION CONCEPTS                         |      |

| 2-1 INTRODUCTION                                                | 2.1  |

| 2-2 LEVELS OF ABSTRACTION IN MODELS OF DIGITAL ELECTRONIC SYSTI |      |

| 2-2.1 OVERVIEW                                                  |      |

| 2-2.1 OVEKVIEW  2-2.2 NETWORK MODELS                            |      |

| 2-2.2.1 Performance Models                                      |      |

| 2-2.2.2 Interface models                                        |      |

| 2-2.3 ALGORITHMIC MODELS                                        |      |

| 2-2.4 INSTRUCTION SET ARCHITECTURE MODELS                       |      |

| 2-2.5 REGISTER-TRANSFER MODELS                                  |      |

| 2-2.6 GATE-LEVEL MODELS                                         |      |

| 2-2.7 USES OF ABSTRACTION AND HIERARCHICAL DECOMPOSITION        |      |

| PROCESS                                                         |      |

| 2-3 BEHAVIORAL DESCRIPTIONS OF HARDWARE DESIGNS                 |      |

| 2-3.1 THE PURPOSE OF BEHAVIORAL DESCRIPTIONS                    |      |

| 2-3.2 THE USE OF HIERARCHY IN BEHAVIORAL DESCRIPTIONS           |      |

| 2-3.3 EXAMPLE OF A BEHAVIORAL DESCRIPTION                       |      |

| 2-4 STRUCTURAL DESCRIPTIONS OF HARDWARE DESIGNS                 |      |

| 2-4.1 THE PURPOSE OF STRUCTURAL DESCRIPTIONS                    | 2-12 |

| 2-4.2 THE USE OF HIERARCHY IN STRUCTURAL DESCRIPTIONS           | 2-13 |

| 2-4.2.1 Hierarchical Decomposition Based on Physical Elements   | 2-13 |

| 2-4.2.2 Leaf Modules in a Hierarchical Structural Description   |      |

| 2-4.3 EXAMPLES OF STRUCTURAL DESCRIPTIONS                       | 2-14 |

| 2-4.3.1 Algorithmic-Level Structural Description                | 2-14 |

| 2-4.3.2 Register-Transfer-Level Structural Description          | 2-20 |

| 2-5 MIXED ABSTRACTION MODELS                                    | 2-22 |

| 2-5.1 THE PURPOSE OF MIXED LEVEL OF ABSTRACTION MODELS          | 2-22 |

| 2-5.2 DESIGNING MODULES FOR MIXED ABSTRACTION MODELS            |      |

| 2-5.3 AN EXAMPLE OF A MIXED LEVEL OF ABSTRACTION MODEL          | 2-23 |

| REFERENCES                                                      |      |

| BIBLIOGRAPHY                                                    |      |

# CHAPTER 3 VHDL CONCEPTS

| 3-1 | INTRODUCTION                                                           | 3-1  |

|-----|------------------------------------------------------------------------|------|

| 3-2 | BASIC VHDL CONCEPTS                                                    | 3-1  |

|     | 3-2.1 VHDL DESIGN ENTITIES                                             | 3-1  |

|     | 3-2.1.1 Entity Interfaces                                              |      |

|     | 3-2.1.2 Architecture Bodies                                            |      |

|     | 3-2.2 THE VHDL CONCEPT OF TIME                                         |      |

|     | 3-2.3 SIGNALS                                                          |      |

|     | 3-2.3.1 Signal Assignment Statements                                   |      |

|     | 3-2.3.2 Resolution Functions                                           |      |

| 3-3 | VHDL SUPPORT FOR BEHAVIORAL DESIGN                                     |      |

| 5-5 | 3-3.1 PROCESSES                                                        |      |

|     | 3-3.2 WAIT STATEMENTS                                                  |      |

|     | 3-3.3 A BEHAVIORAL DESIGN EXAMPLE                                      |      |

| 3-4 | VHDL SUPPORT FOR STRUCTURAL DESIGN                                     |      |

| 3-4 | 3-4.1 STRUCTURAL ARCHITECTURE BODIES                                   |      |

|     |                                                                        |      |

|     | 3-4.2 COMPONENTS                                                       |      |

|     | 3-4.2.1 Component Declarations                                         |      |

|     | 3-4.2.2 Component Instantiations and Interconnections                  |      |

|     | 3-4.3 A STRUCTURAL DESIGN EXAMPLE                                      |      |

| 3-5 | VHDL SUPPORT FOR DATA ABSTRACTION                                      |      |

|     | 3-5.1 USER-DEFINED TYPES                                               |      |

|     | 3-5.2 TYPE CONVERSION FUNCTIONS                                        |      |

|     | 3-5.3 OVERLOADED OPERATORS                                             |      |

| 3-6 | VHDL SUPPORT FOR ANNOTATING MODELS                                     |      |

|     | 3-6.1 ATTRIBUTES                                                       |      |

|     | 3-6.2 GENERIC CONSTANTS                                                |      |

|     | 3-6.3 PHYSICAL TYPES                                                   |      |

| 3-7 | ERROR HANDLING WITH VHDL                                               |      |

|     | 3-7.1 ASSERTION STATEMENTS                                             |      |

|     | 3-7.2 HANDLING SIGNAL ERROR STATES                                     |      |

| 3-8 | VHDL SUPPORT FOR SHARING AND REUSE                                     |      |

|     | 3-8.1 VHDL DESIGN LIBRARIES                                            | 3-16 |

|     | 3-8.1.1 Declaring and Using Libraries                                  | 3-16 |

|     | 3-8.1.2 Constructing Libraries                                         | 3-19 |

|     | 3-8.2 VHDL PACKAGES                                                    | 3-20 |

|     | 3-8.2.1 Constructing VHDL Packages                                     | 3-20 |

|     | 3-8.2.2 Declaring and Using Packages                                   |      |

|     | 3-8.3 CONFIGURATION SPECIFICATIONS AND DECLARATIONS                    |      |

|     | 3-8.3.1 Constructing Configuration Specifications and Declarations     |      |

|     | 3-8.3.2 Using Configuration Specifications and Declarations            |      |

| REF | ERENCES                                                                |      |

|     | LIOGRAPHY                                                              |      |

| 212 |                                                                        |      |

|     | CHAPTER 4                                                              |      |

|     | DoD REQUIREMENTS FOR THE USE OF VHDL                                   |      |

| 4-1 | INTRODUCTION                                                           | 4-1  |

| 4-2 | MIL-HDBK-454 GUIDELINES FOR THE USE OF VHDL                            |      |

|     | 4-2.1 DOCUMENTATION OF ASICs DEVELOPED FOR THE GOVERNMENT WITH VHDL    | 4-1  |

|     | 4-2.2 DOCUMENTATION OF QUALIFIED DIGITAL INTEGRATED CIRCUITS WITH VHDL | 4-2  |

|     | 4-2.3 THE LIBRARY OF VHDL DESCRIPTIONS OF STANDARD DIGITAL PARTS       |      |

|     | 4-2.4 TEST BENCH REQUIREMENTS FOR VHDL DESCRIPTIONS                    | 4-2  |

| 4-3 | OVERVIEW OF THE VHOL DATA ITEM DESCRIPTION                             |      |

|     | 4-3.1 ENTITY INTERFACE REQUIREMENTS                                    | 4-3  |

|            | 4-3.1.1 Entity Names                                                                   |      |

|------------|----------------------------------------------------------------------------------------|------|

|            | 4-3.1.2 Input and Output Definitions                                                   |      |

|            | 4-3.2 BEHAVIORAL DESCRIPTIONS                                                          |      |

|            | 4-3.2.1 Functional Decomposition                                                       |      |

|            | 4-3.2.2 Timing Descriptions                                                            |      |

|            | 4-3.3 STRUCTURAL DESCRIPTIONS                                                          |      |

|            | 4-3.3.1 Acceptable Primitive Elements                                                  |      |

|            | 4-3.3.2 Testability Requirements                                                       |      |

|            | 4-3.4 TEST BENCH REQUIREMENTS                                                          |      |

|            | 4-3.4.1 Test Bench Functions                                                           |      |

|            | 4-3.4.2 Test Bench Relationships to Design Modules                                     |      |

|            | 4-3.5 ERROR MESSAGES                                                                   |      |

|            | 4-3.6 DOCUMENTATION FORMAT                                                             |      |

|            | 4-3.7 REQUIRED ANNOTATIONS OF VHDL MODULES                                             |      |

| DEE        | 4-3.8 AN EXAMPLE OF A TAILORED DID                                                     |      |

|            | ERENCES                                                                                |      |

| RIRI       | LIOGRAPHY                                                                              | 4-9  |

|            | CHAPTER 5                                                                              |      |

|            | CONSTRUCTION OF BEHAVIORAL VHDL MODELS                                                 |      |

| 5-1        | INTRODUCTION                                                                           | 5 1  |

| 5-1<br>5-2 | CREATION OF VHDL BEHAVIORAL MODELS                                                     |      |

| 3-2        | 5-2.1 CONSTRUCTING PERFORMANCE MODELS                                                  |      |

|            | 5-2.1 CONSTRUCTING FERFORMANCE MODELS                                                  |      |

|            | 5-2.1.2 Modeling Tilling in Performance- and Algorithmic-Level Behavioral Models       |      |

|            | 5-2.2 CONSTRUCTING ALGORITHMIC MODELS                                                  |      |

|            | 5-2.2 CONSTRUCTING ALGORITHMIC MODELS  5-2.2.1 Modeling Algorithms With VHDL Processes |      |

|            | 5-2.2.2 An Example of an Algorithmic Model                                             |      |

|            | 5-2.3 CONSTRUCTING INSTRUCTION-SET-ARCHITECTURE-LEVEL MODELS                           |      |

|            | 5-2.3.1 Modeling Processors                                                            |      |

|            | 5-2.3.2 Modeling Memory                                                                |      |

|            | 5-2.3.3 Modeling Busses and Bus Controllers                                            |      |

|            | 5-2.4 CONSTRUCTING REGISTER-TRANSFER-LEVEL MODELS                                      |      |

|            | 5-2.4.1 Synthesis of Designs From RTL Models                                           |      |

|            | 5-2.4.2 An Example of a VHDL Register-Transfer-Level Model                             |      |

| 5-3        | VHDL DID SIMULATION REQUIREMENTS FOR BEHAVIORAL MODELS                                 |      |

|            | 5-3.1 CORRECT FUNCTIONAL RESPONSE TO STIMULI                                           |      |

|            | 5-3.2 SIMULATION TIMING                                                                |      |

|            | 5-3.3 ERROR HANDLING                                                                   | 5-21 |

| 5-4        | TIMING IN BEHAVIORAL MODELS                                                            | 5-22 |

|            | 5-4.1 TIMING SHELLS                                                                    | 5-22 |

|            | 5-4.2 CLOCK RATES                                                                      | 5-24 |

|            | 5-4.3 CRITICAL PATH DELAY TIMES                                                        | 5-24 |

|            | 5-4.4 BEST-CASE, WORST-CASE, AND NOMINAL DELAYS                                        | 5-24 |

|            | 5-4.5 PARAMETERIZED DELAY MODELS                                                       | 5-24 |

|            | 5-4.6 TIMING DEFINITION PACKAGE                                                        | 5-26 |

|            | 5-4.7 TIMING THROUGH FILE INPUT                                                        | 5-31 |

|            | 5-4.8 MODELING ASYNCHRONOUS TIMING                                                     | 5-32 |

|            | 5-4.9 MODELING SYNCHRONOUS TIMING                                                      | 5-33 |

| 5-5        | ANNOTATION OF BEHAVIORAL MODELS                                                        | 5-36 |

|            | 5-5.1 DESCRIPTION OF FUNCTION                                                          | 5-36 |

|            | 5-5.2 DESCRIPTION OF RESTRICTIONS                                                      | 5-36 |

|            | 5-5.3 MODELING APPROACH                                                                | 5-36 |

|            | 5-5.4 REVISION HISTORY                                                                 |      |

|            | 5-5.5 BACK ANNOTATION OF TIMING INFORMATION                                            | 5-37 |

|            | USE OF STRUCTURAL HIERARCHY IN BEHAVIORAL MODELS                         |      |

|------------|--------------------------------------------------------------------------|------|

|            | TERENCES                                                                 |      |

| BIB        | LIOGRAPHY                                                                | 5-38 |

|            | CHAPTED (                                                                |      |

|            | CHAPTER 6 CONSTRUCTION OF STRUCTURAL VHDL MODELS                         |      |

|            |                                                                          |      |

| 6-1        | INTRODUCTION                                                             |      |

| 6-2        | CILLITION OF BIRCOTORE VIEW TOPPLES                                      |      |

|            | 6-2.1 TRANSLATION OF SCHEMATIC CAPTURE MODELS                            |      |

|            | 6-2.2 SYNTHESIS OF STRUCTURAL MODELS FROM REGISTER-TRANSFER-LEVEL MODELS |      |

|            | 6-2.3 SYNTHESIS OF STRUCTURAL MODELS FROM FINITE STATE MACHINES          |      |

| <i>c</i> 2 | 6-2.4 ENHANCEMENT OF GATE-LEVEL MODELS WITH GENERATED STRUCTURE          |      |

| 6-3        | VHDL DID ORGANIZATIONAL REQUIREMENTS FOR STRUCTURAL MODELS               |      |

|            | 6-3.1 HIERARCHICAL ORGANIZATION OF STRUCTURAL MODELS                     |      |

|            | 6-3.2 ALLOWABLE LEAF-LEVEL MODULES                                       |      |

|            | 6-3.2.1 Government-Approved Models                                       |      |

|            | 6-3.2.2 Modules With Stimulus-Response Behavior                          |      |

|            | 6-3.2.3 Modules Without Detailed Designs                                 |      |

|            |                                                                          |      |

|            | 6-3.3.1 Physical View Requirements                                       |      |

|            | 6-3.3.2 Electrical View Requirements                                     |      |

| 6-4        | 6-3.3.3 Timing View Requirements                                         |      |

| 0-4        | 6-4.1 SUPPORT FOR LOGIC-LEVEL FAULT MODELING                             |      |

|            | 6-4.2 SUPPORT FOR TEST VECTOR GENERATION                                 |      |

| 6-5        | TIMING SPECIFICATIONS FOR STRUCTURAL MODELS                              |      |

| 6-6        | BACK ANNOTATION OF STRUCTURAL MODELS                                     |      |

| 0-0        | 6-6.1 BACK ANNOTATION OF TIMING INFORMATION                              |      |

|            | 6-6.2 BACK ANNOTATION OF TIMING INFORMATION                              |      |

|            | 6-6.3 BACK ANNOTATION OF TESTABILITY INFORMATION                         |      |

| DEE        | ERENCES                                                                  |      |

|            | LIOGRAPHY                                                                |      |

| DID        | LIOURATITI                                                               | 0-13 |

|            | CHAPTER 7                                                                |      |

|            | PREPARATION OF VHDL MODELS FOR SIMULATION                                |      |

| 7-1        | INTRODUCTION                                                             | 7_1  |

|            | INTEROPERABILITY OF MODELS                                               |      |

| 1-2        | 7-2.1 USE OF STANDARD SIGNAL DATA TYPES                                  |      |

|            | 7-2.2 TYPE CONVERSION FOR DIFFERENT SIGNAL DATA TYPES                    |      |

|            | 7-2.3 INTEROPERABILITY OF TIMING MODELS                                  |      |

|            | 7-2.4 PORTABILITY REQUIREMENTS FOR INTEROPERABLE VHDL MODELS             |      |

| 7-3        | TEST BENCH DEVELOPMENT                                                   | 7-3  |

| 13         | 7-3.1 WAVES                                                              |      |

|            | 7-3.1.1 Standard WAVES Packages                                          |      |

|            | 7-3.1.2 Local WAVES Packages                                             |      |

|            | 7-3.1.3 WAVES Test Suites                                                |      |

|            | 7-3.2 DOCUMENTATION OF TEST BENCHES                                      |      |

| 7-4        | TEST VECTOR DEVELOPMENT                                                  |      |

| , 4        | 7-4.1 BEHAVIOR TESTS                                                     |      |

|            | 7-4.2 PROPAGATION DELAY TESTS                                            |      |

|            | 7-4.3 ERROR CONDITION TESTS                                              |      |

|            | 7-4.3.1 Invalid Operating Condition Tests                                |      |

|            | 7-4.3.2 Invalid Input State Tests                                        |      |

|            | 7-4.3.3 Timing Constraint Violation Tests                                |      |

|            |                                                                          |      |

|     | 7-4.4 INTEROPERABILITY TESTS                                              |      |

|-----|---------------------------------------------------------------------------|------|

|     | 7-4.5 ORGANIZATION AND DOCUMENTATION OF TEST VECTORS                      | 7-13 |

| 7-5 | USE OF CONFIGURATION DECLARATIONS TO INSTANTIATE THE TEST BENCH           |      |

|     | FOR A MODEL                                                               | 7-14 |

|     | 7-5.1 SELECTION OF ALTERNATIVE DESIGN LIBRARIES                           | 7-14 |

|     | 7-5.2 SELECTION OF ALTERNATIVE ARCHITECTURES                              |      |

|     | 7-5.3 BINDING OF GENERICS                                                 | 7-15 |

|     | 7-5.4 PORT MAPPING                                                        | 7-15 |

| 7-6 | DEFINITION OF SIMULATOR OPTIONS                                           | 7-15 |

|     | 7-6.1 CONTROL OVER ENVIRONMENTAL PARAMETERS                               | 7-16 |

|     | 7-6.2 SELECTION OF DELAY TYPES                                            |      |

|     | 7-6.3 CONTROL OVER EXECUTION OF ASSERTIONS                                |      |

|     | 7-6.4 CONTROL OVER PROPAGATION OF UNKNOWN SIGNAL STATES                   | 7-16 |

| REF | FERENCES                                                                  | 7-17 |

| BIB | LIOGRAPHY                                                                 | 7-17 |

|     |                                                                           |      |

|     | CHAPTER 8                                                                 |      |

|     | MODELING TESTABILITY WITH VHDL MODELS                                     |      |

| 8-1 | INTRODUCTION                                                              |      |

| 8-2 |                                                                           |      |

| 8-3 | TESTABILITY DESIGN ISSUES                                                 |      |

|     | 8-3.1 TEST STRATEGIES AND TECHNIQUES FOR MAINTENANCE AND FAULT TOLERANCE. |      |

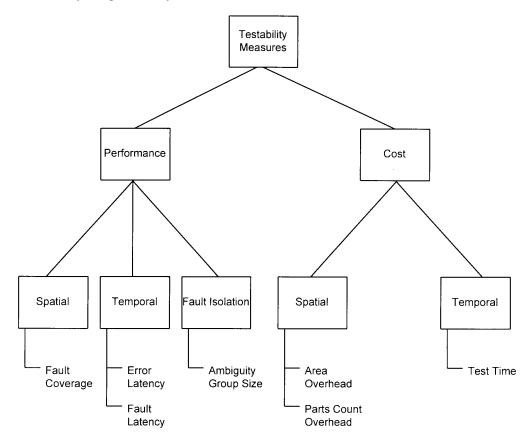

|     | 8-3.2 TESTABILITY MEASURES                                                | 8-3  |

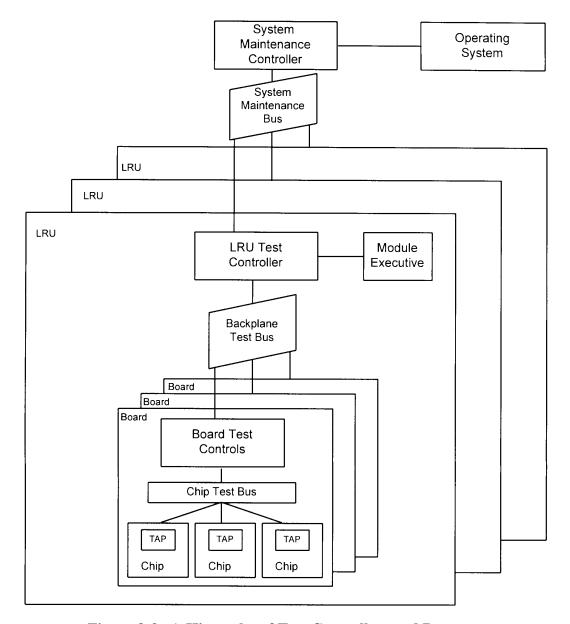

|     | 8-3.3 TEST STRUCTURE BOUNDARIES                                           | 8-4  |

|     | 8-3.4 TEST COMPONENTS AND INTERFACES                                      |      |

| 8-4 |                                                                           |      |

|     | 8-4.1 EVALUATING TEST STRATEGIES                                          | 8-6  |

|     | 8-4.2 MODELING TEST INTERFACES IN VHDL                                    | 8-7  |

|     | 8-4.3 MODELING TEST CONTROLLER FUNCTIONS                                  | 8-7  |

|     | 8-4.4 EVALUATION OF TEST COMMUNICATION AND STORAGE REQUIREMENTS FOR BIT   |      |

| 8-5 | MODELING TESTABILITY USING VHDL STRUCTURAL MODELS                         |      |

|     | 8-5.1 DESCRIPTION OF TEST CIRCUITRY GENERATED FROM STRUCTURAL INFORMATION |      |

|     | 8-5.2 SUPPORT FOR FAULT DICTIONARY GENERATION                             |      |

|     | 8-5.3 SUPPORT FOR AUTOMATIC TEST GENERATION                               |      |

|     | 8-5.4 SUPPORT FOR COVERAGE ANALYSIS                                       |      |

|     | 8-5.5 SUPPORT FOR TEST TIME COMPUTATION                                   |      |

| 8-6 | ANNOTATION OF VHDL MODELS WITH TESTABILITY INFORMATION                    |      |

|     | 8-6.1 ANNOTATION OF STRUCTURAL MODELS TO IDENTIFY LRUs                    |      |

|     | 8-6.2 ANNOTATION OF STRUCTURAL MODELS TO IDENTIFY FCRs                    |      |

|     | 8-6.3 BACK ANNOTATION WITH COVERAGE INFORMATION                           |      |

|     | FERENCES                                                                  |      |

| BIB | LIOGRAPHY                                                                 | 8-10 |

|     | CITA PUTED O                                                              |      |

|     | CHAPTER 9                                                                 |      |

|     | PREPARATION OF VHDL MODELS FOR DELIVERY TO THE DoD                        |      |

| 9-1 | INTRODUCTION                                                              |      |

| 9-2 |                                                                           |      |

|     | 9-2.1 LIST OF FILES                                                       |      |

|     | 9-2.2 DID OVERVIEW FILE                                                   |      |

|     | 9-2.3 VHDL ANALYSIS ORDER SPECIFICATION                                   |      |

|     | 9-2.4 GOVERNMENT-APPROVED LEAF MODULE VHDL DESCRIPTIONS                   |      |

|     | 9-2.5 REVISED VHDL MODULE LIST                                            |      |

|     | 9-2.6 ORIGINAL VHDL MODULE LIST                                           |      |

|     | 9-2.7 TEST BENCH CORRELATION LIST                                         |      |

|     | 9-2.8 AUXILIARY INFORMATION FILES                                         |      |

|     | 9-2.9 VHDL DESIGN UNIT FILES                                              | 9-4  |

| 9-3 | 1 122 1 11 11 10 001 1 21 1101 10 1111          |     |

|-----|-------------------------------------------------|-----|

|     | 9-3.1 NAMING VHDL DESIGN UNIT FILES             | 9-5 |

|     | 9-3.2 NAMING AUXILIARY FILES                    |     |

| 9-4 | SUGGESTED CODING CONVENTIONS FOR VHDL MODELS    | 9-6 |

|     | 9-4.1 DESIGN ENTITY NAMING CONVENTIONS          | 9-6 |

|     | 9-4.2 PORT-NAMING CONVENTIONS                   | 9-7 |

|     | 9-4.3 SIGNAL-NAMING CONVENTIONS                 | 9-7 |

|     | 9-4.4 PROCESS AND SUBPROGRAM NAMING CONVENTIONS | 9-7 |

|     | 9-4.5 COMMENTING CONVENTIONS FOR VHDL           | 9-7 |

|     | 9-4.5.1 Files                                   | 9-7 |

|     | 9-4.5.2 Packages                                | 9-7 |

|     | 9-4.5.3 Entity Interfaces                       | 9-7 |

|     | 9-4.5.4 Architecture Bodies                     | 9-8 |

|     | 9-4.5.5 Configuration Declarations              | 9-8 |

|     | 9-4.5.6 Internal Comments                       | 9-8 |

| REF | FERENCES                                        | 9-8 |

| BIB | SLIOGRAPHY                                      | 9-8 |

| APP | PENDIX A                                        | A-1 |

| APP | PENDIX B                                        | B-1 |

| GLC | OSSARY                                          | G-1 |

| IND | DEX                                             | I-1 |

|     | BJECT TERM (KEY WORD) LISTING                   |     |

|     |                                                 |     |

# LIST OF ILLUSTRATIONS

| Figui<br>No. | re<br>Description                                                                                           | Page |

|--------------|-------------------------------------------------------------------------------------------------------------|------|

|              |                                                                                                             | _    |

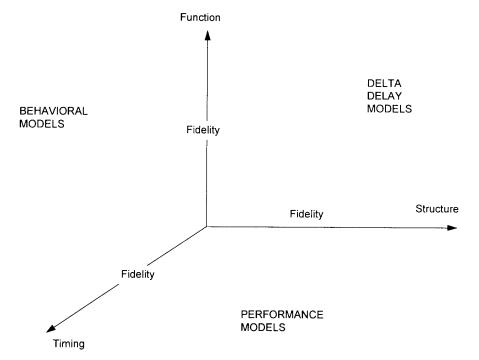

| 2-1          | Functional Models, Structural Models, and Levels of Abstraction                                             |      |

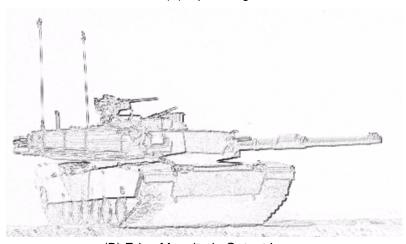

| 2-2          | Example Input Image and Edge Magnitude Output of an Edge Detection Processor                                |      |

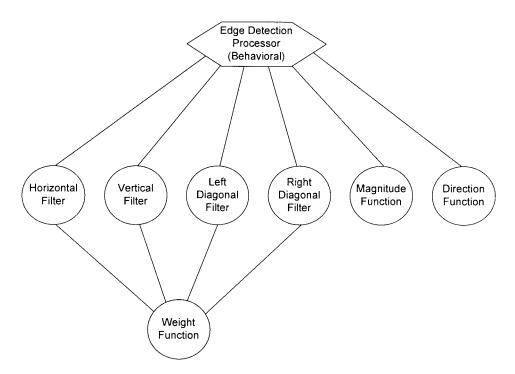

| 2-3          | Hierarchy of Functions in a Behavioral Model                                                                |      |

| 2-4          | Image Data Abstractions and Functions                                                                       |      |

| 2-5          | Interface Specifications for an Edge Detection Processor                                                    |      |

| 2-6          | Behavioral Model for an Edge Detection Processor                                                            |      |

| 2-7          | Example Functions for a Behavioral Model                                                                    |      |

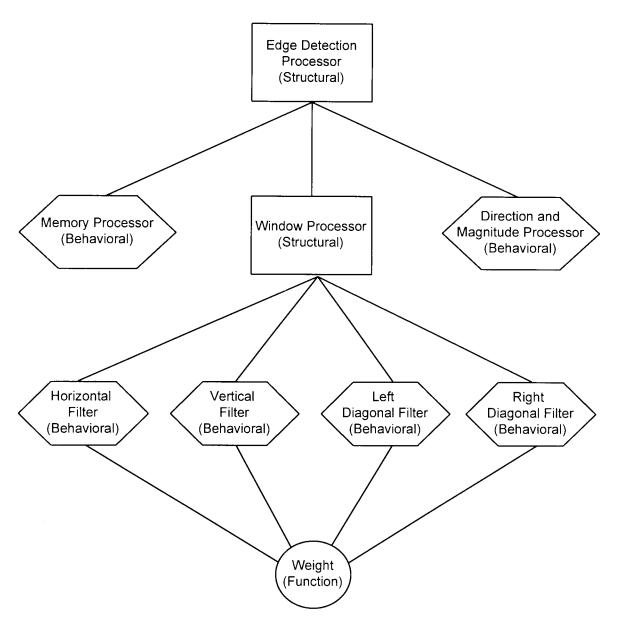

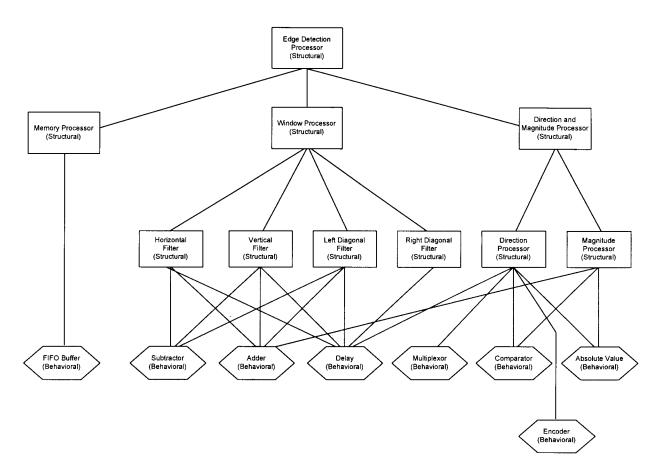

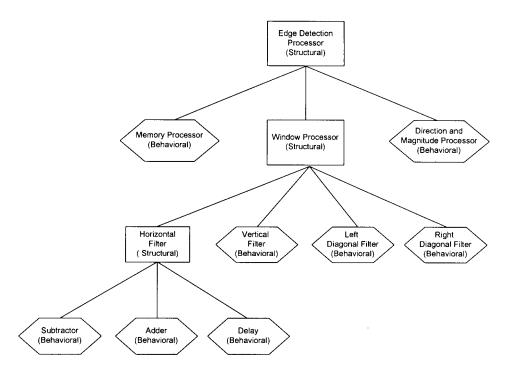

| 2-8          | Hierarchy of Components in an Algorithmic-Level Structural Model                                            |      |

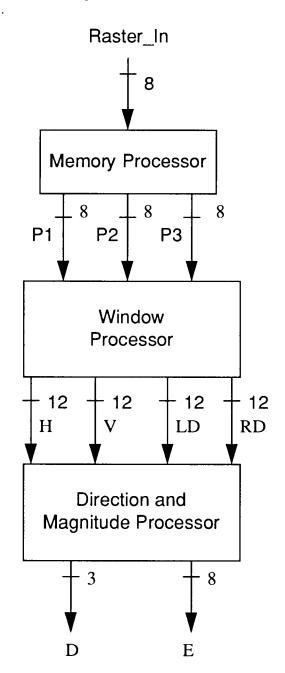

| 2-9          | A Hardware Block Diagram for the Edge Detection Processor  Structural Model for an Edge Detection Processor |      |

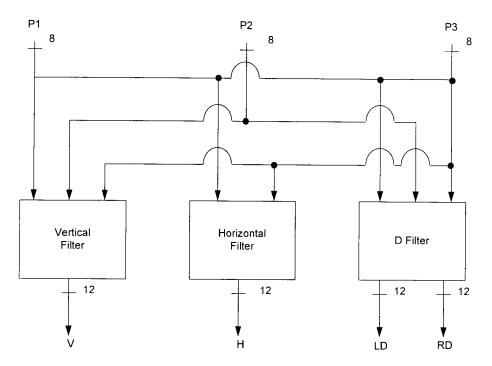

|              | A Hardware Block Diagram for the Window Processor of the Edge Detection Processor                           |      |

|              | VHDL Entity Interface for the Window Processor                                                              |      |

|              | VHDL Structural Architecture Body for the Window Processor                                                  |      |

|              | Interface for the Horizontal Filter                                                                         |      |

|              | Behavioral Model for the Horizontal Filter                                                                  |      |

|              | Hierarchy of Functions in a Structural Model                                                                |      |

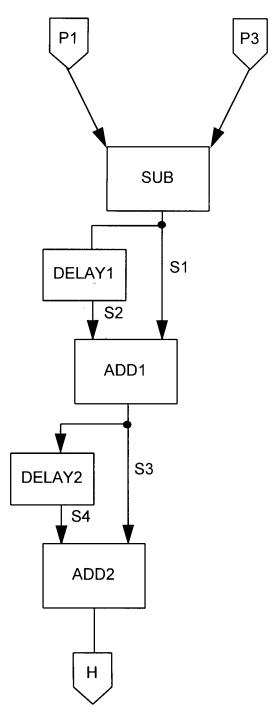

|              | Block Diagram of the Horizontal Filter Processor                                                            |      |

|              | Structural Architecture of the Horizontal Filter                                                            |      |

|              | Hierarchical Organization of a Mixed Level of Abstraction Model                                             |      |

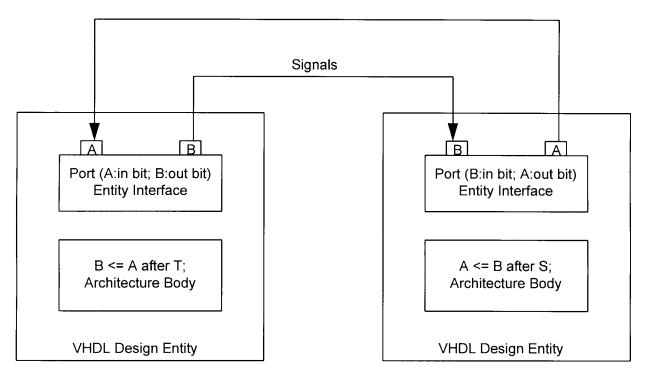

| 3-1          | Design Entities, Entity Interfaces, and Architecture Bodies                                                 |      |

| 3-2          | A VHDL Entity Interface Declaration                                                                         |      |

| 3-3          | Example Signal Assignment Statement                                                                         |      |

| 3-4          | Example of a Resolution Function                                                                            |      |

| 3-5          | Example of a Behavioral Model                                                                               |      |

| 3-6          | A Structural Architecture Body                                                                              |      |

| 3-7          | An Enumerated Type: The IEEE Std 1164 Unresolved Logic Data Type                                            |      |

| 3-8          | Entity Interface Declaration With Generic Constants and an Attribute                                        |      |

| 3-9          | Architecture Body Using an Attribute                                                                        |      |

|              | Example of a Physical Type Declaration                                                                      |      |

|              | An Assertion Statement                                                                                      |      |

|              | An Example of Error Propagation: IEEE Std 1164 AND Operator Table                                           |      |

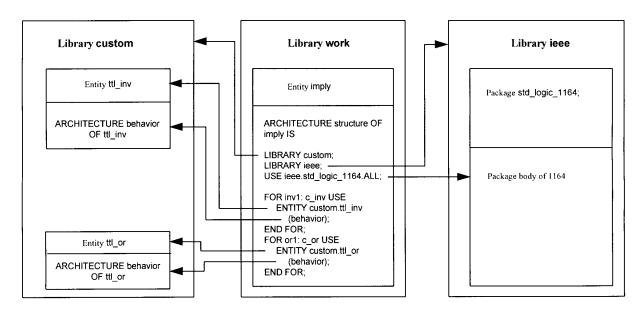

|              | Using a Component Library to Configure a Structural Architecture Body                                       |      |

|              | Use of Library and Use Clauses to Access External Libraries                                                 |      |

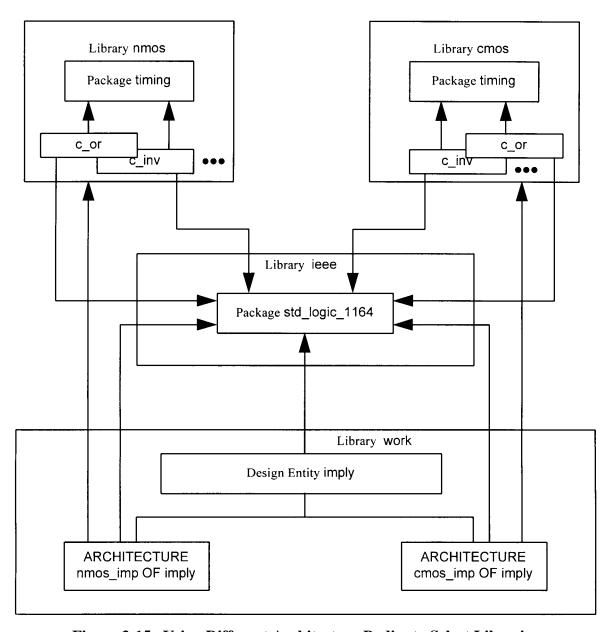

|              | Using Different Architecture Bodies to Select Libraries                                                     |      |

|              | Technology-Dependent Architecture Body Using Configuration Specifications                                   |      |

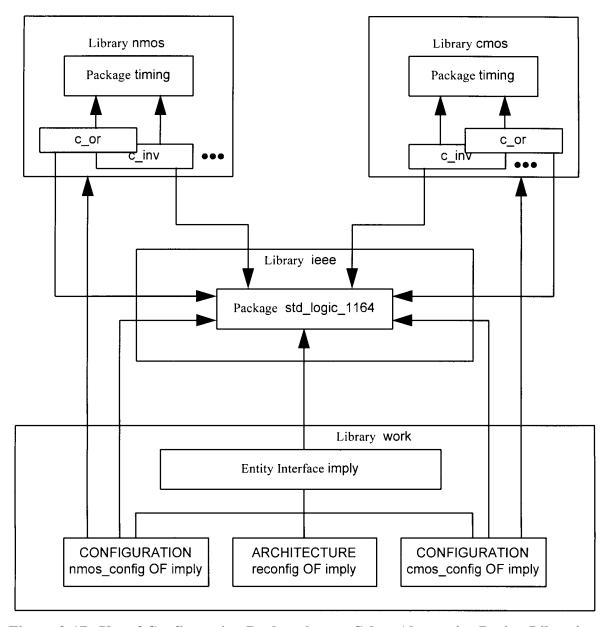

|              | Use of Configuration Declarations to Select Alternative Design Libraries                                    |      |

|              | A Reconfigurable Architecture Body                                                                          |      |

|              | Use of a Configuration Declaration to Select Design Entities From a Library                                 |      |

|              | Using a Configuration Declaration to Specify Generic Constant Values                                        |      |

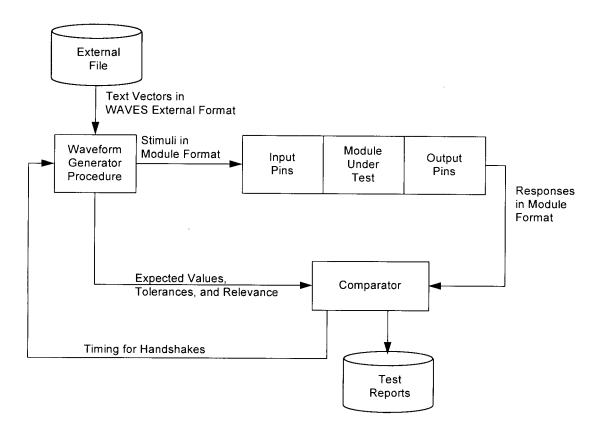

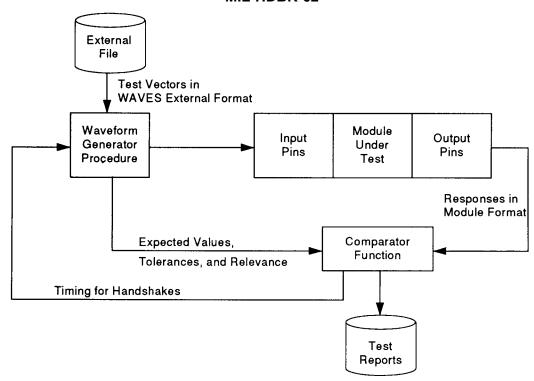

| 4-1          | Logical Structure of a VHDL Test Bench Constructed Using WAVES                                              |      |

| 5-1          | VHDL Package Interface for Statistics for Performance and Algorithmic Models                                | 5-3  |

| 5-2          | The Statistics Package Body for Performance and Algorithmic Models                                          |      |

| 5-3          | VHDL Data Type Definitions for a Performance and Algorithmic Model                                          | 5-5  |

| 5-4          | VHDL Entity Interface for a Performance and Algorithmic Model                                               | 5-5  |

| 5-5          | VHDL Architecture Body for an Algorithmic Model                                                             | 5-6  |

| 5-6          | Package Declaration for an Algorithmic Model of an FFT Processor                                            | 5-8  |

| 5-7          | Part of the Package Body for an Algorithmic Model of an FFT Processor                                       |      |

| 5-8          | The FFT Procedure in the Package Body for an Algorithmic Model of an FFT Processor                          |      |

| 5-9          | Package Declaration for an Instruction Set Architecture Processor Model                                     |      |

| 5-10         | Type Conversion Functions for an Instruction Set Architecture Processor Model                               | 5-13 |

| 5-11 | Operator Overloading Functions for an Instruction Set Architecture Processor Model | 5-14 |

|------|------------------------------------------------------------------------------------|------|

| 5-12 | Program Loading Procedure for an Instruction Set Architecture Processor Model      | 5-14 |

| 5-13 | Entity Interface for an Instruction Set Architecture Processor Model               | 5-15 |

| 5-14 | Architecture Body for an ISA-Level Processor Model                                 | 5-15 |

| 5-15 | Example Instruction Set Architecture Memory Model                                  | 5-17 |

|      | Example State Transition Diagram for a Bus Interface Unit Model                    |      |

| 5-17 | Entity Interface for an Intel Buffered Latch                                       | 5-20 |

| 5-18 | Synthesizable Architecture Body for the Intel Buffered Latch                       | 5-20 |

|      | Entity Interface and Architecture Body for a Functional Model Without Timing       |      |

| 5-20 | Package Declaration for a Model That Uses a Timing Shell                           | 5-22 |

|      | Function Definition for a Timing Function for a Floating Point Adder               |      |

| 5-22 | Entity Interface for a Model That Uses a Timing Shell                              | 5-23 |

| 5-23 | Timing Shell Architecture Body                                                     | 5-24 |

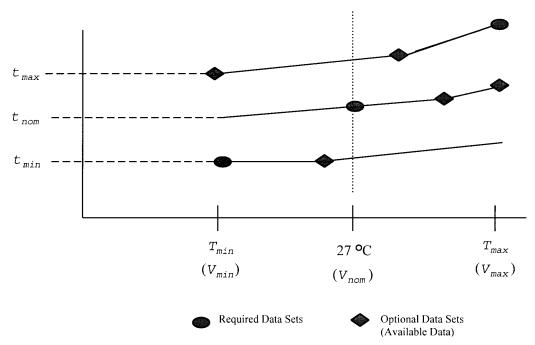

| 5-24 | Best-, Nominal-, and Worst-Case Timing Curves                                      | 5-25 |

| 5-25 | Package Declaration for a Model That Uses Parameterized Timing                     | 5-25 |

| 5-26 | Package Body for a Model That Uses Parameterized Timing                            | 5-26 |

| 5-27 | Entity Interface for a Model That Uses Parameterized Timing                        | 5-26 |

| 5-28 | Architecture Body for a Model That Uses Parameterized Timing                       | 5-27 |

| 5-29 | Package Interface for a Model That Uses a Timing Package                           | 5-28 |

| 5-30 | Package Body for a Model That Uses a Timing Package                                | 5-29 |

|      | Package Declaration for a Model That Uses File I/O for Timing                      |      |

|      | Package Body for a Model That Uses File I/O for Timing                             |      |

| 5-33 | Entity for a Module That Uses File I/O for Timing                                  | 5-32 |

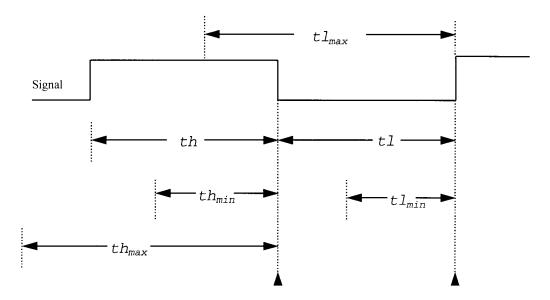

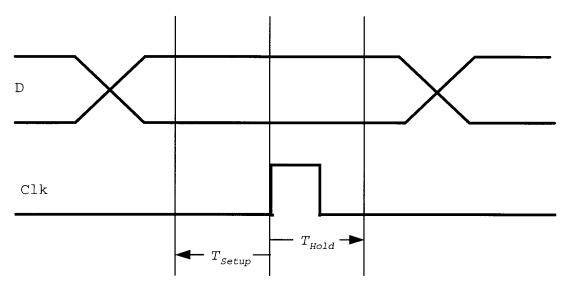

| 5-34 | Potential Asynchronous Timing Constraints                                          | 5-33 |

| 5-35 | Potential Synchronous Timing Constraints                                           | 5-33 |

| 5-36 | Package Interface That Checks Synchronous Timing Constraints                       | 5-34 |

| 5-37 | Procedure Body That Checks Setup Time Constraints                                  | 5-34 |

| 5-38 | Procedure Body That Checks Hold Time Constraints                                   | 5-35 |

| 5-39 | Entity Interface That Checks Timing Constraints                                    | 5-35 |

| 5-40 | Annotation of a VHDL Package Using Header Comments                                 | 5-36 |

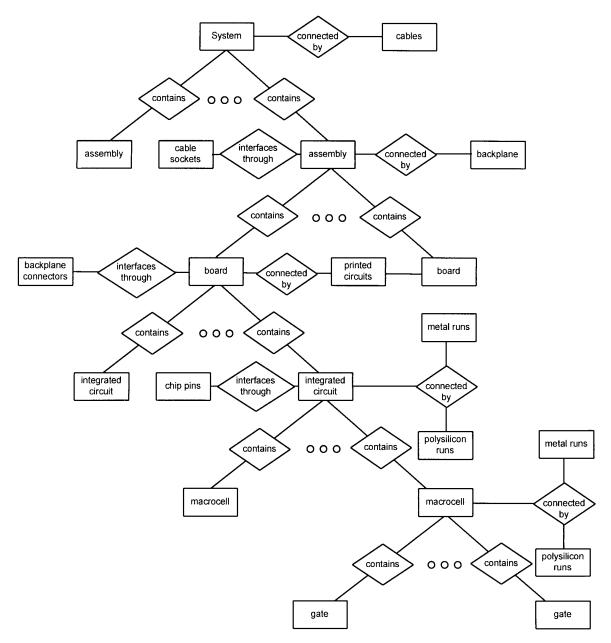

| 6-1  | Typical Physical Hierarchy of an Embedded Electronic System                        | 6-3  |

| 6-2  | EIA 567 Physical View Organization                                                 | 6-6  |

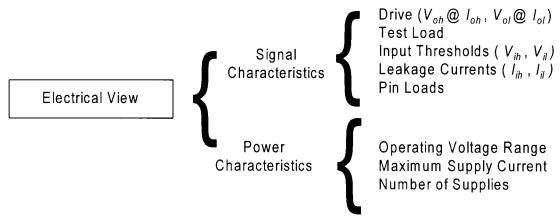

| 6-3  | EIA 567 Electrical View Organization                                               | 6-7  |

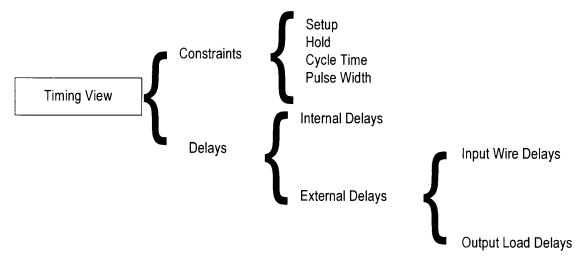

| 6-4  | EIA Timing View Organization                                                       | 6-7  |

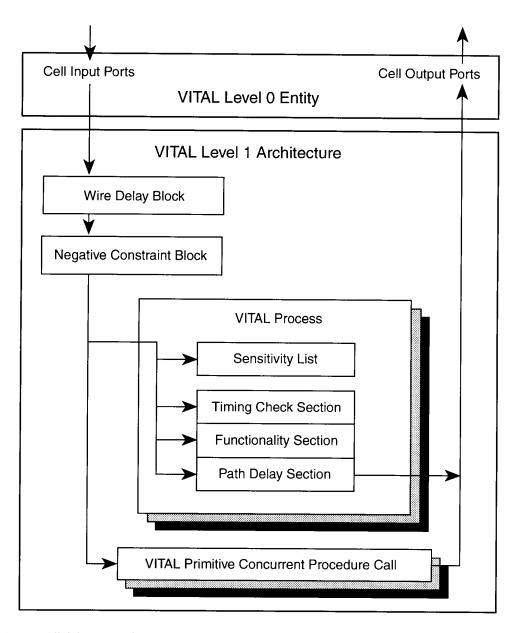

| 6-5  | VITAL Model Organization                                                           | 6-9  |

| 6-6  | Extrinsic Timing Delay VHDL Model                                                  | 6-11 |

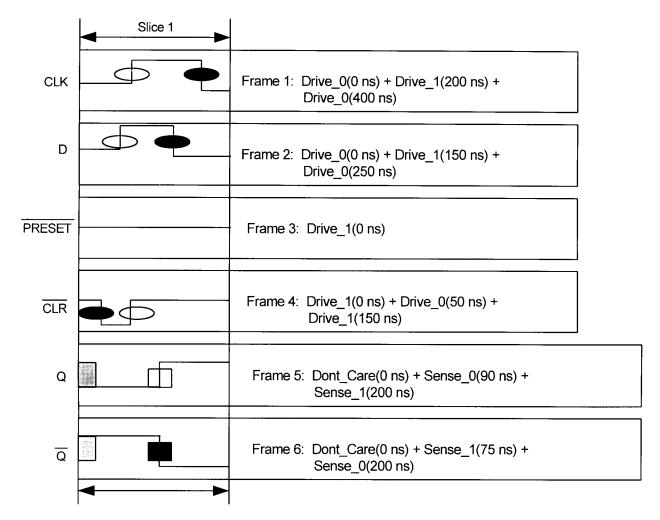

| 7-1  | Slice and Frames of a Waveform                                                     | 7-5  |

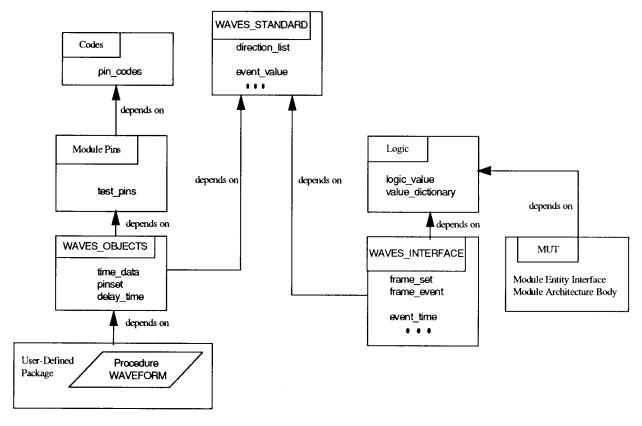

| 7-2  | Dependencies Between WAVES Packages                                                | 7-6  |

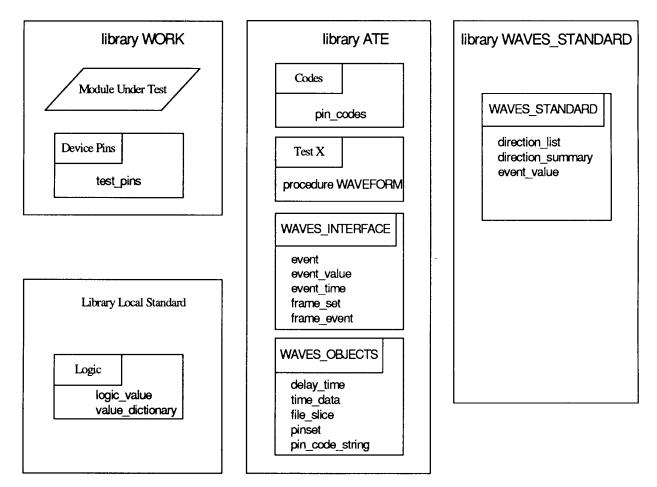

| 7-3  | Partitioning of WAVES Packages into Libraries                                      |      |

| 7-4  | Library Structure of WAVES Packages                                                | 7-8  |

| 7-5  | Example WAVES Header File                                                          |      |

| 7-6  | Example WAVES External File                                                        | 7-10 |

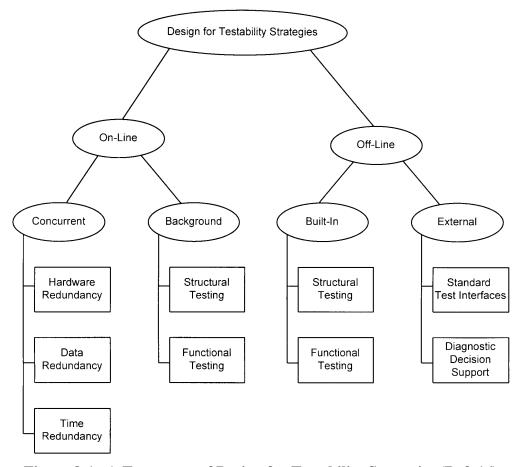

| 8-1  | A Taxonomy of Design for Testability Strategies                                    |      |

| 8-2  | A Taxonomy of Test Measures                                                        |      |

| 8-3  | A Hierarchy of Test Controllers and Busses                                         |      |

| 9-1  | Directory Structure and File Names for Sobel Algorithm Library                     |      |

# LIST OF TABLES

| Tab | le                                                                                |      |

|-----|-----------------------------------------------------------------------------------|------|

| No. | Description                                                                       | Page |

| 2-1 | Features of Behavior, Structure, and Timing and Different Levels of Abstraction   | 2-3  |

| 6-1 | Internal (Pin-to-Pin) Delay Specifications                                        | 6-10 |

| 8-1 | Testability Functions, Components, and Interfaces for a Physical Design Hierarchy | 8-5  |

# LIST OF ABBREVIATIONS AND ACRONYMS

|       | A                                                                                 | FIFO  | = first in, first out                                                |

|-------|-----------------------------------------------------------------------------------|-------|----------------------------------------------------------------------|

| AC    | = alternating current                                                             | FSM   | = finite state machine                                               |

|       | = arithmetic and logic unit                                                       |       | Н                                                                    |

| ANSI  | = American National Standards Institute                                           | HCDD  |                                                                      |

| ASCII | = American standard code for information inter-                                   |       | = high-speed data bus<br>= hardware                                  |

|       | change                                                                            |       |                                                                      |

| ASIC  | = application-specific integrated circuit                                         | nwci  | = hardware configuration item                                        |

|       | = automatic test equipment                                                        |       | I                                                                    |

| ATPG  | = automatic test pattern generator                                                | IC    | = integrated circuit                                                 |

|       | В                                                                                 | IEEE  | = Institute of Electrical and Electronic Engineers                   |

| BIM   | = bus interface module                                                            | IGES  | = International Graphics Exchange Standard                           |

|       | = built-in test                                                                   |       | = infinite impulse response                                          |

|       | = bus interface unit                                                              |       | = input/output                                                       |

|       | = boundary scan definition language                                               | IPC   | = Institute for Interconnecting and Packaging<br>Electronic Circuits |

|       | $\mathbf{C}$                                                                      | ISA   | = instruction set architecture                                       |

| CAD   | = computer-aided design                                                           |       | J                                                                    |

| CAE   | = computer-aided engineering                                                      | ITAG  | = Joint Test Action Group                                            |

| CALS  | = computer-aided acquisition and logistics support                                | 31710 | L                                                                    |

| CDR   | = Critical Design Review                                                          | IRM   | = language reference manual                                          |

|       | = contract data requirements list                                                 |       | = line-replaceable module                                            |

|       | = commercial off-the-shelf                                                        |       | = line-replaceable unit                                              |

| CMOS  | = complementary metal-oxide semiconductor                                         |       | = level-sensitive scan design                                        |

|       | = central processing unit                                                         |       | _                                                                    |

| CSP   | = communicating sequential process                                                |       | M                                                                    |

|       | D                                                                                 |       | = multichip module                                                   |

| DAGC  | _                                                                                 | MUT   | = module under test                                                  |

|       | = Design Automation Standards Committee                                           |       | N                                                                    |

|       | <ul><li>Defense Electronics Supply Center</li><li>data item description</li></ul> | NMOS  | = negative metal-oxide semiconductor                                 |

|       | = Department of Defense                                                           |       | P                                                                    |

| Dob   | _                                                                                 | DDD   |                                                                      |

|       | ${f E}$                                                                           |       | = Preliminary Design Review                                          |

|       | = electronic computer-aided design                                                |       | = processor interface                                                |

|       | = electronic design interchange format                                            |       | = programmable logic array<br>= processor memory switch              |

|       | = electronic data sheet                                                           | LMD   | - processor memory switch                                            |

|       | = Electronic Industries Association                                               |       | Q                                                                    |

|       | = electrostatic discharge                                                         | QPL   | = qualified products list                                            |

| EW    | = electronic warfare                                                              |       | R                                                                    |

|       | F                                                                                 | R     | = reset                                                              |

| FCR   | = fault containment region                                                        |       | = random-access memory                                               |

| FDIR  | = fault detection, isolation, and recovery                                        |       | = request for proposal                                               |

| FFT   | = fast Fourier transform                                                          |       | = read-only memory                                                   |

|       |                                                                                   |       | = register-transfer level                                            |

xii

$\mathbf{S}$  $\mathbf{U}$ S = set

SA/0 = stuck at zero

SA/1 = stuck at oneSDF = standard delay format

SPSP = special-purpose signal processor

SW = software

$\mathbf{T}$

TAP = test access port

TIREP = Technology Independent Representation of

**Electronic Products**

TMS = test mode select

TRR = Test Readiness Review

UUT = unit under test

V

VHDL = very high-speed integrated circuit (VHSIC)

hardware description language

VHSIC = very high-speed integrated circuit

VITAL = VHDL initiative toward ASIC libraries

VLSI = very large-scale integrated

VML = VHDL model library

V&V = validation and verification

WAVES = Waveform and Vector Exchange Specification

WGP = waveform generator procedure

# CHAPTER 1 INTRODUCTION

The goals, scope, and intended audience of the handbook are described in this chapter. Included are references to industry standardization efforts related to the goals of this handbook. Also provided is an overview of each chapter of the handbook.

## 1-1 PURPOSE

This handbook describes the use of the very high-speed integrated circuit (VHSIC) hardware description language (VHDL) to document the design of military digital electronic systems. This handbook is designed to help Government personnel involved in the acquisition of military digital electronic systems understand the following issues related to the use of VHDL models to document military digital electronic systems:

- 1. What VHDL models are required to be delivered with a contract? In particular, this handbook discusses the guidelines described in MIL-HDBK-454 (Ref. 1) and the requirements of the VHDL data item description (DID) (Ref. 2). (The VHDL DID provides comprehensive requirements for VHDL models that include the need for extensive auxiliary and testing support files. This handbook contains approaches to structuring VHDL models so that DID requirements and intent can be met without an excessive number of auxiliary and testing support files. Government personnel can use information in this handbook to tailor definitions of items in the DID to fit their project needs. Contractors can use the information to propose the organization and content of VHDL models they will deliver to the Government.)

- 2. Which VHDL models should be developed during the different stages of the lifetime of a system? The Department of Defense (DoD) requirements now mandate delivery of VHDL models after a system or chip has been fabricated and is ready for deployment, but VHDL models have great potential to support the evaluation of system and chip designs before fabrication is started. The types of VHDL models appropriate for delivery early in the system design process are discussed in this handbook. This information may be useful to DoD personnel during the preparation of requests for proposals (RFPs). This handbook may also be useful to DoD personnel in preparing phased development programs for which multiple awards are made in the early phases of the program to prepare competing designs (which should include VHDL models of the designs).

- 3. How can VHDL models be structured to be consistent with modeling standards? It is of critical importance to the DoD that VHDL models of compatible pieces of hardware are themselves compatible. Because VHDL is such an expressive language, different descriptions may not be easily interfaced if standards for defining interfaces are not observed. Guidelines and reference modeling standards

to ensure compatibility between VHDL models are described in this handbook. In particular, standards for descriptions of test vectors such as the Waveform and Vector Exchange Specification (WAVES) standard (Ref. 3), standard bus interfaces such as the Institute of Electrical and Electronics Engineers (IEEE) Standards 1149.1 (Ref. 4) and 1149.5 (Ref. 5) or test and maintenance, and standard data-type descriptions such as IEEE Standard 1164 (Ref. 6) are discussed.

# 1-2 SCOPE

Use of VHDL to model military digital electronic systems is described in this handbook. In particular, this handbook addresses the development of models compliant with the VHDL DID (Ref. 2) and MIL-HDBK-454 (Ref. 1). Digital electronics are only part of most military systems. Most modern weapons platforms use sensors and actuators that are tightly coupled with the digital electronic systems; however, the modeling of these sensors and actuators is outside the scope of this handbook. Many military electronic systems have both digital and analog components. The modeling of only the digital components is discussed in this handbook. Researchers are currently exploring the use of VHDL for analog components and considering changes to the language to allow VHDL to better support modeling of analog and hybrid components and subsystems. Although VHDL models are frequently used to provide test beds for testing software before the hardware is fabricated, this handbook does not discuss the issues of developing tests for soft-

The handbook is not intended to provide a working knowledge of VHDL. On the other hand, the handbook introduces VHDL terms and concepts so it can serve as a stand-alone reference document for readers familiar with VHDL.

## 1-3 INTENDED AUDIENCE

This handbook is intended for use by DoD personnel who are writing requests for proposals for digital electronic systems, DoD contractors who are developing VHDL models to be delivered to the Government, and DoD personnel or independent validation and verification contractors who are evaluating or reviewing models that have been delivered to the Government. DoD personnel include people who are writing RFPs for the development of digital electronic systems, are serving on proposal review teams, are negotiating the deliverables and tailoring the DIDs associated with a

contract, are part of Government validation and verification (V&V) teams, or are in government laboratories tracking the evolution of technology for the design of digital electronic systems. VHDL tool vendors or VHDL library vendors may also find this handbook useful in terms of understanding the needs of DoD contractors.

Users of this handbook should have some formal training or some experience with electrical engineering and/or computer science and should have experience reading and writing VHDL models.

Although the user does not need a complete understanding of VHDL to read this handbook, he or she will need to understand VHDL to implement the suggestions made in this handbook and to understand the example VHDL programs.

# 1-4 HISTORY, PURPOSE, AND SCOPE OF VHDL

# 1-4.1 HISTORY OF VHDL

The VHSIC program was created to ensure that the digital microelectronic systems in the weapon systems fielded by the DoD would be at least comparable to state-of-the-practice commercial technology. Over its 10-yr lifetime this program developed tools and technology for the design, manufacture, and use of state-of-the-art integrated circuits (ICs).

At the start of the VHSIC program in 1980, the DoD was already experiencing a problem with the obsolescence of ICs. VHSIC studies (Ref. 7) indicated that by 1990, 80% of nonmemory ICs in military electronic systems would be application-specific integrated circuits (ASICs). At the same time the VHSIC studies also indicated that the average lifetime of a fabrication process would be two years. Since the acquisition process for DoD systems was seven to ten years, a majority of the ICs in a DoD system would be obsolete before the system could be fielded.

VHDL began as a research effort under the DoD VHSIC program to document fully the DoD digital systems (Ref. 8). As experience with the language was gained, the language was improved by incorporating additional features. The language was subsequently standardized by the IEEE and adopted by the American National Standards Institute (ANSI) as ANSI/IEEE Std 1076-1987 (Ref. 9). This standard was updated in 1994 by IEEE Std 1076-1993 (Ref. 10).

## 1-4.2 THE PURPOSE OF VHDL

VHDL was developed to provide a standardized language to describe formally the behavior and structure of DoD digital electronic systems (Ref. 8). These descriptions serve as a procurement device by specifying exactly what functions a new device would have to perform in order to replace an old device. Through simulation of these descriptions the ability of the design of a new device to perform the same required functions as the old device can be more accurately es-

timated before being physically verified. Furthermore, the VHDL descriptions may contain timing information. As a result, the performance of competing designs can be compared before the devices are built. This performance simulation provides an ability to perform an impartial assessment of proposals for integrated circuits and for complex electronic systems containing many ICs.

Because VHDL has been standardized, it is now being used as the primary hardware description language for commercial computer-aided design (CAD) vendors, and it is likely that this trend will continue. VHDL is also coming into use as an exchange standard between tool sets provided by different vendors.

As previously stated, VHDL was developed to serve the need of the DoD to document the functionality of digital electronic systems delivered to it by the defense industry (Ref. 8). This documentation is required to procure new systems and to assist in the maintenance of fielded systems. VHDL provides a powerful, technology-independent way to describe a wide range of electronic hardware systems from individual integrated circuits to large multiprocessor systems. It supports top-down and bottom-up design methodologies or mixtures of the two.

For new systems a VHDL model can be provided by the DoD that specifies the exact functional behavior desired of the system. This description can then be offered to potential bidders for competitive procurement. Bidders can be required to submit VHDL models of their proposed designs, and these can be simulated and compared with the original DoD model. The VHDL models could be evaluated as part of the overall proposal evaluation process. This step ensures that bidders understand the functions the system is to perform and that the designs will meet functional requirements.

VHDL also provides important benefits after a system is fielded. As fielded systems fail and are repaired, additional spare parts must be acquired as stocks of original spare parts are exhausted. For electronic systems this need requires that the DoD provide, among other things, a complete functional specification of the desired parts to potential bidders. This functional specification must be technology independent because it is often impossible or excessively expensive to acquire parts in the original technology; thus it becomes desirable to reimplement the function in a different technology. Technology independence permits the separation of the behavior function (plus timing) from its implementation, which makes incorporating new technologies easier.

Until the advent of VHDL there was no standard way to provide this functional specification. Documentation delivered with the original systems was usually in a technology-dependent, proprietary format that was not supportable long term. This obsolescence raised the cost and technical risk of reprocuring new parts because using technically obsolete engineering data is expensive and time-consuming. VHDL offers the technical means to provide functional, timing, and other specifications for digital electronic systems in a form that will be useful long after the original system is delivered.

# 1-4.3 THE SCOPE OF VHDL

VHDL supports describing hardware at many levels of abstraction from an entire system composed of individual racks of equipment down to gate-level descriptions of integrated circuits. VHDL includes primitive functions for gatelevel operations. VHDL supports processes, a rich data abstraction facility, and synchronization capabilities for algorithmic descriptions. VHDL allows different levels of abstraction to be mixed in the same description, and this flexibility can reduce both the amount of time for simulation and the introduction of unnecessary detail. VHDL also provides for the specification of detailed hardware timing requirements. Timing specification is particularly important when the VHDL description represents a hardware component that must be integrated with other components, as is almost always the case. VHDL also supports annotating designs and allows the user to specify physical types and their units, which can be used as attributes for a design.

The DoD is actively incorporating VHDL requirements into procedures used to develop military electronic computers. VHDL is required documentation under Guideline 64 of MIL-HDBK-454, which defines the requirements for VHDL descriptions to accompany any digital electronics that are being added to the DoD qualified products list (QPL). A data item description, DI-EGDS-80811 (Ref. 2), defines the detailed characteristics of a VHDL model to be delivered to the Government. VHDL models of systems will become part of the Computer-Aided Acquisition and Logistic Support (CALS) Program (Ref. 11) usage guidelines.

# 1-5 RELATED INDUSTRY STANDARDS

Realizing the benefits for customers of standardized models and modeling languages, the electronics industry is developing commercial standards for electronic systems. This is a continuing process. For example, the IEEE requires updates of its standards every five years.

The DoD recognizes and strongly supports VHDL standardization efforts, including the following: (1) the IEEE VHDL (1076) standardization, (2) the IEEE Design Automation Standards Committee (DASC) standards, (3) the Joint Test Action Group (JTAG) definition of test interface standards, including the IEEE 1149.1 boundary scan test bus and the IEEE 1149.5 test and maintenance bus, as well as the Boundary Scan Definition Language (BSDL) (Ref. 12), a VHDL style that describes implementations of IEEE Std 1149.1 boundary scan test circuitry, (4) the IEEE 1164 standard logic package, and (5) the IEEE 1029.1 WAVES test vector standards.

The IEEE has adopted and standardized VHDL as IEEE Std 1076 (Ref. 10). The standard is the VHDL Language Reference Manual (LRM). The VHDL DID requires the use of IEEE Std 1076. This handbook uses the VHDL LRM as its definition of VHDL. IEEE standards are revised approximately every five years; therefore, the IEEE VHDL standard released in 1988 was revised in 1993. The revised VHDL standard is the DoD-required standard until it is

again revised. The LRM is described in more detail in Chapter 3

The IEEE DASC is developing standards to support the interoperability of VHDL models. One aspect of this effort is IEEE Std 1164, which defines a standard set of values for signals that includes values for unknowns and high-impedance values. IEEE Std 1164 is discussed in Chapter 7. A second aspect is the VHDL initiative toward ASIC libraries (VITAL) (Refs. 13 and 14), which is developing a standard for use in the sign-off process for chip designs by fabrication vendors.

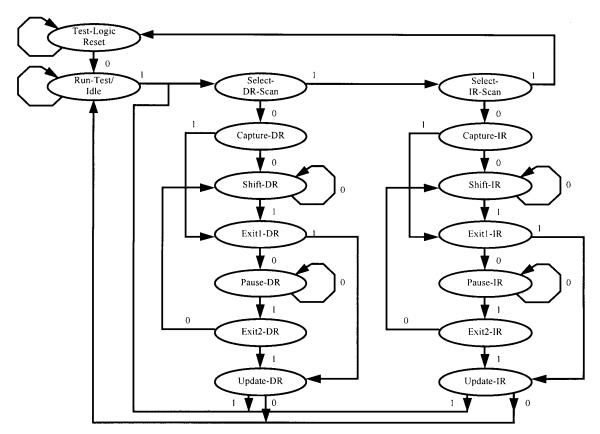

The JTAG is developing a standard VHDL practice to describe implementations of the IEEE 1149.1 boundary scan test circuitry (Ref. 4). This practice provides a method used to describe modifications to a low-level structural model of an integrated circuit in order to incorporate the circuitry required for a boundary scan built-in test capability. The IEEE 1149 series of standards is discussed in Chapter 8.

The WAVES IEEE Std 1029.1 (Ref. 3) is intended to create a standard representation of test vectors or waveforms for electronic devices. It uses features of VHDL to describe procedures used to generate test vectors and waveforms and to describe methods used to ensure the output of the module under test matches the required output. WAVES provides a common format used to describe test vectors for many different automatic test equipment (ATE) machines and a common output format for automatic test pattern generation software. This standard reduces the amount of work required to interface ATE machines with many VHDL parts models. MIL-HDBK-454 (Ref. 1) states that the VHDL models delivered to the Government should be compatible with WAVES and requires the use of WAVES for any test vectors or waveforms delivered with the model. The WAVES standard is discussed in Chapter 7.

# 1-6 OVERVIEW

In Chapter 2 the use of hierarchies in modeling computer hardware is discussed, and the concepts of behavioral and structural models of electronic systems are described. These concepts are essential to VHDL models compliant with the VHDL DID. Models with mixed levels of abstraction are discussed. Also discussed is the use of simulation to support functional correctness checking and performance evaluation. Examples of these concepts are presented.

In Chapter 3 the use of VHDL to capture the structure and behavior of electronic computers is discussed. Aspects of VHDL that support the reuse of VHDL models are presented. The development and use of libraries of VHDL descriptions for reuse of both VHDL programs within a model and between models, as well as the annotation of VHDL models with descriptive information, are described.

Chapter 4 discusses two Government documents concerning the use of VHDL: MIL-HDBK-454 (Ref. 1) and the VHDL DID, DI-EGDS-80811 (Ref. 2). The need for VHDL descriptions of all application-specific integrated circuits and all digital electronic components on the DoD qualified

products list is discussed. The required structure and contents of VHDL descriptions provided to the Government, as defined by the VHDL DID, are presented. In particular, the requirement for both structural and behavioral models of each component of an electronic subsystem is described. This chapter provides guidelines to be used to tailor the VHDL DID and discusses an example of a tailored VHDL DID. This chapter also contains required annotations for VHDL models.

Chapter 5 contains a description of the construction and use of behavioral VHDL models. Common techniques used to create behavioral VHDL models, specify the timing for behavioral models, and annotate behavioral models are described. Also discussed are the usefulness of behavioral models in top-down design and the simulation of models with mixed levels of abstraction.

Chapter 6 discusses the construction and use of structural VHDL models. Common techniques used to create structural VHDL models, including automatic synthesis and schematic capture, are described. Applications of structural models for hybrid model simulation, physical design, testability analysis, and annotation with layout and testability information are also described in this chapter.

The preparation of VHDL models for simulation is detailed in Chapter 7. The process of configuring a model from libraries of component descriptions is described. Techniques that support the interoperability of models are emphasized. In component libraries these models can be combined freely to provide hybrid structural and behavioral models of systems. The development of test benches and test vectors to check the correctness and completeness of the model rather than the development of test vectors to check the correctness of the component design is discussed. Also discussed are the use of parameterized timing models and the selection of timing options for simulation.

Chapter 8 discusses issues surrounding VHDL modeling of the test and diagnostic functions of digital electronic systems. This chapter describes measures of and techniques for testability and describes different levels of testability based on the IEEE 1149 hierarchy of testing interfaces. The use of behavioral modeling to verify that the test bus and test controller systems respond properly to error conditions detected by on-chip BIT without requiring gate-level implementation details is emphasized. The use of detailed structural models as the starting point for built-in test structure generation, such as boundary scan, is discussed. This chapter also emphasizes that detailed structural models are necessary for evaluation of many testability measures.

Chapter 9 describes the preparation of a VHDL model for delivery to the Government. The contents and organization of the files delivered to the Government, as specified in the VHDL DID, are described. The files that must be delivered include not only the VHDL source models but also test vec-

tors, annotations, certain other external files, and documentation. Chapter 9 also includes recommendations for VHDL model style and recommendations for naming files and organizing libraries.

# REFERENCES

- 1. MIL-HDBK-454M, General Guidelines for Electronic Equipment, 28 April 1995.

- 2. DI-EGDS-80811, VHSIC Hardware Description Language (VHDL) Documentation, 11 May 1989.

- 3. IEEE Std 1029.1-1992, Waveform and Vector Exchange Specification (WAVES), IEEE Design Automation Standards Subcommittee, The Institute of Electrical and Electronics Engineers, Inc., New York, NY, 1992.

- IEEE Std 1149.1-1990, IEEE Standard Test Access Port and Boundary Scan Architecture, IEEE Standards Board, The Institute of Electrical and Electronics Engineers, Inc., New York, NY, May 1990.

- 5. P. McHugh, "IEEE P1149.5 Module Test and Maintenance Bus", *IEEE Design and Test of Computers* (December 1992).

- IEEE Std 1164-1993, IEEE Standard Multivalue Logic System for VHDL Model Interoperability, The Institute of Electrical and Electronics Engineers, Inc., New York, NY, May 1993.

- Very High-Speed Integrated Circuits Final Program Report, VHSIC Program Office, Office of the Under Secretary of Defense for Acquisition, Washington, DC, September 1990.

- 8. J. Hines, "Where VHDL Fits Within the CAD Environment", 24th ACM\*/IEEE Design Automation Conference Proceedings, Miami Beach, FL, June 1987, The Institute of Electrical and Electronics Engineers, Inc., New York, NY.

- ANSI/IEEE Std 1076-1987, IEEE Standard VHDL Language Reference Manual, The Institute of Electrical and Electronics Engineers, Inc., New York, NY, March 1988

- ANSI/IEEE Std 1076-1993, IEEE Standard VHDL Language Reference Manual, The Institute of Electrical and Electronics Engineers, Inc., New York, NY, April 1994.

- 11. MIL-STD-1840B, Automated Interchange of Technical Information, 1992.

- K. Parker and S. Oresjo, "A Language for Describing Boundary Scan Devices", *Proceedings of the IEEE International Test Conference*, Los Alamitos, CA, 1990, The Institute of Electrical and Electronics Engineers, Inc., New York, NY.

- 13. V. Berman, "An Analysis of the VITAL Initiative", VHDL Boot Camp, VHDL International Users' Forum, San Jose, CA, October 1993, VHDL Interna-

<sup>\*</sup>Association for Computing Machinery

- tional Users' Forum, c/o Conference Management Services, Menlo Park, CA.

- O. Levia and F. Abramson, "ASCI Sign-Off in VHDL", *VHDL Boot Camp*, VHDL International Users' Forum, San Jose, CA, October 1993, VHDL International Users' Forum, c/o Conference Management Services, Menlo Park, CA.

# **BIBLIOGRAPHY**

- J. R. Armstrong, *Chip-Level Modeling in VHDL*, Prentice-Hall, Inc., Englewood Cliffs, NJ, 1988.

- D. Coelho, *The VHDL Handbook*, Kluwer Academic Publishers, Norwell, MA, 1989.

- R. Lipsett, C. Schaefer, and C. Ussery, VHDL: Hardware

- *Description and Design*, Kluwer Academic Publishers, Norwell, MA, 1989.

- D. Perry, *VHDL*, McGraw-Hill Book Co., Inc., New York, NY, 1991.

- VHSIC Annual Report for 1986, AD-A191-027, VHSIC Program Office, Office of the Under Secretary of Defense for Acquisition, Washington, DC, December 1986.

- VHSIC Annual Report for 1987, AD-A199-880, VHSIC Program Office, Office of the Under Secretary of Defense for Acquisition, Washington, DC, December 1987.

- VHSIC Annual Report for 1988, AD-A223-725, VHSIC Program Office, Office of the Under Secretary of Defense for Acquisition, Washington, DC, December 1988.

# CHAPTER 2 HARDWARE DESCRIPTION CONCEPTS

As digital electronic systems approach complexity levels of hundreds of millions of devices, the hardware architect needs techniques to reduce the design complexity to an understandable level without eliminating any design detail. Two mechanisms used to control complexity are hierarchy and abstraction. Techniques that create models of hardware by using hierarchy and different levels of abstraction are described. The concepts of structural and behavioral models of digital electronic systems are essential to very high-speed integrated circuit (VHSIC) hardware description language (VHDL) models that comply with the VHDL data item description (DID); these concepts are described in this chapter. Models with mixed levels of abstraction, in which a hierarchical model of a system contains behavioral elements at different levels of abstraction, are discussed. Also discussed are the uses of simulation to support functional correctness checking and performance evaluation. Examples of these concepts are presented.

# 2-1 INTRODUCTION

A hardware design is usually developed by constructing a series of models that become less abstract (and thus more implementation specific) as the design process progresses. This iterative design process is known as top-down design. The goal of this process is to allow the hardware architect the flexibility to construct and evaluate models of very different design alternatives rapidly during the early stages of the design process. In the later stages of the process, the models become more detailed, more accurate, and more difficult and expensive to change and evaluate. Thus in these later stages the architect cannot explore as many options.

Before a hardware design begins the project manager must specify milestones, i.e., when models of the design are to be completed, verified, and evaluated. Evaluation occurs as part of a tradeoff between different designs or as part of the verification of the correctness of the design. Models may be verified by simulating the models and comparing the simulation results with expected results or against each other. When the project manager specifies the milestones, he or she must clearly indicate for each milestone the level of abstraction of the model to be delivered, the approach to verification to be used, and the types of evaluations to be performed on the model. For a military contract these milestones are specified in the contract data requirements list (CDRL) and its associated DIDs. This chapter discusses some possible levels of abstraction that can be provided for hardware models. This chapter also describes the two types of models identified in subpar. 10.2.1 of the VHDL DID (Ref. 1): behavioral and structural models. Discussion of design methodologies is beyond the scope of this handbook.