## HANDBOOK OF SEMICONDUCTOR INTERCONNECTION TECHNOLOGY

Second Edition

# HANDBOOK OF SEMICONDUCTOR INTERCONNECTION TECHNOLOGY

Second Edition

## EDITED BY GERALDINE C. SCHWARTZ KRIS V. SRIKRISHNAN

A CRC title, part of the Taylor & Francis imprint, a member of the Taylor & Francis Group, the academic division of T&F Informa plc.

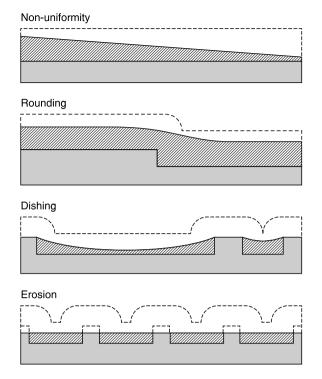

Published in 2006 by CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2006 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-10: 1-57444-674-6 (Hardcover) International Standard Book Number-13: 978-1-57444-674-6 (Hardcover) Library of Congress Card Number 2005054909

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

Trademark Notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Handbook of semiconductor interconnection technology / edited by Geraldine C. Schwartz and Kris V. Srikrishnan.--2nd ed.

p. cm.

Includes bibliographical references and index.

ISBN 1-57444-674-6 (alk. paper)

1. Interconnects (Integrated circuit technology) 2. Semiconductors--Junctions. 3. Semiconductors--Design and construction. I. Schwartz, G. C. II. Srikrishnan, K. V., 1948-

TK7874.53.H36 2006 621.3815--dc22

2005054909

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

### Preface

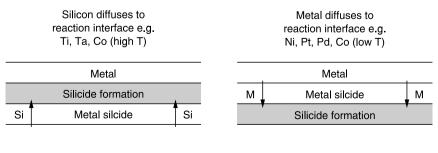

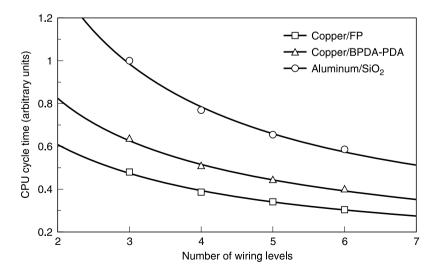

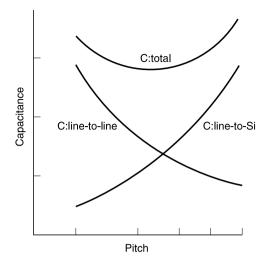

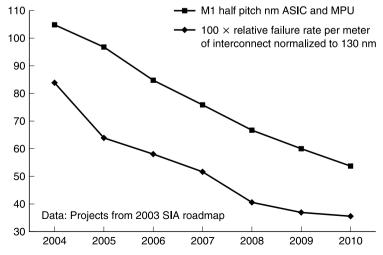

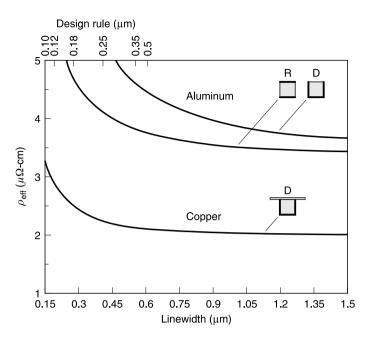

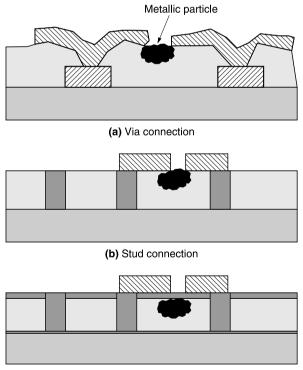

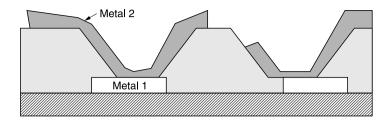

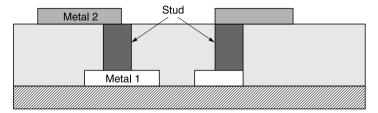

Since the first edition of this handbook, semiconductor technology has gone through a continued evolution of new devices and materials like never before. Wafer sizes continue to grow with most of the new fabs equipped for 12-inch wafers. The changes are triggered by many considerations: continued need to provide more functions at lower cost; technology features less than 1000 Å requiring new processes, and exponential increase in the number of device elements. At the device level, the field effect transistor (FET) speed is continually improved by things such as use of insulating substrates, straining the silicon (channel region), and use of dual- and triple-gate (FINFET) structures. The interconnection technology is also going through changes, starting with copper wiring in place of AlCu, low-dielectric insulators in place of silicon dioxide, and use of cobalt and nickel silicide in place of titanium silicide for contacts. In parallel, the decreasing feature size and increasing aspect ratio of lines and studs (vertical vias), along with an increase in the number of wiring levels, have created not only the need for new materials but also unprecedented requirement of reliability per unit interconnect. This again has led to process innovations and improvement in equipment for depositing and patterning conducting and insulating films. *In situ* monitoring of several processes has become routine.

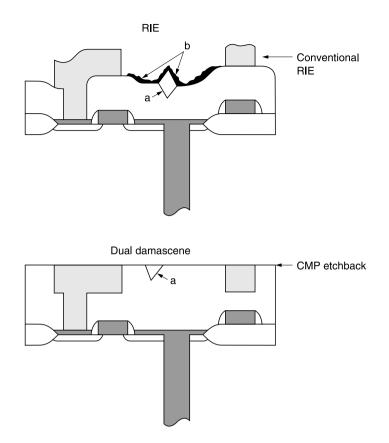

Many of the materials and processes described as likely directions in the first edition of this book have become standard in today's chip fabrication facilities: for example (1) dual damascene processes, including both insulator and metal polished using CMP, (2) use of electroplating of copper, which at one time was considered to be potentially fatal, and (3) fluorine-doped silicon dioxide followed by low-dielectric films containing silicon, carbon, hydrogen, and oxygen, and increasing discussion on the use of porous films. Even more fascinating is the evolution of the fabs which process the 12-inch wafers extensively, using single-wafer equipment that is kept isolated from ambient exposure through most of the process steps, traveling in ambient controlled tunnels from station to station with little human intervention. There has been a huge shift in the traditional focus for cleanrooms with emphasis shifting to particulate generation within tools and during processes from ambient- and operator-generated particulates. This is the main reason why the last chapter in the previous edition on cleanrooms has not been included in this revised edition.

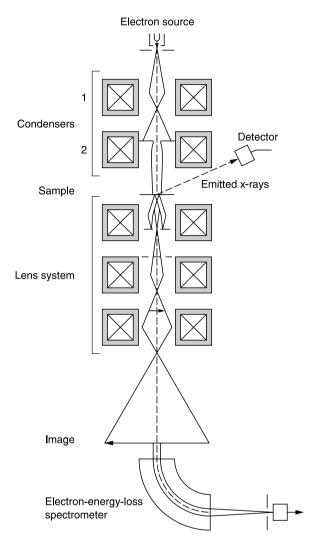

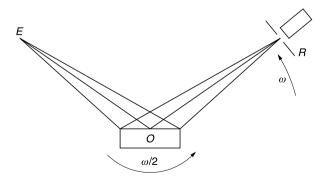

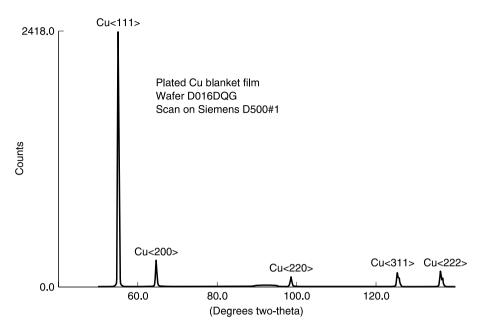

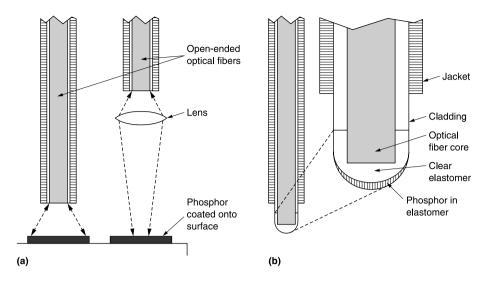

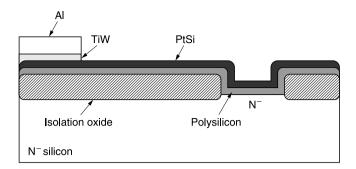

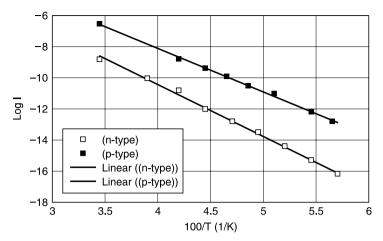

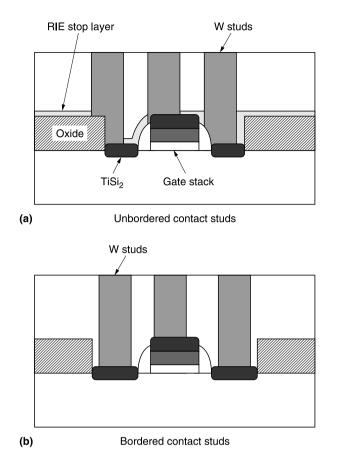

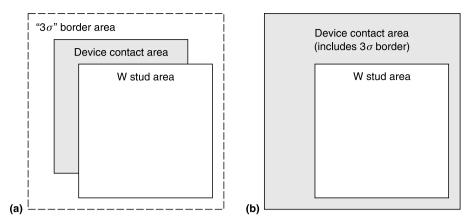

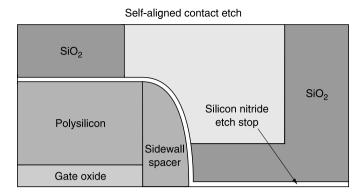

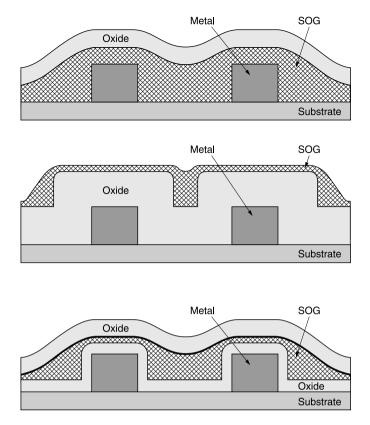

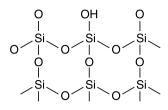

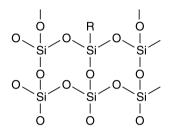

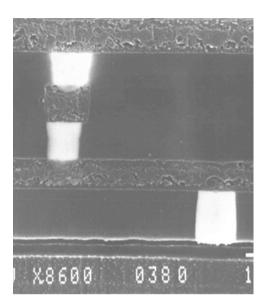

Chapter 1 describes the equipment commonly used in manufacturing for deposition and etching and the principles underlying the design and use of the equipment. In this edition, electrochemical deposition equipment used for plating copper is discussed in detail, in addition to updating previous discussions on equipment used for evaporation, chemical vapor deposition (CVD), and plasma processes. Chapter 2 includes many standard techniques used for characterizing metal and insulator films. The principles of electrochemical deposition are also covered. Measurement of the mechanical and thermal properties of insulators is emphasized in this edition, as is the greater use of electron energy loss spectroscopy (EELS), energy filtering TEM, and atomic force microscopy (AFM). The several recently reported methods for characterizing porous dielectric thin films are also included. Chapter 3 is devoted to contacts and in this edition greater focus has been given to integration issues and properties of titanium, cobalt, and nickel. The need for borderless contacts for gates and source/ drain has led to newer process schemes that are also discussed. Use of contact studs with planarized CVD tungsten has become widely established. From all indications this is not likely to change in the future. Based on the need to keep the devices and interconnection safely apart, the use of barrier films for both physical (diffusion barrier) and electrical (barrier heights) requirements is reviewed. Chapter 4 now includes a greater discussion of recently reported choices for low-dielectric insulators. The need for planarization at the macro level has become less, since the use of dual damascene has now become widespread; however, the challenges of managing topography fluctuations at the local level remain. There is extensive coverage of low dielectric constant insulators, particularly the newer ones. The mechanical properties of insulators have become important along with their thermal and thermomechanical properties. Chapter 5 covers the deposition and etching of metallic films (tungsten, copper, aluminum) but a greater focus is placed on electroplated copper, with emphasis on the morphology of plated films and their properties. Clearly a big challenge for the next generations of devices is the continuing need to form thin adhesion and barrier layers for copper films in the lines and studs. This has led to the pursuit of atomic layer deposition processes and precursor materials that result in continuous nonporous films covering all sides of trench openings of high aspect ratios (two or more). Chapter 6 deals with two main issues: (1) the problems associated with topography and solutions to these problems, emphasizing the details of CMP and dual damascene processes, (2) process/structure choice conflicts, process compatibility, reliability, manufacturability, and methods for defect-free manufacturing. Chapter 7 is devoted to the reliability of thin metallic and insulating films and this revised edition has an expanded discussion on copper reliability. There is an extensive review of electromigration mechanism and testing procedures as well as other wear-out phenomena for wires and vias. The issue of corrosion is also addressed. The reliability of interlevel insulators is examined, with the impact of migration to low dielectric constant materials and the planned use of pores.

## **The Editors**

**Geraldine Cogin Schwartz** was a senior engineer at IBM Microelectronics, Hopewell Junction, New York. She retired from IBM after more than 25 years of research in many areas of semiconductor interconnection technology and since has given several invited talks. A Fellow of the Electrochemical Society and a member of the American Vacuum Society and Sigma Xi, she is the author of several key publications in semiconductor technology and the holder of over 15 U.S. patents. Dr. Schwartz received a Ph.D. degree in chemistry from Columbia University, New York.

**K.V. Srikrishnan** is a distinguished engineer at Systems and Technology Group in IBM. The author of numerous professional papers and holder of over 20 patents in different areas of semiconductor technology, he is a member of the Electrochemical Society and Sigma Xi. Dr. Srikrishnan received a Ph.D. degree in solid state technology from Syracuse University, Syracuse, New York. He has been with IBM for over 25 years and has held both technical and management positions.

## Contributors

**Dr. David R. Campbell** Retired from IBM Microelectronics Portland, Oregon

**Dr. Catherine Ivers** Senior Engineer IBM Systems and Technology Group Hopewell Junction, New York

**Dr. James R. Lloyd** Research Staff Member IBM Thomas Watson Research Center Yorktown Heights, New York

#### Dr. Kenneth P. Rodbell

Research Staff Member IBM Thomas Watson Research Center Yorktown Heights, New York

#### **Dr. Geraldine Cogin Schwartz**

Retired from IBM Microelectronics Fellow of Electrochemical Society Poughkeepsie, New York

#### Dr. K.V. Srikrishnan

Distinguished Engineer at IBM Systems and Technology Group Hopewell Junction, New York

## Contents

| Chapter 1<br>Aethods/Principles of Deposition and Etching of Thin Films |

|-------------------------------------------------------------------------|

| Chapter 2<br>Characterization                                           |

| Chapter 3<br>emiconductor Contact Technology                            |

| Chapter 4<br>Interlevel Dielectrics                                     |

| Chapter 5<br>Aetallization                                              |

| Chapter 6<br>Chip Integration                                           |

| Chapter 7<br>Reliability                                                |

## CHAPTER 1

## Methods/Principles of Deposition and Etching of Thin Films

#### **Geraldine Cogin Schwartz**

#### CONTENTS

| 1.1 | Introd | uction     |                                 |

|-----|--------|------------|---------------------------------|

| 1.2 | Evapo  | ration     |                                 |

| 1.3 | Chemi  | ical Vapor | Deposition                      |

|     | 1.3.1  | Introduc   | xtion                           |

|     | 1.3.2  | Principl   | es                              |

|     | 1.3.3  | Reactor    | s7                              |

|     |        | 1.3.3.1    | Classification                  |

|     |        | 1.3.3.2    | Examples of Reactors            |

|     | 1.3.4  | Film Pro   | perties                         |

| 1.4 | Photoe | enhanced   | CVD                             |

| 1.5 | Plasm  | a Processi | ng                              |

|     | 1.5.1  | Introduc   | tion                            |

|     | 1.5.2  | Capacit    | ively Coupled RF Glow Discharge |

|     |        | 1.5.2.1    | Frequencies                     |

|     |        | 1.5.2.2    | Reactor Requirements            |

|     |        | 1.5.2.3    | Capacitively Coupled Reactors   |

|     |        | 1.5.2.4    | Magnetic Confinement            |

|     |        | 1.5.2.5    | Hollow Cathode                  |

|     | 1.5.3  | Tempera    | ature Effects                   |

|     |        | 1.5.3.1    | Heating                         |

|     |        | 1.5.3.2    | Temperature Control             |

|     | 1.5.4  | Sputteri   | ng                              |

|     |        | 1.5.4.1    | Introduction                    |

|     |        | 1.5.4.2    | Sputter Deposition              |

|     |        | 1.5.4.3    | Sputter Etching; Ion Milling    |

|     | 1.5.5  | Angula     | Dependence of Sputtering Yield  |

|     | 1.5.6  | High-D     | ensity Plasmas                  |

|     |        | 1.5.6.1    | Introduction                    |

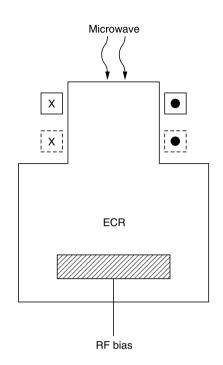

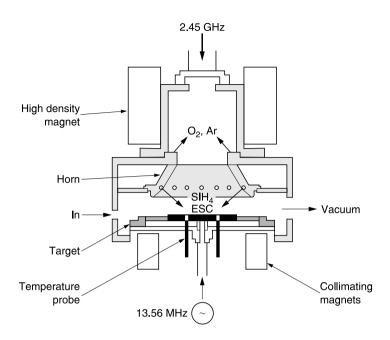

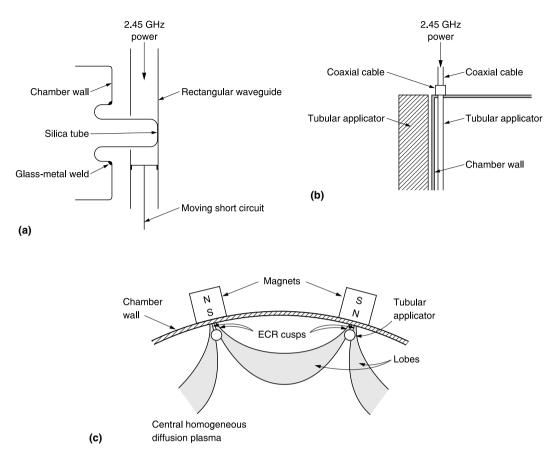

|     |        | 1.5.6.2    | Electron Cyclotron Resonance    |

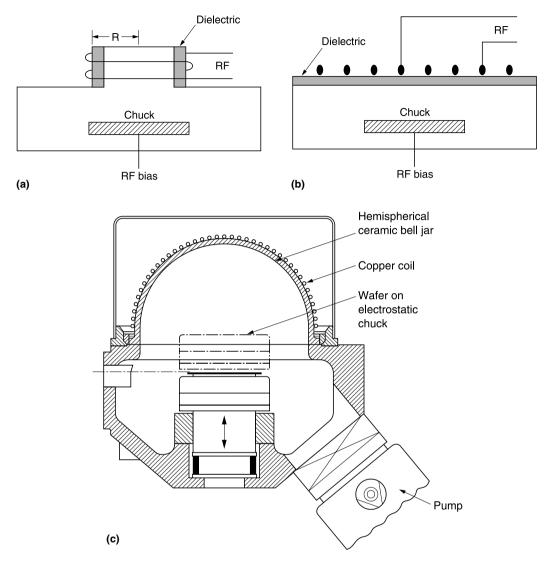

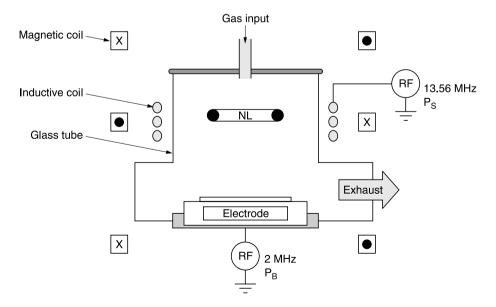

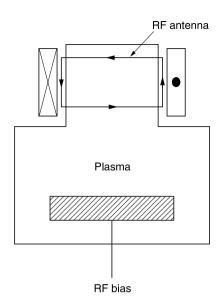

|     |        | 1.5.6.3    | Radio-Frequency Induction (RFI) |

|      |         | 1.5.6.4     | Helicon Sources                                              | 37 |

|------|---------|-------------|--------------------------------------------------------------|----|

|      |         | 1.5.6.5     | Concluding Remarks about High-Density Reactors               | 38 |

|      |         | 1.5.6.6     | Ultrahigh-Frequency (UHF) Source                             | 39 |

|      | 1.5.7   | Plasma-E    | nhanced CVD.                                                 |    |

|      |         | 1.5.7.1     | Introduction                                                 | 39 |

|      |         | 1.5.7.2     | Mechanisms                                                   | 39 |

|      |         | 1.5.7.3     | Reactors                                                     | 40 |

|      | 1.5.8   | Reactive I  | Plasma-Enhanced Etching                                      | 42 |

|      |         | 1.5.8.1     | Introduction                                                 | 42 |

|      |         | 1.5.8.2     | Mechanisms                                                   | 43 |

|      |         | 1.5.8.3     | Etching Systems                                              | 44 |

|      |         | 1.5.8.4     | Reactive Ion Etching (RIE) or Reactive Sputter Etching (RSE) | 44 |

|      |         | 1.5.8.5     | Choice of Etchants                                           | 45 |

|      |         | 1.5.8.6     | System Parameters                                            | 45 |

|      |         | 1.5.8.7     | Profile Control                                              | 45 |

|      |         | 1.5.8.8     | Masking                                                      | 48 |

|      |         | 1.5.8.9     | Loading Effect                                               | 49 |

|      |         | 1.5.8.10    | Feature Size Dependence of Etch Rates                        | 50 |

|      |         | 1.5.8.11    | Angular Dependence of the RIE Yield                          | 50 |

|      |         | 1.5.8.12    | Temperature Effects                                          | 51 |

| 1.6  | Electr  | ochemical 1 | Deposition                                                   | 51 |

|      | 1.6.1   | Electroles  | s Plating                                                    | 51 |

|      | 1.6.2   | Electrolyt  | ic Plating (Electroplating)                                  | 53 |

| 1.7  | Spin C  | Coating     |                                                              | 53 |

| 1.8  |         |             |                                                              |    |

| Refe | rences. |             |                                                              | 55 |

|      |         |             |                                                              |    |

#### **1.1 INTRODUCTION**

This chapter covers many of the methods of depositing and etching both dielectric and conducting films used today in semiconductor manufacturing as well as the basic principles behind them. Some specialized techniques such as beam deposition and chemical mechanical polishing (CMP) are covered in Chapter 6.

A brief overview of deposition techniques can be found in Table 1.1 and of etching in Table 1.2.

#### **1.2 EVAPORATION**

Sputtering has almost completely displaced evaporation as a method of deposition because of its superior control of alloy composition, step coverage/hole fill by substrate biasing, ease of integration into cluster tools, etc. Since there are some applications of evaporation, particularly for forming lift-off metal patterns, a brief review of the technique is included.

Evaporation is usually used for metal deposition but has also been used to deposit some nonmetallic compounds (e.g., SiO, MgO). Early reviews of evaporation principles and equipment can be found in Holland (1961) and in Glang (1970); a later one is in Bunshah (1982). A review of some of the basics of high-vacuum technology can be found in Glang et al. (1970).

Glang distinguished the steps of the evaporation process: (1) transition from a condensed phase (solid or liquid) into a gaseous phase, (2) transport of the vapor from source to substrate at reduced

| Method                     | Materials Deposited                                   | General Comments                                                                                                                                                                                                   |

|----------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Evaporation <sup>a</sup>   | Pure metals; alloys; compounds                        | High-vacuum process; need adequate vapor pressure;<br>various support materials; <sup>b</sup> single/multiple sources<br>for alloys; reactive evaporation                                                          |

| Sublimation                | Metals; compounds                                     | Used when very high temperature is needed                                                                                                                                                                          |

| Sputtering°                | Pure metals; alloys; compounds; dielectrics           | Can control film properties; control stoichiometry of<br>alloys; use bias, high-density plasma, magnetic<br>enhancement, ICP, IMP; directional deposition using<br>collimation, large source-to-substrate distance |

| CVD/PECVD/ALD <sup>d</sup> | Pure metals; alloys; dielectrics                      | Better step coverage/gap fill; film composition and<br>properties by choice of reactants, deposition<br>conditions; commercial cluster systems; operating<br>parameters, bias, temperature                         |

| Plating <sup>e</sup>       | Pure metals; alloys                                   | Hole fill; film properties through bath control                                                                                                                                                                    |

| Spin coat <sup>f</sup>     | Soluble, dispersible materials:<br>organic insulators | Planarization; step coverage; curing to remove<br>solvents or promote reactions                                                                                                                                    |

| Beams <sup>g</sup>         | Metals; dielectrics                                   |                                                                                                                                                                                                                    |

#### Table 1.1 Deposition Methods

<sup>a</sup> Source heating: resistance heaters, RF induction heaters, e-gun.

<sup>b</sup> Crucibles, wires, foils.

° Metals: DC or RF; dielectrics: RF; option of DC or RF reactive sputtering.

<sup>d</sup> Includes high-density PECVD systems.

<sup>e</sup> Electroless; electrolytic.

<sup>f</sup> Examples: polyimides, xerogels, FOx, SiLK; one report of Cu spin-on.

<sup>9</sup> Beams covered in Chapter 6.

| Table 1.2 | Etching | for | Pattern | Definition |

|-----------|---------|-----|---------|------------|

|-----------|---------|-----|---------|------------|

| Method                               | Materials Etched                | General Comments                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wet chemical                         | Conductors, insulators, silicon | Almost always isotropic <sup>a</sup> ; form a soluble product; need insoluble<br>mask with good adhesion; mask profile not important;<br>usually selective, batch processing                                                                                                                                                  |

| Sputter etch,<br>ion-beam<br>etching | All above                       | Poor selectivity; faceting, trenching, possible vertical etch;<br>redeposition, possible substrate damage; slow, ion beam<br>(single-wafer mode), sputter etch single or batch mode;<br>used in dep-etch gap fill; angle-dependent etch                                                                                       |

| Reactive plasma,<br>RIE, RSE, RIBE   | Widely used in BEOL             | Product needs to be volatile/desorbed by ions; high selectivity<br>possible; profile control: both anisotropic and isotropic; <sup>b</sup> mask<br>profile, erosion; redeposition, trenching, and substrate<br>damage issues; aspect ratio-dependent etch rates; batch,<br>single wafer (cluster); high etch rates attainable |

<sup>a</sup> Directionality possible in some cases: e.g., "slow" etched for Si which follow crystal planes; columnar structure resulting in vertical profile (Mo).

<sup>b</sup> Anisotropy vs. isotropy: depends on many factors: reactants, etch parameters, ion energy, sidewall protection, etc.

gas pressure, and (3) condensation of the gas at the substrate. The stages of film growth following condensation of the vapor were outlined by Neugebauer (1970): (1) nucleation and island growth, (2) coalescence of islands, (3) channel formation, and (4) formation of a continuous film.

The source that contains the evaporant must have a negligible vapor pressure at the operating temperature and must not react with the evaporant. There are many types of sources and materials (Holland, 1961; Glang, 1970; Bunshah, 1982), e.g., crucibles of refractory oxides, nitrides,

carbides, and metals, refractory metal wires, and foils of various designs and shapes (Mathis Co. bulletins). Some materials, such as Cr, Mo, Pd, Si, can be sublimed which relaxes the temperature stability requirements for the source. Vaporization is accomplished by the use of resistance, induction, or electron bombardment heating; several configurations of electron guns (e-guns) are described by Bunshah. Many types are available commercially. E-guns are now used most commonly, except where radiation damage may be a problem, e.g., causing flat-band shifts in FET devices. In properly controlled e-gun evaporation, a shell of solid material shields the molten mass from the crucible, preventing interaction between the evaporant and the hearth. Multiple-pocket crucibles are also available. They may be used for sequential evaporation of different films. Or, using several guns simultaneously, with appropriate control of the source temperatures, multiple component films of a desired composition may be deposited (Glang, 1970). Alloy sources have also been used; the component ratio of the source is adjusted so that the deposited film has the required composition, although the vapor pressures of the constituents are different. The source composition is usually determined empirically. Flash evaporation, in which small quantities of the constituents in the desired ratio are completely evaporated, is another way of depositing alloy films and many kinds of dispensers have been used (Glang, 1970). However, whatever the evaporative technique, the control of the composition is rarely as reliable as that obtained by sputtering an alloy target.

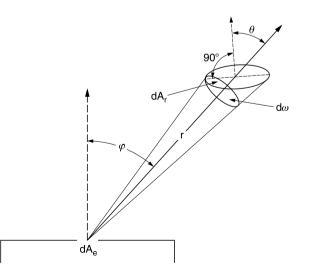

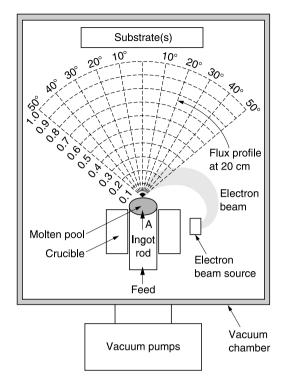

Evaporation is carried out at very low pressures, e.g.,  $10^{-5}$  to  $10^{-8}$  torr. At these low pressures, the mean free path is very large compared to the source to substrate distance, so that the transport of the vapor stream is collisionless. The emission pattern of the evaporating species is directional; it is described by a cosine law:  $dM/dA = M/\pi r^2(\cos \phi \cos \theta)$  which is illustrated in Figure 1.1. The profile of the emitted flux is shown in Figure 1.2. A comprehensive discussion can be found in Neugebauer (1970).

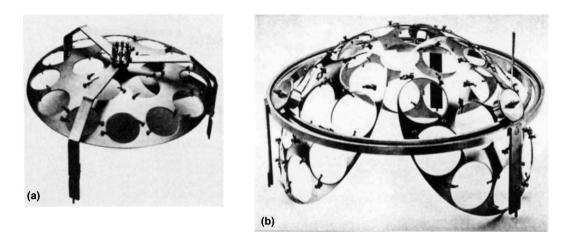

Since the thickness of the deposited film is greatest directly in line with the source and decreases to either side, uniformity requires the use of planetary (rotating) substrate holders tailored to the particular deposition requirements. Typical of the holders available commercially is the so-called normal-angle-of incidence fixture (Figure 1.3a), which is used for high uniformity and minimum step coverage, suitable for lift-off processes. Another type (Figure 1.3b) has additional planets which rotate at a higher speed and is designed for good step coverage as well as uniformity. Radiant substrate heating, using refractory wires or quartz lamps, is required because the properties

Figure 1.1 Evaporation from a point source dA<sub>e</sub> onto a receiving surface element dA<sub>r</sub>.

Figure 1.2 Profile of emitted flux. (From Bunshah, R.F., Ed., *Deposition Technologies for Films and Coatings*, Noyes Publications, Park Ridge, NJ, 1982.)

of the deposited thin films are dependent upon the deposition temperature. Temperature monitors and controllers are, therefore, also needed.

There are several kinds of thickness monitors, e.g., ionization gauges and particle impingement rate monitors, for the vapor stream. Crystal oscillators are used most frequently to measure the deposited mass; they utilize the piezoelectric properties of quartz. A thin crystal is part of an oscillator circuit so that the AC field induces thickness-shear oscillations whose frequency is inversely proportional to the crystal thickness; increasing the mass of deposit decreases the frequency. The crystal used has a specific orientation known as the AT cut, because this orientation exhibits the smallest temperature dependence. The thinner the crystal, the greater the sensitivity, if the mass deposited is small with respect to the wafer thickness. For a quartz thickness of 0.28 mm, and an initial frequency of 6 MHz, the change of frequency/thickness is 81.5 Hz/µg/cm (Wagendristel and Wang, 1994). The availability and simplicity of use makes the crystal oscillator preferable to microbalances. Interferometry is used for transparent films. For metals, optical techniques such as light absorption, transmittance and reflectance techniques, as well as resistance monitoring have also been used, but with less success. Thickness control is achieved by simply following the thickness monitor and stopping the process when the desired thickness is reached. Rate control is more complex; it requires adjustment of the source temperature, which means that a measurement and feedback mechanism is required.

The brochures supplied by equipment manufacturers are an excellent source of detailed information about the currently available evaporation systems and their operation. *In situ* sputter cleaning prior to evaporation of a metal film into a via hole is used to remove a contaminant film which causes high interfacial resistance (Bauer, 1994). When the lower surface is aluminum, the native oxide can be regrown quickly after sputter cleaning, due to the presence of residual water vapor.

**Figure 1.3** Substrate holders for evaporators: (a) normal angle of incidence fixture; (b) planetary fixture. (From Temescal Co., Airco coating technology bulletins. With permission.)

Sputtering of an aluminum electrode, before exposing the wafers to the plasma, is an efficient way of reducing the partial pressure of water vapor, thereby eliminating the need for prolonged sputter cleaning.

#### **1.3 CHEMICAL VAPOR DEPOSITION**

#### 1.3.1 Introduction

The term chemical vapor deposition, CVD, used without modifiers, refers to a thermally activated reaction. Plasma and photon activation have also been used; these processes are called plasma-enhanced CVD (PECVD) and photon-enhanced CVD (sometimes referred to as LACVD, for laser-activated CVD) and are discussed elsewhere in this chapter. The term MOCVD refers to the use of an organometallic compound as a source gas in CVD. CVD processes have been used in the preparation of both metallic and insulating thin films as well as for depositing semiconductors. There are a number of reviews that contain more detailed information than can be covered here: Kern and Ban (1978), Sherman, (1987), Mitchener and Mahawili (1987), and Jensen (1989). There is also a book by Kodas and Hampden-Smith (1994). In addition, there are individual papers collected in CVD symposia proceedings volumes of the Electrochemical Society.

Because of temperature restraints imposed by interconnnection metallization, high-temperature CVD processes cannot be used for interlevel dielectrics but have been used for (usually) doped oxides to smooth the topography beneath the first interconnection level. CVD is being used to deposit metals (e.g., W, Al, Cu, Ti), nitrides of, for example, Ti and Ta, and various silicides. Currently, important uses of CVD of metals are the deposition of (1) thin conformal metal films to line trenches (barriers and seed layers) and (2) thicker films to fill vertical via holes (the vertical interconnections are termed "plugs" or "studs") and to fill vertical vias and trenches of damascene structures.

A more recent development is atomic layer deposition (ALD) used to prepare *very* thin, continuous, conformal metal films for barriers and as seed layers in the electrodeposition of Cu. Discussions of specific CVD processes are postponed to the chapters covering the particular flms.

#### 1.3.2 Principles

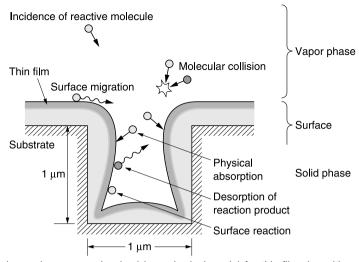

Film formation by chemical vapor deposition is a heterogeneous chemical reaction in which volatile reactants produce a solid film upon reaction at a hot surface. The sequential kinetic steps have been summarized by Jensen (1989) as follows:

"(1) mass transport in the bulk gas flow region from the reactor inlet to the deposition zone, (2) gas-phase reactions leading to the formation of film precursors, (3) mass transport of film precursors to the growth surface, (4) adsorption of film precursors on the growth surface, (5) surface diffusion of film precursors to growth sites, (6) incorporation of film constituents into growing film, (7) desorption of volatile byproducts of the surface reaction, (8) mass transport of byproducts in the bulk gas flow region away from the deposition zone toward the reactor exit."

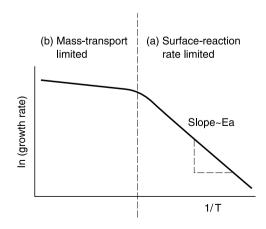

Homogeneous gas-phase reactions must be suppressed since they are responsible for the formation of dust particles which become incorporated into the growing film, making it hazy and defective. In a thermally activated reaction, the dependence of rate on the temperature is given by the Arrhenius equation:

#### $\ln (\text{rate}) = -E/RT + \text{constant}$

where E is the energy of activation. However, if the deposition rate is controlled by the transport of the reactant, the rate will be approximately independent of temperature. In many CVD reactions, two regions are observed: (1) the surface rate-limited reaction (temperature controlled) and (2) the mass transport-limited reaction (temperature independent), as illustrated in Figure 1.4. In the latter, the surface reaction is fast relative to the transport of reactants. Temperature uniformity is critical for film uniformity for the first type of reactions. For the second type flow across the wafer surface is critical.

#### 1.3.3 Reactors

#### 1.3.3.1 Classification

One way of classifying CVD reactors is by the relative temperatures of the parts of the system: there is the hot-wall system in which the substrate and reactor walls are at the same temperature, and the cold-wall system in which the substrate is at a higher temperature than the walls so that deposition occurs only on the substrate. There is the possibility of contamination by

Figure 1.4 Deposition rate vs. temperature for CVD processes.

deposition on and subsequent flaking off the heated chamber walls. As pointed out by Kern and Ban (1978), the deposit is dense and adherent, and if not permitted to become too thick the problem of flaking may not be severe, particularly since there is no thermal cycling. Also, since the wafers are stacked vertically, any flakes would not be likely to fall on them. In the cold-wall reactor, this source of contamination is negligible, but convection due to temperature differentials can arise (Carlsson, 1985).

Another classification scheme is in terms of the pressure at which a reactor is operated. The earlier classifications were atmospheric pressure (APCVD) and low pressure (LPCVD) which covers a pressure range of about 0.05 torr to several torr. More recently, particularly for the deposition of SiO<sub>2</sub> films, both sub-atmospheric (SACVD; ~600 torr) and intermediate pressure (no acronym; ~60 torr) have been used. At higher pressures, the rates of mass transfer of the volatile reactants and byproducts and of reaction at the surface are about the same order of magnitude. Reducing the pressure increases the mass transfer rate so that reaction at the surface becomes the rate-limiting step. Reactor configuration greatly influences mass transport and thus is a critical factor for APCVD, but not for LPCVD. Uniform deposition is more easily achieved in LPCVD but the deposition rates are much lower than in APCVD.

Another way of classifying a reactor is by the deposition temperature: high temperature (HTCVD; ~750 to 950°C) and low temperature (LTCVD; below ~500°C). It can be seen that there are many possible combinations for CVD reactor and process design.

#### 1.3.3.2 Examples of Reactors

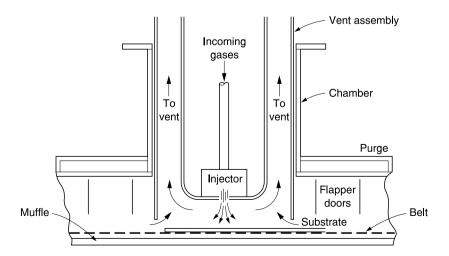

Winkle and Nelson (1981) described a cold-wall low-temperature (LT) APCVD reactor, made by Watkins-Johnson. It is used for depositing undoped and P-doped SiO<sub>2</sub> and is shown in Figure 1.5. At temperatures of ~350 to 450°C, deposition rates as high as ~1  $\mu$ m/min were achieved using mixtures of O<sub>2</sub> and the appropriate hydrides. A feature of this reactor is the gas injector design which improves surface reaction uniformity and coating efficiency and prevents homogeneous gas phase reactions.

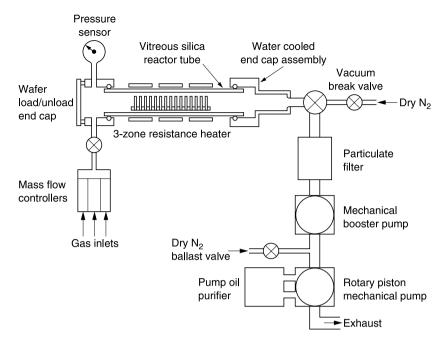

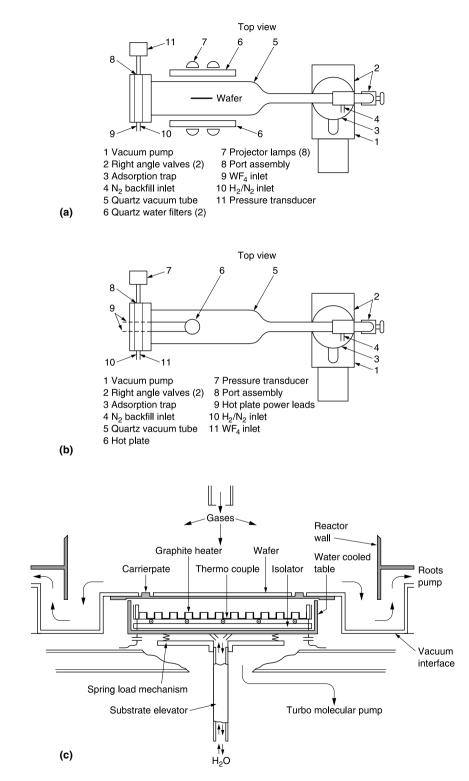

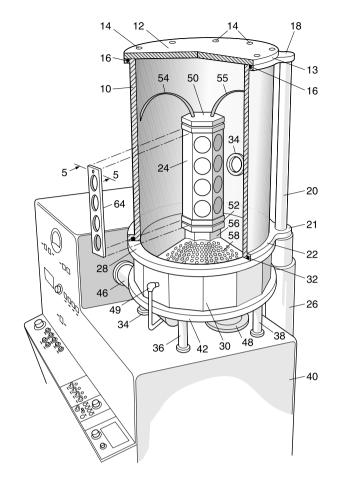

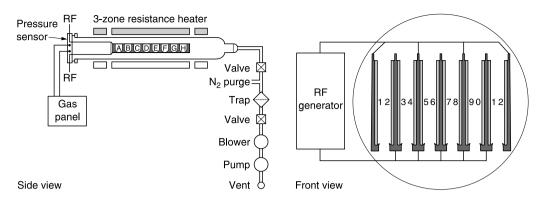

An example of a hot-wall LPCVD system is shown in Figure 1.6; this is typical of reactors used to deposit insulators and metals. Two versions of an experimental single-wafer, LP cold-wall reactor, designed for selective W deposition from  $WF_6$  and  $H_2$ , are shown in Figure 1.7 (Stoll and Wilson, 1986). In the system in Figure 1.7a, the substrate is heated radiantly by means of quartz lamps; in

Figure 1.5 Schematic of an APCVD reactor. (Watkins-Johnson.)

Figure 1.6 Schematic of an LPCVD reactor. (Reproduced from Kern, W. and G.L. Schnable, IEEE *Trans. Electron Dev.*, ED-26, 647, 1979. With permission of the Electrochemical Society, Inc.)

that in Figure 1.7b the wafer is heated on a hot plate. Another system (Heiber and Stolz, 1987) was an adaptation of a sputtering module and was equipped with a load lock, as shown in Figure 1.7c

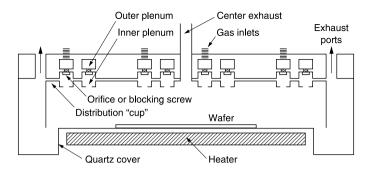

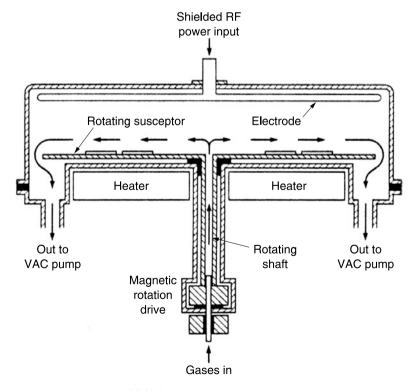

A commercially available, single-wafer, cluster-compatible, cold-wall LPCVD chamber is the Watkins-Johnson SELECT<sup>TM</sup> reactor shown in Figure 1.8, in which the wafer rests on a quartz cover and is heated by an encapsulated three-zone graphite heater. The system pressure is about 1 torr, and has been used to deposit SiO<sub>2</sub> doped with both P and B (BPSG) from SiH<sub>4</sub> and O<sub>2</sub>.

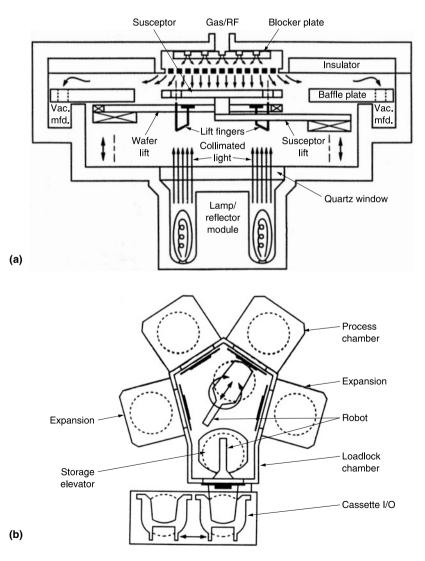

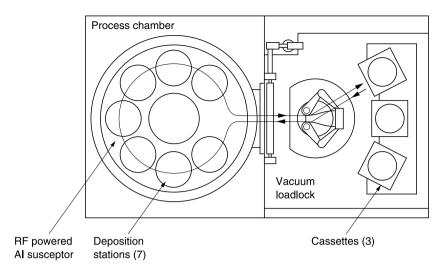

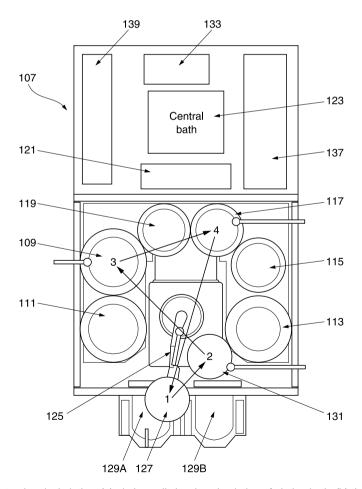

Another commercially available, load-locked, single-wafer, cold-wall reactor is the Applied Materials Precision 5000 system shown in Figure 1.9a; it has been integrated into a "cluster tool" (Figure 1.9b). This reactor has been used for blanket W deposition from  $WF_6$  and  $H_2$  at 10 to 80 torr (Clark et al., 1991) and for SiO<sub>2</sub> (doped and undoped) from TEOS + O<sub>3</sub> (plus dopants) at 60 torr or at 600 torr (SACVD) (Lee et al., 1992). For these applications, the radio-frequency (RF) feed-through shown in the diagram is not used. This thermal CVD/PECVD reactor is covered by patents (Wang et al., 1989, 1991).

#### 1.3.4 Film Properties

The composition and purity of a film, its electrical and mechanical properties, the deposition rate, and its uniformity are controlled by the many variables involved and the interaction among them is complex and difficult to categorize. The reviews cited above contain more detailed information. Some discussion of specific films can be found in Chapter 4 and Chapter 5.

#### **1.4 PHOTOENHANCED CVD**

True photochemical processes depend on the fragmentation/activation of the reactant molecules, in the gas phase or on the surface, by photons. The advantage of photoinduced reactions is

**Figure 1.7** Experimental cold-wall CVD reactors. (a) Tungsten filament lamp heating; (b) hot plate heating. (From Stoll and Wilson (1986). With permission of the Electrochemical Society, Inc.) (c) Single-wafer cold-wall system with load lock. (From Hieber, K. and M. Stolz, 1987 VMIC, 1987, p. 216. With permission.)

Figure 1.8 Schematic of a single-wafer CVD system: Watkins-Johnson Select™.

**Figure 1.9** Schematic of an Applied Materials Precision 5000<sup>™</sup> single-wafer CVD reactor: (a) side view of an individual chamber; (b) top view of the cluster system configuration.

the absence of electromagnetic radiation and charged species which can induce damage in dielectric films. To quote Eden (1991):

Optical radiation can induce specific chemical reactions in the gas phase or at a surface. The selective production of atoms, radicals or other excited species in the vicinity of a surface independently of the substrate temperature, effectively decouples temperature from the number density of the species of interest. The introduction of photons allows one to drive the chemical environment far from equilibrium by selectively producing species not normally present in conventional CVD reactors.

In some cases, radiation merely heats the surface and the process is, in reality, thermally activated LPCVD, although the process may be localized to some degree if the light source is very narrow. If the light source simply heats the source gases, thermal fragmentation occurs as in conventional CVD processes. Ultraviolet (UV) and vacuum ultraviolet (VUV) lamps and lasers are used as energy sources. Photo-CVD has not, at least up to now, been used in production because the deposition rates are low and therefore the process is expensive.

#### **1.5 PLASMA PROCESSING**

#### 1.5.1 Introduction

Plasma processing has become essential for depositing and etching the materials used in building semiconductor devices. The low-plasma-density capacitively coupled discharge was used exclusively in fabrication until recently, when high-plasma-density reactors became available commercially. Specific applications are discussed in Chapter 4 to Chapter 6. The reliability issues associated with plasma processing, e.g., contamination, electrical damage, surface modification, are covered in the chapters on reliability and contamination.

#### 1.5.2 Capacitively Coupled RF Glow Discharge

When an increasing RF voltage is applied between electrodes in a low-pressure (~10 to 1000 mtorr) gas, ultimately the gas breaks down, i.e., it ionizes and current flows. A glow is observed. Adjacent to the electrodes are dark spaces, the sheaths, and a voltage drop occurs across the sheath regions. The glow region is virtually field-free; there are approximately equal numbers of positive and negative charges. Electron impact dissociation produces not only ions but also photons, free radicals, and metastables (the neutral species). The potential in this plasma region is the most positive potential in the system. Thus all electrodes (which may include the chamber walls) have a negative potential with respect to the plasma and are all bombarded by positive ions. Sputtering of the surfaces is a source of contamination making the choice of reactor materials an important issue (Vossen, 1979; Oehrlein, 1989). The relative potential (bias) developed at each electrode determines the ion bombardment energy; this is a function of their areas. If the electrodes have equal areas (symmetrical reactors), the voltage, i.e., the DC bias, is the same on both so that both are bombarded by ions of equal energy (Vossen, 1979) and the plasma potential is relatively high; the point of attachment of the power is irrelevant.

When the electrodes are unequal in area, the DC voltage is higher on the smaller one (Koenig and Maissel, 1970); if the area of one electrode is very much smaller than the other (called asymmetric systems), the bias on the small electrode is approximately one half the peak-to-peak applied voltage. The high-bias electrode is usually called the cathode. The plasma potential is low; the potential of the plasma and that of the larger electrode are approximately equal. Thus the ion bombardment energy at the very large electrode is low, but not zero. For convenience and safety, the smaller electrode is powered and the chamber (counter-electrode) is grounded. However, the ion bombardment on a specific electrode does not depend on which electrode is powered (Coburn and Kohler, 1987), although the plasma potential is higher when the larger electrode is powered.

In addition to the electrode potentials there is the floating potential which exists on all surfaces, neither externally biased nor grounded. This is a function of the electron mass and temperature and of the ion mass and charge.

The plasma in these reactors is a nonequilibrium plasma in which the temperature of the electrons is much higher than the temperature of the gas. The plasma density is low  $\sim 10^9$  to  $10^{11}$  cm<sup>-3</sup> and the fractional ion density (i.e., the ratio of ion to neutral species) is low ( $\sim 10^{-6}$  to  $10^{-3}$ ).

#### 1.5.2.1 Frequencies

A range of frequencies has been used, from 50 kHz to 2.54 GHz (microwave); 13.56 MHz (or multiples) is the most commonly used frequency (no interference with communications). However, Goto et al. (1992) preferred to treat the frequency as a process parameter and have investigated the 10 to 215 MHz range. Martinu et al. (1989) used microwave (2.54 GHz) excitation. Colgan et al. (1994) suggested the use of very high-frequency capacitive discharges to obtain high plasma densities at low ion energy. An ultrahigh-frequency (UHF) 500 MHz discharge has been used in conjunction with a new antenna. In the low-frequency range, electrons and ions follow the electric field and the ions experience the full amplitude of the RF voltage resulting in higher bombardment energy of the electrode. Above  $\sim$ 3 MHz ions can no longer follow the field, as do the electrons. The ions interact only with the time-averaged field since it takes several RF cycles to cross the sheath. Therefore, the average energy is reduced and the electrode is bombarded with lower energy ions. However, at higher frequencies, energy coupling is more efficient so that, for a given power, the plasma densities are greater than at lower frequencies. At low frequencies the peak energy of the ions is greater than at high frequencies but the energy distribution is broader (Bruce, 1981; Coburn and Kohler, 1987; Hey et al., 1990; Meyers et al., 1994). At low frequencies the angular distribution of the ions is more directional than at higher frequencies (Meyers et al., 1994).

A two-frequency or dual-excitation mode in which both frequencies are applied simultaneously is now used frequently for independent control of the substrate bias in both reactive plasma-enhanced etching and deposition. The excitation electrode may be powered using the higher frequency and the substrate electrode powered with the lower (using appropriate filter networks). A variety of combinations have been used, e.g., 13.56 MHz/200 kHz (Tsukune et al., 1986), 13.56 MHz/450 kHz (van de Ven et al., 1988, 1990), 2.54 GHz/13.56 MHz (Martinu et al., 1989), 100 MHz/30 MHz (Goto et al., 1992). In an electrically equivalent mode of operation, *both* frequencies are fed to one electrode, e.g., 13.56 MHz/450 kHz, (Hey et al., 1990), 13.56 MHz/350 kHz (Matsuda et al., 1996).

#### 1.5.2.2 Reactor Requirements

Whatever the electrical configuration of the reactors, whether inert or reactive gases are used, and whether used for etching or for deposition, the reactors have many features in common. Some of these are (1) the reaction chamber with the associated vacuum apparatus, e.g., pumps, pressure controllers/monitors, and the gas distribution systems with the appropriate control and monitoring equipment and (2) the glow discharge generation equipment consisting of power source(s) and, where required, an impedance matching network for efficient power transfer. It should be noted that the power to the glow discharge may be significantly less than the input power due to (undetermined) losses in the matching network (Logan, 1990) There is optional equipment for following the processes: rate monitors, e.g., interferometers, grating patterns, etc., which can act as end-point detectors in some cases. Particularly in reactive plasma etching processes, there are several other kinds of end-point detectors, e.g., optical emission spectroscopy (OES), discharge impedance and pressure monitoring systems, etc., as well as plasma diagnostic equipment, e.g., OES, mass

spectrometry, and laser-induced fluorescence spectrometry. Unfortunately much of this equipment is often not compatible with the configuration of reactors used for manufacturing.

Many of the newer reactors used in manufacturing are integrated into multichamber processing systems (cluster tools) in which each chamber processes a single wafer (Singer, 1993, 1995). These provide not only load-locked entry into the first chamber and exit from the last but also vacuum transfer between chambers. *In situ* plasma-cleaning capability is often a feature of such systems. The chambers in the system shown in Figure 1.12b, into which a CVD reactor was incorporated, have been configured for plasma processing (PECVD and inert or reactive plasma etching) as well.

#### 1.5.2.3 Capacitively Coupled Reactors

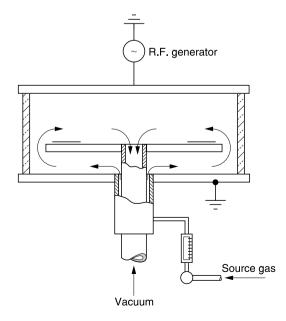

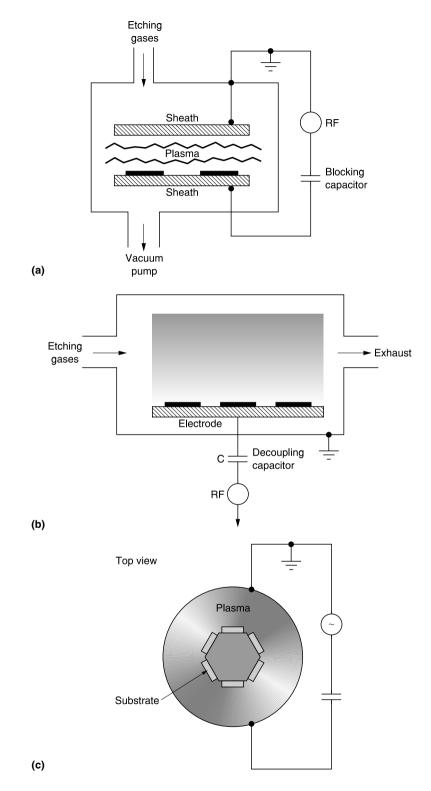

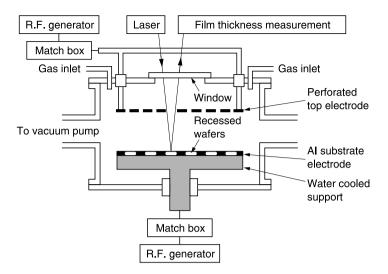

The earliest reactors for the commercial production of chips are what have been called planar or parallel plate diode reactors with an internal electrode capacitively coupled to an RF source. In symmetrical systems, used frequently in reactive plasma-assisted processing, there are actually two flat electrodes inside a dielectric chamber; one is powered and the other, on which the wafers are placed, is grounded. These systems are based on the radial flow reactor patented by Reinberg (1973) and are usually operated at relatively high pressures (several hundred millitorr). A schematic representation of the reactor is shown in Figure 1.10.

Asymmetrical reactors were developed for sputter deposition and etching. In these reactors there may be a counter-electrode connected to the grounded chamber enclosure (Figure 1.11a), or the grounded enclosure itself acts as the counter-electrode, as shown in Figure 1.11b. Both are called planar diodes and are operated at relatively lower pressures (tens of millitorr). An axial configuration, the so-called hexode reactor, patented by Maydan (1981) is electrically equivalent to an asymmetric planar diode system. A schematic representation of the hexode is shown in Figure 1.11c, and a sketch of the reactor, taken from the patent, is shown in Figure 1.11d.

Figure 1.10 Reinberg's radial flow reactor. (From Reinberg, A.R., U.S. Patent 3,757,733, 1973.)

**Figure 1.11** (a) Capacitively coupled asymmetric reactor. (b) Capacitively coupled reactor used for RIE. (c) Schematic of a hexode reactor. (d) Sketch of an actual hexode reactor.

(d)

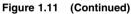

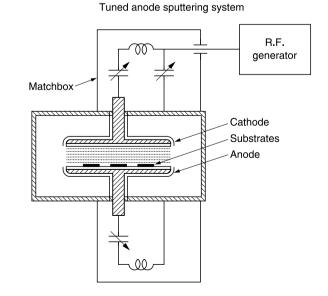

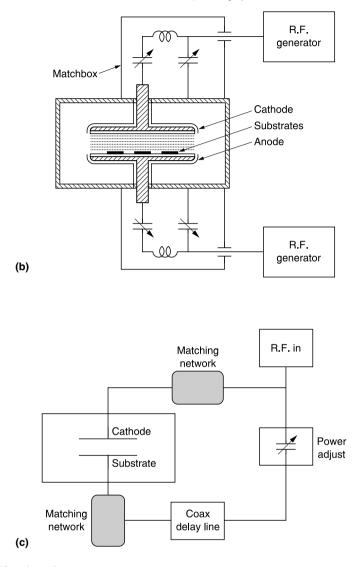

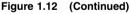

**Figure 1.12** (a) Schematic of a tuned anode sputtering system. (b) Schematic of a driven anode sputtering system with two generators. (c) Power-splitting RF drive for driven anode system.

© 2006 by Taylor & Francis Group, LLC

(a)

Driven anode sputtering system

The dual-frequency mode of operation is described above. The triode system is an extension of the diode reactor; a third electrode is added so that the substrate bias can be controlled essentially independently of the excitation energy, using the same or a different frequency. Reactors of this kind have been called substrate-biased reactors. Substrate biasing is used to improve the properties of the deposited material. The chamber walls are grounded and the target and substrate are isolated. Two versions of a triode have been used for bias-sputtered oxide deposition: the tuned-substrate in which the bias at the substrate is controlled by a tuning network (Figure 1.12a); and the driven system in which both electrodes are powered using two RF generators (Figure 1.12b) or a single power supply and a power-splitting network (Figure 1.12c). One version, the flexible diode, shown in Figure 1.13, is a planar reactor used for etching (Ephrath, 1981a).

Figure 1.13 Schematic of a flexible diode RIE reactor (From Ephrath, L.M., IEEE *Trans. Electron Dev.*, ED-28, 1315, 1981.)

#### 1.5.2.4 Magnetic Confinement

Magnetic confinement is used to obtain a high plasma density, higher ion/neutral ratio at relatively low voltages and at lower pressure than in an unconfined system. The magnetic field confines the electrons in the discharge.

#### 1.5.2.4.1 Magnetrons

Axial magnetic fields used with a planar diode increase the path length of the electrons and keep them away from the chamber walls. In magnetron sputtering systems, the object is to trap electrons near the target to increase their ionizing effect, thus increasing the deposition rate. The electric and magnetic fields are usually perpendicular (Chapman, 1980).

The many magnetron configurations, cylindrical, circular (sputter-gun and S-gun), and planar, used for sputtering, are described extensively in Kern and Ban (1978) and in Chapman (1980). A high-vacuum planar magnetron discharge, operating at pressures at or below 1 mtorr, but with reasonable deposition rates, has been described by Asamaki et al. (1992, 1993).

Magnetron reactors in which the magnetic field lines are parallel to the cathode surface are used for reactive ion etching (RIE); these systems have been called magnetically enhanced RIE (MERIE) and magnetron ion etcher (MIE) systems. Among the various magnet configurations are the planar (Hinson et al., 1983), band, quadrupole (Hill and Hinson, 1985), and annular (Kinoshita et al., 1986).

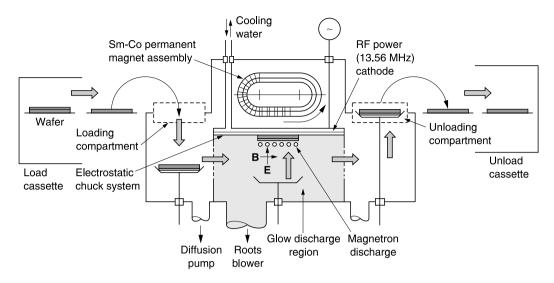

An example of a single-wafer magnetron RIE system (Schultheis, 1985) is shown in Figure 1.14.

#### 1.5.2.4.2 Multipoles

Multipolar confinement or surface magnetic field confinement is one in which the chamber walls and sometimes an end wall are lined with strong permanent magnets arranged in an alternating N–S arrangement, used with several kinds of reactors.

The magnets produce a series of magnetic cusps around the wall, in effect forming a magnetic bottle (Mantei and Wicker, 1983; Mantei et al., 1985; Wicker and Mantei, 1985; Kuypers et al., 1988).

Figure 1.14 Schematic of a single-wafer magnetron RIE system. (From Schultheis, S., *Solid State Technol.*, 4/85, 233, 1985.)

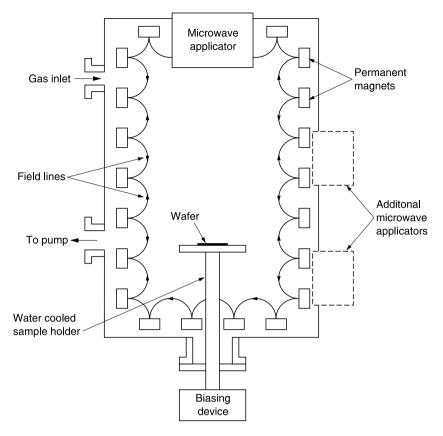

The charged species are reflected by the magnetic mirror into the plasma away from the walls. In one of the multipolar reactors using a hot filament discharge, there is an increase in the plasma density of a factor of about 100 and a reduction of operating pressure to about 1 mtorr. Figure 1.15 shows a multipolar microwave reactor.

Another use of multipoles is in the magnetically confined reactor (MCR). This is a triode etcher, 13.56 MHz applied to the annular electrode and 100 kHz applied to the wafer holder and the common top electrode is grounded. The multipoles are arranged around the chamber walls and embedded in the top electrode (Engelhardt et al., 1990; Engelhardt, 1991). A similar arrangement of a grounded cylindrical multipolar bucket, but using the same frequency at both electrodes, in a triode reactor was described by Singh et al. (1992a).

Multipolar confinement has also been used with high-density discharges, which are discussed below.

#### 1.5.2.5 Hollow Cathode

A modification of the capacitively coupled reactor is the hollow cathode (HC) configuration (Horwitz, 1989a,b; Gross and Horwitz, 1993). Plasma confinement is provided by opposing RF-powered electrodes, which increases the utilization of the ions in the discharge and provides an electron mirror by which secondary electrons are trapped. This configuration makes it possible to operate a high-plasma-density, low-voltage discharge at low pressure. This kind of system has not been developed commercially.

#### 1.5.3 Temperature Effects

#### 1.5.3.1 Heating

Bombardment by energetic ions heats a surface. In low-pressure environments, the heat transfer between the wafer and its holder is poor, unless a heat-conducting medium (e.g., thermal grease, a moderate pressure of He) is interposed between. The temperature rise is proportional to the ion

19

**Figure 1.15** Schematic of a multipolar microwave plasma processing chamber. (From Asmussen, J., in *Handbook of Plasma Processing Technology*, Rossnagel, S.M., Cuomo, J.J., and Westwood, W.D., Eds., Noyes Publications, Park Ridge, NJ, 1989, chap. 11.)

energy, e.g., the input RF power in sputter etching (Schwartz and Schaible, 1981) or the sheath voltage in ion-driven reactive etch processes (Fortuno, 1986). If the wafers are exposed at the same time to a plasma, and one is bombarded with the full ion energy and the other is shielded, the temperature of the first wafer is significantly higher.

#### 1.5.3.2 Temperature Control

Since many of the recently developed processes require either cooling the wafer or keeping it at a constant, uniform, and reproducible temperature, wafer clamps have been used in many reactors. At first the wafers were mechanically clamped by a ring on the topside of the wafer to the temperature-controlled wafer holder (Hinson et al., 1983; Katetomo et al., 1992), but the purely mechanical contact was often found to be inadequate. The next advance was the use of several torr of a heat-transfer gas (Wright et al., 1992), often helium, forced across the backside of the mechanically clamped wafer, as shown in Figure 1.16. However, the topside ring covers a portion of the edge of the wafer; in addition the ring may be responsible for increased contamination and nonuniformity.

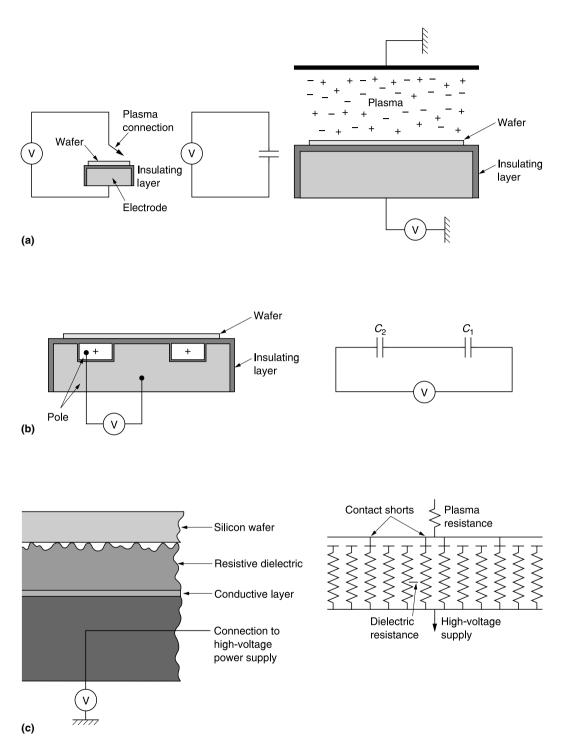

Electrostatic wafer clamping is now the usual choice. This technique, which had been used earlier for, for example, holding a wafer during transport (Lewin, 1985; Kumagai, 1988; Nakasuji and Shimizu, 1992) and during lithographic processing (Clemens and Hong, 1991), uses the attractive

Figure 1.16 Schematic of a mechanical clamp with helium backside cooling. (From Field, J., *Solid State Technol.*, 9/94, 21, 1994. With permission.)

force between the charged plates of a capacitor to hold the wafer in place. This chuck can be installed in a plasma reactor, eliminating the need for a topside clamp, while maintaining the flow of gas across its back. There are several configurations, described by Field (1994). The configurations and equivalent circuits are shown in Figure 1.17. For each type, Field has also discussed the advantages and disadvantages, such as declamping time and device damage. There are numerous patents describing the materials used for fabricating electrostatic chucks, their structures, as well as the methods of applying the voltage. Several do not state a particular application (Lewin and Plummer, 1985a; Lewin, 1985; Ward and Lewin, 1987; Suzuki, 1987; Logan et al., 1991; Horwitz and Boronkay, 1992; Watanabe and Kitabayashi, 1992; Liporace and Seirmarco, 1992; Hongoh and Kondo, 1993; Logan et al., 1993; Barnes et al., 1993; Collins and Gritters, 1994). Others are specifically for use in a plasma reactor (Nozawa et al., 1993; Arami and Ito, 1994; Su et al., 1994).

#### 1.5.4 Sputtering

#### 1.5.4.1 Introduction

Sputtering is a physical process (Wehner and Anderson, 1970; Maissel, 1970; Vossen and Cuomo, 1978; Chapman, 1980; Logan, 1990; Wasa and Hayakawa, 1992) in which the positive ions in a glow discharge strike a surface and eject atoms from it by momentum transfer. About 1% of the incident energy goes into particle ejection, about 75% into heating the bombarded surface, and the rest is dissipated by secondary electrons which heat the substrate (Vossen and Cuomo, 1978). Ejection occurs when the kinetic energy of the incoming ions exceeds the binding energy of the surface atoms of a solid. Sputtering is the result of a collision cascade, a sequence of independent binary collisions; it is not a simple interaction between an incoming ion and a surface atom.

#### 1.5.4.2 Sputter Deposition

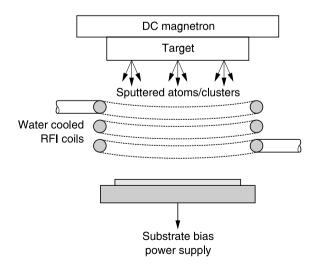

Sputter deposition has almost always been carried out in a capacitively coupled reactor, often with magnetic enhancement and independent substrate bias control. Recently, high-density plasma reactors have supplanted these systems for some applications.

#### 1.5.4.2.1 Sputtering Target

The solid from which the atoms are ejected is termed the "target." When used as a sputtering target for film deposition, a dense target is preferred, to eliminate the possibility of contamination, although for some materials only sintered, hot-pressed, or powder targets may be available. Since the target is heated by the bombarding ions, the backing electrode to which the target is bonded must be cooled, and the bonding material must be a good heat-transfer medium that will not be a source of contamination. Shields, often called ground shields or dark space shields, surround the back of the

Figure 1.17 Schematic of electrostatic wafer clamps with equivalent circuits: (a) unipolar; (b) bipolar; (c) Johnsen–Rahbek configuration.

target (placed at such a distance that no discharge will be initiated in that space) to suppress sputtering of the backing material; some shield configurations are illustrated in Chapman (1980).

#### 1.5.4.2.2 Threshold Energy

The minimum ion energy required for sputtering is called the threshold energy which depends on the heat of sublimation of the target material; it is relatively insensitive to the nature of the bombarding ions. The sputtered material is usually monatomic, although diatomic species (e.g., SiO from an SiO<sub>2</sub> target (Coburn et al., 1974)) have been detected. In most sputtering processes, the ion source is solely an inert gas, most often argon, but in reactive sputtering (discussed more completely below)  $O_2$  or  $N_2$  is added, depending on the material to be deposited.

#### 1.5.4.2.3 Yield

The sputtering yield is the number of atoms ejected for each incoming ion; it increases with ion energy, exponentially at lower energies and then linearly, reaching a plateau and finally decreasing at very high energy. In the low energy range of exponential increase, the yields are very low, reaching ~0.1 in the energy range used in practical sputtering. Although it is often the case that the sputtering yield increases with increasing mass of the bombarding ion, as the oft-quoted results of Almen and Bruce (1961) for inert gas ion sputtering of copper indicate, this does not appear to be true for all substrates, as perusal of sputtering yield tables reveals (Vossen and Cuomo, 1978). Molecular ions dissociate into energetic atoms upon impact with the target surface and behave as though the individual atoms arrived separately. That is, an ion  $X_i^+$  at an energy *E* has the same sputtering effect as *i*  $X^+$  ions at energy *E*/*i* (Steinbruchel, 1984). The sputtering yield of neutral species is the same as the corresponding ion. The effect of the angle of incidence is discussed in a separate section.

#### 1.5.4.2.4 Film Composition

The composition of the deposited film is usually the same as that of a homogeneous target. In the case of an alloy target, composed of atoms of different sputtering yields, an altered layer forms at the surface of the target. Initially, the component with the highest sputtering yield is preferentially removed, leaving the surface enriched with the lower sputtering yield component. At steady state, the composition of the material sputtered from the altered layer onto the substrate is the same as that of the bulk target. However, if there is significant preferential resputtering from the substrate surface and/or diffusion at the target surface, the composition of the deposited film will differ from that of the source. If one of the components of the target is volatile, ion heating of the target may result in a difference in stoichiometry between the target and deposit; addition of the volatile component to the sputtering gas can compensate for this.

#### 1.5.4.2.5 Effect of Operating Conditions

Raising the gas pressure increases the number of ions (ion current) for sputtering and, although the energy of the ions decreases, the net result is an increase in deposition rate, because the yield decreases slowly with decreasing energy in the energy range used for sputtering. At some pressure, however, backscattering in the gas will result in a rate decrease.

The flow rate of the gas does not directly affect the deposition rate, but some contaminants (from the vacuum chamber or desorbed/sputtered from the target), which would be swept out in a high flow, do affect the rate: e.g., a small partial pressure of  $O_2$  reduces the deposition rate of  $SiO_2$  significantly (Jones et al., 1968). And removing the contaminants also reduces the probability of incorporating them into the growing film and degrading its properties.

Increasing the source-to-substrate distance reduces the accumulation rate but improves uniformity. The net accumulation rate decreases with increasing substrate temperature. The use of the term accumulation rate takes into account the fact that, in some instances, not all of the material sputtered from the target and arriving at the substrate remains on the surface; some of it may be resputtered or reemitted thermally.

Metals may be sputtered in a DC glow discharge, but when insulators are exposed to a DC plasma a positive charge accumulates on the surface preventing further positive ion bombardment. The use of RF sputtering, in which an RF potential is applied to a cooled metal electrode to which the insulating target is bonded, circumvents this problem. A grounded metal shield prevents sputtering from the edges of the metal electrode. In sputtering, the use of frequencies higher than 13.56 MHz can be advantageous. At higher frequencies, the ion current increases but the ion energy decreases, resulting in higher deposition rates at lower target voltages. Lowering the target voltage reduces the energy of the secondary electrons produced at the target, and substrate heating due to secondary electrons is also reduced.

#### 1.5.4.2.6 Advantages of Sputter Deposition

There are a number of advantages to sputtering: (1) controlled stoichiometry of the deposit, (2) easy sputter cleaning of the substrates, (3) improved adhesion, (4) better control of film thickness, and (5) use of bias sputtering for improving the physical properties of the films and for step coverage/gap-fill. The improvement in film properties by the use of substrate bias can be related to the removal by the impinging ions of atoms trapped in nonoptimal surface sites and that of gap-fill/step coverage to the angle dependence of the sputtering yield and perhaps by the elevated temperature resulting from ion bombardment heating.

#### 1.5.4.2.7 Temperature Effects

Since many film properties are influenced by the deposition temperature, temperature control is desirable. Substrate holders may be cooled or heated by various techniques, but it must emphasized that, since the substrates are heated by ion bombardment and secondary electrons, their temperatures may be different from that of the holder, unless a heat transfer medium is interposed between them. The review by Lamont (1979) contains a more extended discussion of the thermal history of substrates during sputter deposition and etching. Accurate measurement of the surface temperature is possible using fluoroptic probes, but they are difficult to implement in a system used in manufacturing, so their use in feedback controls may not be possible. Monitoring and controlling the holder temperature is more feasible, but is only meaningful when there is excellent thermal contact between it and the wafer.

#### 1.5.4.2.8 Reactive Sputtering

Reactive sputter deposition is one way of depositing an insulator in a DC sputtering system, although RF reactive sputtering is more common. In reactive sputtering, a metal target is sputtered in a mixture of an inert gas and the appropriate reactive constituent. One reason for preferring reactive sputtering is that metal targets are usually denser and more easily fabricated than compound targets. In addition, by changing the sputtering gas mixture, several compounds can be deposited using the same target. The reaction to form the required compound may occur on the target surface, in the gas phase (unlikely), or at the substrate. Since sputtering rates of metals are higher than those of oxides, it is best to adjust conditions so that reaction occurs at the substrate; this occurs at low reactive gas partial pressure and high target sputtering rates. This effect was utilized for high-rate deposition of  $Al_2O_3$ , which has a particularly low sputter yield (Jones and Logan, 1989). The stoichiometry of the film is a function of the relative arrival rates at the substrate.

#### 1.5.4.2.9 Collimated Sputtering

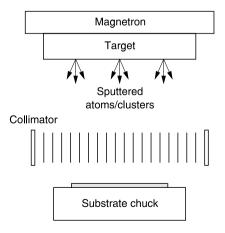

In sputter deposition, a large fraction of the particles impinging on the substrate do not arrive at normal incidence because the atoms are emitted from the sputtering target in a cosine distribution and pressures are such that gas scattering is significant. To reduce the angular distribution of the impinging species, so that high-aspect-ratio (AR) features can be filled adequately, a collimator (an array of directional filters) can be placed between the sputtering target and the substrate in a magnetron system (Rossnagel et al., 1991; Cheng et al., 1995). A schematic of such a reactor is shown in Figure 1.18. Increasing the AR of the collimator increases the directionality of the deposit. In a modification called "dual collimation" (Kools et al., 1999) the target-to-substrate distance was similar to the target dimension and the collimator placed relatively close to the wafer (out of the plasma). It was stated that this configuration reduced the build-up, since fewer of the atoms emitted at off-normal angles reach it. In addition, the position out of the plasma reduced thermal cycling (particle generation).

Further discussion of the use of collimated sputtering for enhanced edge and bottom coverage of etched features is found in Chapter 6.

#### 1.5.4.2.10 Long Target-to-Substrate Distance Sputtering

An alternative to collimated sputtering is sputtering using a wide separation between the target and substrate, a low pressure (~1 mtorr), a smaller target (to mimic a point source), and, possibly, a light sputtering gas. These modifications result in a narrow angular distribution of the sputtered species. The application of this technique, called long target-to-substrate (T/S) distance sputtering or long-throw distance sputtering, is discussed in Chapter 6.

Rossnagel (1998) has written a comprehensive review of physical vapor deposition, including both collimated and T/S distance sputtering.

#### 1.5.4.2.11 Self-Sputtering

In this technique, used for depositing metals, ions of the same element are used in the absence of an inert gas. Further discussion is contained in Chapter 6.

Figure 1.18 Cross-section of magnetron sputtering system with (grounded) collimators. (From Rossnagel S.M., D. Mikalsen, H. Kinoshite, J.J. Cuoma, *J. Vac. Sci. Technol.*, A9, 261 1991.)

#### 1.5.4.2.12 Conclusions

Although insulator films of excellent quality can be deposited by sputtering at low temperatures, defined as temperatures compatible with aluminum alloy metallization, there are a number of disadvantages to sputter deposition as practiced traditionally. One is high cost. Batch systems were used, and although such systems can be very large, the throughput is quite low. Load locks are difficult to implement in such systems so that flaking from the chamber walls during wafer load/unload becomes a major reliability problem when the flakes become incorporated into the film. The wafer temperature is a function of the input power. In order to increase the deposition rate to meet the demands of higher throughput, the power must be increased; this often results in an excessive rise in wafer temperature. Helium backside temperature control of wafer temperature is impossible to implement in batch systems. Step coverage and gap-filling capabilities are limited (although they are superior to single-pass PECVD and early low-temperature CVD) and even marginal improvement requires much extended processing time. This last is probably responsible for the lack of interest in further development of advanced reactors and in the use of sputtering for insulator deposition.

Also, there have been major improvements in alternative insulator deposition methods with, apparently, costs lower than traditional sputtering. Better low-temperature CVD and PECVD reactors and processes have been developed. The dielectric and physical properties of the films have been improved significantly, although the properties of some of them are still inferior to sputtered films. Reasonable throughput multistep processes for gap fill have been developed. In addition there has been great activity in the commercial development of high-density plasma reactors for gap-fill capability. Understanding of the interactions of reactor, process, and film properties is progressing. These factors, plus the integration of many of the processes into high-throughput, single-wafer, often integrated-chamber reactors, have essentially eliminated sputtering for insulator deposition.

Sputter deposition of metals has almost completely superceded the previously ubiquitous process of evaporation, despite the greater complexity of sputtering systems (the need for the networks in addition to the vacuum apparatus). For the most part, deposition is carried out in integrated systems, in which the individual chambers have been configured to meet the objectives of high film quality and gap-fill, e.g., bias, magnetron, high temperature, collimated, and long target-to-substrate sputtering, with vacuum transport among the various deposition chambers (if several metals are to be deposited sequentially) and to etching and annealing chambers where needed; in addition there are entrance and exit load locks.

#### 1.5.4.3 Sputter Etching; Ion Milling

#### 1.5.4.3.1 Introduction

Etching by means of inert ion bombardment is usually performed in a capacitively coupled diode system, which is essentially an RF sputtering system in which the wafers are placed on a holder that takes the place of the target in a deposition system. In some systems, the wafers are held against the upper electrode (cathode) facing the anode. A more convenient arrangement is one in which the wafers are placed on the lower electrode (cathode) and the chamber itself is the counter-electrode.

Another method of bombarding a substrate with ions is in an ion milling or ion beam etching system. There are several types of ion sources, among which are the Kaufman, Penning, duoplasmatron, hollow anode, and glow discharge, all of which have been described by Harper (1978).

#### 1.5.4.3.2 Applications Other Than Pattern Transfer

Sputter etching in an inert plasma can be used for patterning, but is also used to clean surfaces before subsequent processing, e.g., *in situ* sputter cleaning, which minimizes interface resistance by

removing an insulating surface layer from a metal before deposition of a second metal. It has also been used to roughen a surface to enhance adhesion of a second layer.

Ion milling is used in depth profiling for Auger and x-ray photoelectron spectroscopy surface analysis and as part of the process in secondary ion mass spectrometry. Other uses of sputter etching are in a process called PECVD/sputter etch and in bias sputtering and biased high-density-plasma deposition. These take advantage of the angle-dependent sputter yield in increasing the acceptance angle for incoming species. This is discussed in detail in a later section.

#### 1.5.4.3.3 Pattern Transfer

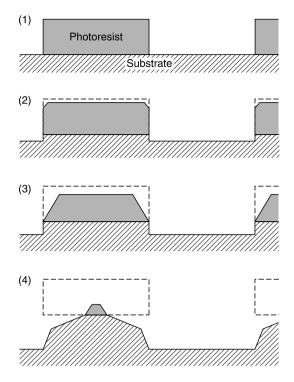

In this section, pattern transfer by sputter etching in a glow discharge or by ion milling is treated. Patterning by sputter etching is carried out in an RF discharge by bombarding the masked substrates with positive ions formed by excitation of an inert gas (Davidse, 1971).

One of the theoretical advantages of sputter etching or ion milling is that, because of the directionality of the ions and the absence of chemical (isotropic) components, it is possible to etch without undercutting the mask and to form vertical edges. Undercutting is not observed, but often the end results are not vertical profiles due to faceting of the mask (discussed in Section 1.5.5). Masking by lithographic techniques is the first step. However, since sputter etching is a physical process, there is not the same degree of selectivity that exists when using chemical reagents, such as solutions or reactive plasmas, since all materials can be etched by ion bombardment techniques. Thus mask erosion can be a significant problem, particularly since some resists are among those materials with the highest sputtering yields. However, thick resists degrade lithographic performance. Therefore it may be necessary to add to the complexity of the process by using a thinner resist layer to form a secondary mask in a material of somewhat lower sputter yield, such as an oxide.

In addition, the resist mask can flow and change shape because of the temperature rise due to ion bombardment.

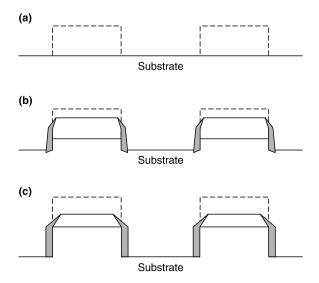

Another problem is redeposition of sputtered material. Material deposited on the sidewalls of the masking pattern will alter the profile; grooves will be narrower and lines will be wider than the original mask (Lehmann et al., 1977). Redeposition on the sidewalls can be seen in scanning electron microscopes (Gloersen, 1975) and is shown schematically in Figure 1.19.

Figure 1.19 Redeposition during ion bombardment of a resist layer.

Figure 1.20 (a) Catcher plate; (b) catcher plate installed in a sputtering system. (From Maissel, L.I., C.L. Standley, and I.V. Gregor, *IBM J. Res. Develop.* 16, 67, 1972.)

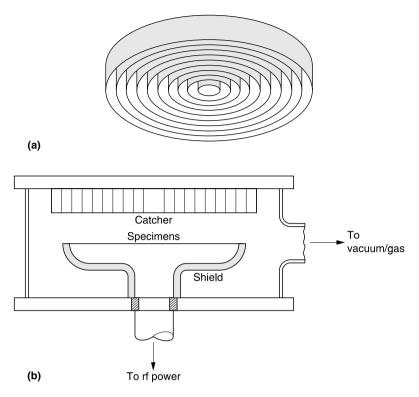

Backscattered impurities can mask areas on the surface and, due to the angular dependence of the sputtering yield (see Section 1.5.5), cones can develop on the surface during sputter etching. The use of a catcher plate, a series of concentric rings with deep aspect ratios bonded to the anode of a sputter etching system, reduces redeposition (Maissel et al., 1972). A catcher plate is shown in Figure 1.20a and as installed in an etcher in Figure 1.20b.

Finally there is trenching, enhanced etching at the sidewalls of an etched feature. This is a result of increased ion flux at the sidewall (forward reflection) due to differential charging (a consequence of the difference in the angular distribution for ions and electrons) (Arnold and Sawin, 1991). Another factor in trenching is redeposition. The region close to the step will see a reduced solid angle ( $\theta$ ) for redeposition from above, while further out a larger angle ( $\theta$ ) is apparent so that more redeposition (slower net etch rate) will occur (Melliar-Smith, 1976).

The problem of faceting the mask is covered in Section 1.5.5. In ion milling there is an extra degree of freedom since the substrate (or the ion gun) can be rotated. This offers additional control of linewidths and profiles (Somekh, 1976). Etching for pattern transfer in inert plasmas has, for the most part, given way to reactive plasma-assisted etching processes, although some of the problems described above are also problems in reactive plasma etching.

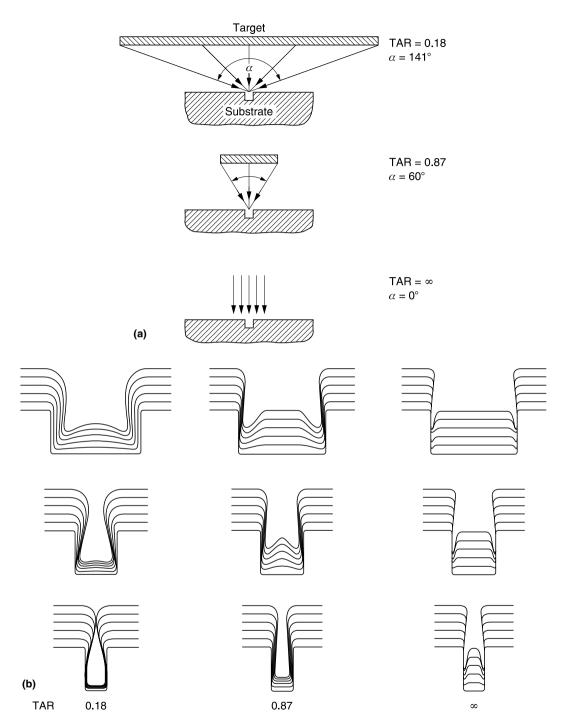

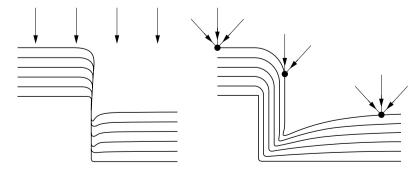

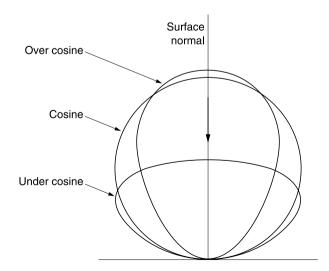

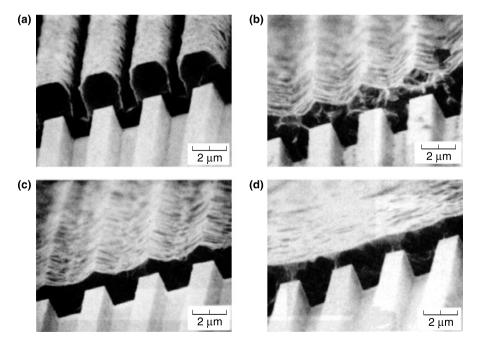

#### 1.5.5 Angular Dependence of Sputtering Yield