## Department of Computing Course 112 - Hardware Tutorial 4

This tutorial contains exercises that are assessed. Make certain that your name, initials and group are clearly filled in. Do all your work on this sheet and hand it in at the end of the tutorial session.

| LAST NAME | IN | ITIALS | GROUP |

|-----------|----|--------|-------|

|           |    |        |       |

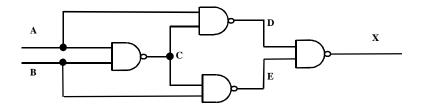

Consider the following famous circuit:

.

**1.** Using the simple switch model (ie Boolean Algebra) construct a truth table to determine its function.

| A | B | С | D | E | Χ |

|---|---|---|---|---|---|

| 0 | 0 |   |   |   |   |

| 0 | 1 |   |   |   |   |

| 1 | 0 |   |   |   |   |

| 1 | 1 |   |   |   |   |

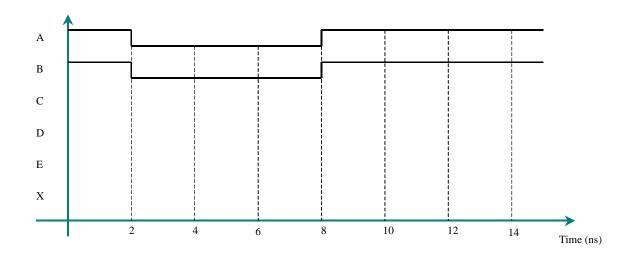

2. Now, assume the switch model has a time delay, and let the time delay for a two input NAND gate be  $2ns (2*10^{-9} \text{ seconds})$ . Complete the following timing diagram for the circuit:

3. Assuming that an inverter causes a time delay of 1ns re-draw the circuit to make it safe. Would this solution work if the inverters had a time delay of 0.95 ns rather than 1ns.

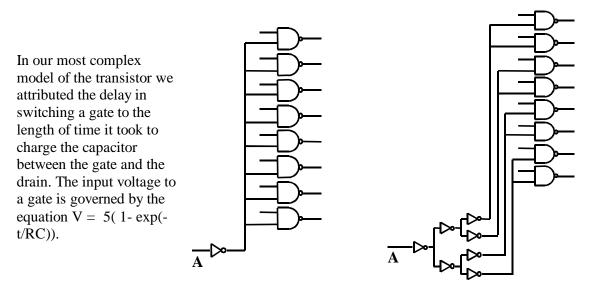

4. (A difficult optional problem for those geniuses who understand Physics)

Using this model, and assuming that

1. the input capacitances of all gates are the same

2. the gates all switch at about the same voltage level eg 1V for logic 1

determine which of the two implementations of an eight way buffer circuit will be the faster.

.