# Board Designer's Guide Testable Logic Circuits

### COLIN MAUNDER

Are you looking to reduce the cost of testing your board design?

Reading this book you will realize that design-for-test has many benefits and need not be difficult. By following a few essential steps you will significantly reduce the cost of testing your finish eel board design.

Matching the way a board is designed, this comprehensive book considers design-for-test requirements in a step-by-step fashion with explanations of why a feature is needed and what the consequences of ignoring it might be.

The hook:

- *3* presents design-for-test principles In a manner that matches the way a board is designed

- 3 provides checklists to assess the testability of each completed design

- *3* includes a chapter on the important IEEE standard on boundary-scan (IEEE Std 1149.1)

- *3* discusses how a development project should be managed so that a testable design is achieved

This book will be very valuable for engineers and managers involved wish electronic board design. It will also be suitable for students in electrical and electronic engineering and related disciplines to support courses in test development and design-for-test.

Colin Maunder is a consultant in computer-aided testing at BT Laboratories, UK. He is well known internationally for his courses on design-for-test and his work on IEEE Std 1149.1. He received a major IEEE Computer Society award for leading the development of this important new standard for design-for-test and is currently Emeritus Chair of the international working group that is enhancing and maintaining the standard.

#### ELECTRONIC SYSTEMS ENGINEERING SERIES

Consulting editors

**E L Dagless** University of Bristol

J O'Reilly University College of Wales

#### OTHER TITLES IN THE SERIES

Advanced Microprocessor Architectures L Ciminiera and A Valenzano Optical Pattern Recognition Using Holographic Techniques JV Collings Modern Logic Design D Green Data Communications, Computer Networks and OSI (2nd Edn) FHalsall Multivariate Feedback Design J M Maciejowski Microwave Components and Systems KF Sander Tolerance Design of Electronic Circuits R Spence and R Soin Computer Architecture and Design A J van de Goor Digital Systems Design with Programmable Logic M Bolton Introduction to Robotics P I McKerrow MAP and TOP Communications: Standards and Applications A Valenzano. C Demartini and L Ciminiera Integrated Broadband Networks *R Handel and M N Huber*

## **Board Designer's Guide** Testable Logic Circuits

COLIN MAUNDER BT Laboratories, Martlesham Heath, Ipswich

Addison-Wesley Publishing Company

Wokingham, England • Reading, Massachusetts • Menlo Park, California • New York Don Mills, Ontario • Amsterdam • Bonn • Sydney • Singapore • Tokyo • Madrid San Juan • Milan • Paris • Mexico City • Seoul • Taipei (£) 1992 Addison-Wesley Publishers Ltd.

© 1992 Addison-Wesley Publishing Company Inc.

AH rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior written permission of the publisher.

The programs in this book have been included for their instructional value. They have been tested with care but are not guaranteed for any particular purpose. The publisher does not offer any warranties or representations, nor does it accept any liabilities with respect to the programs.

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Addison-Wesley has made every attempt to supply trademark information about manufacturers and their products mentioned in this book.

Cover designed by Designers & Partners of Oxford and printed by The Riverside Printing Co. (Reading) Ltd. Printed in Great Britain at the University Press, Cambridge.

First printed 1991.

#### **British Library Cataloguing in Publication Data**

Maunder, Colin The board users guide to testable logic circuits. I. Title 621.38153

ISBN 0-201-56513-7

#### Library of Congress Cataloging-in-Publication Data

Maunder, Colin M.

The board designers guide to testable logic circuits / by Colin Maunder.

p. cm. — (Electronic systems engineering series)

Includes bibliographical references and index.

ISBN 0-201-56513-7

1. Logic circuits—Testing. I. Title. II. Series.

TK7868.L6M376 1992

621.39'5—dc20

91-29663

CIP

### Preface

When I first got involved in test engineering in the 1970s, boards were, by today's standards, simple. They contained, on average, a few thousand logic gates in the form of small- and medium-scale integration components. Testing was done by applying signals at the board's functional connector and by examining the board's response.

Of course, board complexities increased. Soon, it was recognized that functional (from the edge) testing was too costly — it was expensive to develop test programs and these were relatively inefficient at locating common manufacturing faults, such as open and short circuits. The in-circuit tester was introduced as a solution to these problems. It allowed test generation costs to be significantly reduced and, by virtue of its connection to every chip-to-chip interconnection on the board, allowed rapid diagnosis of the most common manufacturing-induced faults.

During the 1980s, the in-circuit tester became the principal type of test system used for testing loaded boards. Initially, some were concerned that the backdriving technique used by these testers might cause damage or reliability degradation to components on the boards. In response, techniques were developed to control the way that in-circuit tests were applied — ensuring that the chance of damage was minimized. In essence, these techniques required careful sequencing of the tests applied to the board, allowing a recovery period following backdriving of a particular IC, and imposition of a maximum time. limit for each test, calculated according to the characteristics of the components adjacent to that under test.

VI rtikPAUK

Unfortunately, technology doesn't stand still. Board complexities continued to increase during the 1980s, fuelled by advancing integrated circuit technology and by the move towards the use of smaller surface-mount packages. This caused three problems for the in-circuit tester:

- O First, test times for individual components increased and began to exceed the time limit imposed to avoid the possibility of damage during backdriving. Tests had to be shortened, with the result that they were less comprehensive than before.

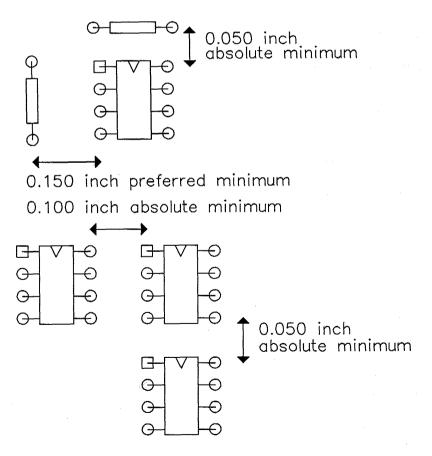

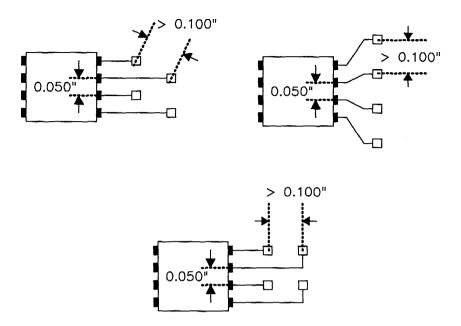

- G Second, the pin-to-pin spacing for surface-mount packages is less than the 0.1" of dual-in-line ICs. The spacing between in-circuit test probes had to be reduced to allow connections into and out of these ICs to be accessed. Unfortunately, however, probes become less robust and less reliable as their size reduces.

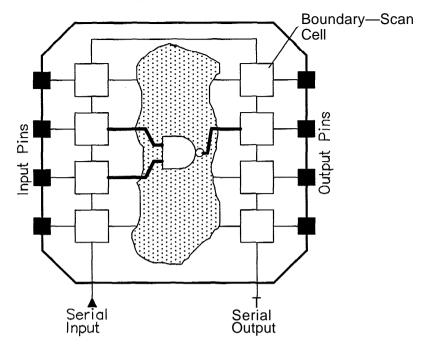

Towards the end of the 1980s, these problems were becoming acute in certain sectors of the electronics industry. An industry pressure group (the Joint Test Action Group — JTAG) was formed to develop and promulgate a change of approach — from in-circuit testing to a technique more suited to highly-complex, miniaturized loaded board designs, JTAG and, subsequently, the IEEE drafted a standard for the design of integrated circuits that would ensure that chips would be able to assist in the task of testing the loaded board. This standard — *ANSI/IEEE Std 1149.1, Standard Test Access Port and Boundary-Scan Architecture* — is now supported by several leading IC vendors and test equipment companies and is set to provide the basis of board testing through the 1990s.

While these changes have helped to control the cost of testing (which would otherwise have risen much more rapidly as board complexity increased), it is clear that testing has become an expensive part of the total cost of developing, manufacturing, and (in particular) supporting electronic systems. As a result, design-for-test has become an essential aspect of the designer's task — those who ignore it do so at their peril.

The objective of this book is to present design-for-test in a manner that matches the way that a board is designed — starting with top-level block design and progressing through component selection and circuit design to board layout. The design-for-test requirements that should be considered at each stage are, wherever possible, grouped into a single chapter. An explanation is provided for each requirement so that the designer can understand why the feature is needed and what the consequences of ignoring the requirement might be. Finally, a set of checklists is provided to help assess the testability of each completed design — again, stage by stage.

As you will see, design-for-test is not difficult. The various requirements are easy to understand and to implement. If implemented, the various design-for-test features will significantly reduce the cost of testing the finished board design. So why not give it a try?

#### Acknowledgements

Many people have contributed to this book. Particular acknowledgement should be given to the following:

- O my employer, BT, for providing the time to develop the internal design-for-test 'manual' that was the basis of this book and for giving permission for its publication;

- Ben Bennetts, of Bennetts Associates, who introduced me to test engineering and with whom I have lectured on test generation and design-for-test over many years;

- 3 the students on courses presented in Amsterdam and elsewhere, who unwittingly acted as the test-bed for the material in this book and, in some cases, contributed items that have been included in it;

- O Ken Totton and other colleagues at BT Laboratories, who provided comments on early drafts; and, lastly,

- *H* my wife and children, who were starved of attention at evenings and weekends as the draft was converted into this book.

Finally, Chapter 3 contains material from two previously-published papers:

- O Maunder CM. and Tulloss R.E. (1991). An introduction to the boundary-scan standard: ANSI/IEEE Std 1149.1. *Journal of Electronics Test, Theory, and Applications*, 2(1), 27-42.

- Maunder CM. (1991). The impact of testability standards on design and EDA. In *Proc. Concurrent Engineering and Electronic Design Automation Conference*. Bournemouth, UK, March.

Acknowledgement is made to Kluwer Academic Publishers and Bournemouth Polytechnic, respectively, for permission to reuse this material.

Colin Maunder BT Laboratories Martlesham Heath Ipswich, IP5 7RE, UK

November 11, 1991

### Contents

| Pı | reface  |                                    | v  |

|----|---------|------------------------------------|----|

| G  | lossary | xiii                               |    |

| P  | art 1   |                                    | I  |

| 1  | Introd  | luction to testing and testability | 3  |

|    | 1.1 •   | Introduction                       | 3  |

|    | 1.2     | Basics                             | 4  |

|    | 1.3     | Test generation                    | 8  |

|    | 1.4     | Test application                   | 14 |

|    | 1.5     | Fault diagnosis                    | 18 |

|    | 1.6     | Design-for-test                    | 21 |

|    |         | References                         | 23 |

| 2  | Design  | n-for-test techniques              | 24 |

|    | 2.1     | Introduction                       | 24 |

|    | 2.2     | Do nothing                         | 26 |

|    | 2.3     | Design-for-test guidelines         | 27 |

|    | 2.4     | Scan design                        | 30 |

|    | 2.5     | Self-test                          | 42 |

|    |         | References                         | 51 |

| x CONTENTS |

|------------|

|------------|

| 3  | Boundary  | /-scan                                          | 52  |

|----|-----------|-------------------------------------------------|-----|

|    | 3.1       | Introduction                                    | 52  |

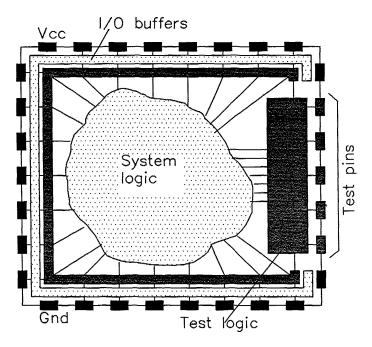

|    | 3.2       | A chip-level view                               | 53  |

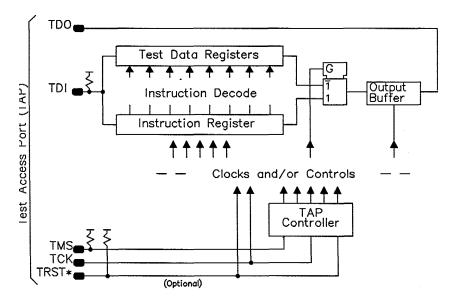

|    | 3.3       | The test logic architecture                     | 54  |

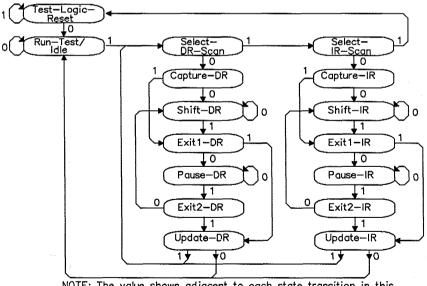

|    | 3.4       | The TAP                                         | 56  |

|    | 3.5       | The TAP controller                              | 57  |

|    | 3.6       | The instruction register                        | 59  |

|    | 3.7       | The test data registers                         | 60  |

|    | 3.8       | The BYPASS instruction                          | 62  |

|    | 3.9       | The IDCODE and USERCODE instructions            | 63  |

|    | 3.10      | Boundary-scan register instructions             | 65  |

|    | 3.11      | Machine-readable descriptions of ANSI/IEEE Std  |     |

|    |           | 1149.1-compatible ICS                           | 75  |

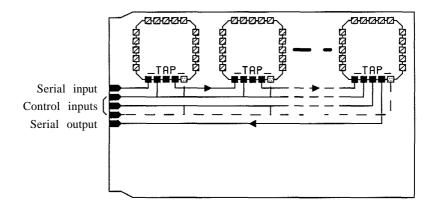

|    | 3.12      | Using boundary-scan                             | 76  |

|    | 3.13      | Conclusion                                      | 81  |

|    |           | References                                      | 82  |

| 4  | Planning  | for design-for-test                             | 83  |

|    | 4.1       | Introduction                                    | 83  |

|    | 4.2       | Planning for a testable design                  | 83  |

|    | 4.3       | Testability checklists and design reviews       | 86  |

|    | 4.4       | The test strategy                               | 90  |

|    | 4.5       | Choosing a design-for-test strategy             | 91  |

|    | 4.6       | Setting a design-for-test budget                | 94  |

|    |           | References                                      | 95  |

| Pa | art 2     |                                                 | 97  |

|    | Test acce | ss <b>techniques</b>                            | 99  |

|    | 5.1       | Introduction                                    | 99  |

|    | 5.2       | Connector 'U' links                             | 100 |

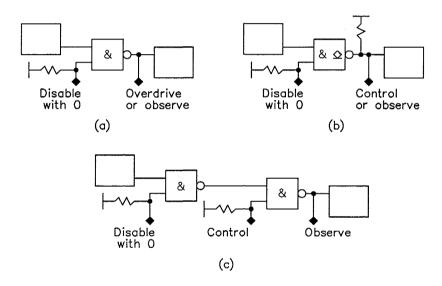

|    | 5.3       | 3-state devices                                 | 102 |

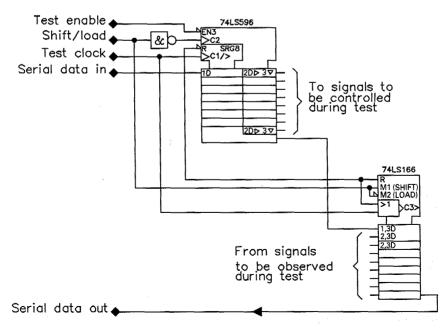

|    | 5.4       | Multiplexors and shift-registers                | 102 |

|    | 5.5       | Use of simple logic gates                       | 104 |

|    | 5.6       | Test support chips                              | 104 |

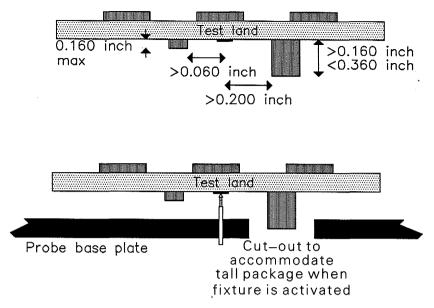

|    | 5.7       | Bed-of-nails                                    | 105 |

|    | Designing | g self-testing products                         | 106 |

|    | 6.1       | Introduction                                    | 106 |

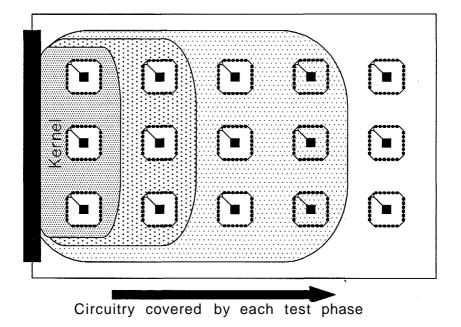

|    | 6.2       | Start small                                     | 107 |

|    | 6.3       | Triggering self-test                            | 109 |

|    | 6.4       | Pass/fail indications                           | 109 |

|    | 6.5       | Control of external interfaces during self-test | 110 |

|    | 6.6       | Component-specific self-test requirements       | 110 |

|    | 6.7       | Some useful techniques                          | 112 |

| 7  | Compone   | ent selection and design                      | 113 |

|----|-----------|-----------------------------------------------|-----|

|    | 7.1       | Introduction                                  | 113 |

|    | 7.2       | Component selection                           | 114 |

|    | 7.3       | Programmable device design                    | 115 |

|    | 7.4       | ASIC design                                   | 117 |

| 8  | Circuit d | lesign                                        | 122 |

|    | 8.1       | Introduction                                  | 122 |

|    | 8.2       | Initialization                                | 123 |

|    | 8.3       | Architectural issues                          | 128 |

|    | 8.4       | Function-oriented requirements                | 132 |

|    | 8.5       | Connection-oriented requirements              | 138 |

|    | 8.6       | Controllability and observability improvement | 143 |

| 9  | Supplyin  | g power to the product                        | 144 |

|    | 9.1       | Introduction                                  | 144 |

|    | 9.2       | Safety during testing                         | 144 |

|    | 9.3       | Power inputs                                  | 145 |

|    | 9.4       | Decoupling                                    | 146 |

|    | 9.5       | Conversion and validation                     | 146 |

|    | 9.6       | Power-on resets                               | 146 |

| 10 | Connecto  | or selection and layout                       | 147 |

|    | 10.1      | Introduction                                  | 147 |

|    | 10.2      | Connector selection                           | 148 |

|    | 10.3      | Signal-to-pin mapping                         | 148 |

| 11 | Printed o | circuit layout                                | 151 |

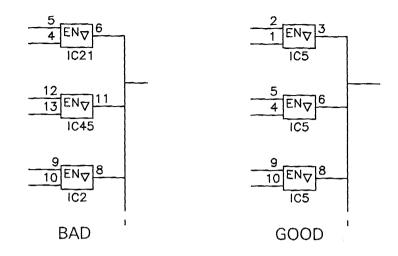

|    | 11.1      | Introduction                                  | 151 |

|    | 11.2      | Using this chapter                            | 152 |

|    | 11.3      | Terminology                                   | 155 |

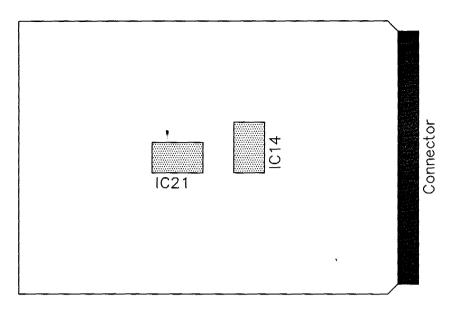

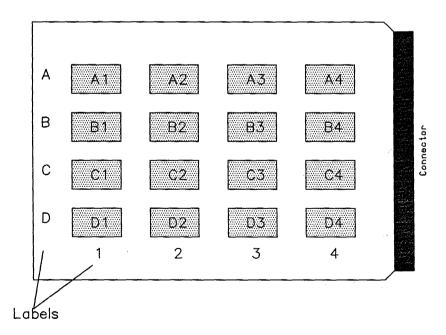

|    | 11.4      | Overall layout                                | 155 |

|    | 11.5      | Interconnect, vias, etc.                      | 157 |

|    | 11.6      | Packaging of logic elements                   | 157 |

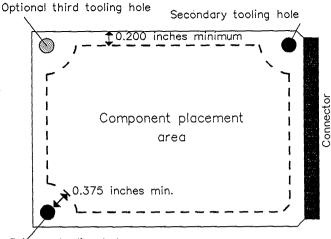

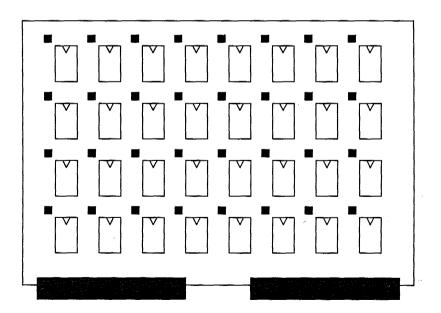

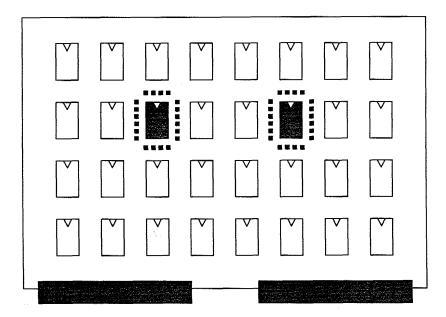

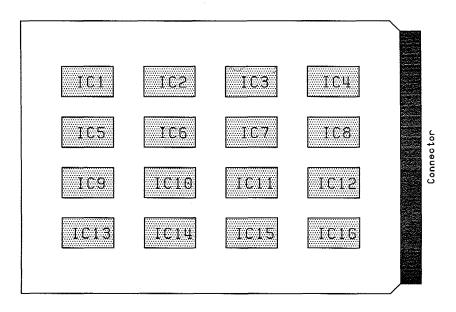

|    | 11.7      | Component placement                           | 159 |

|    | 11.8      | Test access provision                         | 162 |

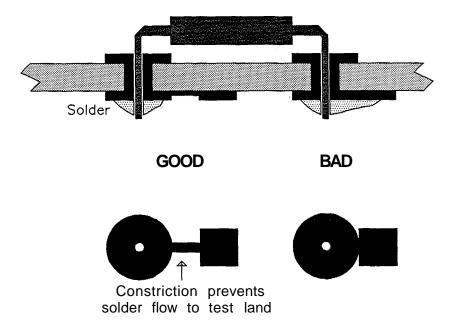

|    | 11.9      | Test access point design                      | 166 |

|    | 11.10     | Labelling                                     | 168 |

|    | 11.11     | Construction                                  | 171 |

|    |           | References                                    | 172 |

| 12 | Documer   | ntation                                       | 173 |

|    | 12.1      | Introduction                                  | 173 |

|    | 12.2      | Documentation required for test               | 173 |

#### xii CONTENTS

| Appendix | Testability checklists        | 175 |

|----------|-------------------------------|-----|

| A. 1     | Introduction                  | 175 |

|          | Self-testing products         | 176 |

|          | Component selection           | 177 |

|          | Programmable device design    | 178 |

|          | ASIC design                   | 179 |

|          | Circuit design                | 180 |

|          | Power supply and distribution | 183 |

|          | Connectors                    | 185 |

|          | Printed circuit layout        | 186 |

|          | Documentation                 | 188 |

| Index    |                               | 189 |

### Glossary

| AC    | Alternating current                                |  |  |  |  |

|-------|----------------------------------------------------|--|--|--|--|

| ACL   | Approved component list                            |  |  |  |  |

| ALU   | Arithmetic logic unit                              |  |  |  |  |

| AOT   | Adjust on test                                     |  |  |  |  |

| ASIC  | Application-specific IC                            |  |  |  |  |

| ATE   | Automatic test equipment                           |  |  |  |  |

| ATPG  | Automatic test program generation                  |  |  |  |  |

| BILBO | Built-in logic block observer                      |  |  |  |  |

| BIST  | Built-in self-test                                 |  |  |  |  |

| BOM   | Bill of materials                                  |  |  |  |  |

| BSDL  | Boundary-scan description language                 |  |  |  |  |

| CCITT | International Telephone and Telegraph Consultative |  |  |  |  |

|       | Committee                                          |  |  |  |  |

| CMOS  | Complementary metal oxide semiconductor            |  |  |  |  |

| DC    | Direct current                                     |  |  |  |  |

| DIL   | Dual-in-line                                       |  |  |  |  |

| DIP   | Dual-in-line package                               |  |  |  |  |

| DTL   | Diode transistor logic                             |  |  |  |  |

| DUT   | Device-under-test                                  |  |  |  |  |

| ECL   | Emitter-coupled logic                              |  |  |  |  |

| EDA   | Electronic design automation                       |  |  |  |  |

| EMC   | Electromagnetic compatibility                      |  |  |  |  |

| FBT   | Functional board tester: a type of ATE             |  |  |  |  |

|       |                                                    |  |  |  |  |

| FDDI<br>IC<br>ICT<br>ISDN<br>JEDEC<br>JTAG<br>LED<br>LFSR<br>LSSD<br>MISR<br>MOS | Fibre distributed data interface<br>Integrated circuit<br>In-circuit tester: a type of ATE<br>Integrated services digital network<br>Joint Electron Device Engineering Council<br>Joint Test Action Group<br>Light-emitting diode<br>Linear-feedback shift register<br>Level-sensitive scan design<br>Multiple-input signature register<br>Metal oxide semiconductor |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Overdrive                                                                        | Force the logic state of a connection by supplying more                                                                                                                                                                                                                                                                                                              |  |  |

| PBX                                                                              | current than the circuit that would normally drive it<br>Private branch exchange: a telephone and/or data exchange                                                                                                                                                                                                                                                   |  |  |

| PCB<br>PLD                                                                       | installed on a company's premises, etc.<br>Printed circuit board<br>Programmable logic device                                                                                                                                                                                                                                                                        |  |  |

| PTH                                                                              | Plated through hole                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PWB                                                                              | Printed wiring board                                                                                                                                                                                                                                                                                                                                                 |  |  |

| RAM                                                                              | Random-access memory                                                                                                                                                                                                                                                                                                                                                 |  |  |

| ROM                                                                              | Read-only memory                                                                                                                                                                                                                                                                                                                                                     |  |  |

| RTL                                                                              | Resistor transistor logic                                                                                                                                                                                                                                                                                                                                            |  |  |

| S-a-0                                                                            | Stuck-at-0: a fault in which a connection becomes                                                                                                                                                                                                                                                                                                                    |  |  |

| S-a-1                                                                            | permanently fixed at logic 0<br>Stuck-at-1: a fault in which a connection becomes                                                                                                                                                                                                                                                                                    |  |  |

| SIP<br>SMT<br>SOT<br>Stuck-at fault                                              | permanently fixed at logic 1<br>Single-in-line package<br>Surface-mount technology<br>Select on test                                                                                                                                                                                                                                                                 |  |  |

| Stuck-at Tault                                                                   | A fault that causes a signal to take on a fixed logic value                                                                                                                                                                                                                                                                                                          |  |  |

| TAP<br>Test fixture                                                              | regardless of the output of preceeding logic<br>The ANSI/IEEE Std 1149.1 test access port<br>Hardware used to connect the printed circuit board being                                                                                                                                                                                                                |  |  |

| Test Land                                                                        | tested to the ATE.<br>Contact area on a printed circuit board used by bed-of-nails                                                                                                                                                                                                                                                                                   |  |  |

| TTL<br>VHDL<br>VHSIC<br>Via<br>VLSI<br>UUT<br>ZIF                                | HDL       Infansision transision togic         HDL       VHSIC hardware description language         HSIC       Very high speed integrated circuit         a       A plated-through hole on a printed circuit board used solely         LSI       to convey a connection from one layer to another         Very large scale integration       Unit under test        |  |  |

|                                                                                  | Zero insertion force                                                                                                                                                                                                                                                                                                                                                 |  |  |

### Part 1

This part provides an introduction to testing and design-for-testability. It provides an overview of the principal design-for-test techniques, for both chips and loaded boards, and discusses the formulation of plans to ensure that products are designed to be testable.

### CHAPTER 1. Introduction to Testing and Testability

| 1.1 | Introduction    | 1.4 | Test application |

|-----|-----------------|-----|------------------|

| 1.2 | Basics          | 1-5 | Fault diagnosis  |

| 1.3 | Test generation | 1.6 | Design-for-test  |

|     | -               |     | References       |

#### 1.1. Introduction

A combination of two factors — greater competition and the wider use of 'information technology' — is bringing about a rapid growth in the variety of electronic products available to the consumer. Also evident is the increasing complexity of these products, made possible through the combination of low-cost state of the art integrated circuit technology and advanced manufacturing techniques.

To compete successfully in such an environment, companies need to bring new products from the drawing board to the marketplace as quickly (and as cheaply) as possible, and to encourage their suppliers to do the same. The costly and time-consuming 'production engineering' phases that have traditionally followed initial design must now be avoided, with the consequence that the responsibility for production engineering tasks is increasingly placed on the designer. The areas of design covered by these tasks do, however, contribute significantly to the product's commercial viability and it is therefore important that they continue to be considered carefully.

One such design area is 'design-for-testability' which stems from the need to make the process of testing the product, both following production and during repair, as cost-effective as possible. The purpose of this chapter is to explain why design-for-testability (and hence this book) is needed through a discussion of test technology and the problems of test generation, test application and fault diagnosis.

#### 1.2. Basics

#### 1.2.1. Types of testing

Testing is performed at a number of stages in the development of a product and for a variety of purposes. Perhaps the most important of these types of testing are:

- (1) *Design Verification Testing.* Carried out to ensure that the design adequately performs the function which is expected of it. This stage of testing is most often performed using bench-top instrumentation (oscilloscopes, logic analysers, etc.), although in the case of more complex designs programmable test systems may be used.

- (2) *Production Testing.* Performed to locate any defects which might exist in each copy of a design once it has been manufactured. Typically, this stage of testing will be done using a programmable **automated test equipment** (ATE), which for assembled printed circuit boards may cost \$1,000,000 or more. The principal types of ATE are described in Section 1.4.1.

- (3) *Repair Testing.* Performed when a product fails during use. The aim is to isolate the cause of failure sufficiently to allow it to be repaired. Once again, this may be accomplished using ATE.

- (4) *Self-testing.* An example of self-test is the routining of telephone exchanges, computers, or military equipment during idle periods, performed to locate faults before they cause failure in use. Self-test procedures are also provided for other reasons, for example to reduce the costs of performing on-site repair. They are particularly suitable for use in equipment that is to be installed in a customer's premises (for example, office equipment or telephone switches) since they allow the customer to check which piece of equipment is at fault before asking for repair.

This book is directed at all stages of testing a product during its life and at ways in which products can be designed to make test tasks easier.

#### 1.2.2. Test activities

There are three stages of activity involved in the testing of a product.

- (1) *Test Development.* Firstly, a test for the product must be developed, and demonstrated to be sufficiently good at detecting and locating faults. We will look at one typical method for achieving this in Section 1.3.

- (2) *Test Application.* Secondly, once the test has been developed, it will be applied to units as they leave the production line, or as they arrive for repair, using the available ATE. After this stage units will have been marked faulty or fault-free. Types of ATE, and other aspects of test application, are considered in Section 1.4.

- (3) *Diagnosis.* Finally, if a unit is found faulty, the ATE will be used to produce a diagnosis of the cause of failure, for example a failed component. In this way, a repair can be effected, the success of which will be determined by re-testing the unit. Ways in which automated diagnosis is accomplished are discussed in Section 1.5.

#### 1.2.3. What is testability?

Since cost is an important factor in any commercial environment, it should not be surprising that the overall cost of performing testing activities discussed in Section 1.2.2 is one measure of the product's testability. The higher the cost of each activity, the lower the product's testability.

Cost is, however, not the only factor which determines testability, and for the purpose of this discussion two other factors will be considered.

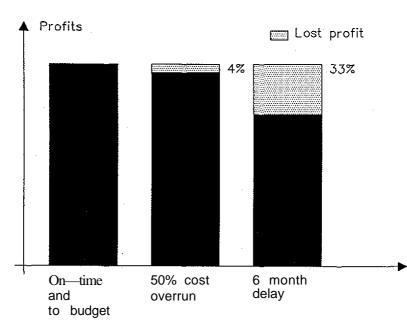

Firstly, the time taken to perform the various test tasks is important, and cannot always be measured through the costs of labour, etc. In some cases, for example when deadlines have to be met, time may actually be more important than cost. In these cases, the most significant impact of reduced testability may be lengthened test development timescales. Figure 1.1 (Reinerstein, 1983) shows the importance of time-to-market in high-growth markets where product life cycles are relatively short. It can be seen that a loss of up to 33% of profits may occur if a product is six months late on to the market.

Secondly, there is the adverse effect that reduced testability can have on the quality of the product. Ideally, a test program should be able to detect IOOfo of the faults that might occur in the product; if this were the case, then the quality of the product could be guaranteed. Inevitably, the test will be less than perfect (as will be discussed later) and so some faults will escape

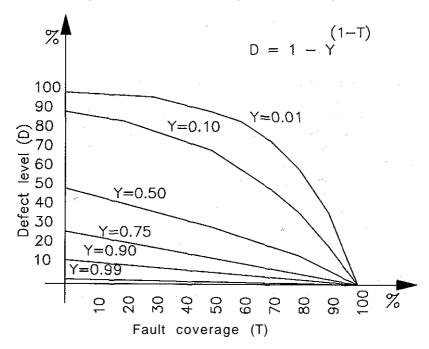

Figure 1.2 Defect level as a function of process yield and fault coverage.

detection, the number depending on the difficulty of testing the product — its 'untestability'.

Figure 1.2 (Williams and Brown, 1981) shows how three factors — process yield (that is, the fraction of products manufactured fault-free), fault coverage (test performance), and shipped defect level (quality) — are related. It is clear that high-performance tests are required if the quality of shipped products is to be acceptable, particularly when the yield of the production process is low.

The possibility that units passed as fault-free by the test might actually contain faults will, of course, appear as a reduction in quality when the product reaches the consumer. Frequently, therefore, *a business's reputation can be damaged if product testability is inadequate.*

#### 1.2.4. Why is testability important?

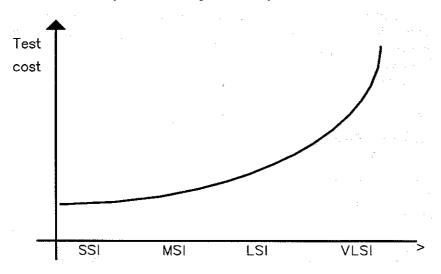

Figure 1.3 gives some idea of the way in which test costs in the semiconductor industry have risen with each advance in integrated circuit technology.

For a very-large-scale-integration (VLSI) integrated circuit, the development of an adequate test program can account for a major part of the overall cost of bringing the chip into production. Chip manufacturers are increasingly resorting to rigid 'design-for-testability' procedures as a means of reducing this expenditure. Indeed, the indications are that it will be impossible for chips as complex as those now starting to come onto the market to be produced economically unless such design procedures are used. To give a rough idea of costs, a VLSI chip may require 24 man-months or more of effort solely in test development — say, at a cost of \$200,000.

Figure 1.3 Test cost trends.

#### 8 INTRODUCTION TO TESTING AND TESTABILITY

Obviously, chips of this complexity are a major cause of testability problems in the systems into which they are assembled. Not surprisingly, therefore, the costs of testing for circuit cards and systems are also increasing rapidly.

This raises another point: the need for the designer not only to design his product to be testable in its own right but also to ensure that it does not contribute to poor testability when it is assembled into other products. Testable chips can easily be assembled into untestable systems! As one test engineer put it in 1979:

### 'LSI technology has brought the design of truly untestable circuits within the reach of everyone!'

A further motivation for high testability comes from the 'Rule of 10s'. This empircal rule, which is widely accepted by the test engineering community, relates the cost of testing for a fault at various stages in product assembly. For example, assume that there is a single fault present in a newly manufactured integrated circuit and that the cost of testing the chip is \$C. If the fault is detected by the chip test, the cost is %C.

If the fault is not detected by the chip test, then the faulty integrated circuit (IC) will be assembled into a loaded board. The Rule of 10s predicts that the cost of finding the fault while testing the board and then effecting a repair is  $10 \times C$ .

Of course, if the quality of the test program is insufficient (due to poor testability), the fault may not be detected by the loaded board test. In this case, the faulty board will be inserted in a system. The Rule of 10s predicts that the cost of finding the fault during the system test and then effecting a repair will be  $100 \times C$ .

Finally, if the fault escapes detection during system test, a faulty system will be shipped to a customer. *Customers always find faults that have not been detected by the manufacturer!* The Rule of 10s predicts that the cost of correcting the fault once the system has been installed in the field will be  $1000 \times C$ .

#### 1.3. Test generation

#### 1.3.1. Fault models

Before starting to develop a test for a logic circuit we need to know precisely what the objectives of the test are in terms of the faults it should be able to detect.

Ideally, we would like the test to be able to detect all failures which might occur. However, if each of the failure modes of each transistor, resistor, etc. in the circuit is considered, together with the possibility of unwanted connections between each pair of signals, it becomes apparent that the number of different failures that could potentially occur (many of them are extremely unlikely!) is very large, even for a fairly small circuit. For larger circuits the number of possible failures would very rapidly become prohibitive.

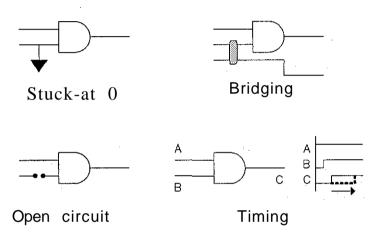

To produce a manageable objective for the test it is common to work in terms of a small range of fault models, each of which covers a range of failure modes. These fault models represent the effects (rather than the causes) of the malfunction and are significantly easier to comprehend. The more common of these fault models are illustrated in Figure 1.4 and described below.

Figure 1.4 Simple fault models.

#### The 'stuck-at\* fault model

The 'stuck-at' fault model was originally proposed in 1959 when the dominant logic technologies were **resistor transistor logic (RTL)** and **diode transistor logic** (DTL) (Eldred, 1959).

In these technologies, almost all failures of circuit components result in one or more circuit connections becoming stuck at one or other of the two logic values (0 or 1) and these failures could therefore be said to result in nodes becoming 'stuck-at 0' (s-a-0) or 'stuck-at 1' (s-a-1).

Despite the fact that integrated circuit technology has advanced considerably 'stuck-at' models are still used widely today. This is because of two factors. Firstly, the models are extremely easy to introduce into circuit simulations — they merely result in nodes being permanently assigned the appropriate logic value. This means that it is relatively easy to ensure that the test is good at detecting stuck-at faults. Secondly, experience has shown that tests which are effective at detecting stuck-at faults are effective at detecting the types of failure more representative of modern technology —

for example failures in **metal oxide semiconductor** (MOS) integrated circuits and **random-access memories** (RAMs).

#### The 'open circuit\* fault model

Open circuit failures in **transistor transistor logic** (TTL) are equivalent to the stuck-at fault models, since most undriven TTL device inputs will 'float' to a logic 1 state. For this reason, open circuit failures may not be considered separately for TTL-compatible circuits.

In MOS technologies, however, the same assumption cannot be made since 'floating' inputs behave in considerably different ways. The use of specific models for open circuit failures during integrated circuit test development is therefore increasing.

#### The bridging fault model

An extremely common production defect, both for integrated circuits and for circuit boards, is for two nodes to become shorted together. Such a defect is termed a bridging fault, since in circuit board production it is the result of accidental bridging connections being inserted by solder splashes. In integrated circuits the same defect is caused by the failure of insulation between areas of silicon, conductors, and so on. Obviously, many potential bridging faults are unlikely to occur since the relevant connections are too widely spaced. For this reason only specific sets of bridging faults are simulated. Common examples are those between adjacent pins on a device or between adjacent PWB tracks since these are most likely to be shorted by extraneous solder.

Note that it is important to model the result of the short-circuit fault correctly. For some faults, the outcome will be the wire-OR combination of the signals that drive the shorted tracks, while for others the outcome may be the wire-AND or an indeterminate voltage level.

#### The timing fault model

Fortunately by avoiding the use of asynchronous circuits (which is good design practice anyway) the likelihood of drifts in the timing behaviour of devices causing the failure of a circuit can be made extremely small. However, in circuits where accurate timings are required for successful operation, the possibility of such timing drifts must be considered and this is done using the timing fault model. In this model, the possibility of increased or decreased propagation delays through a device can be represented.

#### 1.3.2. Developing a test

The most common method of developing a test for a logic circuit combines the intelligence of the human-bejng (the designer or a specialist test programmer) with the computational ability of the computer. The test programmer defines a sequence of inputs to be applied to the circuit and the corresponding outputs. The computer runs a program called a fault simulator which takes descriptions of the circuit and test waveform, together with a list of the faults to be considered and returns an accurate assessment of the test's performance (amongst other information — see Section 1.3.3).

Ways of quantifying test performance and the use of fault simulators are considered in more detail in the following section; here the task of the test programmer in defining the test waveform is considered. First, however, it must be mentioned briefly that computer programs do exist which can automate this task for certain, relatively simple, types of circuit or for circuits designed using highly structured design methods which will guarantee successful automatic test pattern generation. An example of a design methodology that guarantees fully automatic test generation is scan design, which is discussed in detail by Bennetts (1984). Until recently, these structured design methods have only been able to be used for integrated circuit design. The publication of ANSI/IEEE Std 1149.1 has, however, allowed similar techniques to be used at the board level for products constructed from compliant components (see Chapter 3).

How then does the test programmer set about producing a test for a given circuit? Probably there are about as many answers to that question as there are test programmers, so the approach described here — the so-called 'functional<sup>1</sup> approach — should only be thought of as an example.

The aim of the functional approach is to attempt to get each of the identifiable functional blocks in the circuit — for example, the more complex integrated circuit packages on a printed circuit board — to perform its intended function, and to allow this to be observed at the circuit's normal operating outputs. For example, counters in the circuit will be made to count, shift registers to shift, and so on.

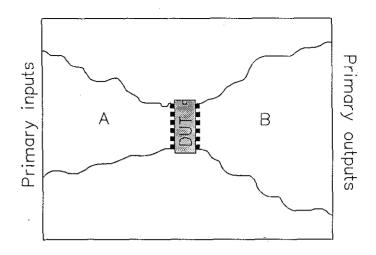

This task is not, unfortunately, as easy as it might appear. If we consider the device-under-test (DUT) shown in Figure 1.5, which we will assume to be embedded in the circuit, there are two tasks that must be accomplished.

Firstly, some sequence of values must be applied to the DUT inputs to stimulate it into performing its function. If we consider the DUT to be a counter, then it must be supplied with clock signals and appropriate enables, etc. All these signal values will need to be derived by changing the circuit's 'primary' inputs — the points to which the tester will have access — and propagating the changes through other devices in the region 'A'. Propagation of the changes may be extremely difficult, since the connections between the devices in region 'A' may be such as to cause the required values to be destroyed before they arrive at the DUT.

Secondly, to complete the test of the DUT, its response must be made observable to the tester; that is changes at its outputs must be propagated through devices in region 'B' to the circuit's 'primary' outputs. Again, this will not necessarily be as easy as it might appear, since conflicts

Figure 1.5 The functional test development approach.

may occur on the way. There is the additional problem that the values which have to be set on the devices in region 'B' to allow the DUT's response to be made visible have to be set by applying changes at the circuit's primary inputs, giving rise to the possibility that conflicts may occur between the inputs needed to cause the DUT to operate and those needed to make its operation apparent at the circuit's primary outputs.

To summarize, the two tasks involved are, firstly, control of the DUT inputs and, secondly, observation of the DUT outputs, both of which must be accomplished through the normal circuit connections. The ease of accomplishing these tasks is referred to as the **controllability** and **observability** of the connections and devices in the circuit. These parameters will be mentioned again in the chapters which discuss methods of designing circuits to be more easily testable.

#### 1.3.3. Evaluating test performance

To determine if the performance of the test is sufficient, we need to be able to determine if it detects the target faults for the circuit. This is normally done using a fault simulator which introduces each fault into a simulation of the circuit's behaviour. If the fault causes a change that could be observed by the ATE, then it is deemed detected.

#### Fault coverage

The measure of test performance is its **fault coverage**. Fault coverage is expressed as the percentage of modelled faults which the test has been

shown to detect. Commonly, organizations will set a target of 95% of all stuck-at faults (plus selected open-circuit and bridging faults) below which a test program is unacceptable, although a figure much closer to 100% is desirable. The reasons for accepting a lower figure include:

- G Certain faults, such as s-a-1 on a connection which is normally tied to logic 1, cannot be detected since they do not change the logical behaviour of the circuit. Such faults may, however, degrade the performance of the circuit for example, through changes in noise immunity, power dissipation, and so on.

- d Poor testability may make it very difficult for tests to be produced for some faults within the budget (time and cost) set for the work.

For a figure for the fault coverage of a test to be useful, the set of faults to which the figure relates must be defined. To yield an effective test, the target fault set should include all single stuck-at faults, open-circuit faults, and bridging faults between adjacent pins or tracks.

High fault coverage (as close to 100% as possible) is essential, since faults that the test does not detect may lead to reliability problems when the circuits are installed in working systems, with a consequent loss of the company's reputation for quality (see also Section 1.2.3). Many companies set a minimum acceptable fault coverage of 95%, with the target fault set being all single stuck-at-0 and stuck-at-1 faults.

#### Fault simulation

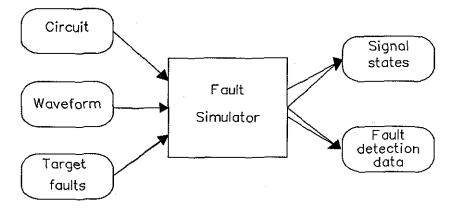

As was mentioned briefly before, a fault simulator is a complex computer program used to predict the fault coverage of a test program. It requires three principal computer readable inputs (Figure 1.6):

- a description of the circuit diagram (often called a netlist)

- a specification of the test waveform

- *d* a list of target faults

Once these inputs have been prepared, the simulator can be run and a set of results obtained. Typically, the results will include a list of the faults detected by the test, those not detected, and data to help in locating the source of any fault (for example, a diagnostic dictionary and data for guided probing — see Section 1.5). This process can be extremely expensive and must be carefully planned. For example, fault simulation run times for large, complex circuits are usually measured in central-processor-unit- (cpu-) days, even when using highly-tuned simulation algorithms running on high-performance computers.

Figure 1.6 The fault simulator.

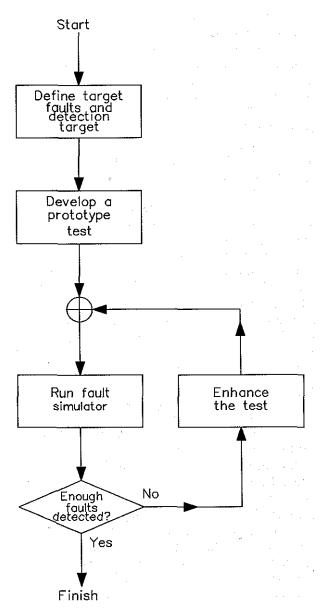

If the simulation shows that there are faults remaining to be detected, then the test programmer will enhance his test program to attempt to test for them. This cycle — test definition, fault simulation, test definition, etc. — may have to be repeated several times until the performance of the test becomes adequate (Figure 1.7).

#### 1.4. Test application

#### 1.4.1. Automatic test equipment

The automated test systems used for production and maintenance testing come in several varieties.

#### Integrated circuit testers

Integrated circuit testers can be found both on a semiconductor production line, checking the quality of components as they are manufactured and packaged, or in the incoming goods department of a systems company, where they screen components before they are assembled into hybrids, boards, and so on.

As integrated circuit complexities and operating speeds have increased, general purpose IC testers have become extremely expensive with costs in excess of \$1M being commonplace. Less sophisticated or less generally applicable types of IC tester are available, for example to test prototype IC designs or to test particular types of device (for example, RAMs). These systems can be significantly cheaper, but the performance and range of possible measurements may be limited.

Figure 1.7 The test development process.

#### Bare-board testers

Bare-board and backplane testers serve an important function in the production of electronic systems. Perhaps the simplest type of tester, they are used to check the integrity of wiring contained on printed circuit boards, or in backplanes or wiring harnesses. The objectives are to confirm that all wanted connections are present, and that no unwanted connections exist.

The tester design is very simple since it has only to allow for resistance measurements to be performed between pairs of contact pins. However, the number of connections can be vast — for example, testers are available that allow simultaneous contact to up to 15,000 points.

#### **In-circuit board testers**

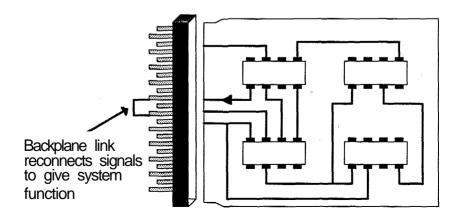

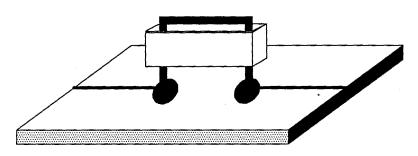

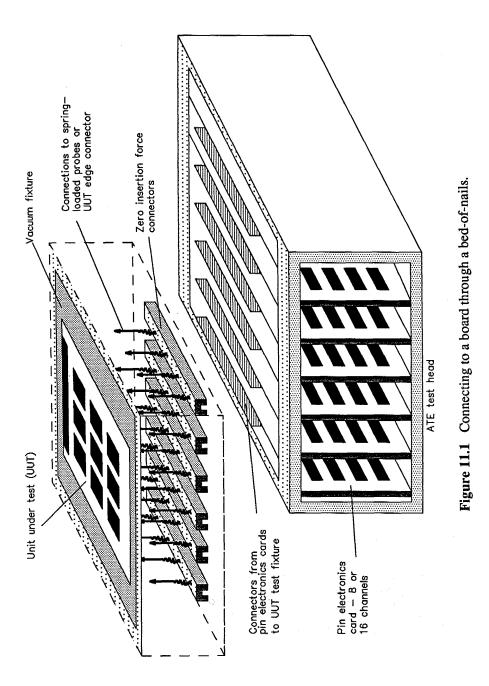

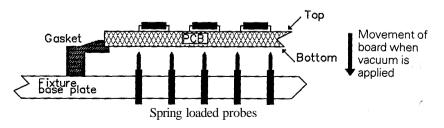

The advantages of the bed-of-nails — an array of pins on to which the product is placed during testing that gives access to many internal connections simultaneously — are exploited to the full by the in-circuit board tester. The idea is to provide direct access from the tester to each connection of each component in the circuit and to use these connections to test for the correct operation of each component in isolation, and of the links between them. The assumption is that the majority of the faults that are likely to be introduced during production can be detected in this way. The benefit is that test development costs are low, since tests for a device type can be reused on other products containing the device.

While this type of tester has become increasingly popular in recent years, primarily because the development of test programs for it is relatively inexpensive, it is important to note two points. Firstly, the tests which incircuit testers apply cannot detect certain faults that can arise through incorrect interaction between components. Secondly, the question of whether the technique may actually damage the components being tested remains unresolved. The problem is that, in order to apply a test to the inputs of one component, the outputs of others will have to be overdriven if they are not in the required logic state. The overdriving process causes a significant amount of current to flow into the output stages of the devices driving the network, which may cause damage if not carefully controlled.

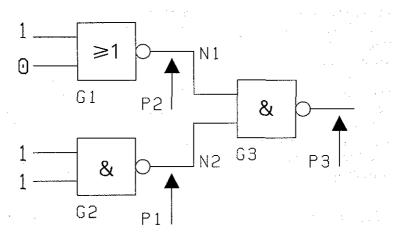

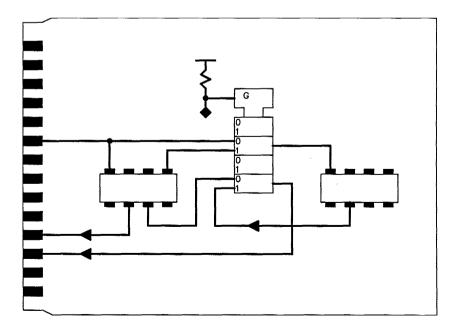

The small example circuit, in Figure 1.8 will be used to illustrate the overdriving process. During the test of component G3, components Gl and G2 are powered up and, as a result of signals at their inputs, would normally be driving wires Nl and N2 to 1 and 0 respectively. To test G3 wires Nl and N2 must be set to both 0 and 1 as shown and the ATE does this through the bed-of-nails by supplying sufficient current to force the wires to the required test values, irrespective of the values being driven by Gl and G2. During overdriving the current supplied by the ATE flows mainly through the output stages of Gl and G2 and, if testing continues for sufficient time, this may cause damage. The facility to place a component's outputs in a high impedance state while the components it drives are tested eliminates the possibility of damage to the IC from overdriving.

Another problem area for in-circuit testing arises from the need to make contact to every connection on the board. This may require 1000 or more contacts to be made to the board through a bed-of-nails. For **dual-in**-

Figure 1.8 In-circuit testing.

**line/plated-through-hole** (DIL/PTH) technology this degree of access is achievable; however, for miniaturized **surface-mount technology** (SMT) the need for such extensive access can become a significant problem. Cluster/functional testers provide one way of avoiding the worst of these difficulties.

#### **Functional board testers**

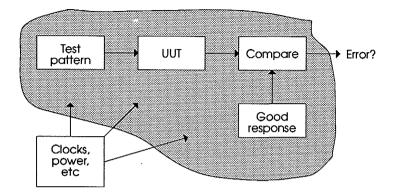

The functional board ATE works by applying a sequence of logic value changes, the test program, to the product and comparing its observed response with that which would be expected if it were fault-free. The test program is carefully designed for each product with the aim of exercising every part of the circuit. Both the test program and the expected response are held in the memory of the test system.

Normally, both the application of the test program and the observation of the product's response would be done using the product's normal operating connections. However, in some cases the test program may be made more effective by allowing the tester direct access to internal parts of the circuit, either through the use of hand-positioned probes and clips or via a bed-of-nails. Such techniques are used extensively when diagnosing faults in circuit cards, as will be discussed in Section 1.5.

#### Cluster/functional board testers

Cluster testers provide an effective combination of the in-circuit and functional test approaches. In cluster testing (also known as function testing) groups of components performing an identifiable function within the complete design are tested independently of surrounding circuitry. For example, a microprocessor board will contain functions such as RAM, **read**-

**only memory** (ROM), communication interfaces, the processor, and so on. Some of these functions are implemented in a single component (for example, the processor), while others require groups of components (for example, the RAM).

The ability to test components in small groups with a clear function allows test development costs to be reduced and, where a function is used in several products, for the test to be reused (as for in-circuit testing). Unlike in-circuit testing, however, defects due to improper interaction between components will be detected. The fact that groups of components are tested, rather than a single component, means that diagnostic tools must be provided (see Section 1.5).

#### 1.4.2. Problems encountered in test application

As with test development, the process of applying a test to a circuit using an ATE can be made more difficult and time-consuming if certain problems are encountered, due both to the electrical and physical design of the circuit.

Considering first the circuit's electrical design, the problems are in the main due to difficulty in controlling the circuit from the ATE. One example is with circuits containing on-board clocks. In such cases it is necessary for the ATE to be able to synchronize to the on-board clock if the circuit is to be tested at all, and (preferably) for the ATE to be able to substitute for the on-board clock during testing. This latter approach allows testing to proceed at the ATE's own speed. Other similar examples of difficulty exist, primarily due to problems in matching the timing of the circuit to that of the ATE. In many cases, the operating speed of the ATE will be considerably lower than that of the circuit being tested, and this, should be considered when the circuit is designed. It is almost certain that circuits which depend on critical timings for their successful operation will not be able to be properly tested.

The other area in which problems can arise is in the physical design of the circuit or product — the way that printed circuit boards are designed, and so on. Of particular interest is the ease with which the circuit can be connected to the tester — obviously the more difficult the connection is to make, the slower the process will be.

#### 1.5. Fault diagnosis

After the first application of the test, the ATE will be able to say either that the circuit is fault-free (in which case no further action needs to be taken) or that it contains one or more faults. The next step depends on the type of product and the type of tester being used.

For IC testing, diagnosis is frequently not required, since repair is not practical for many component designs. However, some devices (e.g., RAMs)

allow repair by including 'spare' logic blocks within the design that can be switched into the circuit in place of faulty blocks. Diagnosis may also be needed to isolate the cause of the fault to allow modification of the design such that the problem is avoided or to tune the production process.

For board testing, diagnosis is implicit when using an in-circuit test system since the test is applied to one replaceable unit (chip) at a time. For functional and cluster/functional test systems, however, further work must be done to locate the fault once it has been detected. Two methods of automated diagnosis are possible — the use of a fault dictionary, or guided probing — and, while they can be used separately, a combination of them is likely to be more efficient. These two techniques are discussed briefly below.

#### 1.5.1. Fault dictionaries

The fault dictionary is prepared as a by-product of the fault simulation process described in Section 1.3.3. It is a reference table which, for example, gives a list of the faults that will be detected at each step in the test program, organized according to the particular output of the circuit at which the fault becomes apparent. In many cases, the ATE will stop running the test on the first step at which a fault is detected, in which case the fault dictionary will list those faults which are first found at each step.

It is not uncommon for each line of the dictionary to include just one or two faults, so the dictionary can be used to significantly restrict the area of the circpit that needs to be examined for exact diagnosis using the guided probe.

#### 1.5.2. Guided probing

The guided probe is an additional source of information, and can be used to examine each connection in the circuit as if it were a direct connection to the ATE. The fault-free behaviour of all internal connections will have been evaluated during fault simulation and filed in the ATE's memory, for later comparison with the performance of a circuit under test.

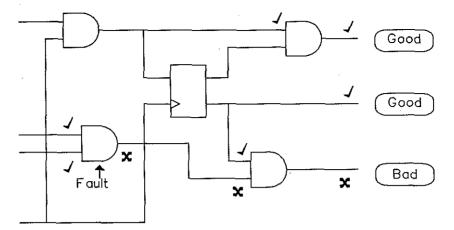

During guided probing, the ATE will direct the operator to place the probe at specific points in the circuit in an ordered manner, as illustrated in Figure 1.9. In the absence of a fault dictionary, probing will start from the circuit output at which the fault was first detected. The probe is then placed in turn on the input connections to the device feeding that output and the test program re-run. The output from each connection is compared with that stored on the ATE and, as a result, 'bad' or 'good' flags can be associated with each of the inputs to the device. The process is repeated, tracing the 'bad' connections back through the circuit, until either:

Figure 1.9 Guided probing.

- (1) A device is found which has a 'bad' output but 'good' inputs. This may be caused by a faulty device, by a fault on the output connection (for example, a short circuit or a stuck-at fault but not by an opencircuit fault), or by a fault at the input of a device driven from a 'bad' signal.

- (2) A connection is found with a 'good' signal at the driving end, but a 'bad' signal at the receiving end. This could be caused by an opencircuit fault, for example.

The basic procedure described above will almost certainly be enhanced to improve the accuracy of the diagnosis. For example, both the driving and receiving ends of a suspect connection may be probed so that open-circuit connections can be diagnosed. Also, if a fault dictionary is available, then probing may start at some point within the circuit rather than at the circuit outputs, thus cutting out much unnecessary activity.

A further refinement is the use of a current-sensitive probe to resolve the locations of certain types of fault on bus-structured circuits. The probe allows the location of the fault to be determined, even though its effect is evident on all parts of the bus.

#### 1.5.3. Problems encountered during fault diagnosis and repair

Problems encountered during diagnosis are primarily due to the physical design of the product being tested — for example, problems in placing probes on connections in the circuit because devices are too closely spaced. Other problems can be caused by the layout of the circuit which can impede diagnosis by making it difficult for the operator to locate or access the points he is asked to probe.

#### 1.6. Design-for-test

The goal of design-for-test is to ensure that a completed product design can be economically tested, both following manufacture and during its operational life. The following sections provide a brief introduction to the aims and scope of design-for-test.

#### 1.6.1. Do you want to create a 'quality' design?

Would you like to feel that you have created an excellent product and not have the manufacturing and repair organizations complain about poor testability?

If your answer is yes, read on. This book has the information you need to create a testable product that is matched to test capability in a wide range of manufacturing and repair operations.

#### 1.6.2. Design-for-test starts when design work starts

Designs which work as bench-top prototypes may not necessarily be capable of volume manufacture or be economically supportable, since manufacturability or maintainability may not have been properly considered. Manufacturability issues include the suitability of the product for autoinsertion of its components, the suitability for wave soldering, the provision of adequate timing margins, and the ease of testing the assembled product. Maintainability issues include reliability, the ease of testing in the field and during repair, and the ease of diagnosing faults. Indeed the general experience throughout the electronics industry is that the designer must specifically target manufacturability, maintainability and other issues from the outset if a product is to be a success, both technically and commercially.

Testability — the ease of testing a product and, when required, locating faults — is a key contributor to both manufacturability and maintainability. Many electronics companies now state that test costs account for of the order of 50% of the total life cycle cost, so testability can have a significant impact on a product's commercial viability.

The best way to achieve adequate testability is to include testability as a design objective from the outset. Designing testability into a product after the initial design is complete is difficult, a waste of valuable resources, and will, in general, produce a less than satisfactory result.

#### 1.6.3. What aspects of a design impact its testability?

From the preceding sections, it can be seen that testability impacts two facets of product design:

#### 22 INTRODUCTION TO TESTING AND TESTABILITY

- *O Circuit design.* Here design-for-testability will permit easier test development and may give shorter test application times.

- *O Physical design.* For example, design-for-testability will ensure that sufficient access is available to allow internal connections of the product to be examined during fault diagnosis.

## 1.6.4. Testability isn't free

To make a product testable, circuitry or other features must usually be added to those needed to realize the intended function. Therefore the benefits of having a testable design must clearly be viewed against the costs of achieving testability. Costs (like benefits) fall in two areas:

- O *Non-recurring costs.* Non-recurring costs arise through increased design time, both to include testability features in the design and in the testability assurance process. Generally these costs will be a small fraction of the complete design cost, particularly if the designer is properly trained in design-for-testability. Non-recurring costs are offset by reductions in the start-up costs of testing (e.g., in test development) and savings in recurring test costs (e.g., the time to test and diagnose the product).

- *O Recurring (per item) costs.* These arise during manufacture and/or maintenance. Recurring costs result from increased board or chip size, added logic or components needed to achieve testability, and so on. These costs will be offset by benefits such as reduced test and diagnosis time on the ATE (giving increased throughput).

The objective is to give a reduced overall life cycle cost for the product, not to minimize the localized costs of one aspect of the product's life. Testability may not be free, but any investment must produce a return.

The benefits of having a testable design must clearly be viewed against the costs of achieving testability. Costs (like benefits) fall in two areas: non-recurring costs during product development and recurring (per item) costs during manufacture and/or maintenance. Non-recurring costs arise through increased design time, both to include testability features in the design and in the testability assurance process. Generally these costs will be a small fraction of the complete design cost, particularly if the designer is properly trained in design-for-testability. Recurring costs result from increased board or chip size, added logic needed to achieve testability, and so on. Clearly an objective during design-for-testability is to keep the recurring costs to a minimum — but it must be recognized that testability may not be free.

REFERENCES 23

# References

#### Useful tutorial texts

The following is a short list of tutorial texts which contain a more complete discussion of electronic test technology (including test generation and design-for-testability) than that included in this chapter.

- Agrawal V.D. and Seth S.C. (1988). *Test Generation for VLSI Chips*. Los Alamitos, Calif.: IEEE Computer Society Press.

- Bennetts R.G. (1981). *Introduction to Digital Board Testing*. New-York & London: Crane-Russak/Edward Arnold.

- Bennetts R.G. (1984). *Design of Testable Logic Circuits*. London: Addison-Wesley.

- Miczo A. (1986), *Digital Logic Testing and Simulation*. New York: Harper & Row.

- Parker K.P. (1987). Integrating Design and Test—Using CAE Tools for ATE Programming. Los Alamitos, Calif.: IEEE Computer Society Press.

## Papers

- Eldred R.D. (1959). Test routines based on symbolic logic statements. Journal of ACM, 6(1), 33-36.

- Reinerstein D.G. (1983). Whodunit? The search for the new-product killers. *Electronic Business*, (July), 62, 64, 66.

- Williams T.W. and Brown N.C. (1981). Defect level as a function of fault coverage. *IEEE Transactions on Computers*, C-30(12), 987-988.

# CHAPTER 2. Design-for-Test Techniques

- 2.2 Do nothing

- 2.3 Design-for-test guidelines

- 2.4 Scan design2.5 Self-test References

# 2.1. Introduction

Chapter 1 highlighted several problems that can arise when testing an integrated circuit or loaded board. Key causes of these problems are:

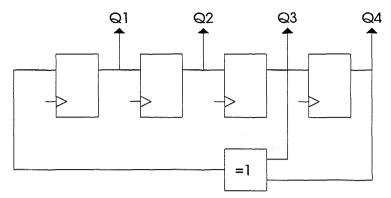

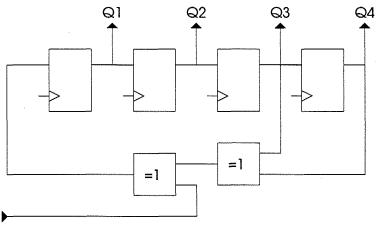

- (1) Complexity. The difficulty in generating a test is related both to the size (for example, number of gate-equivalents) and complexity (for example, amount of feedback around or cross-connection between logic blocks). For combinational circuits, test generation costs vary on the order of  $N^2$ , where N is the number of gate-equivalents in the design (Goel, 1980). For sequential circuits, test costs are further increased by the presence of stored-state devices and feedback.

- (2) *Speed.* For state-of-the-art ICs or boards, the maximum operating speed is likely to exceed that of the automatic test equipment (ATE)

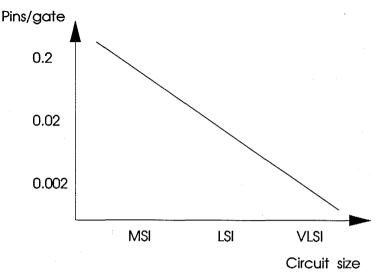

Figure 2.1 Variation of pin count with IC complexity.

used to apply tests. The ATE is built using yesterday's technology, but is expected to test today's products.

- (3) Access. During functional testing, most (if not all) connections between the ATE and the IC or board are made through the normal inputs and outputs (the package pins or board connectors). While the complexity of ICs and boards is rising rapidly, the number of external connections is relatively static (e.g., as shown in Figure 2.1). Therefore, more and more test data must be transferred through a limited number of connections from the ATE to the unit under test (UUT). This causes a bottle-neck, increasing test time and, in consequence, reducing ATE throughput.

- (4) *Miniaturization.* Through use of surface-mount assembly techniques, the geometries of loaded boards can be reduced considerably. The result, however, is that access to internal chip-to-chip interconnections on the board using bed-of-nails or guided probes becomes difficult. Unfortunately, probing is an inherent feature of incircuit and functional testing.

The use of design-for-test techniques during the development of a new circuit design can reduce these problems and, as a result, reduce the cost of testing the circuit in production or during field service.

In this chapter, an overview will be given of the principal design-fortest techniques for digital circuits — both for ICs and for loaded boards. The intention here is to give readers an understanding of what each technique involves. The techniques that are of most value in the design of loaded boards — design-for-test guidelines and boundary-scan — will be discussed in more detail later in the book. The remainder are most widely used in the design of ICs. In these cases, the aim of this chapter is to give readers sufficient information to allow them to converse with the designers and vendors of ICs — not to enable them to design the ICs themselves.

For convenience, the design-for-test techniques are introduced in an historical sequence.

# 2.2. Do nothing

Of course, the designer could decide to ignore testability completely — to concentrate solely on meeting the functional requirement for the design.

Nobody worried about design-for-test when designing boards with small and medium scale ICs, so why bother now? The test engineering department could generate tests for everything we sent them. Can't they still do that for designs that use VLSI ICs?'

The problem is that test costs rise exponentially as the complexity of a circuit rises. Double the circuit complexity and, without design-for-test, test costs may quadruple — that is, if a test can be generated at all.

True, in the 1970s, when ICs and loaded boards contained only simple circuits, test engineers were able to create thorough test programmes for every design they received. They did not have to become involved in the design process themselves because, although it would be more difficult to create tests for some designs than for others, the cost of the work was small compared to the design cost — even for those designs that were quite difficult to test.

Organizations and the people in them adapted to this scenario:

- Highly-separated design and test teams were created.

- G The 'over the wall' mentality evolved. Designers created the product and refined it up to a point where it could be passed on to production engineering. Production engineering dealt with the task of turning the prototype design into something that could be manufactured and tested. Test engineering could be staffed with relatively low-grade labour. Highly-trained engineers were needed for design; failed designers went into test engineering! (Needless to say, the author does not share this view!)

Some companies are still suffering from these attitudes and organizational structures today.

For very-large-scale integration (VLSI) ICs, and boards that contain them, test engineering is a function that requires highly-skilled staff who must be closely involved in the design process from the outset. Today, a company that omits consideration of testability from the design process is taking an enormous commercial risk:

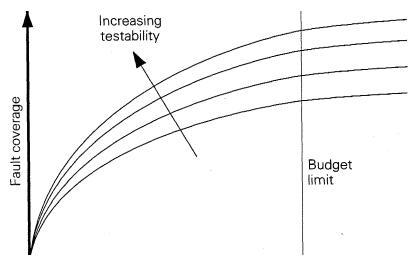

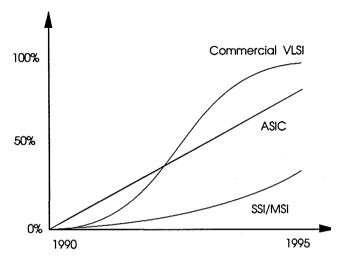

O The usual result of poor testability is that the test engineering team will not be able to create a sufficiently thorough test programme within the time and budget allowed. This is illustrated in Figure 2.2.

As testability reduces, the fault coverage achievable on a fixed budget reduces. This is important, because time-to-market pressures normally prevent more time and budget being allocated to overcome test problems (Reinerstein, 1983).

- G With an inadequate test programme, a greater number of defective parts will be shipped to customers — the tests needed to highlight the presence of their faults just aren't in the test programme. Figure 1.2 in Chapter 1 showed the relationship between shipped product quality, manufacturing yield, and test programme effectiveness.

- O Customers find the defects missed by the test Murphy's Law applies (if anything can go wrong, it will usually at the most inconvenient time).

- O Companies with a reputation for poor quality lose business!

Test development time

Figure 2.2 The effect of testability on test development time.

# 2.3. Design-for-test guidelines

Design-for-test guidelines are lists of *dos* and *donts* generated by test engineering departments. They record ways of designing circuits shown by

experience to result in reduced test costs (the *dos*) and ways of designing circuits that result in increased test costs (the *don'ts*). In effect they provide a feedback path from test engineers to designers that, over a period of time, will result in better (that is, more testable) designs emerging from the design department.

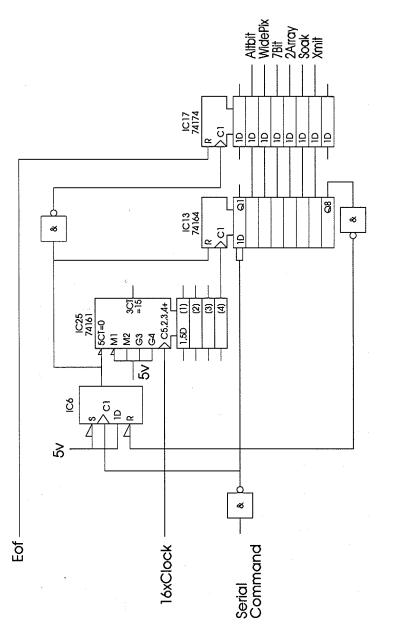

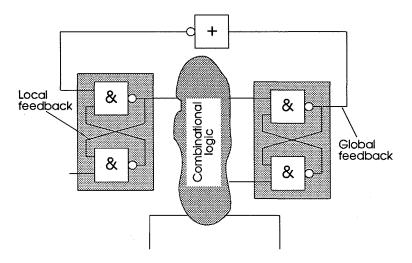

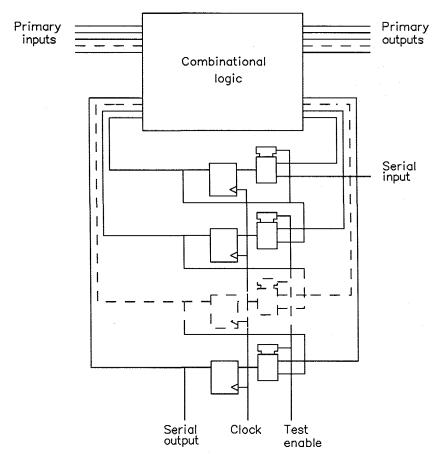

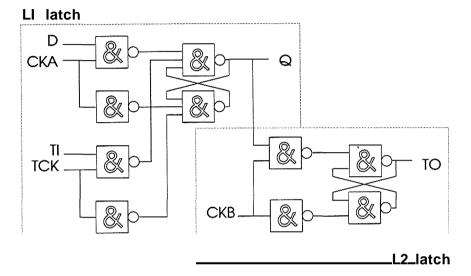

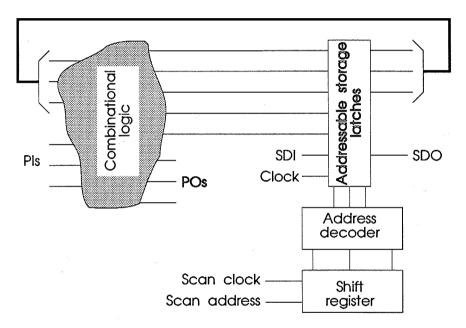

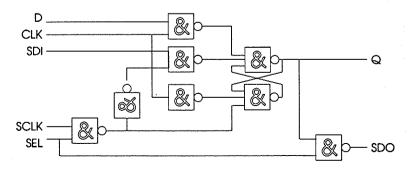

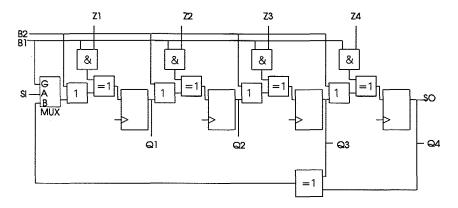

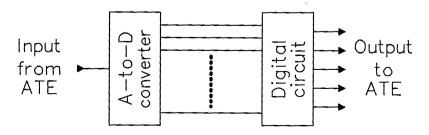

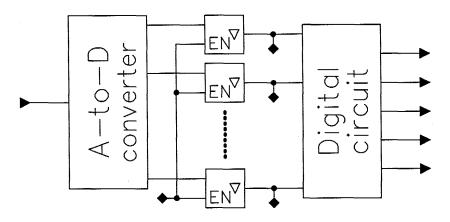

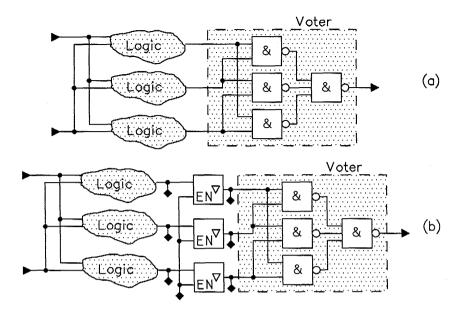

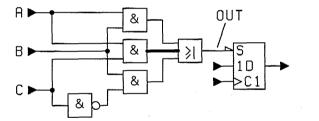

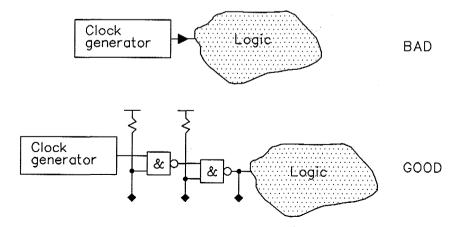

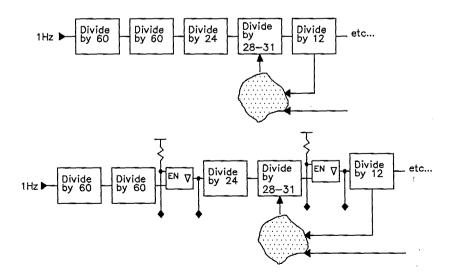

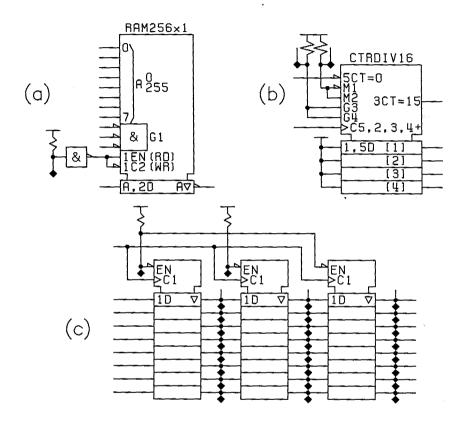

Part 2 of this book contains an extensive list of design-for-test guidelines for use during board design. Many of these guidelines are also useful in the design of ICs. To illustrate how design-for-test guidelines might be applied, consider Figure 2.3.