#### Nanoscale Devices Physics, Modeling, and Their Application

Edited by Brajesh Kumar Kaushik

## Nanoscale Devices

## Nanoscale Devices Physics, Modeling, and Their Application

Edited by Brajesh Kumar Kaushik

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2019 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works

Printed on acid-free paper

International Standard Book Number-13: 978-1-138-06034-0 (Hardback)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www. copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

Trademark Notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

| Library of Congress Cataloging-in-Publication Data                                   |  |

|--------------------------------------------------------------------------------------|--|

| Names: Kaushik, Brajesh Kumar, editor.                                               |  |

| Title: Nanoscale devices : physics, modeling, and their application / [edited        |  |

| by] Brajesh Kumar Kaushik.                                                           |  |

| Description: Boca Raton : Taylor & Francis, a CRC title, part of the Taylor &        |  |

| Francis imprint, a member of the Taylor & Francis Group, the academic                |  |

| division of T&F Informa, plc, 2019.   Includes bibliographical references and index. |  |

| Identifiers: LCCN 2018026865  ISBN 9781138060340 (hardback : acid-free paper)        |  |

| ISBN 9781315163116 (ebook)                                                           |  |

| Subjects: LCSH: Nanoelectronics.   Nanoelectromechanical systems.                    |  |

| Nanotechnology.                                                                      |  |

| Classification: LCC TK7874.84 .N3835 2019   DDC 621.381dc23                          |  |

| LC record available at https://lccn.loc.gov/2018026865                               |  |

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

To my Father, Late Mr. Jai Prakash Kaushik, and my Mother, Mrs. Karuna Kaushik, for their affection and untiring efforts in my upbringing. Also dedicated to my wife, Supriya, and our loving son, Partha Kaushik. Life has been really enjoyable because of the efforts of all my friends and students. Dedicated to all of them.

Brajesh Kumar Kaushik

### Contents

| Preface         | .ix |

|-----------------|-----|

| Acknowledgmentx |     |

| Editor          |     |

| Contributorsxv  |     |

#### Section I Nanoscale Transistors

| 1. | 1. Simulation of Nanoscale Transistors from Quantum and Multiphysics<br>Perspective                                     |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------|--|--|

|    | Zhipeng Dong, Wenchao Chen, Wen-Yan Yin, and Jing Guo                                                                   |  |  |

| 2. | <b>Variability in Nanoscale Technology and EδDC MOS Transistor</b> 25<br>Sarmista Sengupta and Soumya Pandit            |  |  |

| 3. | <b>Effect of Ground Plane and Strained Silicon on Nanoscale FET Devices</b>                                             |  |  |

| Se | ction II Novel MOSFET Structures                                                                                        |  |  |

| 4. | <b>U-Shaped Gate Trench Metal Oxide Semiconductor Field Effect Transistor:</b><br><b>Structures and Characteristics</b> |  |  |

| 5. | <b>Operational Characteristics of Vertically Diffused Metal Oxide</b><br><b>Semiconductor Field Effect Transistor</b>   |  |  |

| 6. |                                                                                                                         |  |  |

#### Section III Modeling of Tunnel FETs

| Sec | ction IV                                        | Graphene and Carbon Nanotube Transistors<br>and Applications                                            |     |

|-----|-------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|

| 9.  |                                                 | <b>f Graphene Plasmonic Terahertz Devices</b><br>nd Nagendra P. Pathak                                  | 175 |

| 10. |                                                 | <b>CNTFET for SRAM Cell Design</b>                                                                      | 205 |

| 11. |                                                 | <b>Ternary Logic Circuits Using CNFETs</b>                                                              | 225 |

| Sec | tion V                                          | Modeling of Emerging Non-Silicon Transistors                                                            |     |

| 12. | and Outloo                                      | nalytical Models for Organic Thin-Film Transistors: Overview<br>k<br>and R. Bourguiga                   | 257 |

| 13. | <b>A Fundame</b><br>and Its App<br>D. Nirmal ar | ntal Overview of High Electron Mobility Transistor<br>lications<br>Id J. Ajayan                         | 275 |

| Sec | ction VI                                        | Emerging Nonvolatile Memory Devices<br>and Applications                                                 |     |

|     |                                                 | <b>Based Memory and Logic Devices</b><br>atterjee, Pankaj Sethi, and Chandrasekhar Murapaka             | 301 |

| 15. |                                                 | als, Modeling, and Application of Magnetic Tunnel Junctions<br>l, Arman Roohi, and Ronald F. DeMara     | 337 |

| 16. | Application                                     | rices: Underlying Physics, SPICE Modeling, and Circuit                                                  | 369 |

| 17  |                                                 | atem, T. Nandha Kumar, and Haider A. F. Almurib<br>of Nanoscale Memristor Device for Analog and Digital |     |

|     | Application                                     | gh and Balwinder Raj                                                                                    | 393 |

| Ind | ex                                              |                                                                                                         | 425 |

### Preface

The pace of advances in nanoscale materials and devices has led to a gamut of developments in the emerging areas of science and technology that has permeated to almost all applications. The *rapid growth* of the electronics industry can be attributed by and large to the continuous progress in nanotechnology driven by a relentless pursuit of innovation. With the new prospects from emerging nanomaterial and devices, a frontier challenge is to gain insight into their behavior and properties. The aim of this book is to integrate developments in the area of nanoelectronics devices and systems, evolving from a unifying set of principles and practices. This book is a collective effort of well-known pioneers and many leading researchers in the field of nanoelectronics, nanomaterials, plasmonics, and related areas, providing extraordinary breadth and depth of coverage. To comprehend this book, a basic knowledge of semiconductor physics is assumed. In 17 chapters, grouped under 6 subareas, the book eloquently covers the major advancements in the field of nanoelectronics. The book presents an interdisciplinary perspective of nanoelectronics and can serve as a comprehensive reference for researchers and academicians working in the area of nanotechnology.

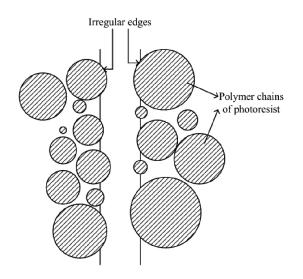

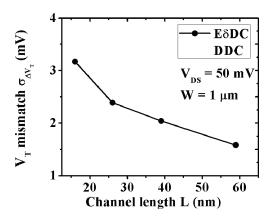

The continuous miniaturization of transistors has been considered a primary reason behind the progress in the electronics industry. New approaches based on quantum mechanics and a multiphysics perspective are now required to accurately model these nanoscale transistors. The first section of this book provides a comprehensive overview of quantitative understanding of the operation of nanoscale transistors. It begins with an introduction to nanoscale transistors, their current state of development, and various challenges associated with commercialization of the technology. Chapter 1 of the book deals with the recent development in modeling and simulation of nanoscale transistors. A multiphysics approach has been used to capture the relevant physics at the atomic level while taking quantum effects into account. The major challenge to the present and nextgeneration nanoscale device is the variability that requires serious attention. Considering this fact, Chapter 2 discusses the major sources of variability in nanoscale devices and circuits. To increase the robustness of a design, the impact of process, voltage, and temperature variation has been modeled and analyzed using technology computer-aided design (TCAD) simulations. An epitaxial delta-doped channel (E $\delta$ DC) MOS transistor is a promising approach for extending the scalability of bulk metal oxide semiconductor (MOS) technology for low-power system-on-chip applications. The subsequent part of the chapter discusses the structure and characteristics of  $E\delta DC$  MOS transistors and compares them with a conventional MOS transistor.

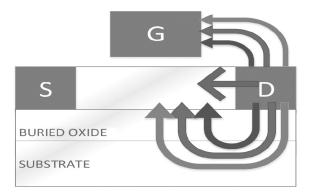

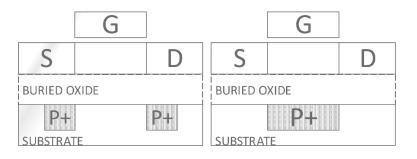

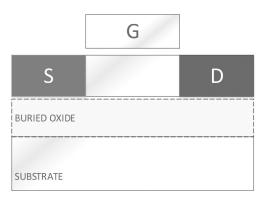

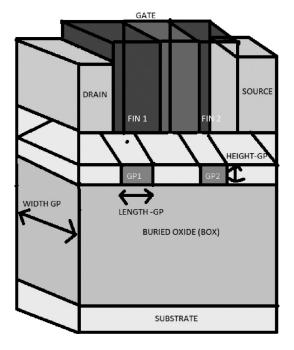

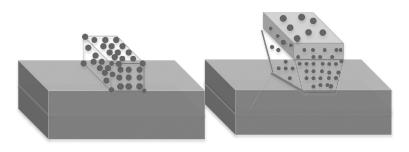

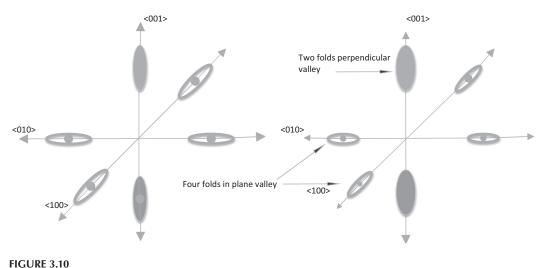

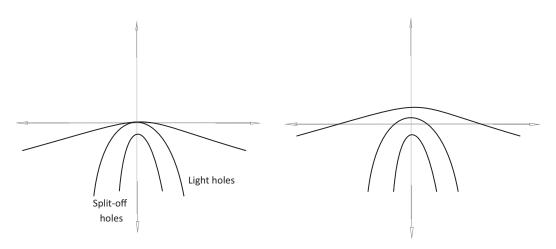

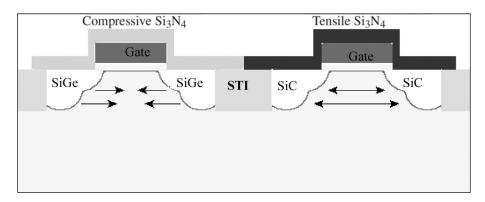

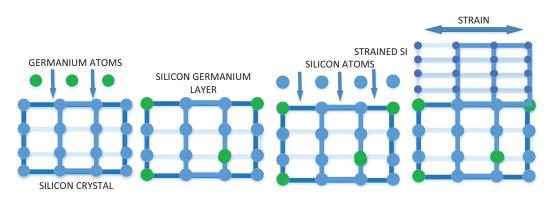

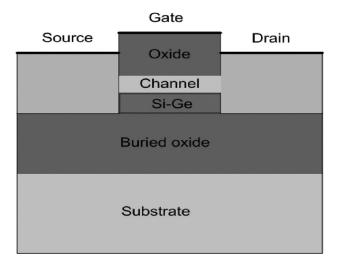

For nanoscale semiconductor field-effect transistor (FET) devices, several efforts have been made to reduce the short-channel effects (SCEs). For controlling short-channel effects, a ground plane can be formed in the silicon substrate underneath the buried oxide. Chapter 3 compiles the application of ground plane and strained engineering for high-performance silicon on insulator (SOI) FET devices. The first part introduces the concept of ground plane in SOI structures and the method of incorporation in fully depleted silicon on insulator (FDSOI) and fin field-effect transistor (FinFET) devices. The later part of the chapter discusses the strained-silicon concept to boost the device performance through higher carrier mobility and reduced source/drain resistance. The chapter discusses the basic concepts for introducing strain in CMOS transistor channels. The methods and structures for making strained FDSOI and strained FinFET device structure have been presented.

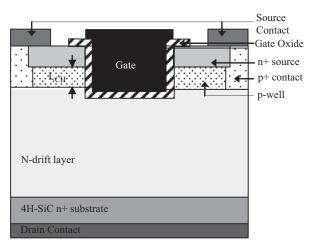

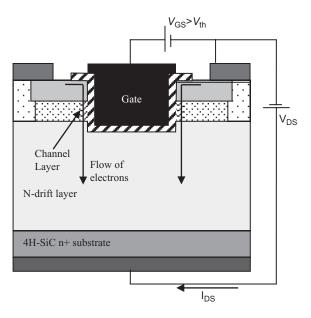

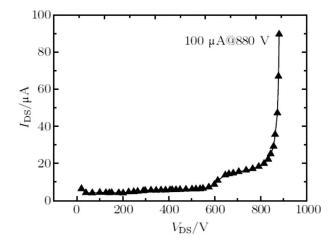

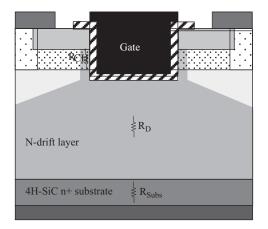

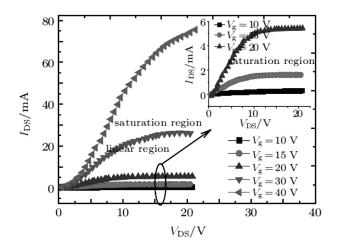

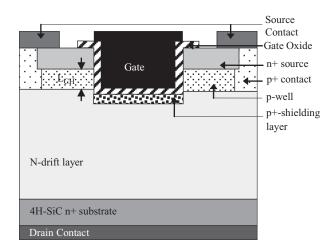

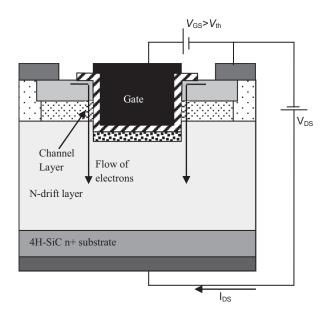

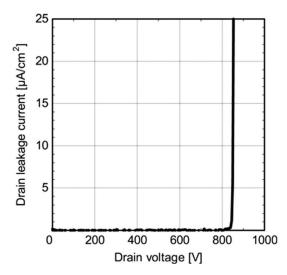

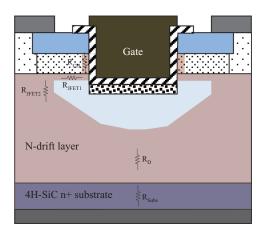

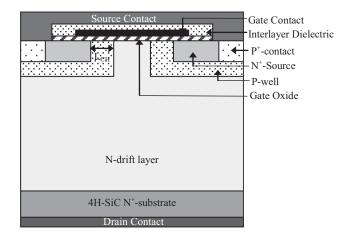

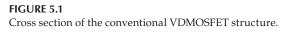

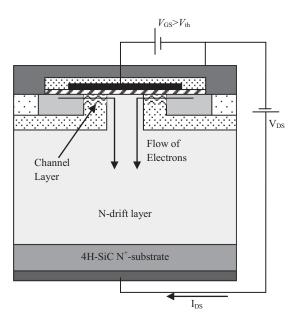

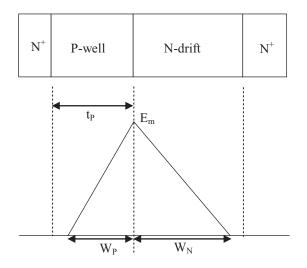

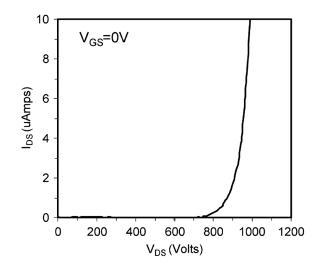

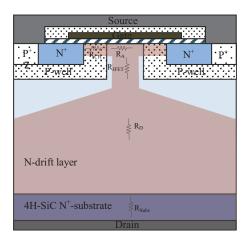

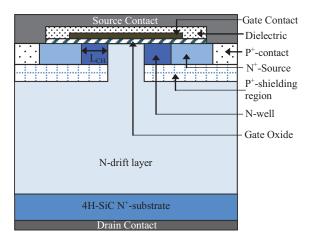

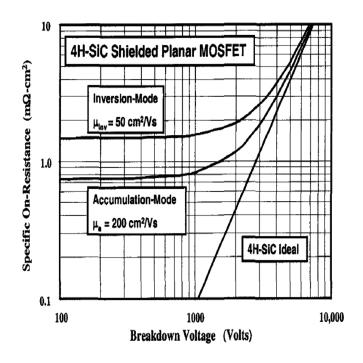

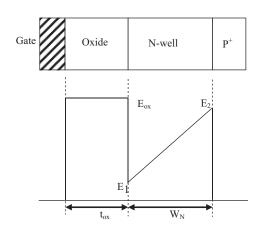

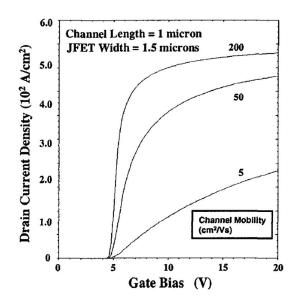

Improvement in the transistor structure is considered to be a novel way for sustaining performance improvement with aggressive device scaling. The benefits derived with various alternative device architectures can be seen as a possible alternative to the conventional planar MOSFET. Section II of the book presents such novel structures to improve device performance. It is organized with the aim of finding and building a successful novel device structure that can replace conventional MOSFET. The need for higher operating voltages and switching speeds has necessitated the use of alternative structures and materials in the power electronics domain. Basic principles of operation of the U-shaped gate trench MOSFET (UMOSFET) structure are discussed in Chapter 4. The superior onresistance for this structure makes it a possible contender in high-frequency power circuits. Numerical analysis has been presented for evaluating the effectiveness of the device in comparison to vertical double-diffused MOSFET (VDMOSFET). The VDMOSFET dominates the medium voltage-level power electronic applications. Chapter 5 analyzes performance of the VDMOSFET structure including shielded accumulation-mode MOSFET (ACCUFET) structures for the development of monolithic power switches from silicon carbide. To accommodate future technology nodes, double-gate MOSFET (DGFET) has been shown to be more optimal due to the improved short-channel effects and reduced leakage current compared to conventional FET. The double-gate MOSFET (DG-MOSFET) has several advantages over conventional single-gate (SG) MOSFETs. Chapter 6 explores the scope of DGMOSFETs for use in future high-performance, low-power nanoscale device applications. Modeling and analysis of various configurations of DGMOSFETs, such as symmetric/asymmetric with gate and channel engineering, have been presented in the chapter.

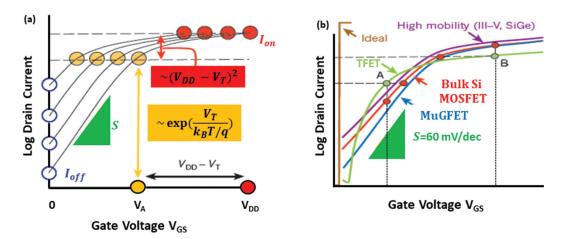

Tunnel field-effect transistors (TFETs) are also considered to be a potential successor of MOSFETs by enabling the supply voltage ( $V_{DD}$ ) scaling at nanometer dimensions due to the absence of a subthreshold swing limit of 60 mV/decade. The third section of the book would enhance the knowledge base of the reader in the area of tunnel FETs. Currently, it is of prime interest to develop compact analytical models, describing the device operation to meet the circuit and system design. Chapter 7 of the book deals with potentials and challenges of analog circuits based on unique characteristics of *TFET*. The chapter discusses parameters of TFET that are important for analog circuit operations. Different TFET architectures have been studied to overcome the challenges in conventional TFET. Doping-less structure has been proposed as a potential solution to overcome the need of creating abrupt junctions in TFETs. Chapter 8 deals with the performance analysis of a dual-metal double-gate tunnel FET device and its advantages over doping-less TFET.

The fourth section of the book focuses on nanocarbons, in particular carbon nanotubes and graphene, and their application in the area of electronics and plasmonics. The realization of these carbon-based materials has facilitated many interesting nanodevices for future technological revolutions. In recent years, there have been substantial efforts in filling the (*THz*) design gap. The recent advancement in photonics and nanofabrication technology opens up the development of plasmon-assisted devices. The prospects of graphene-based plasmonic devices for THz applications attract several research and application areas. Chapter 9 of the book provides an overview of optical and electronic properties of graphene and discusses graphene-based plasmonic waveguides for the terahertz range operation while targeting the multiplexing/demultiplexing and sensing applications. In nano-regime, carbon nanotube field-effect transistor (CNTFET) technology has been actively researched as an alternative to the conventional CMOS technology. CNTs have shown remarkable electronic properties that distinguish them as a good replacement for channel material in MOSFET also. CNTFET significantly outperforms the MOSFET and FinFET-based memory cells in the metrics of power, delays, and noise. Chapter 10 covers the important aspects of CNT for various electronic applications. The chapter presents the fundamental concepts of CNTFETs with a major focus on application of CNTFET for low-power static random access memory (SRAM) cell design. It is quite sensible to investigate newer circuit with CNFETs because of their unique structure and electrical characteristics. Ternary logic is a promising alternative to conventional binary logic, realizing energy-efficient circuits. Chapter 11 discusses the design of ternary logic circuits that are benefitted from the unique properties of carbon nano-tube field-effect transistors. The combination of ternary logic and CNFETs has the capability of achieving highly efficient digital systems.

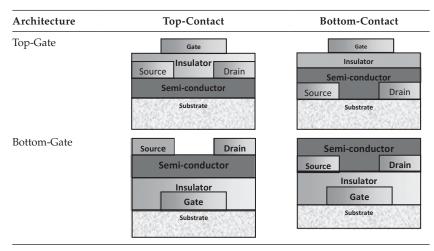

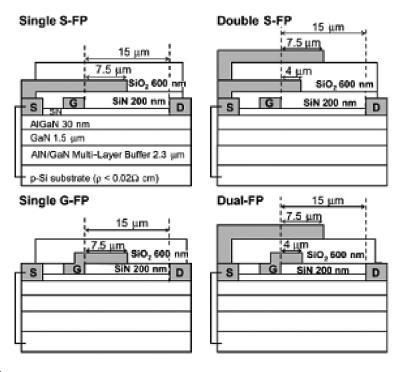

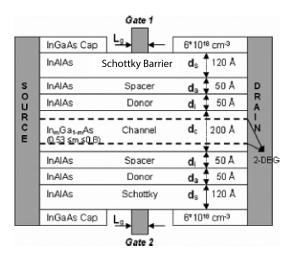

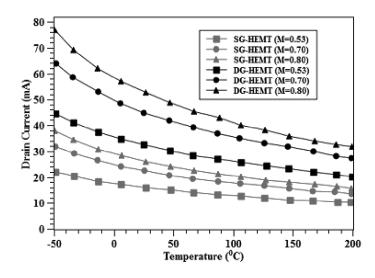

The section V of the book presents recent approaches toward the modeling of emerging transistors employing non-silicon materials. The III-V compound semiconductors-based high electron mobility transistors (HEMTs) are rapidly emerging as front-runners in high-power millimeter, submillimeter, and microwave and THz applications. Chapter 12 provides readers with an overview of state-of-the-art HEMT devices. The chapter covers the working principle of the device followed by analysis of different structures of HEMTs. It develops a detailed theoretical framework of HEMT devices along with their application areas and future directions. Recently, the organic semiconductor (OSC)-based devices have been in focus due to low-cost fabrication techniques and their application in large-area electronics. Chapter 13 covers the emerging field of organic thin-film transistor (OTFT) while discussing the analytical methods for evaluation of device performance. The chapter deals with the device models that are developed using the underlying device physics and geometry-related parameters.

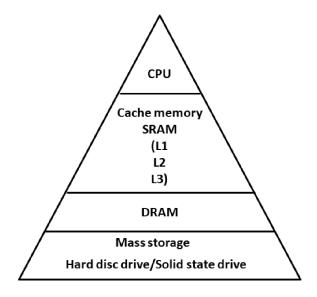

The last section of the book presents recent advances in nonvolatile memory and storage technology and provides an overview of future trends in the field. It covers a wide range of emerging memory device applications from state-of-the-art spintronic devices, magnetic tunnel junction to RRAM and memristor-based logic. Chapter 14 provides a comprehensive introduction to spintronics for an emerging class of high-speed, low-power memory and logic devices. Spintronic devices that utilize electron spin as a state variable for logic computation have recently emerged as one of the leading candidates for computing and data storage applications. The chapter focuses toward the future aspects of spintronics including spintronics-based energy-efficient on-chip memory and logic. Magnetic tunnel junctions (MTJs), are an important subset of spintronics devices. Magnetic storage technology has been under intensive study in recent years and is capable of overcoming the shortcomings of CMOS. Chapter 15 provides a platform to understand the fundamentals of MTJs, advanced device models, and their application in the area of field-programmable reconfigurable fabrics and logic-in-memory circuits. The past few years have seen an increased interest in resistive switching (RS) resistive random access memory (RRAM) for future data storage. Chapter 16 covers RRAM as one of the potential candidates for nonvolatile memories (NVMs) and their circuit applications. The chapter investigates the physicsbased mathematical models and circuit models of the  $Ta_2O_5/TaO_x$  bi-layered RRAM. A SPICE model has been developed to study the behavior of devices to be used in circuit simulations. The memristor provides an opportunity for design of high-performance circuits and memories at a nanoscale level. Chapter 17 reports the latest advances in the area of memristor and its application in the area of digital and analog computing.

The book integrates the recent research and development in the area of nanoelectronics and provides a synergic platform for further advancement of devices and systems. This book shall prove to be a convenient and thorough reference for academicians and practitioners in the field of nanoelectronics.

> Brajesh Kumar Kaushik Roorkee, India

## Acknowledgment

This book is the collective efforts of many researchers committed to the diversified fields of nanotechnology. I would like to acknowledge with gratitude all the authors for spending their precious time in creation of this edition.

I wish to express my heartfelt gratitude to one and all who directly or indirectly helped in the completion of this book.

Brajesh Kumar Kaushik

### Editor

**Brajesh Kumar Kaushik** received doctorate of philosophy (PhD) in 2007 from Indian Institute of Technology, Roorkee, India. He joined Department of Electronics and Communication Engineering, Indian Institute of Technology, Roorkee, as an assistant professor in December 2009; and since April 2014 he has been an associate professor. He has served as General Chair, Technical Chair, and Keynote Speaker of many reputed international and national conferences. Dr. Kaushik is a senior member of IEEE and member of many expert committees constituted by government and non-government organizations. He is an editor of *IEEE Transactions on Electron*

Devices; associate editor of IET Circuits, Devices & Systems; editor of Microelectronics Journal, Elsevier; editorial board member of Journal of Engineering, Design and Technology, Emerald; and editor of Journal of Electrical and Electronics Engineering Research, Academic Journals. He also holds the position of editor-in-chief of International Journal of VLSI Design & Communication Systems, and SciFed Journal of Spintronics & Quantum Electronics. He has received many awards and recognitions from the International Biographical Center (IBC), Cambridge. His name has been listed in Marquis Who's Who in Science and Engineering® and Marquis Who's Who in the World®. Dr. Kaushik has been conferred with Distinguished Lecturer award of IEEE Electron Devices Society (EDS) to offer EDS chapters with quality lectures in his research domain. His research interests are in the areas of high-speed interconnects, low-power VLSI design, memory design, carbon nanotube-based designs, organic electronics, FinFET device circuit co-design, electronic design automation (EDA), spintronics-based devices, circuits and computing, image processing, and optics- and photonics-based devices.

### Contributors

#### Paula Ghedini Der Agopian

Telecommunication Engineering Department Sao Paulo State University (UNESP) Sao Joao da Boa Vista, Brazil

#### J. Ajayan

Department of Electronics and Communication Engineering SNS College of Technology Coimbatore, India

#### Haider A. F. Almurib Department of Electrical and Electronic Engineering University of Nottingham Semenyih, Malaysia

Shashi Bala

VLSI Design Lab Department of ECE NIT Jalandhar Jalandhar, India

#### Deepshikha Bharti

Department of Electronics and Communication Engineering BIT, Mesra Ranchi, India

#### W. Boukhili

Laboratoire de Physique des Matériaux: Structure et Propriétés Groupe Physique des Composants et Dispositifs Nanométriques Faculté des Sciences de Bizerte Université de Carthage Carthage, Tunisia

#### R. Bourguiga

Laboratoire de Physique des Matériaux: Structure et Propriétés Groupe Physique des Composants et Dispositifs Nanométriques Faculté des Sciences de Bizerte Université de Carthage Carthage, Tunisia

#### Rajeevan Chandel

Department of Electronics & Communication Engineering National Institute of Technology Hamirpur, India

#### Jyotirmoy Chatterjee

CEA, CNRS, Grenoble-INP, INAC-SPINTEC Université Grenoble Alpes Grenoble, France

#### Saurabh Chaudhury

Department of Electrical Engineering NIT Silchar Silchar, India

#### Wenchao Chen

Zhejiang Province Lab of Advanced Micro/Nano Electronic Devices and Smart Systems State Key Lab of MOI College of Information and Electronic Engineering Innovative Institute of Electromagnetic Information and Electronic Integration Zhejiang University Hangzhou, China

#### and

ZJU-UIUC Institute Zhejiang University Haining, China **Cor Claeys** Electrical Engineering Department (ESAT) KU Leuven Leuven, Belgium

Ronald F. DeMara Department of Electrical and Computer Engineering College of Engineering and Computer Science University of Central Florida Orlando, Florida

#### **Rohit Dhiman**

Department of Electronics & Communication Engineering National Institute of Technology Hamirpur, India

#### **Zhipeng Dong**

Department of Electrical and Computer Engineering University of Florida Gainesville, Florida

#### Jing Guo

Department of Electrical and Computer Engineering University of Florida Gainesville, Florida

#### Firas Odai Hatem

Department of Electronics and Electrical Engineering Liverpool John Moores University Liverpool, United Kingdom

#### Aminul Islam

Department of Electronics and Communication Engineering BIT, Mesra Ranchi, India

#### Neetu Joshi

Department of Electronics and Communication Engineering IIT-Roorkee Roorkee, India

#### Ramandeep Kaur

Department of Electronics & Communication Engineering National Institute of Technology Hamirpur, India

#### Mamta Khosla

VLSI Design Lab Department of ECE NIT Jalandhar Jalandhar, India

#### T. Nandha Kumar

Department of Electrical and Electronic Engineering University of Nottingham Semenyih, Malaysia

#### Joao Antonio Martino

Laboratory of Integrated Systems Electronic System Department University of Sao Paulo Sao Paulo, Brazil

#### Marcio Dalla Valle Martino

Electronic System Department University of Sao Paulo Sao Paulo, Brazil

#### Chandrasekhar Murapaka

CEA, CNRS, Grenoble-INP, INAC-SPINTEC Université Grenoble Alpes Grenoble, France

#### D. Nirmal

Department of Electronics and Communication Engineering School of Electrical Sciences Karunya University Coimbatore, India **Soumya Pandit** Institute of Radio Physics and Electronics University of Calcutta Kolkata, India

Nagendra P. Pathak Department of Electronics and Communication Engineering Indian Institute of Technology-Roorkee Roorkee, India

#### Balwinder Raj

VLSI Design Lab Department of ECE NIT Jalandhar Jalandhar, India

#### Arman Roohi

Department of Electrical Engineering and Computer Science College of Engineering and Computer Science University of Central Florida Orlando, Florida

#### Sarmista Sengupta

Institute of Radio Physics and Electronics University of Calcutta Kolkata, India

#### Pankaj Sethi

CEA, CNRS, Grenoble-INP, INAC-SPINTEC Université Grenoble Alpes Grenoble, France

**Eddy Simoen** Imec Leuven, Belgium

Avtar Singh

Department of Electronics and Communication Engineering Invertis University Bareilly, India

#### Jeetendra Singh

VLSI Design Lab Department of ECE NIT Jalandhar Jalandhar, India

#### M. B. Srinivas

School of Engineering and Technology BML Munjal University Gurgaon, India

#### Chetan Vudadha

Electrical and Electronics Engineering BITS-Pilani Hyderabad, India

#### Wen-Yan Yin

Zhejiang Province Lab of Advanced Micro/Nano Electronic Devices and Smart Systems State Key Lab of MOI College of Information and Electronic Engineering Innovative Institute of Electromagnetic Information and Electronic Integration Zhejiang University Hangzhou, China

#### **Ramtin Zand**

Department of Electrical Engineering and Computer Science College of Engineering and Computer Science University of Central Florida Orlando, Florida

## Section I

## **Nanoscale Transistors**

# 1

### Simulation of Nanoscale Transistors from Quantum and Multiphysics Perspective

#### Zhipeng Dong, Wenchao Chen, Wen-Yan Yin, and Jing Guo

#### CONTENTS

| 1.1                                                                        | Backg | round and Introduction                                           | 3  |

|----------------------------------------------------------------------------|-------|------------------------------------------------------------------|----|

| 1.2 Overview on Quantum and Multiphysics Simulation of Nanoscale Transisto |       |                                                                  | 4  |

|                                                                            | 1.2.1 | Quantum Simulation Approach for Nanotransistors                  | 4  |

|                                                                            | 1.2.2 | Approach of Multiphysics Simulation for Nanotransistors          | 6  |

| 1.3                                                                        | Asses | sment of Nanotransistors Near Scaling Limit                      | 10 |

|                                                                            |       | 2D Material-Based MOSFET Characteristics with ~10 nm Gate Length |    |

|                                                                            |       | TMDC FET Performance at Sub-5 nm Gate Length Scale               |    |

|                                                                            |       | Performance Limits of Device Applications                        |    |

| 1.4                                                                        |       | physics Simulation of Nanoscale Transistors                      |    |

|                                                                            |       | Igment                                                           |    |

|                                                                            |       | 0                                                                |    |

|                                                                            |       |                                                                  |    |

#### 1.1 Background and Introduction

The success of the semiconductor industry critically relies on collaborative efforts on fabrication, characterization, and design. It is estimated by the electronics industry that the use of computer-aided design saves the semiconductor development cost by 40%. Conventional technology computer-aided design (TCAD) simulation tools describe electrons in semiconductor devices as classical particles based on continuum theories. The physics base does not extend to nanoelectronic devices and sensors. As transistors scale down, multiphysics phenomena, quasi-ballistic transport, quantum effects, and even atomistic scale features of devices, interfaces, and surfaces become inevitably important for nanoscale devices and sensors.

This chapter describes our recent efforts in modeling nanoscale transistors, with an emphasis on modeling quantum transport and multiphysics phenomena. Section 1.2 discusses a simulation approach based on the non-equilibrium Green's function formalism and multiphysics approach. Section 1.3 gives examples of applying the simulation capability to assess transistors based on 2D semiconductor materials near the scaling limits, and Section 1.4 applies the multiphysics simulation capability to ultra-thin-body silicon on insulator (SOI) MOSFETs.

## **1.2** Overview on Quantum and Multiphysics Simulation of Nanoscale Transistors

#### 1.2.1 Quantum Simulation Approach for Nanotransistors

Electrons in semiconductor devices are traditionally modeled as semiclassical particles based on a continuum theory, such as the drift-diffusion theory. For nanoelectronic devices, quantum effects and atomistic scale features become inevitably important. Recent research has led to the evolution of a unified and powerful quantum transport simulation framework based on the non-equilibrium Green's function (NEGF) formalism [1–6]. The NEGF formalism provides a general approach for quantum simulations of nanoscale transistors as diverse as nanoscale silicon FETs, nanowire FETs, CNTFETs, graphene and graphene nanoribbon FETs, molecular FETs, and TMDC FETs.

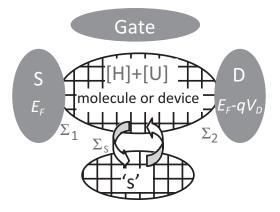

Figure 1.1 summarizes the procedure of applying the NEGF approach to a transistor. The transistor channel is connected to the source and drain contacts, and the gate modulates the conductance of the channel. One first identifies a suitable basis set and derives the Hamiltonian, [*H*], for the isolated channel, which can be a molecule, CNT, graphene, or silicon. Then, the contact self-energy matrices,  $[\Sigma_1]$  and  $[\Sigma_2]$  are computed, which describe how the channel couples to the source and drain contacts. Next, the scattering self-energy  $[\Sigma_s]$  is identified to describe the dissipative process. After that, the retarded Green's function is computed self-consistently with the potential matrix [*U*]. After self-consistency is achieved, the physical quantities of interest, such as the charge density and current, are computed from the Green's function. The NEGF formalism meets the needs of nanodevice modeling by providing (i) an atomistic description, (ii) treatment of open boundary and non-equilibrium transport, and (iii) treatment of inelastic scattering. The formalism, however, treats electron-electron interaction based on an independent-electron approximation. Many-body effects such as magnetism, single-electron charging, Kondo effect, and entanglement are left out [1–6].

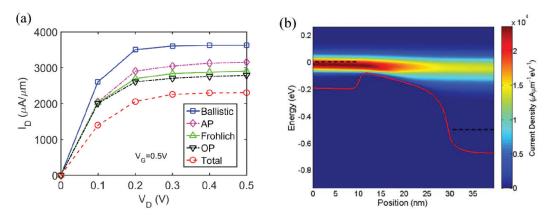

Figure 1.2 shows our preliminary results on modeling a  $MoS_2$  FET with a channel length of 20 nm by using the NEGF formalism. The device performance at the ballistic limit and in the presence of phonon scattering is presented. Phonon scattering plays an important role in establishing the intrinsic device performance limits and the impact of self-heating effects, which is carefully treated by using the self-consistent Born approximation with a

**FIGURE 1.1** The NEGF applied to a generic nanodevice.

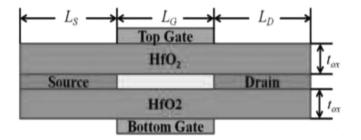

NEGF simulation of  $MoS_2$  horizontal homojunction FETs with  $L_G = 20$  nm. (a)  $I_D - V_D$  characteristics at the ballistic limit and in the presence of various phonon scattering mechanisms, including acoustic phonon (AP), optical phonon (OP), and Frohlich scattering. (b) The energy resolved current spectrum at on state with phonon scattering shows energy relaxation and back scattering. The red solid line is a potential profile, and the black dashed curve is the Fermi level at the source (drain).

first principle description of the phonon energy and electron-phonon coupling strength. The results in Figure 1.2 establish the ballistic performance limits as well as the practical intrinsic device performance limits with phonon scattering, and they provide a detailed and physical description of heat generation due to self-heating effects in the TMDC FET device.

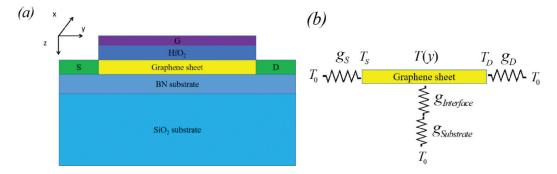

Self-heating effects, which highlight the importance of modeling coupled with electronthermal transport, can play an important role in nanoscale transistors. Take graphene transistor as an example: Figure 1.3 illustrates the corresponding thermal transport model of the simulated device. The top surface is assumed to be adiabatic. The interface thermal resistance between the graphene layer and the BN layer is equivalent to a 15-nm thick SiO<sub>2</sub> layer.  $g_S(g_D)$  is the source (drain) contact thermal conductance. Its value depends on the quality of the contact, and the quantum limit is about 1.5 Wm<sup>-1</sup>K<sup>-1</sup> [7]. In simulation, we use the quantum limit value for the perfect thermal conductance contacts and a 10 times

#### FIGURE 1.3

(a) Simulated device structure. HfO<sub>2</sub> is used for the top gate insulator with a thickness of 3 nm and dielectric constant of 25. Pd is used for the metal contacts, which have a Schottky barrier height of 0.2 eV for electrons. A BN layer deposited on the SiO<sub>2</sub> substrate is used as the improved substrate for the graphene sheet. The thickness of SiO<sub>2</sub> substrate is 300 nm. (b) The corresponding thermal boundary model of the device. The interface thermal resistance between the graphene sheet and BN layer is equivalent to a 15 nm-thick SiO<sub>2</sub>.

Nanoscale Devices

smaller value for the realistic contacts. The steady state heat transport equation for 2D graphene along the transport direction is given by

$$A\frac{\partial}{\partial y}\left(k\frac{\partial T}{\partial y}\right) = -\left(p\left(y\right) - g\left(T - T_{0}\right)\right)$$

(1.1)

where *A* is the cross section of graphene,  $k \approx 600 \text{ Wm}^{-1}\text{K}^{-1}$  is the thermal conductivity of supported graphene [8],  $p(y) = -\partial I_{\text{heat}}/\partial y$  is the Joule heating rate where  $I_{\text{heat}}$  is the heat flux,  $g = (g_{\text{Interface}}^{-1} + g_{\text{Substrate}}^{-1})^{-1}$  is the effective thermal conductance to the substrate where  $g_{\text{Interface}}$  is the thermal conductance between the graphene sheet and the BN layer, and  $g_{\text{Substrate}}$  is the thermal conductance of the SiO<sub>2</sub> substrate.  $T_0$  is ambient temperature, which is fixed at 300K. The thermal boundary conditions at contacts are given by

$$\begin{cases} \text{Source} : g_{S}(T_{0} - T_{S}) = -k \frac{\partial T}{\partial y} \Big|_{y=0} \\ \text{Drain} : g_{D}(T_{D} - T_{0}) = -k \frac{\partial T}{\partial y} \Big|_{y=L} \end{cases}$$

(1.2)

The thermal transport equation is solved self-consistently by coupling it to the NEGF formalism with phonon scattering. The simulation results under both equilibrium and hotphonon circumstances can be considered to study the self-heating effects in GFETs by this approach.

#### 1.2.2 Approach of Multiphysics Simulation for Nanotransistors

Short-channel effect (SCE) limits further miniaturization of field effect transistors. To minimize the SCE, transistors based on new structures and new materials as discussed in previous sessions have been experimentally and theoretically investigated more recently. As the transistors keep shrinking, the integration density increases with the reduction of device size. Hence, self-heating effect (SHE) becomes more severe for smaller transistors [9–12], especially for silicon-on-insulator (SOI) MOSFETs with insertion of buried oxide (BOX) layer, which has low thermal conductivity. High temperature deteriorates hot carrier injection (HCI) and causes worse reliability for sub-100 nm Si-MOSFETs [13–15]. In order to capture the effects of HCI in MOSFETs stressed by different signals, transient electrothermal simulation needs to be employed [16].

The primary heat carriers in silicon are the acoustic phonons, which have group velocities around 5000 m/s for transverse modes and around 9000 m/s for longitudinal modes [12]. Scattering time of acoustic phonons is in the scale of tenths of picoseconds [17]. Electrons with energy above 50 meV scatter mainly with optical phonons, which have low group velocities around 1000 m/s [12]. Optical phonons decay into acoustic phonons in the scale of picoseconds [17]. The electrons gain energy from an electric field, and they need to travel several mean-free paths to release it to the lattice [12,18]. With an electron velocity of 10<sup>7</sup> cm/s, which is the saturation velocity in silicon [12], the transit time for electrons in the sub-100 nm channel MOSFET is in the scale of picoseconds. On the other hand, the transistors typically operate at GHz frequencies. Each operating pulse lasts for several

hundreds of picoseconds, which is several orders higher than the heat generation process. Hence, the heat generation can be treated as an instantaneous process as the GHz pulse is applied to transistors.

The heat generation rate can be calculated by various methods, including drift diffusion, Monte Carlo, and NEGF, which treat carriers classically, semi-classically, and quantum mechanically, respectively. The heat generation rate in a quasi-ballistic transistor with a channel length of 20 nm is presented by using different methods as shown in [19]. The heat generation rate obtained by drift diffusion has larger magnitude and also large negative value, and the Monte Carlo simulation results indicate that heat dissipates far into the drain [19].

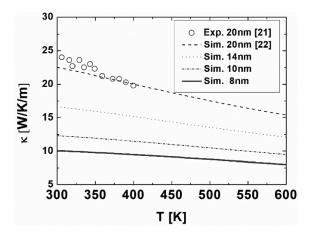

Thermal conductivity has temperature dependence. Specifically, the thermal conductivity of Si thin film depends not only on temperature but also its thickness [20–22]. As the thickness decreases, boundary scattering starts to play an important role in determining the overall thermal conductivity [20]. In particular, based on the modeling method given in [22], the temperature-dependent thermal conductivity of Si thin film with nanoscale thickness can be calculated as shown in Figure 1.4. For the thickness around 10 nm, its thermal conductivity shows linear dependence on temperature; it can be described by

$$\kappa_{\text{Si film}}(T) = \kappa_{\text{Si 0}} + \gamma(T - 300) \tag{1.3}$$

where  $\kappa_{Si 0}$  is the thermal conductivity of Si thin film with certain thickness at 300K, and  $\gamma$  is the linear coefficient. The values of  $\kappa_{Si 0}$  and  $\gamma$  for Si thin film with different thicknesses are listed in Table 1.1.

Usually, the field effect transistor is buried inside several hundred micrometers thick Si substrate and several micrometers thick insulator. The heat will spread out through its surroundings. Hence, once the heat generation rate in the transistor is determined, heat transport on the circuit level can be described by the following heat conduction equation,

$$C(T)\partial T(\vec{r},t)/\partial t = \kappa(T)\nabla^2 T(\vec{r},t) + Q(t)$$

(1.4)

#### FIGURE 1.4

Experimental and simulated thermal conductivities of Si thin films with different nanoscale thicknesses. The simulated results are obtained by the method provided in Liu et al. (From Liu, W. et al., *IEEE Trans. Electron Devices*, 53, 1868–1876, 2006.)

| Thickness of Si Film (nm) | к <sub>Si0</sub> (W/K/m) | γ (W/K²/m)             |

|---------------------------|--------------------------|------------------------|

| 12                        | 14.60                    | $-1.25 \times 10^{-2}$ |

| 11                        | 13.52                    | $-1.11 \times 10^{-2}$ |

| 10                        | 12.41                    | $-9.66 \times 10^{-3}$ |

| 9                         | 11.29                    | $-8.27 \times 10^{-3}$ |

| 8                         | 10.14                    | $-6.93 \times 10^{-3}$ |

| 7                         | 8.96                     | $-5.64	imes10^{-3}$    |

| 6                         | 7.76                     | $-4.42 \times 10^{-3}$ |

Thermal Conductivity of Silicon Thin Film with Nanoscale Thickness

where C(T) is the heat capacity,  $\kappa(T)$  is the thermal conductivity of materials involved, and Q(t) is the heat generation. Equation (1.4) can be simplified into a static thermal conduction equation by setting the left-hand side to be zero,

$$\kappa(T)\nabla^2 T(\vec{r}) + Q = 0 \tag{1.5}$$

Following the standard procedure of time domain finite element method [23], the matrix form of Equation (1.4) can be obtained by doing backward difference with respect to time, i.e.,

$$([M] + \Delta t[K]) \{T\}^{t+\Delta t} = \Delta t[S] \{Q\}^{t+\Delta t} + [M] \{T\}^{t} + \{B\}$$

(1.6)

where [*M*] is the time-dependent matrix, [*K*] is the thermal conduction matrix, [*S*] is the overlap matrix, {*B*} is the boundary condition matrix, {*Q*} is the heat generation vector, and  $\Delta t$  is the time step for time evolution. For steady case, the matrix form of Equation (1.5) can be written as

$$[K]{T} = [S]{Q} + {B}$$

(1.7)

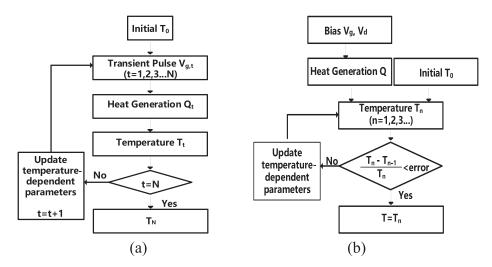

The processes for solving time-dependent and static thermal conduction equations with temperature-dependent parameters are shown in Figure 1.5.

Different from conventional long-channel MOSFETs, the worst case of HCI effect happens at  $V_g = V_d = V_{DD}$  for sub-100 nm Si-MOSFET [13]; it also gets worse as temperature increases [13–15]. Based on the empirical model of threshold voltage shift as a function of time [24], a temperature-dependent exponential coefficient  $\alpha$  can be introduced,

$$\Delta V_{\rm th} = \Delta V_{\rm th0} (t/t_0)^{\alpha} \tag{1.8}$$

According to the measured threshold voltage shift given in [25], a linear model to characterize the temperature-dependent  $\alpha$  can be given as

$$\alpha = \alpha_0 + \beta (T - T_0) \tag{1.9}$$

where nominal values  $\alpha_0 = 0.1$ ,  $T_0 = 300$ K and  $\beta = 5 \times 10^{-4}$  /K are used in our simulation.

To numerically calculate the threshold voltage shift, we need to do a derivative of Equation (1.8) with respect to time,

**TABLE 1.1**

Flowchart for solving (a) time-dependent thermal conduction equation and (b) static thermal conduction equation with temperature-dependent parameters.

$$\frac{d\Delta V_{\rm th}}{dt} = \frac{\alpha}{t_0} \Delta V_{\rm th0} (t / t_0)^{\alpha - 1}$$

(1.10)

At time step *n*, the threshold voltage shift is

$$\Delta V_{\rm th}(n) = \sum_{m=1}^{n} \frac{\alpha}{t_0} \Delta V_{\rm th0}(t/t_0)^{\alpha_m - 1} dt$$

$$= \Delta V_{\rm th}(n-1) + \frac{\alpha}{t_0} \Delta V_{\rm th0}(t/t_0)^{\alpha_n - 1} dt$$

(1.11)

It should be noted that  $\Delta V_{\text{th}}$  does not change as a function of time when the gate bias  $V_g$  is zero at time step *n*. Therefore, Equation (1.11) can be rewritten as

$$\Delta V_{\rm th}(n) = \begin{cases} = \Delta V_{\rm th}(n-1) + \frac{\alpha}{t_0} \Delta V_{\rm th0} \left(\frac{t}{t_0}\right)^{\alpha_n - 1} dt; & \text{if } V_{g,n} \neq 0 \\ = \Delta V_{\rm th}(n-1) + 0; & \text{if } V_{g,n} = 0 \end{cases}$$

(1.12)

where  $V_{g,n}$  is the gate bias  $V_g$  at time step *n*.

It should be noted that the previous equations are derived under the condition that  $V_d$  is fixed at  $V_{DD}$ , and  $V_g$  is biased by step pulse or a sequence of AC pulses, which is a typical way in which hot-carrier injection is measured.

#### 1.3 Assessment of Nanotransistors Near Scaling Limit

#### 1.3.1 2D Material-Based MOSFET Characteristics with ~10 nm Gate Length

New emerging 2D semiconductor materials such as  $MoS_2$ , which belongs to the transition metal dichalcogenides (TMDCs) material family, have been extensively studied in research [26–28]. The ballistic performance limit of monolayer  $MoS_2$  FET has been studied in literature [29,30]. Here, we investigate the effects of phonon scattering on the device performance as well as the scaling limit of  $MoS_2$  transistors [31].

A double-gated MOSFET is studied here, as shown in Figure 1.6. Monolayer  $MoS_2$  is used as the channel material with the source and drain heavily doped. By solving the Schrodinger equation coupled with Poisson equation, the  $I_D - V_D$  characteristics of a monolayer  $MoS_2$  FET are shown in Figure 1.7 with  $L_G = 5$  nm. The electron-phonon interaction is treated by the self-consistent Born approximation within the NEGF formalism [32]. With scattering effect, the on-state current is degraded with  $L_G = 5$  nm compared with the on-current in ballistic limit. This highlights the significance of phonon scattering on accurate estimation of performance limits of monolayer  $MoS_2$  FETs even with a channel length

#### FIGURE 1.6

Cross section of studied  $MoS_2 MOSFET$  with  $L_G$  gate length. The source and drain are heavily doped.

#### FIGURE 1.7

NEGF simulation of MoS<sub>2</sub> horizontal homojunction FETs with  $L_G = 5$  nm. (a)  $I_D - V_D$  characteristics at the ballistic limit and in the presence of various phonon scattering mechanisms, including acoustic phonon (AP), optical phonon (OP), and Frohlich scattering. (b) The energy resolved current spectrum at on state with phonon scattering shows energy relaxation and back scattering. The solid line is a potential profile, and the black dashed curve is the Fermi level at the source (drain). down to 5 nm. Because of the large direct source-drain tunneling, the FET with  $L_G = 5$  nm does not have good  $I_D - V_D$  saturation behavior as shown in Figure 1.7a. Figure 1.7b shows the on-state position-resolved current spectrums of monolayer MoS<sub>2</sub> FETs with  $L_G = 5$  nm. It shows that when electrons travel across the top of a potential barrier, the energy of electrons is relaxed due to phonon scattering. Hence, the current spectrum is broadened, and the energy of peak current density is lowered after phonon scatterings. For a gate length with 5 nm, energy relaxation is not significant since electron transport is quasi-ballistic, compared with Figure 1.2b. In addition, direct source-to-drain tunneling is more significant since the energy barrier of a device with  $L_G = 5$  nm is thinner.

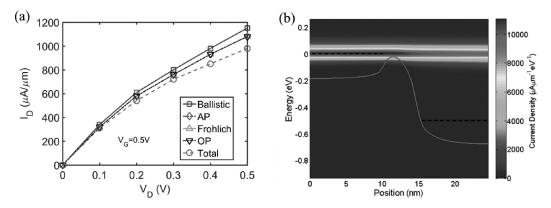

We also compare the channel-length scaling behavior of drain-induced barrier lowering (DIBL) and subthreshold swing (SS) between monolayer MoS<sub>2</sub> FETs and ultra-thin-body Si FETs in Figure 1.8. The body thickness of Si film is 3 nm, and all the other device parameters are the same as that of MoS<sub>2</sub> FET. It shows that DIBL and SS are independent of phonon scattering since phonon scattering has little impact to the subthreshold region. Both DIBL and SS increase quickly when the channel length decreases due to large source-drain tunneling. For both monolayer MoS<sub>2</sub> FETs and ultra-thin-body Si FETs, the DIBL disappears and SS approaches the 60 mV/decade limit when the gate length is beyond 15 nm. In short-channel FETs, severe source-to-drain tunneling results in large degradation of DIBL and SS as shown in Figure 1.8b. When the channel length scales down to sub-10 nm, monolayer  $MoS_2$ FETs show smaller DIBL and better SS compared to 3-nm-thick-body Si FETs. The reason is that  $MoS_2$  has an atomic thin body that would provide better gate control and has higher effective mass, which reduces direct source-to-drain tunneling. If DIBL of ~100 mV/V is a practically acceptable value [33], Figure 1.8a suggests a minimum gate length of ~8 nm for monolayer MoS<sub>2</sub> FETs and 10 nm for ultra-thin-body Si FETs, respectively. Their corresponding SS of ~75 and 77 mV/decade, respectively, are also acceptable for practical applications [33]. In conclusion, the gate length of monolayer MoS<sub>2</sub> FETs can be scaled down to 8 nm, while the gate length scaling limit of 3-nm-thick-body Si FETs is 10 nm.

#### 1.3.2 TMDC FET Performance at Sub-5 nm Gate Length Scale

Further scaling gate length to sub 5 nm is necessary since the ITRS requires a gate length of 5.9 nm in the year of 2026 [34]. Recently, S. B. Desai et al. have demonstrated a MoS<sub>2</sub> transistor

#### FIGURE 1.8

(a) DIBL and SS of monolayer  $MoS_2$  FETs and ultra-thin-body Si FETs versus gate length. (b) Percentage of direct source-drain tunneling in off-state current in ballistic case. Different gate work functions are used to achieve the specific off-current (0.1  $\mu$ A/ $\mu$ m).

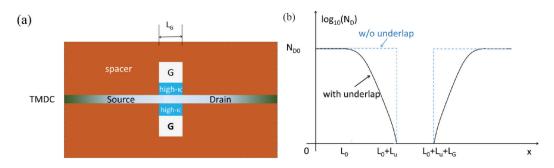

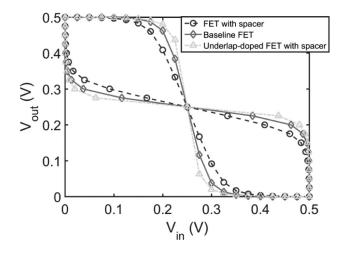

Schematic cross section of the modeled, double-gated MoS<sub>2</sub> FET. (a) The high- $\kappa$  gate insulator, metal gate (*G*), and gate spacer are denoted. The dashed line shows the modeled region. (b) Sketch of the doping density as a function of the position with (solid line) and without (dashed line) the gate underlap doping. The modeled source extension length ( $L_0$ ), gate underlap length ( $L_u$ ), and metal gate length ( $L_G$ ) are denoted. The doping density in the source extension is  $N_{D0}$ , and a Gaussian doping profile is used in the gate underlap region. The gate insulator dielectric constant is  $\kappa_{ins} = 20$ . Three FETs are simulated: (i) a baseline FET, which is without spacer (i.e.,  $\kappa = 20$  in the spacer region) and without underlap doping; (ii) a FET with spacer, which is with underlap doping and spacer (i.e.,  $\kappa_{sp} = 4$  in the spacer region).

with a 1 nm gate length [35], which shows the importance of a gate-fringing field to achieve ultimate channel-length scaling. By solving the non-equilibrium Green's function (NEGF) transport equation self-consistently with a Poisson equation, device scaling, design, and performance potentials of 2D TDMC FETs in the sub-5 nm gate length scale are studied [36].

Figure 1.9a is the schematic of the modeled double-gated monolayer TMDC FET with a gate length of  $L_G$ , high- $\kappa$  insulator thickness of  $t_{ins} = 3$  nm, and dielectric constant of  $\kappa_{ins} = 20$ . The monolayer MoS<sub>2</sub> material is used as a representative case with the effective mass as  $m_x \approx m_y \approx 0.57 m_0$ . Three types of devices are proposed and simulated to study the effects of the gate spacer dielectric constant and the underlap doping: (i) a baseline FET, which is without a gate spacer (i.e.,  $\kappa = 20$  in the spacer region) and without the underlap doping, (ii) a FET with spacer, which is with a gate spacer of  $\kappa_{sp} = 4$  and without underlap doping, and (iii) an underlap-doped FET with spacer, which is with a gate spacer of  $\kappa_{sp} = 4$ and underlap doping. For the modeled devices without underlap doping, the doping density changes abruptly from  $N_{D0} = 10^{13}/\text{cm}^2$  in the source and drain regions to 0 in the intrinsic gated region, as noted in the dashed line in Figure 1.9b. For the modeled devices with underlap doping, there exists a gate underlap region with a length of  $L_u$  and a Gaussian profile of the doping density, as shown in the solid line in Figure 1.9b.

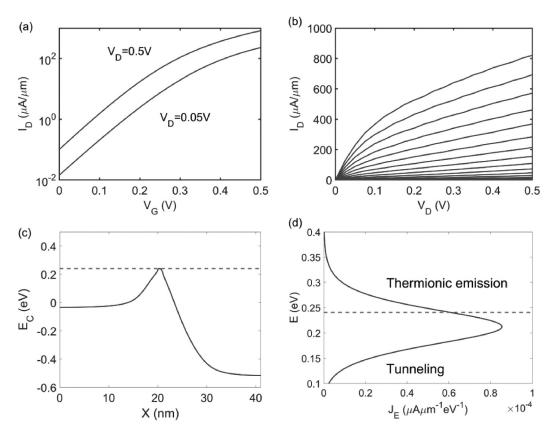

Figure 1.10a and b show the simulated I-V characteristics at  $V_D = 0.05$ V and  $V_D = V_{DD} = 0.5$ V for a baseline FET with  $L_G = 1$  nm. The gate work function is tuned to produce an off-current of  $I_{OFF} = 0.1 \,\mu$ A/ $\mu$ m. A large transconductance of 5106  $\mu$ S/ $\mu$ m, on-current of  $I_{ON} = 820 \,\mu$ A/ $\mu$ m, and an on-/off-current ratio of about 8200 are achieved even with a 1 nm gate length and lower power supply voltage 0.5V. The calculated SS and the DIBL are 84.6 mV/dec and 107 mV/V, respectively, which indicate relatively good sub-threshold characteristics at a short gate length of  $L_G = 1$  nm. The percentage of tunneling current in the off-current is also studied. Figure 1.10c shows the conduction band profile for the baseline FET at off state ( $V_G = 0$ V,  $V_D = 0.5$ V), and the energy-resolved current density is plotted in Figure 1.10d. The dashed line denotes the top of the barrier. The current density is from direct source-to-drain tunneling when the electron energy is below the top of the barrier. Although the relatively large effective mass of MoS<sub>2</sub> suppresses the

(a)  $I_D - V_G$  and (b)  $I_D - V_D$  characteristics of the baseline FET. The gate voltage ranges from 0 V to 0.5 V at 0.025 V per step. The modeled baseline FET is shown in Figure 1.9, with a gate length  $L_G = 1$  nm. (c) The corresponding conduction band profile and (d) energy-resolved current density of the baseline FET is at the off state. The dashed line denotes the top of the barrier.

direct source-to-drain tunneling, source-to-drain tunneling is still dominant at off state for the baseline FET with  $L_G = 1$  nm.

With the short gate length and the high- $\kappa$  dielectrics in the gate spacer region in the baseline FET, a large gate-fringing capacitance is expected, which will lower the switching speed and frequency performance. Hence, we examine the effect of the spacer region by using dielectrics with  $\kappa_{sp} = 4$ . The simulated I-V characteristics for the FET with spacer are shown in Figure 1.11a and b. The figure shows that the design of the gate spacer has a considerable impact on the DC I-V characteristics of the device with  $L_G = 1$  nm. At the same specified off-current and power supply voltage, the on-current reduces to 269  $\mu$ A/ $\mu$ m, and the SS and DIBL increase to 101 mV/dec and 267 mV/V, respectively. Meanwhile, the output conductance increases, and the output I-V characteristics show lack of saturation. This indicates that the high- $\kappa$  dielectrics in the gate spacer region can be used to improve the immunity to electrostatic SCEs at a short gate length by increasing the effective channel length through the gate-fringing field in the spacer region.

Next, we investigate the gate underlap doping effect on the device performance. Figure 1.11c and d show the I-V characteristics for the underlap-doped FET with spacer with  $L_G = 1$  nm. A low SS of 81 mV/dec and a DIBL of 94 mV/V can be achieved, which are lower than both baseline FET and a FET with spacer. With the underlap doping,

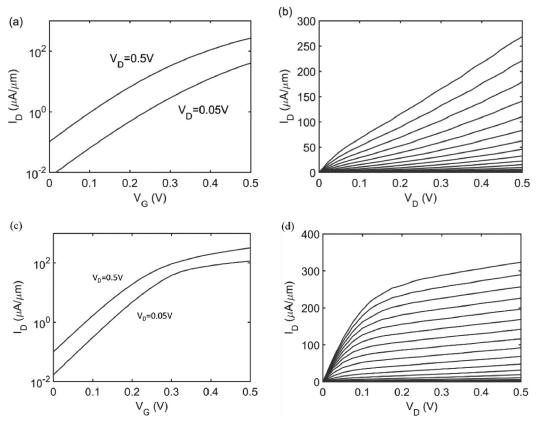

(a)  $I_D - V_G$  characteristics and (b)  $I_D - V_D$  characteristics of the FET with spacer and (c)  $I_D - V_G$  characteristics and (d)  $I_D - V_D$  characteristics of the underlap-doped FET with spacer at a gate length  $L_G = 1$  nm. The gate voltage ranges from 0 V to 0.5 V at 0.025 V per step. The underlap doping length is  $L_u = 10$  nm and the steepness is 1 nm/dec. The gate work function is tuned to achieve the specified off-current of  $I_{OFF} = 0.1 \,\mu\text{A}/\mu\text{m}$ .

the on-current value increases from 269  $\mu$ A/ $\mu$ m for a FET with spacer to 323  $\mu$ A/ $\mu$ m due to improved SS. And the output I-V characteristics saturate better with the output conductance value drops to 162  $\mu$ S/ $\mu$ m. The underlap doping design can significantly improve the immunity to electrostatic SCEs.

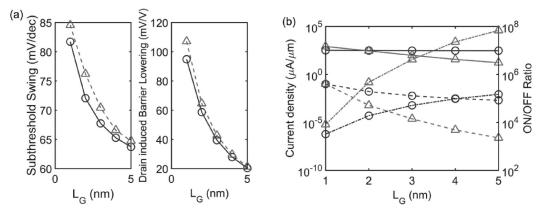

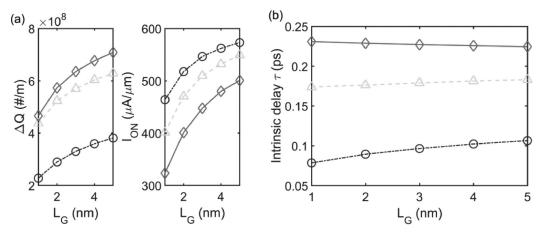

Figure 1.12 presents the scaling behaviors with regard to the gate length  $L_G$  for both the baseline FET and the underlap-doped FET with spacer. When  $L_G$  scales from 5 nm down to 1 nm, the SS increases to a reasonable range for the underlap-doped FET with spacer and the baseline FET, respectively, as shown in Figure 1.12a. The scaling behaviors of the on-current, off-current, and on-/off-current ratios are shown Figure 1.12b. The figure shows that the on-current and off-current of underlap-doped FET with spacer are less sensitive to the gate length variation compared to the baseline FET, indicating that the FET designs with underlap doping are beneficial for reducing the device variability due to  $L_G$  variation.

#### **1.3.3 Performance Limits of Device Applications**

In addition, we access the performance limit of the 2D FET at sub-5 nm gate length for both high-frequency application and digital electronics application [36].

Scaling behaviors with regard to the gate length: (a) The SS and DIBL and (b) the on-current (solid), off-current (dashed), and on-/off-current ratio (dash-dot) as a function of the gate length  $L_G$  down to 1 nm. The lines with circles are for the underlap-doped FET with spacer, and the lines with triangles are for the baseline FET. For the underlap-doped FET with spacer, the underlap doping length is  $L_u = 10$  nm and the steepness is 1 nm/dec.

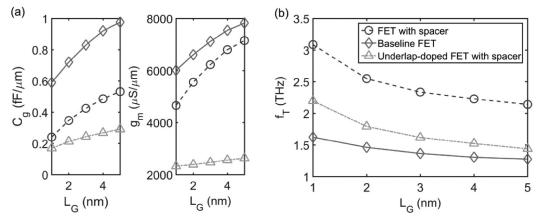

A quasi-static treatment is used to study the high-frequency performance of the  $MoS_2$  FETs. An equivalent circuit model is numerically extracted. The gate capacitance  $C_g$  and the transconductance  $g_m$  can be expressed as

$$c_g = \frac{\partial Q_g}{\partial V_g}\Big|_{V_d} \tag{1.13}$$

$$g_m = \frac{\partial I_D}{\partial V_g}\Big|_{V_d} \tag{1.14}$$

The intrinsic cut-off frequency  $f_T$  is computed as

$$f_T = \frac{1}{2\pi} \frac{g_m}{C_g}$$

(1.15)

The gate capacitance, transconductance, and cut-off frequency values are extracted with a DC bias of  $V_{DD} = 0.5V$  and a common specified DC current of  $I_{DC} = 1000 \,\mu\text{A}/\mu\text{m}$  for the three FET structures. The gate capacitance and transconductance as a function of the gate length  $L_G$  for the three devices are shown in Figure 1.13a. Due to the high- $\kappa$  dielectrics in the gate-fringing region, which leads to large gate-fringing capacitance, the baseline FET has the largest gate capacitance. At  $L_G = 1$  nm, the gate capacitance can be reduced by over a factor of 2 by introducing a gate spacer with a low dielectric constant. This also shows that the underlapped doping design can further lower the gate capacitance. Since the length scale of the gate length and insulator thickness are comparable, the gate capacitance that is used for MOSFET with a long gate length. Due to the degraded gate control of the channel, the transconductance also decreases as the gate length scales down.

#### FIGURE 1.13

(a) Gate capacitance  $C_g$  and transconductance  $g_m$  and (b) cut-off frequency  $f_T$  as a function of the gate length  $L_G$  for the modeled MoS<sub>2</sub> FETs. The solid lines with diamonds are for the baseline FET. The dashed lines with circles are for the FET with spacer, and the dash-dot lines with triangles are for the underlap-doped FET with spacer.

Figure 1.13b shows that cut-off frequency increases as the gate length decreases at the common specified DC current. Both devices with a gate spacer have a larger cut-off frequency than the baseline FET without a gate spacer due to smaller gate-fringing capacitance. A lower dielectric constant value in the gate spacer region is favorable to improve the RF performance. At  $L_G = 1$  nm, the FET with spacer has the largest cut-off frequency due to large transconductance and lower gate capacitance, while the baseline FET has the lowest cut-off frequency because of large gate-fringing capacitance. A good current saturation and small output conductance in the  $I_D - V_D$  characteristics are preferred to achieve a good power gain frequency ( $f_{max}$ ) performance. Among three modeled devices, the underlap-doped FET with spacer has the best saturation in the output I-V characteristics as well as relative large cut-off frequency, which are mostly preferred for improving the power gain frequency  $f_{max}$ . The results indicate that designs of the gate spacer and underlap doping are important for improving the RF high-frequency performance. TMDC FETs with a 1 nm gate length can have attractive RF performance with the cut-off frequency above 2 THz by proper design of the gate spacer and underlap doping.

The performance potential of studied devices in digital electronics is analyzed next. Figure 1.14 shows the intrinsic delay of the modeled underlap-doped FET with spacer as a function of the gate length. The intrinsic gate delay is computed as  $\tau = \Delta Q / I_{ON}$ , where  $\Delta Q = (Q_{G,ON} - Q_{G,OFF})$  and  $Q_{G,ON}$  and  $Q_{G,OFF}$  are the gate charge computed at the on and off states, respectively, and  $I_{\rm ON}$  is the on-current computed at a common specified off-current of  $I_{OFF} = 0.1 \,\mu A / \mu m$ . A slight increase of intrinsic delay is observed for the underlapdoped FET with spacer as the gate length scales down from 5 nm to 1 nm. The reason is that the decrease of the on-current outpaces the decrease of the gate charge change as  $L_{\rm G}$ decreases. A similar trend is also observed for both the baseline FET and the FET with spacer, all of which have a gate insulator thickness of 3 nm. However, by scaling down the gate oxide thickness, we can reverse the trend. Figure 1.14b compares the underlapdoped FET with different gate insulator thickness values. A gate insulator with dielectric constant of 4 is used for the device with a gate insulator thickness of  $t_{ins} = 1$  nm. It shows that for the FETs with  $t_{ins} = 2 \text{ nm}$  and 1 nm, the intrinsic delay decreases as the gate length decreases. Meanwhile, a large decrease of the intrinsic gate delay is shown when the gate insulator thickness decreases from 3 nm to 1 nm. A thinner gate oxide improves the

### FIGURE 1.14

(a) Gate charge variation from the off to on state  $\Delta Q$  and the on-current and (b) intrinsic delay as a function of  $L_c$ . Three FETs modeled all have the structure of the underlap-doped FET with spacer but with different gate insulator thickness and dielectric constant. The solid lines with diamonds have a gate insulator of  $t_{ins} = 3$  nm and  $\kappa = 20$ . The dashed lines with triangles have a gate insulator of  $t_{ins} = 2$  nm and  $\kappa = 20$ . The dashed lines with triangles have a gate insulator of  $t_{ins} = 2$  nm and  $\kappa = 20$ . The dashed lines with triangles have a gate insulator of  $t_{ins} = 2$  nm and  $\kappa = 20$ . The dashed lines with triangles have a gate insulator of  $t_{ins} = 2$  nm and  $\kappa = 20$ . The dashed lines with triangles have a gate insulator of  $t_{ins} = 2$  nm and  $\kappa = 20$ . The dashed lines with diamonds have a gate insulator of  $t_{ins} = 1$  nm and  $\kappa = 4$ . A common off-current of  $I_{OFF} = 0.1 \ \mu\text{A}/\mu\text{m}$  is achieved by adjusting the gate work function.

#### FIGURE 1.15

Simulation of inverter characteristics. The butterfly curves of the inverters based on the three modeled  $MoS_2$  with  $L_G = 1$  nm. The solid lines with diamonds are for the baseline FET, the dashed lines with circles are for FET with spacer, and the dash-dot lines with triangles are for the underlap-doped FET with spacer. Balanced *p*-type and *n*-type transistors are assumed, because the effective mass values for electrons and holes are close in monolayer  $MoS_2$ .

intrinsic gate delay because of a decreased ratio of the fringing capacitance to the total gate capacitance.

Finally, we simulate an inverter circuit based on the modeled monolayer  $MoS_2$  FETs. Figure 1.15a shows the butterfly curves of the inverter for the three modeled devices with  $L_G = 1$  nm. Balanced *p*-type and *n*-type transistors are assumed because the effective mass values for electrons and holes are close for monolayer  $MoS_2$ . The result shows that good inverter characteristics can be achieved for all three devices at a gate length of  $L_G = 1$  nm. The underlap-doped FET with spacer shows the most preferred butterfly curve in terms of the largest voltage gain and static noise margin (SNM), whereas the FET with spacer shows the smallest noise margin due to lack of saturation in the output I-V characteristics as shown in Figure 1.11b. Our work demonstrates the good performance potential for 2D TMDC FET with carefully designed gate spacer and underlap doping in both RF and digital electronics applications.

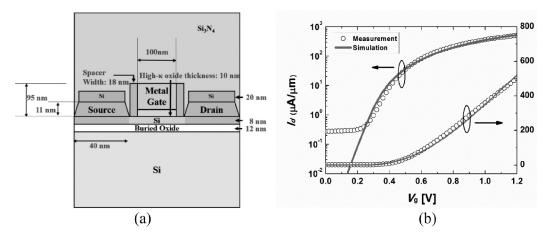

## 1.4 Multiphysics Simulation of Nanoscale Transistors

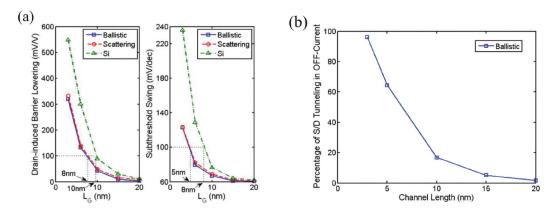

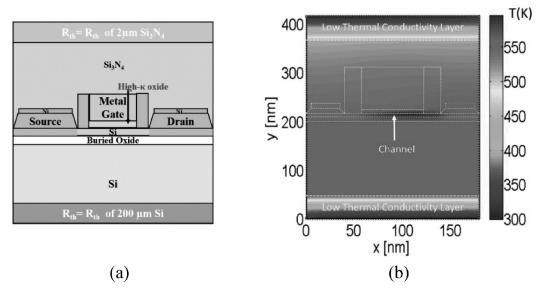

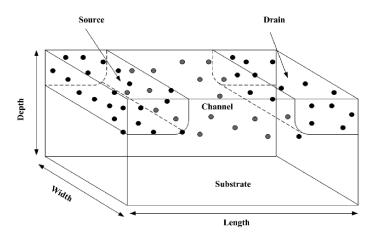

A fully depleted silicon-on-insulator (SOI) MOSFET is taken as an example to study electrothermal effects on its hot-carrier reliability [16]. The channel length is 100 nm, and the thickness of the Si thin-film channel is 8 nm, as shown in Figure 1.16a. In order to get the heat generation rate in the channel region, various methods can be applied as mentioned previously. Here, a drift-diffusion method is applied since the channel length is in the scale of 100 nm, which is relatively long, and it can be a reasonable treatment. The simulated *J-V* curves agree well with experiments as shown in Figure 1.16b.

Typically, the SOI MOSFETs are fabricated with several hundred micrometers thick Si substrate and several micrometers thick Si<sub>3</sub>N<sub>4</sub> insulator. To mimic the heat conduction process in a real chip and meanwhile save computational cost, two thin layers with d = 50 nm thickness are added on top and at bottom as shown in Figure 1.17a. The top thin layer has its thermal resistance  $R_{\text{th}}$  as that of  $l_{\text{Si}_3\text{N}_4} = 2 \,\mu\text{m} \,\text{Si}_3\text{N}_4$ , and the bottom one has  $R_{\text{th}}$  as that of  $l_{\text{Si}_3\text{N}_4} = 200 \,\mu\text{m} \,\text{Si}$ . With the top layer as an example, its effective thermal conductivity can be written as

$$\kappa_{\rm eff, top} = d/R_{\rm th} = d/(l_{\rm Si_3N_4}/\kappa_{\rm Si_3N_4}) = \kappa_{\rm Si_3N_4} d/l_{\rm Si_3N_4}$$

(1.16)

#### FIGURE 1.16

(a) Schematic of a fully depleted SOI MOSFET with its dimensions as noted. The channel length is 100 nm. (b) Comparison between the simulated and measured  $I_d - V_g$  curve in linear plot and logarithmic scale.

#### FIGURE 1.17

(a) The schematics for modeling of heat conduction. The top and bottom thin layers are with the same thermal resistance as 2  $\mu$ m Si<sub>3</sub>N<sub>4</sub> and 200  $\mu$ m Si substrate to mimic the real environment around the active region of the transistor. (b) Temperature profile at steady state  $V_g = 1.2$ V and  $V_d = 1.2$ V. The top and bottom layers are with low thermal conductivity to mimic the thick insulator and substrate.

Similarly, the effective thermal conductivity of the bottom layer can be obtained.

By using the finite element method and following the simulation procedures illustrated in Figure 1.5, the steady temperature profile is obtained and plotted in Figure 1.17b. The white dotted line shows the skeleton of the modeling structure as in Figure 1.17a. The top and bottom low thermal conductivity layers are used to mimic the effects of 2  $\mu$ m Si<sub>3</sub>N<sub>4</sub> and 200  $\mu$ m Si substrate. It is observed that the highest temperature is localized around the drain region and is about 600K.

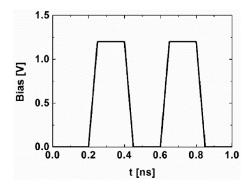

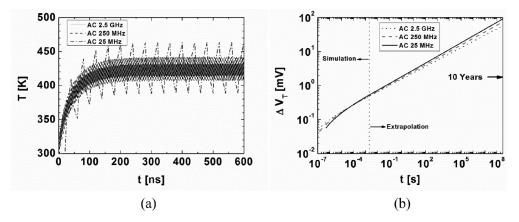

In state-of-the-art digital ICs, transistors are typically operated at GHz frequencies. In traditional experiments and simulations, AC signals with MHz frequencies are usually used to characterize the HCI. To further capture the electrothermal effects on HCI behavior under transient signal stress, time-dependent thermal conduction needs to be further studied. The AC signal with frequency 2.5 GHz is shown in Figure 1.18. Both rising and falling times are 50 ps, and the period is 400 ps, with 1-bit endurance as 200 ps.

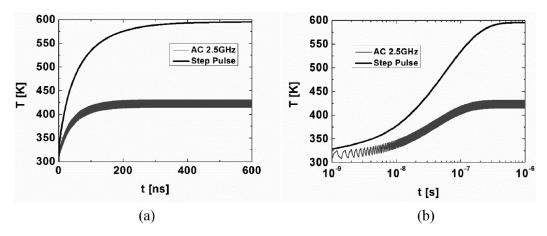

The temperature responses to the step pulse and AC signal with 1.2V magnitude are shown in linear and logarithmic timescale as plotted in Figure 1.19. The temperature is the highest temperature captured in the channel at each time step. The thermal response time is around 300ns, as shown in the temperature response to step pulse. The temperature for the step pulse is much higher than that of the AC pulse because the input power of the step pulse is higher.

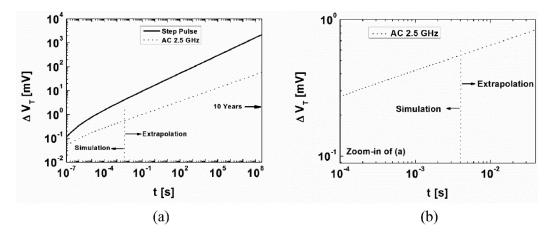

Based on the temperature response in Figure 1.19 and Equation (1.12), the TVS evolution up to 10 years for the SOI MOSFET under different signal stresses can be obtained as shown in Figure 1.20. TVS for AC with time larger than 4 ms is extrapolation based on simulation for saving computational cost. The slope of extrapolation is obtained by linearly fitting the simulation results from 0.4 ms to 4 ms. The step pulse has the largest TVS due to these reasons: (i) the temperature response to step pulse has the largest magnitude

#### FIGURE 1.18

AC signal with both pulse rising and falling times as 50 ps. The period for the pulse is 400 ps and corresponds to frequency 2.5 GHz.

### FIGURE 1.19

Temperature response in linear timescale (a) and logarithmic scale (b) to different signal stresses.

### FIGURE 1.20

(a) Simulated threshold voltage shift  $\Delta V_T$  as a function of time for different signal biases. Data for AC with time larger than 4 ms is extrapolation based on simulation for saving computational cost. (b) Zoom-in of (a). The slope of extrapolation is obtained by linearly fitting the simulation results from 0.4 ms to 4 ms.

and it leads to large temperature-dependent exponential  $\alpha$ , and (ii) the SOI MOSFET is always in on state when it is stressed by the step pulse, while the device is half on and half off when it is stressed by the AC signals.

The temperature responses to AC signals with different frequencies are presented in Figure 1.21a. As the frequency decreases, the temperature oscillation magnitude increases. Since both on and off states last long for the low frequency signal, the transistor has a long, continuous time to absorb and dissipate the heat. As a result, long endurance of the on or off state leads to more time for the temperature to increase or fall.

Similarly, based on the temperature response to AC signals, the TVS evolution up to 10 years for the SOI MOSFET under AC signal stresses with different frequencies is shown in Figure 1.21b. As the frequency decreases, the slope of TVS evolution increases due to a large temperature magnitude during the on state when the device is stressed by a low frequency signal.

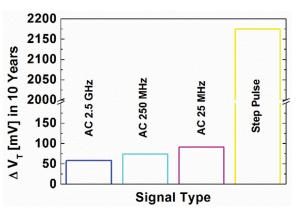

The values of TVS in 10 years for the SOI MOSFET under stress of various types of signals are summarized in Figure 1.22. It should be noted that there is a breakpoint in the y axis

#### FIGURE 1.21

(a) Temperature response to the AC signals with different frequencies. The lower frequency results in large temperature oscillation. (b) Simulated threshold voltage shift  $\Delta V_T$  as a function of time for the AC signals with different frequencies.

**FIGURE 1.22** Prediction of the threshold voltage shift  $\Delta V_T$  for the SOI MOSFET under 10-year stress of various signals.

in order to show the data more clearly. Although the TVS evolves differently for devices with different temperature exponentials as in Equation (1.9), the following trends should remain the same when the HCI is measured by applying AC or step pulse as gate bias with fixed  $V_D = V_{DD}$ . Firstly, for the sub-100 nm *n*-type SOI MOSFETs, the TVS under step pulse bias is worse than AC bias. Secondly, as the frequency of a measurement AC signal decreases from GHz to tens of MHz, the TVS increases.

## Acknowledgment

Z. D. and J. G. were supported in part by the National Science Foundation under Awards #1618762, #1610387, and #1809770. W. C. and W. Y. Y. were supported in part by the National Natural Science Foundation of China under grants 61431014, 61504121. The authors would also like to thank the supports from the ECE Department of University of Florida, the College of ISEE of Zhejiang University, and the ZJU-UIUC Institute of Zhejiang University. And this work was led by Principal Investigators: Jing Guo, Wen-Yan Yin, and Wenchao Chen.

## References

- 1. L. V. Keldysh, "Diagram technique for non-equilibrium processes," *Sov. Phys. JETP*, vol. 20, p. 1018, 1965.

- 2. S. Datta, Quantum Transport: Atom to Transistor, Cambridge, UK: Cambridge University Press, 2005.

- 3. S. Datta, *Electronic Transport in Mesoscopic Systems*, Cambridge, UK: Cambridge University Press, 1995.

- D. K. Ferry and S. M. Goodnick, *Transport in Nanostructures*, Cambridge, UK: Cambridge University Press, 1997.

- 5. A. Nitzan and M. A. Ratner, "Electron transport in molecular wire junctions," *Science*, vol. 300, pp. 1384–1389, 2003.

- 6. G. D. Mahan, Many-Particle Physics, 3rd ed., New York: Kluwer Academic/Plenum Publishers, 2000.

- 7. Y. Lu and J. Guo, "Thermal transport in grain boundary of graphene by non-equilibrium Green's function approach," *Appl. Phys. Lett.*, vol. 101, pp. 043112-1–043112-5, 2012.

- 8. J. H. Seol, I. Jo, A. L. Moore, L. Lindsay, Z. H. Aitken, M. T. Pettes, X. Li et al., "Two-dimensional phonon transport in supported graphene," *Science*, vol. 328, pp. 213–216, 2010.

- 9. C. Fiegna, Y. Yang, E. Sangiorgi, and A. G. O'Neill, "Analysis of self-heating effects in ultrathin-body SOI MOSFETs by device simulation," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 233–244, 2008.

- D. Vasileska, K. Raleva, and S. M. Goodnick, "Self-heating effects in nanoscale FD SOI devices: the role of the substrate, boundary conditions at various interfaces, and the dielectric material type for the BOX," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 3064–3071, 2009.

- 11. E. Pop, C. O. Chui, S. Sinha, R. Dutton, and K. Goodson, "Electro-thermal comparison and performance optimization of thin-body SOI and GOI MOSFETs," *IEEE IEDM Tech. Dig.*, 2004.

- 12. E. Pop, S. Sinha, and K. E. Goodson, "Heat generation and transport in nanometer-scale transistors," *Proc. IEEE*, vol. 94, no. 8, pp. 1587–1601, 2006.

- 13. E. X. Zhao, J. Chan, J. Zhang, A. Marathe, and K. Taylor, "Bias and temperature dependent hot-carrier characteristics of sub-100nm partially depleted SOI MOSFETs," *IRW Final Report*, 2002.

- P. Aminzadeh, M. Alavi, and D. Scharfetter, "Temperature dependence of substrate current and hot carrier-induced degradation at low drain bias," *Symposium on VLSI Technology*, pp. 178–179, 1998.

- 15. N. Sano, M. Tomizawa, and A. Yoshii, "Temperature dependence of hot carrier effects in shortchannel Si-MOSFET's," *IEEE Trans. Electron Devices*, vol. 42, no. 12, pp. 2211–2216, 1995.

- W. Chen, R. Cheng, D. W. Wang, H. Song, X. Wang, H. Chen, E. Li, W. Y. Yin, and Y. Zhao, "Electrothermal effects on hot-carrier reliability in SOI MOSFETs-AC versus circuit-speed random stress," *IEEE Trans. Electron Devices*, vol. 63, no. 9, pp. 3669–3676, 2016.

- 17. D. K. Ferry, Semiconductor Transport, New York: Taylor & Francis Group, 2000.

- 18. M. Lundstrom, *Fundamentals of Carrier Transport*, 2nd ed., Cambridge, UK: Cambridge University Press, 2000.

- E. Pop, J. Rowlette, R. W. Dutton, and K. E. Goodson, "Joule heating under quasi-ballistic transport conditions in bulk and strained silicon devices," in *Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices (SISPAD)*, pp. 307–310, 2005.

- D. Vasileska, K. Raleva, and S. M. Goodnick, "Electrothermal studies of FD SOI Devices that utilize a new theoretical model for the temperature and thickness dependence of the thermal conductivity," *IEEE Trans. Electron Devices*, vol. 57, no. 3, pp. 726–728, 2010.

- W. Liu and M. Asheghi, "Thermal conductivity of measurements of ultra-thin single crystal silicon layers," J. Heat Transfer, vol. 128, no. 1, pp. 75–83, 2006.

- W. Liu, K. Etessam-Yazdani, R. Hussin, and M. Asheghi, "Modeling and data for thermal conductivity of ultrathin single-crystal SOI layers at high temperature," *IEEE Trans. Electron Devices*, vol. 53, no. 8, pp. 1868–1876, 2006.

- 23. Y. W. Kwon and H. Bang, *The Finite Element Method Using MATLAB*, 2nd ed., Boca Raton, FL: CRC Press, 2000.

- 24. E. Takeda and N. Suzuki, "An empirical model for device degradation due to hot-carrier injection," *IEEE Electron Device Lett.*, vol. 4, no. 4, pp. 111–113, 1983.

- S. Poli, S. Reggiani, M. Denison, E. Gnani, A. Gnudi, and G. Baccarani, "Temperature dependence of the threshold voltage shift induced by carrier injection in integrated STI-based LDMOS transistors," *IEEE Electron Device Lett.*, vol. 32, no. 6, pp. 791–793, 2011.

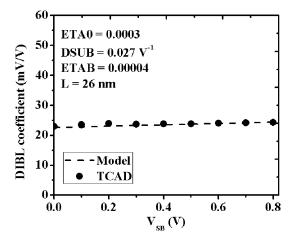

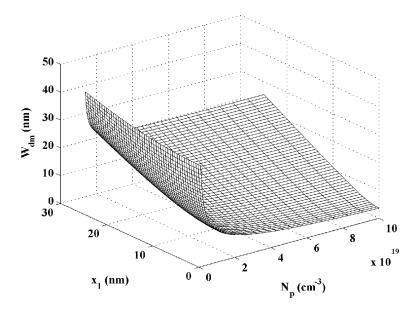

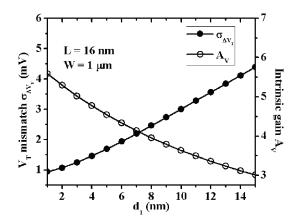

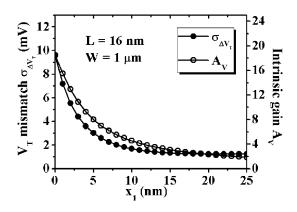

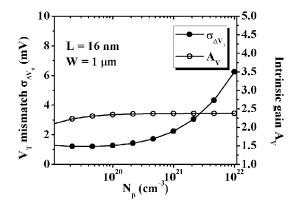

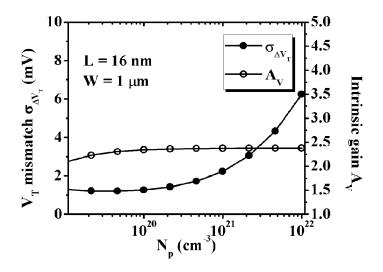

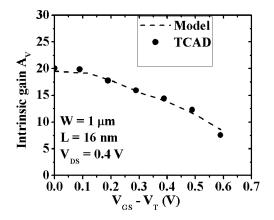

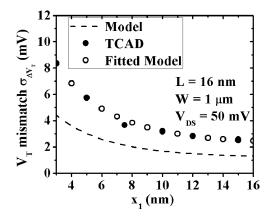

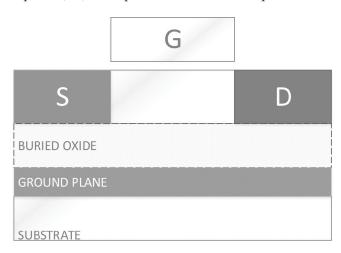

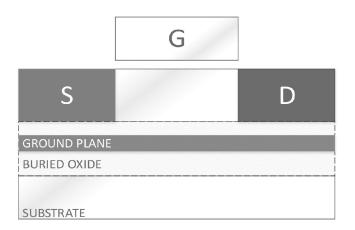

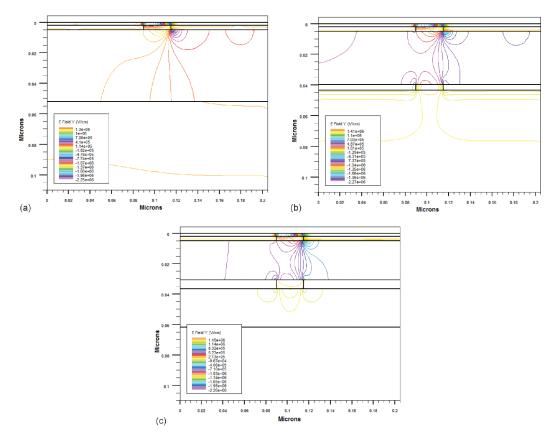

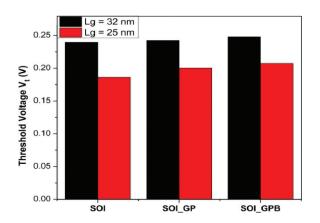

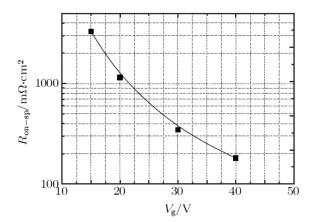

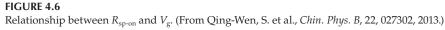

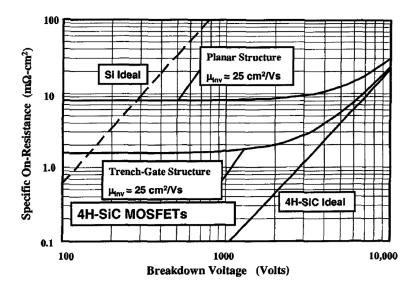

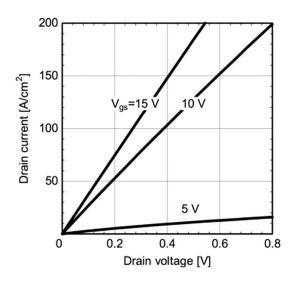

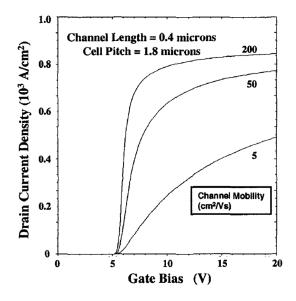

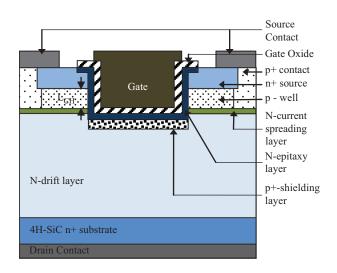

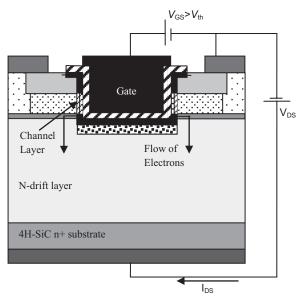

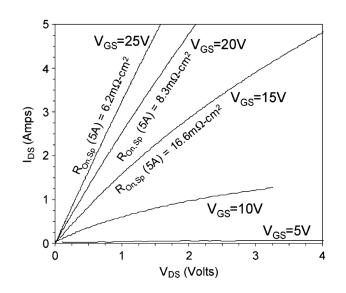

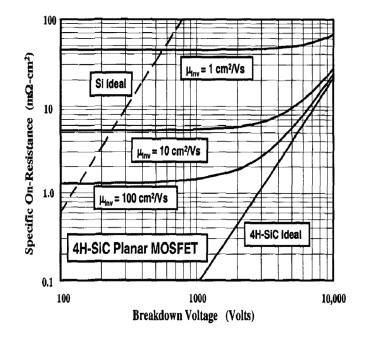

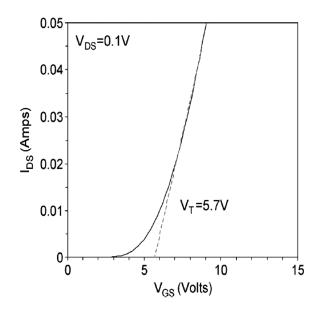

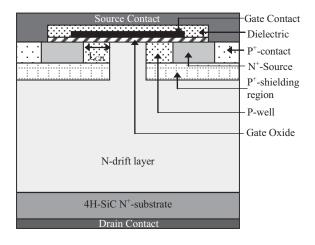

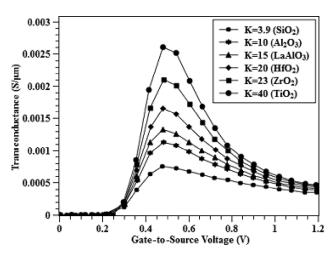

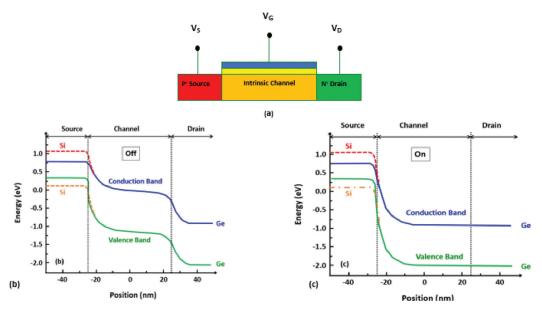

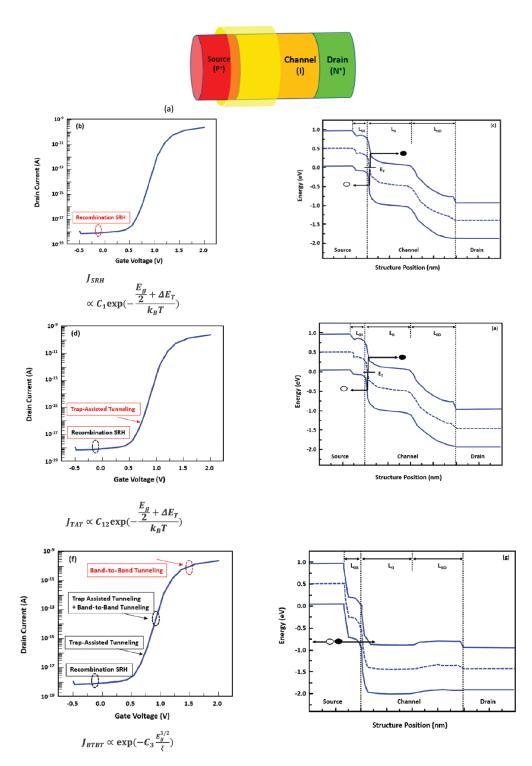

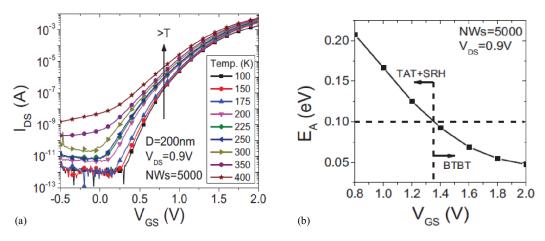

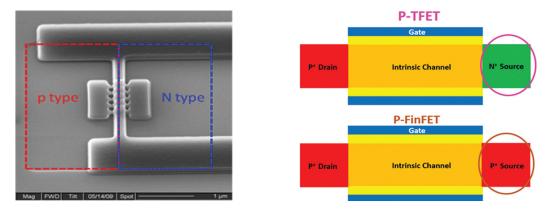

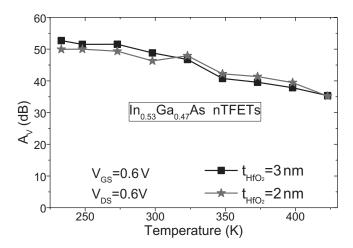

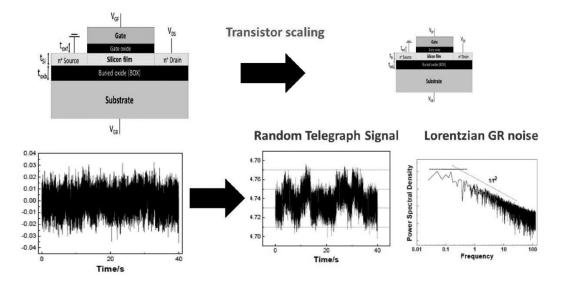

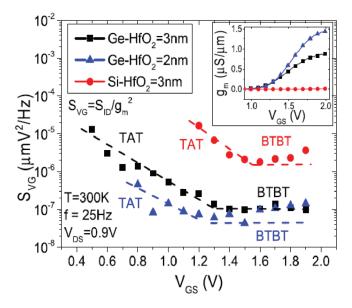

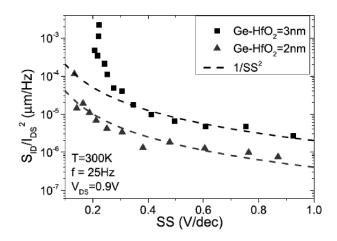

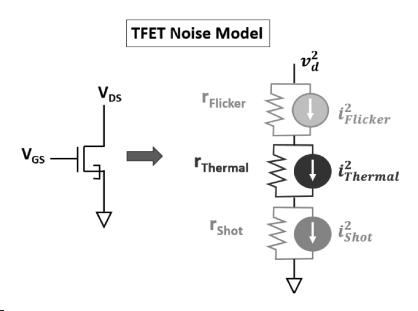

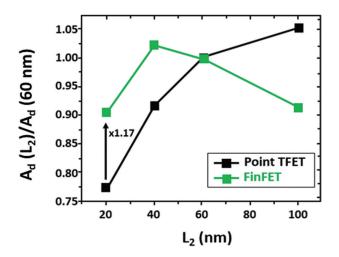

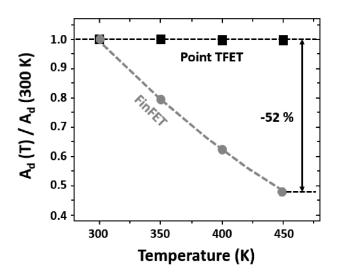

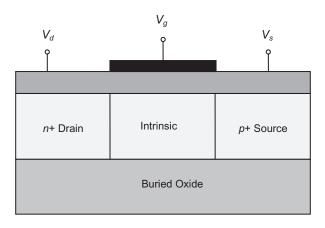

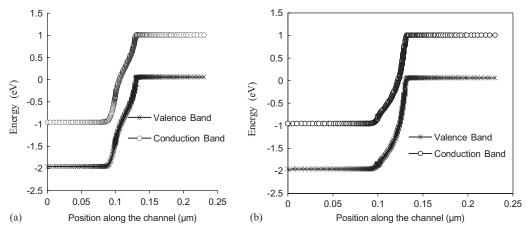

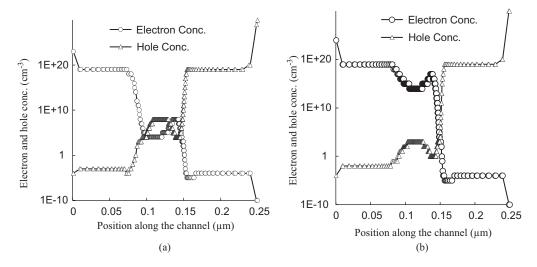

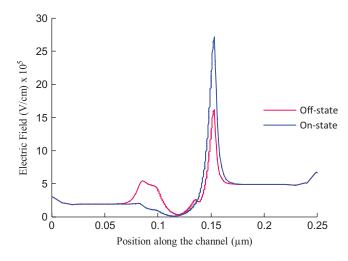

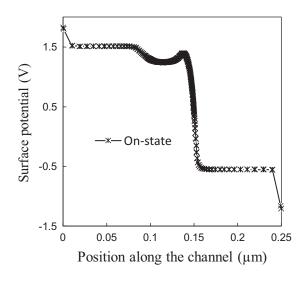

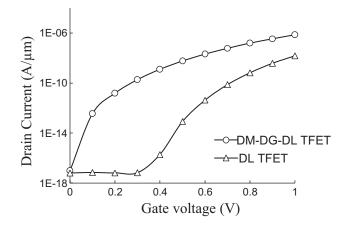

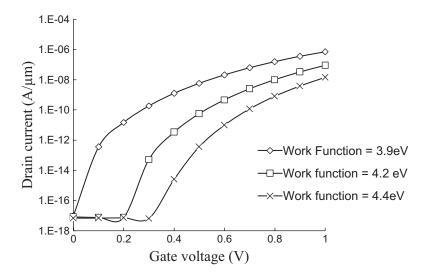

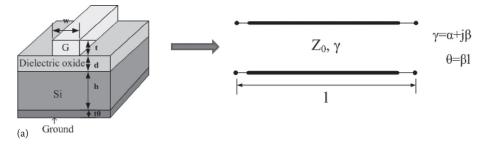

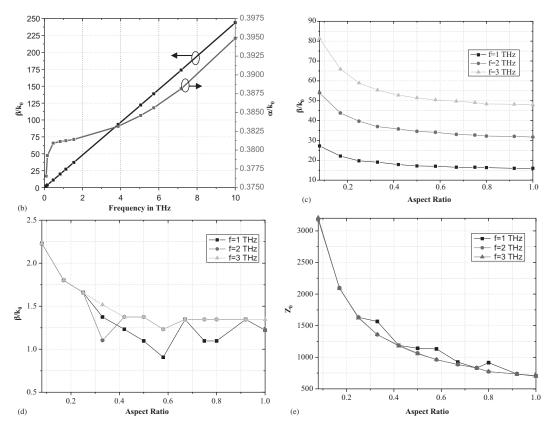

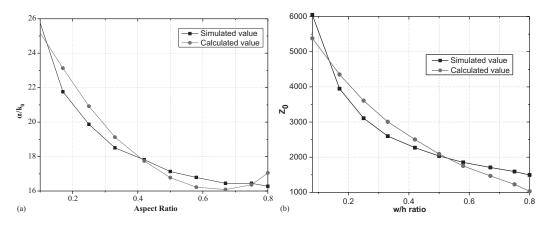

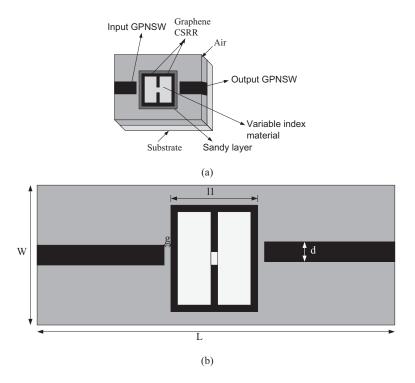

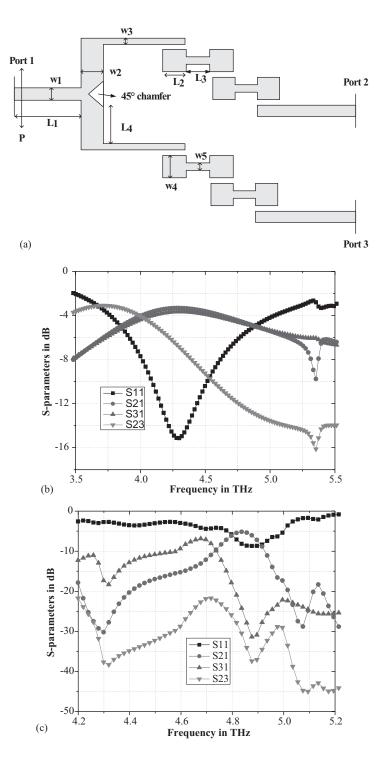

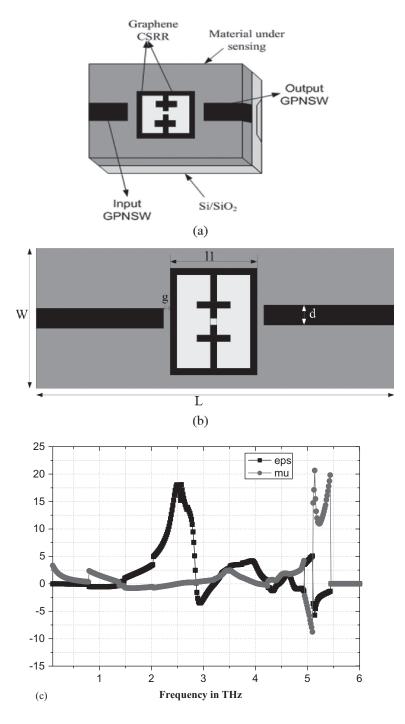

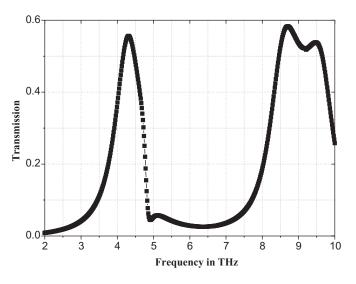

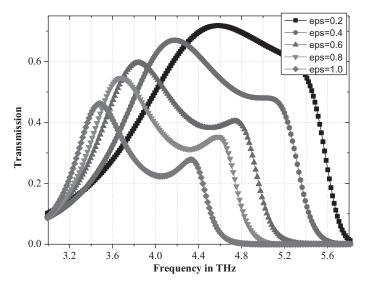

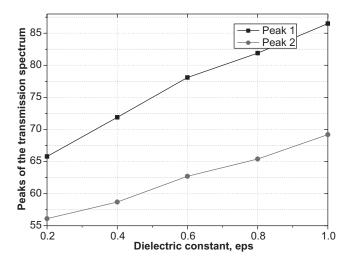

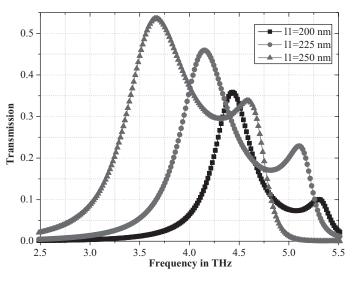

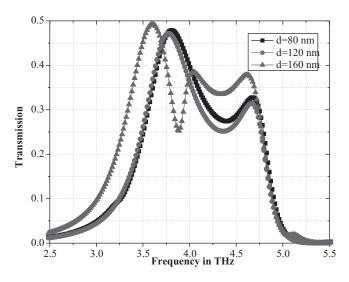

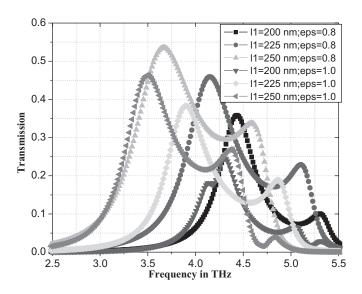

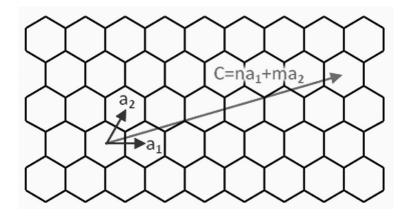

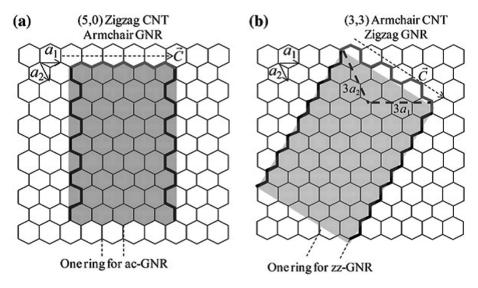

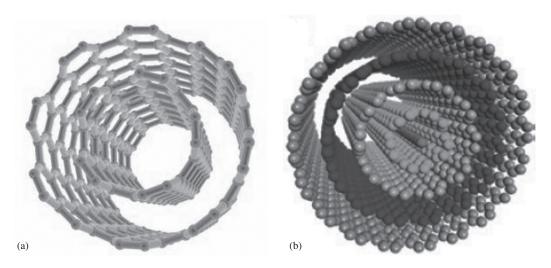

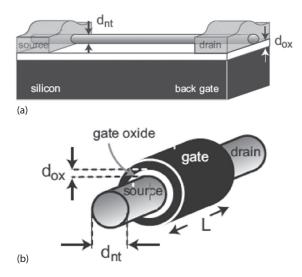

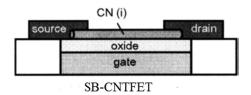

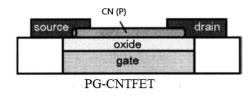

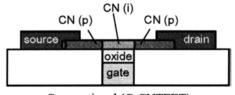

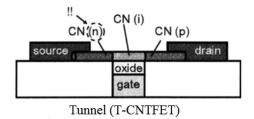

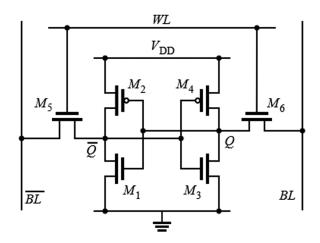

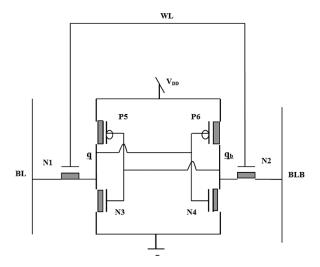

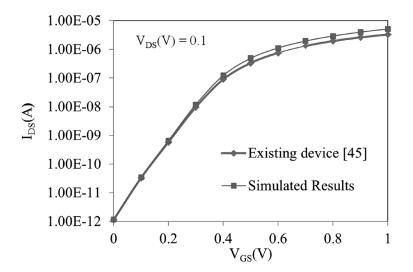

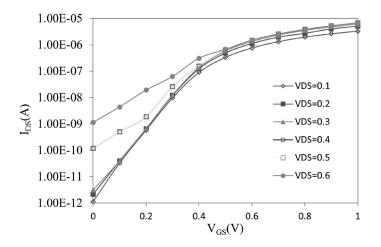

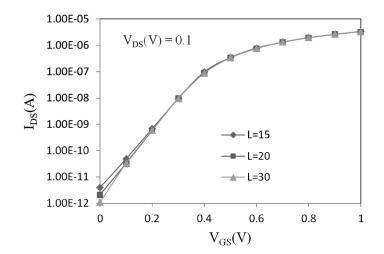

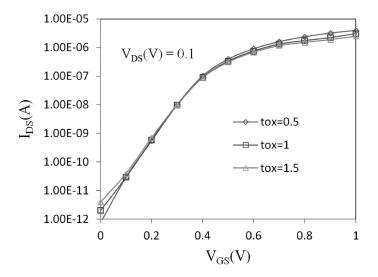

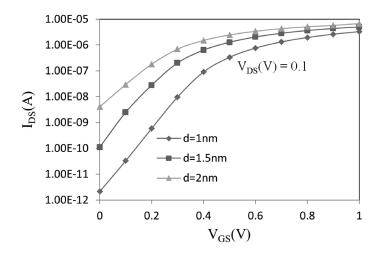

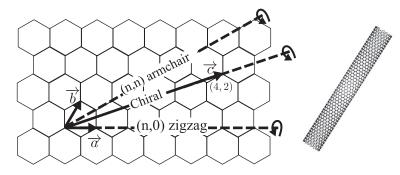

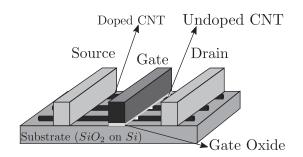

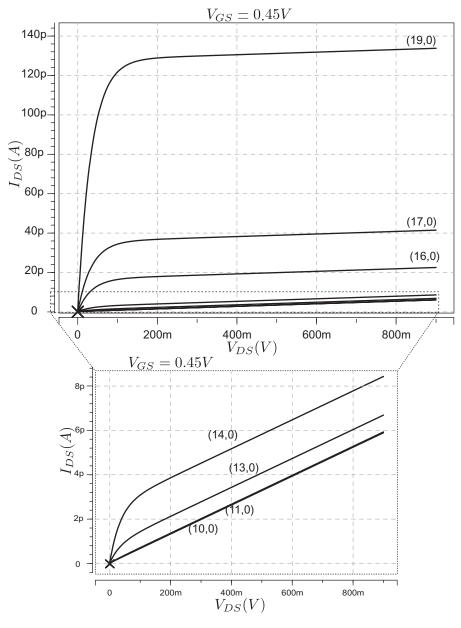

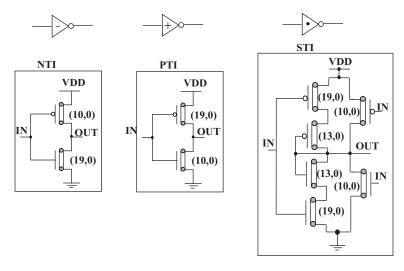

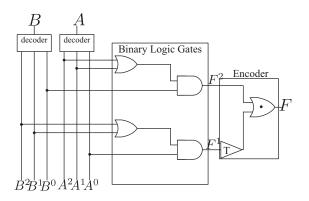

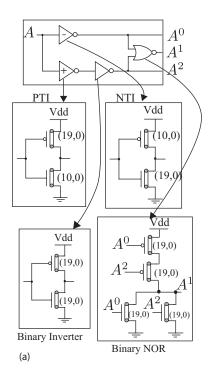

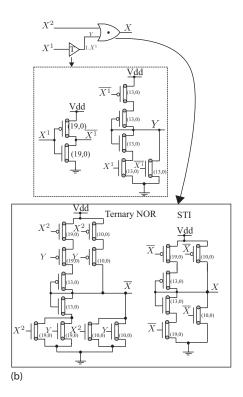

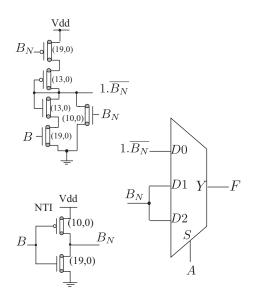

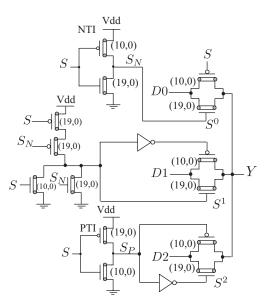

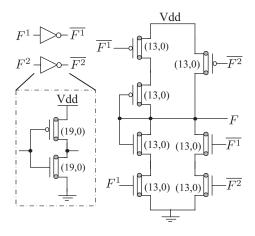

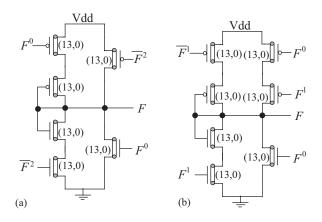

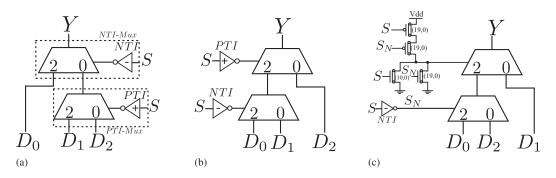

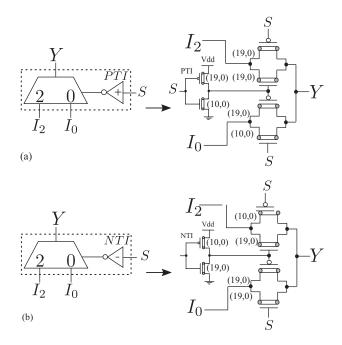

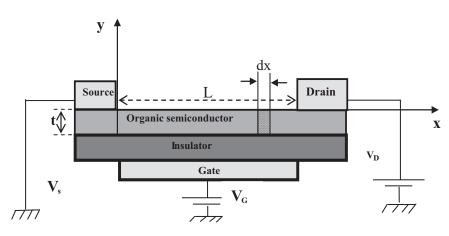

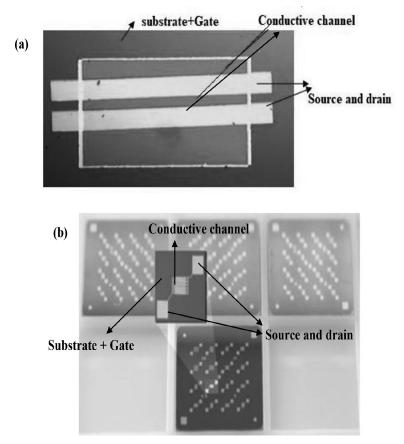

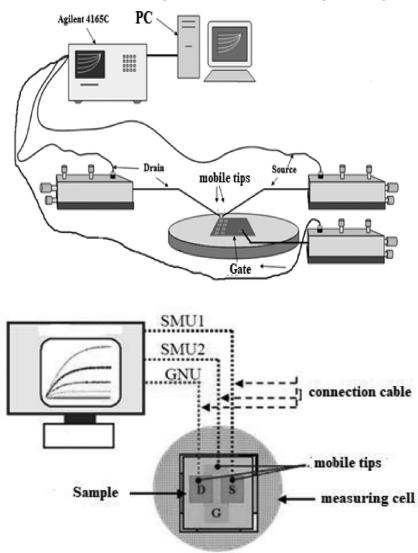

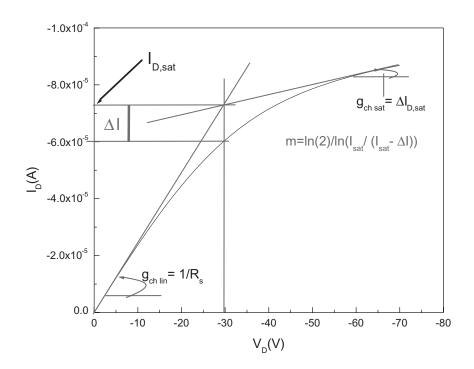

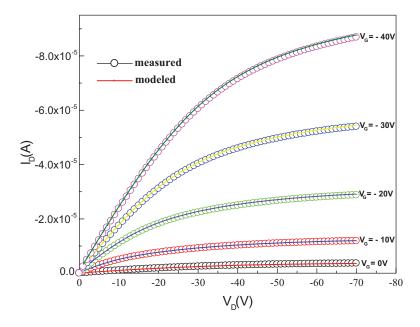

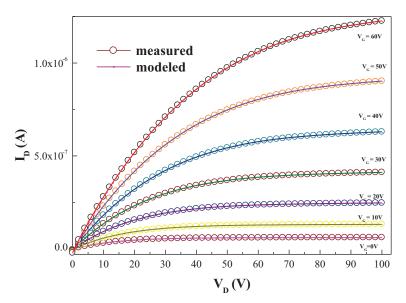

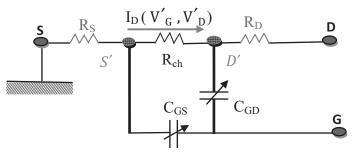

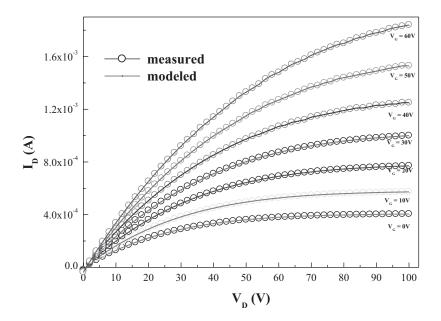

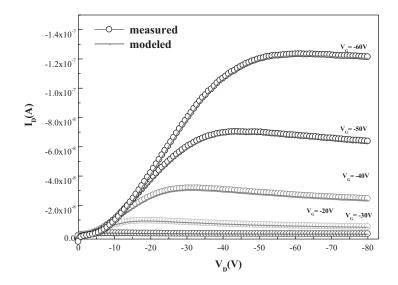

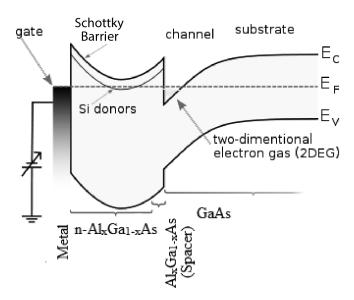

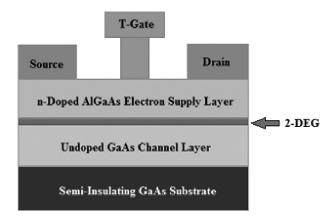

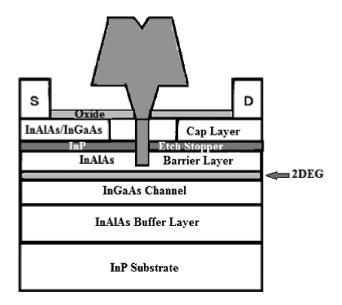

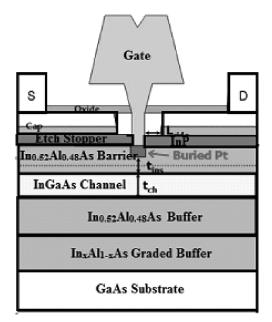

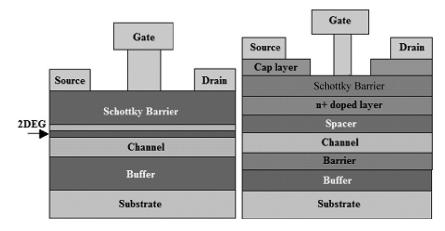

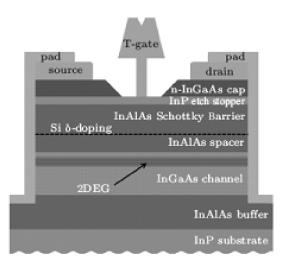

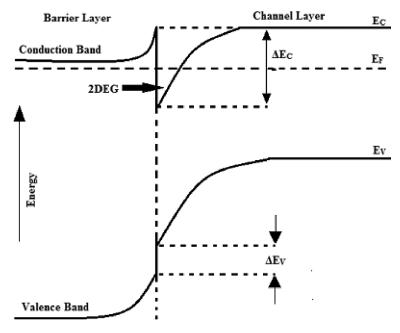

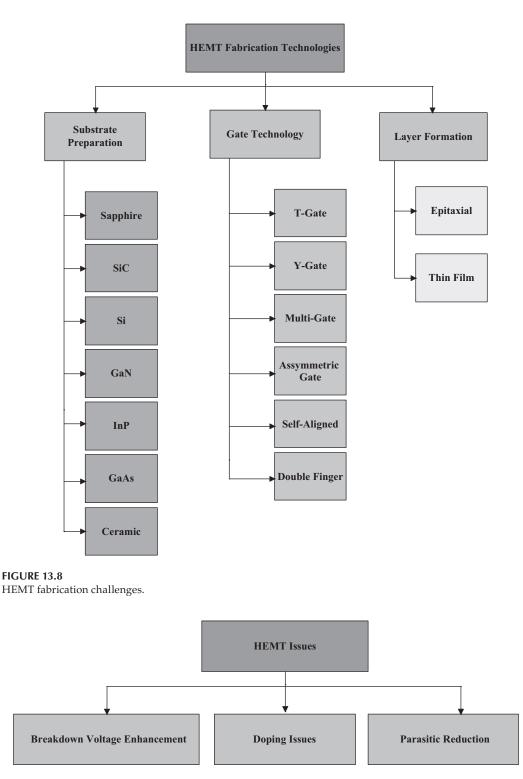

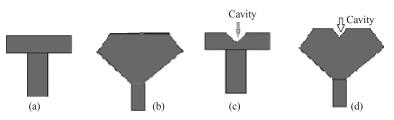

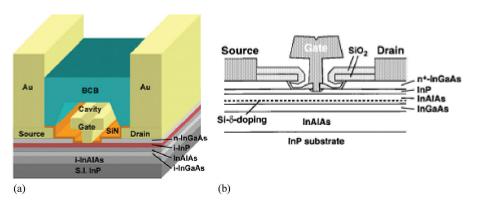

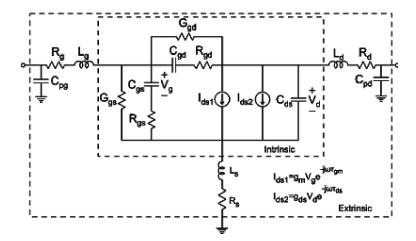

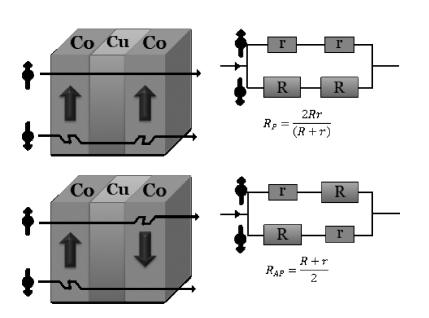

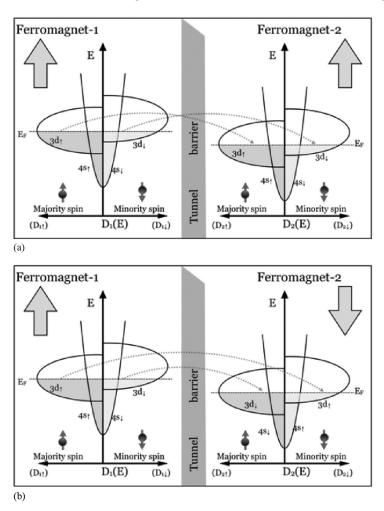

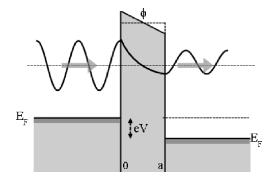

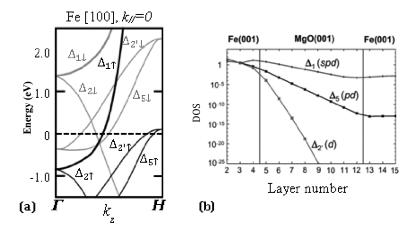

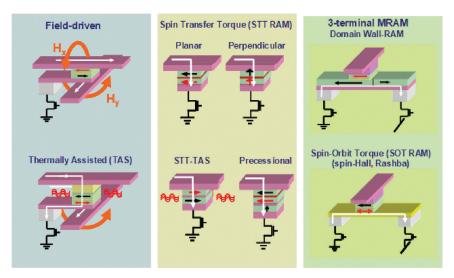

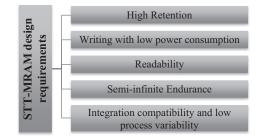

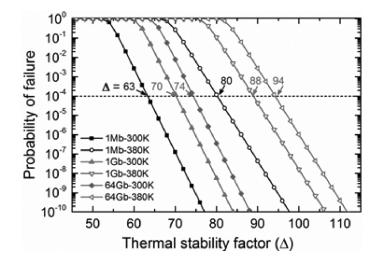

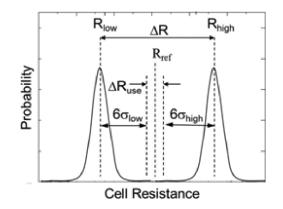

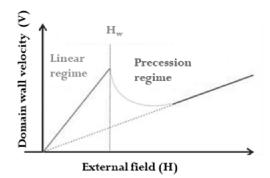

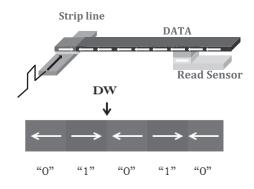

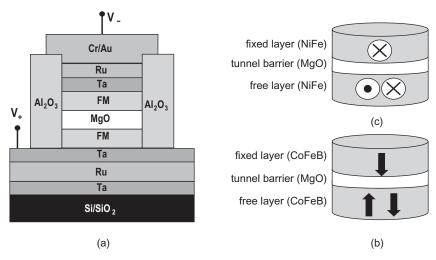

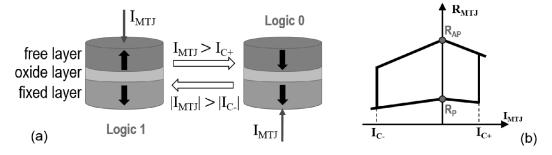

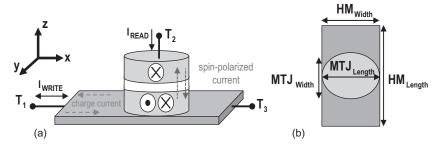

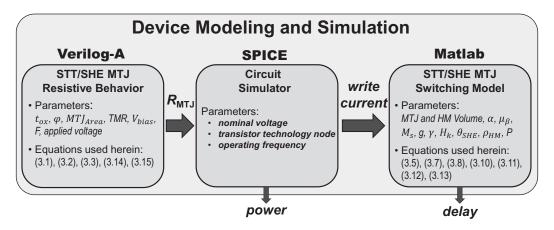

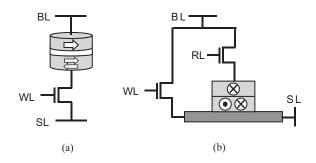

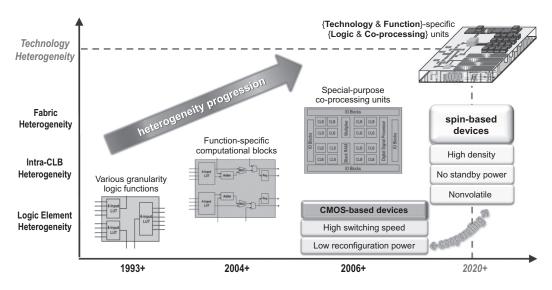

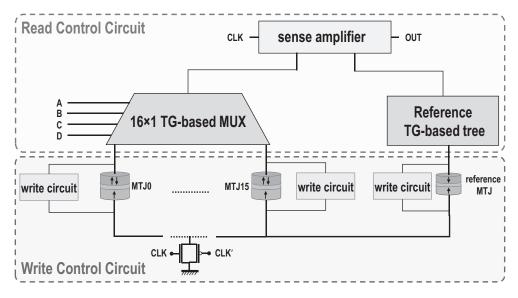

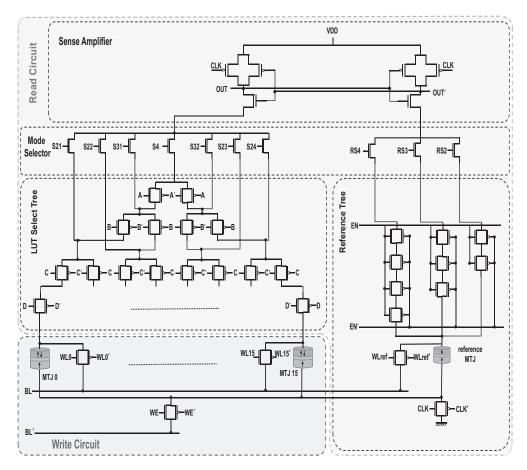

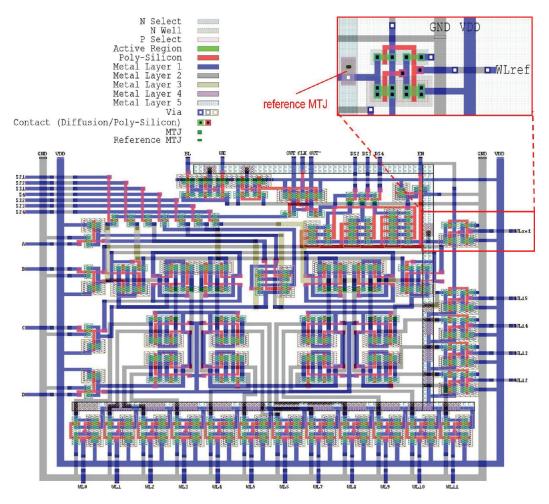

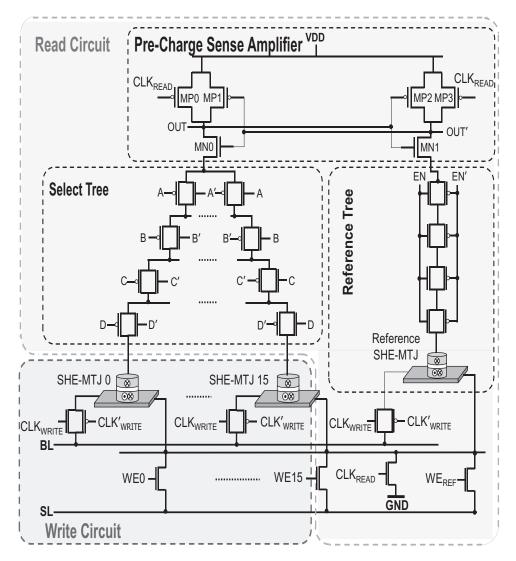

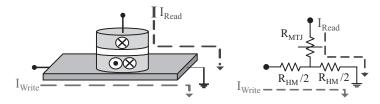

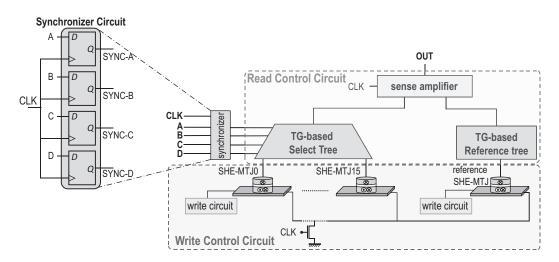

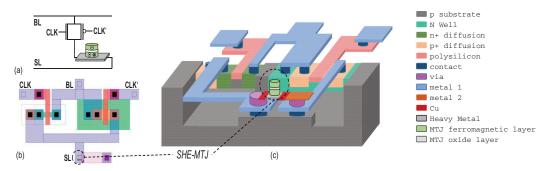

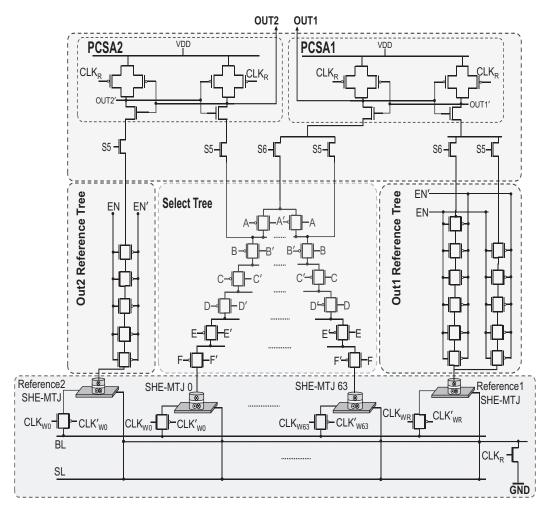

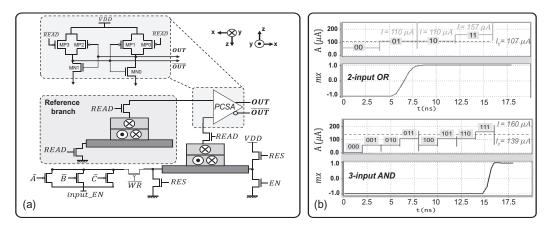

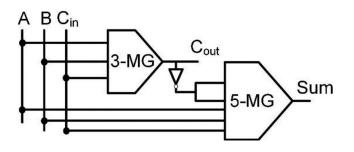

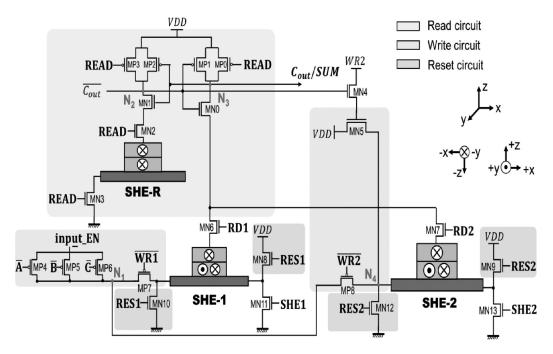

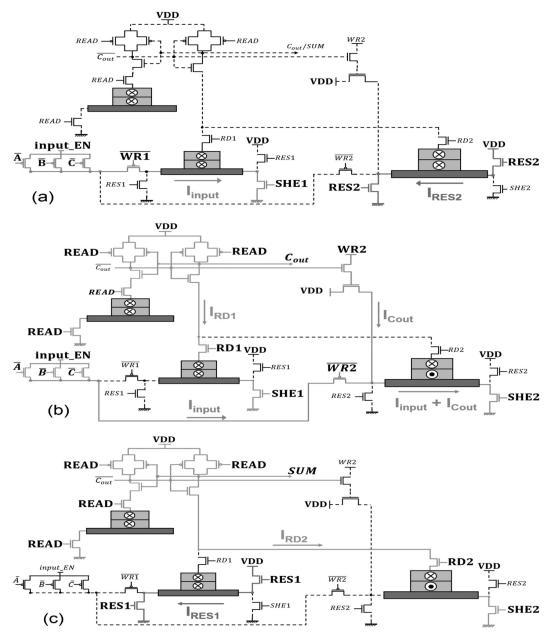

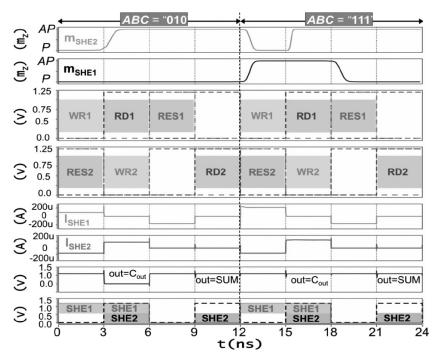

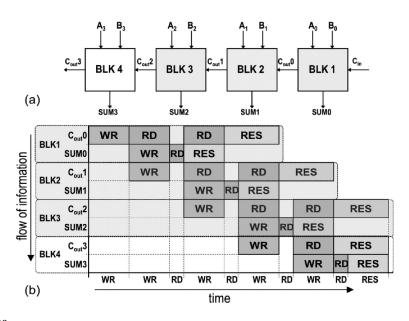

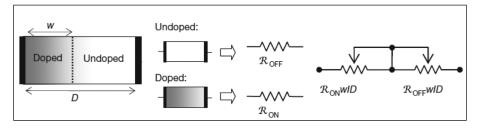

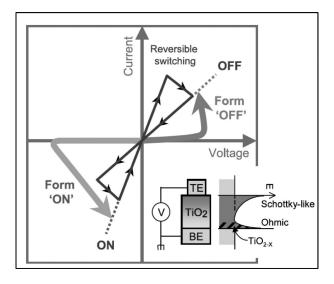

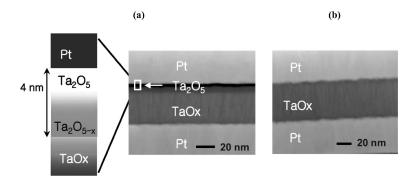

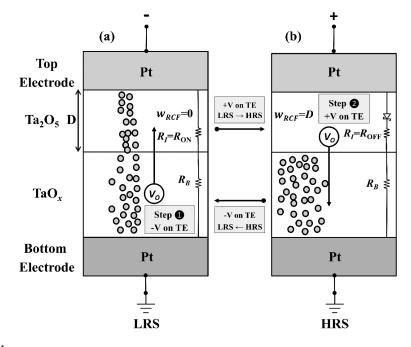

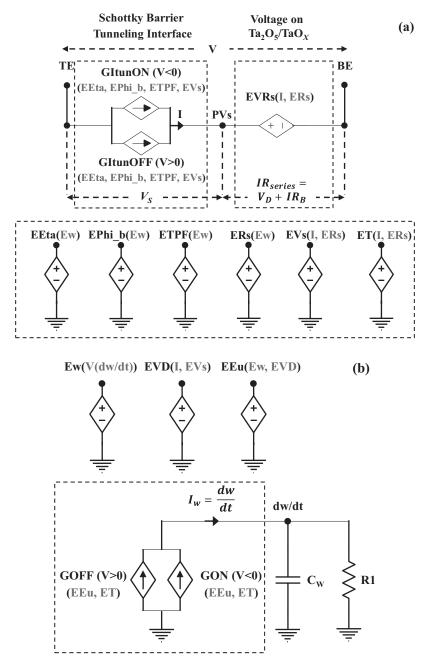

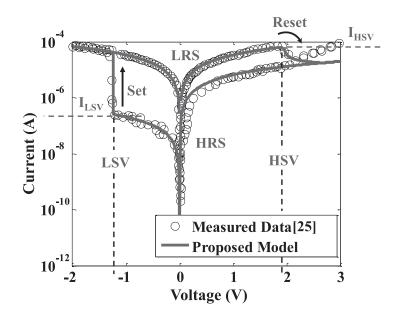

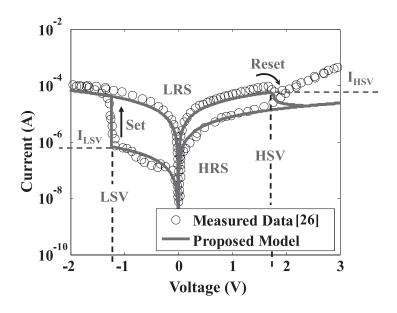

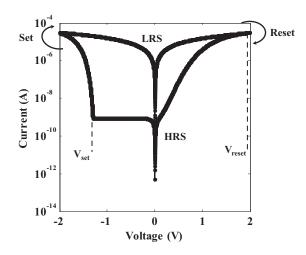

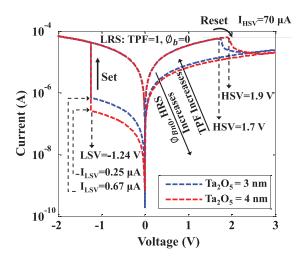

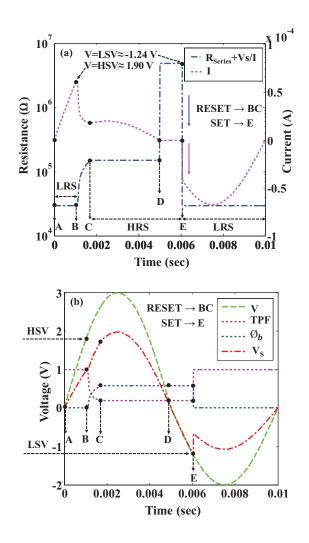

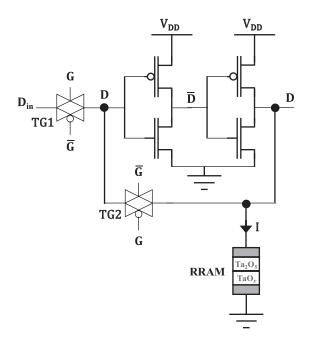

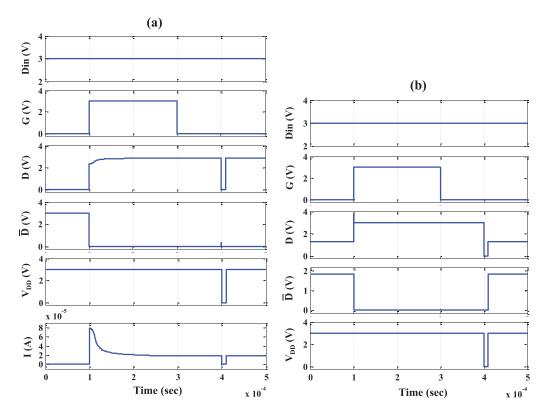

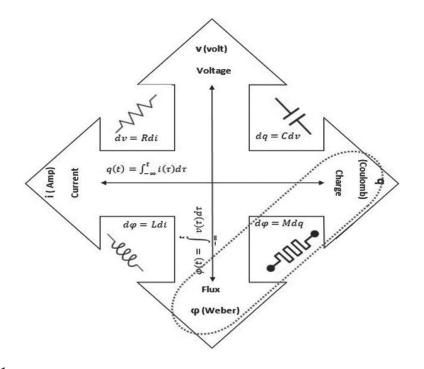

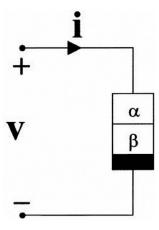

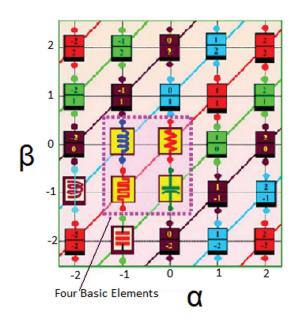

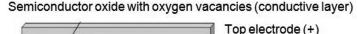

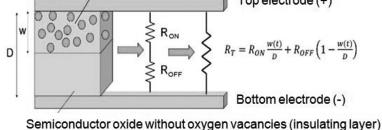

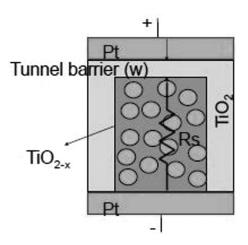

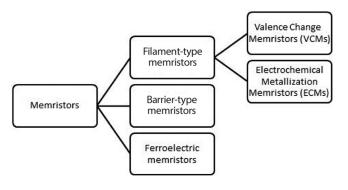

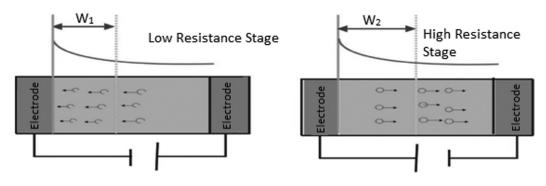

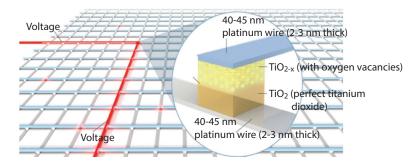

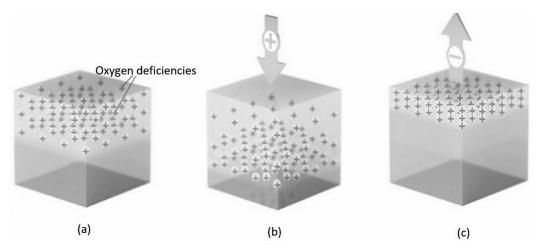

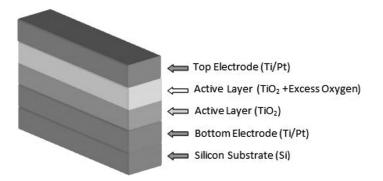

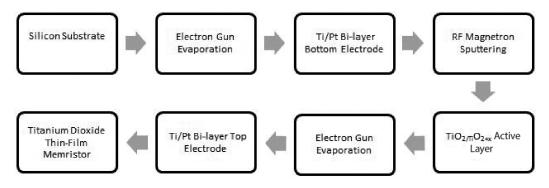

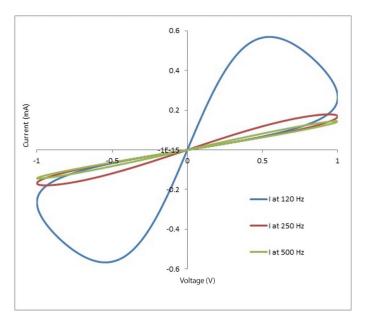

- B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer MoS<sub>2</sub> transistors," *Nature Nanotechnol.*, vol. 6, no. 3, pp. 147–150, 2011.